(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-533083

(P2016-533083A)

(43) 公表日 平成28年10月20日(2016.10.20)

(51) Int.Cl.

H03K 5/04 (2006.01)

G06F 1/08 (2006.01)

F 1

H03K 5/04

G06F 1/08

テーマコード(参考)

5 J 001

審査請求 未請求 予備審査請求 有 (全 29 頁)

(21) 出願番号 特願2016-531765 (P2016-531765)

(86) (22) 出願日 平成26年7月24日 (2014.7.24)

(85) 翻訳文提出日 平成28年3月24日 (2016.3.24)

(86) 國際出願番号 PCT/US2014/047959

(87) 國際公開番号 WO2015/017233

(87) 國際公開日 平成27年2月5日 (2015.2.5)

(31) 優先権主張番号 13/954,691

(32) 優先日 平成25年7月30日 (2013.7.30)

(33) 優先権主張国 米国(US)

(71) 出願人 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】デューティ・サイクル補正を含むクロック・ダブル

## (57) 【要約】

典型的な実施形態は、クロック・ダブルに関する。デバイスは、入力クロック信号を受け取り、補正されたクロック信号を伝達する、ように構成されたデューティ・サイクル補正回路を含み得る。デューティ・サイクル補正回路は、入力クロック信号の第1のサイクルの間、出力電圧を伝達し、入力クロック信号の第2のサイクルの間、第1の回路の電流ミスマッチを補正する、ための第1の回路を含み得る。デューティ・サイクル補正回路はまた、第2のサイクルの間、出力電圧を伝達し、第1のサイクルの間、第2の回路の電流ミスマッチを補正する、ための第2の回路を含み得る。さらに、デバイスは、補正されたクロック信号を受け取り、出力クロックを生成する、ためのクロック生成器を含み得る。

**【特許請求の範囲】****【請求項 1】**

デバイスであって、前記デバイスは下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を伝達するように構成されたデューティ・サイクル補正回路であって、

前記入力クロック信号の第1のサイクルの間、出力電圧を伝達し、前記入力クロック信号の第2のサイクルの間、第1の回路の電流ミスマッチを補正する、第1の回路と、

前記第2のサイクルの間、前記出力電圧を伝達し、前記第1のサイクルの間、第2の回路の電流ミスマッチを補正する、第2の回路と、

を含むデューティ・サイクル補正回路と、

前記補正されたクロック信号を受け取り、出力クロックを生成するためのクロック生成器。

**【請求項 2】**

前記第1のサイクルおよび前記第2のサイクルの各々の間、前記出力電圧を受け取るように構成された出力コンデンサをさらに備える、請求項1に記載のデバイス。

**【請求項 3】**

前記出力クロックは、実質的に50%であるデューティ・サイクルと、前記補正されたクロック信号の周波数に対して増加された周波数とを有する、請求項1に記載のデバイス。

**【請求項 4】**

前記第1の回路は、前記第2のサイクルの間、第1および第2の電流を受け取るように構成されたコンデンサの両端の電圧と、基準電圧とを比較するためのトランジスタの差動ペアを含む、請求項1に記載のデバイス。

**【請求項 5】**

前記コンデンサの両端の前記電圧が前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、請求項4に記載のデバイス。

**【請求項 6】**

前記第2の回路は、前記第1のサイクルの間、第1および第2の電流を受け取るように構成されたコンデンサの両端の電圧と、基準電圧とを比較するためのトランジスタの差動ペアを含む、請求項1に記載のデバイス。

**【請求項 7】**

前記コンデンサの両端の前記電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、請求項6に記載のデバイス。

**【請求項 8】**

デバイスであって、前記デバイスは下記を備える、

入力クロック信号のフェーズの間、出力電圧を生成するように構成された第1のチャージ・ポンプと、

前記入力クロック信号のもう1つの、異なるフェーズの間、前記出力電圧を生成するための第2のチャージ・ポンプ、ここで、前記第1および前記第2のチャージ・ポンプの各々は、前記入力クロック信号に基づいて、補正されたクロック信号を生成するように構成される、と、

前記第1および前記第2のチャージ・ポンプの各々に接続され、前記補正されたクロック信号を受け取り、前記補正されたクロック信号の周波数に対して2倍された周波数を有する出力クロック信号を生成するように構成されたクロック生成器。

**【請求項 9】**

前記第1のチャージ・ポンプはさらに、前記入力クロック信号のもう1つの、異なるフェーズの間、前記第1のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを検出し補正するように構成された、請求項8に記載のデバイス。

**【請求項 10】**

前記第2のチャージ・ポンプはさらに、前記入力クロック信号のフェーズの間、前記第

10

20

30

40

50

2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを検出し補正するよう構成された、請求項8に記載のデバイス。

【請求項11】

前記出力クロック信号は、実質的に50%であるデューティ・サイクルを有する、請求項8に記載のデバイス。

【請求項12】

前記第1のチャージ・ポンプはさらに、前記入力クロック信号のもう1つの、異なるフェーズの間、前記第1のチャージ・ポンプのアップ電流およびダウン電流を受け取るよう構成されたコンデンサを備える、請求項8に記載のデバイス。

【請求項13】

前記第1のチャージ・ポンプはさらに、前記コンデンサの両端の電圧と基準電圧との差分を測定するよう構成されたトランジスタの差動ペアを備える、請求項12に記載のデバイス。

【請求項14】

前記コンデンサの両端の前記電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、請求項13に記載のデバイス。

【請求項15】

前記第2のチャージ・ポンプはさらに、前記入力クロック信号のフェーズの間、前記第2のチャージ・ポンプのアップ電流およびダウン電流を受け取るよう構成されたコンデンサを備える、請求項8に記載のデバイス。

【請求項16】

前記第2のチャージ・ポンプはさらに、前記コンデンサの両端の電圧と基準電圧との差分を測定するよう構成されたトランジスタの差動ペアを備える、請求項15に記載のデバイス。

【請求項17】

前記コンデンサの両端の前記電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、請求項16に記載のデバイス。

【請求項18】

方法であって、前記方法は下記を備える、

複数のチャージ・ポンプを用いて、補正されたクロック信号を生成すること、ここで、前記複数のチャージ・ポンプの各々は、入力クロック信号のサイクルの一部の間に、電流ミスマッチを補正するよう構成される、と、

前記補正されたクロック信号の周波数よりも大きな周波数を有する出力クロックを生成すること。

【請求項19】

補正されたクロック信号を生成することは、

前記入力クロック信号の第1のサイクルの間、前記複数のチャージ・ポンプのうちの第1のチャージ・ポンプを用いて出力電圧を生成すること、

前記入力クロック信号の第2のサイクルの間、前記複数のチャージ・ポンプのうちの第2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

前記第2のサイクルの間、前記第2のチャージ・ポンプを用いて、前記出力電圧を生成することと、

前記第1のサイクルの間、前記第1のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

を備える、請求項18に記載の方法。

【請求項20】

前記第1のチャージ・ポンプの第1の前記電流と前記第2の電流との間の前記ミスマッチを検出することと、

前記第2のチャージ・ポンプの前記第1の電流と前記第2の電流との間の前記ミスマッチを検出することと、

10

20

30

40

50

をさらに備える、請求項 19 に記載の方法。

【請求項 21】

前記第 1 のチャージ・ポンプおよび前記第 2 のチャージ・ポンプの何れかにおける前記ミスマッチを検出することは、基準電圧を、コンデンサの両端に蓄積された電圧と比較することを備える、請求項 20 に記載の方法。

【請求項 22】

方法であって、前記方法は下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を生成することと、

前記入力クロック信号の第 1 のサイクルの間、第 1 のチャージ・ポンプを用いて出力電圧を生成することと、

前記入力クロック信号の第 2 のサイクルの間、第 2 のチャージ・ポンプの第 1 の電流と第 2 の電流との間のミスマッチを補正することと、

前記第 2 のサイクルの間、前記第 2 のチャージ・ポンプを用いて、前記出力電圧を生成することと、前記第 1 のサイクルの間、前記第 1 のチャージ・ポンプの第 1 の電流と第 2 の電流との間のミスマッチを補正することと、

前記補正されたクロック信号に基づいて、2 倍されたクロック信号を生成すること。

【請求項 23】

2 倍されたクロック信号を生成することは、実質的に 50 % であるデューティ・サイクルと、前記 2 倍されたクロック信号の周波数よりも小さい周波数とを有する前記補正されたクロック信号に基づいて、実質的に 50 % であるデューティ・サイクルを有する前記 2 倍されたクロック信号を生成することを備える、請求項 22 に記載の方法。

【請求項 24】

デバイスであって、前記デバイスは下記を備える、

補正されたクロック信号を生成するための手段、ここで、前記生成するための手段は、入力クロック信号のサイクルの一部の間に、電流ミスマッチを補正するように構成される、と、

前記補正されたクロック信号の周波数よりも大きな周波数を有する出力クロック信号を生成するための手段。

【請求項 25】

デバイスであって、前記デバイスは下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を生成するための手段と、

前記入力クロック信号の各サイクルの間に、出力電圧を生成するための手段と、

前記入力クロック信号の各サイクルの間に、電流ミスマッチを補正するための手段と、

前記補正されたクロック信号に基づいて、出力クロック信号を生成するための手段。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願に対する相互参照

[0001] 本願は、その全体が本明細書において参照によって明確に組み込まれている「CLOCK DOUBLER INCLUDING DUTY CYCLE CORRECTION」と題された 2013 年 7 月 30 日出願の米国出願番号第 13/954,691 号の優先権を主張する。

【0002】

[0002] 本発明は、一般に、デューティ・サイクル補正を含むクロック・ダブル (clock doubler) に関する。さらに詳しくは、本発明は、補正されたデューティ・サイクルに基づいてクロック信号を生成するための実施形態に関する。

【背景技術】

【0003】

[0003] クロック信号は、さまざまなタイプの発振器および支援回路を用いて生成され得、一般に、多くの電子回路において、さまざまな目的のために使用される。例えば、クロック信号は、プロセッサ、メモリ・デバイス等のようなデジタル回路における同期回路 (

10

20

30

40

50

例えば、フリップ・フロップ)をトリガするために使用され得る。

【0004】

[0004]クロック信号は、論理 High (logic high) における持続時間、および論理 Low (logic low) における持続時間によって決定されるデューティ・サイクルを有し、論理 High と論理 Lowとの間を反復して遷移する。可能な限り 50 % に近いデューティ・サイクルを有するクロック信号を生成し、これによって、論理高の持続時間が、論理低の持続時間に近くなることが所望され得る。デジタル回路は、より高速な動作速度を達成するように同期回路をトリガするために、クロック信号の立ち上がりエッジと立ち下がりエッジとの両方を使用し得る。クロック信号のための 50 % デューティ・サイクルは、同期回路に最大のタイミング・マージンを提供し得る。

10

【0005】

[0005]クロック信号のデューティ・サイクルは、クロック信号を生成するために使用されるトランジスタ・デバイスにおけるミスマッチのようなさまざまな現象によって歪められ得る。デバイス・ミスマッチを最小化するために、クロック生成および配信回路を設計する際にはしばしば、多大な注意が払われる。高度な IC プロセスで製造されたデジタル回路は、一般に、例えば 1 ギガ・ヘルツ (GHz) またはそれ以上のような高速で動作する。この高速は、例えば 1 GHz に対して 1 ナノ秒 (nsec) のようなより小さなクロック周期に相当する。小さな回路ミスマッチは、その後、より小さなクロック周期のデューティ・サイクルにおける比較的大きな誤差へと変わり得る。

20

【発明の概要】

【0006】

[0006]クロック・デューティ・サイクル問題は、良好なデューティ・サイクルを有するクロック信号を生成するために、しばしば、所望の周波数の 2 倍で発振器を動作させ、発振器出力信号を 2 で除することによって対処される。しかしながら、このアプローチは、いくつかの理由により、望ましくないか、または不適切であり得る。第 1 に、発振器および 2 分周回路 (divide-by-2 circuit) を、所望の周波数の 2 倍で動作させるために、より多くの電力が消費される。第 2 に、2 分割回路におけるランダムなデバイス・ミスマッチによって、クロック信号内に、著しいデューティ・サイクル歪みがなお存在し得る。

【0007】

[0007]クロック・ダグラに対するニーズがある。さらに詳しくは、補正されたデューティ・サイクルに基づいてクロック信号を生成するための、クロック・ダグラに関連する実施形態に対するニーズがある。

30

【図面の簡単な説明】

【0008】

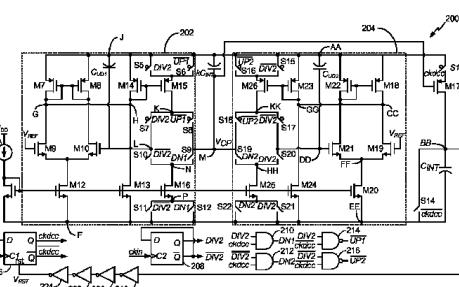

【図 1】[0008]図 1 は、デューティ・サイクル補正器を例示する。

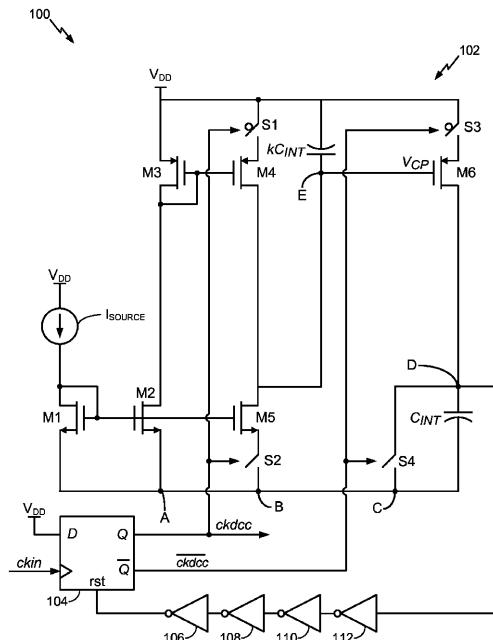

【図 2 A】[0009]図 2 A は、本発明の典型的な実施形態に従うデューティ・サイクル補正器を図示する。

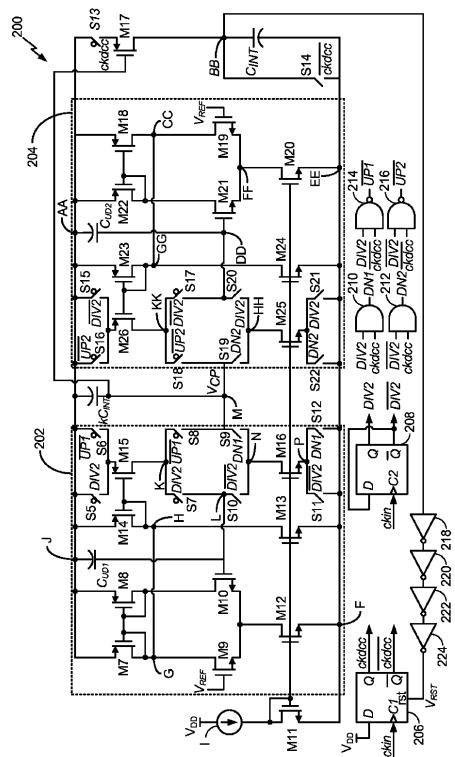

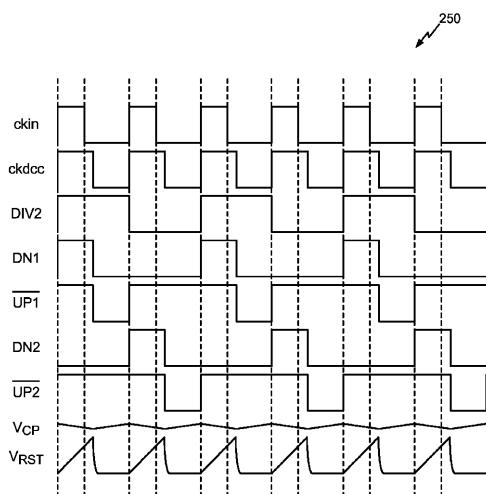

【図 2 B】[0010]図 2 B は、図 2 A のデューティ・サイクル補正器に関連付けられたタイミング図である。

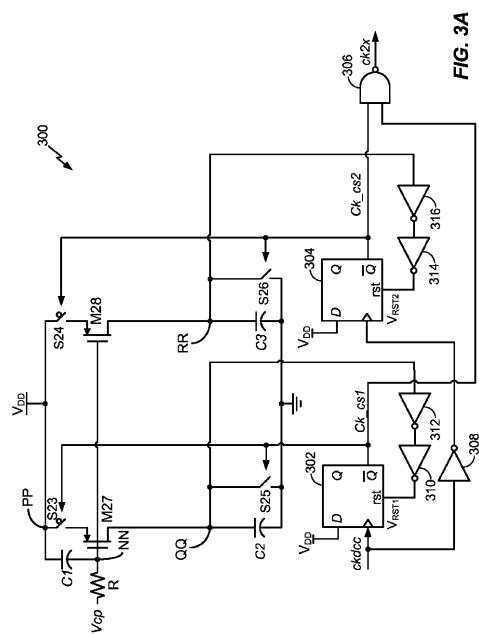

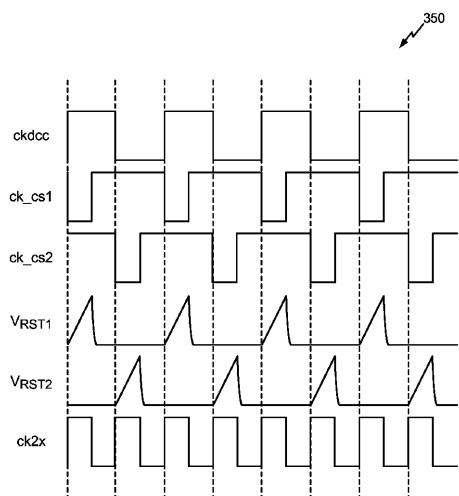

【図 3 A】[0011]図 3 A は、本発明の典型的な実施形態に従うクロック生成器を例示する。

40

【図 3 B】[0012]図 3 B は、図 3 A のクロック生成器に関連付けられたタイミング図である。

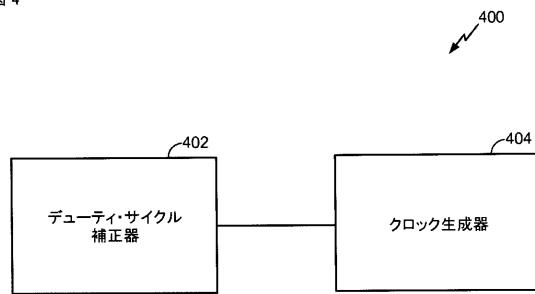

【図 4】[0013]図 4 は、本発明の典型的な実施形態に従う、デューティ・サイクル補正器およびクロック生成器を含むクロック・ダグラのブロック図である。

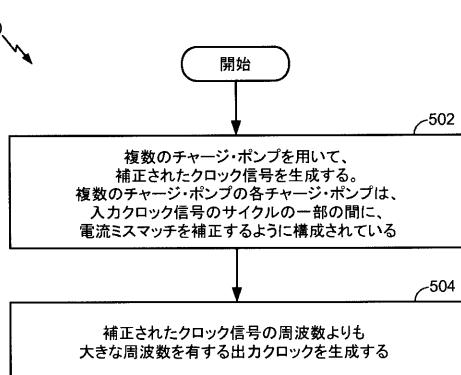

【図 5】[0014]図 5 は、本発明の典型的な実施形態に従う方法を図示するフローチャートである。

【図 6】[0015]図 6 は、本発明の典型的な実施形態に従う別のある方法を図示するフローチャートである。

【図 7】[0016]図 7 は、本発明の典型的な実施形態に従う、デューティ・サイクル補正器

50

およびクロック生成器を含むデバイスを例示する。

【発明を実施するための形態】

【0009】

[0017]添付図面に関連して以下に記載される詳細な説明は、本発明の典型的な実施形態の説明として意図されており、本発明が実現される唯一の実施形態を表すとは意図されていない。この説明を通じて使用されている「典型的」という用語は、「例、事例、または例示として役立つ」ことを意味しており、他の典型的な実施形態よりも好適であるとか有利であるとか必ずしも解釈されるべきではない。この詳細な説明は、本発明の典型的な実施形態の完全な理解を提供するための具体的な詳細を含んでいる。本発明の典型的な実施形態は、これら具体的な詳細無しで実現され得ることが当業者に明らかになるだろう。いくつかの事例では、本明細書に表された典型的な実施形態の新規性を不明確にすることを避けるために、周知の構成およびデバイスが、ブロック図形式で図示される。

10

【0010】

[0018]当業者によってしばしば認識されるであろうが、1つの水晶発振器基準クロック（例えば、19.2MHz）だけが、フェーズ・ロック・ループ（PLL）ベースの周波数シンセサイザに利用可能である。リング発振器電圧制御発振器（VCO）を用いたPLLの場合、PLLの帯域幅を増加させることによって、出力フェーズ・ノイズが、大幅に改善され得る。所与の基準周波数のための最大安定帯域幅のためにPLLが既に設計されている場合、この帯域幅はさらに、基準周波数を増加することのみによって増加され得る。

20

【0011】

[0019]図1は、デューティ・サイクル補正器100を図示する。デューティ・サイクル補正器100は、チャージ・ポンプ102、フリップ・フロップ104、論理回路106、108、110および112を含む。例示されるように、論理デバイス106、108、110および112の各々は、インバータを備え得る。フリップ・フロップ104は、50%ではないデューティ・サイクルを有する入力クロック信号ckinを受け取るように構成される。さらに、フリップ・フロップ104は、ポートDを介して電源電圧VDDを受け取り、リセット・ポートrstを介してフィードバック信号を受け取るように構成される。フリップ・フロップ104はさらに、ポートQを介してクロック出力ckdccを出力し、ポート

30

【数1】

$\overline{ckdcc}$

を介してクロック出力

【数2】

$\overline{Q}$

40

を出力するように構成される。

【0012】

[0020]チャージ・ポンプ102は、電流源ISOURCE、トランジスタM1～M6、コンデンサkCINTおよびCINT、およびスイッチS1～S4を含む。電流源ISOURCEは、電源電圧VDDとトランジスタM1のドレンとの間に接続され、それはさらに、トランジスタM1のゲート、トランジスタM2のゲート、およびトランジスタM5のゲートに接続されている。トランジスタM1のソースは、ノードAに接続され、それはさらに、ノードBと、トランジスタM2のソースとに接続されている。トランジスタM2のドレンは、トランジスタM3のドレンに接続され、それはさらに、トランジスタM3のゲート、およびトランジスタM4のゲートに接続されている。トランジスタM3のソースは

50

、電源電圧  $V_{DD}$  に接続され、トランジスタ M4 のソースは、スイッチ S1 を介して電源電圧  $V_{DD}$  に切り替え可能に（例えば、選択的に）接続されている。トランジスタ M4 のドレンは、トランジスタ M5 のドレンに接続され、トランジスタ M5 のソースは、スイッチ S2 介してノード B に切り替え可能に接続されている。

【0013】

[0021]コンデンサ  $C_{INT}$  は、電源電圧  $V_{DD}$  とノード E との間に接続され、それは、トランジスタ M5 のドレンと、トランジスタ M6 のゲートとに接続されている。コンデンサ  $C_{INT}$  は、ノード C と、ノード D を介したトランジスタ M6 のドレンとの間に接続されている。トランジスタ M6 は、スイッチ S3 を介して電源電圧  $V_{DD}$  に切り替え可能に接続され、ノード C とノード D とが、スイッチ S4 を介して共に接続され得る。ノード D は、論理デバイス 112 の入力に接続され得る。さらに、スイッチ S1 およびスイッチ S2 は、フリップ・フロップ 104 のポート Q から伝達された信号を受け取るように構成され、スイッチ S3 およびスイッチ S4 は、フリップ・フロップ 104 のポート

【数3】

$\bar{Q}$

から伝達された信号を受け取るように構成される。

【0014】

[0022]公称上等しいアップ電流およびダウン電流のチャージ・ポンプと、積分コンデンサとが、入力クロックの高時間と低時間との間のあらゆるミスマッチを検出するために使用される。コンデンサ  $C_{INT}$  における電圧（すなわち、電圧  $V_{CP}$ ）は、トランジスタ M6 を介してコンデンサ  $C_{INT}$  へ伝達される電流を制御する。コンデンサ  $C_{INT}$  における電圧がインバータしきい値に達するのに要する時間の長さは、補正されたクロックの High 時間を設定するために使用される。理想的には、電圧  $V_{CP}$  が定常状態に達した場合、補正されたクロック・デューティ・サイクルは 50% でなければならない。このアプローチの 1 つの欠点は、チャージ・ポンプのアップ電流およびダウン電流の正確な一致に依存することである。

【0015】

[0023]典型的な実施形態は、本明細書に記載されているように、デューティ・サイクル・ミスマッチ除去を含むクロック・ダブラーに関する。1 つの典型的な実施形態によれば、デバイスは、入力クロック信号を受け取り、補正された出力クロック信号を伝達するように構成されたデューティ・サイクル補正回路を含み得る。デューティ・サイクル補正回路は、入力クロック信号の第 1 のサイクルの間、出力電圧を伝達し、入力クロック信号の第 2 のサイクルの間、第 1 の回路の電流ミスマッチを補正する、ための第 1 の回路を含み得る。デューティ・サイクル補正回路はまた、第 2 のサイクルの間、出力電圧を伝達し、第 1 のサイクルの間、第 2 の回路の電流ミスマッチを補正する、ための第 2 の回路を含み得る。さらに、デバイスは、補正されたクロック信号を受け取り、出力クロック信号を生成する、ためのクロック生成器を含み得る。

【0016】

[0024]別の典型的な実施形態によれば、本発明は、クロック信号を生成するための方法を含み得る。そのような方法のさまざまな実施形態は、複数のチャージ・ポンプを用いて、補正されたクロック信号を生成することを含み得る。ここで、複数のチャージ・ポンプの各々は、入力クロック信号のサイクルの一部の間に、電流ミスマッチを補正するように構成される。この方法はまた、補正されたクロック信号の周波数よりも大きな周波数を有する出力クロックを生成することをも含み得る。

【0017】

[0025]本発明の他の態様は、さまざまな態様の特徴および利点と同様に、後述する詳細な説明、添付図面、および添付された特許請求の範囲を考慮することによって、当業者に明らかになるであろう。

10

20

30

40

50

## 【0018】

[0026]図2Aは、本発明の典型的な実施形態に従うデバイス200を図示する。デバイス200は、デューティ・サイクル補正器を備え得、デュアル・チャージ・ポンプを含んでいる。より具体的には、デバイス200は、チャージ・ポンプ202およびチャージ・ポンプ204を含んでいる。デバイス200はさらに、フリップ・フロップ206、フリップ・フロップ208、ANDゲート210および212、NANDゲート214および216、およびインバータ218、220、222、および224を含んでいる。さらに、デバイス200のためのバイアス電流を提供するための電流源Iが構成されている。

## 【0019】

[0027]チャージ・ポンプ202は、トランジスタM7～M16、スイッチS5～S12、およびコンデンサC<sub>UD1</sub>を含んでいる。電流源Iは、電源電圧V<sub>DD</sub>と、トランジスタM11のドレンとの間に接続され、それはさらに、トランジスタM11のゲート、トランジスタM12のゲート、トランジスタM13のゲート、およびトランジスタM16のゲートに接続されている。トランジスタM11のソースは、ノードFに接続され、それはさらに、トランジスタM12のソースと、トランジスタM13のソースに接続されている。トランジスタM12のドレンは、トランジスタM9のソースおよびトランジスタM10のソースに接続されている。トランジスタM9のゲートは、基準電圧V<sub>REF</sub>を受け取るよう構成され、トランジスタM9のドレンは、ノードGに接続され、それはさらに、トランジスタM7のドレンに接続されている。トランジスタM7のソースは、トランジスタM8のソースに接続され、トランジスタM7のゲートは、トランジスタM8のゲートに接続されている。トランジスタM8のゲートは、トランジスタM8のドレンに接続され、それはさらに、トランジスタM10のドレンに接続されている。

10

20

30

## 【0020】

[0028]トランジスタM13のドレンは、ノードHを介してトランジスタM14のドレンに接続されている。例示されているように、ノードHはノードGに接続されている。トランジスタM14のドレンはさらに、トランジスタM14のゲートに接続され、それは、トランジスタM15のゲートにも接続されている。トランジスタM14のソースは、ノードJに接続されている。トランジスタM15のソースは、スイッチS5、スイッチS6、またはこれら両方を介して、電源電圧ノードJに、切り替え可能に（例えば、選択的に）接続されている。トランジスタM15のドレンは、ノードKに接続され、それは、スイッチS7を介してノードLに切り替え可能に接続されている。ノードKはまた、スイッチS8を介してデバイス200のノードMにも接続されている。ノードLは、スイッチS10を介してノードNに接続され、ノードMは、スイッチS9を介してノードNに接続され得る。ノードNはさらに、トランジスタM16のドレンに接続され、トランジスタM16のソースは、ノードPに接続され、それは、スイッチS11、スイッチS12、またはこれら両方を介してノードFに選択的に接続されている。さらに、コンデンサC<sub>UD1</sub>は、ノードJと、トランジスタM10のゲートとの間に接続され、それは、ノードLにも接続されている。

30

## 【0021】

[0029]チャージ・ポンプ204は、トランジスタM17～M26、スイッチS13～S22、およびコンデンサC<sub>UD2</sub>およびC<sub>INT</sub>を含んでいる。トランジスタM17のソースは、スイッチS13を介してノードAAに切り替え可能に（例えば、選択的に）接続されており、トランジスタM17のゲートは、デバイス200のノードMに接続されており、トランジスタM17のドレンは、ノードBBに接続されている。

40

## 【0022】

[0030]トランジスタM20は、ノードEEに接続されたソースと、トランジスタM24のゲートに接続されたゲートとを有し、それはさらに、トランジスタM25、M11、M12、M13、およびM16のゲートに接続されている。トランジスタM20のドレンは、ノードFFに接続されている。ノードFFはまた、トランジスタM21のソースと、トランジスタM19のソースとにも接続されている。トランジスタM19のゲートは、基準

50

電圧  $V_{REF}$  を受け取るように構成され、トランジスタ M19 のドレンは、トランジスタ M18 のドレンおよびノード C\_C に接続され、それはさらに、トランジスタ M23 のドレンに接続されている。トランジスタ M21 のゲートは、ノード D\_D に接続され、トランジスタ M21 のドレンは、トランジスタ M22 のドレンに接続され、それはさらに、トランジスタ M22 のゲートと、トランジスタ M18 のゲートとに接続されている。トランジスタ M22 のソースおよびトランジスタ M18 のソースは各々、ノード A\_A に接続されている。

【0023】

[0031]さらに、トランジスタ M24 のソースは、ノード E\_E に接続され、トランジスタ M25 のソースは、スイッチ S22、スイッチ S21、またはこれら両方を介してノード E\_E に接続され得る。トランジスタ M24 のドレンは、トランジスタ M23 のドレンに接続され、それはさらに、トランジスタ M23 のゲートおよびノード G\_G に接続されている。トランジスタ M23 のゲートはまた、トランジスタ M26 のゲートにも接続されており、トランジスタ M23 のソースは、ノード A\_A に接続されている。さらに、トランジスタ M25 のドレンは、ノード H\_H に接続され、それは、スイッチ S20 を介してノード D\_D へ、および、スイッチ S19 を介してノード M へ接続され得る。さらに、トランジスタ M26 のドレンはノード K\_K に接続され、それは、スイッチ S17 を介してノード D\_D へ、スイッチ S18 を介してノード M へ接続され得る。さらに、トランジスタ M26 のソースは、スイッチ S15、スイッチ S16、またはこれら両方を介してノード A\_A に接続され得る。

10

20

【0024】

[0032]ノード J およびノード A\_A が共に接続され、デバイス 200 のコンデンサ  $C_{NT}$  は、ノード M\_M とノード M との間に接続されることが注目される。チャージ・ポンプ電圧  $V_{CP}$  は、ノード M を介して伝達され得ることがさらに注目される。

【0025】

[0033]さらに、フリップ・フロップ 206 は、電源電圧  $V_{DD}$  に接続された入力ポート D と、論理デバイス 224 の出力に接続され、リセット電圧  $V_{RST}$  を受け取るように構成されたリセット・ポート  $r_{st}$  と、入力クロック  $ck_{in}$  を受け取るように構成された別のポート C1 と、を含んでいる。フリップ・フロップ 206 はさらに、信号  $ck_{dc}$  を伝達するように構成された出力ポート Q を含み、それは、スイッチ S13 の動作を制御するために使用され得る。以下により完全に記載されるように、信号  $ck_{dc}$  はまた、AND デバイス 210 および 212 へ伝達され得る。フリップ・フロップ 206 はまた、スイッチ S14 の動作を制御するために使用され得る信号

30

【数4】

$\overline{ckdc}$

を伝達するように構成された別の出力ポート

【数5】

40

$\overline{Q}$

を含んでいる。信号

【数6】

$\overline{ckdc}$

はまた、以下により完全に記載されるように、NAND デバイス 214 および 216 へ伝達され得る。

50

## 【 0 0 2 6 】

[0034] フリップ・フロップ 208 は、入力クロック  $ckin$  を受け取るように構成されたポート C2 を含んでいる。フリップ・フロップ 206 はさらに、信号 DIV2 を伝達するように構成された出力ポート Q を含み、信号 DIV2 は、スイッチ S5、S7、S20、および S21 の動作を制御するために使用され得る。信号 DIV2 は、以下により完全に記載されるように、AND デバイス 210 および NAND デバイス 214 にも伝達され得る。フリップ・フロップ 206 はまた、信号

## 【 数 7 】

$\overline{DIV2}$

10

を伝達するように構成された別の出力ポート

## 【 数 8 】

$\overline{Q}$

をも含み、それはスイッチ S10、S11、S15、および S17 の動作を制御するために使用され得る。信号

20

## 【 数 9 】

$\overline{DIV2}$

は、以下により完全に記載されるように、AND デバイス 212 および NAND デバイス 216 へ伝達され得る。さらに、図 2A に例示されるように、出力ポート

## 【 数 10 】

$\overline{Q}$

30

が、フリップ・フロップ 208 の入力ポート D に接続されている。

## 【 0 0 2 7 】

[0035] AND ゲート 210 は、信号 DIV2 および信号  $ckdcc$  を受け取り、信号 DN1 を出力するように構成され、それは、スイッチ S9 を制御するために使用され得る。

AND ゲート 212 は、信号

## 【 数 11 】

$\overline{DIV2}$

および信号  $ckdcc$  を受け取り、信号 DN2 を出力するように構成され、それは、スイッチ S19 および S22 を制御するために使用され得る。さらに、NAND ゲート 214 は、信号 DIV2 および信号

40

## 【 数 12 】

$\overline{ckdcc}$

を受け取り、それは、スイッチ S6 および S8 を制御するために使用され得る信号

【数13】

$\overline{UP1}$

を出力するように構成される。さらに、NANDゲート216は、信号

【数14】

$\overline{DIV2}$

10

および信号

【数15】

$\overline{ckdcc}$

を受け取り、それは、スイッチS16およびS18を制御するために使用され得る信号

【数16】

$\overline{UP2}$

20

を出力するように構成される。

【0028】

[0036]したがって、デバイス200は、それぞれが、自身のアップ／ダウン・ミスマッチ補正回路を備えた2つのチャージ・ポンプ（すなわち、チャージ・ポンプ202および204）を含んでいる。チャージ・ポンプ202および204は、入力クロックの交互のサイクルで動作するように構成されている。さらに詳しくは、第1のサイクル（すなわち、フェーズ）中、チャージ・ポンプ202は、電圧 $V_{CP}$ を駆動し、チャージ・ポンプ204は、これのミスマッチを検出し、補正し得る。さらに、別のフェーズ（つまり、サイクル）中、チャージ・ポンプ204は、電圧 $V_{CP}$ を駆動し、チャージ・ポンプ202は、これのミスマッチを検出し、補正し得る。

30

【0029】

[0037]より具体的な例として、1サイクル（例えば、偶数サイクル）中、入力クロックは、コンデンサ $C_{INT}$ に積分されるチャージ・ポンプ202のアップ電流およびダウン電流の持続時間を制御する。同時に、チャージ・ポンプ204のアップ／ダウン電流ミスマッチが、コンデンサ $C_{UD2}$ に積分される。チャージ・ポンプ204のアップ電流およびダウン電流が等しくないのであれば、GMステージ（すなわち、トランジスタM21およびM19を含む差動ペア）が、コンデンサ $C_{UD2}$ の電圧と、基準電圧 $V_{REF}$ （例えば、公称上、固定値である電圧 $V_{CP}$ に等しい）との差分を測定し、チャージ・ポンプ204のアップ電流を、チャージ・ポンプ204のダウン電流に等しくなるまで調節する。さらに具体的には、チャージ・ポンプ204のアップ電流と、チャージ・ポンプ204のダウン電流とを実質的に等しくさせるために、補正電流（すなわち、トランジスタM23のドレンと、トランジスタM18のドレンとの間を流れる電流）が使用され得る。

40

【0030】

[0038]同様に、別の異なるサイクル（例えば、奇数サイクル）中、入力クロックは、コンデンサ $C_{INT}$ へ積分されるチャージ・ポンプ204のアップ電流およびダウン電流の持続時間を制御する。同時に、チャージ・ポンプ202のアップ／ダウン電流ミスマッチが、コンデンサ $C_{UD1}$ へ積分される。チャージ・ポンプ202のアップ電流およびダウン電流が等しくないのであれば、GMステージ（すなわち、トランジスタM9およびM10を含む差動ペアを含む）が、コンデンサ $C_{UD1}$ の電圧と、基準電圧 $V_{REF}$ （例え

50

ば、公称上、固定値である電圧  $V_{C_P}$  に等しい)との差分を測定し、チャージ・ポンプ 202 のアップ電流を、チャージ・ポンプ 202 のダウントラップ電流に等しくなるまで調節する。さらに具体的には、チャージ・ポンプ 202 のアップ電流と、チャージ・ポンプ 202 のダウントラップ電流とを実質的に等しくさせるために、補正電流(すなわち、トランジスタ M7 のドレンと、トランジスタ M14 のドレンとの間を流れる電流)が使用され得る。

【0031】

[0039] 図 2B は、図 2A の動作デバイス 200 に関する例示的なタイミング図 250 である。タイミング図 250 は、クロック入力信号  $ckin$ 、クロック信号  $ckdcc$ 、信号  $DIV2$ 、信号  $DN1$  および  $DN2$ 、信号

【数 17】

10

UP1

および

【数 18】

UP2

チャージ・ポンプ電圧  $V_{C_P}$ 、およびリセット電圧  $V_{RST}$  のためのタイミング信号を含む。タイミング図 250 に示されるように、デバイス 200 は、デューティ・サイクル補正によって、それぞれ実質的に 0° および 180° フェーズでクロック信号  $cdkcc$  の立ち上がりエッジおよび立ち下りエッジを位置決めするように構成される。

20

【0032】

[0040] さらに、典型的な実施形態によれば、デューティ・サイクル補正されたクロック(例えば、クロック信号  $ckdcc$ )の立ち上がりエッジおよび立ち下りエッジにおける 1/4 周期パルスが、クロック生成器によって生成され得る。図 3A は、典型的な実施形態に従うクロック生成器 300 を例示する。クロック生成器 300 は、トランジスタ M27 および M28、コンデンサ C1、C2 および C3、抵抗 R、スイッチ S23～S26、フリップ・フロップ 302 および 304、NAND ゲート 306、およびインバータ 308、310、312、314 および 316 を含んでいる。

30

【0033】

[0041] トランジスタ M27 のゲートは、トランジスタ M28 のゲートおよびノード NN に接続され、それはさらに、抵抗 R を介して入力に接続されている。コンデンサ C1 は、ノード NN とノード PP の間に接続されている。ノード PP は電源電圧  $V_{DD}$  に接続されており、スイッチ S23 を介してトランジスタ M27 のソースに接続され得る。トランジスタ M27 のドレンは、コンデンサ C2 の一方に接続されているノード QQ に接続されている。コンデンサ C2 の他方は、アース電圧 GND に接続されている。ノード QQ は、スイッチ S25 を介してアース電圧 GND に接続され得、また、インバータ 312 の入力にも接続されている。インバータ 312 の出力は、インバータ 310 の入力に接続され、それは、フリップ・フロップ 302 のリセット・ポート  $rst$  に接続された出力を有する。

40

【0034】

[0042] トランジスタ M28 のソースは、スイッチ S24 を介して電源電圧  $V_{DD}$  に接続され得る。さらに、トランジスタ M28 のドレンは、コンデンサ C3 の片側に接続されたノード RR に接続されている。コンデンサ C3 の他の側は、アース電圧 GND に接続される。さらに、ノード RR は、スイッチ S26 を介してアース電圧 GND に接続され得、また、インバータ 316 の入力にも接続されている。インバータ 316 の出力は、インバータ 314 の入力に接続され、それは、フリップ・フロップ 304 のリセット・ポート  $rst$  に接続された出力を有する。一例によれば、コンデンサ C2 および C3 は各々、コンデンサ  $C_{INT}$  (図 2 参照) の静電容量値の 1/2 である(すなわち、例えば、C2 =

50

$C_3 = 1 / 2 C_{INT}$  ) である静電容量値を備え得る。

【 0 0 3 5 】

[0043] フリップ・フロップ 302 および 304 の各々は、電源電圧  $V_{DD}$  およびクロック信号  $ckdccc$  を受け取るように構成される。さらに、フリップ・フロップ 302 は NAND ゲート 306 のポートへ信号  $ck\_cs1$  を伝達するように構成される。信号  $ck\_cs1$  はまた、スイッチ S23 および S25 の動作を制御するために、スイッチ S23 および S25 によって受け取られ得る。フリップ・フロップ 304 は、NAND ゲート 306 の別のポートへ信号  $ck\_cs2$  を伝達するように構成される。信号  $ck\_cs2$  はまた、スイッチ S24 および S26 の動作を制御するために、スイッチ S24 および S26 によって受け取られ得る。NAND ゲート 306 は、実質的に 50% のデューティ・サイクルと、クロック信号  $ckdccc$  の周波数に対して 2 倍である周波数と、を有するクロック信号  $ck2x$  を出力するように構成される。

10

【 0 0 3 6 】

[0044] したがって、クロック生成器 300 は、デバイス 200 の最終ステージ（すなわち、トランジスタ M17 およびコンデンサ  $C_{INT}$  を含むステージ）に類似した電流源およびコンデンサからなる 2 つのステージ（すなわち、トランジスタ M27 およびコンデンサ  $C_2$  を含むステージと、トランジスタ M28 およびコンデンサ  $C_3$  を含むステージ）を含んでいる。しかしながら、前述されるように、コンデンサ  $C_2$  および  $C_3$  は、コンデンサ  $C_{INT}$  の静電容量の 1/2 である静電容量を備え得る。したがって、コンデンサ  $C_2$  および  $C_3$  は、入力クロック・サイクルの 1/4 で、インバータしきい値に積分されるであろう。クロック生成器 300 の 1 つのステージは、補正されたクロックの偶数フェーズで動作し、1 つのステージは、補正されたクロックの逆フェーズで動作する。フリップ・フロップ 302 および 304 の各々の出力は、クロック信号  $ckdccc$  と同じ周波数のクロックであるが、25% のデューティ・サイクルである。クロック信号  $ck\_cs1$  の反転と、クロック信号  $ck\_cs2$  の反転とが、NAND ゲート 306 を介して結合され、クロック信号  $ck2x$  が生成され得る。RC フィルタ（すなわち、抵抗 R およびコンデンサ  $C_I$ ）は、電圧  $V_{CP}$  におけるリップルが、2 倍されたクロックのデューティ・サイクルに過渡な影響を与えることを防ぐために、電圧  $V_{CP}$  の三角波を除去し得ることが注目される。

20

【 0 0 3 7 】

30

[0045] 図 3B は、図 3A の動作デバイス 300 のための例示的なタイミング図 350 である。タイミング図 350 は、クロック信号  $ckdccc$ 、信号  $ck\_cs1$ 、信号  $ck\_cs2$ 、リセット電圧  $V_{RST1}$ 、リセット電圧  $V_{RST2}$ 、およびクロック信号  $ck2x$  のためのタイミング信号を含む。

【 0 0 3 8 】

40

[0046] 図 4 は、本発明の典型的な実施形態に従うデバイス 400 を図示する。デバイス 400 は、ミスマッチが除去されたクロック・ダブラを備え得、クロック生成器 404 に接続されたデューティ・サイクル補正器 402 を含む。例示のみによって、デューティ・サイクル補正器 402 は、図 2 に例示されるようなデバイス 200（例えば、デューティ・サイクル補正器）を備え、クロック生成器 404 は、図 3 に例示されるようなクロック生成器 300 を備え得る。デバイス 402 は、クロック信号を受け取り、補正されたクロック信号を出力するように構成され得る。さらに、クロック生成器 404 は、補正されたクロック信号を受け取り、補正されたクロック信号の周波数に対して 2 倍された周波数を有するクロック信号を出力するように構成され得る。

【 0 0 3 9 】

50

[0047] 図 5 は、1 つまたは複数の典型的な実施形態に従う方法 500 を例示するフローチャートである。方法 500 は、複数のチャージ・ポンプを用いて、補正されたクロック信号を生成することを含み得る。複数のチャージ・ポンプの各々は、（数字 502 によって示されるように）入力クロック信号のサイクルの一部の間に、電流ミスマッチを補正するように構成されている。さらに、方法 500 はまた、（数字 504 によって示されるよ

50

うに)補正されたクロック信号の周波数よりも大きな周波数を有する出力クロックを生成することを含み得る。

【0040】

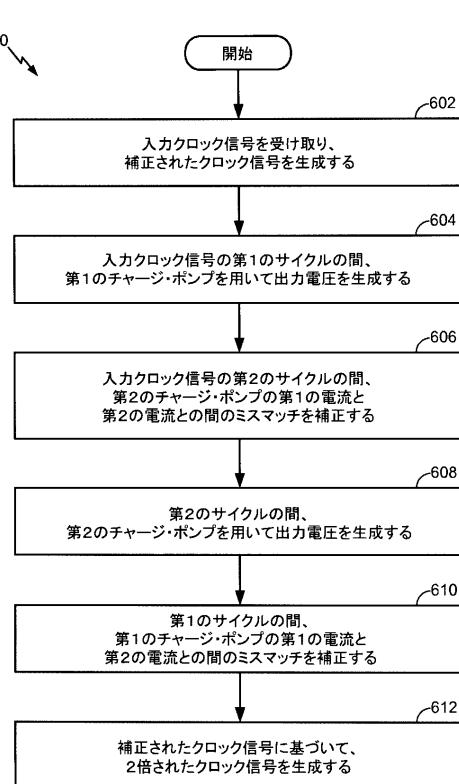

[0048]図6は、1つまたは複数の典型的な実施形態に従う別の方法600を例示するフローチャートである。方法600は、(数字602によって示されるように)入力クロック信号を受け取ることと、補正されたクロック信号を生成することとを含み得る。さらに、方法600はまた、(数字604によって示されるように)入力クロック信号の第1のサイクルの間、第1のチャージ・ポンプを用いて出力電圧を生成することを含み得る。方法600はさらに、(数字606によって示されるように)入力クロック信号の第2のサイクルの間、第2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することをも含み得る。方法600はさらに、(数字608によって示されるように)第2のサイクルの間、第2のチャージ・ポンプを用いて出力電圧を生成することを含み得る。それに加えて、方法600は、(数字610によって示されるように)第1のサイクルの間、第1のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することを含み得る。さらに、方法600は、(数字612によって示されるように)補正されたクロック信号に基づいて、2倍されたクロック信号を生成することを含み得る。

10

【0041】

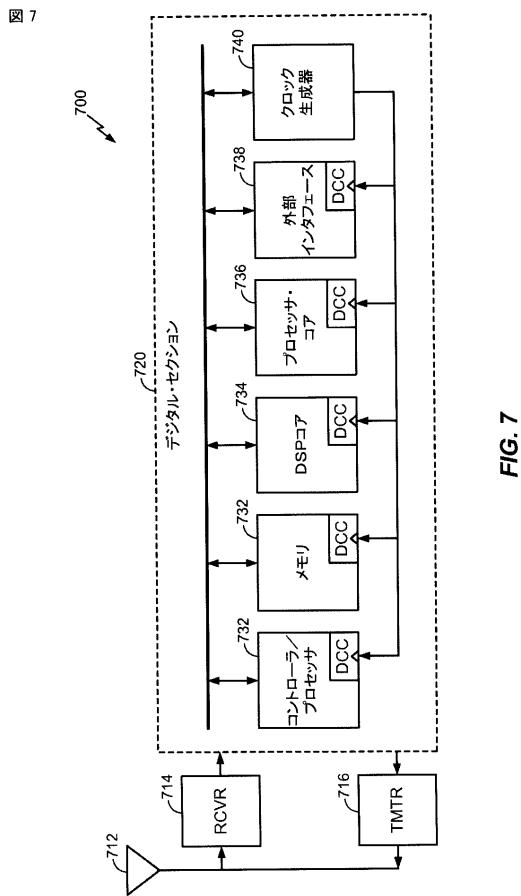

[0049]図7は、ワイヤレス・デバイス700、それはセルラ電話、端末、情報携帯端末(PDA)、ハンドセット、またはその他のあるデバイスであり得る、のブロック図を図示する。ワイヤレス・デバイス700は、CDMA、TDMA、FDMA、GSM(登録商標)、OFDMA、GPS、および/または、当該技術分野で周知の他のシステムのようなさまざまなワイヤレス通信システムと通信することができ得る。

20

【0042】

[0050]受信経路では、アンテナ712が、基地局および/または衛星によって送信された信号を受信し、受信した信号を、受信機(RCVR)714に提供する。受信機714は、受信した信号を処理(例えば、フィルタ、増幅、周波数ダウンコンバート、およびデジタル化)し、更なる処理のために、デジタル・モジュール720へサンプルを提供する。送信経路では、デジタル・モジュール720が、送信されるべきデータを処理し、送信機(TMTR)716へデータ・チップを提供する。送信機716は、データ・チップを処理(例えば、アナログ変換、フィルタ、増幅、周波数アップコンバート)し、変調された信号を生成する。これは、アンテナ712を介して送信される。

30

【0043】

[0051]デジタル・モジュール720は、通信および/または他の機能をサポートするさまざまな処理ユニットを含んでいる。デジタル・モジュール720内では、デジタル信号プロセッサ(DSP)コア734が、送信経路のための処理(例えば、符号化および変調)、受信経路のための処理(例えば、復調および復号)、および/または、他のアプリケーションおよび機能のための処理、を実行する。プロセッサ・コア736は、ビデオ、オーディオ、グラフィックス、ゲーム等のようなさまざまな機能をサポートする。コントローラ/プロセッサ730は、デジタル・モジュール720内の処理ユニットの動作を指図する。メモリ732は、処理ユニットのためのデータおよびプログラム・コードを格納する。外部インターフェース・ユニット738は、デジタル・モジュール720に対する外部の他のユニットとインターフェースする。

40

【0044】

[0052]デバイス400(図4参照)を備え得るクロック生成器740は、デジタル・モジュール720内の処理ユニットによって使用されるクロック信号を生成する。クロック・ダブラーを備え得るクロック生成器740は、クロック信号を生成するために、1つまたは複数のVCOおよび/またはPLLを含み得る。クロック生成器740は、デジタル・モジュール720内の他の処理ユニットにクロック信号を配信する。クロック配信ネットワークは、クロック生成器740から他の処理ユニットへ進むラインによって表される。クロック生成器740は、コントローラ/プロセッサ730、メモリ732、DSP

50

コア 734、プロセッサ・コア 736、インターフェース・ユニット 738、および／またはその他のユニットにおいて実現され得る。

【0045】

[0053]本明細書において記載されたクロック生成器は、発振器、PLL、クロック配信ネットワーク、またはその他のあるクロック・ソースからのクロック信号のデューティ・サイクルを改善するために使用され得る。クロック生成器は、例えば 50% に近い、良好なデューティ・サイクルを有する出力クロック信号を生成し得る。デューティ・サイクルは、クロック信号の重要な仕様であり、多くの現代の電子デバイスにおいて使用されている、より高いクロック・レートのためにより重要であり得る。クロック生成器は、集積回路の任意の部分において便利に実現され、必要な場合にはどこでもクロック・デューティ・サイクルを補正するために使用され得る。任意の数のクロック生成回路が、所与の集積回路において実現され得る。

10

【0046】

[0054]本明細書に記載されたクロック生成器は、集積回路 (IC)、特定用途向け集積回路 (ASIC)、デジタル信号プロセッサ (DSP)、デジタル信号処理デバイス (DSPD)、プログラマブル論理デバイス (PLD)、フィールド・プログラマブルム・ゲート・アレイ (FPGA)、プロセッサ、コントローラ、マイクロ・コントローラ、マイクロ・プロセッサ、およびその他の電子ユニットにおいて実現され得る。クロック生成器はまた、CMOS、N-MOS、P-MOS、BJT、GaAs 等のようなさまざまな IC 処理技術を用いて製造され得る。クロック生成器はまた、ディスクリートな構成要素を用いて実現され得る。

20

【0047】

[0055]当業者であれば、情報および信号は、さまざまな異なる技術および技法のうちの何れかを用いて表され得ることを理解するであろう。例えば、上記説明を通じて参照され得るデータ、命令群、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場または磁性粒子、光学場または光学粒子、あるいはこれらの任意の組み合わせによって表現され得る。

30

【0048】

[0056]当業者であれば、さらに、本明細書で開示された典型的な実施形態に関連して記載されたさまざまな例示的な論理ブロック、モジュール、回路、およびアルゴリズム・ステップが、電子ハードウェア、コンピュータ・ソフトウェア、あるいはこれらの組み合わせとして実現されることを理解するであろう。ハードウェアとソフトウェアとの相互置換性を明確に説明するために、さまざまな例示的な構成要素、ブロック、モジュール、回路、およびステップが、それらの機能の観点から一般的に記載された。これら機能がハードウェアとしてまたはソフトウェアとして実現されるかは、特定の用途およびシステム全体に課せられている設計制約に依存する。当業者であれば、記載された機能を、特定の各用途のために変化する方式で実現し得るが、このような実現は、本発明の典型的な実施形態の範囲からの逸脱をもたらすものとして解釈されるべきではない。

【0049】

[0057]本明細書において開示された典型的な実施形態に関連して記載された例示的なさまざまな論理ブロック、モジュール、および回路が実現され得るか、または、汎用プロセッサ、デジタル信号プロセッサ (DSP)、特定用途向け集積回路 (ASIC)、フィールド・プログラマブル・ゲート・アレイ (FPGA) またはその他のプログラマブル論理デバイス、ディスクリート・ゲートまたはトランジスタ・ロジック、ディスクリート・ハードウェア構成要素、または、本明細書に記載された機能を実行するように設計されたこれら任意の組み合わせ、と共に実行され得る。汎用プロセッサは、マイクロ・プロセッサであり得るが、代わりに、従来技術によるプロセッサ、コントローラ、マイクロ・コントローラ、あるいは順序回路であり得る。プロセッサは、例えば DSP とマイクロ・プロセッサとの組み合わせ、複数のマイクロ・プロセッサ、DSP コアと連携する 1 つまたは複数のマイクロ・プロセッサ、またはその他任意のこのような構成であるコンピューティン

40

50

グ・デバイスの組み合わせとして実現され得る。

【0050】

[0058] 1 または複数の典型的な実施形態では、記載された機能は、ハードウェア、ソフトウェア、ファームウェア、あるいはそれらの任意の組み合わせによって実現され得る。ソフトウェアで実現される場合、これら機能は、コンピュータ読取可能な媒体上に格納されるか、あるいは、コンピュータ読取可能な媒体上の1つまたは複数の命令群またはコードとして送信され得る。コンピュータ読取可能な媒体は、コンピュータ記憶媒体と通信媒体との両方を含む。これらは、コンピュータ・プログラムのある場所から別の場所への転送を容易にする任意の媒体を含む。記憶媒体は、コンピュータによってアクセスされ得る利用可能な任意の媒体である。例として、限定することなく、このようなコンピュータ読取可能な媒体は、RAM、ROM、EEPROM(登録商標)、CD-ROMまたはその他の光ディスク記憶装置、磁気ディスク記憶装置またはその他の磁気記憶デバイス、あるいは、所望のプログラム・コード手段を命令群またはデータ構造の形式で搬送または格納するために使用され、しかも、コンピュータによってアクセスされ得るその他任意の媒体を備え得る。さらに、いかなる接続も、コンピュータ読取可能な媒体として適切に称される。同軸ケーブル、光ファイバ・ケーブル、対より線、デジタル加入者線(DSL)、あるいは、例えば赤外線、無線およびマイクロ波のような無線技術を使用して、ウェブサイト、サーバ、あるいはその他の遠隔ソースからソフトウェアが送信される場合、同軸ケーブル、光ファイバ・ケーブル、対より線、DSL、あるいは、例えば赤外線、無線およびマイクロ波のような無線技術が、媒体の定義に含まれる。本明細書で使用されるdiskおよびdискは、コンパクト・ディスク(disk)(CD)、レーザ・ディスク(dиск)、光ディスク(disk)、デジタル多用途ディスク(disk)(DVD)、フロッピー(登録商標)ディスク(disk)、およびBlu-ray(登録商標)ディスク(disk)を含む。ここでdiskは、通常、データを磁気的に再生する一方、diskは、レーザを用いてデータを光学的に再生する。上記の組み合わせもまた、コンピュータ読取可能な媒体の範囲内に含まれるべきである。

10

20

30

【0051】

[0059] 開示された典型的な実施形態の前述した記載は、当業者が、本発明を製造または使用することを可能にするように提供されている。これら典型的な実施形態に対するさまざまな修正が、当業者に容易に明らかになるであろう。そして、本明細書に記載された一般的な原理は、本発明の精神または範囲から逸脱することなく、他の実施形態に適用され得る。したがって、本発明は、本明細書で示された典型的な実施形態に限定されるものではなく、本明細書で開示された原理および新規な特徴に一致した最も広い範囲に相当することが意図されている。

【図1】

FIG. 1

【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図3A】

FIG. 3A

【図 3B】

FIG. 3B

【図 4】

図 4

FIG. 4

【図 5】

図 5

FIG. 5

【図 6】

図 6

FIG. 6

【図7】

FIG.7

## 【手続補正書】

【提出日】平成28年3月29日(2016.3.29)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

デバイスであって、前記デバイスは下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を伝達するように構成されたデューティ・サイクル補正回路であって、

前記入力クロック信号の第1のサイクルの間、出力電圧を伝達し、前記入力クロック信号の第2のサイクルの間、第1の回路の電流ミスマッチを補正する、第1の回路と、

前記第2のサイクルの間、前記出力電圧を伝達し、前記第1のサイクルの間、第2の回路の電流ミスマッチを補正する、第2の回路と、

を含むデューティ・サイクル補正回路と、

前記補正されたクロック信号を受け取り、出力クロックを生成するためのクロック生成器。

## 【請求項2】

前記第1のサイクルおよび前記第2のサイクルの各々の間、前記出力電圧を受け取るように構成された出力コンデンサをさらに備える、請求項1に記載のデバイス。

## 【請求項3】

前記出力クロックは、実質的に50%であるデューティ・サイクルと、前記補正されたクロック信号の周波数に対して増加された周波数とを有する、請求項1に記載のデバイス

。

#### 【請求項 4】

前記第1の回路は、前記第2のサイクルの間、第1および第2の電流を受け取るように構成されたコンデンサの両端の電圧と、基準電圧とを比較するためのトランジスタの差動ペアを含む、請求項1に記載のデバイス。

#### 【請求項 5】

前記コンデンサの両端の前記電圧が前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、請求項4に記載のデバイス。

#### 【請求項 6】

前記第2の回路は、前記第1のサイクルの間、第1および第2の電流を受け取るように構成されたコンデンサの両端の電圧と、基準電圧とを比較するためのトランジスタの差動ペアを含む、請求項1に記載のデバイス。

#### 【請求項 7】

前記コンデンサの両端の前記電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、請求項6に記載のデバイス。

#### 【請求項 8】

デバイスであって、前記デバイスは下記を備える、

入力クロック信号のフェーズの間、出力電圧を生成するように構成された第1のチャージ・ポンプと、

前記入力クロック信号のもう1つの、異なるフェーズの間、前記出力電圧を生成するための第2のチャージ・ポンプ、ここで、前記第1および前記第2のチャージ・ポンプの各々は、前記入力クロック信号に基づいて、補正されたクロック信号を生成するように構成される、と、

前記第1および前記第2のチャージ・ポンプの各々に接続され、前記補正されたクロック信号を受け取り、前記補正されたクロック信号の周波数に対して2倍された周波数を有する出力クロック信号を生成するように構成されたクロック生成器。

#### 【請求項 9】

前記第1のチャージ・ポンプはさらに、前記入力クロック信号のもう1つの、異なるフェーズの間、前記第1のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを検出し補正するように構成された、請求項8に記載のデバイス。

#### 【請求項 10】

前記第2のチャージ・ポンプはさらに、前記入力クロック信号のフェーズの間、前記第2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを検出し補正するように構成された、請求項8に記載のデバイス。

#### 【請求項 11】

前記出力クロック信号は、実質的に50%であるデューティ・サイクルを有する、請求項8に記載のデバイス。

#### 【請求項 12】

前記第1のチャージ・ポンプはさらに、前記入力クロック信号のもう1つの、異なるフェーズの間、前記第1のチャージ・ポンプのアップ電流およびダウン電流を受け取るように構成されたコンデンサを備える、請求項8に記載のデバイス。

#### 【請求項 13】

前記第1のチャージ・ポンプはさらに、前記コンデンサの両端の電圧と基準電圧との差分を測定するように構成されたトランジスタの差動ペアを備える、請求項12に記載のデバイス。

#### 【請求項 14】

前記コンデンサの両端の前記電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、請求項13に記載のデバイス。

#### 【請求項 15】

前記第2のチャージ・ポンプはさらに、前記入力クロック信号のフェーズの間、前記第

2のチャージ・ポンプのアップ電流およびダウン電流を受け取るように構成されたコンデンサを備える、請求項8に記載のデバイス。

【請求項16】

前記第2のチャージ・ポンプはさらに、前記コンデンサの両端の電圧と基準電圧との差分を測定するように構成されたトランジスタの差動ペアを備える、請求項15に記載のデバイス。

【請求項17】

前記コンデンサの両端の前記電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、請求項16に記載のデバイス。

【請求項18】

方法であって、前記方法は下記を備える、

複数のチャージ・ポンプを用いて、補正されたクロック信号を生成すること、ここで、前記複数のチャージ・ポンプの各々は、入力クロック信号のサイクルの一部の間に、電流ミスマッチを補正するように構成される、と、

前記補正されたクロック信号の周波数よりも大きな周波数を有する出力クロックを生成すること。

【請求項19】

補正されたクロック信号を生成することは、

前記入力クロック信号の第1のサイクルの間、前記複数のチャージ・ポンプのうちの第1のチャージ・ポンプを用いて出力電圧を生成することと、

前記入力クロック信号の第2のサイクルの間、前記複数のチャージ・ポンプのうちの第2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

前記第2のサイクルの間、前記第2のチャージ・ポンプを用いて、前記出力電圧を生成することと、

前記第1のサイクルの間、前記第1のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

を備える、請求項18に記載の方法。

【請求項20】

前記第1のチャージ・ポンプの前記第1の電流と前記第2の電流との間の前記ミスマッチを検出することと、

前記第2のチャージ・ポンプの前記第1の電流と前記第2の電流との間の前記ミスマッチを検出することと、

をさらに備える、請求項19に記載の方法。

【請求項21】

前記第1のチャージ・ポンプおよび前記第2のチャージ・ポンプの何れかにおけるミスマッチを検出することは、基準電圧を、コンデンサの両端に蓄積された電圧と比較することを備える、請求項20に記載の方法。

【請求項22】

方法であって、前記方法は下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を生成することと、

前記入力クロック信号の第1のサイクルの間、第1のチャージ・ポンプを用いて出力電圧を生成することと、

前記入力クロック信号の第2のサイクルの間、第2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

前記第2のサイクルの間、前記第2のチャージ・ポンプを用いて、前記出力電圧を生成することと、

前記第1のサイクルの間、前記第1のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

前記補正されたクロック信号に基づいて、2倍されたクロック信号を生成すること。

【請求項23】

2倍されたクロック信号を生成することは、実質的に50%であるデューティ・サイクルと、前記2倍されたクロック信号の周波数よりも小さい周波数とを有する前記補正されたクロック信号に基づいて、実質的に50%であるデューティ・サイクルを有する前記2倍されたクロック信号を生成することを備える、請求項22に記載の方法。

【請求項24】

デバイスであって、前記デバイスは下記を備える、

補正されたクロック信号を生成するための手段、ここで、前記生成するための手段は、

入力クロック信号のサイクルの一部の間に、電流ミスマッチを補正するように構成される

、と、

前記補正されたクロック信号の周波数よりも大きな周波数を有する出力クロック信号を

生成するための手段。

【請求項25】

デバイスであって、前記デバイスは下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を生成するための手段と、

前記入力クロック信号の第1のサイクルの間、第1のチャージ・ポンプを用いて出力電

圧を生成するための手段と、

前記入力クロック信号の第2のサイクルの間、第2のチャージ・ポンプの第1の電流と

第2の電流との間のミスマッチを補正するための手段と、

前記第2のサイクルの間、前記第2のチャージ・ポンプを用いて、前記出力電圧を生成

するための手段と、

前記第1のサイクルの間、前記第1のチャージ・ポンプの第1の電流と第2の電流との

間のミスマッチを補正するための手段と、

前記補正されたクロック信号に基づいて、出力クロック信号を生成するための手段。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0051

【補正方法】変更

【補正の内容】

【0051】

[0059]開示された典型的な実施形態の前述した記載は、当業者が、本発明を製造または

使用することを可能にするように提供されている。これら典型的な実施形態に対するさまざま

な修正が、当業者に容易に明らかになるであろう。そして、本明細書に記載された一般的な原理は、本発明の精神または範囲から逸脱することなく、他の実施形態に適用され

得る。したがって、本発明は、本明細書で示された典型的な実施形態に限定されるものでは

なく、本明細書で開示された原理および新規な特徴に一致した最も広い範囲に相当する

ことが意図されている。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

[C1]

デバイスであって、前記デバイスは下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を伝達するように構成されたデ

ューティ・サイクル補正回路であって、

前記入力クロック信号の第1のサイクルの間、出力電圧を伝達し、前記入力クロック

信号の第2のサイクルの間、第1の回路の電流ミスマッチを補正する、第1の回路と、

前記第2のサイクルの間、前記出力電圧を伝達し、前記第1のサイクルの間、第2の

回路の電流ミスマッチを補正する、第2の回路と、

を含むデューティ・サイクル補正回路と、

前記補正されたクロック信号を受け取り、出力クロックを生成するためのクロック生成

器。

[C2]

前記第1のサイクルおよび前記第2のサイクルの各々の間、前記出力電圧を受け取るよ

うに構成された出力コンデンサをさらに備える、C 1 に記載のデバイス。

[ C 3 ]

前記出力クロックは、実質的に 50 % であるデューティ・サイクルと、前記補正されたクロック信号の周波数に対して増加された周波数とを有する、C 1 に記載のデバイス。

[ C 4 ]

前記第 1 の回路は、前記第 2 のサイクルの間、第 1 および第 2 の電流を受け取るように構成されたコンデンサの両端の電圧と、基準電圧とを比較するためのトランジスタの差動ペアを含む、C 1 に記載のデバイス。

[ C 5 ]

前記コンデンサの両端の電圧が前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、C 4 に記載のデバイス。

[ C 6 ]

前記第 2 の回路は、前記第 1 のサイクルの間、第 1 および第 2 の電流を受け取るように構成されたコンデンサの両端の電圧と、基準電圧とを比較するためのトランジスタの差動ペアを含む、C 1 に記載のデバイス。

[ C 7 ]

前記コンデンサの両端の電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、C 6 に記載のデバイス。

[ C 8 ]

デバイスであって、前記デバイスは下記を備える、

入力クロック信号のフェーズの間、出力電圧を生成するように構成された第 1 のチャージ・ポンプと、

前記入力クロック信号のもう 1 つの、異なるフェーズの間、前記出力電圧を生成するための第 2 のチャージ・ポンプ、ここで、前記第 1 および前記第 2 のチャージ・ポンプの各々は、前記入力クロック信号に基づいて、補正されたクロック信号を生成するように構成される、と、

前記第 1 および前記第 2 のチャージ・ポンプの各々に接続され、前記補正されたクロック信号を受け取り、前記補正されたクロック信号の周波数に対して 2 倍された周波数を有する出力クロック信号を生成するように構成されたクロック生成器。

[ C 9 ]

前記第 1 のチャージ・ポンプはさらに、前記入力クロック信号のもう 1 つの、異なるフェーズの間、前記第 1 のチャージ・ポンプの第 1 の電流と第 2 の電流との間のミスマッチを検出し補正するように構成された、C 8 に記載のデバイス。

[ C 10 ]

前記第 2 のチャージ・ポンプはさらに、前記入力クロック信号のフェーズの間、前記第 2 のチャージ・ポンプの第 1 の電流と第 2 の電流との間のミスマッチを検出し補正するように構成された、C 8 に記載のデバイス。

[ C 11 ]

前記出力クロック信号は、実質的に 50 % であるデューティ・サイクルを有する、C 8 に記載のデバイス。

[ C 12 ]

前記第 1 のチャージ・ポンプはさらに、前記入力クロック信号のもう 1 つの、異なるフェーズの間、前記第 1 のチャージ・ポンプのアップ電流およびダウン電流を受け取るように構成されたコンデンサを備える、C 8 に記載のデバイス。

[ C 13 ]

前記第 1 のチャージ・ポンプはさらに、前記コンデンサの両端の電圧と基準電圧との差分を測定するように構成されたトランジスタの差動ペアを備える、C 12 に記載のデバイス。

[ C 14 ]

前記コンデンサの両端の電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正

するためのフィードバック・ループをさらに備える、C 1 3 に記載のデバイス。

[ C 1 5 ]

前記第2のチャージ・ポンプはさらに、前記入力クロック信号のフェーズの間、前記第2のチャージ・ポンプのアップ電流およびダウン電流を受け取るように構成されたコンデンサを備える、C 8 に記載のデバイス。

[ C 1 6 ]

前記第2のチャージ・ポンプはさらに、前記コンデンサの両端の電圧と基準電圧との差分を測定するように構成されたトランジスタの差動ペアを備える、C 1 5 に記載のデバイス。

[ C 1 7 ]

前記コンデンサの両端の電圧が、前記基準電圧と異なる場合に、電流ミスマッチを補正するためのフィードバック・ループをさらに備える、C 1 6 に記載のデバイス。

[ C 1 8 ]

方法であって、前記方法は下記を備える、

複数のチャージ・ポンプを用いて、補正されたクロック信号を生成すること、ここで、前記複数のチャージ・ポンプの各々は、入力クロック信号のサイクルの一部の間に、電流ミスマッチを補正するように構成される、と、

前記補正されたクロック信号の周波数よりも大きな周波数を有する出力クロックを生成すること。

[ C 1 9 ]

補正されたクロック信号を生成することは、

前記入力クロック信号の第1のサイクルの間、前記複数のチャージ・ポンプのうちの第1のチャージ・ポンプを用いて出力電圧を生成することと、

前記入力クロック信号の第2のサイクルの間、前記複数のチャージ・ポンプのうちの第2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

前記第2のサイクルの間、前記第2のチャージ・ポンプを用いて、前記出力電圧を生成することと、

前記第1のサイクルの間、前記第1のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

を備える、C 1 8 に記載の方法。

[ C 2 0 ]

前記第1のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを検出することと、

前記第2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを検出することと、

をさらに備える、C 1 9 に記載の方法。

[ C 2 1 ]

前記第1のチャージ・ポンプおよび前記第2のチャージ・ポンプの何れかにおけるミスマッチを検出することは、基準電圧を、コンデンサの両端に蓄積された電圧と比較することを備える、C 2 0 に記載の方法。

[ C 2 2 ]

方法であって、前記方法は下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を生成することと、

前記入力クロック信号の第1のサイクルの間、第1のチャージ・ポンプを用いて出力電圧を生成することと、

前記入力クロック信号の第2のサイクルの間、第2のチャージ・ポンプの第1の電流と第2の電流との間のミスマッチを補正することと、

前記第2のサイクルの間、前記第2のチャージ・ポンプを用いて、前記出力電圧を生成することと、

前記第1のサイクルの間、前記第1のチャージ・ポンプの第1の電流と第2の電流との

間のミスマッチを補正することと、

前記補正されたクロック信号に基づいて、2倍されたクロック信号を生成すること。

[ C 2 3 ]

2倍されたクロック信号を生成することは、実質的に50%であるデューティ・サイクルと、前記2倍されたクロック信号の周波数よりも小さい周波数とを有する前記補正されたクロック信号に基づいて、実質的に50%であるデューティ・サイクルを有する前記2倍されたクロック信号を生成することを備える、C 2 2に記載の方法。

[ C 2 4 ]

デバイスであって、前記デバイスは下記を備える、

補正されたクロック信号を生成するための手段、ここで、前記生成するための手段は、

入力クロック信号のサイクルの一部の間に、電流ミスマッチを補正するように構成される

、と、

前記補正されたクロック信号の周波数よりも大きな周波数を有する出力クロック信号を

生成するための手段。

[ C 2 5 ]

デバイスであって、前記デバイスは下記を備える、

入力クロック信号を受け取り、補正されたクロック信号を生成するための手段と、

前記入力クロック信号の各サイクルの間に、出力電圧を生成するための手段と、

前記入力クロック信号の各サイクルの間に、電流ミスマッチを補正するための手段と、

前記補正されたクロック信号に基づいて、出力クロック信号を生成するための手段。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2014/047959 |

|---------------------------------------------------|

|                                                                                  |

|----------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. H03K3/017 H02M3/07 H03L7/089<br>ADD. |

|----------------------------------------------------------------------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| According to International Patent Classification (IPC) or to both national classification and IPC |

|---------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

|                                                                                                             |

|-------------------------------------------------------------------------------------------------------------|

| Minimum documentation searched (classification system followed by classification symbols)<br>H03K H02M H03L |

|-------------------------------------------------------------------------------------------------------------|

|                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |

|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) |

|------------------------------------------------------------------------------------------------------------------------------|

|                        |

|------------------------|

| EPO-Internal, WPI Data |

|------------------------|

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                               | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | HUILI XU ET AL: "Design of a low power charge pump circuit for phase-locked loops", HIGH SPEED INTELLIGENT COMMUNICATION FORUM (HSIC), 2012 4TH INTERNATIONAL, IEEE, 10 May 2012 (2012-05-10), pages 1-4, XP032203041, DOI: 10.1109/HSIC.2012.6213018 ISBN: 978-1-4673-0678-2 page 1 - page 3; figures 1-5 ----- | 1-22,24, 25           |

| Y         | -----                                                                                                                                                                                                                                                                                                            | 23                    |

| X         | US 2002/075050 A1 (MA STANLEY JEH-CHUN [CA]) 20 June 2002 (2002-06-20) paragraph [0042] - paragraph [0056]; figures 1-8 -----                                                                                                                                                                                    | 1-3,5,7, 11,25        |

|                                                                                                |                                                              |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C. | <input checked="" type="checkbox"/> See patent family annex. |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|                                           |

|-------------------------------------------|

| * Special categories of cited documents : |

|-------------------------------------------|

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

|                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               |

|-----------------------------------------------|

| "&" document member of the same patent family |

|-----------------------------------------------|

|                                                           |

|-----------------------------------------------------------|

| Date of the actual completion of the international search |

|-----------------------------------------------------------|

|                                                    |

|----------------------------------------------------|

| Date of mailing of the international search report |

|----------------------------------------------------|

|                 |

|-----------------|

| 5 November 2014 |

|-----------------|

|            |

|------------|

| 12/11/2014 |

|------------|

|                                      |

|--------------------------------------|

| Name and mailing address of the ISA/ |

|--------------------------------------|

|                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 |

|------------------------------------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| Authorized officer |

|--------------------|

|                    |

|--------------------|

| Mesplede, Delphine |

|--------------------|

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/US2014/047959            |

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                      | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y         | <p>HUH H ET AL: "Comparison Frequency Doubling and Charge Pump Matching Techniques for Dual-Band&lt;tex&gt;\\$Delta Sigma&lt;/tex&gt;Fractional-&lt;tex&gt;\\$N\\$&lt;/tex&gt;Frequency Synthesizer", IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE SERVICE CENTER, PISCATAWAY, NJ, USA, vol. 40, no. 11, 1 November 2005 (2005-11-01), pages 2228-2236, XP011141631, ISSN: 0018-9200, DOI: 10.1109/JSSC.2005.857368 page 2230 - page 2232; figures 6-7,9</p> <p>-----</p> | 23                    |

| A         | <p>NINGBING HOU ET AL: "Design of high performance CMOS charge pump for phase-locked loops synthesizer", COMMUNICATIONS, 2009. APCC 2009. 15TH ASIA-PACIFIC CONFERENCE ON, IEEE, PISCATAWAY, NJ, USA, 8 October 2009 (2009-10-08), pages 209-212, XP031597489, ISBN: 978-1-4244-4784-8 figures 1,3-4</p> <p>-----</p>                                                                                                                                                   | 1-25                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2014/047959

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| US 2002075050                          | A1 20-06-2002    | NONE                    |                  |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72)発明者 ヒンリッチス、ジェフリー・マーク

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775、クワアルコム・インコーポレイテッド気付

F ターム(参考) 5J001 BB05 BB10 BB12 BB25 CC01 CC04 DD06