(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7137913号**

**(P7137913)**

(45)発行日 令和4年9月15日(2022.9.15)

(24)登録日 令和4年9月7日(2022.9.7)

(51)国際特許分類

|        |                  |     |        |          |         |

|--------|------------------|-----|--------|----------|---------|

| H 01 L | 21/336 (2006.01) | F I | H 01 L | 29/78    | 3 7 1   |

| H 01 L | 29/788 (2006.01) |     | H 01 L | 29/78    | 6 1 8 B |

| H 01 L | 29/792 (2006.01) |     | H 01 L | 29/78    | 6 1 3 B |

| H 01 L | 29/786 (2006.01) |     | H 01 L | 27/108   | 3 2 1   |

| H 01 L | 21/8242(2006.01) |     | H 01 L | 27/11582 |         |

請求項の数 1 (全50頁) 最終頁に続く

(21)出願番号 特願2017-123146(P2017-123146)

(22)出願日 平成29年6月23日(2017.6.23)

(65)公開番号 特開2019-9259(P2019-9259A)

(43)公開日 平成31年1月17日(2019.1.17)

審査請求日 令和2年6月19日(2020.6.19)

(73)特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72)発明者 松崎 隆徳

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

吉住 健輔

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

審査官 宮本 博司

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

絶縁表面を有する基板上に、メモリトランジスタと、トランジスタと、を有する半導体装置であって、

前記メモリトランジスタは、第1の導電層、第2の導電層、第3の導電層、第1の絶縁層、第2の絶縁層、第3の絶縁層、及び第1の半導体層を有し、

前記トランジスタは、第4の導電層、第5の導電層、第6の導電層、第4の絶縁層、及び第2の半導体層を有し、

前記第1の導電層は、開口を有し、

前記第1の絶縁層は、前記開口の内側に接して設けられ、

前記第2の絶縁層は、前記第1の絶縁層の内側に接して設けられ、

前記第3の絶縁層は、前記第2の絶縁層の内側に接して設けられ、

前記第1の半導体層は、前記第3の絶縁層の内側に接して設けられ、且つ、前記第1の導電層の前記開口よりも上下方向に突出して設けられ、

前記第1の半導体層は、前記第1の絶縁層の上部、前記第2の絶縁層の上部、及び前記第3の絶縁層の上部よりも突出し、且つ前記第1の絶縁層の上部、前記第2の絶縁層の上部、及び前記第3の絶縁層の上部と接して設けられ、

前記第2の導電層は、前記第1の半導体層の底部に接して設けられ、

前記第3の導電層は、前記第1の半導体層の上部に接して設けられ、

前記第3の導電層の端部は、前記第1の半導体層の端部と一致し、

10

20

前記第4の導電層及び前記第5の導電層は、前記第2の半導体層にそれぞれ接して設けられ、

前記第4の導電層の端部及び前記第5の導電層の端部は、前記第2の半導体層の端部と一致し、

前記第4の絶縁層は、前記第2の半導体層に接して設けられ、

前記第6の導電層は、前記第4の絶縁層を介して前記第2の半導体層と重なる部分を有し、

前記第1の絶縁層、前記第3の絶縁層、及び前記第4の絶縁層は、それぞれ酸化物を含み、

前記第2の絶縁層は、窒化物を含み、

前記第1の半導体層と、前記第2の半導体層とは、同じ金属酸化物を含む、

半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の一態様は、半導体装置に関する。本発明の一態様は、記憶装置に関する。

##### 【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、電子機器、照明装置、入力装置、入出力装置、それらの駆動方法、又はそれらの製造方法、を一例として挙げることができる。

##### 【0003】

なお、本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタ、半導体回路、演算装置、記憶装置等は半導体装置の一態様である。また、撮像装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器は半導体装置を有している場合がある。

##### 【背景技術】

##### 【0004】

近年、扱われるデータ量の増大に伴って、より大きな記憶容量を有する半導体装置が求められている。単位面積あたりの記憶容量を増加させるためには、メモリセルを積層して形成することが有効である（特許文献1、特許文献2参照）。メモリセルを積層して設けることにより、単位面積当たりの記憶容量をメモリセルの積層数に応じて増加させることができる。

##### 【0005】

また、特許文献3には、酸化物半導体を用いた不揮発性の記憶装置が開示されている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0006】

【文献】米国特許公開2011/0065270号公報

米国特許第9634097号公報

米国特許公開2016/0079268号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0007】

記憶装置はデータを格納するメモリセルアレイの他に、書き込みや読み出し動作を制御するための制御回路を有する。一般にメモリセルアレイの駆動電圧は制御回路よりも高いため、制御回路で生成された信号に基づいてメモリセルアレイを駆動する駆動回路には、高耐圧な素子が必要となる。しかしながら、このような高耐圧なトランジスタなどの素子は、制御回路を構成する素子よりもサイズが大きいため、メモリセルの数（すなわち記憶容量）が増大することに伴って、駆動回路を含む周辺回路の占有面積も増大してしまうと

10

20

30

40

50

いった問題があった。

【0008】

本発明の一態様は、周辺回路の占有面積を縮小することを課題の一とする。または、単位面積当たりの記憶容量の大きい半導体装置を提供することを課題の一とする。または、生産性の高い半導体装置を提供することを課題の一とする。または、新規な半導体装置、または記憶装置を提供することを課題の一とする。

【0009】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から抽出することが可能である。

10

【課題を解決するための手段】

【0010】

本発明の一態様は、メモリトランジスタと、トランジスタと、を有する半導体装置である。メモリトランジスタは、第1の導電層、第2の導電層、第3の導電層、第1の絶縁層、第2の絶縁層、第3の絶縁層及び第1の半導体層を有する。トランジスタは、第4の導電層、第5の導電層、第4の絶縁層、及び第2の半導体層を有する。第1の導電層は開口を有し、第1の絶縁層は当該開口の内側に接して設けられ、第2の絶縁層は第1の絶縁層の内側に接して設けられ、第3の絶縁層は第2の絶縁層の内側に接して設けられ、第1の半導体層は第3の絶縁層の内側に接して設けられ、且つ、第1の導電層の開口よりも上下方向に突出して設けられる。また第2の導電層は第1の半導体層の底部に接して設けられ、第3の導電層は第1の半導体層の上部に接して設けられる。第4の導電層及び第5の導電層は、第2の半導体層にそれぞれ接して設けられる。第4の絶縁層は第2の半導体層に接して設けられる。第5の導電層は第4の絶縁層を介して第2の半導体層と重なる部分を有する。さらに、第1の絶縁層、第3の絶縁層、及び第4の絶縁層は、それぞれ酸化物を含む。さらに第2の絶縁層は、窒化物を含む。また、第1の半導体層と、第2の半導体層とは、同じ金属酸化物を含む。

20

【0011】

また、上記において、第3の導電層と、第4の導電層と、第5の導電層とは、互いに同じ金属元素を含むことが好ましい。

【0012】

30

また、上記において、第1の半導体層と、第2の半導体層とは、同じ金属酸化物膜を加工して形成されていることが好ましい。

【0013】

また、上記において、第3の導電層、第4の導電層、及び第5の導電層は、互いに同じ導電膜を加工して形成されていることが好ましい。

【0014】

また、上記において、第1の導電層と、第4の導電層とは、電気的に接続されていることが好ましい。

【0015】

また、上記において、基板を有することが好ましい。このとき、メモリトランジスタは、当該基板上に複数設けられていることが好ましい。さらに、複数のメモリトランジスタは、基板の一面に対して垂直方向に積層して設けられていることが好ましい。

40

【0016】

また、上記において、第1の半導体層及び第2の半導体層は、第1の半導体膜と、第2の半導体膜の積層構造を有することが好ましい。このとき、第1の半導体膜と、第2の半導体膜とは、結晶性が異なることが好ましい。または、第1の半導体膜と、第2の半導体膜とは、組成が異なることが好ましい。

【発明の効果】

【0017】

本発明の一態様によれば、周辺回路の占有面積を縮小できる。または、単位面積当たり

50

の記憶容量の大きい半導体装置を提供できる。または、生産性の高い半導体装置を提供できる。または、新規な半導体装置、または記憶装置を提供できる。

#### 【0018】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から抽出することが可能である。

#### 【図面の簡単な説明】

#### 【0019】

【図1】半導体装置の上面図及び断面図。

【図2】半導体装置の斜視図。

10

【図3】半導体装置の上面図。

【図4】半導体装置の断面図。

【図5】半導体装置の作製方法例を説明する図。

【図6】半導体装置の作製方法例を説明する図。

【図7】半導体装置の作製方法例を説明する図。

【図8】半導体装置の作製方法例を説明する図。

【図9】半導体装置の作製方法例を説明する図。

【図10】半導体装置の作製方法例を説明する図。

【図11】半導体装置の作製方法例を説明する図。

【図12】半導体装置の作製方法例を説明する図。

20

【図13】半導体装置の作製方法例を説明する図。

【図14】半導体装置の作製方法例を説明する図。

【図15】半導体装置の作製方法例を説明する図。

【図16】半導体装置の作製方法例を説明する図。

【図17】半導体装置の作製方法例を説明する図。

【図18】記憶装置のブロック図及び回路図。

【図19】記憶装置の三次元構造例を示す図。

【図20】記憶装置の三次元構造例を示す図。

【図21】記憶装置の三次元構造例を示す図。

【図22】記憶装置の回路図。

30

【図23】記憶装置の動作例を説明する回路図。

【図24】記憶装置の構成例。

【図25】A I システムのブロック図。

【図26】A I システムのブロック図。

【図27】I C の構成例。

【図28】電子機器の構成例。

【図29】電子機器の構成例。

#### 【発明を実施するための形態】

#### 【0020】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

40

#### 【0021】

なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

#### 【0022】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されな

50

い。

#### 【0023】

なお、本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

#### 【0024】

トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。本明細書におけるトランジスタは、IGFET (Insulated Gate Field Effect Transistor) や薄膜トランジスタ (TFT : Thin Film Transistor) を含む。

10

#### 【0025】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

#### 【0026】

また、本明細書等において、トランジスタのソース、又はドレインのどちらか一方のことを「第1電極」と呼び、ソース、又はドレインの他方を「第2電極」とも呼ぶことがある。なお、ゲートについては「ゲート」又は「ゲート電極」とも呼ぶ。

20

#### 【0027】

本明細書等において、金属酸化物 (metal oxide) とは、広い表現での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体（透明酸化物導電体を含む）、酸化物半導体 (Oxide Semiconductor または単にOSともいう) などに分類される。例えば、トランジスタの活性層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、OS FETと記載する場合においては、金属酸化物または酸化物半導体を有するトランジスタと換言することができる。

#### 【0028】

##### (実施の形態1)

本実施の形態では、本発明の一態様の半導体装置の構成例、作製方法例、回路構成、及びその動作方法例について説明する。

30

#### 【0029】

本発明の一態様は、メモリセルアレイと、高耐圧のトランジスタを含む回路部と、が同じ基板上に設けられた構成を有する。メモリセルアレイは、複数のメモリトランジスタが厚さ方向（縦方向）に積層された構成を有する。そのため、高耐圧のトランジスタをメモリセルアレイの近傍に配置することが可能となり、半導体装置の占有面積を縮小することができる。

#### 【0030】

ここで、メモリトランジスタが有する半導体層と、高耐圧のトランジスタが有する半導体層とは、同じ半導体膜を加工して形成される。これにより、各半導体層の形成工程を兼ねることができるために、作製工程を簡略化することができ、半導体装置の作製コストを低減できる。さらに、メモリセルアレイに接続される配線等と、高耐圧のトランジスタが有するソース電極、ドレイン電極、またはゲート電極等とが、同じ導電膜を加工して形成されれることが好ましい。

40

#### 【0031】

また、メモリトランジスタと、高耐圧のトランジスタとがそれぞれ有する半導体層に、酸化物半導体を適用することが好ましい。酸化物半導体を用いたトランジスタは、シリコンを用いたトランジスタ等に比べて、ソース - ドレイン間の耐圧を高めることができため、回路部を構成するトランジスタに好適に用いることができる。また酸化物半導体を用いたトランジスタは、シリコンに比べてゲート絶縁層の厚さを厚くしても駆動能力が低下しにくいという特徴を有するため、ゲート耐圧を向上させることができ、このようなト

50

ランジスタを回路部及びメモリトランジスタに用いることで、信頼性を高めることができる。

#### 【0032】

ここで、メモリセルアレイを制御する制御回路上に重畳するように、上記メモリセルアレイや高耐圧トランジスタを含む回路部を設けることが好ましい。例えば制御回路を単結晶シリコン基板上に形成したCMOS回路等で構成し、その上部に、メモリセルアレイや回路部を形成することで実現できる。これにより、さらに半導体装置の占有面積を縮小することができるため、一枚の単結晶シリコン基板あたりのチップ数が増大し、作製コストを低減できる。

#### 【0033】

以下では、より具体的な例について図面を参照して説明する。

#### 【0034】

##### 〔構成例〕

以下では、半導体装置700のメモリトランジスタ、メモリセルアレイ700M、及び回路部700Dが有するトランジスタの構成について、図面を参照して説明する。

#### 【0035】

##### 〔メモリセルアレイ〕

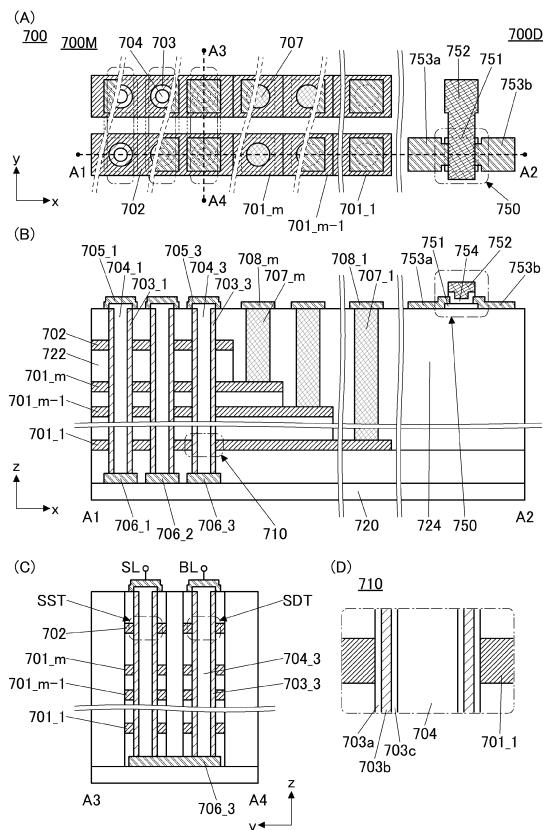

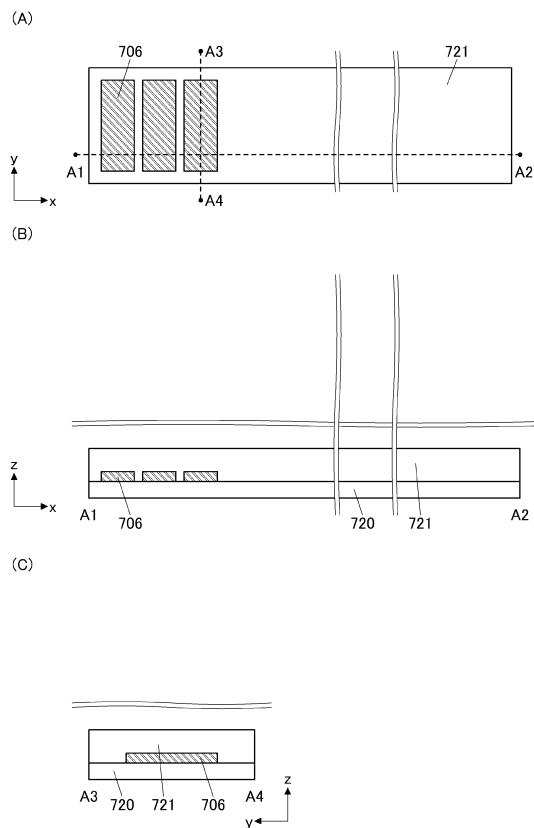

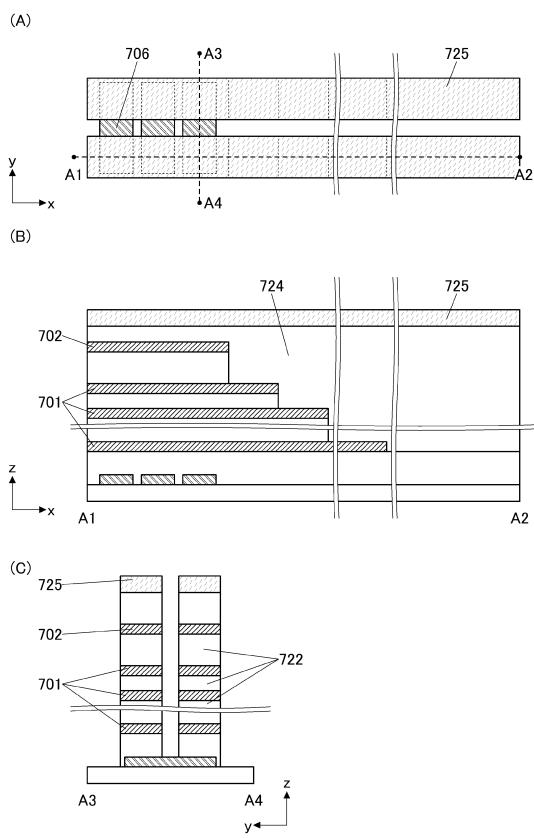

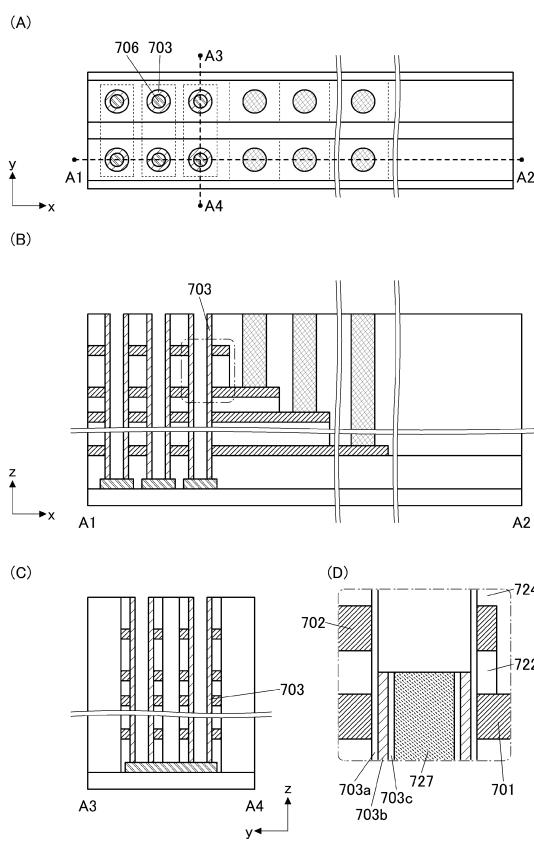

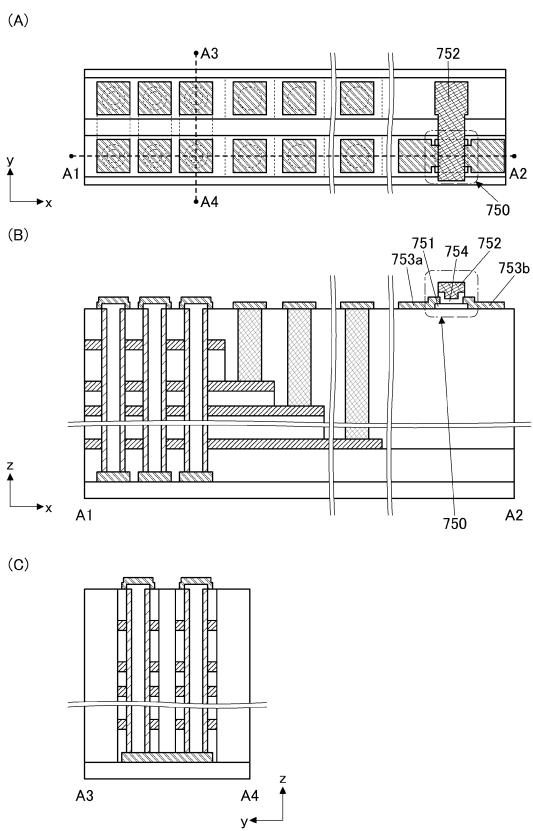

図1(A)は、半導体装置700の上面図であり、図1(B)は、図1(A)にA1-A2の一点鎖線で示す部位の断面図である。また、図1(C)は、図1(A)にA3-A4の一点鎖線で示す部位の断面図であり、メモリストーリングを説明する断面図である。

#### 【0036】

また、図1(D)は、図1(B)において、一点鎖線で囲まれた部分を拡大した断面図、または斜視図であり、メモリセルとして機能するメモリトランジスタを説明する図である。なお、以下においては、図1に示すように、x軸、y軸、z軸からなる直交座標系を便宜上設定して説明する。ここで、x軸およびy軸は、半導体装置700を設ける基板720の上面に平行にとり、z軸は基板720の上面に垂直にとる。

#### 【0037】

半導体装置700は、基板720上に、メモリセルアレイ700Mと、回路部700Dとを有する。図1では、回路部700Dが有するトランジスタ750を示している。

#### 【0038】

メモリセルアレイ700Mは、基板720上に、複数の導電層701(導電層701\_1乃至導電層701\_m:mは、2以上の自然数)、導電層702、複数の絶縁層703(絶縁層703\_1乃至絶縁層703\_3)、複数の酸化物層704(酸化物層704\_1乃至酸化物層704\_3)、複数の導電層705(導電層705\_1乃至導電層705\_3)、複数の導電層706(導電層706\_1乃至導電層706\_3)、複数の接続層707(接続層707\_1乃至接続層707\_m)、複数の導電層708(導電層708\_1乃至導電層708\_m)、複数の絶縁層722、絶縁層724等を有する。

#### 【0039】

導電層701または導電層702と、絶縁層722とは交互に積層され、さらにこれを覆うように設けられた絶縁層724を含む積層体を構成する。絶縁層703は、該積層体を貫通するように形成された開口部の内側に設けられる。酸化物層704は、絶縁層703の内側に設けられる。導電層705は、酸化物層704の上端部と電気的に接続するよう設けられる。導電層706は、酸化物層704の下端部と電気的に接続するよう設けられる。接続層707は、導電層701と電気的に接続する。導電層708は、接続層707と電気的に接続する。

#### 【0040】

なお、図1(B)では、複数の導電層701を表すために、導電層701を3段以上表示しているが、本実施の形態は図1(B)に限られることなく、少なくとも導電層701を2段以上有していればよい。また図1(B)等では、x方向に配列する複数の柱状の開口部内に設けられる絶縁層703及び酸化物層704、並びに導電層706及び導電層7

10

20

30

40

50

05等を表すために、これらを3つ示しているが、これに限られることなく、少なくとも2つ以上有していればよい。

#### 【0041】

ここで、図1(A)および図1(B)に示すように、導電層701はx軸方向に延伸して設けられる。また、図1(B)および図1(C)に示すように、絶縁層703および酸化物層704はz軸方向に延伸して設けられる。絶縁層703は、柱状の酸化物層704の側周辺を囲うように設けられている。つまり、導電層701と、絶縁層703および酸化物層704と、は互いに垂直に交差して設けられることが好ましい。また、図1(B)に示すように、接続層707は柱状に形成されており、z軸方向に延伸して設けられる。また、導電層708をy軸方向に延伸して設けてもよい。また、導電層705に接続される配線BLとして機能する導電層をy軸方向に延伸して設けてもよい。なお、導電層705の一部を配線BLとして機能させ、当該導電層をy軸方向に延伸して設けてもよい。

10

#### 【0042】

柱状の酸化物層704は、z軸方向の下端において、導電層706と電気的に接続し、上端において、導電層705と電気的に接続する。また、図1(C)に示すように、導電層706は、隣り合う2つの柱状の酸化物層704の下端と電気に接続し、該2つの柱状の酸化物層704の上端は、それぞれ、電気的に分離した導電層705と、電気的に接続する。

#### 【0043】

ここで、導電層701と、絶縁層703および酸化物層704と、が交差する領域近傍がメモリトランジスタ(メモリトランジスタ710)として機能する。また、導電層702と、絶縁層703および酸化物層704と、が交差する領域近傍が選択トランジスタ(ピット線側選択トランジスタ:SDT、またはソース線側選択トランジスタ:SST)として機能する。これらのメモリトランジスタおよび選択トランジスタのチャネル長方向はz軸に平行になる。メモリトランジスタまたは選択トランジスタが電気的に直列に接続されており、これらがメリストリングを構成している。

20

#### 【0044】

なお、本実施の形態に示す半導体装置の構成は一例であり、本発明は、本実施の形態に係る図面等に示す、回路素子および配線等の、個数および配置等に限定されるものではない。本実施の形態に係る半導体装置が有する、回路素子および配線等の、個数および配置等は、回路構成や駆動方法に合わせて適宜設定することができる。

30

#### 【0045】

メモリセルアレイ700M及び回路部700Dを設ける基板720は絶縁表面を有していることが好ましい。絶縁表面を有する基板としては、表面に絶縁膜が形成された半導体基板、絶縁性基板、表面に絶縁膜が形成された導電性基板などを用いればよい。半導体基板としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムなどの半導体基板などを用いればよい。また、絶縁性基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板(イットリア安定化ジルコニア基板など)、樹脂基板などを用いればよい。また、前述の半導体基板内部に絶縁性の領域を有する半導体基板、例えばSOI(Silicon On Insulator)基板などを用いてもよい。また、導電性基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などを用いればよい。

40

#### 【0046】

導電層701は、メモリトランジスタ710のゲートとして機能し、ワード線と電気的に接続する。すなわち、導電層701、接続層707、および導電層708は、ワード線の一部としても機能する。ここで、導電層701は、図1(B)に示すように、下層の導電層701が上層の導電層701よりA2側に延伸した、階段状に設けられることが好ましい。このように、導電層701を設けることにより、下層の導電層701の上面の一部の領域が、より上層の導電層701と重ならないため、導電層701各層の当該領域と各

50

接続層 707 を接続させることができる。

#### 【0047】

導電層 701 として、シリコンや、金属など、導電性を有する材料を用いることができる。導電層 701 として、シリコンを用いる場合、アモルファスシリコンや、ポリシリコンを用いることができる。また、シリコンに導電性を持たせるため、p型不純物やn型不純物を添加してもよい。また、シリコンを含む導電性材料として、チタン、コバルト、またはニッケルを含むシリサイドを導電層 701 として用いることができる。また、金属材料を導電層 701 に用いる場合、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニア、ベリリウム、インジウム、ルテニウムなどから選ばれた金属元素を 1種以上含む材料を用いることができる。

10

#### 【0048】

導電層 702 は、絶縁層 722 を介して導電層 701 の上に設けられる。導電層 702 は、選択トランジスタ（ビット線側選択トランジスタ：SDT、およびソース線側選択トランジスタ：SST）のゲートとして機能する。また、導電層 702 は、導電層 701 と同様の材料を用いることができる。また、導電層 702 は、導電層 701 と同じ材料を用いてもよいし、異なる材料を用いてもよい。導電層 701、および導電層 702 は、用途に応じて、仕事関数などを考慮し、決定すればよい。

20

#### 【0049】

導電層 701 および導電層 702 の、上層または下層に設けられる絶縁層 722 として、絶縁性を有する酸化物、窒化物、酸化窒化物、窒化酸化物、金属酸化物、金属酸化窒化物、金属窒化酸化物などを用いることができる。酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、もしくは空孔を有する酸化シリコンまたは樹脂は、比誘電率が低いため、絶縁層 722 に用いることは好適である。

20

#### 【0050】

一方、絶縁層 722 として、酸化アルミニウム、酸化ガリウム、酸化ハフニウム、酸化ジルコニア、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、シリコンおよびハフニウムを有する酸化窒化物またはシリコンおよびハフニウムを有する窒化物などを用いることも可能だが、これらは比誘電率が高いため、2つの導電層 701 の間、または導電層 701 と導電層 702との間に寄生容量が生じる場合がある。そのため、デバイスの設計、用途に応じて絶縁層 722 に用いる材料を決めることができる。

30

#### 【0051】

また、導電層 701、導電層 702 等を覆う絶縁層 724 としては、絶縁層 722 と同様の材料を用いることができる。

#### 【0052】

酸化物層 704、絶縁層 703、および導電層 701（導電層 701\_1 乃至導電層 701\_m のいずれか一）により、メモリトランジスタ 710 が構成される。図 1 (B)、(C) には、メモリトランジスタ 710 が m 段（m は 2 以上の自然数）積層している例を示している。

40

#### 【0053】

導電層 705 は、酸化物層 704 と電気的に接続し、ソース線 SL、またはビット線 BL の一部として機能する。導電層 705 として、金属元素を含む導電性材料を用いることが好ましい。また、導電層 705 と酸化物層 704 の界面には、導電層 705 が有する金属元素と、酸化物層 704 の成分とを含む金属化合物層が形成されていることが好ましい。該金属化合物が形成されることで、導電層 705 と、酸化物層 704 とのコンタクト抵抗が低減するため好ましい。または、酸化物層 704 に含まれる酸素を、導電層 705 が吸収し、酸化物層 704 の、導電層 705 と酸化物層 704 の界面近傍の抵抗を低減することで、導電層 705 と、酸化物層 704 とのコンタクト抵抗を低減することができる。

50

**【 0 0 5 4 】**

導電層 7 0 5 として、アルミニウム、ルテニウム、チタン、タンタル、クロム、タングステン、および銅から選ばれた一、または複数の金属元素を含む導電性材料を用いることが好ましい。

**【 0 0 5 5 】**

導電層 7 0 6 は、図 1 ( C ) に示すように、ビット線 B L の一部として機能する導電層 7 0 5 と電気的に接続する酸化物層 7 0 4 と、ソース線 S L の一部として機能する導電層 7 0 5 と電気的に接続する酸化物層 7 0 4 と、電気的に接続することで、メモリストリングを構成する。図 1 ( A ) 中の一点鎖線で囲まれた領域は、1 つのメモリストリングを表している。なお、図 1 ( A ) では 3 つのメモリストリングが明示されているが、実際には 1 つのメモリセルアレイが有するメモリストリングの数は偶数であることが好ましく、 $2^n$  ( $n$  は 1 以上の自然数) であることがより好ましい。

10

**【 0 0 5 6 】**

導電層 7 0 6 は、導電層 7 0 5 と同様の材料を用いることができる。また、導電層 7 0 6 は、導電層 7 0 5 と同じ材料を用いてもよいし、異なる材料を用いてもよい。

**【 0 0 5 7 】**

また、導電層 7 0 6 と酸化物層 7 0 4 の界面には、導電層 7 0 6 が有する金属元素と、酸化物層 7 0 4 の成分とを含む金属化合物層が形成されていることが好ましい。該金属化合物が形成されることで、導電層 7 0 6 と、酸化物層 7 0 4 とのコンタクト抵抗が低減するため好ましい。または、酸化物層 7 0 4 に含まれる酸素を、導電層 7 0 6 が吸収し、酸化物層 7 0 4 の、導電層 7 0 6 と酸化物層 7 0 4 の界面近傍の抵抗を低減することで、導電層 7 0 6 と、酸化物層 7 0 4 とのコンタクト抵抗を低減することができる。

20

**【 0 0 5 8 】**

図 1 ( D ) は、1 つのメモリトランジスタ 7 1 0 及びその近傍の拡大図を示している。図 1 ( D ) に示すように、絶縁層 7 0 3 は、絶縁層 7 0 3 a 、絶縁層 7 0 3 b 、および絶縁層 7 0 3 c を有する。絶縁層 7 0 3 a は、導電層 7 0 1 側に設けられ、絶縁層 7 0 3 c は、酸化物層 7 0 4 側に設けられ、絶縁層 7 0 3 b は、絶縁層 7 0 3 a と絶縁層 7 0 3 c の間に設けられる。絶縁層 7 0 3 a はゲート絶縁層として機能し、絶縁層 7 0 3 b は電荷蓄積層として機能し、絶縁層 7 0 3 c はトンネル絶縁層として機能する。

**【 0 0 5 9 】**

30

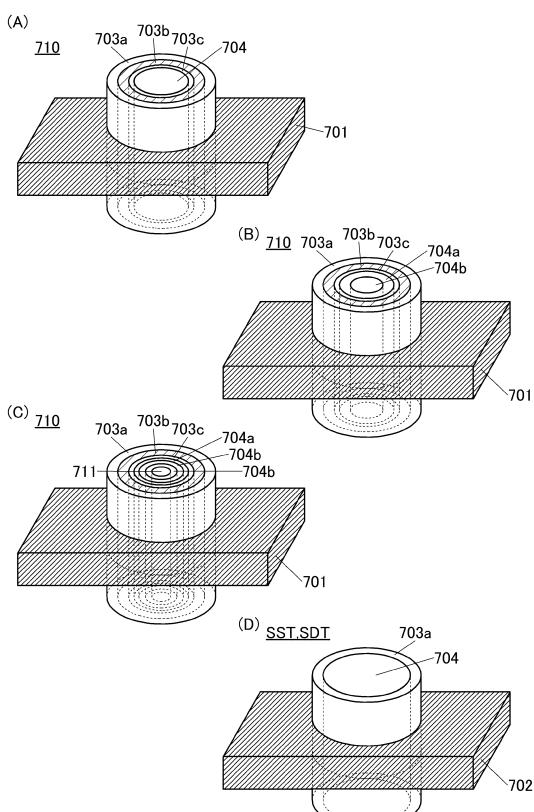

ここで、図 2 ( A ) には、1 つのメモリトランジスタ 7 1 0 及びその近傍の斜視図を示している。

**【 0 0 6 0 】**

絶縁層 7 0 3 a として、酸化シリコンや、酸化窒化シリコンを用いることが好ましい。また、酸化アルミニウム、酸化ハフニウム、またはアルミニウムおよびハフニウムを有する酸化物を用いてもよい。また、これらを積層して絶縁層 7 0 3 a としてもよい。

**【 0 0 6 1 】**

絶縁層 7 0 3 b は、電荷蓄積層として機能する材料を用いることが好ましく、窒化シリコンや、窒化酸化シリコンを用いることが好ましい。また、酸化アルミニウム、酸化ハフニウム、またはアルミニウムおよびハフニウムを有する酸化物を用いてもよい。

40

**【 0 0 6 2 】**

絶縁層 7 0 3 c として、酸化シリコンや、酸化窒化シリコンを用いることが好ましい。また、酸化アルミニウム、酸化ハフニウム、またはアルミニウムおよびハフニウムを有する酸化物を用いてもよい。また、これらを積層して絶縁層 7 0 3 c としてもよい。また、絶縁層 7 0 3 c は、絶縁層 7 0 3 a より薄いことが好ましい。詳細は後述するが、メモリトランジスタへのデータの書き込み、または消去において、絶縁層 7 0 3 c を通って、酸化物層 7 0 4 と絶縁層 7 0 2 b の間で、電荷の移動が行われる。すなわち、絶縁層 7 0 3 c は、トンネル絶縁層として機能する。

**【 0 0 6 3 】**

特に、導電層 7 0 1 、導電層 7 0 2 、および絶縁膜を有する積層体に設けられた開口に

50

絶縁層 703 を形成する場合、開口の底部に形成された絶縁層 703 は、ドライエッチングなどを用いた異方性エッチングにより除去する必要がある。異方性エッチングの際、絶縁層 703c は、側面においても、プラズマ、ラジカル、ガス、薬液などに曝される。これらによって絶縁層 703c の側面がダメージを受けると、絶縁層 703c にトラップセンターが生じ、トランジスタの電気特性に影響を与える場合がある。トラップセンターの生成を抑制するためには、絶縁層 703c の側面は、エッチングによるダメージに対して高い耐性を有していることが求められる。この場合、絶縁層 703c として、酸化アルミニウム、酸化シリコンと酸化アルミニウムの積層、または酸化窒化シリコンと酸化アルミニウムの積層を用いることが好ましい。

## 【0064】

10

絶縁層 703a、絶縁層 703b、および絶縁層 703c は、ALD 法や CVD 法を用いて形成することができる。また、絶縁層 703a、絶縁層 703b、および絶縁層 703c の界面の汚染を防ぐためには、同一チャンバー内で、または複数のチャンバーを有するマルチチャンバ方式の成膜装置を用いて、大気雰囲気に曝すことなく、連続で成膜することが好ましい。

## 【0065】

酸化物層 704 は、酸化物半導体として機能する金属酸化物（以下、酸化物半導体ともいう）を用いることが好ましい。酸化物半導体は、シリコンなどからなる半導体と比較して、トランジスタのオン特性が良好で、高い移動度が得られるため、好ましい。

## 【0066】

20

例えば、酸化物層 704 として、In - M - Zn 酸化物（元素 M は、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種）等の金属酸化物を用いるとよい。また、酸化物層 704 として、In - Ga 酸化物、In - Zn 酸化物を用いてもよい。

## 【0067】

図 2 (B)、(C) には、酸化物層 704 を積層構造とした場合の例を示している。

## 【0068】

図 2 (B) に示すように、メモリトランジスタ 710 は絶縁層 703c 側に設けられる酸化物層 704a と酸化物層 704a の内側に設けられる酸化物層 704b を有することが好ましい。このとき、酸化物層 704a は、酸化物層 704b に対して、相対的にエネルギーギャップの広い酸化物を用いることが好ましい。ここで、エネルギーギャップの広い酸化物を、ワイドギャップ、エネルギーギャップの狭い酸化物をナローギャップと呼ぶことがある。

30

## 【0069】

酸化物層 704a をナローギャップとし、酸化物層 704b をワイドギャップとする場合、酸化物層 704a の伝導帯下端のエネルギーが、酸化物層 704b の伝導帯下端のエネルギーより高くなることが好ましい。また、言い換えると、酸化物層 704a の電子親和力が、酸化物層 704b の電子親和力より小さいことが好ましい。

40

## 【0070】

また、酸化物層 704a と酸化物層 704b は、各金属原子の原子数比が異なる組み合わせにすることが好ましい。具体的には、酸化物層 704a に用いる金属酸化物において、構成元素中の元素 M の原子数比が、酸化物層 704b に用いる金属酸化物における、構成元素中の元素 M の原子数比より、大きいことが好ましい。また、酸化物層 704a に用いる金属酸化物において、In に対する元素 M の原子数比が、酸化物層 704b に用いる金属酸化物における、In に対する元素 M の原子数比より大きいことが好ましい。また、酸化物層 704b に用いる金属酸化物において、元素 M に対する In の原子数比が、酸化物層 704a に用いる金属酸化物における、元素 M に対する In の原子数比より大きいことが好ましい。

50

## 【0071】

酸化物層 704a には、例えば  $In : Ga : Zn = 1 : 3 : 4$ 、 $In : Ga : Zn = 1 : 3 : 2$ 、または  $In : Ga : Zn = 1 : 1 : 1$  の組成およびその近傍の組成を有する金属酸化物を用いることができる。また、酸化物層 704b には、例えば  $In : Ga : Zn = 4 : 2 : 3$  から 4.1、 $In : Ga : Zn = 1 : 1 : 1$ 、または  $In : Ga : Zn = 5 : 1 : 6$  の組成およびその近傍の組成を有する金属酸化物を用いることができる。これらの酸化物層 704a および酸化物層 704b を上記の原子数比の関係を満たして組み合わせることが好ましい。例えば、酸化物層 704a を、 $In : Ga : Zn = 1 : 3 : 4$  の組成およびその近傍の組成を有する金属酸化物、酸化物層 704b を、 $In : Ga : Zn = 4 : 2 : 3$  から 4.1 の組成およびその近傍の組成を有する金属酸化物とするのが好ましい。なお、上記組成は、基板上に形成された酸化物中の原子数比、またはスパッタターゲットにおける原子数比を示す。

10

## 【0072】

また、酸化物層 704a として、後述する、CAC-OS を用い、酸化物層 704b として、CAC-OS を用いることが好ましい。酸化物層 704a として、CAC-OS を用いる場合、c 軸は、図 1 (A) などに示す x - y 平面に平行、すなわち z 軸に垂直で、かつ開口の側面から中心に向かうように配向することが好ましい。

## 【0073】

ここで、酸化物層 704a と酸化物層 704b の接合部において、伝導帯下端はなだらかに変化する。換言すると、酸化物層 704a と酸化物層 704b の接合部における伝導帯下端は、連続的に変化または連続接合するともいうことができる。このようにするために、酸化物層 704a と酸化物層 704b との界面において形成される混合層の欠陥準位密度を低くするとよい。

20

## 【0074】

具体的には、酸化物層 704a と酸化物層 704b が、酸素以外に共通の元素を有する（主成分とする。）ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物層 704b が  $In - Ga - Zn$  酸化物の場合、酸化物層 704a として、 $In - Ga - Zn$  酸化物、 $Ga - Zn$  酸化物、酸化ガリウムなどを用いるとよい。これにより、酸化物層 704a と酸化物層 704b との界面における欠陥準位密度を低くすることができる。そのため、界面散乱によるキャリア伝導への影響が小さくなり、メモリトランジスタ 710 は高いオン電流を得られる。

30

## 【0075】

図 2 (B) に示すように、酸化物層 704b は、酸化物層 704a に囲まれるように設けられている。このような構成の場合、酸化物層 704 に、導電層 705 から導電層 706 への方向、あるいは導電層 706 から導電層 705 への方向（すなわち z 軸方向）にキャリアを流す際、ナローギャップを有する成分において、主にキャリアが流れる。このため、上記構成を用いる場合、トランジスタのオン状態において高い電流駆動力、つまり大きなオン電流、及び高い電界効果移動度を得ることができる。

## 【0076】

また、酸化物層 704b と、絶縁層 703c と、の間に酸化物層 704a を設けることで、キャリアパスとなる酸化物層 704b と、絶縁層 703c が直接接する事なく、トラップセンターの形成を抑制することができる。半導体（酸化物半導体）と、絶縁層との界面に形成されたトラップセンターは、電子を捕獲し、トランジスタのしきい値電圧をプラス方向に変動させるため、トランジスタの信頼性や、オン、オフ特性に悪影響を及ぼす恐れがある。よって、当該酸化物を用いるトランジスタは、トラップセンターによる電気特性の影響を受けることがないため、オン状態においてより高い電流駆動力、つまり大きなオン電流、及び高い電界効果移動度を得ることができる。また、当該トランジスタ、および当該トランジスタを用いた半導体装置は、高い信頼性を得ることができる。

40

## 【0077】

図 2 (D) に示すメモリトランジスタ 710 は、絶縁層 703a、絶縁層 703b、お

50

および絶縁層 703c の内側に、酸化物層 704a が設けられ、酸化物層 704a の内側に酸化物層 704b が設けられ、酸化物層 704b の内側に酸化物層 704c が設けられている。また、酸化物層 704c の内側には、絶縁層 711 が埋め込まれるように設けられていてもよい。なお、絶縁層 711 は、必ずしも設けなくてよく、酸化物層 704c の内側は、空洞でもよい。

#### 【0078】

酸化物層 704b は、酸化物層 704a、および酸化物層 704c に挟まれるように設けられる。このとき、酸化物層 704c は、酸化物層 704a と同様にワイドギャップであることが好ましい。ワイドギャップである酸化物層 704c を設けることで、酸化物層 704 を流れるキャリアを酸化物層 704b に閉じ込めることができ、トランジスタのオン状態において高い電流駆動力、つまり大きなオン電流、及び高い電界効果移動度を得ることができる。10

#### 【0079】

また、酸化物層 704c の内側に絶縁層 711 を設ける場合、絶縁層 711 は、酸化物層 704 に酸素を供給できる材料であることが好ましい。絶縁層 711 として、水素や窒素を極力含まない酸化物を用いることで、酸化物層 704 に酸素を供給できる場合がある。酸化物層 704 に酸素を供給することで、酸化物層 704 中に含まれる水素や水などの不純物を除去することができ、酸化物層 704 は高純度化する。不純物が極力低減された酸化物を酸化物層 704 として用いることで、メモリトランジスタ、および当該トランジスタを用いた半導体装置は、高い信頼性を得ることができる。20

#### 【0080】

また、絶縁層 711 として、水素や窒素などの不純物を供給できる材料を用いることができる。絶縁層 711 に水素や窒素を含む酸化物を用いることで、酸化物層 704 に水素や窒素を供給できる場合がある。酸化物層 704 に水素や窒素を供給することで、酸化物層 704 の抵抗値が下がる場合がある。酸化物層 704 の抵抗値を、回路動作の弊害にならない程度に下げることで、より低い駆動電圧で、メモリトランジスタを動作させることができる。また、メモリトランジスタのオン状態において高い電流駆動力、つまり大きなオン電流、及び高い電界効果移動度を得ることができる。20

#### 【0081】

図2(D)には、選択トランジスタ(ピット線側トランジスタ: SDT、またはソース線側トランジスタ: SST)及びその近傍における斜視図を示している。30

#### 【0082】

図2(D)に示すように、選択トランジスタには電荷蓄積層を設けなくてもよい。よって、ピット線側トランジスタ: SDT、およびソース線側トランジスタ: SSTにおいて、絶縁層 703 として絶縁層 703b および絶縁層 703c を設けず、絶縁層 703a のみを設ける構成にしてもよい。

#### 【0083】

なお、図2(D)において、酸化物層 704 を単層で示しているが、これに限らない。酸化物層 704 は、上記で例示した、2層構造または3層構造としてもよいし、4層以上の積層構造でもよい。また、酸化物層 704 の内側に、絶縁層 711 が設けられていてもよい。40

#### 【0084】

なお、メモリトランジスタ 710 が設けられる、積層体に形成された開口は、図1(A)や、図2の各図において、上面を円形状としているがこれに限られるものではなく、例えば上面を橢円形状としてもよいし、三角形、四角形などの多角形状にしてもよい。また、多角形状とする場合、角部が丸みを帯びている形状としてもよい。また、当該開口の上面形状や断面形状に合わせて、絶縁層 703、および酸化物層 704 の上面形状や断面形状も変化することがある。また、当該開口は、上方(導電層 705 側)の開口の断面積と比較して、下方(導電層 706 側)の開口の断面積が狭くなるような形状としてもよい。

#### 【0085】

10

20

30

40

50

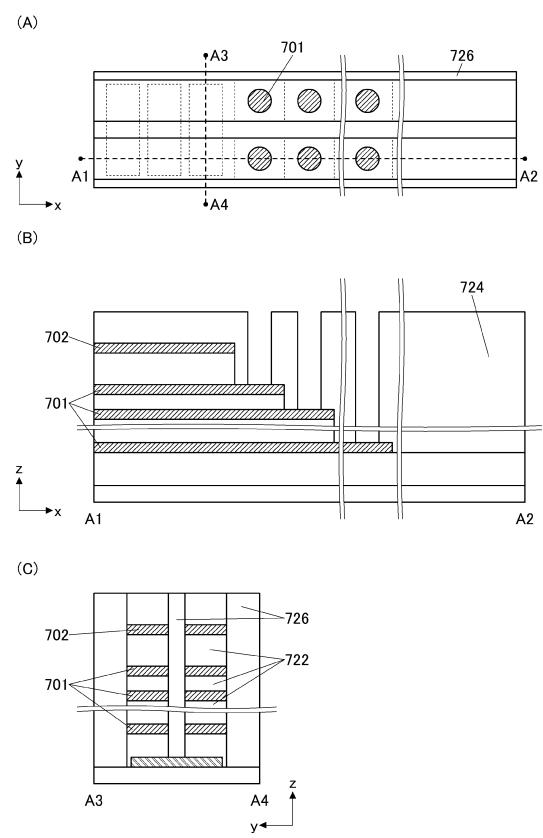

〔接続構成例〕

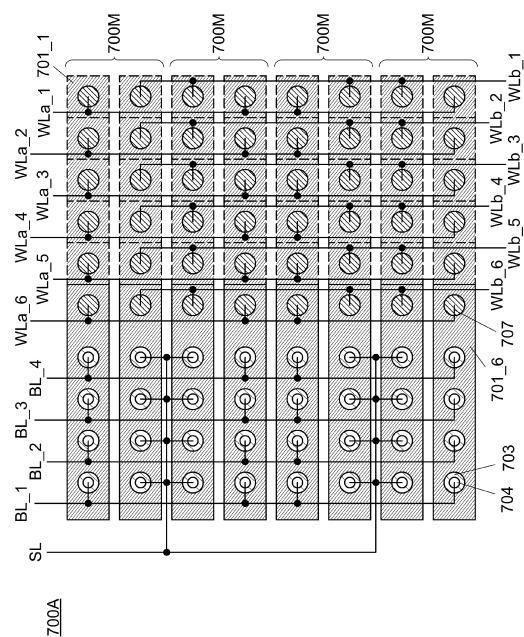

図3は、メモリトランジスタを6段有するメモリセルアレイ700Mを複数組み合わせた記憶装置700Aを説明する上面図である。なお、図3では、説明を容易にするため、一部の構成要素を省略している。例えば、導電層701上に設けられる選択トランジスタ（ピット線側トランジスタ：SDT、およびソース線側トランジスタ：SST）や、それらの構成要件である導電層702は、省略している。また、ピット線BLやソース線SLの一部として機能する導電層705、およびワード線WLの一部として機能する導電層708は、実線にて示している。

【0086】

記憶装置700Aにおいて、各メモリセルアレイ700Mは、6段のメモリトランジスタを有するメモリストリングを4つ有する。

10

【0087】

メモリストリングのピット線側の端は、それぞれ異なるピット線BL（BL\_1乃至BL\_4）と電気的に接続する。一方、メモリストリングのソース線側の端は、ソース線SLと電気的に接続されており、共通の電位が与えられている。ソース線SLは、接地されてもよいし、一定の電位が与えられてもよい。また、回路の動作に合わせて、電位を変動させてもよい。

【0088】

導電層701\_1乃至導電層701\_6は、それぞれ異なるワード線WLと電気的に接続する。ピット線側の導電層701\_1乃至導電層701\_6は、それぞれWL\_a\_1乃至WL\_a\_6と電気的に接続し、ソース線側の導電層701\_1乃至導電層701\_6は、それぞれWL\_b\_1乃至WL\_b\_6と電気的に接続する。

20

【0089】

ピット線BL（BL\_1乃至BL\_4）、およびワード線（WL\_a\_1乃至WL\_a\_6、およびWL\_b\_1乃至WL\_b\_6）を適宜選択することで、メモリセルアレイ700M内の任意のメモリトランジスタを選択することができる。また、選択されたメモリトランジスタに対して、書き込み、読み出し、消去などを行うことができる。

【0090】

また、各メモリストリングには、選択トランジスタ（図示しない）が設けられているため、記憶装置700A内の任意のメモリセルアレイ700Mを選択し、選択されたメモリセルアレイ700M内の任意のメモリトランジスタに対して、書き込み、読み出し、消去などを行うことができる。

30

【0091】

〔回路部〕

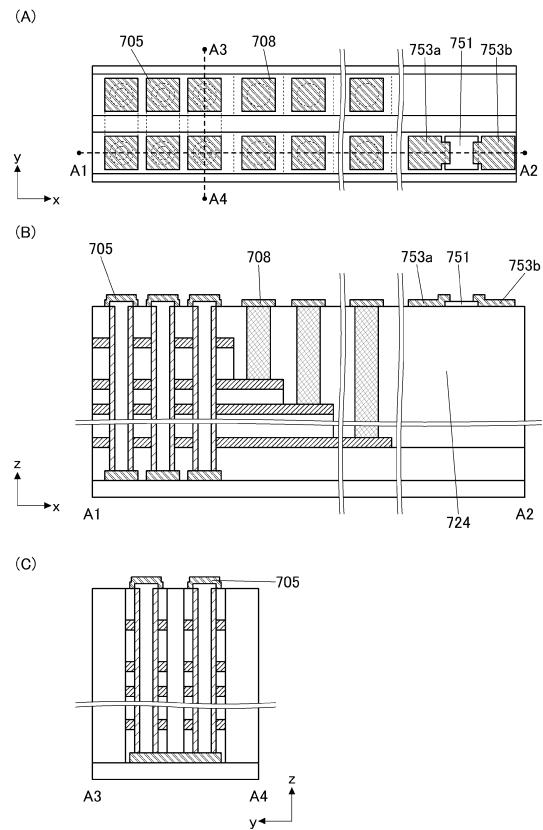

回路部700Dには、少なくとも1つ以上のトランジスタ750が設けられている。図1（A）、（B）には、回路部700Dの例として、トランジスタ750を示している。トランジスタ750は、チャネルが形成される半導体層に金属酸化物が適用され、極めて耐圧の高いトランジスタである。

【0092】

トランジスタ750は、酸化物層751、導電層752、導電層753a、導電層753b、及び絶縁層754を有する。酸化物層751は、絶縁層724上に設けられる。絶縁層754は酸化物層751上に設けられ、その一部はゲート絶縁層として機能する。導電層752は絶縁層754上に設けられ、その一部はゲート電極として機能する。導電層753a及び導電層753bは、それぞれ酸化物層751と接して設けられ、ソース電極またはドレイン電極として機能する。

40

【0093】

ここで、酸化物層751は、上記メモリトランジスタ710が有する酸化物層704と同じ酸化物膜を加工して形成されていることが好ましい。さらに、導電層753a及び導電層753bは、上記メモリセルアレイ700Mの導電層705や導電層708と同じ導電膜を加工して形成されていることが好ましい。

50

**【0094】**

これにより、トランジスタ750の作製工程の一部を、メモリセルアレイ700Mの作製工程と兼ねることができるために、低成本でメモリセルアレイ700Mと回路部700Dとを同一基板上に形成することができる。

**【0095】**

絶縁層754は、上記絶縁層703aと同様の材料を用いることができる。

**【0096】**

導電層752は、上記導電層701等と同様の材料を用いることができる。

**【0097】**

続いて、トランジスタ750とメモリセルアレイ700Mとの接続例について説明する。

10

**【0098】**

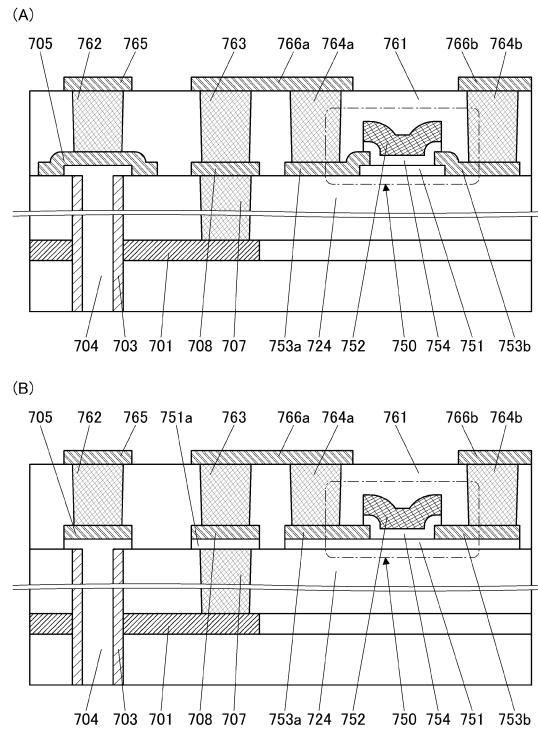

図4(A)には、トランジスタ750の拡大図を示している。さらに図4(A)では、トランジスタ750と電気的に接続する1つのワード線と、1つのメモリストリングの断面概略図を示している。

**【0099】**

図4(A)では、トランジスタ750を覆って、複数の開口を有する絶縁層761が設けられている。また絶縁層761の開口を埋める複数の接続層(接続層762、接続層763、接続層764a、接続層764b等)が設けられている。また、絶縁層761上には、配線として機能する複数の導電層(導電層765、導電層766a、導電層766b等)が設けられている。

20

**【0100】**

トランジスタ750の導電層753bは、接続層764bを介して導電層766bと電気的に接続されている。また、トランジスタ750の導電層753aと、導電層701とは、接続層707、導電層708、接続層763、導電層766a、及び接続層764aを介して電気的に接続されている。また、導電層705は、接続層762を介して導電層765と電気的に接続されている。

**【0101】**

このような構成とすることで、トランジスタ750とワード線として機能する導電層701とを電気的に接続することができる。

**【0102】**

30

ここで、図4(A)に示すトランジスタ750は、半導体層として機能する酸化物層751の上面の一部、及び側面に接して導電層753aと導電層753bとが設けられている。また、絶縁層754と導電層752とは、それぞれ導電層753a及び導電層753bと重畠する部分を有する。図4(A)に示すトランジスタは750の構造は、T G T C(Top-Gate-Bottom-Contact)型のトランジスタと言うことができる。

**【0103】**

図4(B)には、図4(A)とは一部の構成が異なる断面構成例を示している。

**【0104】**

図4(B)に示すトランジスタ750は、酸化物層751の端部と、導電層753aの端部または導電層753bの端部が、それぞれ一致している。また導電層753a及び導電層753bの下には酸化物層751が存在し、導電層753a及び導電層753bと絶縁層724とが接しないように形成されている。このような構成とすることで、導電層753a及び導電層753b等に絶縁層724中の酸素が拡散することを防ぐことができ、絶縁層724から酸化物層751に供給しうる酸素の量が減少することを防止できるとともに、導電層753a及び導電層753bが酸化されて導電性が低下することを抑制することができる。

40

**【0105】**

図4(B)に示すような構成は、例えば酸化物層751となる酸化物膜と、導電層753a及び導電層753bとなる導電膜を積層した積層膜を成膜し、酸化物層751となる

50

領域を残すように当該積層膜を加工し、続いて、酸化物層 751 上のチャネル形成領域と重なる導電膜の一部をエッチングにより除去することで、形成することができる。

#### 【0106】

ここで、導電層 708 と接続層 707との間に、酸化物層 751 と同じ酸化物を含む酸化物層 751a が形成される場合がある。酸化物層 751a は、導電層 708 や接続層 707 と接するため、工程中にかかる熱などにより、膜中の酸素が引き抜かれることや、水素が供給されることなどによって、キャリア密度が十分に高い状態、すなわち十分に低抵抗化された状態となっている。そのため、酸化物層 751a が設けられることによる電気抵抗の上昇の影響はほとんどないと言える。

#### 【0107】

以上が構成例についての説明である。

#### 【0108】

##### [金属酸化物]

以下では、上記構成例で例示した酸化物層 704、および酸化物層 751 等に適用可能な金属酸化物について説明する。

#### 【0109】

金属酸化物は、少なくともインジウムまたは亜鉛を含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウムまたはスズなどが含まれていることが好ましい。また、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニア、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

#### 【0110】

ここでは、金属酸化物が、インジウム、元素 M および亜鉛を有する  $In_n M Z_n$  酸化物である場合を考える。なお、元素 M は、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素 M に適用可能な元素としては、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニア、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウムなどがある。ただし、元素 M として、前述の元素を複数組み合わせることもできる。

#### 【0111】

なお、本明細書等において、窒素を有する金属酸化物も金属酸化物 (metal oxide) と総称する場合がある。また、窒素を有する金属酸化物を、金属酸窒化物 (metal oxy nitride) と呼称してもよい。

#### 【0112】

##### [金属酸化物の構成]

以下では、本発明の一態様で開示されるトランジスタに用いることができる CAC (Cloud-Aligned Composite) - OS の構成について説明する。

#### 【0113】

なお、本明細書等において、CAC (c-axis aligned crystal)、および CAC (Cloud-Aligned Composite) と記載する場合がある。なお、CAC は結晶構造の一例を表し、CAC は機能、または材料の構成の一例を表す。

#### 【0114】

CAC - OS または CAC - metal oxide とは、材料の一部では導電性の機能と、材料の一部では絶縁性の機能とを有し、材料の全体では半導体としての機能を有する。なお、CAC - OS または CAC - metal oxide を、トランジスタの活性層に用いる場合、導電性の機能は、キャリアとなる電子（または正孔）を流す機能であり、絶縁性の機能は、キャリアとなる電子を流さない機能である。導電性の機能と、絶縁性の機能とを、それぞれ相補的に作用させることで、スイッチングさせる機能 (On / Off させる機能) を CAC - OS または CAC - metal oxide に付与することが

10

20

30

40

50

できる。CAC - OSまたはCAC - metal oxideにおいて、それぞれの機能を分離させることで、双方の機能を最大限に高めることができる。

#### 【0115】

また、CAC - OSまたはCAC - metal oxideは、導電性領域、および絶縁性領域を有する。導電性領域は、上述の導電性の機能を有し、絶縁性領域は、上述の絶縁性の機能を有する。また、材料中において、導電性領域と、絶縁性領域とは、ナノ粒子レベルで分離している場合がある。また、導電性領域と、絶縁性領域とは、それぞれ材料中に偏在する場合がある。また、導電性領域は、周辺がぼけてクラウド状に連結して観察される場合がある。

#### 【0116】

また、CAC - OSまたはCAC - metal oxideにおいて、導電性領域と、絶縁性領域とは、それぞれ0.5 nm以上10 nm以下、好ましくは0.5 nm以上3 nm以下のサイズで材料中に分散している場合がある。

#### 【0117】

また、CAC - OSまたはCAC - metal oxideは、異なるバンドギャップを有する成分により構成される。例えば、CAC - OSまたはCAC - metal oxideは、絶縁性領域に起因するワイドギャップを有する成分と、導電性領域に起因するナローギャップを有する成分と、により構成される。当該構成の場合、キャリアを流す際に、ナローギャップを有する成分において、主にキャリアが流れる。また、ナローギャップを有する成分が、ワイドギャップを有する成分に相補的に作用し、ナローギャップを有する成分に連動してワイドギャップを有する成分にもキャリアが流れる。このため、上記CAC - OSまたはCAC - metal oxideをトランジスタのチャネル形成領域に用いる場合、トランジスタのオン状態において高い電流駆動力、つまり大きなオン電流、および高い電界効果移動度を得ることができる。

#### 【0118】

すなわち、CAC - OSまたはCAC - metal oxideは、マトリックス複合材(matrix composite)、または金属マトリックス複合材(metal matrix composite)と呼称することもできる。

#### 【0119】

##### 〔金属酸化物の構造〕

酸化物半導体(金属酸化物)は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、例えば、CAAC - OS(c-axis aligned crystalline oxide semiconductor)、多結晶酸化物半導体、nc - OS(nanocrystalline oxide semiconductor)、擬似非晶質酸化物半導体(a-like OS:a morphous-like oxide semiconductor)および非晶質酸化物半導体などがある。

#### 【0120】

CAAC - OSは、c軸配向性を有し、かつa - b面方向において複数のナノ結晶が連結し、歪みを有した結晶構造となっている。なお、歪みとは、複数のナノ結晶が連結する領域において、格子配列の揃った領域と、別の格子配列の揃った領域との間で格子配列の向きが変化している箇所を指す。

#### 【0121】

ナノ結晶は、六角形を基本とするが、正六角形状とは限らず、非正六角形状である場合がある。また、歪みにおいて、五角形、および七角形などの格子配列を有する場合がある。なお、CAAC - OSにおいて、歪み近傍においても、明確な結晶粒界(グレインバウンダリーともいう。)を確認することは難しい。すなわち、格子配列の歪みによって、結晶粒界の形成が抑制されていることがわかる。これは、CAAC - OSが、a - b面方向において酸素原子の配列が稠密でないことや、金属元素が置換することで原子間の結合距離が変化することなどによって、歪みを許容することができるためである。

10

20

30

40

50

## 【0122】

また、C A A C - O S は、インジウム、および酸素を有する層（以下、I n 層）と、元素M、亜鉛、および酸素を有する層（以下、（M，Z n）層）とが積層した、層状の結晶構造（層状構造ともいう）を有する傾向がある。なお、インジウムと元素Mは、互いに置換可能であり、（M，Z n）層の元素Mがインジウムと置換した場合、（I n，M，Z n）層と表すこともできる。また、I n 層のインジウムが元素Mと置換した場合、（I n，M）層と表すこともできる。

## 【0123】

C A A C - O S は結晶性の高い金属酸化物である。一方、C A A C - O S は、明確な結晶粒界を確認することが難しいため、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。また、金属酸化物の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、C A A C - O S は不純物や欠陥（酸素欠損（V o : oxygen vacancy ともいう）など）の少ない金属酸化物ともいえる。したがって、C A A C - O S を有する金属酸化物は、物理的性質が安定する。そのため、C A A C - O S を有する金属酸化物は熱に強く、信頼性が高い。

10

## 【0124】

n c - O S は、微小な領域（例えば、1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、n c - O S は、異なるナノ結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、a - l i k e O S や非晶質酸化物半導体と区別が付かない場合がある。

20

## 【0125】

a - l i k e O S は、n c - O S と非晶質酸化物半導体との間の構造を有する金属酸化物である。a - l i k e O S は、鬆または低密度領域を有する。すなわち、a - l i k e O S は、n c - O S およびC A A C - O S と比べて、結晶性が低い。

## 【0126】

酸化物半導体（金属酸化物）は、多様な構造をとり、それぞれが異なる特性を有する。本発明の一態様の酸化物半導体は、非晶質酸化物半導体、多結晶酸化物半導体、a - l i k e O S、n c - O S、C A A C - O S のうち、二種以上を有していてもよい。

## 【0127】

30

## 〔金属酸化物を有するトランジスタ〕

続いて、上記金属酸化物をトランジスタのチャネル形成領域に用いる場合について説明する。

## 【0128】

なお、上記金属酸化物をトランジスタのチャネル形成領域に用いることで、高い電界効果移動度のトランジスタを実現することができる。また、信頼性の高いトランジスタを実現することができる。

## 【0129】

また、トランジスタには、キャリア密度の低い金属酸化物を用いることが好ましい。金属酸化物膜のキャリア密度を低くする場合においては、金属酸化物膜中の不純物濃度を低くし、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性または実質的に高純度真性という。例えば、金属酸化物は、キャリア密度が  $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上とすればよい。

40

## 【0130】

また、高純度真性または実質的に高純度真性である金属酸化物膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。

## 【0131】

また、金属酸化物のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い

50

金属酸化物をチャネル形成領域に有するトランジスタは、電気特性が不安定となる場合がある。

#### 【 0 1 3 2 】

したがって、トランジスタの電気特性を安定にするためには、金属酸化物中の不純物濃度を低減することが有効である。また、金属酸化物中の不純物濃度を低減するためには、近接する膜中の不純物濃度も低減することが好ましい。不純物としては、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

#### 【 0 1 3 3 】

##### [ 不純物 ]

ここで、金属酸化物中における各不純物の影響について説明する。

10

#### 【 0 1 3 4 】

金属酸化物において、第14族元素の一つであるシリコンや炭素が含まれると、金属酸化物において欠陥準位が形成される。このため、金属酸化物におけるシリコンや炭素の濃度と、金属酸化物との界面近傍のシリコンや炭素の濃度（二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）により得られる濃度）を、 $2 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{17}$  atoms / cm<sup>3</sup>以下とする。

#### 【 0 1 3 5 】

また、金属酸化物にアルカリ金属またはアルカリ土類金属が含まれると、欠陥準位を形成し、キャリアを生成する場合がある。したがって、アルカリ金属またはアルカリ土類金属が含まれている金属酸化物をチャネル形成領域に用いたトランジスタはノーマリーオン特性となりやすい。このため、金属酸化物中のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。具体的には、S I M S により得られる金属酸化物中のアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup>以下にする。

20

#### 【 0 1 3 6 】

また、金属酸化物において、窒素が含まれると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている金属酸化物をチャネル形成領域に用いたトランジスタはノーマリーオン特性となりやすい。したがって、当該金属酸化物において、チャネル形成領域の窒素はできる限り低減されていることが好ましい。例えば、金属酸化物中の窒素濃度は、S I M S において、 $5 \times 10^{19}$  atoms / cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下、より好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下とする。

30

#### 【 0 1 3 7 】

また、金属酸化物に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損を形成する場合がある。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することがある。従って、水素が含まれている金属酸化物を用いたトランジスタはノーマリーオン特性となりやすい。このため、金属酸化物中の水素はできる限り低減されていることが好ましい。具体的には、金属酸化物において、S I M S により得られる水素濃度を、 $1 \times 10^{20}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>未満とする。

40

#### 【 0 1 3 8 】

不純物が十分に低減された金属酸化物をトランジスタのチャネル形成領域に用いることで、トランジスタのオフ電流を低減し、安定した電気特性を付与することができる。

#### 【 0 1 3 9 】

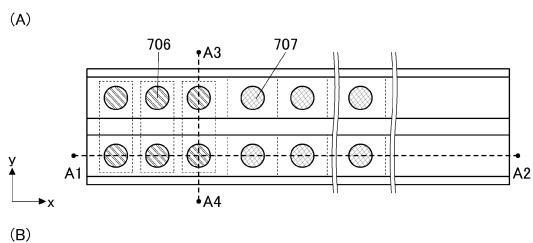

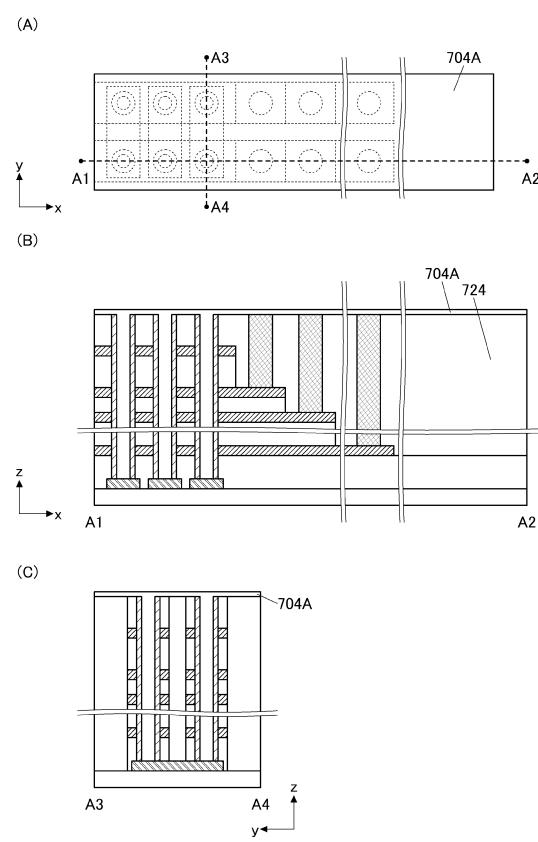

##### [ 作製方法例 ]

以下では、図1で例示した半導体装置700の作製方法の一例について、図5乃至図17を参照して説明する。なお、図5乃至図17の各図において、(A)はz軸方向から見

50

た上面図であり、(B)は(A)にA1-A2の一点鎖線で示す部位の断面図であり、(C)は(A)にA3-A4の一点鎖線で示す部位の断面図である。

#### 【0140】

まず、絶縁表面を有する基板720上に導電層706を形成し、導電層706を覆うよう、絶縁膜721を形成する(図5参照)。

#### 【0141】

導電層706は、まず導電層706となる導電膜を形成し、リソグラフィー法を用いて加工し、導電層706を形成することができる。ただし、導電層706、および絶縁膜721の形成方法はこれに限らない。基板720上に絶縁膜721を形成し、絶縁膜721の不要な部分を除去することで、溝や開口を形成し、該溝や該開口部に導電層706を埋め込むように形成してもよい。このような導電層の形成方法をダマシン法(シングルダマシン法、デュアルダマシン法)と呼ぶ場合がある。ダマシン法で形成された導電層706、および絶縁膜721上にさらに絶縁膜を形成することで、図5に示す構造を得ることができる。

10

#### 【0142】

導電層706や、絶縁膜721の形成は、スパッタリング法、化学気相成長(CVD: Chemical Vapor Deposition)法、分子線エピタキシー(MBE: Molecular Beam Epitaxy)法、パルスレーザ堆積(PLD: Pulsed Laser Deposition)法またはALD(Atomic Layer Deposition)法などを用いて行うことができる。

20

#### 【0143】

なお、CVD法は、プラズマを利用するプラズマCVD(PECVD: Plasma Enhanced CVD)法、熱を利用する熱CVD(TCVD: Thermal CVD)法、光を利用する光CVD(Photo CVD)法などに分類できる。さらに用いる原料ガスによって金属CVD(MCVD: Metal CVD)法、有機金属CVD(MOCVD: Metal Organic CVD)法に分けることができる。

20

#### 【0144】

プラズマCVD法は、比較的低温で高品質の膜が得られる。また、熱CVD法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子(トランジスタ、容量素子など)などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いない熱CVD法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、熱CVD法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

30

#### 【0145】

また、ALD法も、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。また、ALD法も、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

#### 【0146】

CVD法およびALD法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、ALD法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。ただし、ALD法は、比較的成膜速度が遅いため、成膜速度の速いCVD法などの他の成膜方法と組み合わせて用いることが好ましい場合もある。

40

#### 【0147】

CVD法およびALD法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、CVD法およびALD法では、原料ガスの流量比によって、任意

50

の組成の膜を成膜することができる。また、例えば、CVD法およびALD法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間の分、成膜に掛かる時間を短くすることができ、半導体装置の生産性を高めることができる場合もある。

#### 【0148】

なお、リソグラフィー法では、まず、フォトマスクを介してレジストを露光する。次に、露光された領域を、現像液を用いて除去または残存させてレジストマスクを形成する。次に、当該レジストマスクを介してエッチング処理することで導電膜、半導体膜または絶縁膜などを所望の形状に加工することができる。例えば、KrFエキシマレーザ光、ArFエキシマレーザ光、EUV (Extreme Ultraviolet) 光などを用いて、レジストを露光することでレジストマスクを形成すればよい。また、基板と投影レンズとの間に液体（例えば水）を満たして露光する、液浸技術を用いてもよい。また、前述した光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、マスクは不要となる。なお、レジストマスクの除去には、アッティングなどのドライエッティング処理を行う、ウェットエッティング処理を行う、ドライエッティング処理後にウェットエッティング処理を行う、またはウェットエッティング処理後にドライエッティング処理を行うことができる。

#### 【0149】

また、レジストマスクの代わりに絶縁膜や導電膜からなるハードマスクを用いてもよい。ハードマスクを用いる場合、導電膜上にハードマスク材料となる絶縁膜や導電膜を形成し、その上にレジストマスクを形成し、ハードマスク材料をエッチングすることで所望の形状のハードマスクを形成することができる。

#### 【0150】

該加工はドライエッティング法やウェットエッティング法を用いることができる。ドライエッティング法による加工は微細加工に適している。

#### 【0151】

ドライエッティング装置としては、平行平板型電極を有する容量結合型プラズマ（CCP : Capacitively Coupled Plasma）エッティング装置を用いることができる。平行平板型電極を有する容量結合型プラズマエッティング装置は、平行平板型電極の一方の電極に高周波電源を印加する構成でもよい。または平行平板型電極の一方の電極に複数の異なった高周波電源を印加する構成でもよい。または平行平板型電極それぞれに同じ周波数の高周波電源を印加する構成でもよい。または平行平板型電極それぞれに周波数の異なる高周波電源を印加する構成でもよい。または高密度プラズマ源を有するドライエッティング装置を用いることができる。高密度プラズマ源を有するドライエッティング装置は、例えば、誘導結合型プラズマ（ICP : Inductively Coupled Plasma）エッティング装置などを用いることができる。

#### 【0152】

導電膜のエッティングにハードマスクを用いる場合、当該エッティング処理は、ハードマスクの形成に用いたレジストマスクを除去してから行ってもよいし、レジストマスクを残したまま行ってもよい。後者の場合、エッティング中にレジストマスクが消失することがある。上記導電膜のエッティング後にハードマスクをエッティングにより除去してもよい。一方、ハードマスクの材料が後工程に影響が無い、あるいは後工程で利用できる場合、必ずしもハードマスクを除去する必要は無い。

#### 【0153】

導電層706となる導電膜は、スパッタリング法を用いて、金属元素を含む導電膜を形成することが好ましい。また、CVD法を用いて形成することもできる。

#### 【0154】

絶縁膜721の表面は、必要に応じて、平坦化処理が行われていることが好ましい。平坦化処理には、化学機械研磨（CMP）法やリフロー法を用いることができる。

10

20

30

40

50

**【 0 1 5 5 】**

続いて、絶縁膜 721 上に導電膜 701A、および絶縁膜 722A を交互に積層する。本実施の形態では、絶縁膜 721 上に導電膜 701A を形成し、導電膜 701A 上に絶縁膜 722A を形成する例を示しているが、形成の順序はこれに限らない。絶縁膜 721 上に絶縁膜 722A を形成し、絶縁膜 722A 上に導電膜 701A を形成してもよい。導電膜 701A、および絶縁膜 722A の形成には、CVD 法を用いることができる。また、スパッタリング法を用いてもよい。

**【 0 1 5 6 】**

また、本実施の形態では、導電膜 701A、および絶縁膜 722A の積層数は限られない。求められる半導体装置の性能に応じて、それぞれ 2 層以上形成することができる。例えば、導電膜 701A、および絶縁膜 722A は、それぞれ 16 層、32 層、64 層、または 128 層形成してもよいし、200 層以上形成してもよい。

10

**【 0 1 5 7 】**

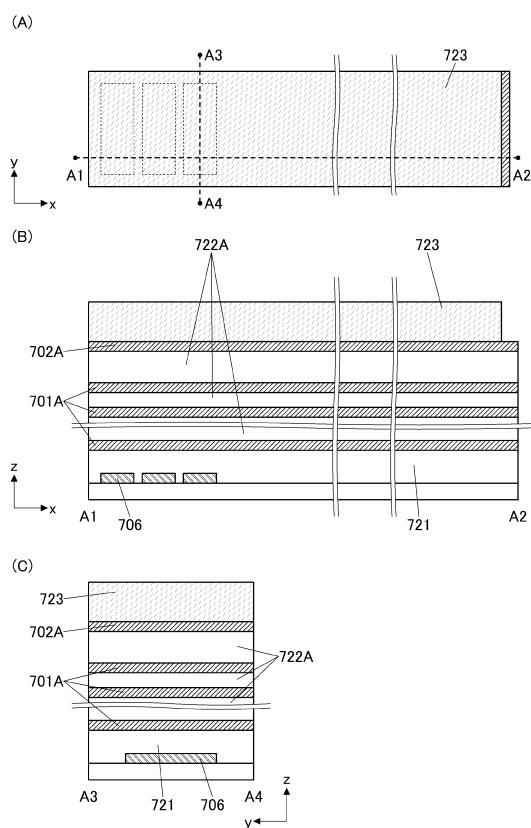

続いて、最も上側に位置する絶縁膜 722A 上に導電膜 702A を形成する。その後、導電膜 702A の上にマスク 723 を形成する（図 6 参照）。導電膜 702A は、導電膜 701A と同様な方法を用い、同様な材料を用いて形成することができる。なお、導電膜 702A は、導電膜 701A と同じ方法で形成してもよいし、異なる方法で形成してもよい。また、導電膜 702A は、導電膜 701A と同じ材料でもよいし、異なる材料でもよい。

**【 0 1 5 8 】**

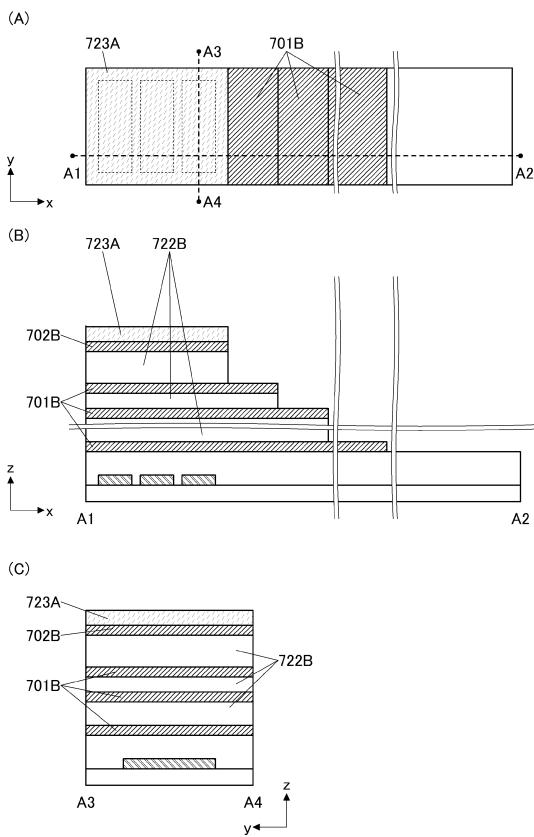

次に、導電膜 702A、導電膜 701A、および絶縁膜 722A を加工し、図 7 (B) に示すような階段状の導電膜 701B、導電膜 702B、および絶縁膜 722B を形成する。導電膜 702A、導電膜 701A、および絶縁膜 722A の加工において、導電膜 702A、導電膜 701A、および絶縁膜 722A のエッチングと、マスク 723 のスリミングを交互に行うことによって、階段状の導電膜 701B、導電膜 702B、および絶縁膜 722B を形成することができる。導電膜 702A、導電膜 701A、および絶縁膜 722A の加工により、マスク 723 は、幅、厚さ共に縮小し、マスク 723A となる（図 7 参照）。

20

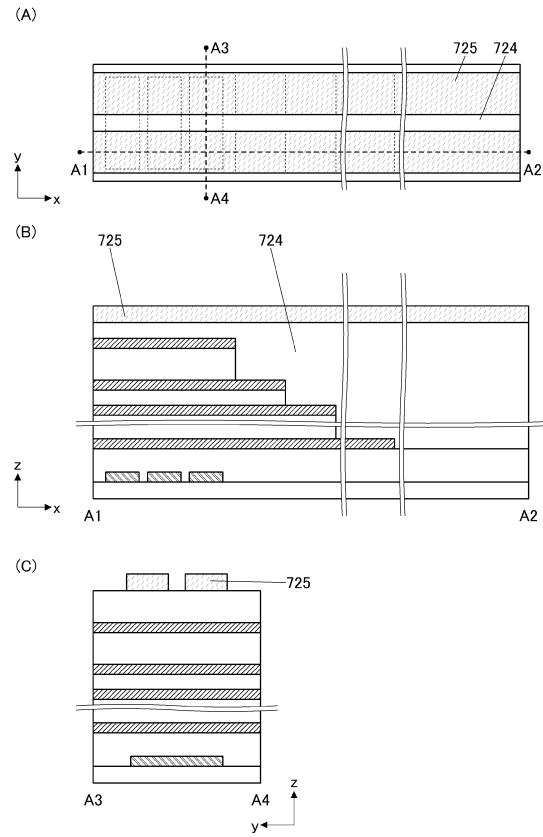

**【 0 1 5 9 】**

次に、マスク 723A を除去し、絶縁層 724 を形成する。絶縁層 724 は、CVD 法を用いて形成することができる。絶縁層 724 は、CMP 法や、リフロー法を用いて、平坦化処理されていることが好ましい。続いて、絶縁層 724 上にマスク 725 を形成する（図 8 参照）。平坦化された絶縁層 724 上にマスク 725 を形成すると、リソグラフィーの精度が向上するため好ましい。

30

**【 0 1 6 0 】**

次に、マスク 725 を用いて、絶縁層 724、導電膜 702B、導電膜 701B、絶縁膜 722B、および絶縁膜 721 を加工する（図 9 参照）。該加工により、メモリトランジスタのゲートとして機能し、ワード線と電気的に接続する導電層 701 と、選択トランジスタのゲートとして機能する導電層 702 が形成される。また、絶縁膜 722B は、該加工により絶縁層 722 となる。

40

**【 0 1 6 1 】**

その後、マスク 725 を除去する。次に、上記加工により除去された部分を埋め込むように絶縁層 726 を形成する。絶縁層 726 は、CVD 法や ALD 法を用いて形成することができる。特に、ALD 法を用いることで、アスペクト比の大きい溝や開口部に対しても、厚さの均一な膜を形成することができるため、好ましい。または、ALD 法と、CVD 法を組み合わせて絶縁層 726 を形成してもよい。絶縁層 726 は、CMP 法や、リフロー法を用いて、平坦化処理されていることが好ましい。CMP 法を用いて平坦化処理を行う場合、絶縁層 724 の表面が露出するまで絶縁層 726 を研磨してもよい。また、絶縁層 724 が消失しない程度に、絶縁層 724 と絶縁層 726 とを一緒に研磨してもよい。

**【 0 1 6 2 】**

50

次に、絶縁層 724 を、リソグラフィー法を用いて加工し、導電層 701 が露出するよう第 1 の開口を形成する(図 10 参照)。第 1 の開口は、階段状に形成された導電層 701 それぞれに対して形成する。また、図示しないが、導電層 702 が露出する開口も同時に形成することが好ましい。

#### 【0163】

次に、上記第 1 の開口に埋め込むように接続層 707 を形成する。接続層 707 は、CVD 法や ALD 法を用いて形成することができる。特に、熱 CVD 法や ALD 法を用いることで、アスペクト比の大きい溝や開口部に対しても、厚さの均一な膜を形成することができるため、好ましい。または、CVD と ALD 法とを組み合わせて接続層 707 を形成してもよい。また、接続層 707 は、複数の層からなる積層構造を有していてもよい。接続層 707 は、絶縁層 724 上、および第 1 の開口内部に接続層 707 となる導電膜を形成し、CMPなどを用いて不要な導電膜を除去することで、形成することができる。

10

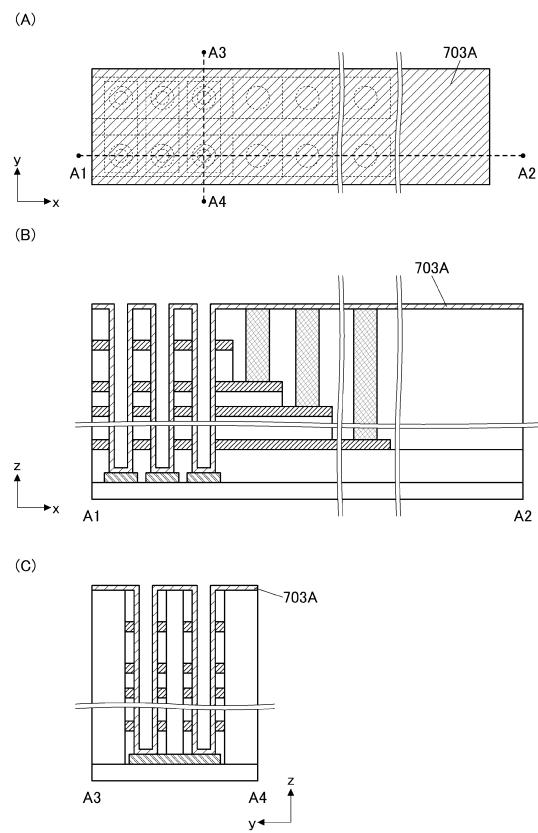

#### 【0164】

次に、絶縁層 724、導電層 702、導電層 701、絶縁層 722、および絶縁膜 721 を、リソグラフィー法を用いて加工し、導電層 706 が露出するよう第 2 の開口を形成する(図 11 参照)。

#### 【0165】

次に、絶縁層 724、および接続層 707 上、および第 2 の開口内部に、絶縁層 703 となる絶縁膜 703A を形成する(図 12 参照)。なお、図示しないが、絶縁膜 703A は、絶縁層 703a となる絶縁膜と、絶縁層 703b となる絶縁膜と、絶縁層 703c となる絶縁膜を順次積層して形成すればよい。絶縁膜 703A は、CVD 法や ALD 法を用いて形成することができる。特に、ALD 法を用いることで、アスペクト比の大きい溝や開口部に対しても、厚さの均一な膜を形成することができるため、好ましい。または、ALD 法と、CVD 法を組み合わせて絶縁膜 703A を形成してもよい。絶縁層 703a となる絶縁膜、絶縁層 703b となる絶縁膜、および絶縁層 703c となる絶縁膜は、同じ成膜装置で形成されてもよいし、異なる成膜装置で形成されてもよい。なお、絶縁層 703c が、絶縁層 703a より薄くなるように、絶縁層 703c となる絶縁膜は、絶縁層 703a となる絶縁膜よりも薄く形成することが好ましい。

20

#### 【0166】

次に、第 2 の開口底部に形成された絶縁膜 703A を除去し、絶縁層 703 を得る(図 13 参照)。絶縁膜 703A の除去には、異方性エッチングを用いることが好ましい。このとき、絶縁層 724、および接続層 707 上の絶縁膜 703A も除去されるため、絶縁層 703 は、第 2 の開口の側壁のみに設けられる。第 2 の開口底部の絶縁膜 703A を除去することで、再び導電層 706 が露出する。

30

#### 【0167】

ここで、図 13(D) に示すように、第 2 の開口上部に位置する絶縁層 703 のうち、絶縁層 703b、および絶縁層 703c を除去することが好ましい。図 13(D) は、図 13(B) における一点鎖線で囲まれた部分の拡大図である。まず第 2 の開口内部に後工程にて容易に除去可能な犠牲層 727 を埋め込むように形成し、第 2 の開口内部の所望の深さまで、エッチングなどにより除去する。該エッチングにより、露出した絶縁層 703c、および絶縁層 703b を順次除去することで、導電層 702 の水平方向(x-y 方向)に位置する絶縁層 703 を、絶縁層 703a のみとすることができる。この場合、選択トランジスタ SST、SDT のゲート絶縁膜は、絶縁層 703a により構成される。絶縁層 703c、および絶縁層 703b の除去後、犠牲層 727 を除去する。

40

#### 【0168】

次に、第 2 の開口内部、及び絶縁層 724 上に、酸化物膜 704A を形成する(図 14 参照)。酸化物膜 704A は、後に酸化物層 704 及び酸化物層 751 となる膜である。ここで、酸化物膜 704A を積層膜とする場合には、2 層または 3 層の酸化物膜を順次形成すればよい。このとき、トランジスタ 750 に適用される酸化物層 751 もまた、同様の積層構造とすることができます。

50

## 【0169】

酸化物膜704Aは、CVD法、ALD法、またはスパッタリング法を用いて形成することができる。特に、ALD法を用いることで、アスペクト比の大きい溝や開口部に対しても、厚さの均一な膜を形成することができるため、好ましい。または、ALD法、スパッタリング法、またはCVD法のうち2以上を組み合わせて酸化物膜704Aを形成してもよい。酸化物膜704Aを積層膜とする場合には、酸化物層704aとなる酸化物膜と酸化物層704bとなる酸化物膜、または酸化物層704aとなる酸化物膜、酸化物層704bとなる酸化物膜、および酸化物層704cとなる酸化物膜を順次成膜する。ここで、異なる酸化物膜は同じ成膜装置で形成されてもよいし、異なる成膜装置で形成されてもよい。

10

## 【0170】

また、酸化物膜704Aの内側に、絶縁層711を形成してもよい。絶縁層711は、CVD法、またはALD法等で形成することができる。絶縁層711は、メモリトランジスタや、該メモリトランジスタを有する半導体装置に必要な特性に合わせて、酸化物層704に酸素を供給する材料や、水素を供給する材料を用いることができる。

## 【0171】

ここで、酸化物膜704Aは、導電層706と接するように形成する。酸化物膜704Aと、導電層706が接することで、導電層706と酸化物膜704Aの界面には、導電層706が有する金属元素と、酸化物膜704Aの成分とを含む金属化合物層が形成される場合がある。該金属化合物が形成されることで、導電層706と、後の酸化物層704とのコンタクト抵抗が低減するため好ましい。また、酸化物膜704Aの底部近傍に含まれる酸素を、導電層706が吸収する場合がある。このとき、酸化物膜704Aの、導電層706との界面近傍の抵抗が低減し、導電層706と、後の酸化物層704とのコンタクト抵抗が低減するため好ましい。酸化物膜704Aと、導電層706が接する状態で、熱処理を行うことで、酸化物膜704Aの一部はより低抵抗化し、導電層706と、後の酸化物層704とのコンタクト抵抗がより低減する。熱処理は、窒素を含む雰囲気で、200以上500以下、このましくは、300以上400以下で行うことが好ましい。

20

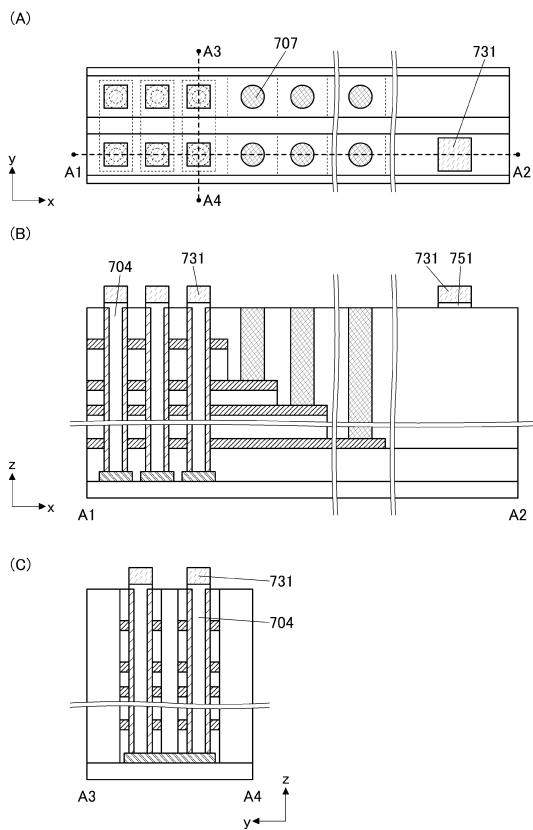

## 【0172】

続いて、酸化物膜704A上に、マスク731を形成し、当該マスク731を用いて酸化物膜704Aの不要な部分をエッチングする(図15参照)。これにより、柱状の酸化物層704と、薄膜状の酸化物層751とを同時に形成することができる。その後、マスク731を除去する。

30

## 【0173】

ここで、絶縁層711を形成した場合には、マスク731を除去した後、エッチングにより酸化物層751及び酸化物層704上の絶縁層711を除去することが好ましい。

## 【0174】

続いて、導電膜を成膜し、リソグラフィー法を用いて加工することにより、導電層705、導電層708、導電層753a、及び導電層753bを形成する(図16参照)。

40

## 【0175】

なお図示しないが、導電膜のエッティングの条件によっては、酸化物層751の上部が薄膜化する場合がある。また、導電膜のエッティングの条件によっては、絶縁層724の導電層705、導電層708、導電層753a、及び導電層753bに覆われない部分が薄膜化する場合がある。

## 【0176】

続いて、絶縁層754となる絶縁膜と、導電層752となる導電膜とを順次成膜し、リソグラフィー法を用いて加工することにより、絶縁層754と、導電層752を形成する(図17参照)。以上の工程により、トランジスタ750を形成することができる。

## 【0177】

なお、絶縁層754となる絶縁膜をエッティングせずに、導電層752となる導電膜のみ

50

をエッティングしてもよい。このとき、絶縁層 754 は導電層 705 や導電層 708 等を覆うように設けられる。

#### 【0178】

なお、図 4 (B) に示すトランジスタを形成する場合には、まず酸化物膜 704A と、導電層 753a 等となる導電膜とを積層した積層膜を形成し、酸化物層 751 となる領域等を残すように当該積層膜を加工する。その後、酸化物層 751 上のチャネル形成領域と重なる導電膜の一部をエッティングにより除去することで、形成することができる。これにより、より微細なトランジスタ 750 を作製することができる。

#### 【0179】

以降の工程では、回路構成に応じて図 4 (A) で例示した絶縁層 761、接続層 762、接続層 763、接続層 764a、接続層 764b、導電層 765、導電層 766a、及び導電層 766b 等を形成すればよい。またこれよりも上部に、さらに絶縁層と、接続層と、配線として機能する導電層と、を積層して形成してもよい。

#### 【0180】

以上のようにメモリセルアレイを作製することにより、各層ごとにメモリトランジスタを作製するためのパターン形成を行うことなく、複数の層のメモリトランジスタを一括で作製することができる。さらに、上記の方法でメモリセルアレイを作製する場合、メモリトランジスタの層数を増やしても、メモリトランジスタのパターン形成およびエッティング処理の工程数が増えない。このように、メモリセルアレイ作製の工程を短縮することができる、生産性の高い半導体装置を提供することができる。

#### 【0181】

さらに、メモリセルアレイの半導体層として機能する酸化物層と、トランジスタの半導体層として機能する酸化物層とを同時に形成することで、工程の増加を最小限に抑えつつ、メモリセルアレイの近傍にトランジスタを形成することができる。さらに、メモリセルアレイに接続する配線と、トランジスタのソース電極及びドレイン電極とを同時に形成することで、さらに工程を簡略化できる。

#### 【0182】

以上が半導体装置の作製方法についての説明である。

#### 【0183】

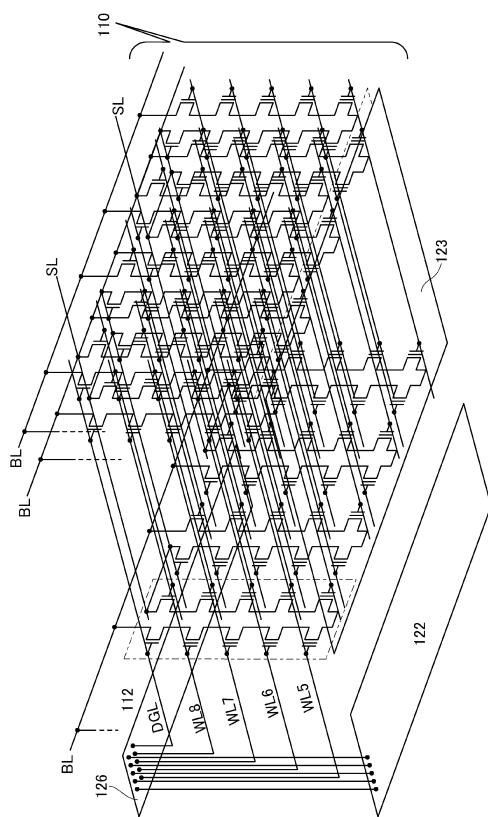

##### [記憶装置の構成例]

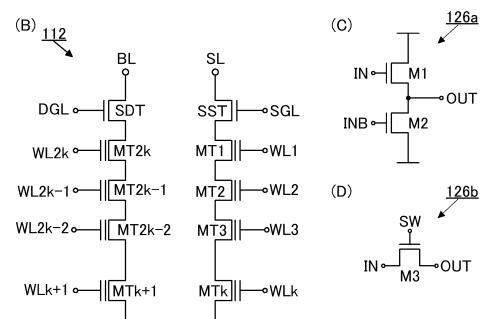

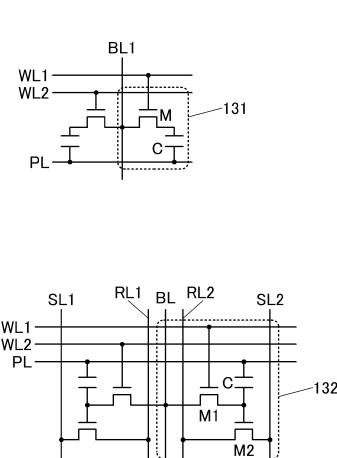

図 18 (A) に、3 次元構造の NAND 型不揮発性記憶装置 (3D NAND) の構成例を示す。図 18 (A) に示す記憶装置 100 は、制御回路 105、メモリセルアレイ 110、及び周辺回路を有する。

#### 【0184】

制御回路 105 は、記憶装置 100 全体を統括的に制御し、データの書き込み、データの読み出しを行う機能を有する。制御回路 105 は、外部からのコマンド信号を処理して、周辺回路の制御信号を生成する。図 18 (A) には、周辺回路として、行デコーダ 121、行ドライバ 122、センスアンプ 123、ソース線ドライバ 124、入出力回路 125、バッファ 126 等が設けられている。

#### 【0185】

メモリセルアレイ 110 は、複数のメモリストリング 112 を有する。図 18 (B) にメモリストリング 112 の回路構成例を示す。メモリストリング 112 において、ビット線 BL とソース線 SL 間に、選択トランジスタ SST、メモリトランジスタ MT1 乃至 MT2k (k は 1 以上の整数)、選択トランジスタ SDT が電気的に直列接続されている。

#### 【0186】

なお、メモリトランジスタ MT1 乃至 MT2k を区別しない場合、メモリトランジスタ MT と呼ぶ。その他の要素についても同様である。

#### 【0187】

選択トランジスタ SST、SDT、メモリトランジスタ MT1 乃至 MT2k は、それぞれ、前述した通り、チャネルが金属酸化物で形成されているトランジスタである。メモリ

10

20

30

40

50

トランジスタM Tは電荷蓄積層を備えており、不揮発性メモリセルを構成する。

【0188】

選択トランジスタS S T、S D Tのゲートは、それぞれ、選択ゲート線S G L、D G Lに電気的に接続されている。メモリトランジスタM T 1乃至M T 2 kのゲートは、それぞれ、ワード線W L 1乃至W L 2 kに電気的に接続されている。ビット線B Lは列方向に延在し、選択ゲート線S G L、D G L、ワード線W Lは行方向に延在する。

【0189】

入出力回路125は、メモリセルアレイ110への書き込みデータを一時的に保持こと、メモリセルアレイ110から読み出されたデータを一時的に保持すること等を行う。

【0190】

ソース線ドライバ124は、ソース線S Lを駆動する。

【0191】

ビット線B Lはセンスアンプ123に電気的に接続される。センスアンプ123は、データの読み出し時において、メモリストリング112からビット線B Lに読みだされた電圧を検知し、増幅する。また、データの書き込み時において、書き込みデータに応じた電圧をビット線B Lに入力する。

【0192】

行デコーダ121は、外部から入力されるアドレスデータをデコードし、アクセスされる行を選択する。行ドライバ122は、行デコーダ121のデコード結果に応じて、データの書き込み、読み出し、および消去に必要な電圧を、選択信号線D G L、S G L、ワード線W Lに入力する。

【0193】

バッファ126は、行デコーダ121とワード線W Lとの間に位置し、ワード線W Lに与える電圧を安定化させる機能を有する。また、スイッチング素子を有し、セレクタとしての機能を有していてもよい。

【0194】

図18(C)に、バッファ126に用いることのできるインバータ回路126aを示す。インバータ回路126aは、トランジスタM 1とトランジスタM 2が直列に接続された構成を有する。またトランジスタM 1のゲートは入力信号が入力される入力端子I Nが接続され、トランジスタM 2のゲートは上記入力信号を反転した信号が入力される入力信号I N Bが接続される。インバータ回路126aの出力端子O U Tには、例えばワード線W Lが接続される。

【0195】

図18(D)に、バッファ126に用いることのできるスイッチ回路126bを示す。スイッチ回路126bは、トランジスタM 3を有する。トランジスタM 3のゲートは入力端子S Wが接続され、ソースまたはドレインの一方は入力端子I Nが接続され、他方は出力端子O U Tが接続される。入力端子S Wに入力される選択信号により、入力端子I Nと出力端子O U Tの導通または非導通が制御される。

【0196】

上記で例示した、高耐圧のトランジスタ750は、例えばバッファ126、行ドライバ122、センスアンプ123、ソース線ドライバ124等が有するトランジスタに適用することができる。またバッファ126にトランジスタ750を適用する場合、例えばインバータ回路126aのトランジスタM 1及びトランジスタM 2の少なくとも一方や、スイッチ回路126bのトランジスタM 3に適用することができる。

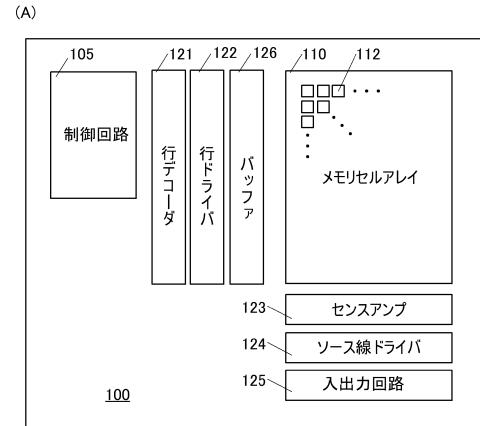

【0197】

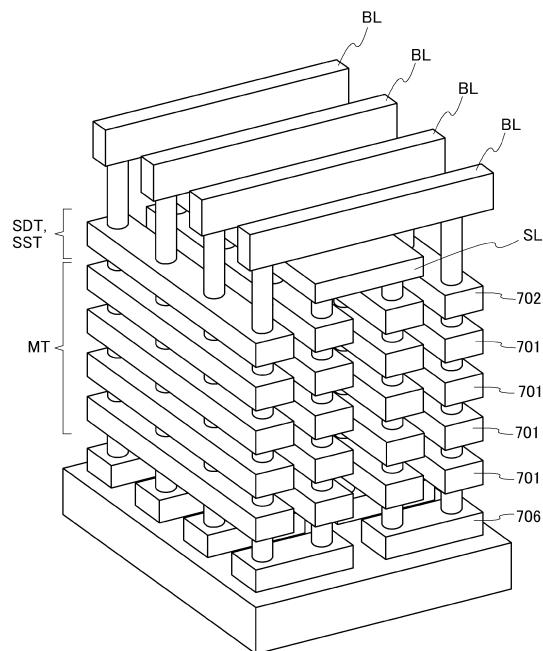

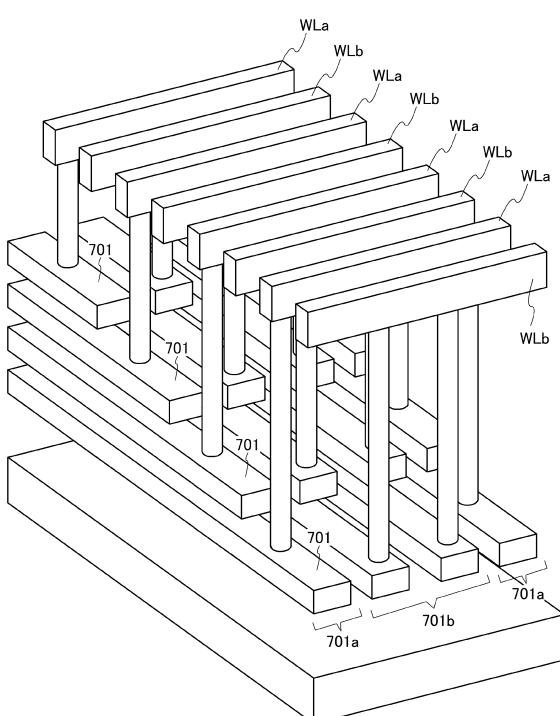

図19乃至図21に、メモリセルアレイ110の三次元積層構造例を示す。図19は、メモリセルアレイ110の三次元構造例を回路図で模式的に示した図である。図20は、メモリセルアレイ110の三次元構造例を示す斜視図である。図21は、ワード線W Lと導電層701の接続部の三次元構造例を示す斜視図である。

【0198】

10

20

30

40

50

図19に示すように、メモリセルアレイ110は、センスアンプ123が形成されている領域に積層して設けられている。これにより、記憶装置100のレイアウト面積を縮小することができる。各ワード線WLは、高耐圧のトランジスタを有するバッファ126と電気的に接続され、バッファ126はその下部に設けられた行ドライバ122に電気的に接続されている。なお、図19では行ドライバ122をバッファ126の下部に設けた例を示したが、行ドライバ122の一部または全部を高耐圧のトランジスタで構成し、バッファ126と並べて配置してもよい。

#### 【0199】

また図20及び図21に示すように、同じ段の導電層701でも、ピット線BL側の導電層701aはワード線WLaに接続され、ソース線SL側の導電層701bはワード線WLbに接続される。なお、図19乃至図21には、1のメモリストリング112あたり、8個のメモリトランジスタMT1乃至MT8を設けた例を示している。

10

#### 【0200】

ここで、上記ではメモリセルアレイ110として、電荷蓄積層を備えるメモリトランジスタが適用されたメモリストリング112を有する例を示した。このようなメモリトランジスタとしては、例えば、MONOS構造を有するトランジスタ、SONOS構造を有するトランジスタ、または、浮遊ゲート(Floating Gate)構造を有するトランジスタなどがある。

#### 【0201】

なお、メモリセルアレイ110に適用できるメモリセルはこれに限られない。図22(A)、(B)に、異なる構成を有するメモリセルの回路図の例を示す。

20

#### 【0202】

図22(A)には、2つのメモリセル131を示している。メモリセル131は、トランジスタMと、容量素子Cを有する。またメモリセル131には、ワード線WL1またはワード線WL2と、ピット線BLと、所定の電位が与えられる配線PLとが接続されている。

#### 【0203】

トランジスタMは、ゲートがワード線WL1またはワード線WL2と接続し、ソースまたはドレインの一方がピット線BLと接続し、ソースまたはドレインの他方が容量素子Cの一方の電極と接続する。容量素子Cは、他方の電極が配線PLと接続する。

30

#### 【0204】

メモリセル131は、容量素子Cに電荷を蓄積することで、データを保持することができる。

#### 【0205】

トランジスタMに、酸化物半導体が適用され、極めてオフ電流の小さいトランジスタを適用することで、シリコンが適用されたトランジスタを用いた場合に比べて、データ保持期間を極めて長いものとすることができます。そのため、リフレッシュ動作の頻度を低減できるため、極めて消費電力の低いメモリセルを実現できる。

#### 【0206】

図22(B)には、2つのメモリセル132を示している。メモリセル132は、トランジスタM1、トランジスタM2、及び容量素子Cを有する。またメモリセル132には、ワード線WL1またはワード線WL2と、ピット線BLと、選択信号線として機能する配線SL1または配線SL2と、読み出し信号線として機能する配線RL1または配線RL2と、所定の信号が与えられる配線PLが接続されている。

40

#### 【0207】

トランジスタM1は、ゲートがワード線WL1またはワード線WL2と接続し、ソースまたはドレインの一方がピット線BLと接続し、ソースまたはドレインの他方が容量素子Cの一方の電極、及びトランジスタM2のゲートと接続する。トランジスタM2は、ソースまたはドレインの一方が配線SL1または配線SL2と接続し、ソースまたはドレインの他方が配線RL1または配線RL2と接続する。容量素子Cは、他方の電極が配線PL

50

と接続する。

#### 【0208】

メモリセル132は、トランジスタM2のゲートが接続されるノードの電位を保持することで、データを保持することができる。また、トランジスタM2にかかる電位に応じて、トランジスタM2の導通状態が変化するため、配線SL1（または配線SL2）と配線RL1（または配線RL2）との間に流れる電流を検知することで、非破壊でデータを読み出すことができる。

#### 【0209】

トランジスタM1に、酸化物半導体が適用され、極めてオフ電流の小さいトランジスタを適用することで、シリコンが適用されたトランジスタを用いた場合に比べて、データ保持期間を極めて長いものとすることができます。またトランジスタM2には、単結晶シリコンを適用したトランジスタを適用することが好ましい。

10

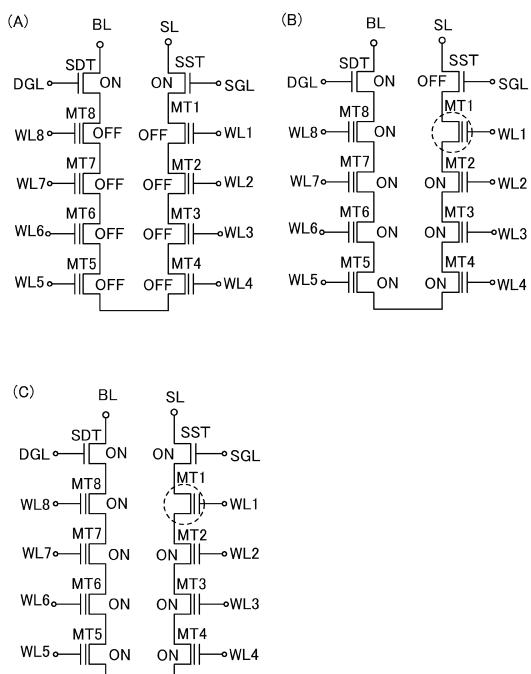

#### 【0210】

##### 〔記憶装置の回路動作について〕

次に、メモリストリング112へのデータの書き込みと読み出し動作について、図23(A)乃至(C)を用いて説明する。なお、以降において、ワード線WL1乃至ワード線WL2kを共有するメモリトランジスタMTのまとまりをページと呼ぶ。

#### 【0211】

図23(A)乃至(C)では、一例として、メモリストリング112がメモリトランジスタMT1乃至MT8を有する例を示しているが、メモリトランジスタMTの数はこれに限定されない。

20

#### 【0212】

##### 〔消去動作〕

メモリトランジスタMTにデータを書き込む場合は、書き込み動作の前にデータを消去しておくことが好ましい。なお、データを消去する動作をリセット動作ともいう場合がある。消去動作は、メモリストリング112（ブロックともいう）ごとに行う。例えば、データを消去したいブロックを選択し、図23(A)に示すように、ワード線WL1乃至WL8には低電位（メモリトランジスタMT1乃至MT8が非導通となる電位、例えば0V）を印加し、ソース線SLおよびピット線BLに消去電位VEを印加し、選択トランジスタSDTおよび選択トランジスタSSTを導通させることで行うことができる。リセット動作により、メモリトランジスタMT1乃至MT8のそれぞれの電荷蓄積層に蓄積された電子を引き抜くことができる。これにより、メモリトランジスタMT1乃至MT8は、データ“1”を保持している状態となる。

30

#### 【0213】

なお、データの書き換えを行わないメモリトランジスタMTのデータは、ブロックの消去動作の前に別のメモリ領域に格納しておくことが好ましい。

#### 【0214】

##### 〔書き込み動作〕

まず、データの書き込み動作について図23(B)を用いて説明する。

#### 【0215】

データの書き込み動作は、上述したページごとに行うことができる。まず、書き込みを行うページのワード線に書き込み電位（例えば15V）を印加し、書き込みを行わないページのワード線に正電位（トランジスタが導通する電位、例えば3V）を印加する。ここでは、図23(B)に示すように、まずワード線WL1に書き込み電位を印加し、ワード線WL2乃至WL8に正電位を印加する。そして、選択トランジスタSSTを非導通状態とし、選択トランジスタSDTを導通状態とする。そうすることで、ピット線BLの電位に応じたデータがメモリトランジスタMT1に書き込まれる。具体的には、ピット線BLの電位が低い電位（例えば0V）である場合、ワード線WL1に印加された書き込み電位との電位差が大きくなることによってメモリトランジスタMT1の電荷蓄積層に電子が注入される。また、ピット線BLの電位が正電位である場合、ワード線WL1に印加された

40

50

書き込み電位との電位差が小さくなることによって、メモリトランジスタM T 1 の電荷蓄積層には電子が注入されない。即ち、ビット線B L に低い電位が印加された場合にはメモリトランジスタM T 1 に データ“0”が書き込まれ、正電位が印加された場合にはメモリトランジスタM T 1 セルのデータは“1”的まとなる。

#### 【0216】

ここで、ビット線B L にメモリストリング112ごとに異なる電位を印加することで、ページごとのデータの書き込みを行うことができる。

#### 【0217】

なお、メモリトランジスタM T に多値のデータを書き込むこともできる。例えば、ビット線B Lなどの電位や、電位を印加する時間によってメモリトランジスタの電荷蓄積層に注入される電荷量を制御すればよい。

10

#### 【0218】

##### [読み出し動作]

次に、データの読み出し動作について図23(C)を用いて説明する。

#### 【0219】

データの読み出し動作も、ページごとに行うことができる。まず、読み出しを行うページのワード線に低い電位（例えば0V）を印加し、読み出しを行わないページのワード線に正電位（トランジスタが導通する電位、例えば3V）を印加する。ここでは、図23(C)に示すように、まずワード線W L 1 に低い電位を印加し、ワード線W L 2 乃至W L 8 に正電位を印加する。そして、選択トランジスタS S T および選択トランジスタS S T を導通状態とする。また、ビット線B L に読み出し電位（例えば1V）を印加し、ソース線S L に低い電位（例えば0V）を印加する。このとき、メモリトランジスタが“data”1であればメモリストリング112に電流が流れ、ビット線B L の電位が降下する。メモリトランジスタM T 1 が記憶するデータが“0”であれば、メモリストリング112に電流は流れず、ビット線B L の電位は変化しない。センスアンプ123は、ビット線B L の電位を検知し、増幅する。以上により、メモリストリング112のデータを読み出すことができる。

20

#### 【0220】

ここで、各メモリストリング112のデータをビット線B L に読み出すことで、ページ単位でデータを読み出すことができる。

30

#### 【0221】

以上が記憶装置の回路動作についての説明である。

#### 【0222】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【0223】

##### (実施の形態2)

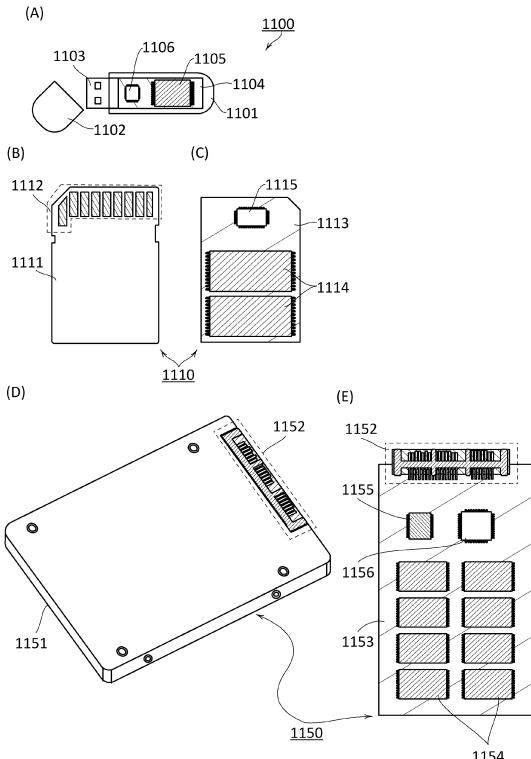

本実施の形態では、先の実施の形態に示す半導体装置を用いた記憶装置の応用例について説明する。先の実施の形態に示す半導体装置は、例えば、各種電子機器（例えば、情報端末、コンピュータ、スマートフォン、電子書籍端末、デジタルカメラ（ビデオカメラも含む）、録画再生装置、ナビゲーションシステムなど）の記憶装置に適用できる。なお、ここで、コンピュータとは、タブレット型のコンピュータや、ノート型のコンピュータや、デスクトップ型のコンピュータの他、サーバシステムのような大型のコンピュータを含むものである。または、先の実施の形態に示す半導体装置は、メモリカード（例えば、SDカード）、USBメモリ、SSD（ソリッド・ステート・ドライブ）等の各種のリムーバブル記憶装置に適用される。図24にリムーバブル記憶装置の幾つかの構成例を模式的に示す。例えば、先の実施の形態に示す半導体装置は、パッケージングされたメモリチップに加工され、様々なストレージ装置、リムーバブルメモリに用いられる。

40

#### 【0224】

図24(A)はUSBメモリの模式図である。USBメモリ1100は、筐体1101

50

、キャップ 1102、USB コネクタ 1103 および基板 1104 を有する。基板 1104 は、筐体 1101 に収納されている。例えば、基板 1104 には、メモリチップ 1105、コントローラチップ 1106 が取り付けられている。基板 1104 のメモリチップ 1105 などに先の実施の形態に示す半導体装置を組み込むことができる。

#### 【0225】

図 24 (B) は SD カードの外観の模式図であり、図 24 (C) は、SD カードの内部構造の模式図である。SD カード 1110 は、筐体 1111、コネクタ 1112 および基板 1113 を有する。基板 1113 は筐体 1111 に収納されている。例えば、基板 1113 には、メモリチップ 1114、コントローラチップ 1115 が取り付けられている。基板 1113 の裏面側にもメモリチップ 1114 を設けることで、SD カード 1110 の容量を増やすことができる。また、無線通信機能を備えた無線チップを基板 1113 に設けてもよい。これによって、ホスト装置と SD カード 1110 間の無線通信によって、メモリチップ 1114 のデータの読み出し、書き込みが可能となる。基板 1113 のメモリチップ 1114 などに先の実施の形態に示す半導体装置を組み込むことができる。

#### 【0226】

図 24 (D) は SSD の外観の模式図であり、図 24 (E) は、SSD の内部構造の模式図である。SSD 1150 は、筐体 1151、コネクタ 1152 および基板 1153 を有する。基板 1153 は筐体 1151 に収納されている。例えば、基板 1153 には、メモリチップ 1154、メモリチップ 1155、コントローラチップ 1156 が取り付けられている。メモリチップ 1155 はコントローラチップ 1156 のワークメモリであり、例えば DRAM チップを用いればよい。基板 1153 の裏面側にもメモリチップ 1154 を設けることで、SSD 1150 の容量を増やすことができる。基板 1153 のメモリチップ 1154 などに先の実施の形態に示す半導体装置を組み込むことができる。

#### 【0227】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【0228】

##### (実施の形態 3)

本実施の形態では、図 25 を用いて、上記実施の形態に示す半導体装置を適用した、AI システムについて説明を行う。

#### 【0229】

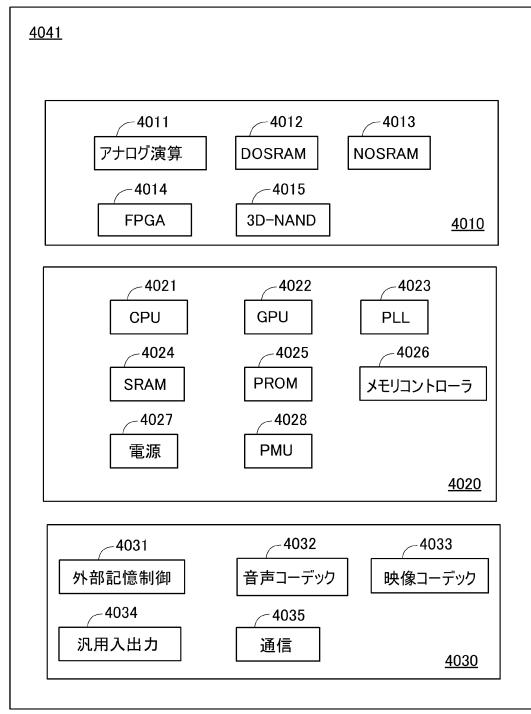

図 25 は AI システム 4041 の構成例を示すブロック図である。AI システム 4041 は、演算部 4010 と、制御部 4020 と、入出力部 4030 を有する。

#### 【0230】

演算部 4010 は、アナログ演算回路 4011 と、DOSRAM 4012 と、NOSRAM 4013 と、FPGA 4014 と、3D-NAND 4015 を有する。

#### 【0231】

ここで、DOSRAM (登録商標) とは、「Dynamic Oxide Semiconductor RAM」の略称であり、1T (トランジスタ) 1C (容量) 型のメモリセルを有する RAM を指す。

#### 【0232】

また、NOSRAM (登録商標) とは「Nonvolatile Oxide Semiconductor RAM」の略称であり、ゲインセル型 (2T型、3T型) のメモリセルを有する RAM を指す。DOSRAM、NOSRAM は、酸化物を半導体に用いたトランジスタ (以下、OSトランジスタと呼ぶ。) のオフ電流が低いことを利用したメモリである。なお、以下において、NOSRAM のように OSトランジスタを用いたメモリ装置を、OSメモリと呼ぶ場合がある。

#### 【0233】

制御部 4020 は、CPU (Central Processing Unit) 4021 と、GPU (Graphics Processing Unit) 4022 と、PLL

10

20

30

40

50

(Phase Locked Loop) 4023と、SRAM(Static Random Access Memory) 4024と、PROM(Programmable Read Only Memory) 4025と、メモリコントローラ 4026と、電源回路 4027と、PMU(Power Management Unit) 4028と、を有する。

#### 【0234】

入出力部 4030は、外部記憶制御回路 4031と、音声コーデック 4032と、映像コーデック 4033と、汎用入出力モジュール 4034と、通信モジュール 4035と、を有する。

#### 【0235】

演算部 4010は、ニューラルネットワークによる学習または推論を実行することができる。

#### 【0236】

アナログ演算回路 4011はA/D(アナログ/デジタル)変換回路、D/A(デジタル/アナログ)変換回路、および積和演算回路を有する。

#### 【0237】

アナログ演算回路 4011はOSトランジスタを用いて形成することが好ましい。OSトランジスタを用いたアナログ演算回路 4011は、アナログメモリを有し、学習または推論に必要な積和演算を、低消費電力で実行することが可能になる。

#### 【0238】

DOSRAM 4012は、OSトランジスタを用いて形成されたDRAMであり、DOSRAM 4012は、CPU 4021から送られてくるデジタルデータを一時的に格納するメモリである。DOSRAM 4012は、OSトランジスタを含むメモリセルと、Siトランジスタを含む読み出し回路部を有する。上記メモリセルと読み出し回路部は、積層された異なる層に設けることができるため、DOSRAM 4012は、全体の回路面積を小さくすることができる。

#### 【0239】

ニューラルネットワークを用いた計算は、入力データが1000を超えることがある。上記入力データをSRAMに格納する場合、SRAMは回路面積に制限があり、記憶容量が小さいため、上記入力データを小分けにして格納せざるを得ない。DOSRAM 4012は、限られた回路面積でも、メモリセルを高集積に配置することができ、SRAMに比べて記憶容量が大きい。そのため、DOSRAM 4012は、上記入力データを効率よく格納することができる。

#### 【0240】

NOSRAM 4013はOSトランジスタを用いた不揮発性メモリである。NOSRAM 4013は、フラッシュメモリや、ReRAM(Resistive Random Access Memory)、MRAM(Magnetoresistive Random Access Memory)などの他の不揮発性メモリと比べて、データを書き込む際の消費電力が小さい。また、フラッシュメモリやReRAMのように、データを書き込む際に素子が劣化することもなく、データの書き込み可能回数に制限が無い。

#### 【0241】

また、NOSRAM 4013は、1ビットの2値データの他に、2ビット以上の多値データを記憶することができる。NOSRAM 4013は多値データを記憶することで、1ビット当たりのメモリセル面積を小さくすることができる。

#### 【0242】

また、NOSRAM 4013は、デジタルデータの他にアナログデータを記憶することができる。そのため、アナログ演算回路 4011は、NOSRAM 4013をアナログメモリとして用いることもできる。NOSRAM 4013は、アナログデータのまま記憶することができるため、D/A変換回路やA/D変換回路が不要である。そのため、NOSRAM 4013は周辺回路の面積を小さくすることができる。なお、本明細書においてア

10

20

30

40

50

ナログデータとは、3ビット(8値)以上分解能を有するデータのことを指す。上述した多値データがアナログデータに含まれる場合もある。

#### 【0243】

ニューラルネットワークの計算に用いられるデータやパラメータは、一旦、NOSRA M4013に格納することができる。上記データやパラメータは、CPU4021を介して、AIシステム4041の外部に設けられたメモリに格納してもよいが、内部に設けられたNOSRAM4013の方が、より高速且つ低消費電力に上記データやパラメータを格納することができる。また、NOSRAM4013は、DOSRAM4012よりもビット線を長くすることができるので、記憶容量を大きくすることができる。

#### 【0244】

FPGA4014は、OSトランジスタを用いたFPGAである。AIシステム4041は、FPGA4014を用いることによって、ハードウェアで後述する、ディープニューラルネットワーク(DNN)、畳み込みニューラルネットワーク(CNN)、再帰型ニューラルネットワーク(RNN)、自己符号化器、深層ボルツマンマシン(DBM)、深層信念ネットワーク(DBN)などの、ニューラルネットワークの接続を構成することができる。上記のニューラルネットワークの接続をハードウェアで構成することで、より高速に実行することができる。

10

#### 【0245】

FPGA4014はOSトランジスタを有するFPGAである。OS-FPGAは、SRAMで構成されるFPGAよりもメモリの面積を小さくすることができる。そのため、コンテキスト切り替え機能を追加しても面積増加が少ない。また、OS-FPGAはブースティングによりデータやパラメータを高速に伝えることができる。

20

#### 【0246】

3D-NAND4015は酸化物半導体を用いた不揮発性メモリである。3D-NAND4015は、高集積化されたメモリであり、単位面積あたりの記憶容量の大きい。

#### 【0247】

また、3D-NAND4015は、1ビットの2値データの他に、2ビット以上の多値データを記憶することができる。3D-NAND4015は多値データを記憶することで、1ビット当たりのメモリセル面積を、さらに小さくすることができる。

#### 【0248】

また、3D-NAND4015として、例えば、上記実施の形態に示す半導体装置を用いることができる。これにより、メモリセルにおける占有面積を低減することができるのと、3D-NAND4015をさらに高集積化させることができる。よって、3D-NAND4015の単位面積当たりの記憶容量を増加させることができる。

30

#### 【0249】

AIシステム4041は、アナログ演算回路4011、DOSRAM4012、NOSRAM4013、およびFPGA4014を1つのダイ(チップ)の上に設けることができる。そのため、AIシステム4041は、高速且つ低消費電力に、ニューラルネットワークの計算を実行することができる。また、アナログ演算回路4011、DOSRAM4012、NOSRAM4013、およびFPGA4014は、同じ製造プロセスで作製することができる。そのため、AIシステム4041は、低コストで作製することができる。

40

#### 【0250】

なお、演算部4010は、DOSRAM4012、NOSRAM4013、およびFPGA4014を、全て有する必要はない。AIシステム4041が解決したい課題に応じて、DOSRAM4012、NOSRAM4013、およびFPGA4014の一または複数を、選択して設ければよい。

#### 【0251】

AIシステム4041は、解決したい課題に応じて、ディープニューラルネットワーク(DNN)、畳み込みニューラルネットワーク(CNN)、再帰型ニューラルネットワーク(RNN)、自己符号化器、深層ボルツマンマシン(DBM)、深層信念ネットワーク

50

(D B N)などの演算を実行することができる。P R O M 4 0 2 5は、これらの演算を実行するためのプログラムを保存することができる。また、これらプログラムの一部または全てを、N O S R A M 4 0 1 3または3 D - N A N D 4 0 1 5に保存してもよい。3 D - N A N D 4 0 1 5は、高集積化されたメモリであり、単位面積あたりの記憶容量が大きいので、大容量のプログラムを保存することができる。

#### 【0 2 5 2】

ライブラリとして存在する既存のプログラムは、G P Uの処理を前提としているものが多い。そのため、A Iシステム4 0 4 1はG P U 4 0 2 2を有することが好ましい。A Iシステム4 0 4 1は、学習と推論で用いられる積和演算のうち、律速となる積和演算を演算部4 0 1 0で実行し、それ以外の積和演算をG P U 4 0 2 2で実行することができる。10

そうすることで、学習と推論を高速に実行することができる。

#### 【0 2 5 3】

電源回路4 0 2 7は、論理回路用の低電圧電位を生成するだけではなく、アナログ演算のための電位生成も行う。電源回路4 0 2 7はO Sメモリを用いてもよい。電源回路4 0 2 7は、基準電位をO Sメモリに保存することで、消費電力を下げることができる。

#### 【0 2 5 4】

P M U 4 0 2 8は、A Iシステム4 0 4 1の電力供給を一時的にオフにする機能を有する。

#### 【0 2 5 5】

C P U 4 0 2 1およびG P U 4 0 2 2は、レジスタとしてO Sメモリを有することが好ましい。C P U 4 0 2 1およびG P U 4 0 2 2はO Sメモリを有することで、電力供給がオフになっても、O Sメモリ中にデータ(論理値)を保持し続けることができる。その結果、A Iシステム4 0 4 1は、電力を節約することができる。20

#### 【0 2 5 6】

P L L 4 0 2 3は、クロックを生成する機能を有する。A Iシステム4 0 4 1は、P L L 4 0 2 3が生成したクロックを基準に動作を行う。P L L 4 0 2 3はO Sメモリを有することが好ましい。P L L 4 0 2 3はO Sメモリを有することで、クロックの発振周期を制御するアナログ電位を保持することができる。

#### 【0 2 5 7】

A Iシステム4 0 4 1は、D R A Mなどの外部メモリにデータを保存してもよい。そのため、A Iシステム4 0 4 1は、外部のD R A Mとのインターフェースとして機能するメモリコントローラ4 0 2 6を有することが好ましい。また、メモリコントローラ4 0 2 6は、C P U 4 0 2 1またはG P U 4 0 2 2の近くに配置することが好ましい。そうすることで、データのやり取りを高速に行うことができる。30

#### 【0 2 5 8】

制御部4 0 2 0に示す回路の一部または全ては、演算部4 0 1 0と同じダイの上に形成することができる。そうすることで、A Iシステム4 0 4 1は、高速且つ低消費電力に、ニューラルネットワークの計算を実行することができる。

#### 【0 2 5 9】

ニューラルネットワークの計算に用いられるデータは外部記憶装置(H D D (H a r d D i s k D r i v e)、S S D (S o l i d S t a t e D r i v e)など)に保存される場合が多い。そのため、A Iシステム4 0 4 1は、外部記憶装置とのインターフェースとして機能する外部記憶制御回路4 0 3 1を有することが好ましい。40

#### 【0 2 6 0】

ニューラルネットワークを用いた学習と推論は、音声や映像を扱うことが多いので、A Iシステム4 0 4 1は音声コーデック4 0 3 2および映像コーデック4 0 3 3を有する。音声コーデック4 0 3 2は、音声データのエンコード(符号化)およびデコード(復号)を行い、映像コーデック4 0 3 3は、映像データのエンコードおよびデコードを行う。

#### 【0 2 6 1】

A Iシステム4 0 4 1は、外部センサから得られたデータを用いて学習または推論を行50

うことができる。そのため、A I システム 4 0 4 1 は汎用入出力モジュール 4 0 3 4 を有する。汎用入出力モジュール 4 0 3 4 は、例えば、U S B ( U n i v e r s a l S e r i a l B u s ) やI 2 C ( I n t e r - I n t e g r a t e d C i r c u i t ) などを含む。

#### 【 0 2 6 2 】

A I システム 4 0 4 1 は、インターネットを経由して得られたデータを用いて学習または推論を行うことができる。そのため、A I システム 4 0 4 1 は、通信モジュール 4 0 3 5 を有することが好ましい。

#### 【 0 2 6 3 】

アナログ演算回路 4 0 1 1 は、多値のフラッシュメモリをアナログメモリとして用いてもよい。しかし、フラッシュメモリは書き換え可能回数に制限がある。また、多値のフラッシュメモリは、エンベディッドで形成する（演算回路とメモリと同じダイの上に形成する）ことが非常に難しい。

#### 【 0 2 6 4 】

また、アナログ演算回路 4 0 1 1 は、R e R A M をアナログメモリとして用いてもよい。しかし、R e R A M は書き換え可能回数に制限があり、記憶精度の点でも問題がある。さらに、2 端子である素子でありため、データの書き込みと読み出しを分ける回路設計が複雑になる。

#### 【 0 2 6 5 】

また、アナログ演算回路 4 0 1 1 は、M R A M をアナログメモリとして用いてもよい。しかし、M R A M は抵抗変化率が低く、記憶精度の点で問題がある。

#### 【 0 2 6 6 】

以上を鑑み、アナログ演算回路 4 0 1 1 は、O S メモリをアナログメモリとして用いることが好ましい。

#### 【 0 2 6 7 】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【 0 2 6 8 】

##### ( 実施の形態 4 )

#### [ A I システムの応用例 ]

本実施の形態では、上記実施の形態に示すA I システムの応用例について図 2 6 を用いて説明を行う。

#### 【 0 2 6 9 】

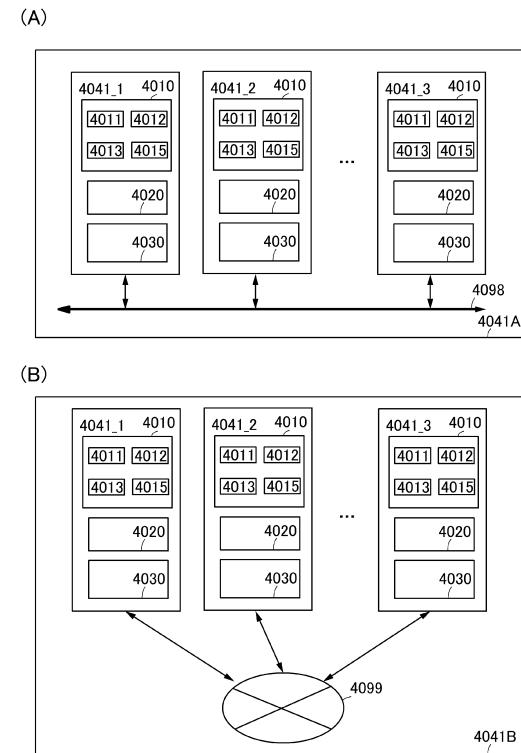

図 2 6 ( A ) は、図 2 5 で説明したA I システム 4 0 4 1 を並列に配置し、バス線を介してシステム間での信号の送受信を可能にした、A I システム 4 0 4 1 A である。

#### 【 0 2 7 0 】

図 2 6 ( A ) に図示するA I システム 4 0 4 1 A は、複数のA I システム 4 0 4 1 \_ 1 乃至A I システム 4 0 4 1 \_ n ( n は自然数 ) を有する。A I システム 4 0 4 1 \_ 1 乃至A I システム 4 0 4 1 \_ n は、バス線 4 0 9 8 を介して互いに接続されている。

#### 【 0 2 7 1 】

また図 2 6 ( B ) は、図 2 5 で説明したA I システム 4 0 4 1 を図 2 6 ( A ) と同様に並列に配置し、ネットワークを介してシステム間での信号の送受信を可能にした、A I システム 4 0 4 1 B である。

#### 【 0 2 7 2 】

図 2 6 ( B ) に図示するA I システム 4 0 4 1 B は、複数のA I システム 4 0 4 1 \_ 1 乃至A I システム 4 0 4 1 \_ n を有する。A I システム 4 0 4 1 \_ 1 乃至A I システム 4 0 4 1 \_ n は、ネットワーク 4 0 9 9 を介して互いに接続されている。

#### 【 0 2 7 3 】

ネットワーク 4 0 9 9 は、A I システム 4 0 4 1 \_ 1 乃至A I システム 4 0 4 1 \_ n のそれぞれに通信モジュールを設け、無線または有線による通信を行う構成とすればよい。

10

20

30

40

50

通信モジュールは、アンテナを介して通信を行うことができる。例えばWorld Wide Web (WWW) の基盤であるインターネット、イントラネット、エクストラネット、PAN (Personal Area Network)、LAN (Local Area Network)、CAN (Campus Area Network)、MAN (Metropolitan Area Network)、WAN (Wide Area Network)、GAN (Global Area Network) 等のコンピュータネットワークに各電子装置を接続させ、通信を行うことができる。無線通信を行う場合、通信プロトコル又は通信技術として、LTE (Long Term Evolution)、GSM (Global System for Mobile Communication: 登録商標)、EDGE (Enhanced Data Rates for GSM Evolution)、CDMA2000 (Code Division Multiple Access 2000)、W-CDMA (登録商標) などの通信規格、またはWi-Fi (登録商標)、Bluetooth (登録商標)、ZigBee (登録商標) 等のIEEEにより通信規格化された仕様を用いることができる。

#### 【0274】

図26(A)、(B)の構成とすることで、外部のセンサ等で得られたアナログ信号を別々のAIシステムで処理することができる。例えば、生体情報のように、脳波、脈拍、血圧、体温等といった情報を脳波センサ、脈波センサ、血圧センサ、温度センサといった各種センサで取得し、別々のAIシステムでアナログ信号を処理することができる。別々のAIシステムのそれぞれで信号の処理、または学習を行うことで一つのAIシステムあたりの情報処理量を少なくできる。そのため、より少ない演算量で信号の処理、または学習を行うことができる。その結果、認識精度を高めることができる。それぞれのAIシステムで得られた情報から、複雑に変化する生体情報の変化を瞬時に統合的に把握することができるといったことが期待できる。

#### 【0275】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【0276】

##### (実施の形態5)

本実施の形態は、上記実施の形態に示すAIシステムが組み込まれたICの一例を示す。

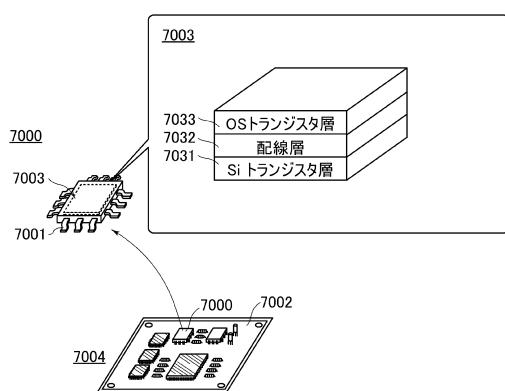

#### 【0277】

上記実施の形態に示すAIシステムは、CPU等のSiトランジスタでなるデジタル処理回路と、OSトランジスタを用いたアナログ演算回路、3D-NAND、OS-FPG AおよびDOSRAM、NOSRAM等のOSメモリを、1のダイに集積することができる。

#### 【0278】

図27に、AIシステムを組み込んだICの一例を示す。図27に示すAIシステムIC7000は、リード7001及び回路部7003を有する。AIシステムIC7000は、例えばプリント基板7002に実装される。このようなICチップが複数組み合わされて、それぞれがプリント基板7002上で電気的に接続されることで電子部品が実装された基板(実装基板7004)が完成する。回路部7003には、上記実施の形態で示した各種の回路が1のダイに設けられている。回路部7003は、先の実施の形態に示すように、積層構造をもち、Siトランジスタ層7031、配線層7032、OSトランジスタ層7033に大別される。OSトランジスタ層7033をSiトランジスタ層7031に積層して設けることができるため、AIシステムIC7000の小型化が容易である。

#### 【0279】

図27では、AIシステムIC7000のパッケージにQFP (Quad Flat Pack) を適用しているが、パッケージの態様はこれに限定されない。

#### 【0280】

CPU等のデジタル処理回路と、OSトランジスタを用いたアナログ演算回路、3D-

10

20

30

40

50

NAND、OS-FPGAおよびDOSRAM、NOSRAM等のOSメモリは、全て、Siトランジスタ層7031、配線層7032およびOSTランジスタ層7033に形成することができる。すなわち、上記AIシステムを構成する素子は、同一の製造プロセスで形成することができる。そのため、本実施の形態に示すICは、構成する素子が増えても製造プロセスを増やす必要がなく、上記AIシステムを低コストで組み込むことができる。

#### 【0281】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【0282】

##### (実施の形態6)

###### [電子機器]

本発明の一態様に係る半導体装置は、様々な電子機器に用いることができる。図28および図29に、本発明の一態様に係る半導体装置を用いた電子機器の具体例を示す。

#### 【0283】

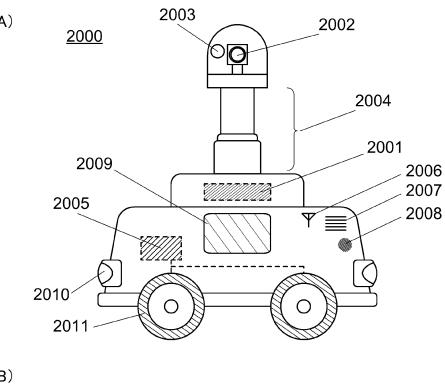

図28(A)に示すロボット2000は、演算装置2001、センサ2002、ライト2003、リフト2004、駆動部2005、移動機構2011を備えており、移動しながら静止画や動画を撮影することができる。このようなロボットは、警備システムや、監視システムとして用いることができる。

#### 【0284】

ロボット2000は、さらに、通信手段2006、スピーカ2007、マイクロフォン2008、表示部2009、発光部2010などを備えていてもよい。

#### 【0285】

演算装置2001には、本発明の一態様に係る半導体装置を用いることができる。また、演算装置2001には、本発明の一態様に係るAIシステムが組み込まれたICを用いることができる。センサ2002は、ロボット2000の周囲を撮影する、カメラとしての機能を有する。ライト2003は、センサ2002でロボット2000の周囲を撮影する際のライトとして用いることができる。なお、センサ2002で、静止画を撮影する際には、ライト2003は、フラッシュライトとして機能することが好ましい。センサ2002は、リフト2004を介して、ロボット本体と接続されている。センサ2002の高さは、リフト2004により調整することができる。リフト2004は、伸縮式であることが好ましい。また、リフト2004は、複数のブームにより構成された折り畳み式のものでもよい。また、ロボット2000には、駆動部2005と、駆動部2005に接続された移動機構2011が設けられているため、センサ2002による撮像範囲、すなわち監視範囲が広がり、好ましい。

#### 【0286】

通信手段2006は、センサ2002により撮像された情報を管理者や、管理者が所有するサーバへ送信することができる。また、センサ2002により撮像された情報を演算装置2001にて解析し、犯罪、事故、火災などの非常事態と判断された場合は、警備会社、警察、消防、医療機関、土地や建物のオーナーへ連絡することができる。スピーカ2007は、犯罪者への警告、怪我人や急病人への問い合わせ、避難の誘導など、ロボット周囲に情報の発信を行うことができる。マイクロフォン2008は、ロボット2000周囲の音声の取得に用いることができる。また、通信手段2006、およびスピーカ2007と合わせて用いることで、ロボット2000は電話としての機能を有することができる。ロボット2000周囲にいる人は、管理者や任意の人と会話することができる。表示部2009は、任意の情報を表示することができる。非常時の場合は、災害情報や避難経路を表示することができる。また、通信手段2006、スピーカ2007、およびマイクロフォン2008と合わせて用いることで、ロボット2000はテレビ電話としての機能を有することができる。ロボット2000周囲にいる人は、管理者や任意の人と表示部2009を見ながら会話することができる。

10

20

30

40

50

**【0287】**

発光部2010は、ロボット2000の進行方向や停止状態を文字や光で示すことができる。また、非常事態を示してもよい。

**【0288】**

図28(B)は、ロボット2000の構成を示すブロック図である。演算装置2001は、センサ2002により得られた映像などの情報から、ライト2003の点灯や消灯、明るさの調整を行う。また、リフト2004の高さの調整、あるいは、駆動部2005の制御を行い、ロボット2000や、センサ2002の位置合わせを行う。また、駆動部2005の動作状況を、発光部2010を用いて示すことができる。また、通信手段2006を用いて、センサ2002やマイクロフォン2008から得られたロボット2000の周囲の情報を管理者、または管理者が所有するサーバに送信することができる。また、演算装置2001や、管理者の判断により、スピーカ2007や表示部2009を用いて、ロボット2000の周囲に情報を発信することができる。10

**【0289】**

センサ2002に用いるセンサとして、周囲が暗くても撮像が可能なセンサを用いる場合は、ライト2003は設けなくてもよい。このようなセンサとして、受光部にセレン(Se)を用いたイメージセンサを用いることができる。

**【0290】**

このようなロボット2000は、商業施設や、オフィスの警備に用いることができる。センサ2002やマイクロフォン2008から得られた情報は、演算装置2001やサーバに保存される。保存された情報は、AIシステムにより解析され、物品の紛失や破損、不審者の侵入、火災などの災害などの異常の有無を判断する。情報の解析には、ディープラーニングを用いてもよい。異常が発生したと判断した場合、ロボット2000は、管理者への連絡および周囲への情報発信を行い、周囲の状況を記録する。20

**【0291】**

また、ロボット2000は、農作物の生育状況の監視に用いてもよい。田んぼや畑に設置されたロボット2000は、センサ2002により、農作物の葉、あるいは実の形、大きさ、色を監視し、病気になつてないか、害虫の付着が無いかを判断する。ロボット2000には、移動機構2011が設けられているため、広範囲の農作物の生育状況を監視することができる。また、ロボット2000には、リフト2004が設けられているため、農作物の種類や、生育状況によらず、任意の高さの葉や実を監視することができる。監視結果は、通信手段2006を用いて生産者に送られ、生産者は、農作物に必要な肥料や農薬の種類、量、散布時期を判断することができる。また、演算装置2001を用いて、監視結果を、AIシステムにより解析し、農作物に必要な、肥料や農薬の種類、量、散布時期を判断して、生産者に通知してもよい。監視結果の解析には、ディープラーニングを用いてもよい。30

**【0292】**

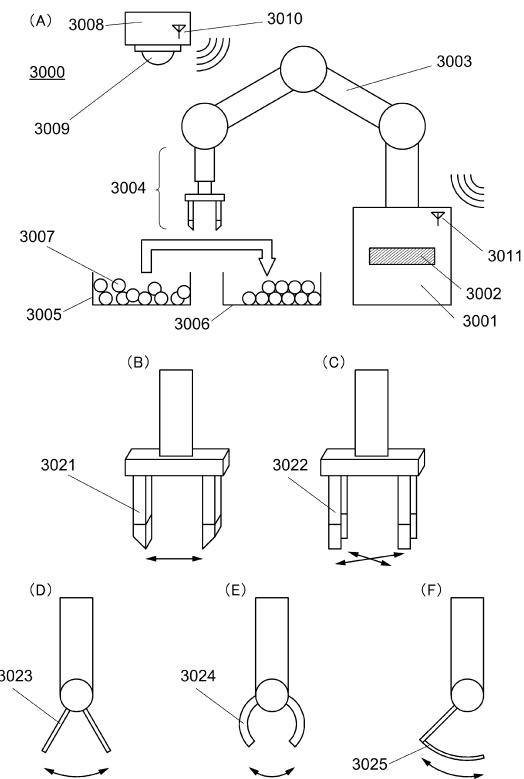

図29(A)は、ロボット3001を用いた、仕分けシステム3000を示す。ロボット3001は、演算装置3002、ブーム3003、およびアーム3004を備えている。また、ロボット3001は有線、または無線の通信手段3011を備えていてもよい。また、仕分けシステム3000は、センサ3009を有する筐体3008を備えている。筐体3008は、通信手段3010を有している。筐体3008は、仕分けシステム3000、または仕分け作業エリアの天井、壁、梁(いずれも図示せず)に設けられる。また、筐体3008は、ロボット3001に設けられていてもよい。例えば、ブーム3003、またはアーム3004に設けられていてもよい。筐体3008がロボット3001に設けられている場合は、センサ3009により得られた情報は、通信手段3010、および通信手段3011を介さず、演算装置3002に送られ、処理されてもよい。40

**【0293】**

ブーム3003は、可動式となっており、アーム3004を所望の位置に配置することができる。また、アーム3004は伸縮式としてもよい。所望の物品3007上に配置さ50

れたアームを伸ばし、所望の物品 3007 を掴み、アーム 3004 を縮めた後、ブーム 3003 によりアーム 3004 を移動してもよい。

**【0294】**

仕分けシステム 3000 は、容器 3005 内の物品 3007 を容器 3006 に移動させることができる。容器 3005 と容器 3006 は、同一形状でも良いし、異なる形状でもよい。また、一つの容器 3005 に入れられた複数の物品 3007 を複数の容器 3006 に振り分けて移動してもよい。

**【0295】**

容器 3005、および容器 3006 として、コンテナ、段ボール箱、商品を梱包する箱、ケース、フィルム、または袋、食品保管用のバット、弁当箱などが用いられる。また、容器 3005、および容器 3006 の少なくとも一方は、鍋やフライパンなどの調理器具でもよい。

10

**【0296】**

演算装置 3002 には、本発明の一態様に係る半導体装置を用いることができる。また、演算装置 3002 には、本発明の一態様に係る AI システムが組み込まれた IC を用いることができる。

**【0297】**

センサ 3009 は、容器 3005 の位置、容器 3006 の位置、容器 3005 内、および容器 3005 内の物品 3007 の状態を読み取り、通信手段 3010 を用いて演算装置 3002 に情報を送信する。情報の送信は無線または、有線で行う。また、通信手段 3010 を用いずに、有線にて情報を送信してもよい。演算装置 3002 は、送信された情報の解析を行う。ここで、物品 3007 の状態とは、形、数、物品 3007 同士の重なりなどのことを指す。演算装置 3002 は、センサ 3009 からの情報をもとに解析を行い、物品 3007 の詳細情報を導出する。演算装置 3002、またはロボット 3001 と通信可能なサーバに保存されたデータと比較し、物品 3007 の三次元形状や、堅さ（柔らかさ）を導出する。また、物品 3007 の三次元形状や堅さ（柔らかさ）から、アーム 3004 の形状を変えることができる。

20

**【0298】**

物品 3007 の詳細情報を導出するには、AI システムを用いた解析を利用することができます。情報の解析には、ディープラーニングを用いてもよい。

30

**【0299】**

図 29 (B) は、一対の板 3021 が水平方向に移動し、物品 3007 を挟むことができるアームである。一対の板 3021 が中心に向かって水平方向に移動することで、物品 3007 を挟むことができる。このようなアームは、物品 3007 を面で捉えることができ、立方体や直方体など、柱状の形を有する物品 3007 を掴むのに適している。図 29 (C) は、複数のバー 3022 が水平方向に移動し、物品 3007 を挟むことができるアームである。複数のバー 3022 が中心に向かって水平方向に移動することで、物品 3007 を挟むことができる。このようなアームは、物品 3007 を点で捉えることができ、球状の形を有する物品 3007、または物品 3007 の形が一定でない場合、すなわち不定型な物品 3007 を掴むに適している。なお、図 29 (C) では、バー 3022 の数を 4 本としたが、本実施の形態はこれに限らない。バー 3022 は 3 本でもよいし、5 本以上でも良い。図 29 (D) は、一対の板 3023 が、共通の軸を中心に、お互いが近づくように回転することで物品 3007 を挟むことができるアームである。このようなアームは、物品 3007 を面で捉えることができ、紙やフィルムなど、薄膜状の形を有する物品 3007 を掴むのに適している。図 29 (E) は、一対のかぎ状の板 3024 が、共通の軸を中心に、お互いの先端が近づくように回転することで物品 3007 を挟むことができるアームである。このようなアームは、物品 3007 を点、または線で捉えることができ、紙やフィルムなど、薄膜状の形を有する物品 3007 や、より小さい粒状の形を有する物品 3007 を掴むのに適している。また、図 29 (F) に示すように、アームの先端にヘラ 3025 を取り付け、より小さい粒状の形を有する物品 3007 をすくってもよい。

40

50

**【0300】**

図29(A)乃至図29(F)に示すアームは、一例であり、本発明の一態様はこれらの形状に限らない。また、各アームの用途の説明も一例であり、本発明の一態様はこれらの記載に限らない。

**【0301】**

ロボット3001は、演算装置3002からの信号に基づき、ブーム3003を動かし、アーム3004を、容器3005内の所望の物品3007上に移動する。伸縮式のアーム3004の場合、アーム3004を伸ばし、アーム3004の先端を物品3007の高さまで降ろす。アームの先端を動かし、所望の物品3007を掴む。物品3007を掴んだまま、アームを縮める。再びブーム3003を動かし、アーム3004を、容器3006の所望の位置に移動する。このとき、容器3006に対する物品3007の角度を調整する為、アーム3004を回転してもよい。アーム3004を伸ばし、物品3007を容器3006に配置し、アーム3004は、物品3007を放す。以上の操作を繰り返し行い、ロボット3001は、物品3007を容器3005から容器3006に移動させることができる。

10

**【0302】**

容器3005、および容器3006の位置情報、および物品3007の状態をA Iシステムを用いて解析しているため、物品3007の形状や堅さによらず、確実に物品3007を移動することができる。物品3007の例としては、立方体、または直方体の箱、または任意の形状の箱やケースに詰められた物品だけでなく、卵、ハンバーグやコロッケなど、成形された加工食品、ジャガイモやトマトなど、不定形な野菜などの食品、ネジやナットなどの機械部品、紙やフィルムなどの薄膜などが挙げられる。本実施の形態に示した仕分けシステム3000は、物品3007の形状や堅さを考慮してアームの形状を変えることができるため、上記に例示した物品3007を、形状や堅さによらず、容器3005から容器3006に移動させることができる。

20

**【0303】**

例えば、本発明の一態様の半導体装置を用いた記憶装置は、上述した電子機器の制御情報や、制御プログラムなどを長期間保持することができる。本発明の一態様に係る半導体装置を用いることで、信頼性の高い電子機器を実現することができる。

30

**【0304】**

また、例えば、上述した電子機器の演算装置などに、上記A Iシステムが組み込まれたI Cを用いることができる。これにより、本実施の形態に示す電子機器は、A Iシステムによって、状況に応じた的確な動作を、低消費電力で行うことができる。

**【0305】**

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

**【符号の説明】****【0306】**

- |       |          |    |

|-------|----------|----|

| 1 0 0 | 記憶装置     | 40 |

| 1 0 5 | 制御回路     |    |

| 1 1 0 | メモリセルアレイ |    |

| 1 1 2 | メモリストリング |    |

| 1 2 1 | 行デコーダ    |    |

| 1 2 2 | 行ドライバ    |    |

| 1 2 3 | センスアンプ   |    |

| 1 2 4 | ソース線ドライバ |    |

| 1 2 5 | 入出力回路    |    |

| 1 2 6 | バッファ     |    |

- |         |         |

|---------|---------|

| 1 2 6 a | インバータ回路 |

| 1 2 6 b | スイッチ回路  |

50

|           |           |    |

|-----------|-----------|----|

| 1 3 1     | メモリセル     |    |

| 1 3 2     | メモリセル     |    |

| 7 0 0     | 半導体装置     |    |

| 7 0 0 A   | 記憶装置      |    |

| 7 0 0 D   | 回路部       |    |

| 7 0 0 M   | メモリセルアレイ  |    |

| 7 0 1     | 導電層       |    |

| 7 0 1 _ m | 導電層       |    |

| 7 0 1 _ 1 | 導電層       |    |

| 7 0 1 _ 6 | 導電層       | 10 |

| 7 0 1 a   | 導電層       |    |

| 7 0 1 A   | 導電膜       |    |

| 7 0 1 b   | 導電層       |    |

| 7 0 1 B   | 導電膜       |    |

| 7 0 2     | 導電層       |    |

| 7 0 2 A   | 導電膜       |    |

| 7 0 2 b   | 絶縁層       |    |

| 7 0 2 B   | 導電膜       |    |

| 7 0 3     | 絶縁層       |    |

| 7 0 3 _ 1 | 絶縁層       | 20 |

| 7 0 3 _ 3 | 絶縁層       |    |

| 7 0 3 a   | 絶縁層       |    |

| 7 0 3 A   | 絶縁膜       |    |

| 7 0 3 b   | 絶縁層       |    |

| 7 0 3 c   | 絶縁層       |    |

| 7 0 4     | 酸化物層      |    |

| 7 0 4 _ 1 | 酸化物層      |    |

| 7 0 4 _ 3 | 酸化物層      |    |

| 7 0 4 a   | 酸化物層      |    |

| 7 0 4 A   | 酸化物膜      | 30 |

| 7 0 4 b   | 酸化物層      |    |

| 7 0 4 c   | 酸化物層      |    |

| 7 0 5     | 導電層       |    |

| 7 0 5 _ 1 | 導電層       |    |

| 7 0 5 _ 3 | 導電層       |    |

| 7 0 6     | 導電層       |    |

| 7 0 6 _ 1 | 導電層       |    |

| 7 0 6 _ 3 | 導電層       |    |

| 7 0 7     | 接続層       |    |

| 7 0 7 _ m | 接続層       | 40 |

| 7 0 7 _ 1 | 接続層       |    |

| 7 0 8     | 導電層       |    |

| 7 0 8 _ m | 導電層       |    |

| 7 0 8 _ 1 | 導電層       |    |

| 7 1 0     | メモリトランジスタ |    |

| 7 1 1     | 絶縁層       |    |

| 7 2 0     | 基板        |    |

| 7 2 1     | 絶縁膜       |    |

| 7 2 2     | 絶縁層       |    |

| 7 2 2 A   | 絶縁膜       | 50 |

|         |            |    |

|---------|------------|----|

| 7 2 2 B | 絶縁膜        |    |

| 7 2 3   | マスク        |    |

| 7 2 3 A | マスク        |    |

| 7 2 4   | 絶縁層        |    |

| 7 2 5   | マスク        |    |

| 7 2 6   | 絶縁層        |    |

| 7 2 7   | 犠牲層        |    |

| 7 3 1   | マスク        |    |

| 7 5 0   | トランジスタ     | 10 |

| 7 5 1   | 酸化物層       |    |

| 7 5 1 a | 酸化物層       |    |

| 7 5 2   | 導電層        |    |

| 7 5 3 a | 導電層        |    |

| 7 5 3 b | 導電層        |    |

| 7 5 4   | 絶縁層        |    |

| 7 6 1   | 絶縁層        |    |

| 7 6 2   | 接続層        |    |

| 7 6 3   | 接続層        |    |

| 7 6 4 a | 接続層        |    |

| 7 6 4 b | 接続層        | 20 |

| 7 6 5   | 導電層        |    |

| 7 6 6 a | 導電層        |    |

| 7 6 6 b | 導電層        |    |

| 1 1 0 0 | U S B メモリ  |    |

| 1 1 0 1 | 筐体         |    |

| 1 1 0 2 | キヤップ       |    |

| 1 1 0 3 | U S B コネクタ |    |

| 1 1 0 4 | 基板         |    |

| 1 1 0 5 | メモリチップ     |    |

| 1 1 0 6 | コントローラチップ  | 30 |

| 1 1 1 0 | S D カード    |    |

| 1 1 1 1 | 筐体         |    |

| 1 1 1 2 | コネクタ       |    |

| 1 1 1 3 | 基板         |    |

| 1 1 1 4 | メモリチップ     |    |

| 1 1 1 5 | コントローラチップ  |    |

| 1 1 5 0 | S S D      |    |

| 1 1 5 1 | 筐体         |    |

| 1 1 5 2 | コネクタ       |    |

| 1 1 5 3 | 基板         | 40 |

| 1 1 5 4 | メモリチップ     |    |

| 1 1 5 5 | メモリチップ     |    |

| 1 1 5 6 | コントローラチップ  |    |

| 2 0 0 0 | ロボット       |    |

| 2 0 0 1 | 演算装置       |    |

| 2 0 0 2 | センサ        |    |

| 2 0 0 3 | ライト        |    |

| 2 0 0 4 | リフト        |    |

| 2 0 0 5 | 駆動部        |    |

| 2 0 0 6 | 通信手段       | 50 |

|             |              |    |

|-------------|--------------|----|

| 2 0 0 7     | スピーカ         |    |

| 2 0 0 8     | マイクロフォン      |    |

| 2 0 0 9     | 表示部          |    |

| 2 0 1 0     | 発光部          |    |

| 2 0 1 1     | 移動機構         |    |

| 3 0 0 0     | システム         |    |

| 3 0 0 1     | ロボット         |    |

| 3 0 0 2     | 演算装置         |    |

| 3 0 0 3     | ブーム          | 10 |

| 3 0 0 4     | アーム          |    |

| 3 0 0 5     | 容器           |    |

| 3 0 0 6     | 容器           |    |

| 3 0 0 7     | 物品           |    |

| 3 0 0 8     | 筐体           |    |

| 3 0 0 9     | センサ          |    |

| 3 0 1 0     | 通信手段         |    |

| 3 0 1 1     | 通信手段         |    |

| 3 0 2 1     | 板            |    |

| 3 0 2 2     | バー           |    |

| 3 0 2 3     | 板            | 20 |

| 3 0 2 4     | 板            |    |

| 3 0 2 5     | ヘラ           |    |

| 4 0 1 0     | 演算部          |    |

| 4 0 1 1     | アナログ演算回路     |    |

| 4 0 1 2     | D O S R A M  |    |

| 4 0 1 3     | N O S R A M  |    |

| 4 0 1 4     | F P G A      |    |

| 4 0 2 0     | 制御部          |    |

| 4 0 2 1     | C P U        |    |

| 4 0 2 2     | G P U        | 30 |

| 4 0 2 3     | P L L        |    |

| 4 0 2 5     | P R O M      |    |

| 4 0 2 6     | メモリコントローラ    |    |

| 4 0 2 7     | 電源回路         |    |

| 4 0 2 8     | P M U        |    |

| 4 0 3 0     | 入出力部         |    |

| 4 0 3 1     | 外部記憶制御回路     |    |

| 4 0 3 2     | 音声コーデック      |    |

| 4 0 3 3     | 映像コーデック      |    |

| 4 0 3 4     | 汎用入出力モジュール   | 40 |

| 4 0 3 5     | 通信モジュール      |    |

| 4 0 4 1     | A I システム     |    |

| 4 0 4 1 _ n | A I システム     |    |

| 4 0 4 1 _ 1 | A I システム     |    |

| 4 0 4 1 A   | A I システム     |    |

| 4 0 4 1 B   | A I システム     |    |

| 4 0 9 8     | バス線          |    |

| 4 0 9 9     | ネットワーク       |    |

| 7 0 0 0     | A I システム I C |    |

| 7 0 0 1     | リード          | 50 |

- 7002 プリント基板

7003 回路部

7004 実装基板

7031 Siトランジスタ層

7032 配線層

7033 OSトランジスタ層

## 【図面】

## 【図1】

## 【図2】

10

20

30

40

50

【図3】

【図4】

10

20

【図5】

【図6】

30

40

50

【図7】

【図8】

10

20

30

40

【図9】

【図10】

50

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

10

20

30

40

50

【図19】

【図20】

10

20

【図21】

【図22】

30

40

50

【図23】

【図24】

10

20

30

40

【図25】

【図26】

50

【図27】

【図28】

10

20

【図29】

30

40

50

---

フロントページの続き

## (51)国際特許分類

|        |                   |     |        |              |

|--------|-------------------|-----|--------|--------------|

| H 01 L | 27/108(2006.01)   | F I | H 01 L | 27/1156      |

| H 01 L | 27/11582(2017.01) |     | H 01 L | 27/108 671 C |

| H 01 L | 27/1156(2017.01)  |     | H 01 L | 27/11556     |

| H 01 L | 27/11556(2017.01) |     |        |              |

## (56)参考文献

特開2017-092432 (JP, A)

特開2017-034144 (JP, A)

特開2016-063027 (JP, A)

特開2012-248823 (JP, A)

特開2011-108882 (JP, A)

特開2013-247143 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 01 L 21 / 336

H 01 L 29 / 786

H 01 L 21 / 8242

H 01 L 27 / 11582

H 01 L 27 / 1156

H 01 L 27 / 11556