(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-223070

(P2009-223070A)

(43) 公開日 平成21年10月1日(2009.10.1)

(51) Int. Cl. F 1 テーマコード (参考)

|                   |                  |           |      |       |

|-------------------|------------------|-----------|------|-------|

| <b>G09G 3/30</b>  | <b>(2006.01)</b> | G09G 3/30 | H    | 3K107 |

| <b>G09G 3/20</b>  | <b>(2006.01)</b> | G09G 3/20 | 612U | 5C080 |

| <b>H01L 51/50</b> | <b>(2006.01)</b> | G09G 3/20 | 642A |       |

|                   |                  | G09G 3/20 | 611F |       |

|                   |                  | G09G 3/20 | 631H |       |

審査請求 未請求 請求項の数 2 O L (全 9 頁) 最終頁に続く

|           |                            |          |                                                                         |

|-----------|----------------------------|----------|-------------------------------------------------------------------------|

| (21) 出願番号 | 特願2008-68632 (P2008-68632) | (71) 出願人 | 590000846<br>イーストマン コダック カンパニー<br>アメリカ合衆国 ニューヨーク州 ロチェスター ステート ストリート 343 |

| (22) 出願日  | 平成20年3月18日 (2008.3.18)     | (74) 代理人 | 100075258<br>弁理士 吉田 研二                                                  |

|           |                            | (74) 代理人 | 100096976<br>弁理士 石田 純                                                   |

|           |                            | (72) 発明者 | 水越 誠一<br>東京都千代田区神田駿河台2-9 KDX<br>御茶ノ水ビル コダック株式会社内                        |

|           |                            | (72) 発明者 | 河野 誠<br>東京都千代田区神田駿河台2-9 KDX<br>御茶ノ水ビル コダック株式会社内                         |

最終頁に続く

(54) 【発明の名称】 ドライバICおよび有機ELパネル

## (57) 【要約】

【課題】複数の用途に効率的に対応する。

【解決手段】補正演算部29は、入力されてくる画像データとメモリ40からの補正データとで演算を行い、輝度ムラの補正を行う。また、画像入力信号インターフェース32は、メモリ40に画像データを記憶し、この記憶している画像データを出力する。このように、メモリ40には、補正データまたは画像データを選択的に記憶可能である。このように用途に応じてメモリ40に何を記憶するかを切り替えることができる。

【選択図】図8

## 【特許請求の範囲】

## 【請求項 1】

入力されてくる画像データと各画素の輝度のばらつきを補正するための補正データとで演算を行い、輝度ムラの補正を行うムラ補正手段と、

同じ画像を表示する場合に、記憶している画像データを出力する表示メモリ手段と、

前記ムラ補正手段において用いる補正データ、または前記表示メモリ手段において用いる画像データを選択的に記憶可能なメモリと、

を備え、

前記ムラ補正手段または表示メモリ手段のいずれが前記メモリを使用するかを選択することができるディスプレイ用のドライバＩＣ。

10

## 【請求項 2】

請求項 1 に記載のドライバＩＣを用いた有機ＥＬパネル。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、ディスプレイ用のドライバＩＣおよびそのドライバＩＣを用いた有機ＥＬパネルに関する。

## 【背景技術】

## 【0002】

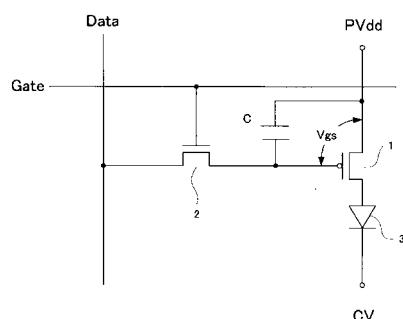

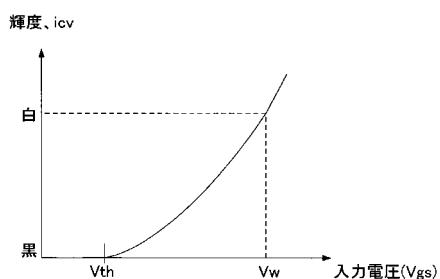

従来より、有機ＥＬディスプレイが知られており、この有機ＥＬディスプレイでは、有機ＥＬ素子を電流駆動するための駆動ＴＦＴを有し、画像データに応じて駆動ＴＦＴの電流量を制御する。

20

## 【0003】

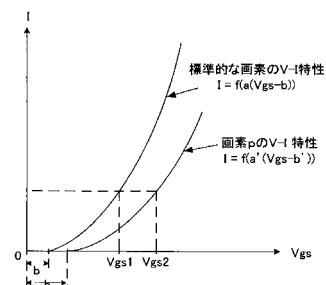

製造上の問題または経年変化等により、駆動ＴＦＴのＶｔｈまたはＶ-Ｉ特性の傾き（ $\mu$ ）がばらつき、輝度ムラとなることがある。このムラを補正するために、各画素を駆動する画像データに所定の値を加算してＶｔｈの補正（オフセット補正）を行ったり、所定の値を乗算することにより $\mu$ の補正（ゲイン補正）をすることがある。

## 【0004】

図3に補正データの計算方法を、図4に補正回路のブロック図を示す。まず、いくつかの画素の電圧対電流特性を測定することにより、そのパネルの標準的な画素のＶ-Ｉ特性のカーブを求める。このカーブが $I = f(a(V - b))$ という式で表されると仮定して関数 $f(x)$ を決定する。このパネルの全ての画素はこの $f(x)$ で表され、特性のばらつきは係数 $a$ と係数 $b$ の違いによるものと仮定すれば、各画素の $a$ と $b$ は2つ以上の入力電圧レベルに対応する画素電流を測定することにより求めることができる。

30

## 【0005】

いま、画素 $p$ のＶ-Ｉ特性が $I = f(a'(V - b'))$ で表される時、先に求めた平均的な画素の $a$ 及び $b$ より、D/A変換の係数を $k$ として、 $offset = k(b' - a / a')$ 及び $gain = a / a'$ を求め、画像データに求められた $offset$ を加算し、 $gain$ を乗算することで、補正が行える。

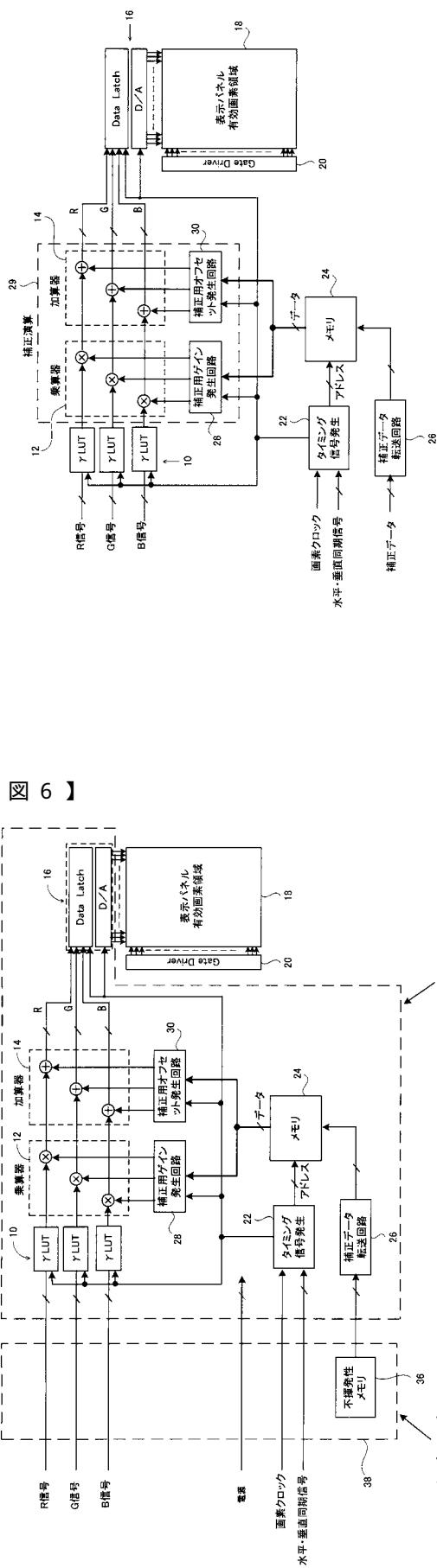

## 【0006】

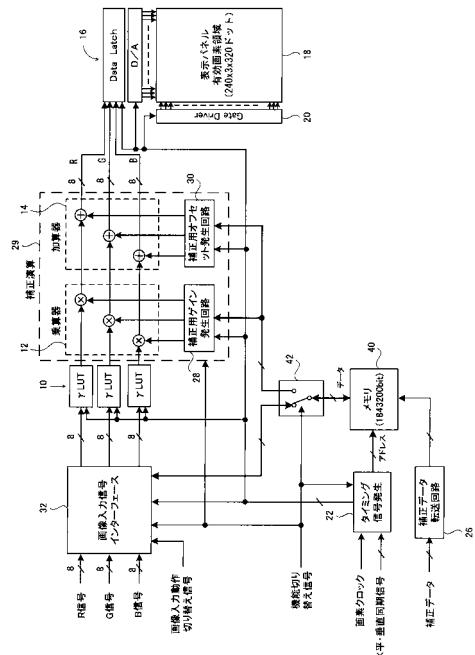

具体的には、図4に示すように、画像データである、R信号、G信号、B信号について、それぞれ入力されてくる画素データと画素電流の関係を直線とするためのガンマルックアップテーブル（LUT）10において、補正した画像データを得る。この補正後の画像データについて、乗算器12で補正用ゲイン $gain$ を乗算し、加算器14で補正用オフセット $offset$ を加算する。

40

## 【0007】

ムラについて補正された画像信号（R, G, B）は、データラッチおよびD/A変換器を含むデータドライバ16を介し、表示パネル18に供給され、ここで表示される。なお、表示パネル18には、ゲートドライバ20が接続されており、このゲートドライバ20が表示パネル18のどのラインに画像データを供給するかを制御する。

50

## 【0008】

タイミング信号発生部22は、画素クロック、水平・垂直同期信号から、各種のタイミング信号を発生するとともに、メモリ24のアドレスを発生する。このメモリ24は高速で読み書きができるRAMで構成されており、電源投入時に、補正データ転送回路26を介して外部の不揮発性メモリなどから補正データ(gain, offset)が送られて記憶される。タイミング信号発生部22が、画素毎の画像データに対応して、その画素についての補正データが記憶されているアドレスを発生し、メモリ24から画素毎の補正データが読み出され、これらが補正用ゲイン発生回路28、補正用オフセット発生回路30を介し、乗算器12、加算器14に供給される。補正用ゲイン発生回路28、補正用オフセット発生回路30、乗算器12、加算器14が、補正演算部29を構成している。

10

## 【0009】

このように、補正後の信号データに演算することによりムラを大幅に改善することができる。このようなムラ補正については、特許文献1~4などに示されている。

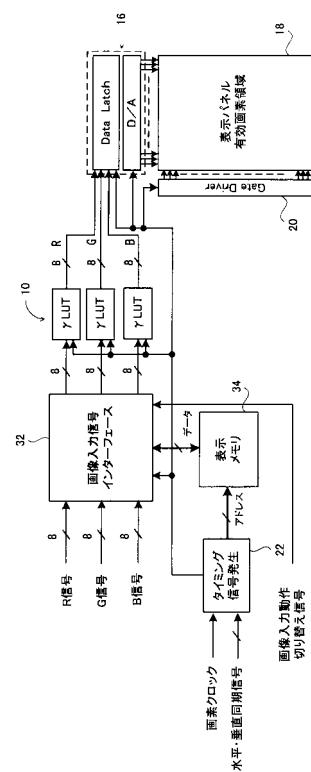

## 【0010】

また、モバイル機器用のドライバICは、グラフィックRAMと呼ばれる表示用RAM(表示メモリ)を内蔵し、1度表示メモリに静止画像を書き込めば表示画像を変更しない限り外部から画像信号を転送する必要がないものがある。図5において画像入力信号インターフェース32では、各色8ビットの入力画像信号を一旦表示メモリ34に保持し、保持された画像をLUT10に送る機能を持つ。また、画素クロックに同期して連続的に入力される信号に対してはそのままLUT10に送る動作も行うことができ、これらの動作の切り替えはシステム側のCPU等からの切り替え信号により行われる。さらに、表示メモリ34上の画像に線や図形を書き込んだり、画像をスクロールしたり、拡大縮小したりするグラフィック機能を持たせることも一般に行われている。

20

## 【0011】

このような表示メモリ34を搭載したドライバICの場合、システム側回路とドライバIC間のデータバスからの不要輻射の低減、データ転送による消費電力の低減、システム側回路の負担軽減化等のメリットがあるが、大容量メモリによりチップサイズが増大しコストが上がるというデメリットもある。現状では一般的に、静止画を表示する機会の多い携帯電話用のパネルには表示メモリが搭載されることが多く、動画の表示も頻繁に行うデジタルカメラやビデオカメラのモニタ用内蔵パネルには表示メモリが搭載されていない。従って、表示用RAMを搭載するべきか否かは一概には言えず、アプリケーション次第で総合的に判断されているのが現状である。

30

## 【0012】

【特許文献1】特開平11-282420号公報

【特許文献2】特開2004-264793号公報

【特許文献3】特開2005-284172号公報

【特許文献4】特開2007-279290号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0013】

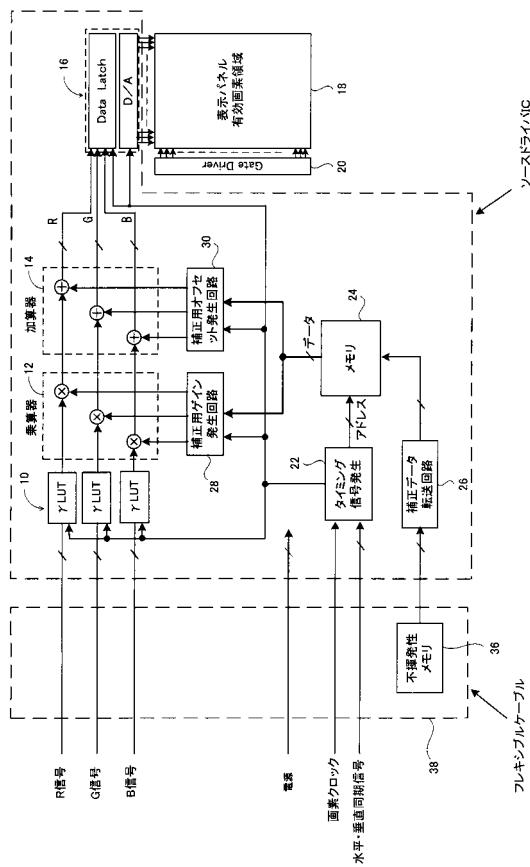

ここで、ムラ補正回路を用いて全画素を補正しようとすると補正データは各画素毎に必要となるので、パネルの画素数分のデータを保持しておくメモリが必要となる。現在、図6及び図7に示す様に、パネルの出荷時にムラのデータを外部の不揮発性メモリ36に書き込んでおき、パネルモジュールの電源投入時に全補正データをドライバIC内部のメモリ(RAM)24に読み込み、このメモリ24のデータを使って補正を行うことが行われている。なお、この例では、不揮発性メモリ36をフレキシブルケーブル38に実装している。

40

## 【0014】

画素数の多い表示パネル18の場合、メモリ24として大容量のRAMが必要となり、ドライバICのチップサイズに影響しコストも高くなる。このように、ドライバICのサ

50

イズに補正用のメモリ24の占める割合は大きく、TFT製造プロセスの最適化や画素回路の工夫によりムラの少ないパネルに関してはこのような外部回路によるムラ補正の回路は、搭載しない方がコスト的に有利である。

【0015】

一方、モバイル機器用のドライバICには表示用RAMである表示メモリ34が搭載されているものがあり、この場合もパネルの画素数分のメモリが使用されるが、前述のように、表示メモリが不要なアプリケーションもある。

【0016】

すなわち、同じ画素数の駆動方式の同じパネルに対し、ムラ補正機能及び表示メモリ機能ともになし、ムラ補正機能のみあり、表示メモリ機能のみあり、ムラ補正機能及び表示メモリ機能ともにあり、という4種類のドライバICを作り、用途に応じて使い分けるのが理想である。しかしながら、実際には開発費や開発工数の観点でこのように4種類のドライバICを開発するのは難しいし、品種が分散することによって大量生産によるコストダウンも望めなくなる。

10

【課題を解決するための手段】

【0017】

本発明は、入力されてくる画像データと各画素の輝度のばらつきを補正するための補正データとで演算を行い、輝度ムラの補正を行うムラ補正手段と、同じ画像を表示する場合に、記憶している画像データ出力をする表示メモリ手段と、前記ムラ補正手段において用いる補正データ、または前記表示メモリ手段において用いる画像データを選択的に記憶可能なメモリと、を備え、前記ムラ補正手段または表示メモリ手段のいずれが前記メモリを使用するかを選択することができる特徴とする。

20

【0018】

また、本発明に係るドライバICは、有機ELパネルに適用することが好適である。

【発明の効果】

【0019】

本発明によれば、メモリをムラ補正用または表示メモリ用のいずれに使用するかを選択することができる。このため、チップサイズに大きな影響を与せず、用途に応じてムラ補正機能と表示メモリ機能が選択的に使用できるドライバICを提供できる。

30

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施形態について、図面に基づいて説明する。

【0021】

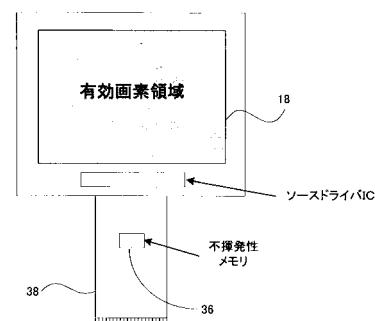

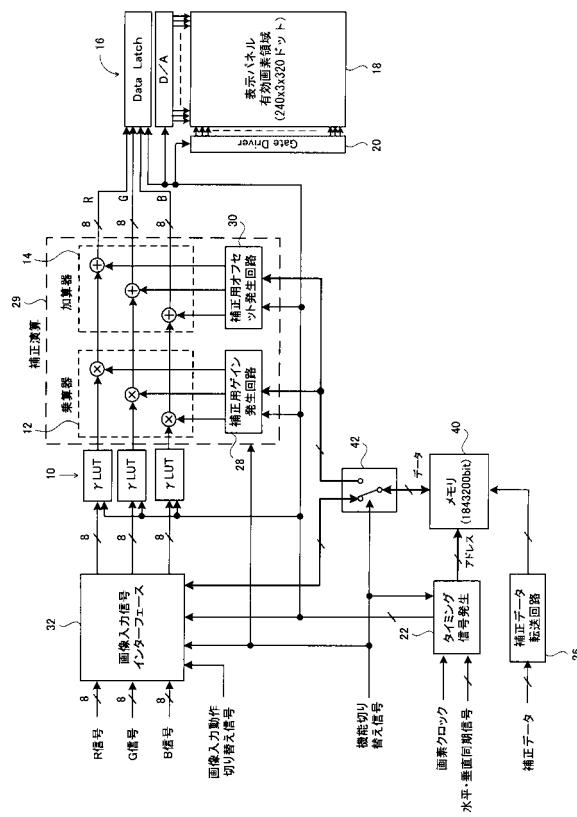

図8に、実施形態のブロック図を示す。このように、メモリ40を有し、このメモリ40は、スイッチ42によって、画像入力信号インターフェース32または補正演算部29のいずれかに選択的に接続される。

40

【0022】

また、タイミング信号発生部22から発生する、メモリ40のアドレスを含めたドライバIC内の全てのタイミング信号も機能によって切り替わる。なお、低消費電力化の観点から、一方の機能でしか使われない回路に入力されるクロックやタイミングパルスは、機能として選択されていない時には停止することが望ましい。

【0023】

機能の切り替えは、例えば生産工程において、機能切り替え信号用ピンをフレキシブルケーブル上で電源又はグランドに接続することにより行う。また、ディスプレイについての輝度、色合いなどの設定と同様に、マイコンの出力信号によって設定してもよいし、前述の外部フラッシュメモリに設定を記憶させておき、電源投入時に読み込んでも良い。

【0024】

機能切り替え信号が設定されていると、スイッチ42が画像入力信号インターフェース32または補正演算部29のいずれかにメモリ40を接続する。

【0025】

50

表示メモリとして使用する場合には、画像入力信号インターフェース32がメモリ40に接続される。外部のCPUは、そのときの状態により、同一画面を表示する場合には、画像入力動作切り替え信号によってその旨の指示を画像入力信号インターフェース32に供給する。この場合、画像入力信号インターフェース32は、入力画像信号を一旦表示メモリ34に保持し、保持された画像をLUT10に送る。これによってメモリ40内の画像信号が繰り返し表示パネル18において表示される。また、CPUからの指令により、表示メモリ34上の画像に線や図形を書き込んだり、画像をスクロールしたり、拡大縮小したりするグラフィック機能を持たせることもできる。

#### 【0026】

一方、動画表示などの場合には、画素クロックに同期して連続的に入力される信号をそのままLUT10に送る。これによって、表示パネル18に、通常のディスプレイと同様の表示が行われる。

#### 【0027】

また、補正データ用の表示メモリとして使用する場合には、補正演算部29がメモリ40に接続される。そして、電源立ち上げ時などに、外部の不揮発性メモリに記憶されている補正データが、補正データ転送回路26によりメモリ40に書き込まれ、補正演算部29に補正データが供給される。

#### 【0028】

ここで、メモリ40を表示メモリとして使用する場合のサイズは、例えばQVGA(240RGB × 320)で1サブピクセルが8ビットのパネルであれば、 $240 \times 3 \times 320 \times 8 = 1843200$ ビットとなる。

#### 【0029】

一方、このメモリ40をそのままムラ補正用のメモリに使用するとすれば、やはり1ドットに8ビットを割り当てることができる。この場合、駆動 TFT の閾値電圧Vth、すなわちオフセットの補正だけを行うとすれば8ビットをオフセット補正に割り当てることができ、μすなわちゲインも補正する場合はそれぞれ4ビットずつ割り当てるともできる。

#### 【0030】

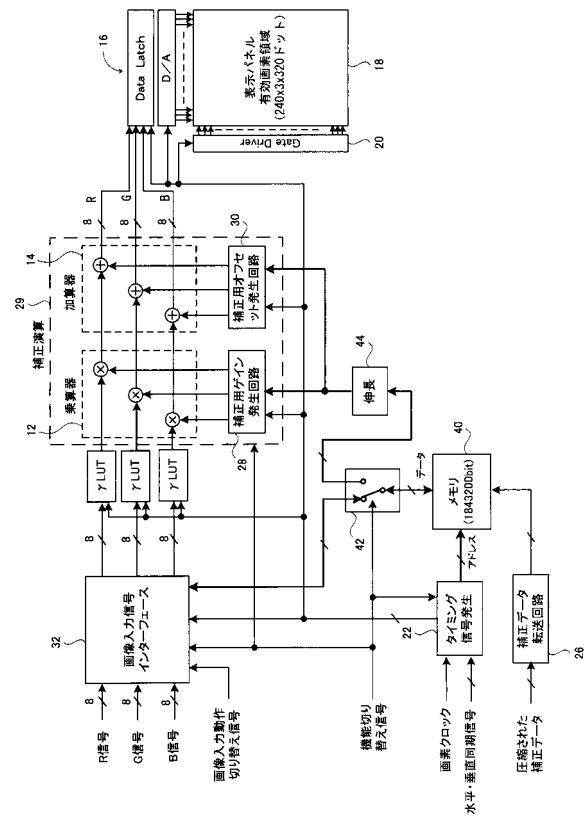

ただし、4ビットでは濃いムラが存在した時に補正し切れない可能性があり、特許文献4に示すようなデータ圧縮を行うことが好適である。この特許文献4に記載されたデータ圧縮を使用した場合、補正可能なムラの濃さはメモリ40のサイズによっては制限されず、補正可能なパネルトータルのムラの量がメモリ40のサイズによって制限される。通常は、オフセットとゲインの両方を補正しても、濃いムラが全体にわたって存在しない限り上記のメモリサイズ内に収めることができる。この場合のブロック図の例を図9に示す。

#### 【0031】

圧縮された補正データは、補正データ転送回路26を介して、メモリ40に書き込まれる。そして、スイッチ42と、補正用ゲイン発生回路28、補正用オフセット発生回路30との間に伸長回路44を設ける。従って、メモリ40をムラ補正用に用いる場合に、メモリ40に圧縮された補正データが記憶され、その圧縮された補正データが伸長回路44で伸長されて補正に利用される。

#### 【0032】

本実施形態では、ムラ補正に使用する記憶手段と、表示メモリ機能に使用する記憶手段の両方にメモリ40を共用化し、一つのドライバICでムラ補正機能と表示メモリ機能を選択可能にする。これにより、1種類のドライバICで、ムラ補正機能のみあり、または、表示メモリ機能のみありのドライバICが実現できる。この場合、ムラ補正機能を選択した時は表示メモリ機能に使用するロジック部は使用しないので冗長となり、また、表示メモリ機能を選択した時はムラ補正機能に使用するロジック部は使用しないので冗長となる。しかし、これらのロジック部分がチップサイズに占める割合はRAMやD/A変換部が占める割合に比べると非常に小さく、ICのチップサイズへの影響は少ない。むしろ、

10

20

30

40

50

ドライバ I C の共用化によって、一般的には、開発費の削減、量産効果によるコストダウンなどのメリットの方が大きくなる。

【図面の簡単な説明】

【0033】

【図1】画素回路の構成を示す図である。

【図2】入力電圧と電流の関係を示す図である。

【図3】画素毎の特性の相違を示す図である。

【図4】ムラ補正のための構成を示す図である。

【図5】表示メモリを用いる場合の構成を示す図である。

【図6】補正データを記憶する不揮発性メモリを設ける構成を示す図である。 10

【図7】補正データを記憶する不揮発性メモリをフレキシブルケーブルに設ける構成を示す図である。

【図8】実施形態の構成を示す図である。

【図9】他の実施形態の構成を示す図である。

【符号の説明】

【0034】

10 L U T、12 乗算器、14 加算器、16 データドライバ、18 表示パネル、20 ゲートドライバ、22 タイミング信号発生部、24 メモリ、26 補正データ転送回路、28 補正用ゲイン発生回路、29 補正演算部、30 補正用オフセット発生回路、32 画像入力信号インターフェース、34 表示メモリ、36 不揮発性メモリ、38 フレキシブルケーブル、40 メモリ、42 スイッチ、44 伸長回路。 20

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 3 1 V |

| H 0 5 B | 33/14 | A       |

(72)発明者 小野村 高一

東京都千代田区神田駿河台2-9 K D X 御茶ノ水ビル コダック株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 CC45 HH04

5C080 AA06 BB05 DD05 DD27 EE29 JJ02 JJ03 JJ05