(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5019210号

(P5019210)

(45) 発行日 平成24年9月5日(2012.9.5)

(24) 登録日 平成24年6月22日(2012.6.22)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| GO6K 19/073 | (2006.01) | GO6K 19/00 | P    |

| GO6F 12/16  | (2006.01) | GO6F 12/16 | 310A |

| GO6F 21/02  | (2006.01) | GO6F 21/02 | 175  |

|             |           | GO6F 21/02 | 177  |

請求項の数 12 (全 23 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2007-157870 (P2007-157870)  |

| (22) 出願日  | 平成19年6月14日 (2007.6.14)        |

| (65) 公開番号 | 特開2008-310595 (P2008-310595A) |

| (43) 公開日  | 平成20年12月25日 (2008.12.25)      |

| 審査請求日     | 平成22年3月16日 (2010.3.16)        |

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                |

| (74) 代理人  | 100075672<br>弁理士 峰 隆司                 |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                |

| (74) 代理人  | 100084618<br>弁理士 村松 貞男                |

最終頁に続く

(54) 【発明の名称】携帯可能電子装置、ICカード、および携帯可能電子装置の制御方法

## (57) 【特許請求の範囲】

## 【請求項1】

外部装置から供給されるコマンドに応じて動作する携帯可能電子装置において、複数ビット長の第1のデータを格納する第1の記憶手段と、当該携帯可能電子装置の状態を示す情報として、前記第1の記憶手段に記憶されている前記第1のデータ、あるいは、前記第1のデータとは異なる第2のデータの何れかを格納する第2の記憶手段と、

前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致するか否かを判断する判断手段と、

この判断手段により前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致すると判断した場合、前記第2の記憶手段に記憶されている内容に応じて外部装置から供給されるコマンドに対応する本処理を実行する実行手段と、

を有することを特徴とする携帯可能電子装置。

## 【請求項2】

さらに、乱数を生成する乱数生成手段を有し、

前記第1の記憶手段は、前記乱数生成手段により生成された乱数に基づくデータを第1のデータとして格納する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

## 【請求項3】

10

20

前記乱数生成手段は、互いに異なる2つの乱数を生成し、

前記第1の記憶手段は、前記乱数生成手段により生成された一方の乱数に基づく第1のデータと前記乱数生成手段により生成された他方の乱数に基づく第2のデータとを記憶する、

ことを特徴とする前記請求項2に記載の携帯可能電子装置。

【請求項4】

さらに、前記判断手段により前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかとも一致しないと判断した場合、当該携帯可能電子装置の動作を停止する停止手段を有することを特徴とする前記請求項1又は3に記載の携帯可能電子装置。

10

【請求項5】

さらに、前記判断手段により前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかとも一致しないと判断した場合、前記第2の記憶手段に異常が発生していることを示す情報を前記外部装置へ送信するエラー処理手段を有することを特徴とする前記請求項1又は3に記載の携帯可能電子装置。

【請求項6】

さらに、前記外部装置から受信したコマンドに対応する処理を実行するための実行条件をチェックし、そのチェック結果を前記第2の記憶手段に記憶する処理を行う前処理手段を有する、

ことを特徴とする前記請求項1乃至5に記載の携帯可能電子装置。

20

【請求項7】

さらに、各種のデータを記憶する第3の記憶手段と、

前記第3の記憶手段に記憶されている各種のデータに対するアクセス権を示す情報を前記第2の記憶手段に格納する処理を行う前処理手段と、を有する、

ことを特徴とする前記請求項1乃至5に記載の携帯可能電子装置。

【請求項8】

さらに、使用者を認証する認証手段を有し、

前記前処理手段は、前記認証手段により認証が成功した使用者に対する各種のデータに対するアクセス権を示す情報を前記第2の記憶手段に格納する処理を行う、

ことを特徴とする前記請求項7に記載の携帯可能電子装置。

30

【請求項9】

前記判断手段は、前記第2の記憶手段に記憶されているデータが前記第1のデータと一致する場合に第1の状態であることを示す信号を出力し、前記第2の記憶手段に記憶されているデータが前記第2のデータと一致する場合には第2の状態であることを示す信号を出力し、前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れとも一致しない場合にはエラー状態であることを示す信号を出力する比較回路である、

ことを特徴とする前記請求項1乃至8に記載の携帯可能電子装置。

【請求項10】

前記第2の記憶手段は、第1のデータあるいは第2のデータを格納するための複数のフラグを有し、

40

前記第1の記憶手段は、前記第2の記憶手段の各フラグに対応する種々の第1のデータを格納する、

ことを特徴する前記請求項1乃至9に記載の携帯可能電子装置。

【請求項11】

外部装置から供給されるコマンドに応じて動作する携帯可能電子装置に用いられる制御方法であつて、

複数ビット長の第1のデータを第1の記憶手段に格納しておき、

当該携帯可能電子装置の状態を示す情報として、前記第1の記憶手段に記憶されている前記第1のデータ、あるいは、前記第1のデータとは異なる第2のデータの何れかを前記

50

第2の記憶手段に格納し、

前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致するか否かを判断し、

この判断により前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致すると判断した場合、前記第2の記憶手段に記憶されている内容に応じて外部装置から供給されるコマンドに対応する本処理を実行する、

ことを特徴とする携帯可能電子装置の制御方法。

【請求項12】

外部装置から供給されるコマンドに応じて動作するICカードにおいて、

複数ビット長の第1のデータを格納する第1の記憶手段と、当該携帯可能電子装置の状態を示す情報として、前記第1の記憶手段に記憶されている前記第1のデータ、あるいは、前記第1のデータとは異なる第2のデータの何れかを格納する第2の記憶手段と、前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致するか否かを判断する判断手段と、この判断手段により前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致すると判断した場合、前記第2の記憶手段に記憶されている内容に応じて外部装置から供給されるコマンドに対応する本処理を実行する実行手段とを具備するモジュールと、

前記モジュールを具備する本体と、

を有することを特徴とするICカード。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば、個人情報あるいは取引情報などが記憶されているICチップが内蔵されているICカードあるいはICタグなどの携帯可能電子装置、および、上記携帯可能電子装置の制御方法などに関する。

【背景技術】

【0002】

近年、ICカードなどの携帯可能電子装置は、様々な用途に利用されている。特に、ICカードには、個人情報や金銭的な取引情報などが記憶されることが多い。このようなICカードあるいはICカードを用いたシステムでは、高いセキュリティ性が求められており、不正なアクセスを確実に防止する技術が求められている。一方、近年、ICカードに対して電源にノイズを印加したり、電磁波、光波あるいは温度などのストレスを与えて、ICカードを誤動作させることにより、ICカード内の内部情報あるいは処理手順などを解析しようとする脅威が高まっている。

【0003】

従来、たとえば、特開昭60-207957号公報（特許文献1）、あるいは、特開平11-282991号公報（特許文献2）には、ICカードに対するコマンドの種類と実行順とに基づいて不正なアクセスを検出する技術が記載されている。これらの技術では、ICカード内のメモリに格納するフラグ（識別情報）に基づいて処理の実行順などを監視する。しかしながら、当該ICカード内のメモリの情報は、上述のような外的な要因により変化してしまう可能性がある。このような場合、ICカード内のメモリに格納されるフラグなどの情報も変化してしまう可能性がある。すなわち、外的な要因によりICカード内のメモリの情報が変化されると、上記したような技術を適用してもICカードが誤動作する可能性があるという問題点がある。

【特許文献1】特開昭60-207957号公報

【特許文献2】特開平11-282991号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

この発明の一形態は、セキュリティ性が高い携帯可能電子装置および携帯可能電子装置

10

20

30

40

50

の制御方法を提供することを目的とする。

【課題を解決するための手段】

【0005】

この発明の一形態としての携帯可能電子装置は、外部装置から供給されるコマンドに応じて動作するものにおいて、複数ビット長の第1のデータを格納する第1の記憶手段と、当該携帯可能電子装置の状態を示す情報として、前記第1の記憶手段に記憶されている前記第1のデータ、あるいは、前記第1のデータとは異なる第2のデータの何れかを格納する第2の記憶手段と、前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致するか否かを判断する判断手段と、この判断手段により前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致すると判断した場合、前記第2の記憶手段に記憶されている内容に応じて外部装置から供給されるコマンドに対応する本処理を実行する実行手段とを有する。

10

【0006】

この発明の一形態としての携帯可能電子装置の制御方法は、外部装置から供給されるコマンドに応じて動作する携帯可能電子装置に用いられる方法であって、複数ビット長の第1のデータを第1の記憶手段に格納しておき、当該携帯可能電子装置の状態を示す情報として、前記第1の記憶手段に記憶されている前記第1のデータ、あるいは、前記第1のデータとは異なる第2のデータの何れかを前記第2の記憶手段に格納し、前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致するか否かを判断し、この判断により前記第2の記憶手段に記憶されているデータが前記第1のデータあるいは前記第2のデータの何れかと一致すると判断した場合、前記第2の記憶手段に記憶されている内容に応じて外部装置から供給されるコマンドに対応する本処理を実行する。

20

【発明の効果】

【0007】

この発明の一形態によれば、セキュリティ性が高い携帯可能電子装置および携帯可能電子装置の制御方法を提供することができる。

【発明を実施するための最良の形態】

【0008】

30

以下、この発明に係る実施の形態について図面を参照しつつ説明する。

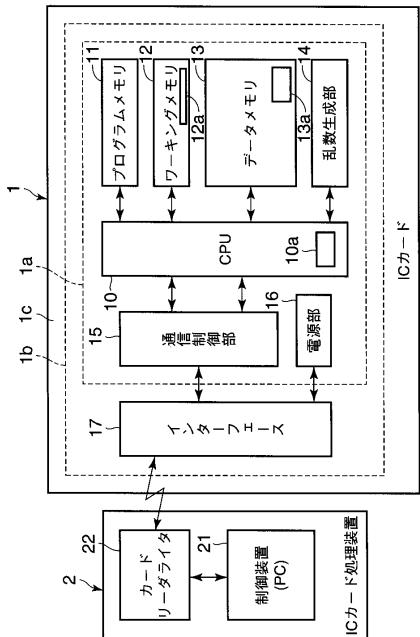

図1は、第1の実施の形態に係る携帯可能電子装置としてのICカード1およびICカード1を含むICカードシステムの構成例を示すブロック図である。

上記ICカード1は、外部装置としてのICカード処理装置2からの電源供給により動作可能な状態となる。動作可能となったICカード1は、上記ICカード処理装置2からのコマンドに応じて種々の処理を行う。上記ICカード処理装置2は、ICカード1を動作させるための電源を供給するとともに、当該ICカード1に対して種々の処理を要求するコマンドを供給する。上記ICカード処理装置2がICカード1に対して供給するコマンドは、用途あるいは運用形態などに応じた処理を要求するものである。

【0009】

40

また、上記ICカード1は、アンテナあるいは無線通信部等により上記ICカード処理装置2と非接触の状態で無線通信を行う非接触式の携帯可能電子装置（非接触式ICカード）であっても良し、上記ICカード処理装置2と物理的に接触して通信を行う接触式の携帯可能電子装置（接触式ICカード）であっても良い。さらには、上記ICカード1は、非接触式ICカードとしての通信機能と接触式ICカードとしての通信機能とを有する複合型のICカード（デュアルインターフェースICカード）であっても良い。なお、第1および第2の実施の形態では、主に、非接触式ICカードを想定して説明する。非接触式ICカードと接触式ICカードとはICカード処理装置2との通信方式等が異なるだけである。このため、以下に説明する実施の形態は、接触式ICカードにも同様に適用できる。

50

## 【0010】

次に、上記 I C カード 1 の構成例について説明する。

図 1 に示すように、上記 I C カード 1 は、CPU 10、プログラムメモリ 11、ワーキングメモリ 12、データメモリ 13、乱数生成部 14、通信制御部 15、電源部 16、および、インターフェース 17 などにより構成される。

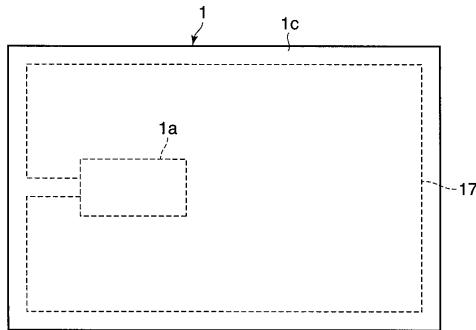

また、上記 I C カード 1 は、カード状の本体により構成される。上記 I C カード 1 を形成するカード状の本体には、1 つ（あるいは複数）の I C チップ 1a とアンテナ 17 とが埋設される。上記 I C チップ 1a は、CPU 10、プログラムメモリ 11、ワーキングメモリ 12、データメモリ 13、通信制御部 15 および電源部 16 などにより構成される。上記 I C チップ 1a は、上記インターフェース 17 としてのアンテナに接続された状態でモジュール化され、当該 I C カード 1 を形成するカード状の本体内に埋設される。たとえば、図 2 は、非接触式 I C カード全体の構成例を示す図である。図 2 に示す非接触式 I C カードは、カード状の本体 1c を有している。この本体 1c 内には、図 2 に点線で示すように、1 つ（あるいは複数）の I C チップ 1a とアンテナ 17 とを有するモジュール 1b が埋め込まれている。

## 【0011】

上記 CPU 10 は、I C カード 1 全体の制御を司るものである。上記 CPU 10 は、データを記憶するための内部メモリとしてのレジスタ 10a を有している。上記 CPU 10 は、上記プログラムメモリ 11 あるいはデータメモリ 13 に記憶された制御プログラムおよび制御データなどに基づいて動作する。上記 CPU 10 は、基本的な動作を司る制御プログラムを実行することにより、外部装置から与えられるコマンドに応じた処理を実行する。たとえば、外部装置から上記データメモリ 13 へのデータの書き込みを要求するコマンドが与えられれば、上記 CPU 10 は、上記データメモリ 13 へのデータの書き込み処理を実行する。また、外部装置から上記データメモリ 13 に記憶されているデータの読み出しを要求するコマンドが与えられれば、上記 CPU 10 は、上記データメモリ 13 からのデータの読み出し処理を実行する。さらに、上記 CPU 10 は、当該 I C カード 1 の用途などに応じてインストールされる処理プログラムを実行することにより、用途に応じた処理を実現するようになっている。

## 【0012】

上記プログラムメモリ 11 は、読み出し専用のメモリ（ROM：リードオンリーメモリ）により構成される。上記プログラムメモリ 11 には、予め基本動作を司る制御プログラムおよび制御データなどが記憶されている。上記プログラムメモリ 11 には、予め当該 I C カード 1 の仕様に応じた制御プログラム及び制御データが記憶される。たとえば、上記 CPU 10 は、上記プログラムメモリ 11 に記憶される制御プログラムにより外部から与えられるコマンドに応じた処理を実現する。また、上記プログラムメモリ 11 には、データメモリ 13 におけるメモリ領域の属性などを指定するための情報なども記憶されている。

## 【0013】

上記ワーキングメモリ 12 は、揮発性のメモリ（RAM；ランダムアクセスメモリ）により構成される。上記ワーキングメモリ 12 は、データを一時保管するバッファメモリとして機能する。例えば、上記ワーキングメモリ 12 には、I C カード処理装置（外部装置）2 との通信処理において、送受信されるデータが一時的に保管される。また、上記ワーキングメモリ 12 には、種々の書き込みデータなどを一時的に保持するメモリとしても利用される。さらに、上記ワーキングメモリ 12 には、当該 I C カード 1 における処理状況あるいは設定情報などを識別するための情報を格納するステータスフラグ（以下、単にフラグとも称する）が設定されるフラグ領域 12a が設けられる。

## 【0014】

上記データメモリ（不揮発性メモリ）13 は、データの書き込みが可能な不揮発性のメモリである。上記データメモリ 13 は、例えば、EEPROM あるいはフラッシュメモリなどにより構成される。上記データメモリ 13 には、当該 I C カード 1 の使用目的に応じ

10

20

30

40

50

た種々の情報が記憶される。上記データメモリ13には、種々の設定情報などを記憶するためのデータテーブルなども設けられる。たとえば、当該ICカードを複数の使用者が使用することが想定される場合、上記データメモリ13には、各使用者の識別情報（ID）、パスワード、および、各使用者ごとの各種のデータに対するアクセス権を示す情報などが格納されるデータテーブル13aが設けられる。

#### 【0015】

また、当該ICカードの使用目的に応じたアプリケーション（処理プログラムおよび運用データなど）は、上記データメモリ13に記憶される。また、当該ICカード1が複数の使用目的に使用される場合、上記データメモリ13には、各使用目的に応じた複数のアプリケーションが記憶される。なお、当該ICカード1の使用目的に応じたアプリケーションは、上記データメモリ13上に定義された使用目的ごとのプログラムファイルおよびデータファイルなどの各ファイルに記憶される。このようなファイル構造は、たとえば、ISO/IEC7816-4に基づくものである。つまり、上記ICカード1のデータメモリ13には、種々のアプリケーションおよび種々の運用データが記憶可能である。

10

#### 【0016】

上記乱数生成部14は、任意のデータとしての乱数を生成するものである。上記乱数生成部14は、ICチップなどにより構成しても良いし、上記CPUなどの制御素子がプログラムを実行することにより実現するようにしても良い。

上記通信制御部15は、上記インターフェース17を介して外部装置（たとえば、ICカード処理装置2）とのデータ通信を制御するものである。外部装置からデータを受信する場合、上記通信制御部15は、上記インターフェース17により受信した電波としての送信データを復調し、復調した信号を上記CPU10に供給する。また、外部装置へデータを送信する場合、上記通信制御部15は、上記CPU10から与えられるデータを変調し、変調したデータを上記インターフェース17としてのアンテナにより電波として発信する。なお、接触式ICカードの場合、上記インターフェース17は、外部装置のコントラクト部と物理的に接触する端子などにより構成されるものとなる。

20

#### 【0017】

上記電源部16は、上記インターフェース17により受信した電波から当該ICカード1の各部を動作させるための電源およびクロックパルスを生成する。上記電源部16は、上記アンテナ17により受信した電波から生成した電源電圧およびクロックパルスを各部に供給するようになっている。また、上記電源部16からの電源供給により起動した場合、上記CPU10は、当該ICカード1の処理状態をリセットする処理を行うようになっている。なお、接触式ICカードの場合、インターフェース17を介して外部装置から直接的に供給される電源およびクロックパルスにより各部が動作するようになっている。

30

#### 【0018】

次に、上記ICカード処理装置2について説明する。

上記ICカード処理装置2は、図1に示すように、制御装置21およびカードリーダライタ22を有している。上記制御装置21は、パーソナルコンピュータ（PC）などにより構成される。上記制御装置21は、CPUなどの演算処理部、RAM、ROM、不揮発性メモリおよびハードディスクドライブなどの各種メモリ、通信インターフェースなどの各種インターフェースなどにより構成される。上記制御装置21では、上記演算処理部がメモリに記憶されている各種の制御プログラムを実行することにより各種の処理を実現している。また、上記制御装置21は、ICカード1とのデータ通信を行う上記カードリーダライタ22とのデータの入出力を実現している。

40

#### 【0019】

たとえば、上記制御装置21には、上記ICカード1を用いた各種の処理に応じた制御プログラムが予め記憶されている。上記制御装置21では、上記のような制御プログラムを実行することにより上記ICカード1を用いた各種の処理を実行する。たとえば、上記ICカード1を用いた各種の処理において、上記制御装置21は、所定のコマンドを所定の手順で供給する。上記制御装置21では、上記のような各コマンドに対するICカード

50

1 からの各レスポンス（コマンドに対する処理結果等を示す情報）に基づいて各種の処理を行うようになっている。

#### 【0020】

上記カードリーダライタ22は、上記ICカード1とのデータ通信を行う通信手段として機能する。上記カードリーダライタ22は、上記ICカード1の通信方式に応じた通信方式によるデータ通信を行うためのものである。つまり、上記カードリーダライタ22を介して制御装置21は、上記ICカード1とのデータ通信を実現している。

#### 【0021】

上記ICカード1が非接触型のICカードである場合、上記カードリーダライタ22は、上記ICカード1との無線によるデータ通信を行うためのアンテナおよび通信制御部（変復調回路等）などにより構成される。非接触型のICカード1へデータを送信する場合、上記カードリーダライタ22では、上記制御装置21から与えられる送信データを変調し、変調した信号を電波としてアンテナにより発信する。また、非接触型のICカード1からデータを受信する場合、上記カードリーダライタ22では、アンテナにより受信した電波としての信号を通信制御部により復調し、復調したデータを受信データとして上記制御装置21へ供給する。また、上記カードリーダライタ22では、上記のようなデータの送受信とともに、上記ICカード1を動作させるための電源およびクロックパルスとなる電波をアンテナにより発信するようになっている。

10

#### 【0022】

また、上記ICカード1が接触型のICカードである場合、上記カードリーダライタ22は、ICカード1と物理的に接触してデータ通信を行うためのコンタクト部および通信制御部などにより構成される。接触型のICカードとのデータの送受信を行う場合、上記カードリーダライタ22では、上記コンタクト部がICカード1側に設けられているコンタクト部と物理的に接触して各種のデータ通信を行う。また、上記カードリーダライタ22では、ICカード1に物理的に接触しているコンタクト部を介して当該ICカード1に對して電源およびクロックパルスを供給するようになっている。

20

#### 【0023】

次に、上記第1の実施の形態に係るICカード1の動作について概略的に説明する。

上記ICカード処理装置2からコマンドを受信した場合、上記ICカード1は、コマンドの種類によっては、当該コマンドを実行するための実行条件のチェック処理を前処理として実行する。また、上記データメモリ13などに記憶されている各種のデータに対するアクセス権を設定されている場合、当該ICカード1では、外部からのコマンド処理を行う前の処理（前処理）として、各種のデータに対するアクセス権を設定する処理を実行することもある。ここでは、これらのような外部装置からのコマンドに対応する所定の処理を実行する前に実行される処理を前処理と総称するものとする。

30

#### 【0024】

上記のような前処理の結果として得られる情報は、上記フラグ領域12aに設けられる各フラグに格納され、CPU10により適宜参照される。たとえば、外部装置からのコマンドに対応する処理を実行するための実行条件のチェック結果は、当該コマンドに対応する所定の処理を実行する前に各実行条件に対応づけたフラグに格納される。また、各種のデータに対するアクセス権を示す情報は、各種のデータへのアクセスを要求するコマンドを実行する前に各種のデータに対応づけたフラグに格納される。

40

#### 【0025】

また、上記のような各フラグは、処理結果あるいは設定情報などを示す2値情報が格納されるものである。各フラグに格納される2値情報は、当該フラグが示す状態が第1の状態（たとえば、オン状態）であるか第2の状態（たとえば、オフ状態）であるかを示すものである。また、本実施の形態において、各フラグに格納される2値情報は、複数ビット長の第1のデータ、あるいは、第1のデータとは値が異なる複数ビット長の第2のデータの何れかである。このため、各フラグとしては、第1のデータおよび第2のデータを構成する複数ビットのデータが格納可能なデータ領域が設定される。

50

## 【0026】

まず、各フラグに格納される2値情報としての第1のデータおよび第2のデータについて説明する。

上記のように、各フラグには、処理結果あるいは設定内容などに応じて、複数ビット長の第1のデータあるいは複数ビット長の第2のデータが格納される。第1のデータは、当該フラグが第1の状態（オン状態）であることを示し、第2のデータは、当該フラグが第2の状態（オフ状態）であることを示すものである。各フラグに格納される第1のデータおよび第2のデータは、I Cカード1内のCPU10が識別できるようになっている必要がある。このため、各フラグに格納される第1のデータおよび第2のデータを示す情報は、たとえば、CPU10内のレジスタ10aなどの当該I Cカード1内のメモリに格納される。

10

## 【0027】

また、上記各フラグに格納される第1のデータおよび第2のデータは、任意の値が設定可能である。ここでは、第1のデータおよび第2のデータは、主に、上記乱数生成部14により生成される乱数に基づいて決定されるランダムな値であるものとする。ただし、第1のデータおよび第2のデータは、予め設定されている値（固定値）であっても良い。この場合、第1のデータおよび第2のデータとしての固定値は、たとえば、当該I Cカード1を利用可能な状態とする発行処理時に設定されるようにすれば良い。また、第1のデータおよび第2のデータは、予め設定されている固定値と上記乱数生成部14により生成される乱数に基づいて決定される値であっても良い。この場合、第1のデータおよび第2のデータは、たとえば、予め設定されている固定値と上記乱数生成部14により生成される乱数との排他的論理和などの演算処理により生成することが可能である。

20

## 【0028】

また、第1のデータおよび第2のデータは、それぞれ関連性のない異なる値を設定するようにしても良いし、何れか一方の値から他方の値を算出できるようにしても良い。前者の場合、第1のデータおよび第2のデータがそれぞれ上記I Cカード1内のメモリ（たとえば、レジスタ10a）に記憶される。また、後者の場合、たとえば、第1のデータをI Cカード1内のメモリ（たとえば、レジスタ10a）に記憶しておき、その第1のデータの各ビットの値を反転させた反転値を第2のデータとすることにより実現可能である。なお、以下の説明では、主に、第1のデータを基準値としてCPU10内のレジスタ10aに格納し、第1のデータ（基準値）の反転値を第2のデータとする場合を想定する。

30

## 【0029】

また、第1のデータおよび第2のデータは、任意のタイミングで設定することが可能である。たとえば、I Cカード内で発生させる乱数などに基づいて第1のデータおよび第2のデータを決定する場合、第1のデータおよび第2のデータは、当該I Cカードのリセット処理を行う際に決定するようにしても良いし、コマンドを受信するごとに決定するようにしても良いし、各フラグを初期化する際に決定するようにしても良い。

なお、以下の説明では、I Cカード1は、リセット処理において、上記乱数生成部14が生成する乱数に基づいて第1のデータとしての基準値Rを決定し、第1のデータの反転値を第2のデータとするものとする。また、第1のデータとしての基準値Rは、上記内部レジスタ10aに格納されるものとする。

40

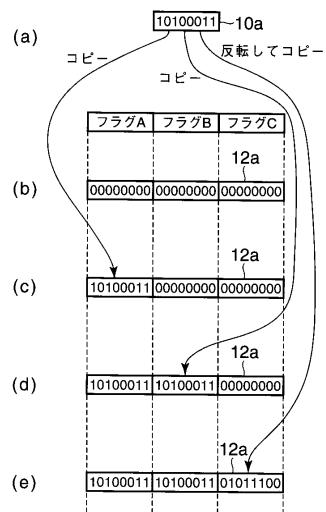

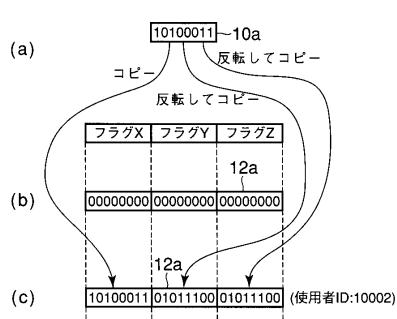

図3(a)は、基準値Rの設定例を示す図である。図3(a)に示す例では、基準値Rとして、8ビットのデータ「10100011」がCPU10の内部メモリとしてのレジスタ10aに格納されている。すなわち、図3(a)に示す例では、外部装置からの電力供給を受けてリセットされたI Cカード1のCPU10は、上記乱数生成部14により乱数を生成させ、生成された乱数に基づく基準値（第1のデータ）Rとして、8ビットのデータ「10100011」をレジスタ10aに格納する。これにより、当該I Cカード1のCPU10は、次に当該I Cカード1がリセットされるまで、レジスタ10aに格納した基準値Rと基準値Rの反転値R'を識別する。

## 【0030】

50

次に、上記各フラグの設定について説明する。

各フラグは、たとえば、ワーキングメモリ12などのICカード1内のメモリ上に設けられる。ここでは、図1に示すように、各フラグは、ワーキングメモリ12上のフラグ領域12aに設定されるものとする。

図3(b)、(c)、(d)、(e)は、フラグ領域12aに設定された3つのフラグA、B、Cの設定例を示す図である。図3(b)は、3つのフラグが初期化された状態を示している。各フラグA、B、Cは、第1のデータおよび第2のデータのデータ長に応じたワーキングメモリ12上の領域が設定される。図3(b)に示す例では、図3(a)に示す基準値R(第1のデータ)および反転値R'(第2のデータ)が8ビットのデータであるため、各フラグは、8ビットのデータが格納可能な領域として設定されている。なお、図3(b)に示す例では、初期化された状態の各フラグには、初期値として「00000000」が格納されている。

#### 【0031】

図3(b)に示すように初期化された各フラグA、B、Cには、図3(c)、(d)、(e)に示すように、処理結果あるいは設定情報などに応じて基準値Rあるいは反転値R'が格納される。たとえば、図3(c)に示す例では、フラグAに基準値R「10100011」が格納された状態を示している。また、図3(d)に示す例では、フラグBに基準値R「10100011」が格納された状態を示している。また、図3(e)に示す例では、フラグCに反転値R'「01011100」が格納された状態を示している。

#### 【0032】

このように、各フラグには、8ビットの第1のデータとしての基準値R、あるいは、8ビットの第2のデータとしての反転値R'が格納される。このようなフラグでは、全てのビットの値が反転させられなければ、状態が変化しない。つまり、上記のようなフラグは、外的な要因により何れかのビットの値が反転させられても、フラグが示す状態が変化しない(ビット異常のエラーとなる)。また、電源にノイズを付加したり、電磁波、光波あるいは温度などのストレスを与えたりしても8ビットのデータを全て反転させるのは、困難であると考えられる。したがって、上記のように、フラグに8ビットのデータを格納することにより、当該ICカードのセキュリティ性を向上させることができる。

#### 【0033】

さらに、上記のように、ICカード1内で発生させる乱数に基づいて基準値Rを決定することにより、基準値Rを推定されにくくすることが可能である。なお、第1のデータとしての基準値Rだけでなく、第2のデータも乱数に基づく値とするようにしても良い。この場合、上記ICカード1では、2つの乱数を発生させ、各乱数に基づいて第1のデータと第2のデータとを設定するようにすれば良い。

#### 【0034】

次に、上記第1の実施の形態に係る第1の処理例について説明する。

この第1の処理例は、コマンドに対応する処理を実行するための種々の実行条件が設定されている場合の処理例である。すなわち、第1の処理例において、上記ICカード1では、外部装置から与えられたコマンドに対応する処理を実行するための種々の実行条件を順次チェックし、それらのチェック結果を順次各フラグに格納する(前処理)。この場合、各実行条件について、実行条件を満たしていれば、対応するフラグに基準値R(第1のデータ)が格納され、実行条件を満たしていなければ、対応するフラグに反転値R'(第2のデータ)が格納されるようになっている。なお、第1の実施の形態として説明する第1の処理例および第2の処理例は、上記CPU10がプログラムメモリ11あるいはデータメモリ13に記憶されているプログラムを実行することにより実現されるものとする。

#### 【0035】

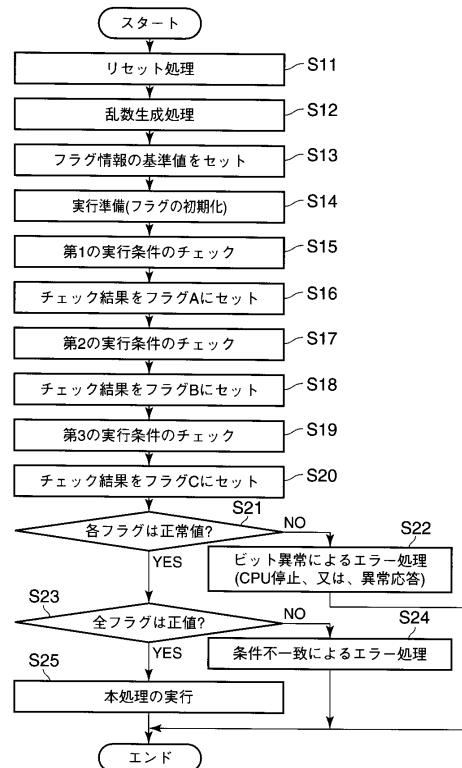

図4は、第1の処理例を説明するためのフローチャートである。

#### 【0036】

上記ICカード1は、上記ICカード処理装置2からの電力の供給を受けて起動するようになっている。上記ICカード処理装置2から電力の供給を受けて起動すると、上記I

10

20

30

40

50

Cカード1のCPU10は、リセット処理を行う（ステップS11）。上記リセット処理が完了すると、上記ICカード1のCPU10は、上記乱数生成部14により乱数を生成する（ステップS12）。上記乱数生成部14により乱数が生成されると、上記ICカード1のCPU10は、生成された乱数に基づいて所定の桁数（ビット数）の基準値（第1のデータ）Rを決定し、決定した基準値Rを内部レジスタ10aに格納する（ステップS13）。たとえば、図3（a）に示す例では、乱数生成部14により発生させた乱数に基づく基準値Rとして「10100011」が決定され、その基準値Rが内部レジスタ10aに格納される

内部レジスタ10aに基準値Rを格納すると、上記CPU10は、ICカード処理装置2からのコマンドに対する処理が実行可能な状態となる。この状態においてICカード処理装置2からコマンドを受信すると、上記CPU10は、当該コマンドの実行準備として、当該コマンドを実行するための実行条件に対応づけたフラグの初期化を行う（ステップS14）。ここで、上記ICカード処理装置2から受信したコマンドには、3つの実行条件が設定されているものとする。このような場合、上記CPU10は、たとえば、図3（b）に示すように、当該コマンドに対応する処理の3つの実行条件に対応する3つのフラグA、B、Cを初期化する。

#### 【0037】

このようなコマンドの実行準備としての各フラグA、B、Cの初期化が完了すると、上記CPU10は、当該コマンドに対応する処理を実行するための各実行条件（第1、第2、第3の実行条件）をチェックする処理（前処理手段）を行う。すなわち、各フラグA、B、Cの初期化が完了すると、上記CPU10は、第1の実行条件をチェックする（ステップS15）。この結果として第1の実行条件を満たすと判定した場合、上記CPU10は、図3（c）に示すように、フラグAに上記内部レジスタ10aに格納している基準値Rを格納する（ステップS16）。なお、第1の実行条件を満たしていないと判定した場合、上記CPU10は、内部レジスタに格納されている基準値Rの各ビットを反転させた値（以下、単に反転値と称する）（第2のデータ）R'をフラグAにセットする（ステップS16）。

#### 【0038】

上記第1の実行条件のチェックが完了すると、上記CPU10は、第2の実行条件をチェックする（ステップS17）。上記第2の実行条件を満たすと判定した場合、上記CPU10は、図3（d）に示すように、内部レジスタ10aに格納している基準値RをフラグBに格納する（ステップS18）。また、上記第2の実行条件を満たさないと判定した場合、上記CPU10は、上記反転値R'をフラグBにセットする（ステップS18）。

#### 【0039】

同様に、上記第2の実行条件のチェックが完了すると、上記CPU10は、第3の実行条件をチェックする（ステップS19）。上記第3の実行条件を満たすと判定した場合、上記CPU10は、フラグBに内部レジスタに格納した基準値Rを格納する（ステップS20）。また、上記第3の実行条件を満たさないと判定した場合、上記CPU10は、図3（e）に示すように、上記反転値R'をフラグCにセットする（ステップS20）。

#### 【0040】

全ての実行条件のチェックが完了すると、上記CPU10は、各フラグA、B、Cの値が基準値Rまたは反転値R'であるか否かを判定する（ステップS21）。これは、各フラグA、B、Cに格納されている値が正常な値であるか否かを判定する処理である。上記のような処理が正常に実行され、かつ、外的な要因などで値が変化させられていなければ、各フラグA、B、Cには、基準値Rまたは反転値R'が格納されているはずである。したがって、何れかのフラグA、B、Cに基準値Rまたは反転値R'以外の値が格納されている場合、何かの異常がICカード内で発生したものと判断できる。すなわち、外的な要因によりフラグA、B、Cの値が変更された場合、フラグA、B、Cの値は、基準値Rまたは反転値R'以外に値になることが予測される。言い換えると、各フラグの値が基準値Rまたは反転値R'であれば、各実行条件のチェックが正常に実行されたものと判定でき

10

20

30

40

50

る。

【0041】

上記判定により基準値 R または反転値 R' 以外の値がフラグに格納されていると判定した場合 (ステップ S21、NO)、上記 C P U 10 は、フラグ内のビット異常が発生したものと判定し、動作を停止するなどのエラー処理を行う (ステップ S22)。この場合、外的な要因により異常となったことが考えられる。このため、上記 C P U 10 は、セキュリティ確保のために、エラー処理として、強制的に動作を停止するようとする。

また、上記判定により各フラグが基準値 R または反転値 R' であると判定した場合 (ステップ S21、YES)、上記 C P U 10 は、各フラグの値が全て基準値 R であるか否かを判定する (ステップ S23)。これは、コマンドに応じた処理の全ての実行条件を満たしているか否かを判定する処理である。

【0042】

すなわち、上記判定により何れかのフラグが基準値 R でないと判定した場合 (ステップ S23、NO)、上記 C P U 10 は、I C カード処理装置 2 に実行条件が満たされていない旨のレスポンスを出力するなどのエラー処理を行う (ステップ S24)。この場合、当該 I C カード 1 内の動作異常ではないと考えられる。このため、上記 C P U 10 は、通常のエラー処理を行う。

また、上記判定により各フラグ A、B、C の値が全て基準値 R であると判定した場合 (ステップ S23、YES)、上記 C P U 10 は、I C カード処理装置 2 から受信したコマンドに応じた本処理を実行する (ステップ S25)。

【0043】

上記のような第 1 の処理例では、コマンドを実行するための種々の実行条件に対応づけた複数ビットからなるフラグを設定し、各フラグには乱数に基づいて決定した複数ビットの基準値あるいは上記基準値に対する反転値の何れかを各実行条件のチェック結果としてセットする。これにより、各フラグに記憶されている情報に基づいて、実行の可否を判定できる。また、各フラグが複数ビットからなっているため、外的なエネルギーでフラグとして利用するメモリ領域の一部のビットの値を反転されても、フラグ全体が示す状態が反転することなく、ビット異常としてエラー処理することが可能となる。

【0044】

次に、上記第 1 の実施の形態としての第 2 の処理例について説明する。

この第 2 の処理例では、設定情報をフラグに格納し、フラグに格納されている情報に基づいて各種の処理を実行する場合の処理例である。ここでは、各種のデータのアクセス権を示す情報をフラグに格納する処理 (前処理) を実行し、各フラグに格納しているアクセス権に従ってデータの出力処理を行う処理例について説明する。また、アクセス可能なデータに対応するフラグには基準値 R (第 1 のデータ) が格納され、アクセスが禁止されているデータに対応するフラグには反転値 R' (第 2 のデータ) が格納されるものとする。

【0045】

次に、上記 I C カード 1 における複数の使用者に対する各種のデータへのアクセス権の設定例について説明する。ここでは、当該 I C カード 1 には、複数の使用者ごとに各種のデータに対するアクセス権が設定されているものとする。

図 5 は、複数の使用者ごとの各種のデータに対するアクセス権を示す情報を記憶するデータテーブル 13a の例を示す図である。図 5 に示す例では、各使用者ごとに、各使用者の識別情報としての I D、各使用者のパスワード、各データ X、Y、Z に対するアクセスの可否を示す情報が格納されている。上記 I D は、各使用者を識別するための識別情報であり、上記パスワードは、各使用者に与えられている認証情報である。これにより、上記 C P U 10 は、上記データテーブル 13a を参照して、上記 I D および上記パスワードにより使用者が特定 (認証) できる。また、上記のようなデータテーブル 13a を参照して、上記 C P U 10 は、認証が成功した使用者に対する各データ X、Y、Z へのアクセス権が判別できるようになっている。

【0046】

10

20

30

40

50

また、図6は、フラグ領域12aに設けたフラグによるアクセス権の設定例を示す図である。図6(a)は、図3(a)と同様に、基準値Rの設定例を示す図である。

#### 【0047】

図6(b)、(c)は、フラグ領域12aに設定された3つのフラグX、Y、Zの設定例を示す図である。図6(b)は、3つのデータXYZに対応づけた3つのフラグX、Y、Zが初期化された状態を示している。ここで、各フラグX、Y、Zは、それぞれデータX、Y、Zに対するアクセス権を示すものとする。各フラグX、Y、Zは、基準値(第1のデータ)および反転値(第2のデータ)のデータ長に応じてワーキングメモリ12上のフラグ領域12aに設定される。図6(b)に示す例では、図6(a)に示す基準値R(第1のデータ)および反転値R'(第2のデータ)が8ビットのデータであるため、各フラグX、Y、Zは、8ビットのデータが格納可能な領域として設定されている。なお、図6(b)に示す例では、初期化された状態の各フラグには、初期値として「00000000」が格納されている。

10

#### 【0048】

図6(b)に示すように初期化された各フラグA、B、Cには、図3(c)に示すように、各データへのアクセス権に応じて基準値Rあるいは反転値R'が格納される。たとえば、図6(c)に示す例では、図5に示す使用者ID「10002」の使用者に対する各データへのアクセス権を反映したものとなっている。すなわち、図5に示す例では、ID「10002」の使用者は、データXへのアクセスが許可され、データY、Zへのアクセスが禁止されている。このため、図6(c)に示す例では、フラグXに基準値R「10100011」が格納され、フラグYおよびフラグZに反転値R'「01011100」が格納されている。つまり、図6(c)に示す例では、基準値RがセットされたフラグXに対応するデータXへのアクセスが許可され、反転値R'がセットされたフラグY、Zに対応するデータY、Zへのアクセスが禁止されていることを示している。

20

#### 【0049】

次に、上記第2の処理例の流れについて説明する。

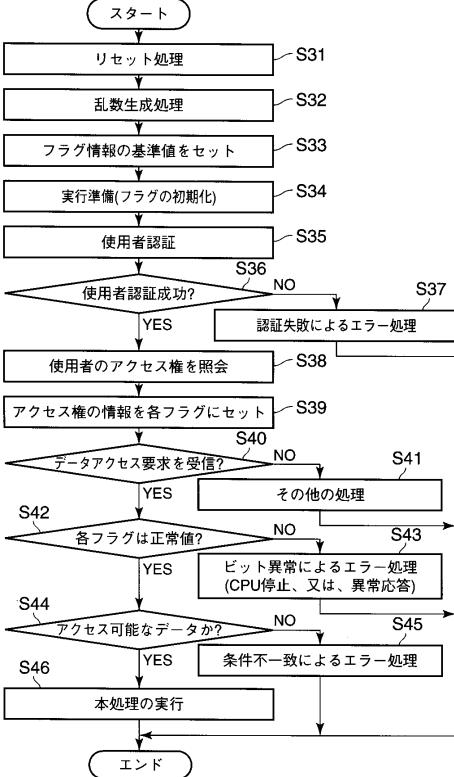

図7は、第2の処理例の流れを説明するためのフローチャートである。

すなわち、上記ICカード処理装置2から電力供給を受けて起動すると、上記ICカード1のCPU10は、リセット処理を行う(ステップS31)。上記リセット処理が完了すると、上記ICカード1のCPU10は、上記乱数生成部14により乱数を生成する(ステップS32)。上記乱数生成部14により乱数が生成されると、上記ICカード1のCPU10は、生成された乱数に基づいて所定の桁数(ビット数)の基準値(第1のデータ)Rを決定し、決定した基準値Rを内部レジスタ10aに格納する(ステップS33)。

30

#### 【0050】

上記内部レジスタ10aに基準値Rを格納すると、上記CPU10は、各コマンドの実行準備として、各種のデータへのアクセス権を示すフラグの初期化を行う(ステップS34)。ここでは、例として、使用者ごとに設定されている3つのデータX、Y、Zに対するアクセス権をフラグX、Y、Zで示すものとする。このような場合、上記CPU10は、3つのデータX、Y、Zへのアクセス権を示す3つのフラグX、Y、Zを初期化する。

40

#### 【0051】

各フラグX、Y、Zの初期化が完了すると、上記CPU10は、まず、使用者を特定するための使用者の認証処理を行う(ステップS35)。ここでは、使用者が指定するIDおよびパスワードにより使用者認証を行うものとする。たとえば、IDおよびパスワードは、使用者がICカード処理装置2に接続された操作部により入力し、認証コマンドとともにICカードへ供給されるものとする。IDおよびパスワードを取得すると、当該ICカード1のCPU10は、取得したIDおよびパスワードと上記データテーブル13aに記憶されている各使用者のIDおよびパスワードと照合する。このような照合処理により使用者が特定される。なお、使用者が特定できない場合、つまり、使用者認証が失敗した場合(ステップS36、NO)、上記CPU10は、使用者認証の失敗に伴うエラー処理

50

を実行する(ステップS37)。

#### 【0052】

上記使用者認証により使用者が特定されると(ステップS36、YES)、上記CPU10は、アクセス権の設定処理(前処理手段)として、当該使用者の各データに対するアクセス権を上記データテーブル13aにより照会し(ステップS38)、上記データテーブル13aにおける設定内容に従って各フラグに基準値Rまたは反転値R'をセットする(ステップS39)。つまり、各データへのアクセス権を示す各フラグには、当該使用者のアクセス権に応じた値がセットされる。たとえば、アクセス可能なデータに対応するフラグには、基準値Rがセットされ、アクセスが禁止されているデータに対応するフラグには、反転値R'がセットされる。

10

#### 【0053】

上記のような各フラグにアクセス権を示す値をセットした状態において、上記CPU10は、データのアクセスを要求するコマンドを受信した場合(ステップS40、YES)、各データへのアクセスをフラグの状態に応じて制御する。すなわち、データへのアクセス要求を受けた場合、上記CPU10は、まず、各フラグX、Y、Zが正常な値であるか否かを判定する(ステップS42)。これは、上記CPU10は、各フラグX、Y、Zの値が基準値Rまたは反転値R'であるか否かを判定する処理である。すなわち、外的な要因などでフラグの値が変化させられていなければ、各フラグX、Y、Zには、基準値Rまたは反転値R'が格納されているはずである。したがって、何れかのフラグX、Y、Zに基準値Rまたは反転値R'以外の値が格納されている場合、何かの異常がICカード内で発生したものと判断できる。

20

#### 【0054】

上記判定により基準値Rまたは反転値R'以外の値がフラグに格納されていると判定した場合(ステップS42、NO)、上記CPU10は、フラグ内のビット異常が発生したものと判定し、エラー処理を行う(ステップS43)。この場合、外的な要因によりフラグ内のビット異常が発生した可能性が考えられる。このため、上記CPU10は、たとえば、セキュリティ確保のために、エラー処理として、強制的に動作を停止するようにする。また、上記CPU10は、エラー処理として、データへのアクセスを行わずに、ビット異常を示す応答を送信する処理のみを行うようにしても良い。

30

#### 【0055】

また、上記判定により各フラグが基準値Rまたは反転値R'であると判定した場合(ステップS42、YES)、上記CPU10は、アクセスが要求されているデータがアクセス可能なデータであるか否かを判定する(ステップS44)。これは、アクセスが要求されているデータに対応するフラグが基準値R(アクセス可能な状態であることを示す第1のデータ)であるか否かを判定する処理である。

#### 【0056】

上記判定によりアクセスが要求されたデータがアクセス可能なデータでないと判定した場合、つまり、当該データに対応するフラグの値が反転値R'である場合(ステップS44、NO)、上記CPU10は、アクセスが要求されたデータに対するアクセス権がない旨のレスポンスを出力するなどのエラー処理を行う(ステップS44)。この場合、当該ICカード1内の動作異常ではないと考えられる。このため、上記CPU10は、通常のエラー処理を行う。

40

また、上記判定によりアクセスが要求されたデータがアクセス可能なデータであると判定した場合、つまり、当該データに対応するフラグの値が基準値Rである場合(ステップS44、YES)、上記CPU10は、ICカード処理装置2から受信したコマンドに応じた本処理を実行する(ステップS46)。

#### 【0057】

上記のような第2の処理例では、アクセス権が設定されている各種のデータに対応づけて複数ビットからなるフラグを設定し、上記各フラグには使用者認証により特定された使用者のアクセス権を示す情報として、乱数に基づいて決定した複数ビットの基準値あるい

50

は上記基準値に対する反転値の何れかをセットする。これにより、各フラグに記憶されている情報に基づいて、各データへのアクセス権を判定できる。また、各フラグが複数ビットからなっているため、外的な要因でフラグとして利用するメモリ領域の一部のビットの値を反転されても、フラグ全体が示す状態が反転する事なく、ビット異常としてエラー処理することが可能となる。

#### 【0058】

次に、第2の実施の形態について説明する。

本第2の実施の形態では、上記CPU内のハードウェア構成によって、上記第1の実施の形態で説明したような処理におけるフラグによる制御を実現するものである。すなわち、第2の実施の形態は、たとえば、上記第1の実施の形態で説明したステップS21およびS23の処理、あるいは、ステップS12およびS13の処理などをCPU内のハードウェア構成によって実現するものである。

10

#### 【0059】

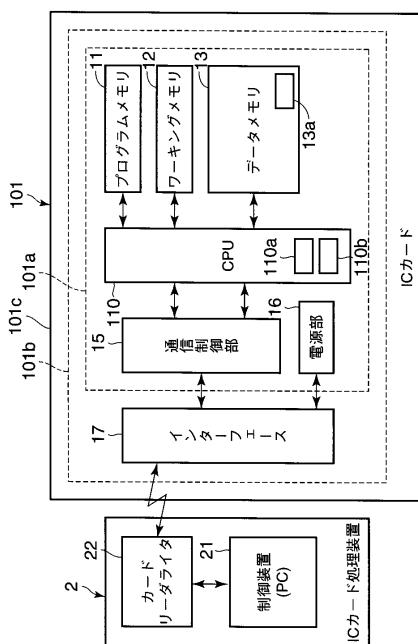

図8は、第2の実施の形態に係る携帯可能電子装置としてのICカード101およびICカード101を含むICカードシステムの構成例を示すブロック図である。

図8に示すICカード101およびICカードシステムは、図1に示すICカード1およびICカードシステムとほぼ同様な機能を有している。このため、図8に示すICカード101およびICカードシステムにおいて、図1に示すICカード1と同様な構成については、同一箇所に同一符号を付して詳細な説明を省略するものとする。なお、上記ICカード101は、ICチップ101aを有するモジュール101bが埋設された本体101cにより構成されている。

20

#### 【0060】

図8に示すICカード101と図1に示すICカード1とでは、主に、CPU110内の構成が異なっている。つまり、第2の実施の形態に係るICカード101では、上記第1の実施の形態で説明したようなフラグによる制御（たとえば、図4のステップS21、S23の処理、あるいは、図7のステップS42、S44の処理）を実現するための構成を主としてCPU110内のハードウェア構成によって実現している。

#### 【0061】

図8に示すCPU110は、レジスタ110aおよびロジック回路110bなどを有している。上記レジスタ110aは、各種のステータスフラグ、あるいは、各ステータスフラグにセットすべき基準値などが記憶されるようになっている。なお、上記基準値は、上記第1の実施の形態で説明したような複数ビット長のデータ（第1のデータ）である。また、本第2の実施の形態では、上記第1の実施の形態と同様に、上記基準値の各ビットを反転させた反転値を第2のデータとするものとする。ただし、第2のデータを反転値以外の値とする場合、第2のデータも上記レジスタ110aに格納される。

30

#### 【0062】

上記ロジック回路110bは、上記レジスタ110aに設けられた各種のステータスフラグにセットされているデータを処理するためのハードウェアにより構成される。上記ロジック回路110bは、たとえば、各ステータスフラグの値と基準値および反転値を比較する比較回路などを有している。なお、上記レジスタ110aおよび上記ロジック回路110bについては、後で詳細に説明するものとする。

40

#### 【0063】

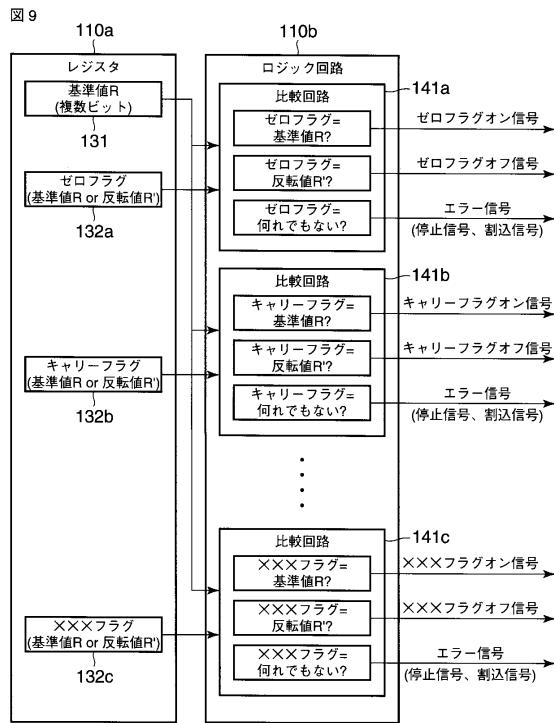

次に、上記CPU110内の第1の構成例について説明する。

#### 【0064】

図9は、上記CPU110内の第1の構成例を示す図である。

図9に示す構成例では、上記CPU110内のレジスタ110aに設定データ領域131とステータスフラグ領域132とが設けられている。また、図9に示す構成例では、各種のステータスフラグとして、ゼロフラグ132a、キャリーフラグ132b、×××フラグ132c、…が上記ステータスフラグ領域132に設けられている。また、図9に示す構成例では、上記設定データ領域131には、予め決定されている1つの基準値Rが記

50

憶されているものとする。従って、各ステータスフラグ 132a、132b、132c、...には、上記基準値 R あるいはその反転値 R' の何れかの値が格納されるようになっている。

#### 【0065】

上記 CPU110 内のロジック回路 110b には、各ステータスフラグ 132a、132b、132c、...に対応する複数の比較回路 141a、141b、141c、...が設けられている。上記比較回路 141a、141b、141c、...は、各ステータスフラグの値に対して、基準値 R および反転値 R' を比較し、その比較結果を出力する。

#### 【0066】

たとえば、上記比較回路 141a (141b、141c、...) は、ステータスフラグ 132a (132b、132c、...) の値が基準値 R と一致する場合、ステータスフラグ 132a (132b、132c、...) が第1の状態（オンの状態）であることを示すオン信号を出力する。また、上記比較回路 141a (141b、141c、...) は、ステータスフラグ 132a (132b、132c、...) の値と反転値 R' とが一致する場合、ステータスフラグ 132a (132b、132c、...) が第2の状態（オフの状態）であることを示すオフ信号を出力する。また、上記比較回路 141a (141b、141c、...) は、ステータスフラグ 132a (132b、132c、...) の値が基準値 R 及び反転値 R' の何れとも一致しない場合、ステータスフラグ 132a (132b、132c、...) がエラー状態であることを示すエラー信号を出力するようになっている。

#### 【0067】

また、上記エラー信号は、各ステータスフラグにおけるビット異常が検出された場合に出力される信号である。このため、上記エラー信号は、各ステータスフラグにおけるビット異常に伴う動作を指示する信号であっても良い。たとえば、フラグのビット異常が検出された場合に CPU110 の動作を強制的に停止させる形態では、エラー信号として、CPU110 の動作を停止させるための信号（停止信号）を出力する。これにより、ステータスフラグにおけるビット異常が検出された場合、強制的に CPU110 の動作を停止させることができる。この結果として、外的な要因による不正な動作を防止できる。

#### 【0068】

また、ステータスフラグにおけるビット異常が検出された場合に CPU110 が優先的（強制的）にステータスフラグにおけるビット異常に伴う所定の処理（エラー処理）を実行する形態では、エラー信号として、CPU110 の演算部にステータスフラグにおけるビット異常に伴う所定のエラー処理を優先的に実行させるための割り込み信号を出力する。これにより、上記 CPU110 は、ステータスフラグにおけるビット異常が検出された場合に、優先的に CPU110 がビット異常の伴う所定のエラー処理を実行するようになる。この結果として、外的な要因による不正な動作を防止できる。

#### 【0069】

上記のように、第1の構成例の CPU110 には、各ステータスフラグ 132a、132b、132c、...に対応づけた比較回路 141a、141b、141c、...が設けられ、各比較回路 141a、141b、141c、...が各ステータスフラグ 132a、132b、132c、...の状態（オン、オフ、エラーの何れかであるか）を示す信号を出力する。このような処理は、上記第1の実施の形態で説明した図4のステップ S21 および S23 の処理あるいは図7のステップ S42 および S44 の処理に相当する処理である。言い換えると、第1の構成例では、CPU110 内のハードウェア構成により、複数ビットからなる基準値が格納されるフラグのチェック処理を実現している。これにより、第1の構成例では、ステータスフラグを参照すべき処理において、複数ビット化された各ステータスフラグのチェック処理などを高速化することができる。また、上記第1の構成例では、CPU 内のハードウェア構成によってステータスフラグの状態（オン、オフ、エラー）を機械的に出力することができるため、CPU 内の演算部（図示しない）によるソフトウェア処理に負荷をかけることなく、ステータスフラグによる制御を効率的に実現できる。

#### 【0070】

10

20

30

40

50

次に、第2の実施の形態に係る上記CPU110内の第2の構成例について説明する。

【0071】

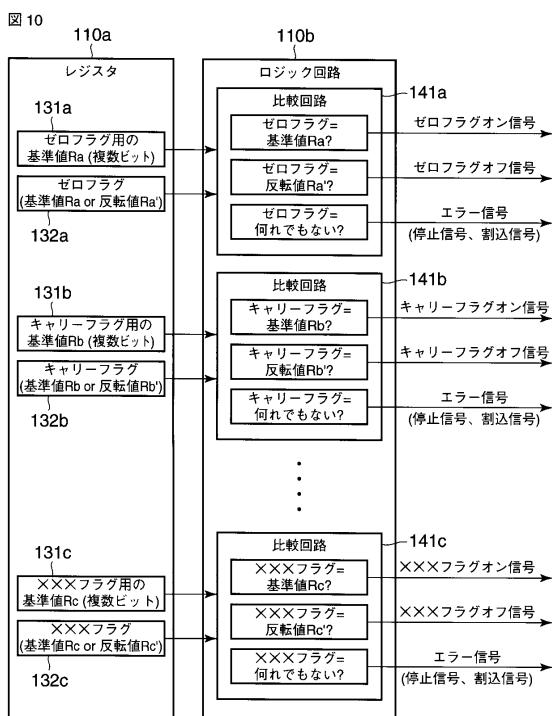

図10は、上記CPU110内の第2の構成例を示す図である。

図10に示す構成例では、上記CPU110内のレジスタ110aの設定データ領域131には、各種のステータスフラグに対する複数の基準値を格納するための複数の基準値格納領域131a、131b、131c、…が設けられている。また、上記CPU110内のレジスタ110aのステータスフラグ領域132には、図9に示す第1の構成例と同様に、各種のステータスフラグとして、ゼロフラグ132a、キャリーフラグ132b、×××フラグ132c、…が設けられている。つまり、図10に示す第2の構成例では、各ステータスフラグごとに基準値が設定されている。

10

【0072】

たとえば、図10に示す構成例では、各基準値格納領域131a、131b、131c、…は、それぞれゼロフラグ132a、キャリーフラグ132b、×××フラグ132c、…に対応づけられ、ゼロフラグ132aに基準値としてセットすべき値、キャリーフラグ132bに基準値としてセットすべき値、×××フラグ132cに基準値としてセットすべき値が格納されている。つまり、各ステータスフラグ132a、132b、132cには、それぞれ対応する基準値格納領域131a、131b、131cに格納されている基準値Ra、Rb、Rcあるいはその反転値Ra'、Rb'、Rc'の何れかの値が格納されるようになっている。

【0073】

20

すなわち、図9に示す第1の構成例では、各ステータスフラグに格納すべき基準値を共通の値としたのに対して、図10に示す第2の構成例では、各ステータスフラグごとに基準値を設定するようにしたものである。なお、図10に示す構成例において、一部の基準値を共通化するようにしても良い。上記のような第2の構成例によれば、特定のステータスフラグに対応する基準値が第3者に推定された場合であっても、全てのステータスフラグに対する基準値が推定されることはなく、安全性を高めることが可能となる。

【0074】

また、図10に示す第2の構成例において、上記CPU110内のロジック回路110bには、図9に示す第1の構成例と同様に、各ステータスフラグ132a、132b、132c、…に対応する複数の比較回路141a、141b、141c、…が設けられている。上記比較回路141a、141b、141c、…は、各ステータスフラグの値に対して、対応する各基準値Ra、Rb、Rcおよび各基準値Ra'、Rb'、Rc'の反転値Ra'、Rb'、Rc'を比較し、その比較結果を出力する。

30

【0075】

たとえば、上記比較回路141a(141b、141c、… )は、ステータスフラグ132a(132b、132c、… )の値が基準値格納領域131a(131b、131c、… )に格納されている基準値Ra(Rb、Rc、… )と一致する場合、ステータスフラグ132a(132b、132c、… )が第1の状態(オンの状態)であることを示すオン信号を出力する。また、上記比較回路141a(141b、141c、… )は、ステータスフラグ132a(132b、132c、… )の値と基準値格納領域131a(131b、131c、… )に格納されている基準値の反転値Ra'(Rb'、Rc'、… )とが一致する場合、ステータスフラグ132a(132b、132c、… )が第2の状態(オフの状態)であることを示すオフ信号を出力する。また、上記比較回路141a(141b、141c、… )は、ステータスフラグ132a(132b、132c、… )の値が基準値Ra(Rb、Rc、… )及び反転値Ra'(Rb'、Rc'、… )の何れとも一致しない場合、ステータスフラグ132a(132b、132c、… )がエラー状態であることを示すエラー信号を出力するようになっている。

40

【0076】

なお、ステータスフラグにおけるビット異常が検出された場合のエラー信号としては、上述した第1の構成例と同様に、CPU110を強制的に停止させるための停止信号を出

50

力するようにしても良いし、ステータスフラグにおけるビット異常に伴う所定のエラー処理を優先的に実行させるための割り込み信号を出力するようにしても良い。これにより、上記 C P U 1 1 0 は、ステータスフラグにおけるビット異常が検出された場合に、強制的（優先的）に停止したり、ビット異常の伴う所定のエラー処理を実行したりすることができる。この結果として、外的な要因による不正な動作を防止できる。

【0077】

上記のように、第2の構成例の C P U 1 1 0 には、各ステータスフラグ 1 3 2 a、1 3 2 b、1 3 2 c、…に対応づけた基準値格納領域 1 3 1 a、1 3 b、1 3 1 c をレジスタに設け、さらに、各ステータスフラグと基準値とに対応づけた比較回路 1 4 1 a、1 4 1 b、1 4 1 c、…をロジック回路に設けられている。上記 C P U 1 1 0 では、各比較回路 1 4 1 a、1 4 1 b、1 4 1 c、…がそれぞれ基準値格納領域 1 3 1 a、1 3 b、1 3 1 c の値と各ステータスフラグ 1 3 2 a、1 3 2 b、1 3 2 c、…の値とを比較することにより、各ステータスフラグ 1 3 2 a、1 3 2 b、1 3 2 c、…の状態（オン、オフ、エラーの何れかであるか）を示す信号を出力する。上記のような処理は、上記第1の実施の形態で説明した図4のステップ S 2 1 および S 2 3 の処理あるいは図7のステップ S 4 2 および S 4 4 の処理に適用可能である。

【0078】

言い換えると、上記第2の構成例では、C P U 内のハードウェア構成により各フラグごとに設定されている複数ビットからなる基準値に基づくフラグの制御を実現している。これにより、上記第2の構成例では、複数ビット化された基準値が各ステータスフラグごとに設定されている場合であっても、ソフトウェア制御による負荷をかけることなく、各ステータスフラグのチェック処理などを高速に実行することができる。

【0079】

次に、上記 C P U 1 1 0 内の第3の構成例について説明する。

【0080】

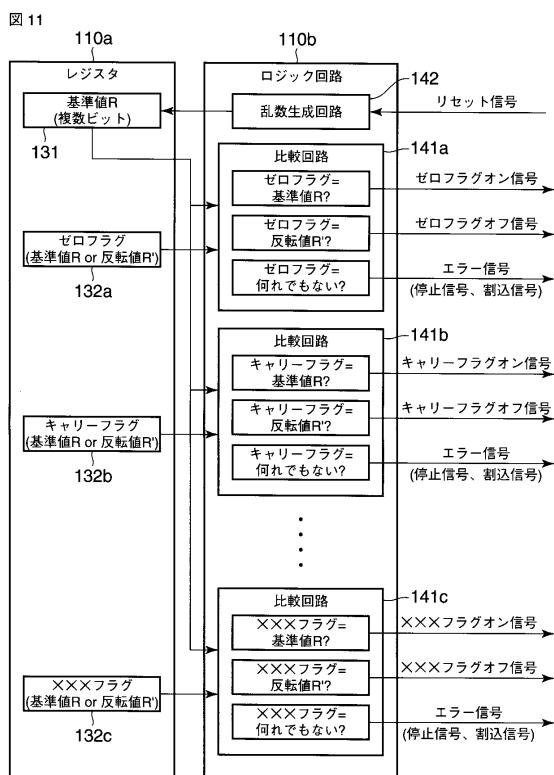

図11は、上記 C P U 1 1 0 内の第3の構成例を示す図である。

図11に示す第3の構成例では、図9に示す第1の構成例に加えて、上記 C P U 1 1 0 内のロジック回路 1 1 0 b に乱数生成回路 1 4 2 が追加されている。上記乱数生成回路 1 4 2 は、リセット信号を受けて乱数を生成し、生成した乱数を基準値 R としてレジスタ 1 1 0 a 内の設定データ領域 1 3 1 に格納する。上記設定データ領域 1 3 1 に基準値 R が設定された状態では、上述した図9に示す第1の構成例と同様な動作を行う。

【0081】

すなわち、図11に示す第3の構成例では、当該 I C カード 1 0 1 がリセットされるごとに、ロジック回路 1 1 0 b 内の乱数生成回路 1 4 2 が乱数を生成し、生成した乱数に基づく基準値 R が設定データ領域 1 3 1 に格納されるようになっている。なお、乱数生成回路 1 4 2 が乱数を生成し、生成した乱数に基づく基準値を設定データ領域 1 3 1 に格納する処理は、リセット時に実行することに限定されるものではなく、たとえば、コマンドを受信するごとなどの任意のタイミングで実現することも可能である。なお、第3の構成例による乱数に基づく基準値の設定処理は、たとえば、第1の実施の形態で説明した図4のステップ S 1 1 ~ S 1 3 の処理あるいは図7のステップ S 3 1 ~ S 3 3 の処理に適用可能である。

【0082】

上記のように、第3の構成例では、設定データ領域 1 3 1 に格納される基準値がリセットされるごとに任意のデータに変更されるため、基準値が第3者に特定されるリスクを軽減し、第3者が種々の解析手法で基準値を推定したとしても、その基準値をリセット時に無効とすることが可能となる。この結果として、上記第3の構成例によれば、I C カードのセキュリティ性を向上させることができる。さらに、上記第3の構成例では、乱数により基準値を設定する処理、および、ステータスフラグのチェック処理などをハードウェアにより実行するため、I C カードにおける処理の高速化および効率化が期待できる。

【0083】

10

20

30

40

50

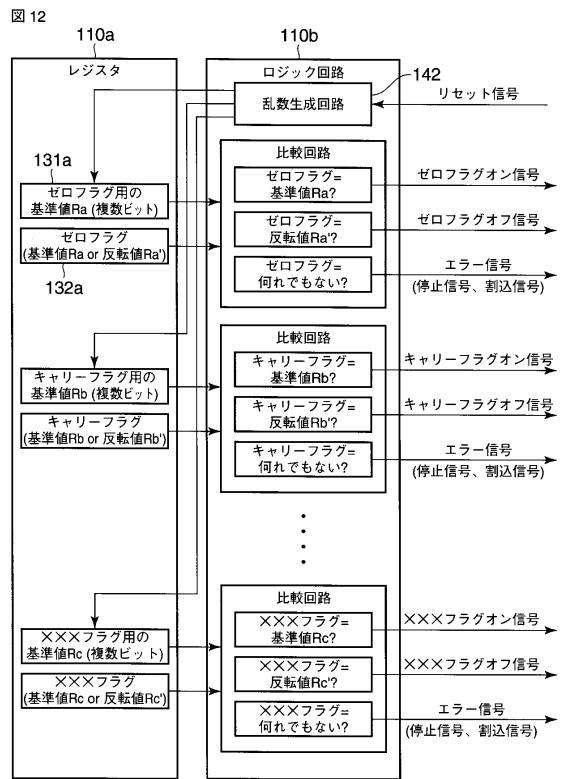

次に、上記 C P U 1 1 0 内の第 4 の構成例について説明する。

図 1 2 は、上記 C P U 1 1 0 内の第 4 の構成例を示す図である。

図 1 2 に示す第 4 の構成例では、図 1 0 に示す第 2 の構成例に加えて、上記 C P U 1 1 0 内のロジック回路 1 1 0 b に乱数生成回路 1 4 2 が追加されている。上記乱数生成回路 1 4 2 は、リセット信号を受けて各基準値格納領域 1 3 1 a、1 3 1 b、1 3 1 c、...ごとに乱数を生成し、生成した各乱数を基準値 R a、R b、R c としてレジスタ 1 1 0 a 内の各基準値格納領域 1 3 1 a、1 3 1 b、1 3 1 c、...に格納する。各基準値格納領域 1 3 1 a、1 3 1 b、1 3 1 c、...に基準値 R a、R b、R c が設定された状態において、上記第 4 の構成例では、上述した第 2 の構成例と同様な動作を行う。

【 0 0 8 4 】

10

すなわち、図 1 2 に示す第 4 の構成例では、当該 I C カード 1 0 1 がリセットされるごとに、ロジック回路 1 1 0 b 内の乱数生成回路 1 4 2 が各基準値となる乱数をそれぞれ生成し、生成した乱数に基づく各基準値 R a、R b、R c、...が各基準値格納領域 1 3 1 a、1 3 1 b、1 3 1 c、...に格納されるようになっている。なお、乱数生成回路 1 4 2 が各基準値用の乱数を生成し、生成した乱数に基づいて各基準値を各基準値格納領域に格納する処理は、リセット時に実行することに限定されるものではなく、たとえば、コマンドを受信するごとなどの任意のタイミングで実現することも可能である。また、第 4 の構成例による乱数に基づく基準値の設定処理は、たとえば、第 1 の実施の形態で説明した図 4 のステップ S 1 1 ~ S 1 3 の処理あるいは図 7 のステップ S 3 1 ~ S 3 3 の処理に適用可能である。

20

【 0 0 8 5 】

上記のように、第 4 の構成例では、各基準値格納領域 1 3 1 a、1 3 1 b、1 3 1 c、...に格納される基準値 R a、R b、R c、...がリセットされるごとに任意のデータに変更される。このため、第 4 の構成例では、各ステータスフラグごとに基準値を設定することにより何れかの基準値が第 3 者に解析された場合のリスクを軽減するだけでなく、基準値が第 3 者に特定されるリスクを軽減し、第 3 者が種々の解析手法で基準値を推定したとしても、その基準値をリセット時に無効とすることが可能となる。この結果として、上記第 4 の構成例によれば、I C カードのセキュリティ性を向上させることができる。さらに、上記第 4 の構成例では、乱数により各基準値を設定する処理、および、ステータスフラグのチェック処理などをハードウェアにより実行するため、I C カードにおける処理の高速化および効率化が期待できる。

30

【 図面の簡単な説明 】

【 0 0 8 6 】

【 図 1 】第 1 の実施の形態に係る I C カードおよび I C カードを含むシステムの構成例を示すブロック図。

【 図 2 】非接触式 I C カードの全体の構成例を示す図。

【 図 3 】実行条件のチェック結果を示す各フラグの設定例を示す図。

【 図 4 】第 1 の実施の形態としての第 1 の処理例の流れを説明するためのフローチャート。

【 図 5 】各使用者に対する各種データへのアクセス権を示すデータテーブルの構成例を示す図。

40

【 図 6 】各種データへのアクセス権を示す各フラグの設定例を示す図。

【 図 7 】第 1 の実施の形態としての第 1 の処理例の流れを説明するためのフローチャート。

【 図 8 】第 2 の実施の形態に係る I C カードおよび I C カードを含むシステムの構成例を示すブロック図。

【 図 9 】第 2 の実施の形態に係る I C カードの C P U における第 1 の構成例を示す図。

【 図 1 0 】第 2 の実施の形態に係る I C カードの C P U における第 2 の構成例を示す図。

【 図 1 1 】第 2 の実施の形態に係る I C カードの C P U における第 3 の構成例を示す図。

【 図 1 2 】第 2 の実施の形態に係る I C カードの C P U における第 4 の構成例を示す図。

50

## 【符号の説明】

## 【0087】

R、R<sub>a</sub>、R<sub>b</sub>、R<sub>c</sub>...基準値(第1のデータ)、R'、R<sub>a'</sub>、R<sub>b'</sub>、R<sub>c'</sub>...反転値(第2のデータ)、1、101...ICカード(携帯可能電子装置)、1a、101a...ICチップ、1b、101b...モジュール、1c、101c...本体、2...ICカード処理装置、10、110...CPU(判断手段、実行手段、停止手段、エラー処理手段)、10a、110a...レジスタ(第1の記憶手段)、11...プログラムメモリ、12...ワーキングメモリ、12a...フラグ領域(第2の記憶手段)、13...データメモリ(第3の記憶手段)、13a...データテーブル、14...乱数生成部(乱数生成手段)、15...通信制御部、16...電源部、17...インターフェース、110b...ロジック回路、131...設定データ領域(第1の記憶手段)、131a、131b、131c...基準値格納領域(第1の記憶手段)、132...ステータスフラグ領域(第2の記憶手段)、132a、132b、132c...ステータスフラグ(ゼロフラグ、キャリーフラグ、×××フラグ)(第2の記憶手段)、141a、141b、141c...比較回路(判断手段)、142...乱数生成回路(乱数生成手段)

10

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

| 使用者ID | パスワード | アクセス可否 |      |      | 13a |

|-------|-------|--------|------|------|-----|

|       |       | データX   | データY | データZ |     |

| 10001 | ***** | ○      | ×    | ×    |     |

| 10002 | ***** | ○      | ×    | ×    |     |

| 10003 | ***** | ○      | ×    | ×    |     |

| 20001 | ***** | ○      | ○    | ○    |     |

| 30001 | ***** | ○      | ○    | ○    |     |

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 関谷 哲

神奈川県川崎市幸区小向東芝町1番地 東芝ソシオシステムズ株式会社内

審査官 和田 財太

(56)参考文献 国際公開第2005/027403 (WO, A1)

特開2005-149438 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 K 19/073

G 06 F 12/16

G 06 F 21/02