등록특허 10-2377668

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년03월22일

(11) 등록번호 10-2377668

(24) 등록일자 2022년03월18일

- (51) 국제특허분류(Int. Cl.)

*H01L 43/02* (2006.01) *H01L 43/12* (2006.01)

- (52) CPC특허분류

*H01L 43/02* (2013.01)

*H01L 43/12* (2021.01)

- (21) 출원번호 10-2015-0011133

(22) 출원일자 2015년01월23일

심사청구일자 2020년01월20일

(65) 공개번호 10-2015-0112757

(43) 공개일자 2015년10월07일

(30) 우선권주장

61/971,032 2014년03월27일 미국(US)

14/325,190 2014년07월07일 미국(US)

## (56) 선행기술조사문헌

JP2006060172 A\*

JP2012038815 A\*

JP2013016587 A\*

KR1020130007638 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

램 리씨치 코포레이션

미국 94538 캘리포니아주 프레몬트 쿠싱 파크웨이

4650

(72) 발명자

탄 사만다 에스.에이치.

미국, 캘리포니아 94555, 프레몬트, 탄 오크 드라

이브 5853

양 위언빙

미국, 캘리포니아 94536, 프렌몬트, 로웰 플레이

스 450

(뒷면에 계속)

(74) 대리인

특허법인인벤팅크

전체 청구항 수 : 총 18 항

심사관 : 이별섭

(54) 발명의 명칭 **비-회발성 금속 재료들을 예칭하는 방법****(57) 요약**

하드마스크, 상기 하드마스크 아래에 배치된 Ru 함유 층, 및 상기 Ru 함유 층 아래에 배치된 자기 터널 접합(MTJ) 스택을 갖는 스택을 예칭하는 방법이 제공되며, MTJ 스택은 고정 층(pinned layer)을 갖는다. 상기 하드마스크를 전식 예칭으로 예칭한다. 상기 Ru 함유 층을 예칭하되, 하이포아염소산염(hypochlorite) 및/또는 O<sub>3</sub> 계 화학물질들을 사용하여 예칭한다. 상기 MTJ 스택을 예칭한다. 상기 MTJ 스택을 유전체 재료들로 캡핑(capping) 한다. 상기 MTJ 스택을 캡핑한 이후에 상기 고정 층을 예칭한다.

**대 표 도** - 도1

(72) 발명자

센 메이후아

미국, 캘리포니아 94539, 프레몬트, 페리 커먼 694

자넥 리차드 피.

미국, 캘리포니아 94606, 오클랜드, 뉴튼 에비뉴

319

마크스 제프리

미국, 캘리포니아 95070, 사라토가, 카메리언 글렌

코트 14578

싱 하미트

미국, 캘리포니아 94539, 프레몬트, 베카도 플레이

스 443

릴 토스텐

미국, 캘리포니아 95057, 산타 클라라, 뮤어 에비

뉴 88

## 명세서

### 청구범위

#### 청구항 1

하드마스크, 상기 하드마스크 아래에 배치된 Ru 함유 층, 및 상기 Ru 함유 층 아래에 배치된 자기 터널 접합(MTJ:magnetic tunnel junctions) 스택을 갖는 스택을 에칭하는 방법으로서,

상기 MTJ 스택은 고정 층(pinned layer)을 가지며,

상기 방법은,

상기 하드마스크를 건식 에칭함으로써 전도성 재료들의 층을 가지는 상기 하드마스크를 패터닝하는 단계;

패터닝된 상기 하드마스크를 사용하여 상기 Ru 함유 층을 에칭하는 단계;

상기 MTJ 스택을 에칭하는 단계;

상기 MTJ 스택을 유전체 재료들로 캡핑(capping)하는 단계; 및

상기 MTJ 스택을 캡핑한 이후에 상기 고정 층을 에칭하는 단계를 포함하고, 상기 하드마스크를 에칭하는 단계, 상기 Ru 함유 층을 에칭하는 단계, 상기 MTJ 스택을 에칭하는 단계, 상기 MTJ 스택을 유전체 재료들로 캡핑(capping)하는 단계, 및 상기 MTJ 스택을 캡핑한 이후에 상기 고정 층을 에칭하는 단계는 단일 플라즈마 프로세싱 챔버 내에서 수행되는, 스택 에칭 방법.

#### 청구항 2

제 1 항에 있어서,

상기 MTJ 스택을 에칭하는 단계는 화학적 에션트 가스 대신에, 비활성 가스로 형성된 플라즈마의 저 바이어스 스퍼터링 (low bias sputter)을 사용하는, 스택 에칭 방법.

#### 청구항 3

제 2 항에 있어서,

상기 저 바이어스 스퍼터링은 10 볼트 내지 500 볼트의 바이어스를 제공하는, 스택 에칭 방법.

#### 청구항 4

제 3 항에 있어서,

상기 Ru 함유 층을 에칭하는 단계는 습식 에칭을 제공하는, 스택 에칭 방법.

#### 청구항 5

제 4 항에 있어서,

상기 MTJ 스택은 적어도 하나의 CoFe 층 및 적어도 하나의 MgO 층을 포함하는, 스택 에칭 방법.

#### 청구항 6

제 5 항에 있어서,

상기 고정 층은 적어도 하나의 PtMn 층을 포함하는, 스택 에칭 방법.

#### 청구항 7

삭제

#### 청구항 8

제 6 항에 있어서,

상기 MTJ 스택을 에칭하는 단계는 화학적 에천트 가스 없이 물리적 충격을 제공하는 비활성 충격 가스 (inert bombardment gas) 를 사용하는, 스택 에칭 방법.

#### 청구항 9

제 8 항에 있어서,

상기 캡핑용 유전체 재료는 실리콘-계 유전체 재료인, 스택 에칭 방법.

#### 청구항 10

제 1 항에 있어서,

상기 Ru 함유 층을 에칭하는 단계는 습식 에칭을 제공하는, 스택 에칭 방법.

#### 청구항 11

제 1 항에 있어서,

상기 MTJ 스택은 적어도 하나의 CoFe 층 및 적어도 하나의 MgO 층을 포함하는, 스택 에칭 방법.

#### 청구항 12

제 1 항에 있어서,

상기 고정 층은 적어도 하나의 PtMn 층을 포함하는, 스택 에칭 방법.

#### 청구항 13

제 1 항에 있어서,

상기 하드마스크를 에칭하는 단계, 상기 Ru 함유 층을 에칭하는 단계, 상기 MTJ 스택을 에칭하는 단계, 상기 MTJ 스택을 캡핑하는 단계 및 상기 고정 층을 에칭하는 단계는 단일 플라즈마 프로세싱 챔버 내에서 수행되는, 스택 에칭 방법.

#### 청구항 14

제 1 항에 있어서,

상기 MTJ 스택을 에칭하는 단계는 화학적 에천트 가스 없이 물리적 충격을 제공하는 비활성 충격 가스 (inert bombardment gas) 를 사용하는, 스택 에칭 방법.

#### 청구항 15

제 1 항에 있어서,

상기 캡핑용 유전체 재료는 실리콘-계 유전체 재료인, 스택 에칭 방법.

#### 청구항 16

고정 층, 상기 고정 층 위의 MTJ 스택, 상기 MTJ 스택 위의 Ru 함유 층, 및 상기 Ru 함유 층 위의 하드마스크를 포함하는 스택을 에칭하는 방법으로서,

전도성 재료들의 층을 가지는 상기 하드마스크를 에칭함으로써 상기 하드마스크를 패터닝하는 단계;

패터닝된 상기 하드마스크를 사용하여 상기 Ru 함유 층을 에칭하는 단계;

상기 MTJ 스택을 패터닝하도록 상기 고정층까지 상기 MTJ 스택을 에칭하는 단계;

유전체 재료들로 상기 고정층의 상단 표면까지 패터닝된 상기 MTJ 스택을 실링 (sealing) 하는 단계; 및

상기 고정 층을 에칭하는 단계를 포함하고, 상기 하드마스크를 에칭하는 단계, 상기 Ru 함유 층을 에칭하는 단계, 상기 MTJ 스택을 에칭하는 단계, 상기 MTJ 스택을 유전체 재료들로 실링하는 단계, 및 상기 고정 층을 에칭

하는 단계는 단일 플라즈마 프로세싱 챔버 내에서 수행되는, 스택 에칭 방법.

### 청구항 17

제 16 항에 있어서,

상기 MTJ 스택을 에칭하는 단계는 화학적 에션트 가스 대신에, 비활성 가스로 형성된 플라즈마의 저 바이어스 스퍼터링 (low bias sputter) 을 사용하며,

상기 저 바이어스 스퍼터링은 10 볼트 내지 500 볼트의 바이어스를 제공하는, 스택 에칭 방법.

### 청구항 18

제 16 항에 있어서,

상기 MTJ 스택은 적어도 하나의 CoFe 층 및 적어도 하나의 MgO 층을 포함하는, 스택 에칭 방법.

### 청구항 19

제 16 항에 있어서,

상기 MTJ 스택을 실링하는 단계는 실리콘-계 유전체 재료로 상기 MTJ 스택을 실링하는, 스택 에칭 방법.

### 청구항 20

삭제

## 발명의 설명

### 기술 분야

#### 관련 출원에 대한 교차 참조

[0001] 본원은 2014년 3월 27일에 출원된 미국 가 특허 출원 번호 61/971,032 "METHODS TO ETCHE AND TO REMOVE POST ETCHE METALLIC RESIDUE"에 대한 우선권을 35 U.S.C. § 119(e) 하에서 주장하며, 이 가 출원은 모든 목적들을 위해서 본 명세서에서 참조로서 통합된다.

[0003] 본 발명은 반도체 디바이스의 생산 동안에 마스크를 통해서 비휘발성 재료들의 층을 에칭하는 것에 관한 것이다. 보다 구체적으로, 본 발명은 금속 MTJ (magnetic tunnel junctions) 스택을 에칭하는 것에 관한 것이다.

### 배경 기술

[0004] 반도체 웨이퍼 프로세싱 동안에, 피처들이 금속 함유 층을 통해서 에칭될 수 있다. MRAM (magnetic random access memories) 디바이스 또는 RRAM (resistance random access memories) 디바이스 형성 시에, 복수의 얇은 금속 층들 또는 막들이 순차적으로 에칭될 수 있다. MRAM에 있어서 복수의 얇은 금속 층들은 MTJ 스택들을 형성하는데 사용될 수 있다.

### 발명의 내용

[0005] 전술한 바를 달성하고 본 발명의 목적에 따라서, 하드마스크, 상기 하드마스크 아래에 배치된 Ru 함유 층, 및 상기 Ru 함유 층 아래에 배치된 자기 터널 접합 (MTJ) 스택을 갖는 스택을 에칭하는 방법이 제공되며, MTJ 스택은 고정 층 (pinned layer) 을 갖는다. 상기 하드마스크를 건식 에칭으로 에칭한다. 상기 Ru 함유 층을 에칭 하되, 하이포아염소산염 (hypochlorite) 및/또는 O<sub>3</sub> 계 화학물질들을 사용하여서 에칭한다. 상기 MTJ 스택을 에칭한다. 상기 MTJ 스택을 유전체 재료들로 캡핑 (capping) 한다. 상기 MTJ 스택을 캡핑한 이후에 상기 고정 층을 에칭한다.

[0006] 본 발명의 다른 양태에서, 고정 층, 상기 고정 층 위의 MTJ 스택, 상기 MTJ 스택 위의 Ru 함유 층, 및 상기 Ru 함유 층 위의 하드마스크를 포함하는 스택을 에칭하는 방법이 제공된다. 상기 하드마스크, 상기 Ru 함유 층, 및 상기 MTJ 스택을 에칭한다. 상기 MTJ 스택을 실링 (sealing) 한다. 상기 고정 층을 에칭한다.

[0007] 본 발명의 다른 양태에서, 하드마스크 층, 상기 하드마스크 층 아래에 배치된 Ru 함유 층, 상기 Ru 함유 층 아래에 배치된 MTJ 스택, 및 상기 MTJ 스택 아래에 배치된 고정 층을 갖는 스택을 에칭하는 방법이 제공된다. 건식 에칭으로 상기 하드마스크 층을 에칭한다. 상기 Ru 함유 층을 에칭한다. 상기 MTJ 스택을 에칭한다. 유전체 재료들로 상기 MTJ 스택을 캡핑한다. 귀금속들에 대해서 선택성을 갖는 화학물질들로 상기 고정 층을 에칭하며, 상기 화학물질들은  $\text{SOCl}_2$ /페리딘 혼합물들;  $\text{HBr}/\text{DMSO}$  혼합물들; 또는  $\text{DMSO}$ , 아세토니트릴, 벤조니트릴(benzonitrile), 또는  $\text{DMF}$  (dimethylformamide) 중 적어도 하나와  $\text{CCl}_4$  간의 혼합물을 포함한다.

[0008] 본 발명의 이러한 그리고 다른 특징들이 다음의 도면들과 함께 그리고 본 발명의 상세한 설명에서 이하에서 보다 상세하게 기술될 것이다.

### 도면의 간단한 설명

[0009] 본 발명은 한정적이 아니라 예시적으로 첨부 도면의 도면들에서 예시되며, 도면들에서 유사한 참조 부호들은 유사한 요소들을 나타낸다.

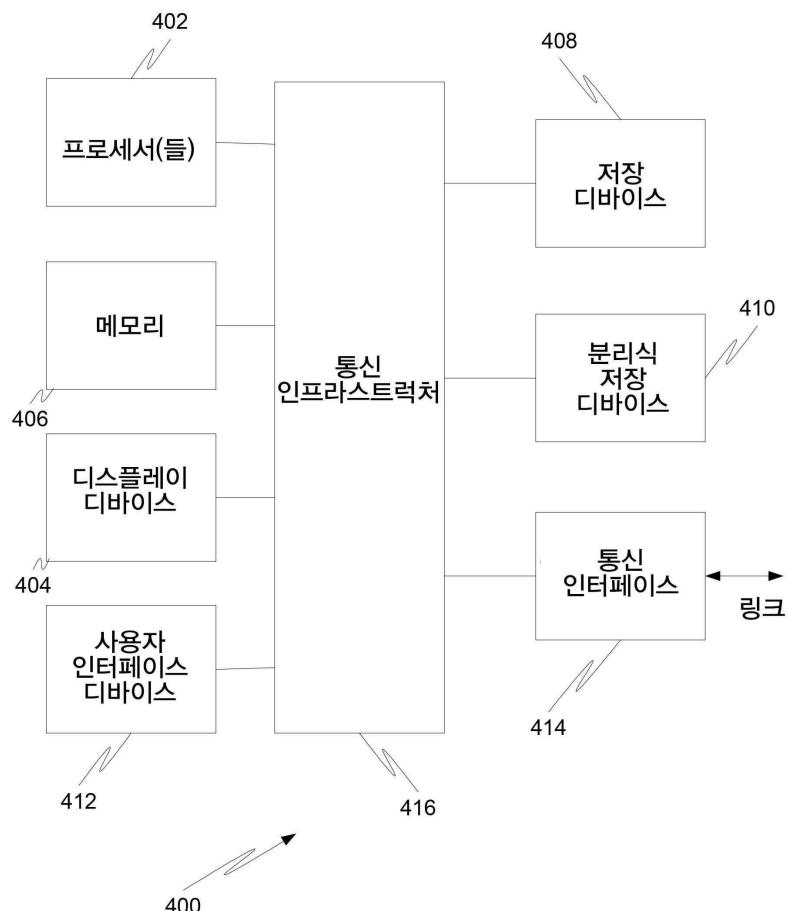

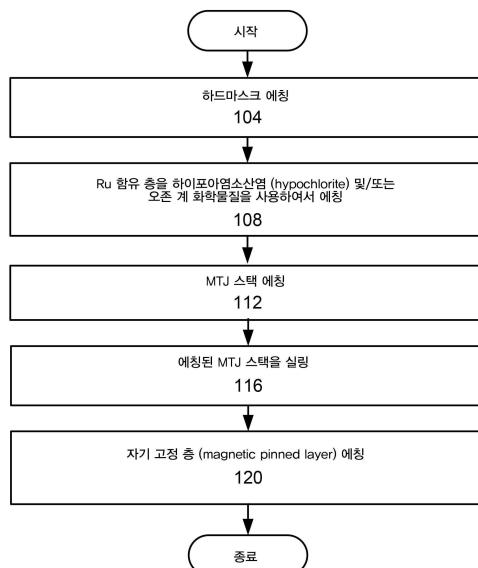

도 1은 본 발명의 실시예의 하이 레벨 흐름도이다.

도 2a 내지 도 2g는 본 발명의 실시예에 따라서 프로세싱된 스택의 개략도들이다.

도 3은 에칭을 위해서 사용될 수 있는 에칭 반응기의 개략도이다.

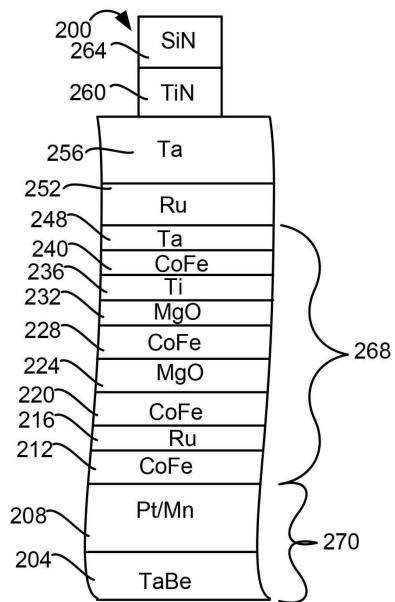

도 4는 본 발명의 실시예들에서 사용된 제어기를 구현하는데 적합한 컴퓨터 시스템을 예시한다.

### 발명을 실시하기 위한 구체적인 내용

[0010] 본 발명이 이제 첨부 도면들에서 예시된 바와 같은 본 발명의 몇몇 바람직한 실시예들을 참조하여서 세부적으로 기술될 것이다. 다음의 설명에서, 다수의 특정 세부사항들이 본 발명의 철저한 이해를 제공하기 위해서 제시된다. 그러나, 본 발명은 이러한 특정 세부사항 전부 또는 일부 없이도 실시될 수 있음이 본 기술 분야의 당업자에게 자명하다. 다른 실례에서, 잘 알려진 프로세스 단계들 및/또는 구조들은 본 발명을 불필요하게 모호하게 하지 않도록 하기 위해서 세부적으로는 기술되지 않았다.

[0011] 이해를 돋기 위해서, 도 1은 본 발명의 실시예에서 사용되는 프로세스의 하이 레벨 흐름도이다. 하드마스크 아래에 그리고 MTJ 스택 위에 배치된 Ru 함유 층을 갖는 스택을 기판이 제공된다. 하드마스크가 에칭 또는 개방된다(단계 104). Ru 함유 층이 하이포아염소산염(hypochlorite) 및/또는 오존 계 화학물질을 사용하여서 에칭된다(단계 108). MTJ 스택이 에칭된다(단계 112). 에칭된 MTJ 스택이 실링된다(sealed)(단계 116). 자기 고정 층(magnetic pinned layer)이 에칭된다(단계 120). 이러한 자기 고정 층은 *Development of the magnetic tunnel junction MRAM at IBM: From first junctions to a 16-Mb MRAM demonstrator chip*, IBM J. RES. & DEV. VOL. 50 NO. 1 JANUARY 2006에 기술되며, 이 문헌은 모든 목적들을 위해서 참조로서 통합된다.

### 실례들

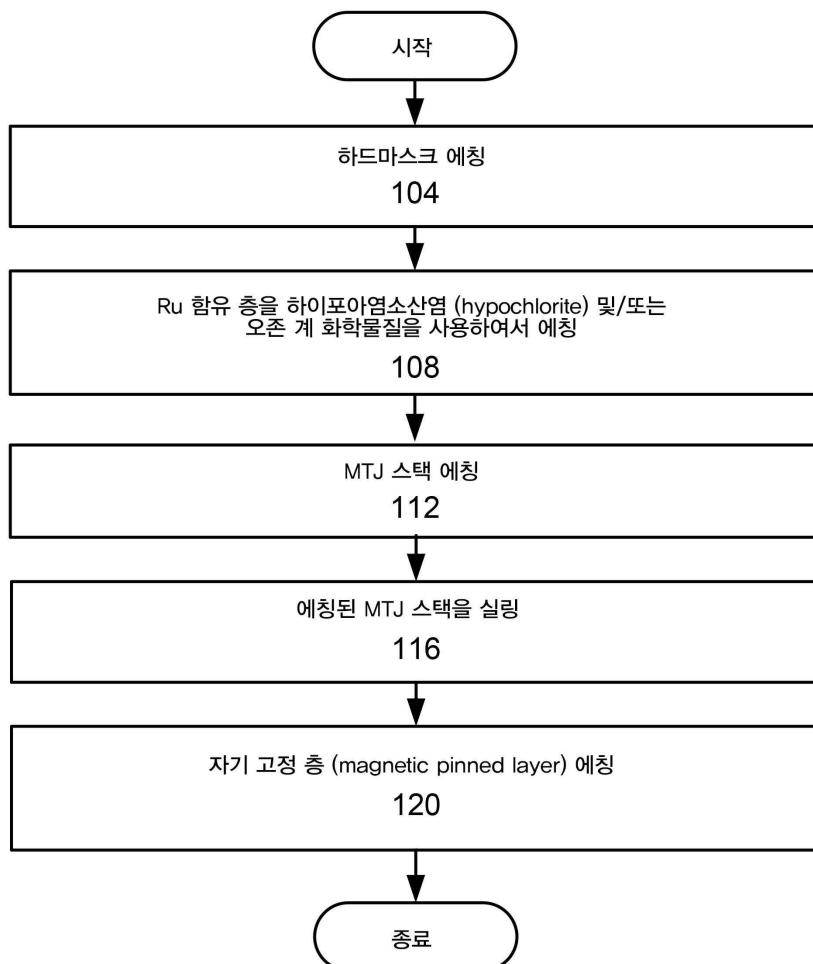

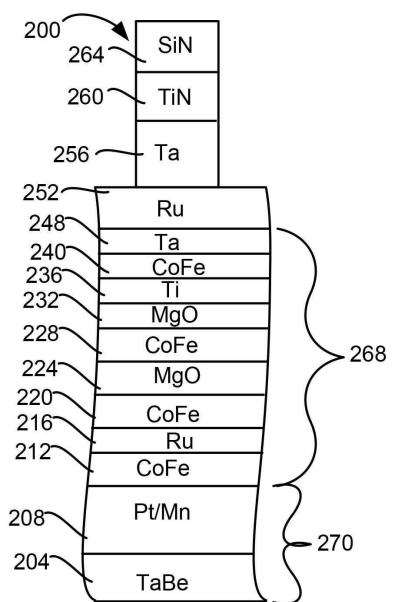

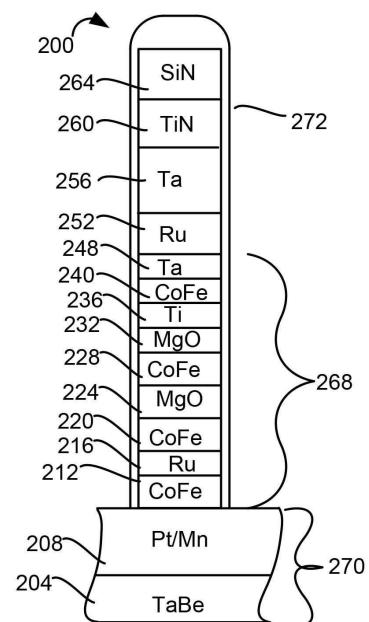

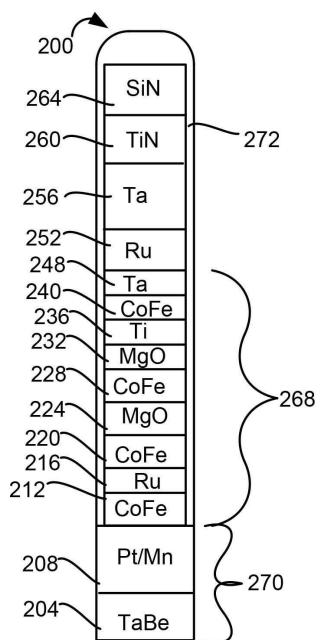

[0013] 도 2a는 본 실례에서 MRAM을 위해서 사용되는 스택(200)의 단면도이다. 본 실례에서 스택(200)의 하단 층은 기판 위에 형성된 탄탈륨 베릴륨(tantalum beryllium)(TaBe) 층(204)이다. 백금 망간(platinum manganese)(PtMn) 층(208)이 TaBe 층(204) 위에 형성된다. 제1코발트 철(CoFe) 층(212)이 PtMn 층(208) 위에 형성된다. 제1루테늄(Ru) 층(216)이 제1CoFe 층(212) 위에 형성된다. 제2CoFe 층(220)이 제1Ru 층(216) 위에 형성된다. 제1망간 산화물(MgO) 층(224)이 제2CoFe 층(220) 위에 형성된다. 제3CoFe 층(228)이 제1MgO 층(224) 위에 형성된다. 제2MgO 층(232)이 제3CoFe 층(228) 위에 형성된다. 티타늄(Ti) 층(236)이 제2MgO 층(232) 위에 형성된다. 제4CoFe 층(240)이 Ti 층(236) 위에 형성된다. 제1탄탈륨(Ta) 층(248)이 제4CoFe 층(240) 위에 형성된다. 제2Ru 층(252)이 제1Ta 층(248) 위에 형성된다. 제2Ta 층(256)이 제2Ru 층(252) 위에 형성된다. 티타늄질화물(TiN) 층(260) 및 실리콘질화물(SiN) 층(264)을 포함하는 마스크가 제2Ta 층(256) 위에서 패터닝된다. 본 실례에서, 제1CoFe 층(212) 및 제1Ta 층(248)을 포함하여 이들 간에 있는 층들은 자기 터널 접합(MTJ) 층(268)을 형성한다. PtMn 층(208) 및 TaBe 층(204)은 고정 층(270)을 형성한다. 고정 층(270)은 다른 재료들로 형성될 수 있다.

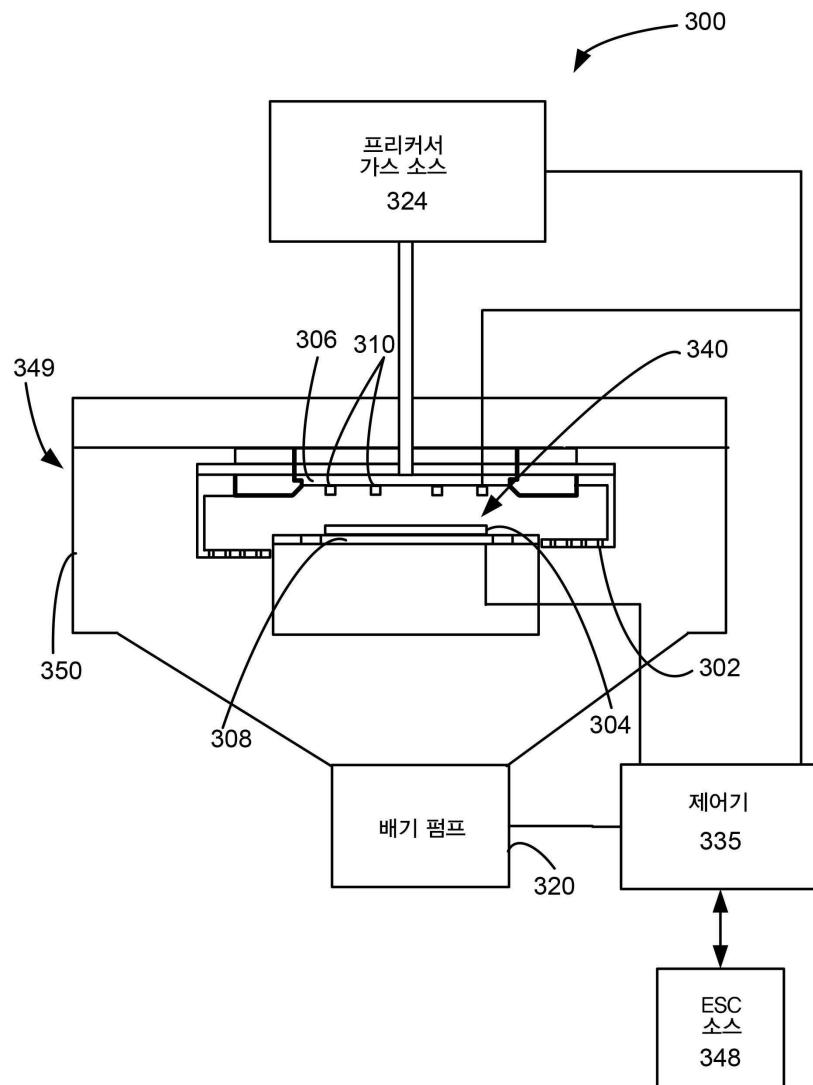

[0014] 일 실시예에서, 모든 프로세싱은 단일 플라즈마 에칭 챔버 내에서 수행될 수 있다. 도 3은 이러한 실시예를 실시하는데 사용될 수 있는 에칭 반응기의 개략도이다. 본 발명의 하나 이상의 실시예들에서, 에칭 반응기(300)

는 챔버 벽 (350)에 의해서 둘러싸인 에칭 챔버 (349) 내에 가스 유입구를 제공하는 가스 분배 플레이트 (306) 및 척 (308)을 포함한다. 에칭 챔버 (349) 내에, 스택이 형성된 기판 (304)이 척 (308)의 상단 상에 위치된다. 척 (308)은 기판 (304)을 훌딩하기 위한 정전 척 (ESC)로서 ESC 소스 (348)로부터의 바이어스를 제공하며 기판 (304)을 훌딩하기 위해서 다른 척킹 힘을 사용할 수도 있다. 가열 램프들과 같은 가열 소스 (310)가 금속 층을 가열하도록 제공된다. 프리커서 가스 소스 (324)가 가스 분배 플레이트 (306)를 통해서 에칭 챔버 (349)에 연결된다.

[0015] 도 4는 본 발명의 실시예들에서 사용되는 제어기 (335)를 구현하는데 적합한 컴퓨터 시스템 (400)을 나타내는 하이 레벨 블록도이다. 컴퓨터 시스템 (400)은 접적 회로, 인쇄 회로 보드, 및 소형 핸드헬드 디바이스로부터 거대 수퍼 컴퓨터에 이르는 수많은 물리적 형태를 가질 수 있다. 컴퓨터 시스템 (400)은 하나 이상의 프로세서 (402)를 포함하며, 전자 디스플레이 디바이스 (404) (그래픽, 텍스트 및 다른 데이터를 디스플레이하기 위함), 주 메모리 (406) (예를 들어서, RAM), 저장 디바이스 (408) (예를 들어서, 하드 디스크 드라이브), 분리식 저장 디바이스 (410) (예를 들어서, 광 디스크 드라이브), 사용자 인터페이스 디바이스들 (412) (예를 들어서, 키보드, 터치 스크린, 키패드, 마우스 또는 다른 포인팅 디바이스 등), 및 통신 인터페이스 (414) (예를 들어서, 무선 네트워크 인터페이스)를 더 포함할 수 있다. 통신 인터페이스 (414)는 링크를 통해서 컴퓨터 시스템 (400)과 외부 디바이스들 간에서 소프트웨어 및 데이터가 전달될 수 있게 한다. 시스템은 또한 전술한 디바이스들/모듈들이 연결되는 통신 인프라스트럭처 (416) (예를 들어서, 통신 버스, 크로스-오버 바 또는 네트워크들)를 포함할 수 있다.

[0016] 통신 인터페이스 (414)를 통해서 전달된 정보는 신호들을 반송하며 와이어 또는 케이블, 광섬유들, 전화 라인, 셀룰러 전화 링크, 무선 주파수 링크 및/또는 다른 통신 채널들을 사용하여 구현될 수 있는 통신 링크를 통해서, 통신 인터페이스 (414)에 의해서 수신될 수 있는 전자적 신호, 전자기적 신호, 광학적 신호 또는 다른 신호를 포함하는 신호 형태로 존재할 수 있다. 이러한 통신 인터페이스를 사용하여서, 하나 이상의 프로세서들 (402)은 상술한 방법 단계들을 수행하는 과정에서 정보를 네트워크로부터 수신하거나 정보를 네트워크로 출력할 수 있다. 또한, 본 발명의 방법 실시예들은 오직 프로세서들 상에서 실행되거나 프로세싱의 일부를 공유하는 원격 프로세서들과 함께 인터넷과 같은 네트워크를 통해서 실행될 수 있다.

[0017] 용어 "비일시적 컴퓨터 판독가능한 매체"는 일반적으로 하드 디스크, 플래시 메모리, 디스크 드라이브 메모리, CD-ROM, 및 다른 형태의 영구 메모리와 같은, 주 메모리 디바이스, 보조 메모리 디바이스, 분리식 저장 디바이스 및 저장 디바이스와 같은 매체를 지칭하는데 사용된다. 컴퓨터 코드의 실례들은 컴파일러에 의해서 생성되는 것과 같은 머신 코드 및 인터프리터를 사용하여서 컴퓨터에 의해서 실행되는 보다 높은 레벨의 코드를 포함하는 파일들을 포함할 수 있다. 컴퓨터 판독가능한 매체는 또한 반송파에서 구현되는 컴퓨터 데이터 신호에 의해서 전송되며 프로세서에 의해서 실행가능한 인스트럭션들의 시퀀스를 표현하는 컴퓨터 코드일 수 있다.

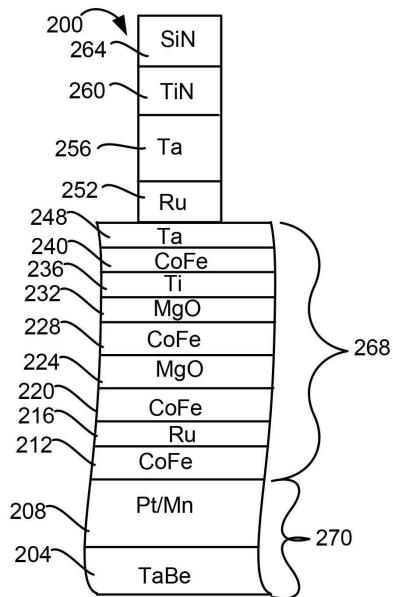

[0018] 하드마스크가 에칭 또는 개방된다 (단계 104). 본 실례에서, 하드마스크는 Ta 층 (256)이다. SiN 층 (264) 및 TiN 층 (260)이 Ta 층 (256)을 에칭하기 위한 마스크로서 사용된다. 본 실시예에서, 플라즈마 에칭이 Ta 층 (256)을 에칭하는데 사용된다. 본 실시예에서 에칭 가스로서 Cl<sub>2</sub>를 사용하는 건식 에칭이 사용될 수도 있다. 도 2b는 Ta 층 (256)이 에칭된 후의 스택 (200)의 단면도이다.

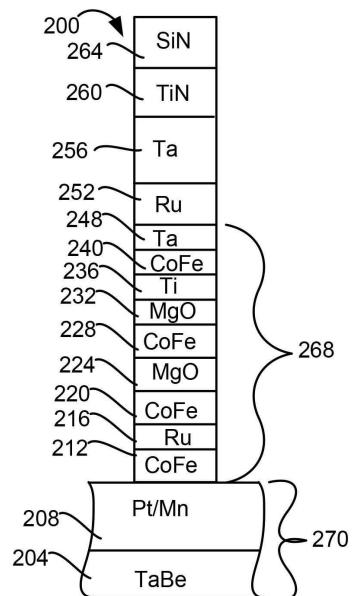

[0019] 제 2 Ru 층 (252)이 하이포아염소산염 (hypochlorite) 및/또는 오존 계 화학물질을 사용하여서 에칭된다 (단계 108). 일 실시예에서, 플라즈마 에칭이 사용되어서 하이포아염소산염 (hypochlorite) 및 오존 화학물 기반 에칭을 제공할 수 있다. 다른 실시예에서, 하이포아염소산염 (hypochlorite) 및 오존 계 화학물질은 습식 에칭 시에 사용될 수도 있다. 이러한 실시예에서, 희석된 플루오르화수소 (dHF) 사전세정이 사용되어서, 제 2 Ru 층 (252)을 에칭하기 이전에 실리콘 산화물 잔류물을 제거할 수 있다. NaClO 수용액이 습식 에칭 시에 사용되어서 제 2 Ru 층 (252)을 에칭할 수도 있다. 본 실례에서, Ru 에칭은 NaClO 수용액을 사용하여서 습식 에칭된다. 다른 하이포아염소산염 에칭 프로세스는 pH>12를 갖는 무-Na 용액 (Na-free solution) 내의 HClO; 유기 용매, R-함유 알킬 (-CH<sub>3</sub>, -CH<sub>2</sub>CH<sub>3</sub>, -C(CH<sub>3</sub>)<sub>3</sub> 등), 사이클로알킬 또는 방향족 카르보닐 내의 유기 하이포아염소산염 R-OCI을 포함한다. 도 2c는 제 2 Ru 층 (252)이 에칭된 후의 스택 (200)의 단면도이다. pH >12을 갖는 오존 함유 수용액을 사용하는 Ru 습식 에칭의 실례들은 오존 포화된 NaOH, NH<sub>4</sub>OH, 또는 테트라메틸암모니움 수산화물 (tetramethylammonium hydroxide) 용액을 포함한다.

[0020] MTJ 스택 (268)이 고정 층 내로 리세스가 있게 에칭된다 (단계 112). 리세스는 후속하는 유전체로의 캡핑 (capping)이 MTJ와 고정 층 간의 계면을 실링할 수 있게 한다. 본 실시예에서 저 바이어스 이온 스퍼터링이 사용되어서 MTJ 스택 (268)을 에칭한다. 본 실시예에서, 이 단계 동안 사용된 가스는 필수적으로 아르곤 (Ar)

으로 구성된다. 바람직하게는, 저 바이어스는 10 볼트와 500 볼트 간의 바이어스를 제공한다. 보다 바람직하게는, 저 바이어스는 20 볼트와 300 볼트 간의 바이어스이다. 가장 바람직하게는, 저 바이어스는 100 볼트와 200 볼트 간의 바이어스이다. 화학적 에천트 가스를 사용하지 않고 오직 비활성 충격 가스만을 사용하는 저 바이어스 이온 스퍼터링이 MTJ 충착을 감소시키면서 MTJ 에칭을 제공한 것이 예기치 않게 발견되었다. 화학적 에천트 가스는 화학적 반응을 사용하여서 에칭하는 성분을 갖는 가스이다. 비활성 충격 가스는 에칭을 위해서 화학적 반응을 사용하지 않고 오직 에칭을 위해서 물리적 충격만을 사용한다. 도 2d는 제 2 MTJ 스택 (268) 이 에칭된 후의 스택 (200) 의 단면도이다.

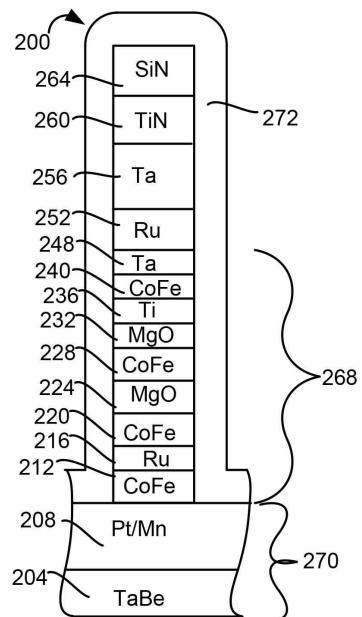

[0021] 에칭된 MTJ 스택 (268) 이 유전체 재료들로 구성된 컨포멀 절연 층 (272) 을 충착함으로써 실링된다 (단계 116). 이러한 캡핑 층 (272) 은 개방된 MTJ 스택들을 캡슐화하여서 MTJ 스택들이 하단 충들을 에칭하기 위한 다음의 프로세스들에 의해서 유발될 수도 있는 손상을 받지 않게 유지한다. 동등하게 중요하게는, 캡핑 층은 또한 후속하는 충들의 에칭 프로세스들을 MTJ 스택 (268) 을 에칭하는 프로세스와 분리시킨다. MTJ에 대한 손상에 관한 2 개의 통상적인 카테고리들은 다음과 같다: 에칭 생성물이 MTJ 측벽 상에 재-충착되어서 MTJ 단락에 이르는 것 및 에칭 화학물이 MTJ 충들과 반응하여서 자기 특성들을 열화시키는 것. 이로써, 모든 스택이 캡핑 층 없이 에칭되는 통상적인 프로세스들에서, MTJ 스택들이 손상을 입는다. MgO 또는 CoFeB에 손상을 주는 임의의 에칭 프로세스는 허용될 수 없으며 이러한 프로세스들은 H<sub>2</sub>O, 산소, 할로겐 계 화학물 에칭 또는 플라즈마 시스템 에칭을 포함한다. 적합한 캡핑 층을 선정하는 것은 개방된 MTJ가 후속하는 프로세스 흐름에서 고장이 나거나 열화되지 않게 한다. 이로써, 이상적인 캡핑 층들이 후속하는 충들을 에칭하기 위해서, MgO/CoFeB와 양립하지 않는 프로세스들을 포함하는 다양한 프로세스를 활용하도록 원도우를 개방하며 MTJ의 자기적/전기적 특성들이 열화되지 않게 유지한다. 다양한 절연 캡핑 충들, 예를 들어서 실리콘-계 유전체 막들, SiN, SiC, SiCN, SiO<sub>2</sub>, SiOC, SiOCH<sub>3</sub>, SiOCH<sub>x</sub>CH<sub>3</sub>, Si; 탄소-계 유전체 막들 (탄소, 폴리머), 질화물 화합물 (BN) 이 선정될 수 있다. 본 실례에서, SiO<sub>2</sub> 및 SiN으로 캡핑 층을 시연하였다. 플라즈마가 SiH<sub>4</sub> 및 O<sub>2</sub>로부터 형성되어서 에칭된 스택 위에 SiO<sub>2</sub> 층을 충착하였다. 다른 실시예에서, SiN 층이 충착된다. 도 2e는 SiO<sub>2</sub> 충착 층 (272) 이 충착된 후의 스택 (200) 의 단면도이다.

[0022] 충착 층 (272) 이 반대로 에칭되어서 (개방되어서) MTJ 스택 (268) 의 측벽이 실링되게 유지되면서 그 아래에 놓인 PtMn 층 (208) 을 노출시킨다. 본 실시예에서, CF<sub>4</sub> 및 Ar 플라즈마 개방 프로세스가 사용되어서 충착 층을 개방시킨다. 도 2f는 충착 층 (272) 이 개방된 후의 스택 (200) 의 단면도이다. 충착 층 (272) 의 하단이 완전하게 제거된다. 충착 층 (272) 의 측벽은 얇아지지만 MTJ 스택 (268) 을 실링하도록 유지된다.

[0023] 자기 고정 층 (270) 이 에칭된다 (단계 120). 일 실시예에서, 자기 고정 층 (270) 은 건식 플라즈마 에칭을 사용하여서 에칭된다. 다른 실시예에서, 자기 고정 층 (270) 은 습식 에칭을 사용하여서 에칭된다. 그 실례들은 가변 비로 피리딘과 티오닐 클로라이드 (SOCl<sub>2</sub>) 를 혼합하는 것을 포함하며, 유기 용매 내의 희석된 혼합물은 다음으로 한정되지 않지만 아세토니트릴 (acetonitrile) 을 포함한다. HBr 및 DMSO 혼합물들이 또한 사용되어서 PtMn 및 다른 귀금속 함유 자기 고정 층을 에칭할 수도 있다. 또한, DMSO, 아세토니트릴, 벤조니트릴 (benzonitrile), 또는 DMF (dimethylformamide) 중 적어도 하나와 CCl<sub>4</sub> 간의 혼합물이 사용되어서 PtMn 및 다른 귀금속 함유 자기 고정 층을 에칭할 수도 있다. 도 2g는 자기 고정 층 (270) 이 에칭된 후의 스택 (200) 의 단면도이다. 충착 층 (272) 을 제거하는 것과 같은 추가 프로세싱 단계들이 스택 (202) 을 MRAM 으로 형성하기 위해서 사용될 수도 있다.

[0024] 본 발명의 일부 실시예들은 종래 기술에 비해서 많은 장점을 제공한다. 예를 들어서, MTJ 스택 (268) 을 실링하는 것은 자기 고정 층 에칭 단계 (단계 120) 동안의 MTJ 스택 (268) 의 손상을 없게 한다. 또한, MTJ 스택 (268) 을 에칭하기 위해서 저 바이어스 이온 스퍼터링을, 화학적 에칭 또는 고 바이어스 이온 스퍼터링 대신에 사용하는 것은 MTJ 스택 (268) 의 손상을 더 줄일 수 있다. 만일에 MTJ 스택 (268) 을 화학적으로 에칭하면 MTJ 스택 (268) 충들의 일부가 손상을 입을 것이다. 이러한 저 바이어스 이온 스퍼터링은 MTJ 스택 (268) 재료들이 덜 재증착되게 하는 것이 예기치 않게 발견되었다. 재증착된 MTJ 재료들이 감소되면 디바이스 품질을 향상시키는데 그 이유는 재증착된 재료는 충들 간의 단락을 유발할 수 있기 때문이다. 이러한 재증착된 재료들의 제거는 MTJ 충들을 손상시킬 수도 있다. MTJ 스택 (268) 이 손상되면 MRAM의 자기 특성이 바람직하지 않게 변화될 것이다. 하이포아염소산염 및/또는 오존 계 화학물질을 사용하여서 제 2 Ru 층 (252) 을 에칭하면, MTJ 스택 (268) 을 에칭하는데 사용된 레시피와는 상이한 에칭 레시피를 요구하는 제 2 Ru 층 (252) 에 대한 선택적 에칭이 향상되는 것이 예기치 않게 발견되었다. Ru는 매우 비활성이다. 하이포아염소산염은 비활성 Ru를 산화

시키는데 요구되는 강한 산화제이다. 이러한 2 개의 단계들에서의 상이하고 선택적인 에칭들은 보다 덜한 MTJ 스택 (268) 손상 및 재증착을 낳는다. 다른 실시예들에서, MTJ 스택 (268) 은 다른 층들을 포함하거나 다른 순서로 존재할 수 있거나 보다 많은 또는 보다 적은 층들을 포함할 수 있다. MTJ 스택 (268) 은 MRAM을 형성할 시에 필수적이다.

[0025]

본 발명은 몇몇 바람직한 실시예들의 차원에서 기술되었지만, 본 발명의 범위 내에 해당하는 변경, 치환, 및 다양한 대체 균등 사항들이 존재한다. 또한, 본 발명의 방법들 및 장치들을 구현하는 수많은 다른 방식들이 존재한다. 따라서, 다음의 첨부된 청구항들은 상기한 변경, 치환, 및 다양한 대체 균등 사항들을 본 발명의 진정한 사상 및 범위 내에 해당하는 것으로서 포함하도록 해석되어야 한다.

## 도면

### 도면1

도면2a

도면2b

도면2c

도면2d

도면2e

도면2f

도면2g

## 도면3

## 도면4