(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5244390号

(P5244390)

(45) 発行日 平成25年7月24日(2013.7.24)

(24) 登録日 平成25年4月12日(2013.4.12)

(51) Int.Cl.

H01L 27/146 (2006.01)

H04N 5/374 (2011.01)

F 1

H01L 27/14

H04N 5/335 740

請求項の数 14 (全 22 頁)

(21) 出願番号 特願2007-532490 (P2007-532490)

(86) (22) 出願日 平成17年9月13日 (2005.9.13)

(65) 公表番号 特表2008-514011 (P2008-514011A)

(43) 公表日 平成20年5月1日 (2008.5.1)

(86) 國際出願番号 PCT/US2005/033123

(87) 國際公開番号 WO2006/137867

(87) 國際公開日 平成18年12月28日 (2006.12.28)

審査請求日 平成20年8月21日 (2008.8.21)

(31) 優先権主張番号 60/610,830

(32) 優先日 平成16年9月17日 (2004.9.17)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/610,831

(32) 優先日 平成16年9月17日 (2004.9.17)

(33) 優先権主張国 米国(US)

(73) 特許権者 598128421

カリフォルニア インスティテュート オ

ブ テクノロジー

アメリカ合衆国 カリフォルニア 911

25, パサデナ, イースト カリフォ

ルニア ブールバード 1200, エムエ

ス 201-85

(74) 代理人 100098899

弁理士 飯塚 信市

(74) 代理人 100063808

弁理士 門間 正一

(72) 発明者 ペイン, ベダブレイタ

アメリカ合衆国 カリフォルニア州 90

046 ロサンゼルス ノース クレセン

ト ハイツ ブルヴァード 828

最終頁に続く

(54) 【発明の名称】 SOI ウェーハで作ったバック照明式CMOS撮像素子 (IMAGER) の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

シリコン・ウェーハと素子シリコン層との間に埋設された、前記素子シリコン層表面に熱酸化により形成された  $SiO_2$  である、絶縁体層を含んだ SOI ウェーハを提供する工程と、

バルク CMOS プロセス・フローにより前記素子シリコン層を処理することにより、複数のフォトダイオードを包含する素子層を形成する工程と、

前記素子層と結合されるべき層間絶縁層を形成する工程と、

前記素子シリコン層の上に、前記フォトダイオードの量子効率 (QE) を維持しつつ暗電流を下げるよう構成された不活性化層を形成する前記絶縁体層を露出させるために、前記シリコン・ウェーハを除去する工程と、

前記フォトダイオードのそれぞれに対応して配置されるようにして、前記不活性化層の上に、マイクロレンズを提供する工程とからなる、

ことを特徴とする、絶縁体上シリコン (SOI; silicon-on-insulator) プロセスと CMOS プロセスとを組み合わせたプロセス。

## 【請求項 2】

前記素子シリコン層は、 $3 \mu m \sim 10 \mu m$  の厚さを有することを特徴とする請求項 1 に記載のプロセス。

## 【請求項 3】

前記素子シリコン層のドーピング濃度は、前記素子シリコン層の空乏領域の厚さと相反

する関係となることを特徴とする請求項 1 又は 2 に記載のプロセス。

【請求項 4】

前記 フォトダイオード が L O C O S または S T I 構造によって互いに分離されていることを特徴とする請求項 1 ~ 3 のいずれかに記載のプロセス。

【請求項 5】

前記 素子シリコン層 が、前記複数のフォトダイオード を含む撮像領域と、C M O S 信号処理回路を含む信号処理領域とを含むことを特徴とする請求項 1 ~ 4 のいずれかに記載のプロセス。

【請求項 6】

前記不活性化層と前記マイクロレンズとの間に反射防止コーティングを形成する工程を 10 さらに含むことを特徴とする請求項 1 に記載のプロセス。

【請求項 7】

前記不活性化層と前記マイクロレンズとの間にカラーフィルタを形成する工程をさらに含むことを特徴とする請求項 1 に記載のプロセス。

【請求項 8】

前記反射防止コーティングと前記マイクロレンズとの間にカラーフィルタを形成する工程をさらに含むことを特徴とする請求項 6 に記載のプロセス。

【請求項 9】

前記複数のフォトダイオードの各々は対応する M O S ゲートに接続されていることを特徴とする請求項 1 に記載のプロセス。 20

【請求項 10】

シリコン・ウェーハと素子シリコン層との間に埋設された、前記素子シリコン層表面に熱酸化により形成された S i O<sub>2</sub> である、絶縁体層を含んだ S O I ウェーハを提供する工程と、

バルク C M O S プロセス・フローにより前記素子シリコン層を処理することにより、複数のフォトダイオードを包含する 素子層 を形成する工程と、

前記素子層と結合されるべき層間絶縁層を形成する工程と、

前記素子シリコン層の上に、前記フォトダイオード の量子効率 ( Q E ) を維持しつつ暗電流を下げるよう構成された不活性化層を形成する前記絶縁体層を露出させるために、前記シリコン・ウェーハを除去する工程と、 30

前記フォトダイオードのそれぞれに対応して配置されるようにして、前記不活性化層の上に、カラーフィルタを提供する工程とからなる、

ことを特徴とする、絶縁体上シリコン ( S O I ; silicon-on-insulator ) プロセスと C M O S プロセスとを組み合わせたプロセス。

【請求項 11】

前記不活性化層と前記カラーフィルタとの間に反射防止コーティングを形成する工程をさらに含むことを特徴とする請求項 10 に記載のプロセス。

【請求項 12】

前記カラーフィルタの上にマイクロレンズを形成する工程をさらに含むことを特徴とする請求項 10 に記載のプロセス。 40

【請求項 13】

前記複数のフォトダイオードの各々は対応する M O S ゲートに接続されていることを特徴とする請求項 10 に記載のプロセス。

【請求項 14】

シリコン・ウェーハと素子シリコン層との間に埋設された、前記素子シリコン層表面に熱酸化により形成された S i O<sub>2</sub> である、絶縁体層を含んだ S O I ウェーハを提供する工程と、

バルク C M O S プロセス・フローにより前記素子シリコン層を処理することにより、複数のフォトダイオードを包含する 素子層 を形成する工程と、

前記素子層と結合されるべき層間絶縁層を形成する工程と、 50

前記素子シリコン層の上に、前記フォトダイオードの量子効率( Q E )を維持しつつ暗電流を下げるよう構成された不活性化層を形成する前記絶縁体層を露出させるために、前記シリコン・ウェーハを除去する工程と、

前記フォトダイオードに対応して配置されるようにして、前記不活性化層の上に、それぞれレンズ及び／又はフィルタを含む光学撮像素子を提供する工程とからなる、

ことを特徴とする、絶縁体上シリコン( S O I ; silicon-on-insulator )プロセスと C M O S プロセスとを組み合わせたプロセス。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願の相互参照)

10

本出願は、Bedabrata PainおよびThomas J Cunninghamによって2004年9月17日に出願された米国仮特許出願通し番号60/610,830「Back-Illuminated Visible Imager」およびBedabrata Painによって2004年9月17日に出願された米国仮特許出願番号60/610,831「Architecture and Methods for High-Efficiency Visible Imager Implementation」の利益を主張する。これらの米国仮特許出願すべての開示内容は本書の一部としてここに組み込まれるものである。本出願は、同じ出願日に出願された米国特許出願(代理人事件番号622737-5)「Structure for Implementation of Back-Illuminated CMOS or CCD Imagers」にも関連している。この米国特許出願の全内容も本書の一部としてここに組み込まれるものである。

20

(連邦利害関係の陳述)

【0002】

ここに記載する発明は、N A S A 契約の規定の下での業務の実行において発明されたもので、公法96-517(35 U S C 202)の規定に従うものであり、この規定において、契約者は所有権を保持することを選択した。

(分野)

【0003】

本開示は、撮像素子( I M A G E R )に関するものであり、更に具体的に言うと、本発明は、バック照明式C M O S またはC C D 撮像素子の製作方法に関するものである。

30

【背景技術】

【0004】

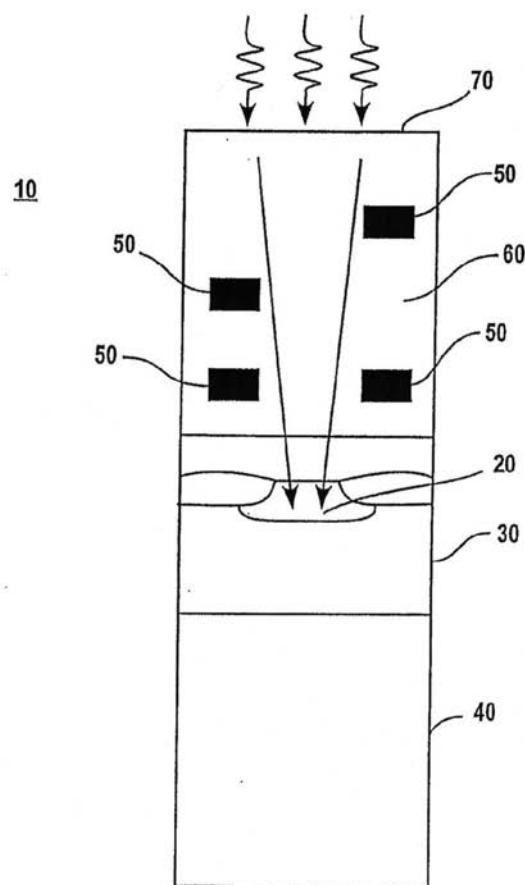

現行の商用C M O S 撮像素子はフロント照明式である。図1はフロント照明式ピクセルの集光部の縦断面を示している。

【0005】

光検出器10は、アノードとして機能するエピタキシャル・シリコン層または基板シリコン層30上にイオン注入カソード20を含んでいる。光検出器10は、従来のV L S I 微細加工のパラダイムに沿った、厚い(約0.5~0.7mm)シリコン基板40によって機械的に支持されている。

【0006】

図1には、エピタキシャル・シリコン層30上に組み立てた回路や光検知器などを相互接続するための金属層50も示してある。それぞれの金属層50は分離されていて、層間絶縁膜( I L D )60で保護されている。

40

【0007】

図1に概略的に示す構造で撮像することについての最も重要な問題は、光がシステムに入射するポイント70と、光が検出される、すなわち、光が光電子に変換されるシリコン30との距離が大きいということにある。図1に示すように、光は、実際にシリコンによって集められる前に、多数回にわたって反射や、掩蔽や、屈折を受けながら、多くの誘導体層および相互接続金属層(金属バスライン)を通って移動しなければならない。小サイズのピクセルの場合、「垂直方向距離 対 フォトダイオード」幅間のアスペクト比は、3:1にもなる。この比率は、峡谷でフラッシュ光を当てるに等しいものである。カラーフ

50

イルタやマイクロレンズと、シリコン表面との間の距離が大きいことにより、この装置では、集光効率が劣り、感度が低く、量子効率（QE）が低く、クロストーク(cross-talk)が大きく、角度応答が劣ることになる。

【0008】

特に、ピクセル・サイズを決めるときに、光学充填率（集光面積対ピクセル面積の比と定義されている）の損失によりQE損失が生じる。角度応答が悪いというのは、特にピクセル・サイズが縮小したときのアスペクト比の増大、並びに、金属縁における望ましくない反射や掩蔽の増大に起因する。クロストークが大きくなるのは、シリコン層とカラーフィルタ層との距離（ILD厚さで決まる）が大きいことによるものであると共に、受光角が変化したときの焦点の側方移動によるものである。

10

【0009】

換言すれば、図1のフロントサイド照明構造では、特にピクセル・サイズを決めようとするときの、QEの悪さと角度応答性の不均一であるとか、光学クロストークが大きくなることや、迷光結合が生じるという問題に悩まされる。反射防止のコーティングを追加するということは、好ましくない誘電率を有する層が多数あるために、そして、集光接合点の非平面性のせいで、ほとんど不可能である。

【0010】

金属の数や、ILDの厚さが、スケーリングと共に増大するので、実際のところ、技術スケーリング（technology scaling）が実際に問題をさらに悪化させ、結局は、アスペクト比のスキューイング（skewing）がいっそう高くなったりしてしまう結果となる。さらにまた、低-k誘電体の導入や、相互接続用の別の金属（たとえば、Cu）の使用も、金属・誘電体の積層体（stack）における吸収や拡散の増大を通して問題をさらに悪化させることが予想される。

20

【発明の開示】

【発明が解決しようとする手段】

【0011】

（要約）

第1の態様によれば、ここに開示する撮像構造を製作するウェーハ・レベル・プロセス（wafer-level process）は、シリコン・ウェーハと素子シリコン（device silicon）の間に埋められた酸化物層を含み、この酸化物層が撮像構造に不活性化層を形成するように用いられるようになるというウェーハを用意する工程と、素子層と層間絶縁膜を形成する工程と、シリコン・ウェーハを除去して酸化物層を露出させる工程と、から成る。

30

【0012】

第2の態様によれば、ここに開示するバックサイド照明式撮像素子製作用ウェーハ・スケール・プロセス（wafer-scale process）は、シリコン・ウェーハと素子シリコンとの間に埋められた熱酸化物層を含んでいるウェーハを用意する工程と、素子層を形成する工程と、該素子層に接続されるようになる層間絶縁膜を形成する工程と、該層間絶縁膜をガラス・ウェーハに結合する工程と、シリコン・ウェーハを除去する工程と、反射防止コーティングを付着させる工程と、から成る。

【0013】

40

第3の態様によれば、ここに開示する、ウェーハ上に撮像素子アレイを形成するための、シリコン・オン・インシュレータ（silicon-on-insulator；SOI）およびCMOSを組み合わせたプロセスは、絶縁体層と素子シリコン層とを含むSOIウェーハを用意する工程と、バルクCMOS手順フローを通して素子シリコン層を処理する工程と、撮像素子アレイを製作する工程と、から成る。

【0014】

本開示による構造は、極めて平坦で、100%の光学充填率をもたらすことで、これにより掩蔽をなくす。光が厚いILDを通って移動してアノード・シリコンに達する必要がないので、この構造は、垂直方向寸法と横方向寸法とのアスペクト比が低くなっている、その結果、優れた角度応答性と、低い光学クロストークをもたらすことになる。掩蔽ある

50

いは、望ましくない反射や屈折がないので、優れた角度応答性や、感度、QEを有する撮像素子を開発できる。

【0015】

本開示の構造の第1の利点は、接合ダイオード近辺に別のMOSFETが存在していても、100%充填率があるために量子効率が高いということにある。

【0016】

本開示の構造の第2の利点は、ILDを通して光学照明を行なっていたら存在したであろう多数の金属層およびILDからの望ましくない反射や掩蔽が存在せず、光がシリコンへ直接的に結合することによる、並びに、光が素子に入射するポイントと光が光電子に変換されるポイントとの距離をなくしたことによる、優れた角度応答にある。

10

【0017】

本開示の構造の第3の利点は、集光用に平坦な面を使用することが可能であることにより、マイクロレンズおよび反射防止コーティングを効果的に実現できることにある。

【0018】

さらに、本開示の構造によれば、電子シャッタリング、ADC実現(ADC implementation)、ゲイン・レンジング(gain-ranging)等々に対し適切なコンデンサと他の信号処理回路との一体化を可能にする。更にまた、本開示の構造においては、光は、光学変換層へ到達するのにILDを通らないので、次世代金属(たとえば、Cu)および低-k誘電体との互換性を得ることができる。

【0019】

20

図1は、従来技術によるフロント照明式ピクセルの集光部の垂直断面を示している。

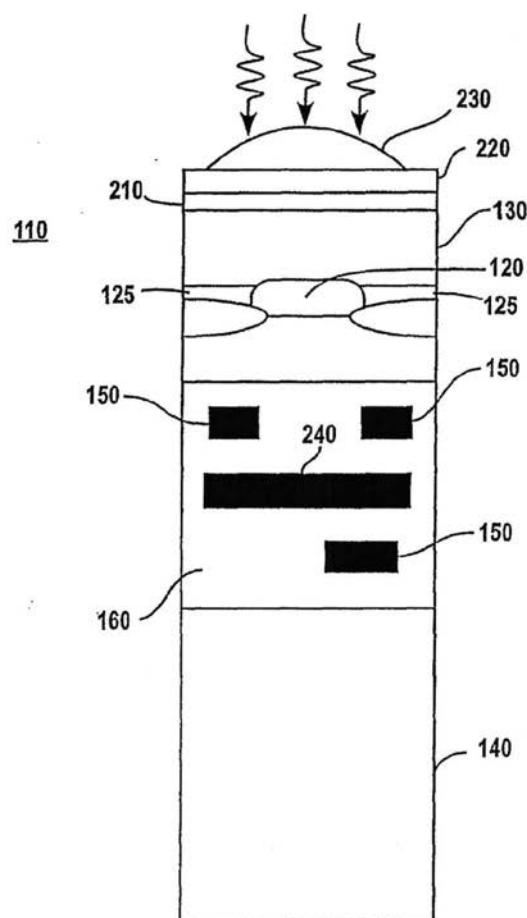

図2は、本開示によるCMOS/CCD撮像素子のためのバックサイド照明式ピクセルの集光部の断面を示している。

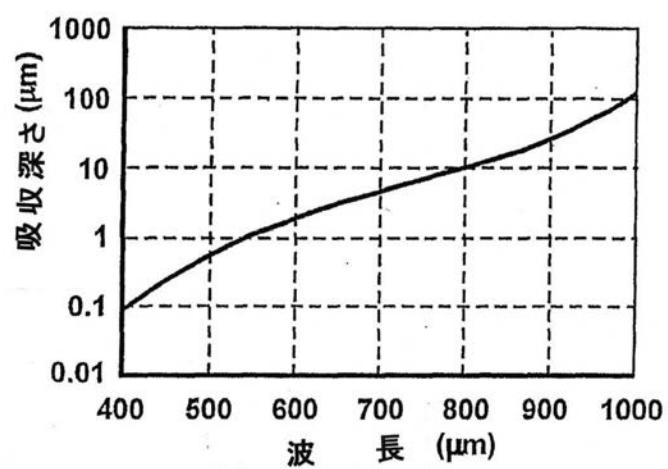

図3は、吸収深さの関数としての波長を示している。

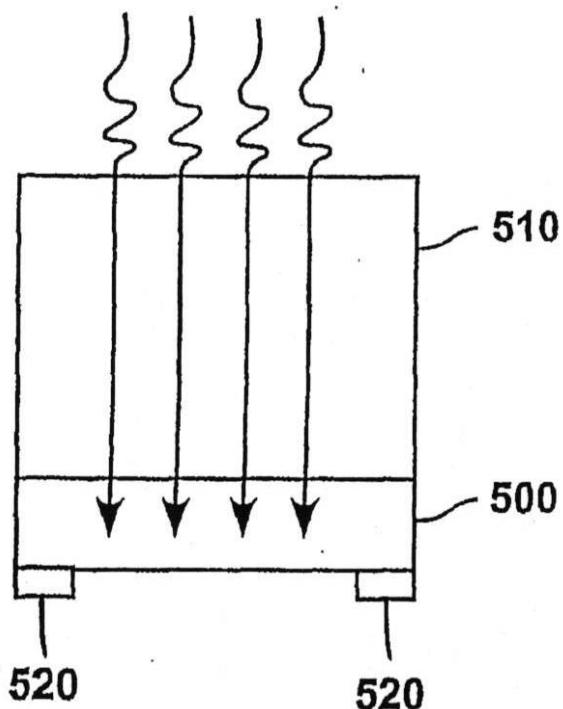

図4は、従来技術によるバックサイド照明式構造を示している。

図5は、本開示の一実施形態によるバックサイド照明式構造を示している。

図6は、撮像構造を製作する従来技術のフローチャートを示している。

図7は、撮像構造を製作する従来技術の断面図を示している。

図8は、本開示による撮像構造を製作する技術のフローチャートを示している。

図9A~9Eは、本開示による撮像構造を製作する技術の断面図を示している。

30

図10は、ウェーハ・レベルで見た図2、9Eの組み合わせの概略図を示している。

図11は、撮像素子アレイを製作するための、ウェーハ・レベルでのSOIバルクCMOS組み合わせプロセスの断面図を示している。

図12は、図11の構造の回路図を示している。

【発明を実施するための最良の形態】

【0020】

本開示では、バックサイド照明式撮像構造が提供される。

【0021】

図2は、本開示によるCMOS/CCD撮像素子のためのバックサイド照明式ピクセルの集光部の断面を示している。

40

【0022】

光検出器110は、接合カソードとして機能する深層埋め込みn-ウェル(n-well)120と、アノードとして機能する低ドープ処理エピタキシャル・シリコン層130とを含む。光検出器110は、基板140によって機械的に支持されている。基板140はガラスまたは有機物質であってよい。

【0023】

図1と同様に、図2も、エピタキシャル・シリコン層130上に作った回路および光検出機構の相互接続用の金属層150を示している。それぞれの金属層150は、分離されていて、層間絶縁膜(ILD)160によって保護されている。

【0024】

50

図2は、アノード・シリコン層130上に適用された不活性化層210を示している。この不活性化層210は、暗電流を許容レベルまで下げるようになることができる、充分なQEが得られるようになることができる。また、図2には、反射防止コーティング220とマイクロレンズ230も示してある。また、カラーフィルタを設けることもできる。不活性化層210は、また、コーティング220、カラーフィルタ、およびマイクロレンズ230を積層する最中に、下層のシリコン130に対する損傷を与えるのを防止することができる。

#### 【0025】

当業者であれば、本開示による装置においては、集光ポイントを光検出器へいっそう近くに持ってこられることは了解できよう。

10

#### 【0026】

接合カソード120の隣に、さらにp-型インプラント125を加えることで、ピクセル対ピクセルのクロストークを防ぐことができる。更には、反射体層240をILD160に埋め込むことで、より長い波長の光子がアノード・シリコン130を多数回通過されることによって、より良好な赤色反応をもたらすことができる。金属反射層240（たとえば、AlまたはCu製）も、また、望ましくない反射を阻止することによってピクセル間の長波長（赤色）クロストークを防ぐ。

#### 【0027】

この段落では、金属反射層240を作るプロセスを簡単に説明する。CMOSプロセスは、多数の金属スタックを含む。全反射層240を実現するためには、金属層が一層、確保される。反射層は、赤色反応および赤色クロストークを改善するのを可能にする。シリコンにおける光の吸収深さは、光の波長が大きくなるにつれて増大する。吸収深さとは、入射光の63%が吸収され且つ光電子に変換される、という深さをいう。

20

#### 【0028】

吸収率の波長依存性は周知のところであり、図3に示してある。この図からわかるように、吸収深さは、400μm（青色光）ではたったの0.1μmであるが、700μm（赤色光）では5μm以上に達する。

#### 【0029】

素子シリコンの厚さがわずか3~4μmであれば、大部分の赤外線光及び近赤外線光は、バック照明式撮像素子構造においては吸収されずに、シリコンを通り抜けてしまう。これらの光子は、異なったインターフェース（たとえば、ILDベースのインターフェース）から異なった深さで元の方向に散乱し、次いで、シリコンによって捕獲される。これらの疑似反射および散乱反射は、多数の画像アーティファクト、たとえば、ゴースト、拡散バックグラウンドからのハロー、画像ぼけ、およびエタロニングなどを発生することで、画質をかなり損なう。

30

#### 【0030】

本開示による層240の存在により、これらの望ましくない反射を除去することができる。金属反射体層は、パターン化されてピクセル構造と整合され、方向性のある反射をもたらし、疑似光結合を抑制する。また、CMOSプロセスについては、これらの反射体はシリコン表面の近くに存在する。層240は2つの目的を果たす。まず第一に、素子シリコンにおいて迅速に吸収されて赤色感度を高めることができるようになるために、層240は、シリコン表面の近くから未吸収の光を元の方向に反射させる。第二に、素子シリコン層近くにあって、高反射性表面をもたらすことによって、層240は、方向性のある反射を行い、散乱疑似反射を抑制し、画質を改善する。層240の存在が、上部に設けた、光を小さな既知のスポットに合焦させるマイクロレンズと共に作用することで、最高の効果を与える。

40

#### 【0031】

バック照明式撮像素子それ自体は周知である。図4に示すように、これらの撮像素子は、透明な基板510に装着したシリコン素子層500（図2のシリコン層130に機能的に類似している）を備え、金属結合パッド520がチップのフロントサイドに存在する。

50

透明な基板 510 は機械的支えを提供するので、故に、数百  $\mu\text{m}$  の厚さが有る。光は、この透明な基板 510 を通過した後で、その下に存在するシリコン撮像素子層において吸収されるようになっている。また、金属パッド 520 は光が撮像素子に入射する側とは反対側に配置されているので、このため標準的でないパッケージング構造を使わなければならない。

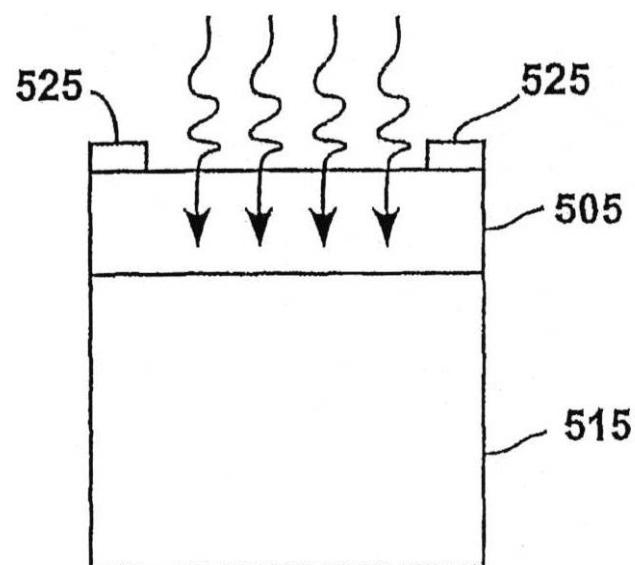

【0032】

図5は、本発明の一実施形態による異なったアプローチを示している。金属パッド 525 がシリコン・ウェーハの裏面を貫いて引き出されており、結合基部 515 の形になる機械的な支持がシリコン 505 の下方に位置している。

【0033】

図5の構造は、いろいろの利点を提供する。第1の利点は、図4の従来構造では、光は数百  $\mu\text{m}$  の透明材料 510 を通過してからシリコン層 500 で吸収されなければならない、ということである。このことは、角度応答を著しく現ずると共に、光学クロストークを非常に劣化させる結果となる。図5の構造においては、光入射ポイントと集光ポイントとの間にスペーサ 510 がまったくない。スペーサ 510 の排除は、角度応答を改善し、光学クロストークを防止するために、重要である。

【0034】

第2の利点は、従来構造では、スペーサ材料 510 の厚さが、カラーフィルタ、反射防止コーティングおよび/またはマイクロレンズを適用して整合させることを不可能にさせる、ということである。図4に示すような従来構造は、スペーサ 510 を取り除くことによってこそ、光学性能およびアライメントの容易の両の点において、非常に効率的な、カラーフィルタ、反反射コーティング、マイクロレンズの一体化が実現可能になるのである。

【0035】

さらに別の利点は、図5の構造においては、金属パッド 525 が光入射側と同じ側にあるということである。したがって、図5の構造は、標準のパッケージング構成およびプロセスと完全に互換性を持ち、それ故、低コストで信頼性の高い解決策を可能にする。

【0036】

以下、図2および図5の撮像素子を製作するための方法を説明する。

【0037】

図2及び図5に示す構造を得る際の主課題は、以下の通りである。

【0038】

1. 表面非平坦度が /10 よりも小さく、たとえば、5~15  $\mu\text{m}$  のオーダーの適切な厚さのエピタキシャル・シリコン層の精密形成。ここで、は検出されるべき最短波長である。ウェーハ・レベル・バックサイド・シンニング (wafer-level backside thinning) は、200~300 mm ウェーハ全体にわたって、500~700  $\mu\text{m}$  ウェーハを、限界の薄さの 5~15  $\mu\text{m}$  にまで、均一に薄くしなければならない（残った局所非均一性は 50 ナノメートル未満）。均一性を欠くということは、適切なエッチストップ層がないことに起因する。大抵のエッチ・ストップ (etch stop) は、エッチングを終わらせるのに、シリコン・ドーピングの差に依存する。しかし、半導体微細加工に固有の熱プロセス後は、高ドープ処理領域と軽ドープ処理領域との境界がひどく汚されるので、これは極めて困難な提案である。

2. 拡散によるキャリア収集の最小化のための構造の形成。

3. 光を浴びるシリコン表面の不活性化、すなわち、ダングリング・ボンド (dangling bonds) およびインタフェース・トラップ密度を、撮像に相応したレベルまで低減すること。シンニング (thinning) した後に、露出したシリコン表面には高密度のインタフェース・トラップができ、これが、暗電流におけるマグニチュード増加の程度および青色量子効率の損失（より短い波長光の吸収深さが非常に小さいので）を招くことになる。ウェーハのフロントサイドに低融点の金属が存在するせいで、インプラントをアニーリング (annealing) するために高温工程を使用することができないので、これらのトラップを不

10

20

30

40

50

活性化するためには、従来とは違う技術を使用する必要がある。しかし、ウェーハ - スケールでは、従来形とは違う不活性化技術を使用しないでもすむ。

4. ダイ - レベル処理 (die-level processing) の代わりのウェーハ - レベル処理 (wafer-level processing)。

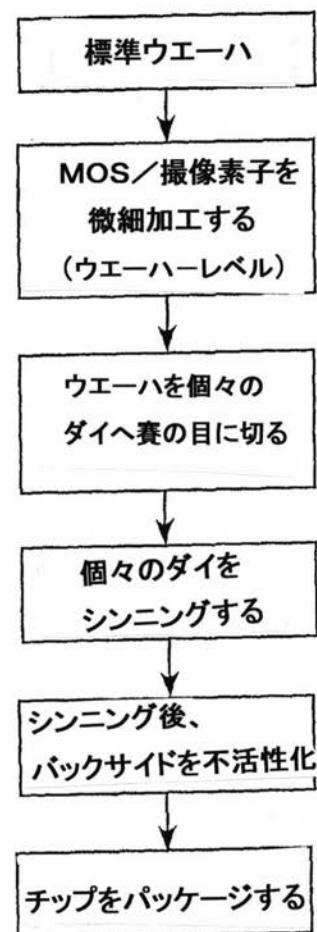

【0039】

図6は、従来技術によるシンニング・プロセス (thinning process) における一連の工程を示している。この図に示すように、シンニングは、ウェーハを個々のダイへ賽の目に切った後に行う。

【0040】

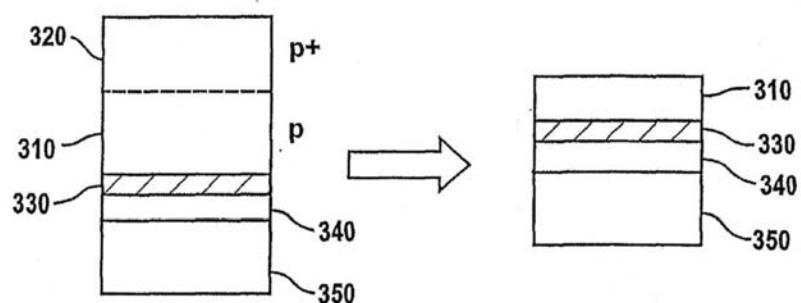

図7は、図6のプロセスによる撮像構造を製作するためのダイ - レベル技術を示している。従来のMOS微細加工プロセスフローを使用して高ドープ処理した基板320上で、エピタキシャル・シリコン層310を成長させる。そして、金属化を含むすべてのMOS処理を実施した後に直ちに高ドープ処理したp+基板320をエッティングする。図6は、素子層330、ILD層340、およびバッキング材料350を概略的に示している。

【0041】

上述のアプローチは、2つの制限を受ける。第一に、適切なエッチ・ストップ層の欠如していることが、制御されていないp-層の厚さという結果を招く。シリコンのエッティングは、タイムド・エッチ (timed-etch) として行なうか、または、ドーパント選択エッチストップ層を用いるか、のどちらかによって行なう。「p+基板の開始厚さ」対「最終p-層厚さ」の比は非常に高い(約50~100)ので、均一で精密に制御したp-層厚さを有する最終構造(図7の右側)を確実に製造することは非常に困難である。後者のアプローチでは、適切なドーパント選択シリコン・エッチ (dopant-selective silicon etches) の使用が可能である。

【0042】

第二に、図7のアプローチでは、望ましくない撮像構造となる可能性がある。シリコン微細加工に固有の高温処理のせいで、図7の左部分の概略断面図で暗示しているように、p+基板320とp-エピタキシャル層310との間のインターフェースがはっきりと定まつていない。310-320インターフェースにおけるドーパントの汚し (smearing of dopants) は、p-層320の望ましくなくドープ処理を生じさせ、撮像性能の損失を引き起こす。加えて、この汚し (smearing) は、ドーパント選択エッチストップ層が、p+基板320およびp-エピタキシャル層310からの急激なドープ処理移行を必要としたであろうから、p-層の精密に制御された厚さをもたらす能力を損なう。

【0043】

さらに、シンニング後、未完成のシリコン表面でのインターフェース・トラップ密度は容認できないほど高く、その一方、自然に形成された自然酸化物(約20 nmの厚さ)が表面を正に帯電させる。望ましくないバンド・ベンディング (band-bending)、そしてダンギング・ボンド (dangling bonds) の存在は、QEの損失と、容認できないほど高い暗電流を引き起こす結果となり、図6に示す構造を撮像のために使用できなくしてしまう。

【0044】

図7に示す構造の表面不活性化は、それ自体に特有の問題を生じさせる。シンニングおよび不活性化は、金属化後プロセス工程として実施されるので、フロントサイドが既に低融点金属(たとえば、Al)で覆われているため、高温(>400 °C)処理工程を行ってはならない。したがって、インプラント活性化は高温アニールを必要とするので、このような場合には、埋め込みによる表面不活性化は使用することができない。

【0045】

この問題を解決するためには、相互接続用に、耐火性金属および多数の多結晶シリコン層を使用するとよい。しかしながら、このような技術は、低融点を有する金属を使用するCMOSプロセス・フローと互換性を持たない。他の不活性化技術としては、紫外線フラッディング (UV-flooding)、フラッシュ・ゲート (MBE付着させた金属の単一層)、ホウ素ドーピングに続く高エネルギー・パルスレーザ・アニール、低圧酸化物体積、分子

10

20

30

30

40

50

ビーム・エピタキシー (MBE) によるデルタ・ドーピング (delta doping) がある。

【0046】

上述したプロセスは複雑で、従来技術にないツールを必要とし、これによりこのようなプロセスに大量シリコン微細加工との互換性を持たせないようにしてしまい、信頼性および収率の厳しい損失を引き起こすことになる。したがって、CCDシンニングは、ダイ・レベルで実施され、ウェーハ・レベルでは実施しないのが普通であり、このことが、バックサイド照明式撮像装置が、再現性、収率、および信頼性に劣るという問題を生じさせ得る主な理由の1つである。

【0047】

これ以降の段落では、上記の問題を解決する方法であって、CCDまたはCMOS撮像素子製作に等しく適用できる方法を説明する。 10

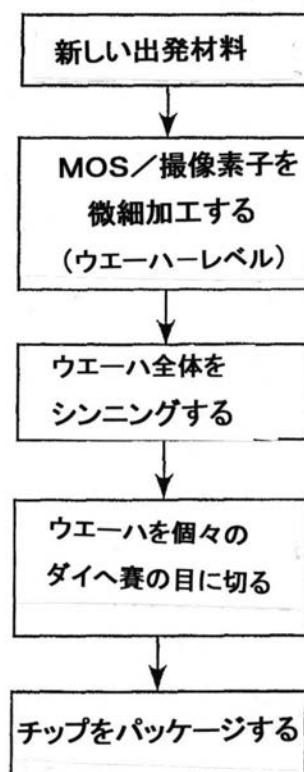

【0048】

図8は、本開示の一実施形態によるシンニング・プロセスの一連の工程を示している。図8の3番目の工程に示すように、シンニングは、ウェーハ・レベルで行い、従来技術のようにダイ・レベルでは行わない。図8によるアプローチにおいては、上述の問題は以下のようにして解決される。

【0049】

シリコン表面を予め不活性化させた状態の新しい出発材料を使用。事前不活性化は、シリコン表面上でSiO<sub>2</sub>を成長させることによって実施される。

【0050】

精密なエッチトップ層の使用。この構造は、シリコンに対し精密エッチトップ層として機能する埋込酸化物層を含む。たとえば、90°でのTMAH (テトラメチルアンモニウム・ヒドロキシド; tetramethylammonium hydroxide) によるシリコンのエッティング速度は、SiO<sub>2</sub>の速度よりも4桁大きい。 20

【0051】

バックサイド・シリコン表面の保護。本開示によるプロセスでは、バックサイド・エッティングは、素子シリコン上部 (撮像素子が存在するところ) に配置してある埋め込みSiO<sub>2</sub>のところで止まる。故に、素子シリコンはシンニング・プロセス中に絶対に露出することがないので、シリコン表面は、エッティングの悪影響から保護される。したがって、従来のバックサイド・シンニング・アプローチとは異なり、バックサイド・エッティングをしても、インタフェース・トラップがシリコン・バックサイドに生じることは全くない。したがって、本開示によるアプローチでは、バックサイドについての事後シンニング不活性化工程の必要性がまったくなく、これにより、バックサイド照明式撮像素子製作の主要な問題点の1つを解決することになる。 30

【0052】

図9A～9Eは、図8のプロセスによる撮像構造を製作するウェーハ・レベル技術を示している。

【0053】

図9A～9Eの実施形態によれば、高ドープ処理したp-型基板上で成長させたp-エピタキシャル層を含む従来のバルクCMOSウェーハを使用する代わりに、特殊な絶縁体上シリコン (SOI; silicon-on-insulator) ウェーハを使用する。 40

【0054】

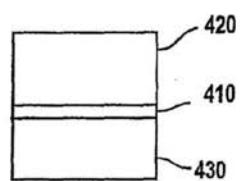

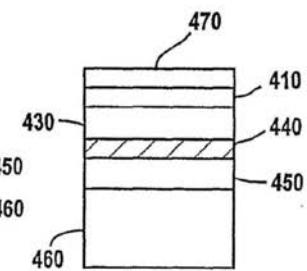

図9Aは出発ウェーハを示しており、低ドープ処理した厚いシリコン・ウェーハ (p型でも、n型でもいずれでもよい) 420と、素子シリコン (たとえば、5 μm厚、2×1014/cm<sup>3</sup>のホウ素ドープ処理したもの) 430との間に、熱酸化物層410が埋め込まれているようになっている。厚いシリコン・ウェーハ420は機械的支持に対するハンドル・ウェーハとして使用される。

【0055】

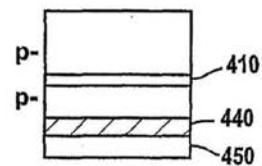

SOIウェーハを用いて出発しているけれども、ウェーハ・レベルでは、埋め込み・酸化・ILD・金属付着・パターニングによってCMOS撮像素子を生成するには、従来の 50

バルク C M O S プロセス・フローが使用できる。どのようなバルク C M O S プロセスでも使用でき、たとえば、撮像に対し最適化したバルク C M O S プロセスが使用され得る。C M O S 製作後、図 9 B に示す構造が得られる。図 9 B には、素子層 4 4 0 および I L D 4 5 0 も示してある。

【 0 0 5 6 】

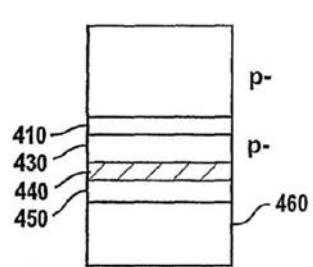

バックサイド照明に備えるために、この構造は、図 9 C に示すように、機械的支持としてのガラス・ウェーハ 4 6 0 に結合する。

【 0 0 5 7 】

図 9 D に示す工程において、シリコン・ハンドル・ウェーハ 4 2 0 は、たとえば、機械的な研磨や、ウエットエッチング、および / または R I E エッチング ( 反応性イオン・エッチング ) によって、除去される。そして、埋込み S i O 2 層 4 1 0 が固有のエッチストップ層を提供することとなり、これにより、均一に平らなバック表面をもたらす。

10

【 0 0 5 8 】

さらに、こうしてできた構造は、撮像中に光を浴びるよう露出されるようになる熱的に成長した S i O 2 インタフェースを含んでいるため、自動不活性化される。故に、シリコンを酸化物層で終わらせることが、更なる不活性化処理を必要とさせるものであり、これにより、標準の V L S I 処理では達成するのが難しいばかりか、互換性を持たすのも難しいであろうような、追加の不活性化処理の必要性をなくす。出発材料 4 1 0 を使用することに起因して不活性化は自動的になるので、図 9 A ~ 9 E に記載したプロセス・フローは、完全に C M O S 互換性を持ち、ウェーハ - レベルで実施される。

20

【 0 0 5 9 】

さらにまた、素子シリコンは、埋込み酸化物を介してハンドル・ウェーハから隔離されているので、C M O S 処理中に、素子シリコンの意図しないドーピングが生じることが全くない。したがって、出発材料の選択時間中に、処理工程を変えることなく、素子シリコン層の適切なドープ処理を選択することが可能になる。このことは、高電荷収集効率 ( フィールド無しの領域の最小化 ) では、バルク C M O S プロセスを経たバルク C M O S ウェーハでは達成するのが難しい、もっと低いレベルの素子シリコン・ドーピングが必要となるために、特に決定的なことである。

【 0 0 6 0 】

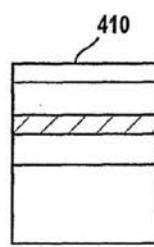

図 9 E は、プロセスの最終工程、すなわち、S i - S i O 2 インタフェースでの反射を抑制することによって光学的結合を改善するための反射防止コーティング 4 7 0 の堆積工程を示している。こうしてできた構造は、完全に平らであり、単一の S i O 2 層 ( 多層誘電体と対照的 ) のみを有するため、フロント照明の場合では光が多層の不均一な I L D を通って進んだ場合も、可能ではあったであろう反射防止層を、完璧に自由に創り、最適化できるようにするのである。

30

【 0 0 6 1 】

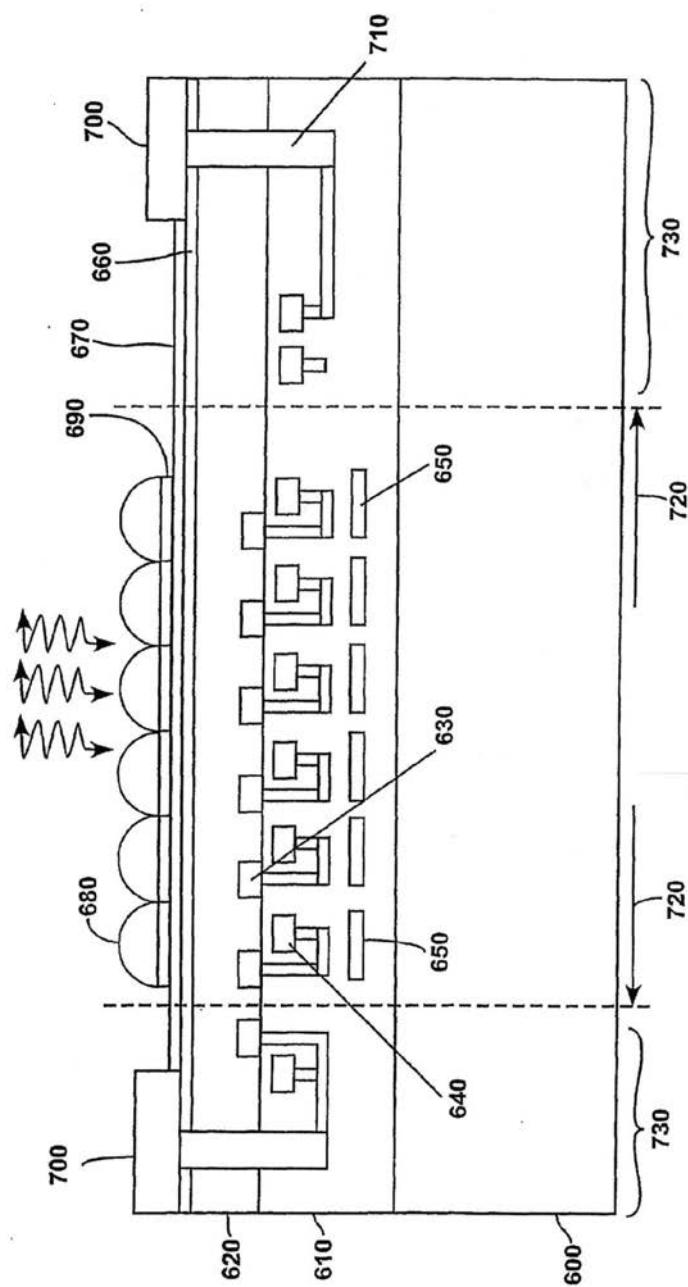

図 1 0 は、ウェーハ - レベルで見た、図 2 、図 9 E の組み合わせの概略図を示している。結合基部 6 0 0 ( 図 2 の要素 1 4 0 , 図 5 の要素 5 1 5 、および図 9 C ~ 9 E の要素 4 6 0 も参照 ) が層間絶縁膜 ( I L D ) 6 1 0 ( 図 2 の要素 1 6 0 および図 9 B ~ 9 E の要素 4 5 0 も参照 ) に連結している。I L D 6 1 0 はシリコン層 6 2 0 ( 図 2 の要素 1 3 0 、図 5 の要素 5 0 5 、および図 9 A ~ 9 E の要素 4 3 0 も参照 ) に連結している。フォトダイオード 6 3 0 および M O S ゲート 6 4 0 が、I L D 6 1 0 、シリコン層 6 2 0 間に配置してある。また、複数の金属反射体 6 5 0 ( 図 2 の要素 2 4 0 も参照 ) も示してある。不活性化層 6 6 0 ( 図 2 の要素 2 1 0 を参照 ) がシリコン層 6 2 0 の上部に配置してあり、反射防止コーティング 6 7 0 ( 図 2 の要素 2 2 0 を参照 ) が不活性化層 6 6 0 上方に配置してある。複数のマイクロレンズ 6 8 0 も、カラーフィルタ 6 9 0 と共に示してある。金属パッド 7 0 0 ( 図 5 の要素 5 2 5 を参照 ) がウェーハの両側に配置してある。これらのパッドは相互接続金属 7 1 0 によって I L D 6 1 0 と連結している。矢印 7 2 0 は、図 8 の 4 番目の工程に従って賽の目に切ることによって得られることになる、撮像アレイを形成する個々のダイの広がりを表している。ウェーハの両側のところの領域 7 3 0 にある

40

50

要素は、金属パッド700および相互接続金属710を含み、撮像機能のない支持電子機器を形成している。したがって、本開示に従って得られるウェーハは、2つの側部領域730と、個々のダイに賽の目に切られ、パッケージされた複数の撮像アレイ領域を含むことになる。

【0062】

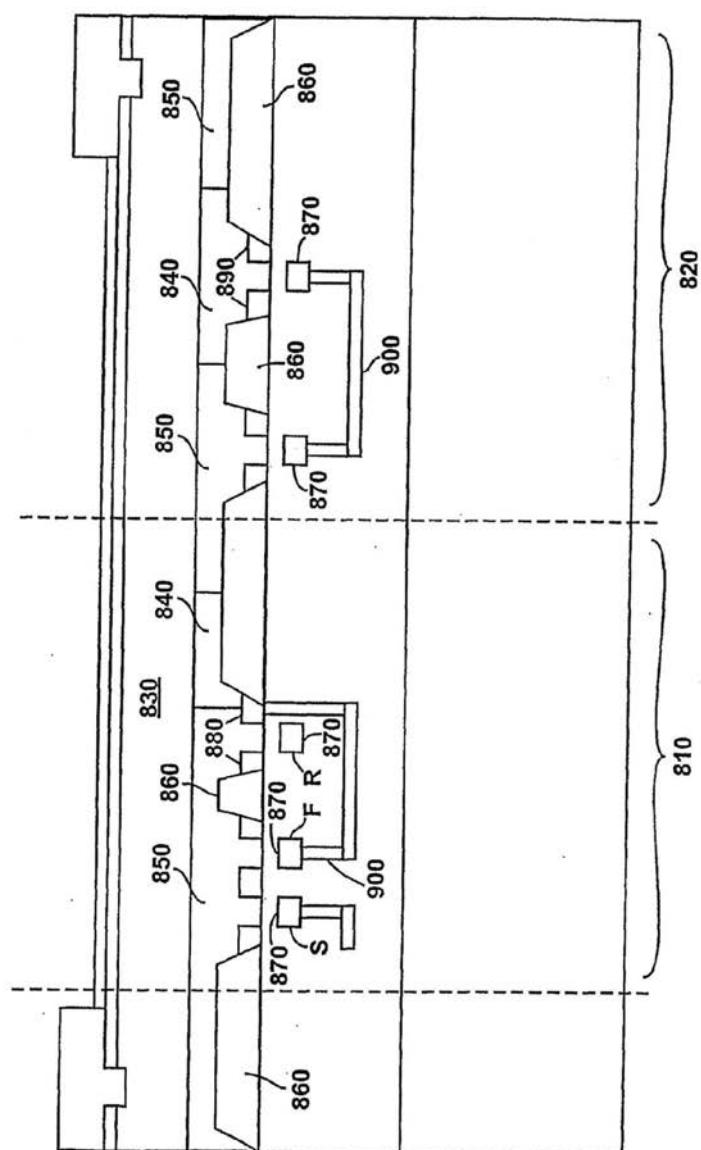

図11、図12は、本開示によるさらに別の実施形態を示している。図11において、撮像チップは、2つのセクションに分割されている。すなわち、撮像アレイを含む第1の領域810と、CMOS周辺/信号処理回路を含む第2の領域820とに分割されている。撮像アレイおよびCMOS回路は、標準のバルクCMOS撮像素子互換製作プロセスを使用して標準のSOIウェーハ(図9Aも参照)上にある素子シリコン830(図8A~8Eの要素430も参照)上に構成されている。

10

【0063】

本開示による構造の好ましい素子シリコン厚さは、充分な光学反応を与えるために、従来SOIシリコンの0.5μm以下の厚さとは異なって、約3μm~約10μmである。

【0064】

このシリコン厚さを考えると、ウェーハはSOIタイプであるが、本開示による素子を製作するためにはバルクCMOSプロセスが用いられるのが好ましい。すべての最新式CMOS撮像素子プロセスがバルクCMOSタイプのあるため、バルクCMOSプロセスの使用は有利である。したがって、本開示による構造では、2つの多様な要素を混合することによって、すなわち、新しいSOIタイプの出発材料にバルクCMOSプロセスを適用することによって、高品質CMOS撮像素子を実現できる。

20

【0065】

異なったシリコン層のドーピング濃度を以下の表に示す。

【表1】

| 層      | 厚さ      | タイプ | 濃度                                                     |

|--------|---------|-----|--------------------------------------------------------|

| 素子シリコン | 3~10μm  | P   | $1\times10^{14}\sim1\times10^{15}$<br>/cm <sup>3</sup> |

| P-ウェル  | 0.5~1μm | P   | $5\times10^{16}\sim5\times10^{17}$<br>/cm <sup>3</sup> |

| N-ウェル  | 1~2μm   | N   | $5\times10^{16}\sim5\times10^{17}$<br>/cm <sup>3</sup> |

30

この表に示すドーピング濃度は、概算であり、使用される特定の製作法に基づいて変わることになる。素子シリコン830のドーピング濃度は、素子シリコンの厚さに基づいて選択される。素子シリコンの厚さは、ここでも、必要な赤色反応の程度に基づいている。素子シリコン厚さが増大するにつれて、空乏領域厚さを増大させ、非空乏シリコンの量を最小限に抑えるためにドーピング濃度は減らすことになる。非空乏シリコンの最小化は、量子効率(それ故、感度)およびクロストーク性能の両方の改善にとって重要である。したがって、出発材料は、シリコンの厚さおよびそのドーピング濃度を変えることによって必要な赤色反応について最適化できる。

40

【0066】

再度図11に戻ると、バルクCMOSプロセス・フローの後、撮像素子アレイおよび支持体電子機器回路を以下の通りに組み立てる。すべてのMOS素子は、フロントサイドから埋め込んだn-ウェル840およびp-ウェル850内にある。LOCOSまたはSTI(浅溝隔離)構造の形とした隔離酸化物(熱および/または堆積)を用いて素子は互い

50

に隔離されている。図11は、STI要素860を有するSTI隔離構造体を示している。このプロセスにおいて、n-ウェルとp-型素子シリコン層との間にフォトダイオードも形成される。

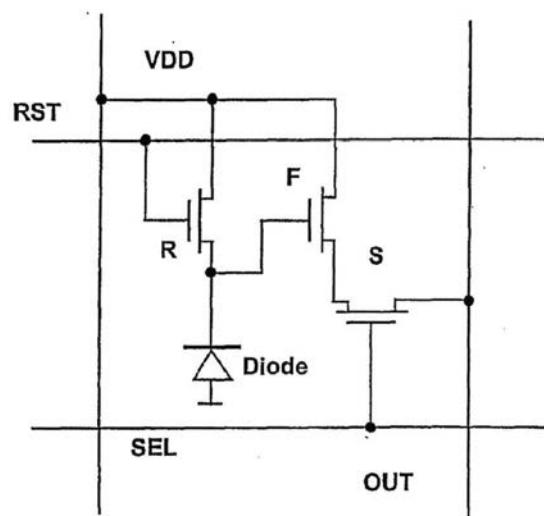

【0067】

上記工程の後に、ゲート酸化物を成長させ、その後、MOSFETポリシリコン・ゲート870の付着およびパターニングを行う。ソース・ドレイン(S/D)インプラント880(N+)、890(P+)を、自動位置合わせ状態(それぞれのポリシリコン・ゲート870に整合)で実施し、完全なMOSFET構成物を完成する。ピクセルのFETは、S(セレクトFET)、R(リセットFET)およびS(ソースフォロアFET)のラベルを付ける。ピクセル回路は図12に示してある。

10

【0068】

図11、図12に示すように、フォトダイオードのカソードまたはn-ウェル840は、RFETのソース880に接続している。S/Dインプラント(たとえば、880, 890)およびゲート870は、典型的には酸化物および窒化物からなる堆積ILDスタックによって互いにかつシリコンから分離されている金属線900によって接続してある。

【0069】

要約すると、バック照明式CMOSまたはCCD撮像素子の製作方法を、本開示の1つまたはそれ以上の実施形態で説明してきた。シリコン・ウェーハと素子シリコンとの間に埋設した酸化物層がもたらされ、この酸化物層が撮像構造の不活性化層を形成する。また、素子層および層間絶縁膜も形成し、そして、シリコン・ウェーハを除去して、酸化物層を露出させる。

20

【0070】

本発明のいくつかの図示実施形態を本明細書に示し、説明してきたが、数多くの変更例および代替実施形態が当業者には明らかであろう。このような変更例および代替実施形態も本発明では意図しており、添付の特許請求の範囲に定義されているような発明の範囲から逸脱することなくそれらを実施することは可能である。

【図面の簡単な説明】

【0071】

【図1】従来技術によるフロント照明式ピクセルの集光部の垂直断面。

【図2】本開示によるCMOS/CCD撮像素子のためのバックサイド照明式ピクセルの集光部の断面。

30

【図3】吸収深さの関数としての波長。

【図4】従来技術によるバックサイド照明式構造。

【図5】本開示の一実施形態によるバックサイド照明式構造。

【図6】撮像構造を製作する従来技術のフローチャート。

【図7】撮像構造を製作する従来技術の断面図。

【図8】本開示による撮像構造を製作する技術のフローチャート。

【図9】本開示による撮像構造を製作する技術の断面図で、図9Aは出発ウェーハを示しており、図9BはCMOS製作後に得られる構造を示し、図9Cは構造が機械的支持としてのガラス・ウェーハ460に結合するのを示し、図9Dは、シリコン・ハンドル・ウェーハが除去され、埋込みSiO<sub>2</sub>層410が露出して固有のエッチストップ層を提供するのを示しており、図9Eは反射防止コーティング470の堆積工程であるプロセスの最終工程を示している。

40

【図10】ウェーハ・レベルで見た図2、図9Eの組み合わせの概略図を示している。

【図11】撮像素子アレイを製作するための、ウェーハ・レベルでのSOIバルクCMOS組み合わせプロセスの断面図を示している。

【図12】図11の構造の回路図を示している。

【図1】

(従来技術)

【図2】

【図3】

【図4】

(従来技術)

【図5】

【図6】

(従来技術)

【図7】

(従来技術)

【図8】

【図9】

9A

9B

9C

9D

9E

【図10】

【図11】

【図 1 2】

---

フロントページの続き

審査官 瀧内 健夫

(56)参考文献 特開2005-150521(JP, A)

特開2003-031785(JP, A)

国際公開第2004/027879(WO, A2)

国際公開第2004/054001(WO, A2)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14 - 27/148