(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3987521号

(P3987521)

(45) 発行日 平成19年10月10日(2007.10.10)

(24) 登録日 平成19年7月20日(2007.7.20)

(51) Int.C1.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| HO1L 23/12 | (2006.01) | HO1L 23/12 | N    |

| HO5K 1/11  | (2006.01) | HO1L 23/12 | 501B |

| HO5K 3/40  | (2006.01) | HO5K 1/11  | N    |

|            |           | HO5K 3/40  | K    |

請求項の数 13 (全 20 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2004-323939 (P2004-323939)  |

| (22) 出願日  | 平成16年11月8日 (2004.11.8)        |

| (65) 公開番号 | 特開2006-135174 (P2006-135174A) |

| (43) 公開日  | 平成18年5月25日 (2006.5.25)        |

| 審査請求日     | 平成18年7月19日 (2006.7.19)        |

早期審査対象出願

|           |                                           |

|-----------|-------------------------------------------|

| (73) 特許権者 | 000190688<br>新光電気工業株式会社<br>長野県長野市小島田町80番地 |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                    |

| (72) 発明者  | 山野 孝治<br>長野県長野市小島田町80番地 新光電気<br>工業株式会社内   |

| 審査官       | 今井 拓也                                     |

最終頁に続く

(54) 【発明の名称】 基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

貫通孔が形成された基材と、該基材の貫通孔に配設された貫通ビアとを備え、前記貫通ビアは、前記貫通孔に配置された貫通部と、該貫通部の一方の端部に設けられ、前記基材から突出した第1の突出部と、を有する基板の製造方法であって、前記貫通孔が形成された前記基材を、第1のレジスト層を介して、給電層上に配置する基材配置工程と、

前記貫通孔に露出された部分の前記第1のレジスト層を除去して、前記給電層を露出させると共に、前記貫通孔の寸法よりも幅広形状の鍔状空間を形成する鍔状空間形成工程と、前記鍔状空間形成工程後に、前記第1のレジスト層を第1の熱処理により硬化させる第1のレジスト層硬化工程と、

第1のレジスト層硬化工程後に、前記給電層からの給電により形成される導電性金属膜により、前記鍔状空間及び前記貫通孔を充填して前記貫通ビアを形成する貫通ビア形成工程と、を含むことを特徴とする基板の製造方法。

## 【請求項2】

貫通孔が形成された基材と、該基材の貫通孔に配設された貫通ビアとを備え、前記貫通ビアは、前記貫通孔に配置された貫通部と、該貫通部の一方の端部に設けられ、前記基材から突出した第1の突出部と、を有する基板の製造方法であって、前記貫通孔が形成された前記基材を、第1のレジスト層を介して、給電層上に配置する基材配置工程と、

10

20

前記貫通孔に露出された部分の前記第1のレジスト層と、前記基材と前記給電層との間に位置する部分の前記第1のレジスト層とを除去して、前記基材と前記給電層との間に、前記貫通孔の寸法よりも幅広形状の鍔状空間を形成する鍔状空間形成工程と、

前記給電層からの給電により形成される導電性金属膜により、前記鍔状空間及び前記貫通孔を充填して前記貫通ビアを形成する貫通ビア形成工程と、を含み、

前記第1の突出部は、前記鍔状空間に前記導電性金属膜を充填することで形成することを特徴とする基板の製造方法。

#### 【請求項3】

前記給電層は、支持板に設けられた金属箔であり、

前記金属箔は、前記鍔状空間に露出されていることを特徴とする請求項1又は2記載の基板の製造方法。 10

#### 【請求項4】

前記基材上に前記貫通孔を露出すると共に、前記貫通孔の寸法よりも幅広形状となる第1の開口部を有した第2のレジスト層を形成する第2のレジスト層形成工程を設けると共に、前記第1の開口部を前記導電性金属膜により充填し、前記貫通部の他方の端部に設けられ、前記基材から突出すると共に、前記貫通部の寸法よりも幅広の形状とされた第2の突出部を形成することを特徴とする請求項1ないし3のうち、いずれか一項記載の基板の製造方法。

#### 【請求項5】

前記鍔状空間形成工程後に、前記第1のレジスト層を第1の熱処理により硬化させる第1のレジスト層硬化工程を設けたことを特徴とする請求項1ないし4のうち、いずれか一項記載の基板の製造方法。 20

#### 【請求項6】

前記鍔状空間形成工程後に、電解めっき法により、前記鍔状空間に露出された前記金属箔に第1の拡散防止膜を形成する第1の拡散防止膜形成工程を設けたことを特徴とする請求項3ないし5のうち、いずれか一項記載の基板の製造方法。

#### 【請求項7】

前記第2の突出部と接続される配線を形成する配線形成工程をさらに設けたことを特徴とする請求項4ないし6のうち、いずれか一項記載の基板の製造方法。

#### 【請求項8】

前記配線形成工程は、

前記第2のレジスト層を除去する第2のレジスト層除去工程と、

前記基材上に、前記第2の突出部を露出する第2の開口部を有した絶縁層を形成する絶縁層形成工程と、

前記配線が形成される部分の前記絶縁層に、シード層を形成するシード層形成工程と、を有し、

前記絶縁層には、パラジウムを含有させた樹脂を用いることを特徴とする請求項7に記載の基板の製造方法。

#### 【請求項9】

前記配線は、外部接続端子を有しており、

前記配線形成工程後、電解めっき法により前記外部接続端子に第2の拡散防止膜を形成する第2の拡散防止膜形成工程を設けたことを特徴とする請求項7または8に記載の基板の製造方法。 40

#### 【請求項10】

前記第2の拡散防止膜形成工程後に、

少なくとも前記配線及び第2の拡散防止膜を覆うよう耐熱性を有した保護部材を配設する保護部材配設工程と、

前記保護部材配設工程後、第2の熱処理により、前記基材から前記支持板を離脱させる支持板離脱工程と、を設けたことを特徴とする請求項9に記載の基板の製造方法。

#### 【請求項11】

10

20

30

40

50

前記支持板離脱工程後に、前記金属箔をエッティングにより除去する金属箔除去工程と、前記第1のレジスト層を除去する第1のレジスト層除去工程と、該第1のレジスト層除去工程後に、前記保護部材を除去する保護部材除去工程と、を設けたことを特徴とする請求項10に記載の基板の製造方法。

#### 【請求項12】

前記第1の拡散防止膜形成工程は、前記支持板に前記金属箔を設けた直後に行うことを特徴する請求項6ないし11のうち、いずれか一項記載の基板の製造方法。

#### 【請求項13】

前記第1のレジスト層を現像液により除去することを特徴とする請求項1ないし12のうち、いずれか一項記載の基板の製造方法。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、基板の製造方法に係り、特に基材を貫通する貫通ビアと、貫通ビアと接続される配線とを備えた基板の製造方法に関する。

##### 【背景技術】

##### 【0002】

近年、半導体微細加工技術を用いたMEMS (Micro Electro Mechanical Systems) と呼ばれるマイクロマシン用パッケージや、半導体素子が実装されるインターポーヴ等のような基板の開発が進められている。このような基板は、基材の両面に形成された配線と、基材を貫通すると共に、基材の両面に形成された配線間を電気的に接続する貫通ビアとを設けた構成とされている。

20

##### 【0003】

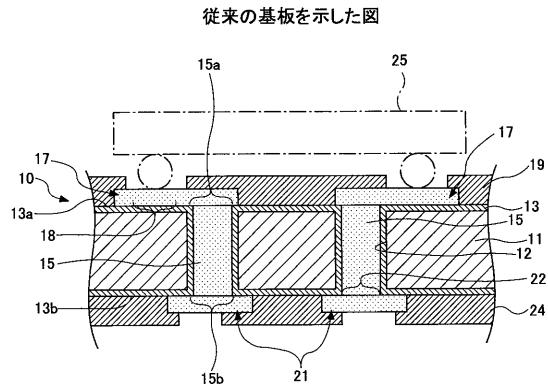

図1は、従来の基板を示した図である。図1に示すように、基板10は、大略するとシリコン基材11と、絶縁層13と、貫通ビア15と、配線17と、ソルダーレジスト19, 24と、配線21とを有した構成とされている。シリコン基材11には、貫通孔12が形成されている。絶縁層13は、貫通孔12が形成されたシリコン基材11の表面に形成されている。絶縁層13は、シリコン基材11と貫通ビア15及び配線17, 21との間を絶縁するためのものである。貫通ビア15は、円柱形状であり、絶縁層13が形成された貫通孔12に配設されている。また、貫通ビア15の端部15aは、絶縁層13の面13aと面一とされており、貫通ビア15の端部15bは、絶縁層13の面13bと面一とされている。このような貫通ビア15は、絶縁層13が形成されたシリコン基材11の上面に、スパッタ法等によりシード層を形成して、電解めっき法によりシード層上にCu等の導電金属膜を析出、成長させることで形成される(例えば、特許文献1参照)。

30

##### 【0004】

配線17は、外部接続端子18を有しており、貫通ビア15の端部15aと接続されるようシリコン基材11の上面側に設けられている。外部接続端子18は、MEMSや、半導体素子25が実装されるものである。ソルダーレジスト19は、外部接続端子18を露出すると共に、外部接続端子18以外の配線17を覆うようシリコン基材11の上面側に形成されている。

40

##### 【0005】

配線21は、外部接続端子22を有しており、貫通ビア15の端部15bと接続されるようシリコン基材11の下面側に設けられている。外部接続端子22は、マザーボード等の他の基板が接続されるものである。ソルダーレジスト24は、外部接続端子22を露出すると共に、外部接続端子22以外の配線21を覆うようシリコン基材11の下面側に形成されている。

#### 【特許文献1】特開平1-258457号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

##### 【0006】

50

しかしながら、従来の貫通ビア15の形状は、円柱形状であるため、貫通ビア15の端部15a, 15bと絶縁層13との界面から水分等が侵入し、貫通ビア15が劣化してしまい、配線17と配線21との間を接続する貫通ビア15の電気的な接続信頼性が低下してしまうという問題があった。また、従来の貫通ビア15の形成方法では、シード層の表面に析出した導電金属膜が貫通孔12の内周面に形成され、貫通孔12の内周面に沿って導体金属膜が成長するため、貫通ビア15の中心付近にボイド(空洞)が発生してしまい、配線17と配線21との間を接続する貫通ビア15の電気的な接続信頼性が低下してしまうという問題があった。

#### 【0007】

そこで本発明は、上述した問題点に鑑みなされたものであり、配線を接続する貫通ビアの電気的な接続信頼性を向上させることのできる基板の製造方法を提供することを目的とする。

10

#### 【課題を解決するための手段】

#### 【0008】

上記課題を解決するために本発明では、次に述べる各手段を講じたことを特徴とするものである。

#### 【0017】

請求項1記載の発明では、貫通孔が形成された基材と、該基材の貫通孔に配設された貫通ビアとを備え、前記貫通ビアは、前記貫通孔に配置された貫通部と、該貫通部の一方の端部に設けられ、前記基材から突出した第1の突出部と、を有する基板の製造方法であって、前記貫通孔が形成された前記基材を、第1のレジスト層を介して、給電層上に配置する基材配置工程と、前記貫通孔に露出された部分の前記第1のレジスト層を除去して、前記給電層を露出させると共に、前記貫通孔の寸法よりも幅広形状の鍔状空間を形成する鍔状空間形成工程と、前記鍔状空間形成工程後に、前記第1のレジスト層を第1の熱処理により硬化させる第1のレジスト層硬化工程と、第1のレジスト層硬化工程後に、前記給電層からの給電により形成される導電性金属膜により、前記鍔状空間及び前記貫通孔を充填して前記貫通ビアを形成する貫通ビア形成工程と、を含むことを特徴とする基板の製造方法により、解決できる。

20

#### 【0018】

上記発明によれば、貫通ビアに貫通部の寸法よりも幅広の形状とされた第1の突出部が形成されるため、貫通部と基材との間に水分等が侵入しにくくなり、貫通ビアの劣化が抑制され、貫通ビアの電気的な接続信頼性を向上させることができる。

30

また、給電層上に導電金属膜を析出成長させることで、鍔状空間及び貫通孔を導電金属膜で順次充填して貫通ビアを形成するため、貫通ビアにボイド(空洞)が発生することを抑制できる。

#### 【0019】

請求項2記載の発明では、貫通孔が形成された基材と、該基材の貫通孔に配設された貫通ビアとを備え、前記貫通ビアは、前記貫通孔に配置された貫通部と、該貫通部の一方の端部に設けられ、前記基材から突出した第1の突出部と、を有する基板の製造方法であって、前記貫通孔が形成された前記基材を、第1のレジスト層を介して、給電層上に配置する基材配置工程と、前記貫通孔に露出された部分の前記第1のレジスト層と、前記基材と前記給電層との間に位置する部分の前記第1のレジスト層とを除去して、前記基材と前記給電層との間に、前記貫通孔の寸法よりも幅広形状の鍔状空間を形成する鍔状空間形成工程と、前記給電層からの給電により形成される導電性金属膜により、前記鍔状空間及び前記貫通孔を充填して前記貫通ビアを形成する貫通ビア形成工程と、を含み、前記第1の突出部は、前記鍔状空間に前記導電性金属膜を充填することで形成することを特徴とする基板の製造方法により、解決できる。

40

上記発明によれば、貫通ビアに貫通部の寸法よりも幅広の形状とされた第1の突出部が形成されるため、貫通部と基材との間に水分等が侵入しにくくなり、貫通ビアの劣化が抑制され、貫通ビアの電気的な接続信頼性を向上させることができる。

50

また、給電層上に導電金属膜を析出成長させることで、鍔状空間及び貫通孔を導電金属膜で順次充填して貫通ピアを形成するため、貫通ピアにボイド（空洞）が発生することを抑制できる。

請求項3記載の発明では、前記給電層は、支持板に設けられた金属箔であり、前記金属箔は、前記鍔状空間に露出されていることを特徴とする請求項1又は2記載の基板の製造方法により、解決できる。

【0020】

上記発明によれば、支持板に設けられた金属箔を給電層とすることにより、金属箔をワッ칭により容易に除去することができる。

請求項4記載の発明では、前記基材上に前記貫通孔を露出すると共に、前記貫通孔の寸法よりも幅広形状となる第1の開口部を有した第2のレジスト層を形成する第2のレジスト層形成工程を設けると共に、前記第1の開口部を前記導電性金属膜により充填し、前記貫通部の他方の端部に設けられ、前記基材から突出すると共に、前記貫通部の寸法よりも幅広の形状とされた第2の突出部を形成することを特徴とする請求項1ないし3のうち、いずれか一項記載の基板の製造方法により、解決できる。10

上記発明によれば、貫通ピアに貫通部の寸法よりも幅広の形状とされた第2の突出部を形成することにより、貫通部と基材との間に水分等が侵入しにくくなり、貫通ピアの劣化が抑制され、貫通ピアの電気的な接続信頼性を向上させることができる。

また、鍔状空間、貫通孔、及び第1の開口部を導電金属膜で順次充填して貫通ピアを形成するため、貫通ピアにボイド（空洞）が発生することを抑制できる。20

【0021】

請求項5記載の発明では、前記鍔状空間形成工程後に、前記第1のレジスト層を第1の熱処理により硬化させる第1のレジスト層硬化工程を設けたことを特徴とする請求項1ないし4のうち、いずれか一項に記載の基板の製造方法により、解決できる。

【0022】

上記発明によれば、第1の熱処理により第1のレジスト層を硬化させることで、第1のレジスト層にめっき液に対する耐性をもたせることができる。

【0023】

請求項6記載の発明では、前記鍔状空間形成工程後に、電解めっき法により、前記鍔状空間に露出された前記金属箔に第1の拡散防止膜を形成する第1の拡散防止膜形成工程を設けたことを特徴とする請求項3ないし5のうち、いずれか一項記載の基板の製造方法により、解決できる。30

【0024】

上記発明によれば、電解めっき法により第1の拡散防止膜を形成することで、無電解めっき法で形成した場合と比較して、膜質に優れた拡散防止膜を形成することができる。

請求項7記載の発明では、前記第2の突出部と接続される配線を形成する配線形成工程をさらに設けたことを特徴とする請求項4ないし6のうち、いずれか一項記載の基板の製造方法により、解決できる。

上記発明によれば、第2の突出部と接続される配線を形成することにより、例えば、半導体チップと接続される配線の位置を調整することができる。40

【0025】

請求項8記載の発明では、前記配線形成工程は、前記第2のレジスト層を除去する第2のレジスト層除去工程と、前記基材上に、前記第2の突出部を露出する第2の開口部を有した絶縁層を形成する絶縁層形成工程と、前記配線が形成される部分の前記絶縁層に、シード層を形成するシード層形成工程と、を有し、前記絶縁層には、パラジウムを含有させた樹脂を用いることを特徴とする請求項7に記載の基板の製造方法により、解決できる。

【0026】

上記発明によれば、絶縁層としてパラジウムを含有させた樹脂を用いることで、絶縁層上にシード層を形成する際、絶縁層を前処理する必要がなくなるため、基板の製造工程を簡略化することができる。50

## 【0027】

請求項9記載の発明では、前記配線は、外部接続端子を有しており、前記配線形成工程後、電解めっき法により前記外部接続端子に第2の拡散防止膜を形成する第2の拡散防止膜形成工程を設けたことを特徴とする請求項7または8に記載の基板の製造方法により、解決できる。

## 【0028】

上記発明によれば、電解めっき法により第2の拡散防止膜を形成することで、無電解めっき法で形成した場合と比較して、膜質に優れた拡散防止膜を形成することができる。

## 【0029】

請求項10記載の発明では、前記第2の拡散防止膜形成工程後に、少なくとも前記配線及び第2の拡散防止膜を覆うよう耐熱性を有した保護部材を配設する保護部材配設工程と、前記保護部材配設工程後、第2の熱処理により、前記基材から前記支持板を離脱させる支持板離脱工程と、を設けたことを特徴とする請求項9に記載の基板の製造方法により、解決できる。

10

## 【0030】

上記発明によれば、少なくとも前記配線及び第2の拡散防止膜を覆うよう耐熱性を有した保護部材を設けることで、基材から接着剤及び支持板を離脱させるための第2の熱処理による熱から配線及び第2の拡散防止膜を保護することができる。

## 【0031】

請求項11記載の発明では、前記支持板離脱工程後に、前記金属箔をエッチングにより除去する金属箔除去工程と、前記第1のレジスト層を除去する第1のレジスト層除去工程と、該第1のレジスト層除去工程後に、前記保護部材を除去する保護部材除去工程と、を設けたことを特徴とする請求項10に記載の基板の製造方法により、解決できる。

20

## 【0032】

上記発明によれば、金属箔除去工程後に、保護部材を除去することで、配線がエッチングされることを防止できる。

## 【0033】

請求項12記載の発明では、前記第1の拡散防止膜形成工程は、前記支持板に前記金属箔を設けた直後に行うことを行なうことを特徴とする請求項6ないし11のうち、いずれか一項に記載の基板の製造方法により、解決できる。

30

## 【0034】

上記発明によれば、第1の拡散防止膜形成工程を金属箔配設工程の直後に行なうことで、第1の拡散防止膜を形成する際のめっき液が、貫通ビアを形成する際のめっき液に混ざることがなくなるため、膜質に優れた導電金属膜を形成することができる。

請求項13記載の発明では、前記第1のレジスト層を現像液により除去することを特徴とする請求項1ないし12のうち、いずれか一項記載の基板の製造方法により、解決できる。

上記発明によれば、現像液を用いて第1のレジスト層の除去を行うことにより、容易に鍔状空間を形成することができる。

## 【発明の効果】

40

## 【0035】

本発明によれば、配線と接続される貫通ビアの電気的な接続信頼性を向上させることのできる基板の製造方法を提供できる。

## 【発明を実施するための最良の形態】

## 【0036】

次に、図面に基づいて本発明の実施例を説明する。

## (第1実施例)

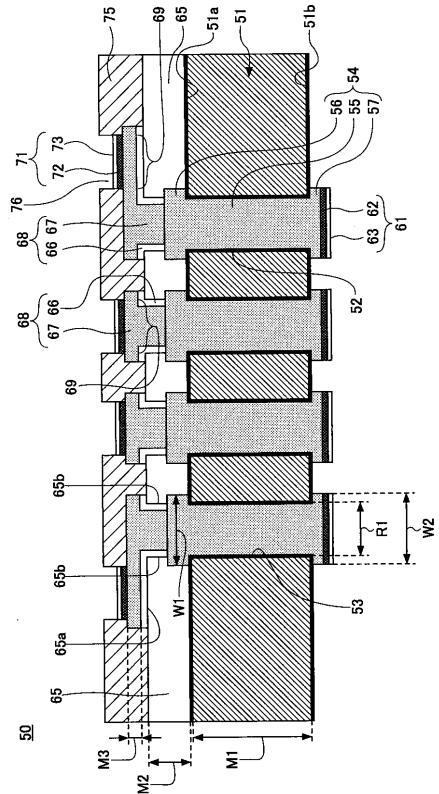

始めに、図2を参照して、本発明の第1実施例の基板50の構成について説明する。図2は、本発明の第1実施例の基板の断面図である。基板50は、大略すると基材51と、絶縁層53と、貫通ビア54と、絶縁層65と、配線68と、第1の拡散防止膜61、第

50

2の拡散防止膜71と、ソルダーレジスト75とを有した構成とされている。基板50は、インターポーザである。図2において、基板50の下面側には、例えば、半導体微細加工技術を用いたMEMS (Micro Electro Mechanical Systems) や半導体素子等が実装され、基板50の上面側(配線68が形成されている側)には、例えば、マザーボード等の基板が接続される。

#### 【0037】

基材51は、シリコンからなるシリコン基材である。基材51の厚さM1は、例えば、 $150\mu\text{m}$ とすることができます。基材51には、貫通ビア54が配設される貫通孔52が基材51を貫通するよう複数形成されている。貫通孔52は、開口径R1となるように形成されている。絶縁層53は、貫通孔52を含む基材51の表面に形成されている。このように、貫通孔52を含む基材51の表面に絶縁層53を設けることにより、基材51と貫通ビア54との間を絶縁することができる。なお、基材51には、ガラス基材等のシリコン基材以外のものを用いても良い。また、基材51として、ガラス基材のように絶縁性の基材を用いる場合には、絶縁層53の形成は不要である。

#### 【0038】

貫通ビア54は、貫通部55と、第2の突出部である配線接続部56と、第1の突出部である接続パッド57とを有した構成とされている。貫通部55は、絶縁層53が形成された貫通孔52に配設されており、その直径はR1(以下、「直径R1」とする)とされている。請求項に記載の貫通部55の寸法とは、直径R1のことである。

#### 【0039】

配線接続部56は、貫通部55の上端部に設けられている。配線接続部56は、基材51の面51aから突出しており、貫通部55の直径R1よりも幅広の形状とされている。配線接続部56の幅W1は、貫通部55の直径R1よりも大きくなるように設定されている( $W1 > R1$ )。配線接続部56は、貫通部55と一体的に構成されている。配線接続部56は、配線68を接続するためのものである。

#### 【0040】

接続パッド57は、貫通部55の下端部に設けられている。接続パッド57は、基材51の面51bから突出しており、貫通部55の直径R1よりも幅広の形状とされている。接続パッド57の幅W2は、貫通部55の直径R1よりも大きくなるように設定されている( $W2 > R1$ )。接続パッド57は、半導体素子等と接続するためのものである。貫通部55、配線接続部56、及び接続パッド57は、導電金属膜により一体的に構成されている。導電金属膜には、例えば、Cu膜を用いることができる。

#### 【0041】

第1の拡散防止膜61は、接続パッド57に設けられている。第1の拡散防止膜61は、はんだのぬれ性向上や、貫通ビア54に含まれるCuが接続パッド57に接続されるはんだ(図示せず)に拡散することを防止するためのものである。第1の拡散防止膜61には、例えば、Ni層62と、Au層63との積層膜により構成することができる。Ni層62の厚さは、例えば、 $2\sim5\mu\text{m}$ とすることができる。また、Au層63の厚さは、例えば、 $0.1\sim0.5\mu\text{m}$ とすることができる。なお、上記Ni/Au層以外に、例えば、Ni/Pd層やNi/Pd/Au層等を第1の拡散防止膜61として用いてもよい(Niが接続パッド57と接続される側となる)。

#### 【0042】

絶縁層65は、配線接続部56を露出する開口部を有しており、基材51の面51aに形成されている。絶縁層65には、例えば、樹脂中にめっき触媒となる金属の粒子や金属の化合物(塩化物、水酸化物、酸化物等)の粒子等を分散させたものを用いることができる。この場合の樹脂としては、例えば、エポキシ系樹脂やポリイミド系樹脂等を用いることができる。めっき触媒となる金属には、例えば、パラジウムや白金が使用することができ、特に、パラジウムが好適である。また、金属の化合物としては、例えば、塩化パラジウムや硫酸パラジウム等を用いることができる。なお、本実施例において、絶縁層65には、エポキシ系樹脂にパラジウムの粒子を分散させたものを用いる。絶縁層65にパラジ

10

20

30

40

50

ウムを含有した樹脂を用いることで、無電解めっきする際、絶縁層 6 5 に対してデスマニア処理及びパラジウム活性化処理等の前処理を行うことなく、直接、絶縁層 6 5 上に無電解めっきすることができる。これにより、基板 5 0 の製造工程を簡略化することができる。絶縁層 6 5 の厚さ M 2 は、例えば、5  $\mu\text{m}$  とすることができる。

#### 【0043】

配線 6 8 は、絶縁層 6 5 上に配線接続部 5 6 と接続されるよう設けられている。配線 6 8 は、外部接続端子 6 9 を有しており、導電金属膜 6 7 とシード層 6 6 とにより構成されている。外部接続端子 6 9 は、マザーボード等の基板が接続されるものである。このような配線 6 8 を設けることで、マザーボード等の基板に設けられた外部接続端子の位置に対応するよう外部接続端子 6 9 の位置を設定することができる。導電金属膜 6 7 には、例えば、Cu 膜を用いることができる。導電金属膜 6 7 に Cu 膜を用いた場合の導電金属膜 6 7 の厚さ M 3 は、例えば、3 ~ 10  $\mu\text{m}$  とすることができます。シード層 6 6 には、例えば、Ni 膜を用いることができる。シード層 6 6 の厚さは、例えば、0.1  $\mu\text{m}$  程度とすることができる。

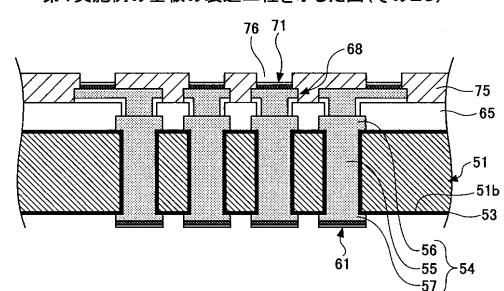

#### 【0044】

ソルダーレジスト 7 5 は、開口部 7 6 を有し、開口部 7 6 により外部接続端子 6 9 を露出すると共に、外部接続端子 6 9 以外の配線 6 8 と絶縁層 6 5 とを覆うように形成されている。ソルダーレジスト 7 5 は、配線 6 8 を保護するためのものである。

#### 【0045】

第 2 の拡散防止膜 7 1 は、外部接続端子 6 9 に設けられている。第 2 の拡散防止膜 7 1 は、はんだのぬれ性向上や、配線 6 8 に含まれる Cu が外部接続端子 6 9 に接続されるはんだ(図示せず)に拡散することを防止するためのものである。第 2 の拡散防止膜 7 1 は、例えば、Ni 層 7 2 と、Au 層 7 3 との積層膜により構成することができる。Ni 層 7 2 の厚さは、例えば、2 ~ 5  $\mu\text{m}$  とすることができます。また、Au 層 7 3 の厚さは、例えば、0.1 ~ 0.5  $\mu\text{m}$  とすることができます。なお、上記 Ni / Au 層以外に、例えば、Ni / Pd 層や Ni / Pd / Au 層等を第 2 の拡散防止膜 7 1 として用いてもよい(Ni が外部接続端子 6 9 と接続される側となる)。

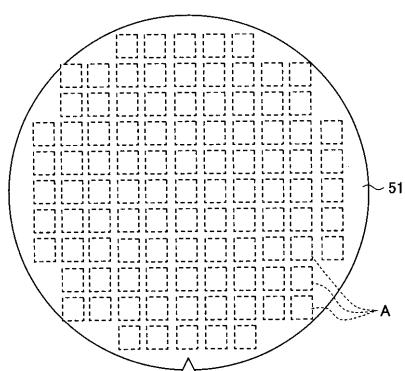

#### 【0046】

図 3 は、本実施例の基板が製造される基材の平面図である。なお、図 3 において、A は基板 5 0 が形成される領域(以下、「基板形成領域 A」とする)を示している。図 3 に示すように、本実施例では、基材 5 1 として、複数の基板形成領域 A を有したシリコン基板(シリコンウェハ)を用いる。このように、基材 5 1 としてシリコン基板を用い、各種製造工程を経た後、基材 5 1 を切り分け、複数の基板 5 0 を一度に製造することで、基板 5 0 の生産性を向上させることができる。

#### 【0047】

次に、図 4 乃至図 2 9 を参照して、第 1 実施例の基板 5 0 の製造方法について説明する。図 4 乃至図 2 9 は、第 1 実施例の基板の製造工程を示した図である。なお、以下の説明においては、基材 5 1 にシリコン基材を用いた場合を例に挙げて説明する。また、図 4 乃至図 2 9 において、図 2 に示した基板 5 0 と同一構成部分には同一の符号を付す。

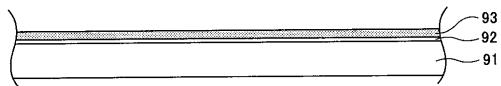

#### 【0048】

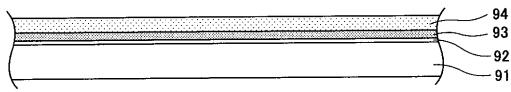

始めに、図 4 に示すように、支持板 9 1 上に接着剤 9 2 を設ける。支持板 9 1 は、基材 5 1 を支持するためのものである。支持板 9 1 には、例えば、ガラス基板やシリコン基板(具体的には、シリコンウェハ等)等を用いることができる。支持板 9 1 としてシリコン基板を用いた場合、支持板 9 1 の厚さ M 4 は、例えば、725  $\mu\text{m}$  とすることができます。接着剤 9 2 は、後述する金属箔 9 3 を支持板 9 1 に接着するためのものである。接着剤 9 2 には、例えば、加熱することにより接着力を失うサーモピールテープや熱剥離接着剤等を用いることができる。

#### 【0049】

次に、図 5 に示すように、接着剤 9 2 を介して、Cu 等の金属箔 9 3 を支持板 9 1 に貼り付ける。続いて、図 6 に示すように、金属箔 9 3 上に、露光しない状態で第 1 のレジス

10

20

30

40

50

ト層 9 4 を形成する。第 1 のレジスト層 9 4 は、接着性を有したレジストであり、例えば、感光性のドライフィルムレジストや液状のレジストを用いることができる。

#### 【 0 0 5 0 】

このような、接着性を有した第 1 のレジスト層 9 4 を用いることで、第 1 のレジスト層 9 4 を介して、貫通孔 5 2 が形成された基材 5 1 を支持板 9 1 に固定することができる(図 7 参照)。第 1 のレジスト層 9 4 の厚さは、例えば、 $10 \mu m \sim 15 \mu m$  とすることができます。また、何らかの処理液により、溶解できる場合、第 1 のレジスト層 9 4 の代わりにエポキシやポリイミド等の接着剤を用いても良い。

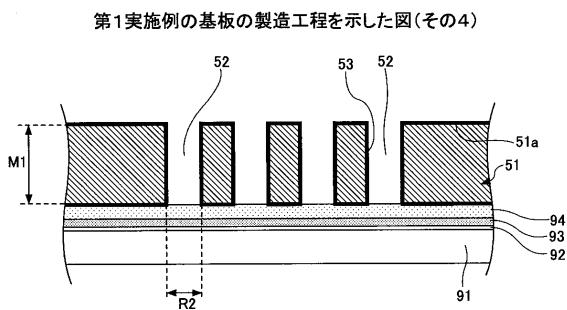

#### 【 0 0 5 1 】

次に、図 7 に示すように、開口径  $R_2$  ( $R_1 = R_2$ ) の貫通孔 5 2 が形成されると共に、基材 5 1 の表面(貫通孔 5 2 に対応する基材 5 1 部分も含む)を覆うように絶縁層 5 3 が形成された基材 5 1 を、接着性を有した第 1 のレジスト層 9 4 上に配置させ、固定する(基材配置工程)。貫通孔 5 2 は、例えば、ドリルを用いたドリル加工、レーザ加工、異方性エッティングのいずれかの方法により形成することができます。また、貫通孔 5 2 の開口径  $R_2$  は、例えば、 $10 \sim 60 \mu m$  程度の範囲内で適宜選択することができます。絶縁層 5 3 には、例えば、CVD 法により形成された酸化膜 ( $SiO_2$ ) や、酸化炉により形成された熱酸化膜 ( $SiO_2$ ) 等を用いることができる。さらに、基材 5 1 の厚さ  $M_1$  は、例えば、 $150 \mu m$  とすることができます。

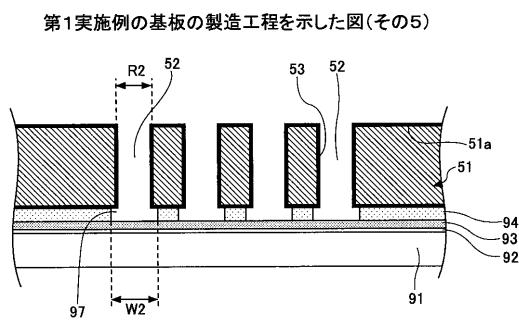

#### 【 0 0 5 2 】

次に、図 8 に示すように、現像液を貫通孔 5 2 の内部に供給し、貫通孔 5 2 に露出された第 1 のレジスト層 9 4 を溶解して、鍍状空間 9 7 を形成する(鍍状空間形成工程)。鍍状空間 9 7 は、貫通孔 5 2 の開口径  $R_2$  よりも幅広形状となる空間であり、鍍状空間 9 7 の幅  $W_2$  は、貫通孔 5 2 の開口径  $R_2$  よりも大きい( $W_2 > R_2$ )。現像液を貫通孔 5 2 の内部に供給する方法としては、例えば、図 7 に示した構造体を現像液中に浸すディップ現像や、貫通孔 5 2 の上方から現像液をシャワー状に吹き付けるスプレー現像がある。

#### 【 0 0 5 3 】

どちらの現像方式においても、現像液の浸潤時間を管理することで、鍍状空間 9 7 を形成することができる。スプレー現像を用いて鍍状空間 9 7 を形成する際の条件としては、例えば、現像液を吹き付ける圧力を  $2.0 \text{ kgf/sq.cm}$ 、温度を  $25 \sim 30$  、現像液を吹き付ける時間を  $6 \text{ min}$  とすることができる。なお、請求項に記載の「貫通孔の寸法」とは、貫通孔 5 2 の開口径  $R_2$  のことである。続いて、図 8 に示した構造体を熱処理(第 1 の熱処理)して、露光されていない第 1 のレジスト層 9 4 を重合反応させ、第 1 のレジスト層 9 4 を硬化させる(第 1 のレジスト層硬化工程)。このように、第 1 のレジスト層 9 4 を硬化させることで、第 1 のレジスト層 9 4 にめっき液に対する耐性をもたせることができる。

#### 【 0 0 5 4 】

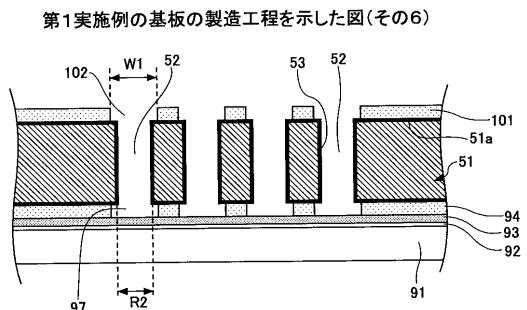

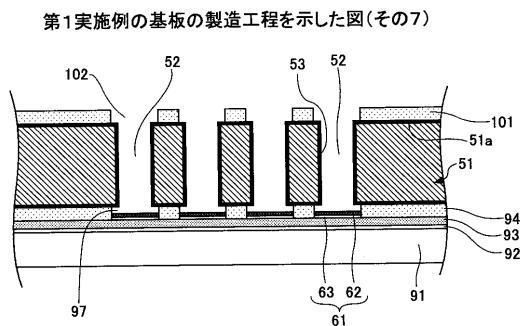

次に、図 9 に示すように、基材 5 1 の面 5 1 a に形成された絶縁層 5 3 上に、貫通孔 5 2 を露出すると共に、貫通孔 5 2 の開口径  $R_2$  よりも幅広形状の開口部 1 0 2 を有した第 2 のレジスト層 1 0 1 を形成する(第 2 のレジスト層形成工程)。第 1 の開口部である開口部 1 0 2 の開口径  $W_1$  は、貫通孔 5 2 の開口径  $R_2$  よりも大きく形成されている( $W_1 > R_2$ )。

#### 【 0 0 5 5 】

続いて、図 10 に示すように、金属箔 9 3 を給電層として、電解めっき法により、Au 層 6 3 と、Ni 層 6 2 とを金属箔 9 3 上に順次析出成長させて、第 1 の拡散防止膜 6 1 を形成する(第 1 の拡散防止膜形成工程)。Au 层 6 3 の厚さは、例えば、 $0.1 \sim 0.5 \mu m$  とすることができます、Ni 層 6 2 の厚さは、例えば、 $2 \sim 5 \mu m$  とすることができます。このように、電解めっき法を用いて、第 1 の拡散防止膜 6 1 を形成することで、無電解めっき法を用いた場合と比較して、膜質に優れた拡散防止膜を形成することができる。

#### 【 0 0 5 6 】

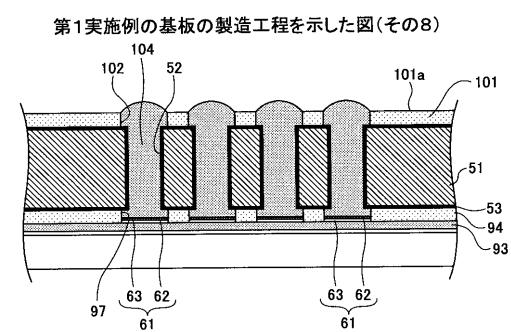

次に、図 11 に示すように、Ni 層 6 2 を給電層として、電解めっき法により鍍状空間

10

20

30

40

50

97、貫通孔 52、及び開口部 102 を充填するよう導電金属膜 104 を析出成長させる（貫通ビア形成工程）。この際、第2のレジスト層 101 の面 101a から導電金属膜 104 が突出する。導電金属膜 104 には、例えば、Cu 膜を用いることができる。

#### 【0057】

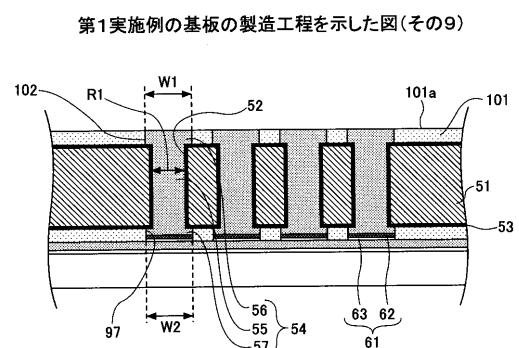

続いて、図 12 に示すように、導電金属膜 104 が第2のレジスト層 101 の面 101a と面一となるように、第2のレジスト層 101 の面 101a から突出した導電金属膜 104 を研磨により除去する。これにより、鍔状空間 97 に幅 W2 の接続パッド 57（第1の突出部）と、貫通孔 52 に直径 R1 の貫通部 55 と、開口部 102 に幅 W1 の配線接続部 56（第2の突出部）とが一度に形成され、貫通ビア 54 が形成される。幅 W1, W2 は、貫通部 55 の直径 R1 よりも幅広の形状とされている。

10

#### 【0058】

このように、貫通ビア 54 に貫通部 55 の直径 R1 よりも幅広の形状とされた接続パッド 57 及び配線接続部 56 を形成することにより、貫通部 55 と基材 51 との間に水分等が侵入しにくくなり、貫通ビア 54 の劣化が抑制され、配線 68 と接続される貫通ビア 54 の電気的な接続信頼性を向上させることができる。

#### 【0059】

また、貫通ビア 54 は、金属箔 93 を給電層として、電解めっき法により、金属箔 93 上に導電金属膜 104 を析出成長させて、鍔状空間 97、貫通孔 52、第1の開口部 102 を導電金属膜 104 で順次充填するよう形成するため、貫通ビア 54 にボイド（空洞）が発生することを抑制できる。

20

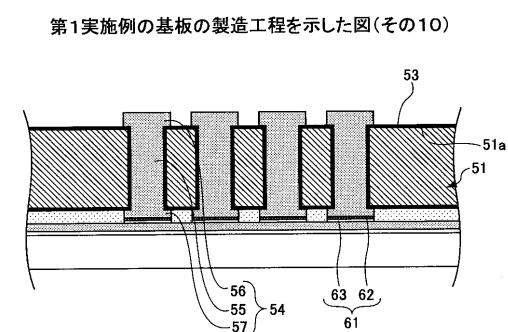

#### 【0060】

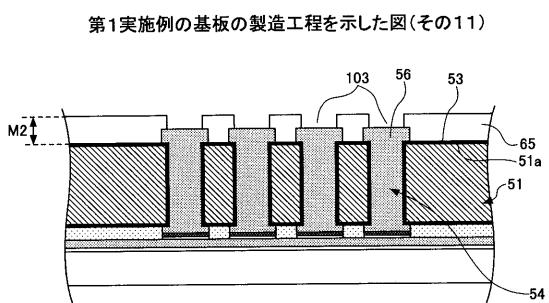

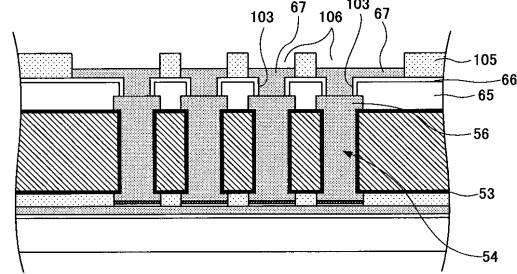

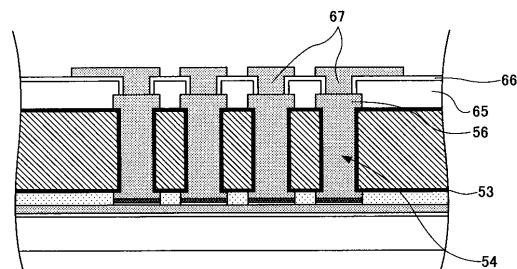

次に、図 13 に示すように、第2のレジスト層 101 をレジスト剥離液により除去する（第2のレジスト層除去工程）。続いて、図 14 に示すように、基材 51 の面 51a 上に、配線接続部 56 を露出する開口部 103 を有した絶縁層 65 を形成する（絶縁層形成工程）。絶縁層 65 として、本実施例では、パラジウムの粒子を含有させたエポキシ系樹脂を用いる。絶縁層 65 の厚さ M2 は、例えば、5 μm とすることができる。

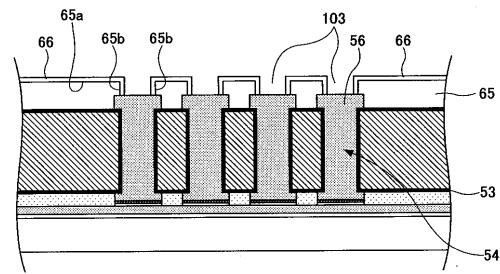

#### 【0061】

次に、図 15 に示すように、無電解めっき法により、絶縁層 65 の上面 65a 及び側面 65b にシード層 66 を形成する（シード層形成工程）。ところで、従来、無電解めっき法で樹脂にシード層を形成する場合には、事前にデスマニア処理で樹脂（絶縁層）の表面を粗化した後、樹脂の表面にパラジウム活性化処理を行う。パラジウム活性化処理とは、キヤタライジング処理液や、アクセレレイティング処理液に被めっき物を浸漬させ、樹脂の表面に無電解めっきの核となるパラジウムを析出させる処理である。従来技術では、このパラジウム活性化処理後に、はじめて、無電解めっき法によるめっき膜を形成することができる。そのため、このような従来技術は、工程が非常に煩雑であった。

30

#### 【0062】

一方、本実施例では、絶縁層 65 として、パラジウムの粒子を含有させたエポキシ系樹脂を適用しているため、シード層 66 を形成する際、絶縁層 65 に対してデスマニア処理及びパラジウム活性化処理等の前処理を行うことなく、無電解めっき法により、直接、絶縁層 65 にシード層 66 を形成することができる。これにより、基板 50 の製造工程を簡略化することができる。シード層 66 には、例えば、Ni 層を用いることができる。絶縁層 65 にパラジウムの粒子を含有させた樹脂を用いた場合には、Ni - B 層を形成することができる。

40

#### 【0063】

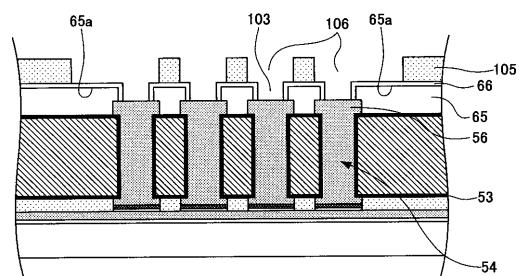

続いて、図 16 に示すように、シード層 66 上に、配線 68 が形成される領域に対応した開口部 106 を有したドライフィルムレジスト 105 を形成する。ドライフィルムレジスト 105 の厚さは、例えば、10 ~ 15 μm とすることができる。次に、図 17 に示すように、配線接続部 56 及びシード層 66 を給電層として、電解めっき法により、開口部 103, 106 に Cu 等の導電金属膜 67 を析出成長させる。

#### 【0064】

50

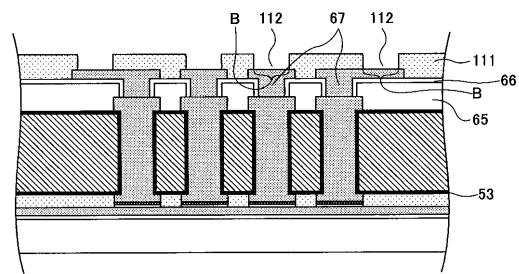

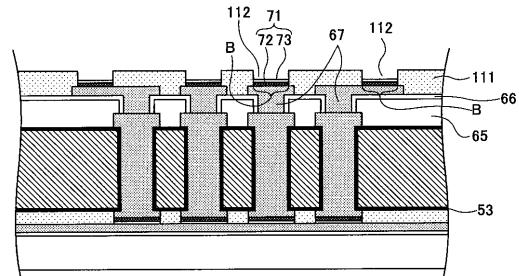

これにより、導電金属膜 6 7 と貫通ピア 5 4 が電気的に接続される。その後、図 1 8 に示すように、ドライフィルムレジスト 1 0 5 は、レジスト剥離液により除去される。続いて、図 1 9 に示すように、図 1 8 に示した構造体上に、外部接続端子 6 9 が形成される領域 B に対応した導電金属膜 6 7 を露出するドライフィルムレジスト 1 1 1 を形成する。ドライフィルムレジスト 1 1 1 には、開口部 1 1 2 が形成されており、この開口部 1 1 2 により領域 B に対応した導電金属膜 6 7 が露出される。

#### 【0065】

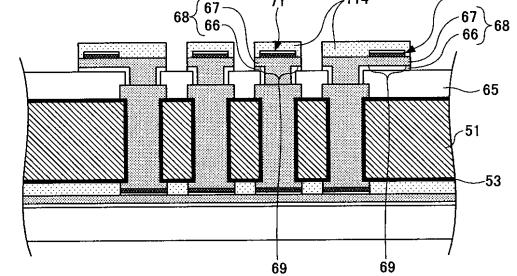

次に、図 2 0 に示すように、導電金属膜 6 7 を給電層として、電解めっき法により、開口部 1 1 2 に露出された導電金属膜 6 7 上に、Ni 層 7 2 と、Au 層 7 3 とを順次析出成長させて、第 2 の拡散防止膜 7 1 を形成する（第 2 の拡散防止膜形成工程）。Ni 層 7 2 の厚さは、例えば、2 ~ 5  $\mu\text{m}$  とすることができます、Au 層 7 3 の厚さは、例えば、0.1 ~ 0.5  $\mu\text{m}$  とすることができます。このように、電解めっき法を用いて、第 2 の拡散防止膜 7 1 を形成することで、無電解めっき法により形成した場合と比較して、膜質に優れた第 2 の拡散防止膜 7 1 を形成することができる。ドライフィルムレジスト 1 1 1 は、第 2 の拡散防止膜 7 1 を形成後に除去される。

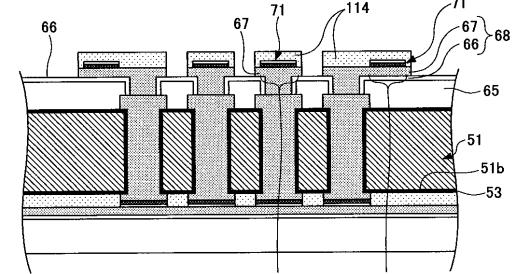

#### 【0066】

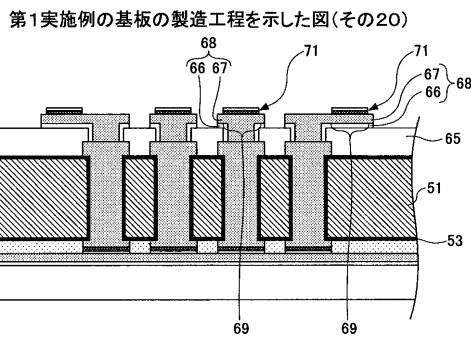

次に、図 2 1 に示すように、導電金属膜 6 7 及び第 2 の拡散防止膜 7 1 のみを覆うようドライフィルムレジスト 1 1 4 を形成する。続いて、図 2 2 に示すように、エッティングにより絶縁層 6 5 上に設けられたシード層 6 6 を除去する。これにより、外部接続端子 6 9 を備えると共に、シード層 6 6 と導電金属膜 6 7 とにより構成された配線 6 8 が形成される。シード層 6 6 除去後、図 2 3 に示すように、ドライフィルムレジスト 1 1 4 をレジスト剥離液により除去する。

#### 【0067】

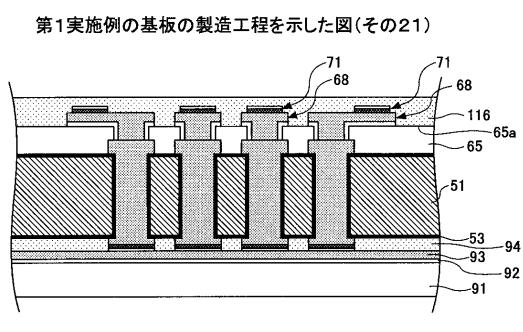

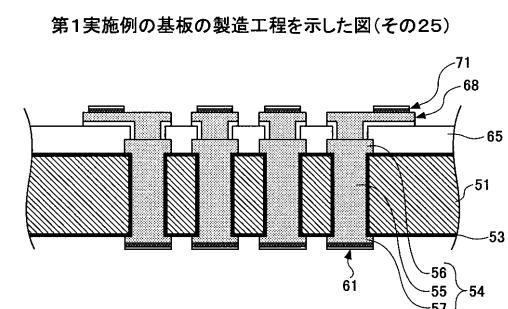

次に、図 2 4 に示すように、配線 6 8 、第 2 の拡散防止膜 7 1 、及び絶縁層 6 5 の上面 6 5 a を覆うように、耐熱性を有した保護部材である耐熱テープ 1 1 6 を貼り付ける（保護部材配設工程）。この耐熱テープ 1 1 6 は、エッティング液に対する耐性も有したテープである。このように、耐熱テープ 1 1 6 により配線 6 8 及び第 2 の拡散防止膜 7 1 を覆うことで、基材 5 1 から支持板 9 1 を離脱させる際の第 2 の熱処理（図 2 5 参照）の熱から配線 6 8 及び第 2 の拡散防止膜 7 1 を保護することができる。また、金属箔 9 3 をエッティングにより除去（図 2 6 参照）する際、配線 6 8 がエッティングされることを防止することができる。耐熱テープ 1 1 6 には、例えば、難燃性の PET や PEN 等を用いることができる。なお、耐熱テープ 1 1 6 は、少なくとも配線 6 8 と第 2 の拡散防止膜 7 1 とを覆うように設けられていれば良い。

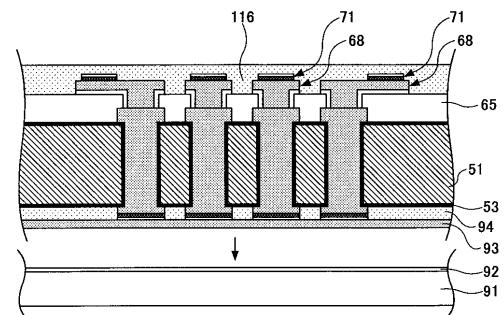

#### 【0068】

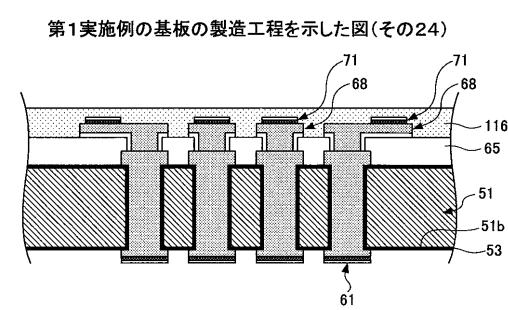

次に、図 2 5 に示すように、図 2 4 に示した構造体に加熱（第 2 の熱処理）して、接着剤 9 2 及び支持板 9 1 を基材 5 1 から取り外す（支持板離脱工程）。本実施例では、接着剤 9 2 として加熱により接着力を失うサーモピールテープを用いる。また、第 2 の熱処理には、例えば、加熱温度が 150 ℃ 、加熱時間 30 分の条件を用いることができる。続いて、図 2 6 に示すように、エッティングにより金属箔 9 3 を除去する（金属箔除去工程）。これにより、第 1 のレジスト層 9 4 と第 1 の拡散防止膜 6 1 とが露出される。先に説明したように、配線 6 8 は、エッティング液に対する耐性を有した耐熱テープ 1 1 6 により覆われているためエッティングされない。

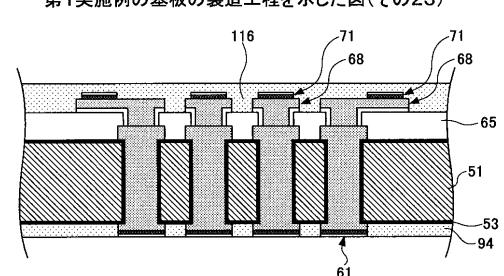

#### 【0069】

次に、図 2 7 に示すように、剥離液により第 1 のレジスト層 9 4 の除去を行う。続いて、図 2 8 に示すように、耐熱テープ 1 1 6 を剥離する。その後、図 2 9 に示すように、第 2 の拡散防止膜 7 1 を露出させると共に、配線 6 8 及び絶縁層 6 5 を覆うようソルダーレジスト 7 5 を形成する。ソルダーレジスト 7 5 には、開口部 7 6 が形成されており、この開口部 7 6 により第 2 の拡散防止膜 7 1 が露出されている。その後、基材 5 1 がダイシングされて、図 2 に示すような基板 5 0 が複数形成される。

#### 【0070】

10

20

30

40

50

以上、説明したような製造工程により、貫通部 5 5 の一方の端部に貫通部 5 5 の直径 R 1 よりも幅広の形状の接続パッド 5 7 と、他方の端部に貫通部 5 5 の直径 R 1 よりも幅広の形状の配線接続部 5 6 とを備えた貫通ビア 5 4 が形成されるので、貫通部 5 5 と基材 5 1 との間に水分等が侵入しにくくなり、貫通ビア 5 4 の劣化が抑制され、配線 6 8 と接続される貫通ビア 5 4 の電気的な接続信頼性を向上させることができる。また、貫通部 5 5 の直径 R 1 よりも幅広の形状の配線接続部 5 6 に配線 6 8 が接続されるので、配線接続部 5 6 に配線 6 8 を容易に接続することができる。

#### 【0071】

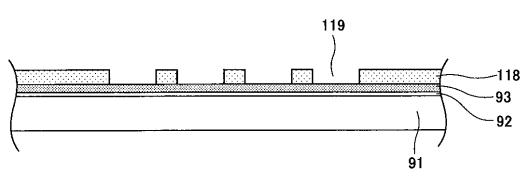

始めに、図 3 0 に示すように、支持板 9 1 上に接着剤 9 2 を設け、Cu 等の金属箔 9 3 を接着剤 9 2 に貼り付け、その後、金属箔 9 3 上に開口部 1 1 9 を有したドライフィルムレジスト 1 1 8 を形成する。なお、開口部 1 1 9 により金属箔 9 3 は露出されている。10

#### 【0072】

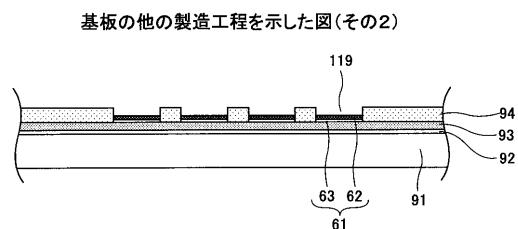

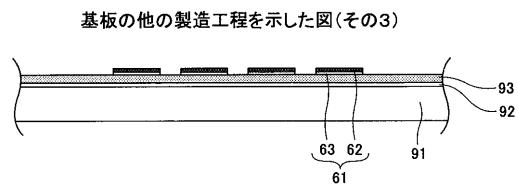

次に、図 3 1 に示すように、金属箔 9 3 を給電層として、電解めっき法により、開口部 1 1 9 に露出された金属箔 9 3 上に Au 層 6 3 と、Ni 層 6 2 とを順次析出成長させて、第 1 の拡散防止膜 6 1 を形成する（第 1 の拡散防止膜形成工程）。続いて、図 3 2 に示すように、ドライフィルムレジスト 1 1 8 をレジスト剥離液により除去する。

#### 【0073】

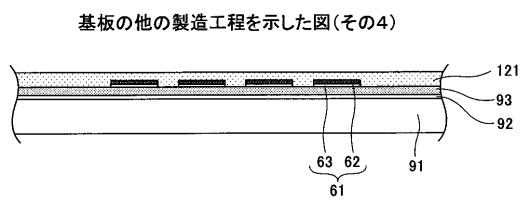

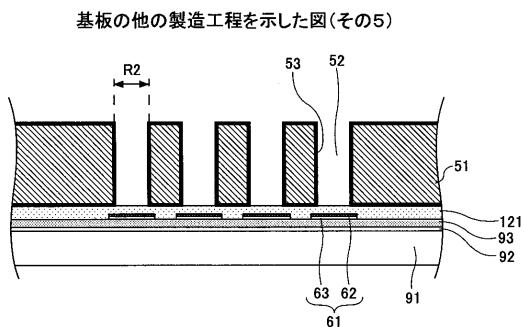

次に、図 3 3 に示すように、第 1 の拡散防止膜 6 1 を覆うように金属箔 9 3 上に、露光しない状態で第 1 のレジスト層 1 2 1 を形成する（第 1 のレジスト層形成工程）。第 1 のレジスト層 1 2 1 は、接着性を有したレジストであり、例えば、感光性のドライフィルムレジストを用いることができる。第 1 のレジスト層 1 2 1 の厚さは、例えば、10 μm ~ 20 15 μm とすることができます。

#### 【0074】

次に、図 3 4 に示すように、開口径 R 2 の貫通孔 5 2 が形成されると共に、基材 5 1 の表面（貫通孔 5 2 に対応する基材 5 1 部分も含む）を覆うよう絶縁層 5 3 が形成された基材 5 1 を、接着性を有した第 1 のレジスト層 1 2 1 上に配置させ、固定する（基材配置工程）。

#### 【0075】

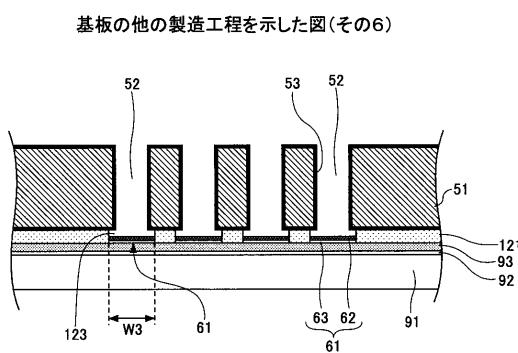

続いて、図 3 5 に示すように、現像液を貫通孔 5 2 の内部に供給し、貫通孔 5 2 に露出された第 1 のレジスト層 1 2 1 を溶解して、鍔状空間 1 2 3 を形成する（鍔状空間形成工程）。鍔状空間 1 2 3 は、貫通孔 5 2 の開口径 R 2 よりも幅広形状となる空間であり、鍔状空間 1 2 3 の幅 W 3 は、貫通孔 5 2 の開口径 R 2 よりも大きい（W 3 > R 2）。鍔状空間 1 2 3 により Ni 層 6 2 は、露出されている。なお、現像液を貫通孔 5 2 の内部に供給する方法には、第 1 実施例で説明したディップ現像やスプレー現像を用いることができる。30

#### 【0076】

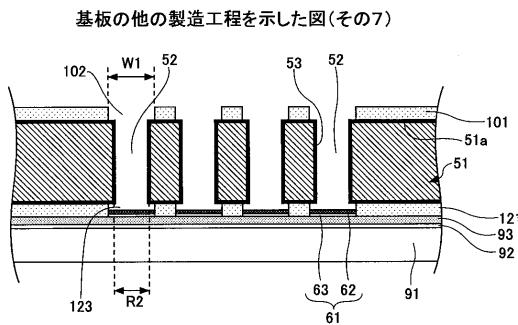

次に、図 3 6 に示すように、基材 5 1 の面 5 1 a に形成された絶縁層 5 3 上に、貫通孔 5 2 を露出すると共に、貫通孔 5 2 の開口径 R 2 よりも幅広形状の開口部 1 0 2 を有した第 2 のレジスト層 1 0 1 を形成する（第 2 のレジスト層形成工程）。第 1 の開口部である開口部 1 0 2 の幅 W 1 は、貫通孔 5 2 の開口径 R 2 よりも大きく形成されている（W 1 > R 2）。その後、図 1 1 乃至図 2 9 に示した製造工程と同様な手法により基板 5 0 を製造することができる。40

#### 【0077】

このように、第 1 の拡散防止膜形成工程と導電金属膜形成工程との間に別の工程（本実施例の場合、例えば、第 1 のレジスト層形成工程。）を設けることで、Ni 層 6 3 を形成する際に使用するめっき液が、導電金属膜 1 0 4 を形成する際に使用するめっき液に混ざることがなくなるため、膜質に優れた導電金属膜 1 0 4 を形成することができる。

#### 【0078】

以上、本発明の好ましい実施例について詳述したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において50

、種々の変形・変更が可能である。なお、第1実施例及び第2実施例では、基材51の上面51aにのみ配線68を設けたが、図14乃至図23に示した製造工程と同様な手法を用いて、接続パッド57と接続される配線（外部接続端子を含む）を設けても良い。このように、基材51の両面51a, 51bに配線を設けることで、様々なマザーボード等の基板、半導体素子、MEMS等と接続することができ、基板の適用範囲を広げることができると共に、基材51の両面に形成された配線間の電気的な接続信頼性を向上させることができる。

#### 【産業上の利用可能性】

#### 【0079】

本発明は、配線を接続する貫通ピアの電気的な接続信頼性を向上させることのできる基板の製造方法に適用できる。

10

#### 【図面の簡単な説明】

#### 【0080】

【図1】従来の基板を示した図である。

【図2】本発明の第1実施例の基板の断面図である

【図3】本実施例の基板が製造される基材の平面図である。

【図4】第1実施例の基板の製造工程を示した図（その1）である。

【図5】第1実施例の基板の製造工程を示した図（その2）である。

【図6】第1実施例の基板の製造工程を示した図（その3）である。

【図7】第1実施例の基板の製造工程を示した図（その4）である。

20

【図8】第1実施例の基板の製造工程を示した図（その5）である。

【図9】第1実施例の基板の製造工程を示した図（その6）である。

【図10】第1実施例の基板の製造工程を示した図（その7）である。

【図11】第1実施例の基板の製造工程を示した図（その8）である。

【図12】第1実施例の基板の製造工程を示した図（その9）である。

【図13】第1実施例の基板の製造工程を示した図（その10）である。

【図14】第1実施例の基板の製造工程を示した図（その11）である。

【図15】第1実施例の基板の製造工程を示した図（その12）である。

【図16】第1実施例の基板の製造工程を示した図（その13）である。

【図17】第1実施例の基板の製造工程を示した図（その14）である。

30

【図18】第1実施例の基板の製造工程を示した図（その15）である。

【図19】第1実施例の基板の製造工程を示した図（その16）である。

【図20】第1実施例の基板の製造工程を示した図（その17）である。

【図21】第1実施例の基板の製造工程を示した図（その18）である。

【図22】第1実施例の基板の製造工程を示した図（その19）である。

【図23】第1実施例の基板の製造工程を示した図（その20）である。

【図24】第1実施例の基板の製造工程を示した図（その21）である。

【図25】第1実施例の基板の製造工程を示した図（その22）である。

【図26】第1実施例の基板の製造工程を示した図（その23）である。

【図27】第1実施例の基板の製造工程を示した図（その24）である。

40

【図28】第1実施例の基板の製造工程を示した図（その25）である。

【図29】第1実施例の基板の製造工程を示した図（その26）である。

【図30】基板の他の製造工程を示した図（その1）である。

【図31】基板の他の製造工程を示した図（その2）である。

【図32】基板の他の製造工程を示した図（その3）である。

【図33】基板の他の製造工程を示した図（その4）である。

【図34】基板の他の製造工程を示した図（その5）である。

【図35】基板の他の製造工程を示した図（その6）である。

【図36】基板の他の製造工程を示した図（その7）である。

#### 【符号の説明】

50

## 【0081】

|                             |             |    |

|-----------------------------|-------------|----|

| 10, 50                      | 基板          |    |

| 11                          | シリコン基材      |    |

| 12, 52                      | 貫通孔         |    |

| 13                          | 絶縁層         |    |

| 13a, 13b, 51a, 51b, 101a    | 面           |    |

| 15, 54                      | 貫通ビア        |    |

| 15a, 15b                    | 端部          |    |

| 17, 21, 68                  | 配線          |    |

| 18, 22                      | 外部接続端子      | 10 |

| 19, 24, 75                  | ソルダーレジスト    |    |

| 22                          | 接続パッド       |    |

| 25                          | 半導体素子       |    |

| 51                          | 基材          |    |

| 53, 65                      | 絶縁層         |    |

| 55                          | 貫通部         |    |

| 56                          | 配線接続部       |    |

| 57                          | 接続パッド       |    |

| 61                          | 第1の拡散防止膜    |    |

| 62, 72                      | Ni層         | 20 |

| 63, 73                      | Au層         |    |

| 65a                         | 上面          |    |

| 65b                         | 側面          |    |

| 66                          | シード層        |    |

| 67, 104                     | 導電金属膜       |    |

| 69                          | 外部接続端子      |    |

| 71                          | 第2の拡散防止膜    |    |

| 76, 102, 103, 106, 112, 119 | 開口部         |    |

| 91                          | 支持板         |    |

| 92                          | 接着剤         | 30 |

| 93                          | 金属箔         |    |

| 94, 121                     | 第1のレジスト層    |    |

| 101                         | 第2のレジスト層    |    |

| 97, 123                     | 鎔状空間        |    |

| 105, 111, 114, 118          | ドライフィルムレジスト |    |

| 116                         | 耐熱テープ       |    |

| A                           | 基板形成領域      |    |

| B                           | 領域          |    |

| M1 ~ M4                     | 厚さ          |    |

| R1                          | 直径          | 40 |

| R2                          | 開口径         |    |

| W1 ~ W3                     | 幅           |    |

【図1】

【図2】

本発明の第1実施例の基板の断面図

【図3】

本実施例の基板が製造される基材の平面図

【図5】

第1実施例の基板の製造工程を示した図(その2)

【図6】

第1実施例の基板の製造工程を示した図(その3)

【図4】

第1実施例の基板の製造工程を示した図(その1)

【図7】

【図9】

【図8】

【図10】

【図11】

【図13】

【図12】

【図14】

【 図 1 5 】

## 第1実施例の基板の製造工程を示した図(その12)

【 図 1 6 】

### 第1実施例の基板の製造工程を示した図(その13)

【 図 1 9 】

### 第1実施例の基板の製造工程を示した図(その16)

【 図 2 0 】

### 第1実施例の基板の製造工程を示した図(その17)

【 図 1 7 】

### 第1実施例の基板の製造工程を示した図(その14)

【 図 1 8 】

### 第1実施例の基板の製造工程を示した図(その15)

【図21】

### 第1実施例の基板の製造工程を示した図(その18)

## 【 図 2 2 】

### 第1実施例の基板の製造工程を示した図(その19)

【図23】

【図24】

【図27】

【図28】

【図25】

第1実施例の基板の製造工程を示した図(その22)

【図26】

第1実施例の基板の製造工程を示した図(その23)

【図29】

第1実施例の基板の製造工程を示した図(その26)

【図30】

基板の他の製造工程を示した図(その1)

【図3 1】

【図3 2】

【図3 3】

【図3 4】

【図3 5】

【図3 6】

---

フロントページの続き

(56)参考文献 特開昭63-137498(JP,A)

特開平05-190610(JP,A)

特開2004-146742(JP,A)

特開2004-193292(JP,A)

特開2004-235528(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H05K 1/11

H05K 3/40