(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2011-0091545

(43) 공개일자 2011년08월11일

(51) Int. Cl.

*H04L 27/18* (2006.01) *H03M 13/13* (2006.01)

*HO4N 7/015* (2006.01)

(21) 출원번호 10-2011-7013826

(22) 출원일자(국제출원일자) 2009년11월17일

심사청구일자 없음

(85) 번역문제출일자 2011년06월16일

(86) 국제출원번호 PCT/US2009/006138

(87) 국제공개번호 WO 2010/056363

국제공개일자 2010년05월20일

(30) 우선권주장

61/115,123 2008년11월17일 미국(US)

(71) 출원인

톰슨 라이센싱

프랑스 애프-92100 볼로뉴-빌랑꾸르 케 아 르 갈

로 46

(72) 별명자

가오, 웬

미국 뉴저지주 08850 웨스트 원저 워릭 로드 73

첸, 호우-신

미국 뉴저지주 08902 노스 브런즈윅 플레인스 캡

로드 26

(74) 대리인

특허법인 아주양현

전체 청구항 수 : 총 26 항

(54) 케이블 텔레비전 신호에 대한 에프이씨 프레임 헤더 설계

### (57) 요 약

디지털 케이블 텔레비전 전송 시스템에 있어 헤더 정보에 적합한 효과적이고 신뢰성있는 인코딩 방법이 제공된다. FEC 헤더에 대한 검출 알고리즘과 함께, 일 실시예가 DVB-C2 표준에서의 FEC 프레임 헤더에 대하여 제시된다. DVB-C2 표준에서, 가능한 많은 유연성을 제공하기 위하여 ACM(Adaptive Coding and Modulation) 또는 VCM(Variable Coding and Modulation)이 각각의 FEC 블럭에 제공된다. 그 결과, 코딩율, 변조 타입 및 물리층 파이프 식별자(physical layer pipe identifier)를 통보하기 위해 프레임 헤더가 각 FEC 프레임의 앞에 부착된다. 물리층 관련 정보의 시그널링 뿐만 아니라, FEC 프레임 헤더는 수신기에서 쉽고 신뢰성있게 검출될 수 있도록 구조를 제공하여야 한다. DVB-C2 표준에서의 필요에 의해 동기화되어, DVB-C2 표준에 대한 FEC 헤더를 인코딩 하기 위한 효율적이고 신뢰성있는 방법 및 장치가 본 명세서의 적어도 하나의 실시예에서 제공된다. 또한, FEC 헤더의 검출 알고리즘이 기재된다.

**대 표 도** - 도3

## 특허청구의 범위

### 청구항 1

헤더 정보를 인코딩하는 방법으로서,

리드-뮬러(Reed-Muller) 코딩을 이용하여 디지털 케이블 텔레비전 환경에서 데이터 패킷에 대한 헤더 비트를 인코딩하는 단계; 및

의사-랜덤 이진 시퀀스로 상기 리드-뮬러 코딩의 출력을 변조하는 단계를 포함하는, 헤더 정보를 인코딩하는 방법.

### 청구항 2

제 1항에 있어서,

상기 리드-뮬러 인코딩 단계는 2차(second order) 리드-뮬러 코드를 사용하는, 헤더 정보를 인코딩하는 방법.

### 청구항 3

제 1항에 있어서,

상기 변조 단계는 오프셋 이진 위상 편이 방식(binary phase shift keying)을 이용하는, 헤더 정보를 인코딩하는 방법.

### 청구항 4

제 1항에 있어서,

상기 변조 단계는 직교 위상 편이 방식(quadrature phase shift keying)을 이용하는, 헤더 정보를 인코딩하는 방법.

### 청구항 5

제 1항에 있어서,

상기 변조 단계는, 상기 데이터 패킷의 데이터 부분에 대하여 어떤 변조 방식이 사용되는가에 의존하는 변조 방식을 이용하는, 헤더 정보를 인코딩하는 방법.

### 청구항 6

제 5항에 있어서,

상기 데이터 패킷의 상기 데이터 부분에 대하여 16-QAM 또는 64-QAM이 사용되는 경우 이진 위상 편이 방식이 상기 헤더 정보를 변조하는 데에 사용되고,

상기 데이터 패킷의 상기 데이터 부분에 대하여 256-QAM, 1K-QAM 또는 4K-QAM이 사용되는 경우 직교 위상 편이 방식이 상기 헤더 정보를 변조하는 데에 사용되는, 헤더 정보를 인코딩하는 방법.

### 청구항 7

헤더 정보를 인코딩하는 장치로서,

디지털 케이블 텔레비전 환경에서 데이터 패킷을 인코딩하기 위한 리드-뮬러 인코더; 및

상기 리드-뮬러 인코더의 출력을 의사-랜덤 이진 시퀀스로 처리하기 위한 변조기를 포함하는, 헤더 정보를 인코딩하는 장치.

#### 청구항 8

제 7항에 있어서,

상기 리드-뮬러 인코더는 2차(second order) 리드-뮬러 코드를 사용하는, 헤더 정보를 인코딩하는 장치.

#### 청구항 9

제 7항에 있어서,

상기 변조기는 오프셋 이진 위상 편이 방식(binary phase shift keying)을 이용하는, 헤더 정보를 인코딩하는 장치.

#### 청구항 10

제 7항에 있어서,

상기 변조기는 직교 위상 편이 방식(quadrature phase shift keying)을 이용하는, 헤더 정보를 인코딩하는 장치.

#### 청구항 11

제 7항에 있어서,

상기 변조기는, 상기 데이터 패킷의 데이터 부분에 대하여 어떤 변조 방식이 사용되는가에 의존하는 변조 방식을 이용하는, 헤더 정보를 인코딩하는 장치.

#### 청구항 12

제 11항에 있어서,

상기 데이터 패킷의 상기 데이터 부분에 대하여 16-QAM 또는 64-QAM이 사용되는 경우 이진 위상 편이 방식이 상기 헤더 정보를 변조하는 데에 사용되고,

상기 데이터 패킷의 상기 데이터 부분에 대하여 256-QAM, 1K-QAM 또는 4K-QAM이 사용되는 경우 직교 위상 편이 방식이 상기 헤더 정보를 변조하는 데에 사용되는, 헤더 정보를 인코딩하는 장치.

#### 청구항 13

헤더 정보를 디코딩하는 방법으로서,

디지털 케이블 텔레비전 환경에서 데이터 패킷에 대한 헤더 정보를 수신하는 단계;

상기 수신된 헤더 정보를 복조하는 단계;

상관값(correlation) 결과를 생성하기 위하여 상기 복조된 수신 헤더 정보를 의사-랜덤 이진 시퀀스와 상관시키

는 단계; 및

상기 복조된 수신 헤더 정보에 대하여 리드-뮬러 대칭 검출을 조건적으로 수행하는 단계를 포함하는, 헤더 정보를 디코딩하는 방법.

#### 청구항 14

제 13항에 있어서,

상기 대칭 검출을 수행하기 위한 조건은 상기 상관값 결과가 임계값보다 더 클 때인, 헤더 정보를 디코딩하는 방법.

#### 청구항 15

제 13항에 있어서,

상기 리드-뮬러 검출 단계는 2차 리드-뮬러 코드를 사용하는, 헤더 정보를 디코딩하는 방법.

#### 청구항 16

제 13항에 있어서,

상기 복조 단계는 오프셋 이진 위상 편이 방식을 이용하는, 헤더 정보를 디코딩하는 방법.

#### 청구항 17

제 13항에 있어서,

상기 복조 단계는 직교 위상 편이 방식을 이용하는, 헤더 정보를 디코딩하는 방법.

#### 청구항 18

제 13항에 있어서,

상기 복조 단계는 상기 데이터 패킷의 데이터 부분에 대하여 어떤 변조 방식이 사용되는가에 의존하는 복조 방식을 이용하는, 헤더 정보를 디코딩하는 방법.

#### 청구항 19

제 18항에 있어서,

상기 데이터 패킷의 상기 데이터 부분에 대하여 16-QAM 또는 64-QAM이 사용되는 경우 이진 위상 편이 방식이 상기 헤더 정보를 복조하는 데에 사용되고,

상기 데이터 패킷의 상기 데이터 부분에 대하여 256-QAM, 1K-QAM 또는 4K-QAM이 사용되는 경우 직교 위상 편이 방식이 상기 헤더 정보를 복조하는 데에 사용되는, 헤더 정보를 디코딩하는 방법.

#### 청구항 20

헤더 정보를 디코딩하는 장치로서,

디지털 케이블 텔레비전 환경에서 데이터 패킷에 대한 헤더 정보를 수신하기 위한 수신기;

상기 수신된 헤더 정보를 복조하기 위한 복조기;

상관값 결과를 생성하기 위하여 상기 복조된 수신 헤더 정보를 의사-랜덤 이진 시퀀스와 상관시키는 상관기; 및 상기 복조된 수신 헤더 정보를 조건적으로 처리하기 위한 리드-뮬러 대칭 검출기를 포함하는, 헤더 정보를 디코딩하는 장치.

### 청구항 21

제 20항에 있어서,

상기 대칭 검출기가 상기 복조된 수신 헤더 정보를 처리하도록 하는 조건은 상기 상관값 결과가 임계값보다 더 큰 것인, 헤더 정보를 디코딩하는 장치.

### 청구항 22

제 20항에 있어서,

상기 리드-뮬러 검출기는 2차 리드-뮬러 코드를 사용하는, 헤더 정보를 디코딩하는 장치.

### 청구항 23

제 20항에 있어서,

상기 복조기는 오프셋 이진 위상 편이 방식을 이용하는, 헤더 정보를 디코딩하는 장치.

### 청구항 24

제 20항에 있어서,

상기 복조기는 직교 위상 편이 방식을 이용하는, 헤더 정보를 디코딩하는 장치.

### 청구항 25

제 20항에 있어서,

상기 복조기는 상기 데이터 패킷의 데이터 부분에 대하여 어떤 변조 방식이 사용되는가에 의존하는 복조 방식을 이용하는, 헤더 정보를 디코딩하는 장치.

### 청구항 26

제 25항에 있어서,

상기 데이터 패킷의 상기 데이터 부분에 대하여 16-QAM 또는 64-QAM이 사용되는 경우 상기 복조기는 상기 헤더 정보를 복조하기 위하여 이진 위상 편이 방식을 사용하고,

상기 데이터 패킷의 상기 데이터 부분에 대하여 256-QAM, 1K-QAM 또는 4K-QAM이 사용되는 경우 상기 복조기는 상기 헤더 정보를 복조하기 위하여 직교 위상 편이 방식을 사용하는, 헤더 정보를 디코딩하는 장치.

## 명세서

## 기술 분야

- [0001] 본 출원은 U.S. Provisional Application Serial No. 61/115123, filed November 17, 2008의 우선권을 주장하며, 이는 여기에 그 전체로서 통합된다.

- [0002] 본 발명 원리는 케이블 전송 시스템 및 기술에 관련된다. 더욱 구체적으로는, 그것은 케이블 텔레비전 전송에 대한 FEC 헤더 설계에 관련된다.

## 배경 기술

- [0003] 케이블, 위성 및 지상파 네트워크는 디지털 방송 서비스를 최종 수요자에게 전달하는 3개의 주요한 매체이다. 위성 및 지상파 전송과는 달리, 케이블 채널은 심각한 시간 및 주파수 선택성을 나타내지는 않는다. 결과적으로, HDTV와 VoD와 같은 대역폭-소모 서비스(bandwidth-consuming services)의 용량 요구를 만족시키고 디지털 비디오 방송의 시장진출을 강화하기 위하여, 스펙트럼적으로 유효한 변조(즉, 256-QAM 및 1024-QAM)가 케이블 네트워크에서 채용된다. 최근에는, 설계 유연성, 디코딩 단순성 및 다양한 채널 타입에 걸쳐 전반적으로 뛰어난 오류 정정 성능 때문에, 저밀도 패리티-체크(low-density parity-check, LDPC) 코드가 DVB-S2 및 DVB-T2 표준에 도입되었다.

- [0004] LDPC 코드는 정방향 오류 정정(forward error correction, FEC) 블럭 코드의 일종으로서, 오디오 및/또는 비디오 데이터를 보호하기 위해 전송 환경에서 흔히 사용된다. 이러한 정방향 오류 정정 코드는, 오류와 함께 수신되는 데이터를 재전송할 필요없이, 수신기가 수신된 멀티미디어 스트림 내의 오류로부터 복원 및 정정하는 것에 대한 가능성을 증가시킨다. FEC 오류 제어 시스템은 전송기가 잔여 데이터(redundant data)를 데이터 스트림에 추가할 것을 요구한다. FEC에 의해 정정될 수 있는 오류의 최대 부분은 오류 정정 코드가 계산되는 방식에 의해 결정된다. FEC의 예로서는, 고정-크기 블럭, 수 패킷의 비트(packets of bits) 또는 미리 결정된 크기의 심볼 상에서 작용하는 LDPC 코드와 같은 블럭코드, 및 비트나 임의 길이의 심볼 스트림 상에서 작용하는 컨볼루션 코드가 있다. 많은 종류의 블럭 오류 정정 코드가 존재하는데, 그 중에는 리드-솔로몬 또는 이미 언급한 LDPC(low-density parity check)가 있다. 다른 종류의 오류 정정코드는 SMPTE 2022(Society of Motion Picture and Television Engineers)와 같이 IP 네트워크 상에서 디지털 비디오 스트림의 전송시 특수한 목적을 위해 개발되었는데, 이것은 리드-솔로몬과 같은 다른 전형적 FEC 스킵과는 달리 매우 단순한 알고리즘에 의존하고, 디지털 텔레비전을 위한 셋톱박스 수신기와 같이 한정된 재원만이 이용가능한 환경에서 유용하다.

- [0005] 정방향 오류 정정 코드는, 전송을 위해 추가되는 어떤 보충적인 데이터도 포함하여, 멀티미디어 스트림이 네트워크를 통하여 전송될 때 그 멀티미디어 스트림을 보호하기 위하여, 전송 시간 동안 연산된다. 하지만, 오류 정정 코드를 연산하는 작업은 연산 수단을 요구한다. 따라서, 실제로 오류 정정 코드는, 멀티미디어 데이터가 방송(broadcast)과 같은 방식으로 전송되도록, 즉 동일한 멀티미디어 데이터가 다수의 수신기를 동시에 담당할 수 있을 때, 생성된다. 케이블 네트워크 뿐만 아니라 방송의 실시예로는 TV/라디오 위성 또는 지상파 방송 또는 유선이나 무선 전송 미디어를 통한 IP 멀티캐스트가 있다.

- [0006] LDPC 코드의 결과로서, 예를 들어 밀도 진화(density evolution), 차분진화(differential evolution) 및 EXIT(extrinsic information transfer) 차트와 같은 프레임워크가 코드 앙상블(code ensemble)의 등급 프로파일(degree profile)을 설계 및 분석하기 위해 유도되었다. 블럭 길이가 무한정이고 코드 구조가 임의적(random)이며 디코딩 반복회수가 제한되어 있지 않다고 가정하면, 컨버전스를 디코딩하기 위한 임계 신호대 잡음비(Signal-to-Noise Ratio, SNR)에 있어서, 상기 프레임워크에 따라 구성되는 코드는 새논 리미트(Shannon limit)에 가까이 근접할 수 있다. 하지만, 실제 실행의 측면에 있어서, 임의적인 구조는 통상적으로 금지적 인코딩/디코딩 복잡성 및 메모리 요구조건으로 이어진다. 이러한 이유 때문에, 전력 효율과 실행 단순성 간에 더 나은 타협을 얻을 수 있는 구조화된 LDPC 코드가 시스템 설계자에게는 더 끌리는 옵션이 되었다. 예를 들어, DVB-S2(ETSI Second Generation Digital Video Broadcasting Standard for Satellite Channels), IEEE 802.11n 및 IEEE 802.16 표준에 의해 채택된 오류 제어 코드는 모두 구조화된 LDPC 코드(structured LDPC codes)의 카테고리에 속한다.

- [0007] 다른 한 편으로, 원래 위성 통신에서의 정방향 오류 제어를 위해 설계된 DVB-S2 LDPC 코드 패밀리는 DVB-T2(Second Generation DVB Standard Terrestrial Channels)에 의해서도 또한 사용되어 왔고 DVB-C2(Second Generation DVB Standard for Cable Channels)에 대해서도 강하게 권장된다. 시스템 호환성을 위한 고려에 더

하여, DVB-S2 코드의 사용 이면의 주된 이유는 다양한 채널 조건 하에서의 보편적인 우수한 성능에 돌려질 수 있다. 하지만, 더 높은 스펙트럼 효율과 유연한 처리에 대한 케이블 오퍼레이터에 의한 요구를 만족시키기 위해, DVB-C2에서 DVB-S2 코드를 사용하는 것에 대한 기술적인 도전은 주어진 코드를 256-QAM에서 4096-QAM의 범위에 이르는 매우 높은 차수의 컨스텔레이션(constellations)으로 맵핑하는 것에 달려있다.

[0008] DVB-C2 프로젝트는 DVB-T2 표준의 내용을 가능한 한 많이 이용하도록 꾀하였다. DVB-T2 표준에 규정된 코딩 기술(BCH+LDPC) 뿐만 아니라 OFDM 변조도 채용될 것이다. 하지만, DVB-C2 표준이 케이블 채널에서의 사용을 위해 설계되는 반면, DVB-T2 표준은 지상파 무선 채널에서의 사용을 위해 설계된다. 케이블 채널은 매우 적은 위크 에코우(weak echoes)를 갖는 고품질(고 SNR) 채널이라는 점에서, 케이블 채널은 지상파 채널과 상이하다. 또한, 케이블 텔레비전 오퍼레이터는 지상파 방송자에 비해 더 적은 스펙트럼 제약을 갖는다. 따라서, DVB-T2에서 사용되는 신호 프레임 구조와 프리앰블(preambles)은 DVB-C2 표준에서 재사용되기에 적합하지 않을 수 있다.

[0009] 정방향 오류 정정(FEC)의 프레임 헤더는 DVB-C2 표준에서의 사용을 위해 설계된다. DVB-C2 표준에서, ACM(Adaptive Coding and Modulation) 또는 VCM(Variable Coding and Modulation)이 가능한 많은 유연성을 제공하기 위하여 각각의 FEC 블럭에 제공된다. FEC 블럭은 BCH(Bose-Chaudhuri-Hocquenghem) 외부 코드와 LDPC(Low-Density-Parity-Check) 내부 코드로 구성된다. 이차원 인터리빙이 또한 수행된다. 인터리빙은 상이한 목적들을 달성하기 위하여 시퀀스의 순위(order)를 재배열하기 위한 절차이다. 시간과 주파수 영역에 걸친 선택적 페이딩(fading)에 영향을 받는 채널에 대하여, 오류 버스트(error bursts)를 분산시키기 위해 채널 코딩과 함께 비트 및/또는 심볼 인터리빙이 사용되어 왔다. 또한, 긴 랜덤 코드가 생성될 수 있도록 정보 비트를 제 2 구성요소 인코더로 스크램블(scramble)하기 위하여, 비트 인터리빙이 연접 코드(concatenated codes) 특히 터보 코드에 의해 채용된다. 코딩율, 변조 타입 및 물리층 파이프 식별자(physical layer pipe identifier)를 지시하기 위해 프레임 헤더가 각 FEC 프레임의 앞에 부착된다. 물리층 관련 정보의 시그널링 뿐만 아니라, FEC 프레임 헤더는 수신기에서 쉽고 신뢰성있게 검출될 수 있도록 구조를 제공하여야 한다.

## 발명의 내용

### 해결하려는 과제

[0010] 본 명세서에서는 적어도 하나의 실시예에 있어서 디지털 케이블 텔레비전 전송을 위한 효율적이고 신뢰성있는 FEC 프레임 헤더가 제공된다. 또한, FEC 헤더의 검출 알고리즘이 기재된다. DVB-C2 표준을 일 예로 이용하여 가능한 일 실시예가 개시된다.

### 과제의 해결 수단

[0011] 정방향 오류 정정(FEC)의 프레임 헤더가 DVB-C2 표준에서의 사용을 위해 설계된다. DVB-C2 표준에서, 가능한 많은 유연성을 제공하기 위하여 ACM(Adaptive Coding and Modulation) 또는 VCM(Variable Coding and Modulation)이 각각의 FEC 블럭에 제공된다. 그 결과, 코딩율, 변조 타입 및 물리층 파이프 식별자(physical layer pipe identifier)를 통보하기 위해 프레임 헤더가 각 FEC 프레임의 앞에 부착된다. 물리층 관련 정보의 시그널링 뿐만 아니라, FEC 프레임 헤더는 수신기에서 쉽고 신뢰성있게 검출될 수 있도록 구조를 제공하여야 한다. DVB-C2 표준에서의 필요에 의해 동기화되어, DVB-C2 표준에 대한 FEC 헤더를 인코딩하기 위한 효율적이고 신뢰성있는 방법 및 장치가 본 명세서의 적어도 하나의 실시예에서 제공된다. 또한, FEC 헤더의 검출 알고리즘이 기재된다.

## 발명의 효과

[0012] 본 명세서에서는 적어도 하나의 실시예에 있어서 디지털 케이블 텔레비전 전송을 위한 효율적이고 신뢰성있는 FEC 프레임 헤더가 제공된다.

## 도면의 간단한 설명

[0013]

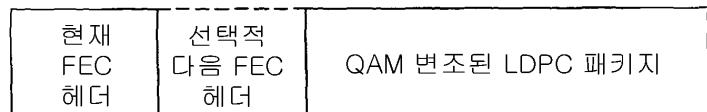

도 1은 FEC 헤더 및 선택적 다음 FEC 헤더(Next FEC Header)와 함께 데이터 슬라이스 패킷의 LDPC 시그널링부의 구조를 나타낸다.

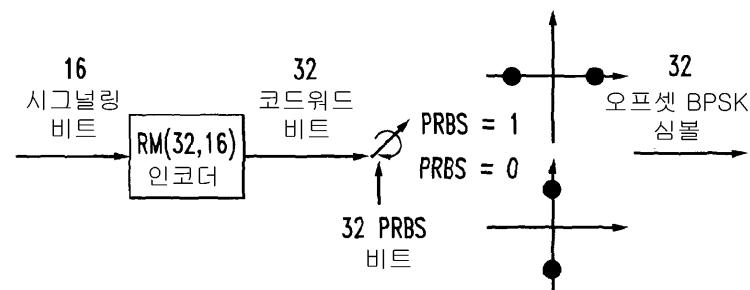

도 2는 본 발명의 원리 중의 일부에 대한 일 실시예를 나타낸다.

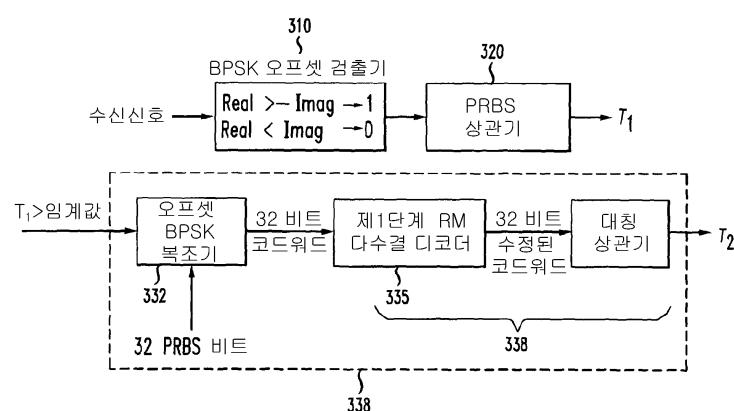

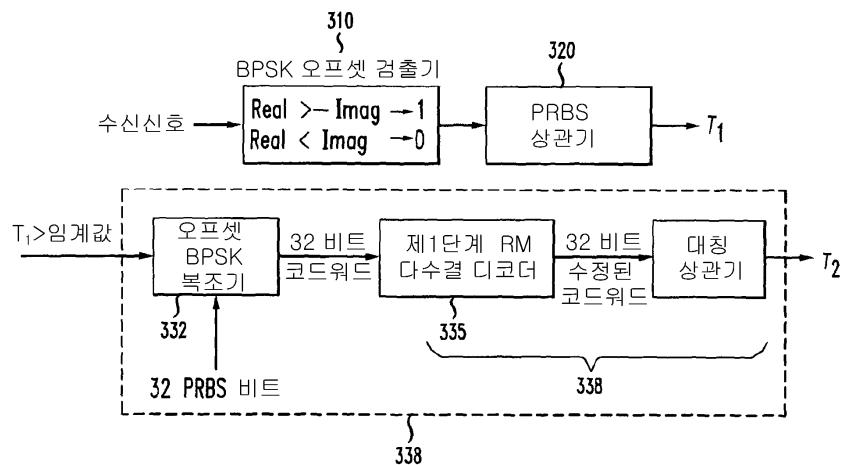

도 3은 본 발명의 원리 중 일부에 있어 FEC 헤더에 대한 검출기의 일 실시예를 나타낸다.

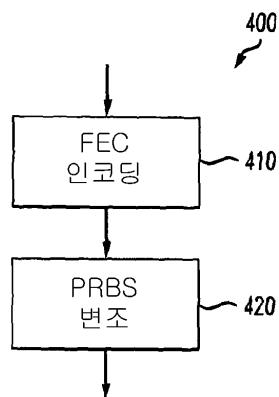

도 4는 본 발명의 원리에 있어서 인코딩 방법을 도시하는 흐름도이다.

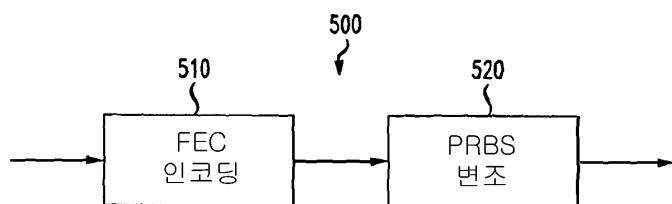

도 5는 본 발명의 원리에 따른 장치를 나타낸다.

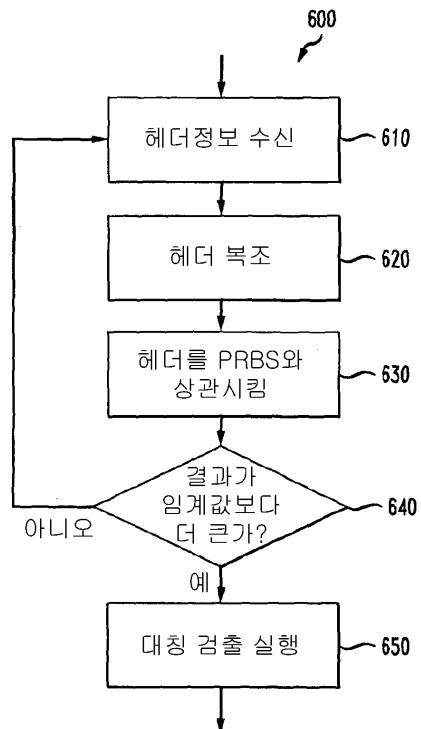

도 6은 본 발명의 원리에 있어서 디코딩 방법을 도시하는 흐름도이다.

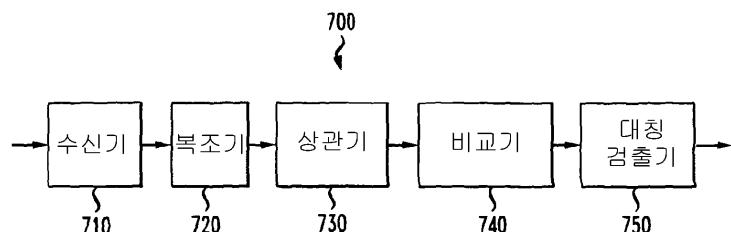

도 7은 본 발명에 있어서 디코딩을 위한 장치를 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0014]

DVB-C2 표준은 DVB 프로젝트에 의해 개발되고 있는 차세대 디지털 케이블 전송 시스템이다. DVB-C2 표준은 DVB-T2 지상파 전송 표준의 내용을 가능한 많이 사용한다. 그 결과, DVB-T2 표준에 규정되어 있는 코딩 기술 (BCH+LDPC) 뿐만 아니라 OFDM 변조도 채용될 것이다. 하지만, DVB-C2 표준은 케이블 채널에서의 사용을 위해 설계되는 반면, DVB-T2 표준은 지상파 무선 채널에서의 사용을 위해 설계된다는 것을 주지해야 한다. 케이블 채널은 단지 조금의 약 애코(weak echoes)를 갖는 고품질(높은 SNR) 채널이고, 케이블 네트워크의 스펙트럼은 다소 더 적은 제한만을 갖고 사용될 수 있는 반면 TV 방송을 위해 할당되는 무선 스펙트럼은 FCC에 의해 정의되기 때문에, 케이블 채널은 무선 채널과는 상이하다. 결과적으로, DVB-T2에서 사용되는 신호 프레임 구조와 프리앰블은 DVB-C2 표준에서 사용되기에 적합하지 않을 수 있다. 여기서 기재되는 원리들은 FEC 프레임 헤더으로 하여금 최소의 복잡도를 갖는 잡음 채널 조건 하에서 검출될 수 있도록 한다.

[0015]

DVB-C2 표준에 따라 전송되는 데이터는 데이터 슬라이스 패킷에 포함된다. 데이터 슬라이스 패킷은 하나 이상의 FEC 프레임 셀로부터 형성된다. 이러한 데이터 슬라이스 패킷은 데이터 슬라이스 타입 1(Data Slice Type 1) 또는 데이터 슬라이스 타입 2일 수 있다. 데이터 슬라이스 타입 1 패킷은 단지 FEC 프레임 데이터만 전송하며 그 시작을 검출하기 위해 레벨 1 시그널링부 2(Level 1 Signaling Part 2) 내의 포인터를 사용한다. 데이터 슬라이스 타입 2 패킷은 동기화를 허용하는 16-비트 FEC 프레임 헤더를 추가적인 정보의 전송없이 데이터 슬라이스 패킷에 전달한다. 상기 헤더는 변조, 코딩 파라미터, PLP 식별자, 및 헤더에 뒤따르는 FEC 프레임(하나 이상의)의 수에 관한 정보를 전달한다. 헤더 정보의 인코딩은 그것이 적절하게 동기화되고 디코딩될 수 있다는 것을 보증 할 수 있어야 한다.

[0016]

FEC 헤더의 배치가 도 1에 도시되어 있고, 헤더 정보를 인코딩하는 것에 대한 본 원리는 도 2에 따라 부분적으로 달성된다. 도 2는 도 1에서 QAM 변조된 LDPC 패킷으로 라벨링된 현재 FEC 프레임의 FEC 헤더 배치를 선택적 다음 FEC 헤더와 함께 나타내며, 선택적 다음 FEC 헤더는 다음 FEC 프레임에 대해 사용되는 헤더이다. FEC 헤더의 변조 순위는 그것이 FEC 프레임 데이터 부분의 변조 순위에 근거하도록 또한 적용될 수 있다. 일 예로서, 만약 FEC 프레임이 16-QAM 또는 64-QAM으로 변조되면, BPSK가 FEC 헤더의 변조를 위해 사용될 수 있다. 만약 FEC 프레임이 256-QAM, 1K-QAM 또는 4K-QAM으로 변조되면, QPSK가 FEC 헤더에 대한 변조로서 사용될 수 있다.

[0017]

도 2는 FEC 헤더의 16 시그널링 비트가 어떻게 16-QAM 또는 64-QAM 변조된 FEC 프레임에 대한 본 발명 원리를 이용하여 추가적으로 인코딩될 수 있는지를 보여준다. FEC 헤더의 16 시그널링 비트는 예를 들어 리드-뮬러(Reed-Muller)(32,16) 코딩에 의해 먼저 FEC 인코딩된다. 그리고 나서, 리드-뮬러(32,16) 코딩의 출력인 32 코드워드 비트가 의사-랜덤 이진 시퀀스(pseudo-random binary sequence)의 32비트에 따라 오프셋 BPSK에 의해 변조된다. 이러한 프로세스는 32 오프셋 BPSK 심볼로 귀결된다. 더 높은 신호-대-잡음 환경에서, 오프셋 QPSK 변조가 FEC 헤더 코딩을 위해 사용될 수 있으며, 그 결과는 16 심볼이 된다.

[0018]

도 3은 오프셋 BPSK의 경우에 대한 FEC 헤더의 검출을 나타낸다. 수신된 신호는 BPSK 오프셋 검출기(BPSK offset detector, 310)로 복조되며, BPSK 오프셋 검출기의 출력은 PRBS 상관기(PRBS correlator, 320)에 의해 의사-랜덤 이진 시퀀스와 상관된다. 만약 상관값(correlation)이 임계값보다 더 크면, 리드-뮬러 대칭 검출(330)이 수행된다. 임계값은, BPSK 복조된 신호의 양호한 상관 성능을 보여주는 값들의 경험적 근거(empirical evidence)에 근거하여 선택될 수 있다. 리드-뮬러(32,16) 코드는 2차(second order) 리드-뮬러 코드이고 그것의 코드워드는 1차 리드-뮬러 코드와는 달리 대칭적인 구조를 갖지 않는다. 리드-뮬러(32,16) 코드의 디코딩은 3 단계의 다수결 디코딩(majority decoding)으로 구성되고, 제 1 단계(335) 이후 수정된 코드워드는 1차 리드-뮬

러 코드와 같이 대칭적인 구조를 갖는다. 이러한 대칭적인 구조는 FEC 헤더의 검출시 도움을 주는 데 사용될 수 있다. 상기 의사-랜덤 이진 시퀀스 상관(332)와 리드-뮬러 대칭 상관(338)의 결과는 디코딩 결정을 하기 위해 결합된다.

[0019] 시뮬레이션 결과는, BPSK 변조와 함께 리드-뮬러(32,16) 코드의 사용이 AWGN 채널(additive white Gaussian noise channels)에 있어 10 dB SNR에서 FEC 헤더 시그널링에 대하여 무오류 결과를 달성할 수 있다는 것을 보여주었다. 다수결 디코딩은 또한 매우 낮은 복잡도를 가지며 이는 간단한 디코더라는 결과로 연결된다.

[0020] 본 기재내용은 일 실시예로서 DVB-C2의 16-비트 헤더에 적용되는 본 발명 원리를 나타낸다. 본 기술분야의 당업자라면, 비록 여기서는 명시적으로 기재되거나 도시되지 않는다는 할지라도, 본 발명의 사상 및 범위에 포함되고 본 발명을 구현하는 다양한 배치를 고안할 수 있다는 것을 이해할 것이다. 본 발명 원리는 본 발명의 방법 및 장치에 대해 적절한 변경을 갖는 상이한 길이의 헤더 정보에 동등하게 적용될 수 있다.

[0021] 도 4는 FEC 프레임 헤더를 인코딩하는 방법을 나타낸다. 인코딩은 FEC 인코딩 단계(410)에 의해 수행된다. 이 인코딩은 예를 들어 리드-뮬러(32,16) 인코딩일 수 있다. 상기 단계에 이어서, 의사-랜덤 이진 시퀀스를 이용하여 변조 단계(420)가 상기 인코딩된 헤더 출력의 변조를 수행한다. 단계(420)에 의해 수행되는 변조는 예를 들어 BPSK 또는 QPSK일 수 있다.

[0022] 도 5는 FEC 프레임 헤더를 인코딩하는 장치를 나타낸다. FEC 인코더(510)는 리드-뮬러(32,16) 인코딩과 같은 입력 FEC 프레임 헤더의 인코딩을 수행하는 데에 사용된다. 인코딩 블럭(510)의 출력은 변조기 블럭(520)에 전달된다. 변조기 블럭(520)은 의사-랜덤 이진 시퀀스를 이용하여 FEC 인코딩된 프레임 헤더값의 변조를 수행하는 데에 사용된다. 상기 변조는 예를 들어 BPSK 또는 QPSK일 수 있다.

[0023] 도 6은 FEC 프레임 헤더를 검출하는 방법을 나타낸다. 단계(610)는 헤더 정보를 수신한다. 그리고 나서 헤더는 예를 들어 BPSK 오프셋 검출기에 의해 단계(620)에서 복조된다. 단계(630)에서, 상기 복조된 헤더 출력은 의사-랜덤 이진 시퀀스와 상관된다. 이어서, 이러한 상관값(correlation)의 결과는 단계(640)에서 임계값과 비교된다. 만약 상기 상관값 결과가 임계값보다 더 크면, 대칭 검출(symmetry detection)이 단계(650)에서 수행된다. 만약 상기 상관값의 결과가 상기 임계값보다 더 크지 않으면, 프로세스는 헤더 정보를 수신하는 것에 의해 재초기화된다.

[0024] 도 7은 본 발명 원리를 이용하여 헤더 정보를 디코딩하기 위한 장치를 나타낸다. 수신기 블럭(710)은 헤더 정보를 수신한다. 수신된 헤더는, 상기 수신된 헤더 정보를 복조하는 복조 블럭(720)으로 입력된다. 상관기 블럭(730)은, 상관값 결과를 산출하기 위해, 상기 복조된 수신 헤더 정보를 의사-랜덤 이진 시퀀스와 상관시키는 데에 사용된다. 비교기 블럭(740)은 상관값 출력을 선택된 임계값과 비교한다. 만약 상기 상관값 결과가 임계값보다 더 크면, 대칭 검출 블럭(750)은 복조된 수신 헤더 정보에 대해 검출을 수행한다.

[0025] 여기에 기재된 모든 실시예 및 조건적 언어는, 발명자에 의해 본 기술분야를 발전시키도록 제공된 본 발명 원리 및 개념을 읽는 사람이 이해하는 것을 돋기 위한 교육적인 목적으로 제공되며, 그러한 구체적으로 언급된 실시예 및 조건에 한정되지 않는 것으로 해석된다.

[0026] 또한, 구체적인 실시예 뿐만 아니라 여기서 본 발명의 원리, 측면 및 실시예를 언급하고 있는 모든 서술내용은 구조적 및 기능적 균등물 모두를 포함하도록 의도된다. 추가적으로, 상기 균등물은 미래에 개발될 균등물 뿐만 아니라 현재 알려진 균등물 모두, 즉 구조에 상관없이 동일한 기능을 수행하는 개발된 어떠한 요소라도 포함한다.

[0027] 이와 같이, 예를 들어, 여기에 제시된 블럭도는 본 발명 원리를 구체화하는 예시적인 회로에 관한 개념도를 나타낸다는 것을 당업자라면 이해할 것이다. 마찬가지로, 모든 흐름 차트, 흐름도, 상태천이도, 의사코드 등은, 컴퓨터 관독하등 미디어에서 실질적으로 표시될 수 있고 컴퓨터나 프로세서에 의해 실행될 수 있는 다양한 프로세스를 나타내며, 이는 상기와 같은 컴퓨터나 프로세서가 명시적으로 도시되어 있는지 여부에 상관없이 그러하다.

[0028] 도면에 도시된 다양한 구성요소의 기능들은 적합한 소프트웨어와 연관하여 소프트웨어를 실행할 수 있는 하드웨어뿐만 아니라 전용 하드웨어의 사용을 통하여 제공될 수 있다. 프로세어에 의해 제공되는 경우, 상기 기능들은 단일 전용 프로세서에 의해, 단일 공유 프로세서에 의해, 또는 일부는 공유될 수도 있는 복수의 개별 프로세서에 의해 제공될 수 있다. 또한, "프로세서" 또는 "제어기"의 명시적인 사용은 소프트웨어를 실행할 수 있는 하드웨어를 배타적으로 언급하는 것으로 해석되어서는 안 되고, 제한없이 디지털 신호 프로세서(digital signal processor, DSP) 하드웨어, 소프트웨어 저장을 위한 ROM(read only memory), RAM(random access memory) 및 비

휘발성 저장매체를 암시적으로 포함할 수 있다.

[0029] 종래 및/또는 통상의 다른 하드웨어도 또한 포함될 수 있다. 마찬가지로, 도면에 도시된 어떠한 스위치들도 단지 개념적인 것이다. 그것들의 기능은 프로그램 로직의 동작을 통해, 전용 로직을 통해, 프로그래 제어와 전용 로직의 상호작용을 통해, 또는 심지어는 수동으로 수행될 수 있고, 그 구체적인 기술은 문맥을 통해 더욱 명확하게 이해될 수 있는 바와 같이 실행자에 의해 선택될 수 있다.

[0030] 여기서의 청구항에서, 특정 기능을 수행하기 위한 수단으로서 표현된 모든 구성요소는 상기 기능을 수행하는 어떠한 방법이라도 포함하도록 의도되고, 이는 예를 들어 a) 상기 기능을 수행하는 회로 구성요소들의 조합 또는 b) 기능을 수행하기 위해 소프트웨어를 실행하기 위한 적정 회로와 결합된 어떤 형태의 소프트웨어라도 포함하며, 이 소프트웨어는 펌웨어, 마이크로코드 등등을 포함한다. 상기 청구항에 의해 정의되는 본 발명의 원리는, 다양한 언급된 수단들에 의해 제공되는 기능들이 상기 청구항이 청구하는 바에 따라 통합되고 결합된다는 사실에 귀속된다. 따라서, 상기 기능들을 제공할 수 있는 어떠한 수단들도 여기에 설명되는 수단들과 균등하다고 여겨진다.

[0031] 다른 다양한 변형에 뿐만 아니라 본 명세서에서 본 발명 원리에 따른 "일 실시예" 또는 "어떤 실시예"라고 언급된 것은, 상기 실시예와 관련하여 기재된 특정의 특징, 구조, 특성 등등이 본 발명의 적어도 일 실시예에 포함된다는 것을 의미한다. 이와 같이, 명세서를 통하여 다양한 곳에서 나타나는 "일 실시예에서" 또는 "어떤 실시예에서"라는 문구의 사용(다른 변형에 뿐만 아니라)은 모두 반드시 동일 실시예를 언급하는 것은 아니다.

## 도면

### 도면1

### 도면2

도면3

도면4

도면5

## 도면6

## 도면7