(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6216616号

(P6216616)

(45) 発行日 平成29年10月18日(2017.10.18)

(24) 登録日 平成29年9月29日(2017.9.29)

(51) Int.Cl.

H01L 29/786 (2006.01)

F 1

|      |       |         |

|------|-------|---------|

| H01L | 29/78 | 6 1 7 U |

| H01L | 29/78 | 6 1 8 B |

| H01L | 29/78 | 6 1 8 E |

| H01L | 29/78 | 6 1 7 T |

| H01L | 29/78 | 6 1 7 N |

請求項の数 3 (全 30 頁)

(21) 出願番号 特願2013-232645 (P2013-232645)

(22) 出願日 平成25年11月11日 (2013.11.11)

(65) 公開番号 特開2014-116591 (P2014-116591A)

(43) 公開日 平成26年6月26日 (2014.6.26)

審査請求日 平成28年8月19日 (2016.8.19)

(31) 優先権主張番号 特願2012-250989 (P2012-250989)

(32) 優先日 平成24年11月15日 (2012.11.15)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 渡邊 裕一

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 大野 普司

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 市川 武宜

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面上の酸化物半導体膜と、

前記酸化物半導体膜上の一対の第1導電膜と、

前記酸化物半導体膜上及び一対の前記第1導電膜上の絶縁層と、

前記絶縁層上において、前記酸化物半導体膜と重なる第2導電膜と、を有し、

前記酸化物半導体膜は、少なくとも第1の酸化物半導体膜乃至第3の酸化物半導体膜を有し、

前記第2の酸化物半導体膜は、前記第1の酸化物半導体膜と前記第3の酸化物半導体膜との間に位置し、

前記第1の酸化物半導体膜乃至前記第3の酸化物半導体膜のそれぞれは、Inと、Gaと、Znと、を有し、

前記第1の酸化物半導体膜または前記第3の酸化物半導体膜に含まれるGaは、前記第2の酸化物半導体膜に含まれるGaよりも1.5倍以上高い原子数比で含み、

前記絶縁層は、少なくとも第1の層乃至第3の層を有し、

一対の前記第1導電膜と前記第2の層の間に位置する前記第1の層と、前記第2の層と前記第2導電膜の間に位置する前記第3の層は、珪素またはアルミニウムの酸化物または窒化物を含み、

前記第2の層は、ガリウム、ジルコニウムまたはハフニウムの酸化物を含む半導体装置。

10

20

**【請求項 2】**

絶縁表面上の第1導電膜と、

前記第1導電膜上の絶縁層と、

前記絶縁層上において、前記第1導電膜と重なる酸化物半導体膜と、

酸化物半導体膜上の一対の第2導電膜と、を有し、

前記酸化物半導体膜は、少なくとも第1の酸化物半導体膜乃至第3の酸化物半導体膜を有し、

前記第2の酸化物半導体膜は、前記第1の酸化物半導体膜と前記第3の酸化物半導体膜との間に位置し、

前記第1の酸化物半導体膜乃至前記第3の酸化物半導体膜のそれぞれは、Inと、Gaと、Znと、を有し、

前記第1の酸化物半導体膜または前記第3の酸化物半導体膜に含まれるGaは、前記第2の酸化物半導体膜に含まれるGaよりも1.5倍以上高い原子数比で含み、

前記絶縁層は、少なくとも第1の層乃至第3の層を有し、

前記第1導電膜と前記第2の層の間に位置する前記第1の層と、前記第2の層と一対の前記第2導電膜の間に位置する前記第3の層は、珪素またはアルミニウムの酸化物または窒化物を含み、

前記第2の層は、ガリウム、ジルコニウムまたはハフニウムの酸化物を含む半導体装置。

。

**【請求項 3】**

絶縁表面上の第1導電膜と、

前記第1導電膜上の絶縁層と、

前記絶縁層上において、前記第1導電膜と重なる酸化物半導体膜と、を有し、

前記酸化物半導体膜は、少なくとも第1の酸化物半導体膜乃至第3の酸化物半導体膜を有し、

前記第2の酸化物半導体膜は、前記第1の酸化物半導体膜と前記第3の酸化物半導体膜との間に位置し、

前記第1の酸化物半導体膜乃至前記第3の酸化物半導体膜のそれぞれは、Inと、Gaと、Znと、を有し、

前記第1の酸化物半導体膜または前記第3の酸化物半導体膜に含まれるGaは、前記第2の酸化物半導体膜に含まれるGaよりも1.5倍以上高い原子数比で含み、

前記絶縁層は、少なくとも第1の層乃至第3の層を有し、

前記第1導電膜と前記第2の層の間に位置する前記第1の層と、前記第2の層と一対の前記第2導電膜の間に位置する前記第3の層は、珪素またはアルミニウムの酸化物または窒化物を含み、

前記第2の層は、ガリウム、ジルコニウムまたはハフニウムの酸化物を含む半導体装置。

。

**【発明の詳細な説明】****【技術分野】****【0001】**

半導体装置、特に酸化物半導体を用いた半導体装置に関する。

**【背景技術】****【0002】**

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路(IC)などの電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

**【0003】**

例えば、インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含むアモルファス酸化物(In-Ga-Zn-O系アモルファス酸化物)からなる半導体薄膜を用いたトランジ

10

20

30

40

50

ンジスタが開示されている（特許文献1参照）。特に、酸化物半導体膜中のインジウムの含有量を多くすることにより、当該酸化物半導体膜を用いたトランジスタの移動度を高くすることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006-165529号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、インジウムを含む酸化物半導体膜上に、ゲート絶縁膜に一般的に用いられる、シリコンを含む絶縁膜を設けると、酸化物半導体膜に含まれていたインジウムが絶縁膜中に拡散することがある。そして、シリコンを含むゲート絶縁膜にインジウムが拡散すると、ゲート絶縁膜の絶縁耐圧が低下し、それによって、当該ゲート絶縁膜を用いたトランジスタの信頼性が低下する。

【0006】

上述したような技術的背景のもと、本発明の一態様では、ゲート絶縁膜の絶縁耐圧を高めることで、高い信頼性を得ることができる半導体装置の提供を、課題の一つとする。

【課題を解決するための手段】

【0007】

上述の課題を解決するため、本発明の一態様では、酸化物半導体膜にチャネル形成領域を有するトランジスタのゲート絶縁膜の材料として、インジウムなどの、酸化物半導体に含まれる金属が混入しても、十分に高い絶縁耐圧を維持することができる金属酸化物を用いる。上記金属酸化物として、酸化ガリウム、酸化ジルコニウム、または酸化ハフニウムなどが望ましい。

【0008】

さらに、本発明の一態様では、金属酸化物を含む絶縁膜と、ゲート電極、ソース電極またはドレイン電極として機能する、金属を含む導電膜との間に、金属酸化物を含む絶縁膜から上記導電膜への酸素の引き抜きを抑止することができる絶縁膜（以下、保護膜と呼ぶ）を設ける。具体的に、本発明の一態様では、ゲート絶縁膜が、第1保護膜と、金属酸化物を含む絶縁膜と、第2保護絶縁膜とが、順に積層された構造を有する。

【発明の効果】

【0009】

本発明の一態様により、ゲート絶縁膜の絶縁耐圧を高め、高い信頼性を有する半導体装置を提供することができる。

【図面の簡単な説明】

【0010】

【図1】半導体装置の一形態を説明する平面図および断面図。

【図2】半導体装置の作製方法の一形態を説明する断面図。

【図3】半導体装置の一形態を説明する断面図。

【図4】トランジスタの構成を説明する平面図および断面図。

【図5】半導体装置の一形態を説明する平面図および断面図。

【図6】半導体表示装置の構成を示す図。

【図7】半導体表示装置の構成を示す図。

【図8】半導体装置の断面図。

【図9】電子機器の図。

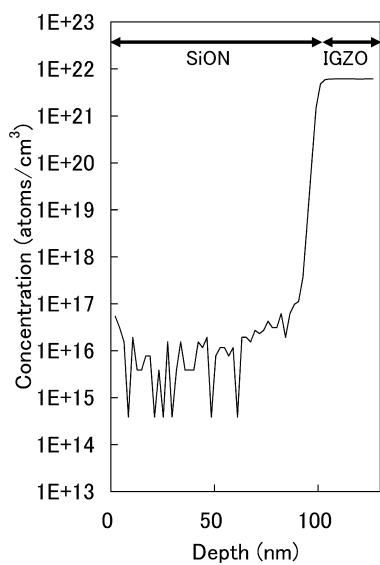

【図10】S I M S 分析の結果を示す図。

【発明を実施するための形態】

【0011】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は

10

20

30

40

50

以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

#### 【0012】

なお、本発明は、集積回路、RFタグ、半導体表示装置など、トランジスタを用いたあらゆる半導体装置を、その範疇に含む。なお、集積回路には、マイクロプロセッサ、画像処理回路、DSP(Digital Signal Processor)、マイクロコントローラを含むLSI(Large Scale Integrated Circuit)、FPGA(Field Programmable Gate Array)やCPLD(Complex PLD)などのプログラマブル論理回路(PLD:Programmable Logic Device)が、その範疇に含まれる。また、半導体表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)など、半導体膜を用いた回路素子を駆動回路に有している半導体表示装置が、その範疇に含まれる。10

#### 【0013】

##### (実施の形態1)

###### トランジスタの構造例1

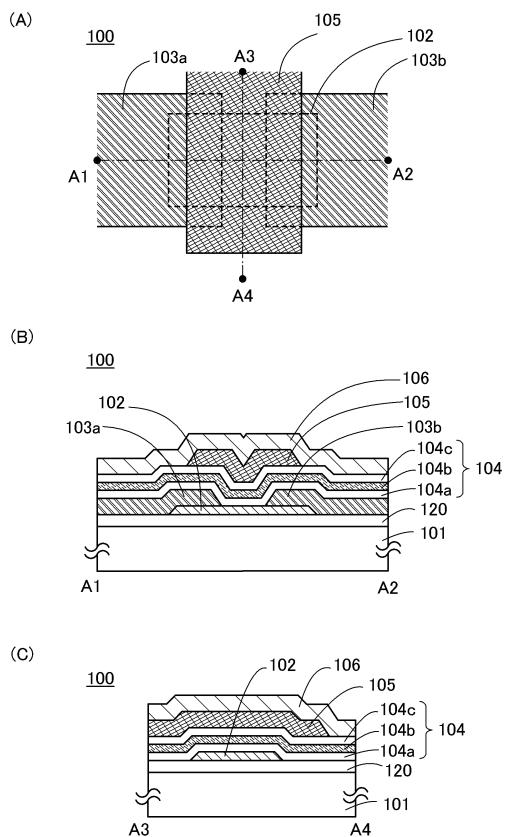

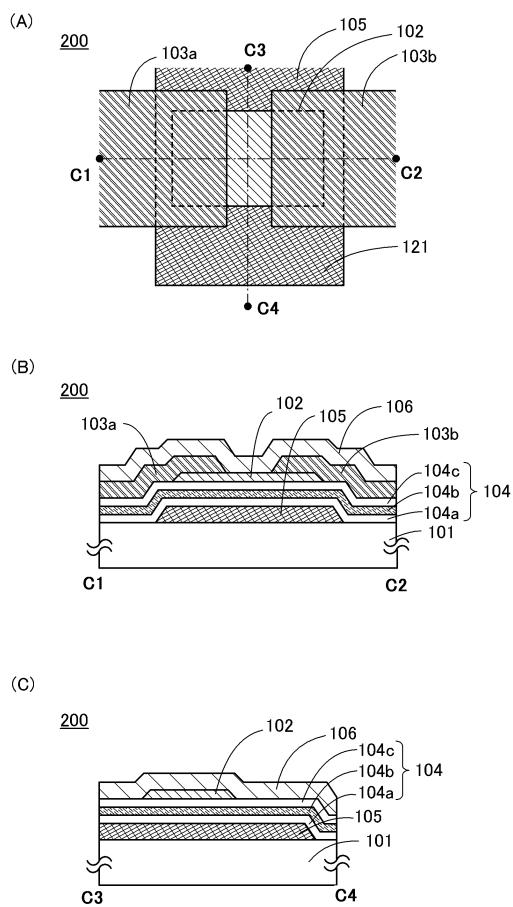

図1を用いて、本発明の一態様に係る半導体装置が有する、トランジスタの構成例について説明する。図1(A)は、トランジスタ100の上面図である。また、図1(B)は、図1(A)に示したトランジスタ100の、鎖線A1-A2における断面図に相当し、図1(C)は、鎖線A3-A4における断面図に相当する。ただし、図1(A)では、トランジスタ100のレイアウトを明確にするために、ゲート絶縁膜を含む各種絶縁膜を省略した上面図を示す。20

#### 【0014】

図1に示すトランジスタ100は、絶縁膜120が形成された基板101上に、酸化物半導体を含む半導体膜102と、半導体膜102に接するように半導体膜102上に位置し、一方がソース電極、他方がドレイン電極としての機能を有する、導電膜103a及び導電膜103bと、半導体膜102、導電膜103a及び導電膜103b上のゲート絶縁膜104と、ゲート絶縁膜104上において半導体膜102と重なるように位置し、ゲート電極としての機能を有する導電膜105と、を有する。30

#### 【0015】

図1(B)及び図1(C)では、トランジスタ100上に絶縁膜106が設けられている構成を例示している。トランジスタ100は、絶縁膜106をその構成要素に含んでいても良い。

#### 【0016】

また、図1では、絶縁膜120は必ずしも設ける必要はない。ただし、絶縁膜120を基板101と半導体膜102の間に設けることで、基板101にアルカリ金属またはアルカリ土類金属などの不純物が含まれていたときに、当該不純物が半導体膜102に混入するのを防ぐことができる。アルカリ金属またはアルカリ土類金属は、酸化物半導体と結合してキャリアを生成する場合があるため、絶縁膜120を設けることで、上記キャリアによってトランジスタ100のオフ電流が大きくなるのを防ぐことができる。40

#### 【0017】

そして、本発明の一態様では、ゲート絶縁膜104が、順に積層された保護膜104aと、金属酸化物を含む絶縁膜104bと、保護膜104cとを少なくとも有する。すなわち、ゲート絶縁膜104は、絶縁膜104bが保護膜104aと保護膜104cに挟まれた構造を有する。そのため、トランジスタ100では、絶縁膜104bと導電膜103a及び導電膜103bの間に保護膜104aが存在しており、絶縁膜104bは導電膜103a及び導電膜103bに接していない。また、トランジスタ100では、絶縁膜104b50

と導電膜 105 の間に保護膜 104c が存在しており、絶縁膜 104b は導電膜 105 に接していない。

【0018】

絶縁膜 104b は、半導体膜 102 に含まれるインジウムなどの金属が少量混入したとしても、十分に高い絶縁耐圧を維持することができる金属酸化物を用いる。上記金属酸化物として、例えば、酸化ガリウム、酸化ジルコニウム、または酸化ハフニウムを含む金属酸化物が望ましい。また、Ga-Zn 系酸化物のように、ガリウム、ジルコニウム、またはハフニウムに加えて、亜鉛を含む酸化物であっても良い。上記構成を有する絶縁膜 104b をゲート絶縁膜 104 に用いることで、保護膜 104a または保護膜 104c を介してインジウムなどの金属が、絶縁膜 104b に混入しても、絶縁膜 104b の絶縁耐圧が低下するのを防ぐことができる。10

【0019】

また、保護膜 104a 及び保護膜 104c には、絶縁膜 104b に含まれる酸素が、導電膜 103a、導電膜 103b、または導電膜 105 によって引き抜かれるのを防ぐことができる絶縁膜を用いる。例えば、保護膜 104a 及び保護膜 104c として、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化窒化アルミニウムなどを含む絶縁膜を用いることができる。

【0020】

なお、本明細書中において、酸化窒化物は、その組成として、窒素よりも酸素の含有量が多い材料を指し、窒化酸化物は、その組成として、酸素よりも窒素の含有量が多い材料を指す。20

【0021】

金属酸化物を含む絶縁膜 104b は、酸素の含有量が低下すると酸素欠損量が増加するため、酸素欠損により生成されるドナーの数も増え、絶縁耐圧が低下しやすくなる。しかし、本発明の一態様では、絶縁膜 104b と導電膜 103a 及び導電膜 103b の間に保護膜 104a を設け、絶縁膜 104b と導電膜 105 の間に保護膜 104c を設けることで、絶縁膜 104b に含まれる酸素が引き抜かれるのを防ぐことができ、上記絶縁膜 104b の絶縁耐圧が低下するのを防ぐことができる。

【0022】

したがって、本発明の一態様では、ゲート絶縁膜 104 が、順に積層された保護膜 104a と、絶縁膜 104b と、保護膜 104c とを少なくとも有することで、酸化珪素膜など、インジウムの混入により絶縁耐圧が低下する絶縁膜だけでゲート絶縁膜が構成されているトランジスタに比べて、絶縁耐圧の高いトランジスタ 100 を得ることができる。30

【0023】

また、酸化ガリウム、酸化ジルコニウム、及び酸化ハフニウムは、酸化珪素よりも比誘電率が高いため、トランジスタ 100 の微細化に伴い、ゲート絶縁膜を介してゲート電極と半導体膜の間に流れる電流（リーク電流）が増加するのを抑えることができる。特に、酸化ジルコニウム及び酸化ハフニウムは酸化珪素に比べて比誘電率が著しく高いため、酸化珪素膜だけでゲート絶縁膜が構成されているトランジスタに比べて、微細化に伴うリーク電流の増加を抑制する効果が高い。40

【0024】

#### トランジスタの作製方法

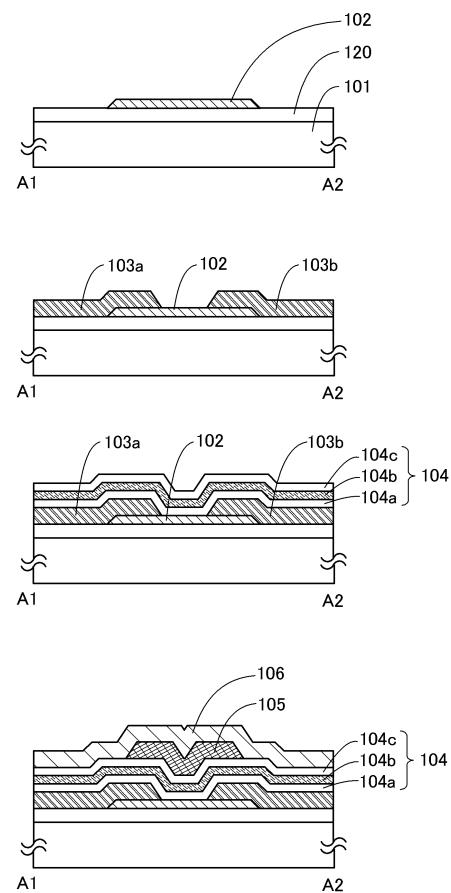

次いで、トランジスタ 100 の作製方法の一例について、図 2 を用いて説明する。

【0025】

基板 101 は、後の作製工程における処理温度に対して、耐熱性を有する基板を用いる。例えば、基板 101 として、ガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、珪素や炭化珪素などの単結晶半導体基板、多結晶半導体基板、珪素ゲルマニウムなどの化合物半導体基板、SOI (Silicon On Insulator) 基板などを用いることも可能である。或いは、既に半導体素子が設けられた基板を、基板 101 として用いてもよい。

## 【0026】

絶縁膜120は、基板101に含まれる不純物が、後に形成される半導体膜102に混入するのを防ぐ機能を有する他、半導体膜102に酸素を供給する機能をも有する。よって、絶縁膜120の材料は酸化物であることが望ましく、例えば、酸化アルミニウム、酸化マグネシウム、酸化珪素、酸化窒化珪素、窒化酸化珪素、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどを用いることができる。絶縁膜120は、プラズマCVD(Chemical Vapor Deposition)法またはスパッタリング法等により、形成することができる。

## 【0027】

10

また、絶縁膜120に、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて酸素を注入してもよい。酸素を注入することによって、絶縁膜120に、化学量論的組成よりも多くの酸素を、含有させることができる。

## 【0028】

次に、絶縁膜120上に酸化物半導体膜を形成し、選択的にエッチングを行うことで、半導体膜102を形成する(図2(A)参照)。

## 【0029】

半導体膜102として用いることのできる酸化物半導体は、少なくともインジウム(In)もしくは亜鉛(Zn)を含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

20

## 【0030】

スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)、アルミニウム(Al)、またはジルコニウム(Zr)等がある。また、他のスタビライザーとしては、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)等がある。

## 【0031】

30

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、In-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、In-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-Zr-Zn系酸化物、In-Ti-Zn系酸化物、In-Sc-Zn系酸化物、In-Y-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物等がある。

40

## 【0032】

例えば、In:Ga:Zn=1:1:1、In:Ga:Zn=3:1:2、あるいはIn:Ga:Zn=2:1:3の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

## 【0033】

また、半導体膜102に用いる酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化

50

物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、CAAC-O<sub>S</sub>(C Axis Aligned Crystalline Oxide Semiconductor)膜などをいう。

#### 【0034】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

#### 【0035】

微結晶酸化物半導体膜は、例えば、1nm以上10nm未満の大きさの微結晶(ナノ結晶ともいう。)を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

10

#### 【0036】

CAAC-O<sub>S</sub>膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が100nm未満の立方体内に収まる大きさである。従って、CAAC-O<sub>S</sub>膜に含まれる結晶部は、一辺が10nm未満、5nm未満または3nm未満の立方体内に収まる大きさの場合も含まれる。CAAC-O<sub>S</sub>膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、CAAC-O<sub>S</sub>膜について詳細な説明を行う。

20

#### 【0037】

CAAC-O<sub>S</sub>膜を透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって観察すると、結晶部同士の明確な境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、CAAC-O<sub>S</sub>膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

#### 【0038】

CAAC-O<sub>S</sub>膜を、試料面と概略平行な方向からTEMによって観察(断面TEM観察)すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-O<sub>S</sub>膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC-O<sub>S</sub>膜の被形成面または上面と平行に配列する。

30

#### 【0039】

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

#### 【0040】

一方、CAAC-O<sub>S</sub>膜を、試料面と概略垂直な方向からTEMによって観察(平面TEM観察)すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

40

#### 【0041】

断面TEM観察および平面TEM観察より、CAAC-O<sub>S</sub>膜の結晶部は配向性を有していることがわかる。

#### 【0042】

CAAC-O<sub>S</sub>膜に対し、X線回折(XRD:X-Ray Diffraction)装置を用いて構造解析を行うと、例えばInGaZnO<sub>4</sub>の結晶を有するCAAC-O<sub>S</sub>膜のout-of-plane法による解析では、回折角(2θ)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、CAAC-O<sub>S</sub>膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

50

**【0043】**

一方、 C A A C - O S 膜に対し、 c 軸に概略垂直な方向から X 線を入射させる in - plane 法による解析では、  $2\theta$  が  $56^\circ$  近傍にピークが現れる場合がある。このピークは、 InGaZnO<sub>4</sub> の結晶の (110) 面に帰属される。 InGaZnO<sub>4</sub> の単結晶酸化物半導体膜であれば、  $2\theta$  を  $56^\circ$  近傍に固定し、 試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行うと、 (110) 面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、 C A A C - O S 膜の場合は、  $2\theta$  を  $56^\circ$  近傍に固定して スキャンした場合でも、 明瞭なピークが現れない。

**【0044】**

以上のことから、 C A A C - O S 膜では、 異なる結晶部間では a 軸および b 軸の配向は不規則であるが、 c 軸配向性を有し、 かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、 前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、 結晶の a b 面に平行な面である。10

**【0045】**

なお、 結晶部は、 C A A C - O S 膜を成膜した際、 または加熱処理などの結晶化処理を行った際に形成される。 上述したように、 結晶の c 軸は、 C A A C - O S 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。 従って、 例えば、 C A A C - O S 膜の形状をエッチングなどによって変化させた場合、 結晶の c 軸が C A A C - O S 膜の被形成面または上面の法線ベクトルと平行にならないこともある。

**【0046】**

また、 C A A C - O S 膜中の結晶化度が均一でなくてもよい。 例えば、 C A A C - O S 膜の結晶部が、 C A A C - O S 膜の上面近傍からの結晶成長によって形成される場合、 上面近傍の領域は、 被形成面近傍の領域よりも結晶化度が高くなることがある。 また、 C A A C - O S 膜に不純物を添加する場合、 不純物が添加された領域の結晶化度が変化し、 部分的に結晶化度の異なる領域が形成されることもある。20

**【0047】**

なお、 InGaZnO<sub>4</sub> の結晶を有する C A A C - O S 膜の out - of - plane 法による解析では、  $2\theta$  が  $31^\circ$  近傍のピークの他に、  $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。  $2\theta$  が  $36^\circ$  近傍のピークは、 C A A C - O S 膜中の一部に、 c 軸配向性を有さない結晶が含まれることを示している。 C A A C - O S 膜は、  $2\theta$  が  $31^\circ$  近傍にピークを示し、  $2\theta$  が  $36^\circ$  近傍にピークを示さないことが好ましい。30

**【0048】**

C A A C - O S 膜を用いたトランジスタは、 可視光や紫外光の照射による電気的特性の変動が小さい。 よって、 当該トランジスタは、 信頼性が高い。

**【0049】**

なお、 酸化物半導体膜は、 例えば、 非晶質酸化物半導体膜、 微結晶酸化物半導体膜、 C A A C - O S 膜のうち、 二種以上を有する積層膜であってもよい。

**【0050】**

C A A C - O S 膜で構成された酸化物半導体膜は、 スパッタリング法によっても作製することができる。 スパッタリング法によって C A A C - O S 膜を得るには酸化物半導体膜の堆積初期段階において六方晶の結晶が形成されるようにすることと、 当該結晶を種として結晶が成長されるようにすることが肝要である。 そのためには、 ターゲットと基板の距離を広くとり ( 例えは、 150 mm ~ 200 mm 程度 ) 、 基板加熱温度を 100 ~ 500 、 好適には 200 ~ 400 、 さらに好適には 250 ~ 300 にすると好ましい。 また、 これに加えて、 成膜時の基板加熱温度よりも高い温度で、 堆積された酸化物半導体膜を熱処理することで膜中に含まれるミクロな欠陥や、 積層界面の欠陥を修復することができる。40

**【0051】**

C A A C - O S 膜は、 例えは、 多結晶である酸化物半導体スパッタリング用ターゲットを用い、 スパッタリング法によって成膜する。 当該スパッタリング用ターゲットにイオンが50

衝突すると、スパッタリング用ターゲットに含まれる結晶領域が a - b 面から劈開し、a - b 面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、C A A C - O S 膜を成膜することができる。

#### 【 0 0 5 2 】

また、C A A C - O S 膜を成膜するために、以下の条件を適用することが好ましい。

#### 【 0 0 5 3 】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が - 80 以下、好ましくは - 100 以下である成膜ガスを用いる。10

#### 【 0 0 5 4 】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起り、スパッタリング粒子の平らな面が基板に付着する。

#### 【 0 0 5 5 】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積 % 以上、好ましくは 100 体積 % とする。20

#### 【 0 0 5 6 】

スパッタリング用ターゲットの一例として、In - Ga - Zn - O 化合物ターゲットについて以下に示す。

#### 【 0 0 5 7 】

In<sub>x</sub>O<sub>y</sub> 粉末、GaO<sub>y</sub> 粉末およびZnO<sub>z</sub> 粉末を所定の mol 数比で混合し、加圧処理後、1000 以上 1500 以下の温度で加熱処理することで多結晶である In - Ga - Zn - O 化合物ターゲットとする。なお、X、Y および Z は任意の正数である。ここで、所定の mol 数比は、例えば、In<sub>x</sub>O<sub>y</sub> 粉末、GaO<sub>y</sub> 粉末およびZnO<sub>z</sub> 粉末が、2 : 2 : 1、8 : 4 : 3、3 : 1 : 1、1 : 1 : 1、4 : 2 : 3 または 3 : 1 : 2 である。なお、粉末の種類、およびその混合する mol 数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。30

#### 【 0 0 5 8 】

なお、半導体膜 102 を構成する酸化物半導体膜に水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じやすい。そして、電子が生じることで、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そこで、絶縁膜 120 上に酸化物半導体膜を形成した後、エッチングにより半導体膜 102 を形成する前に、第 1 の加熱処理を行うことが好ましい。第 1 の加熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、または減圧状態で行えばよい。40 第 1 の加熱処理により、酸化物半導体膜から水素または水分を除去し、絶縁膜 120 に含まれる酸素が酸化物半導体膜に供給されることで酸素欠損を補填することができる。また、第 1 の加熱処理により、酸化物半導体膜の結晶性を高めることができる。なお、第 1 の加熱処理は、不活性ガス雰囲気で加熱処理した後に、酸化性ガスを 10 ppm 以上含む雰囲気で行ってもよい。上記構成により、酸化物半導体膜への酸素の供給量をより高め、酸素欠損量をより減少させることができる。

#### 【 0 0 5 9 】

なお、第 1 の加熱処理は、エッチングにより半導体膜 102 を形成した後に、行われても良い。

#### 【 0 0 6 0 】

10

20

30

40

50

このように、水素または水分が除去され、酸素欠損が補填されることによって高純度化された半導体膜 102 は、i 型（真性）または i 型に限りなく近い。そのため、高純度化された半導体膜 102 にチャネル形成領域を有するトランジスタ 100 は、オフ電流が著しく小さく、信頼性が高い。

#### 【0061】

具体的に、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタのオフ電流が小さいことは、いろいろな実験により証明できる。例えば、チャネル幅が  $1 \times 10^6 \mu\text{m}$  でチャネル長が  $10 \mu\text{m}$  の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が  $1\text{V}$  から  $10\text{V}$  の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち  $1 \times 10^{-13}\text{A}$  以下という特性を得ることができる。

この場合、トランジスタのチャネル幅で規格化したオフ電流は、 $100\text{zA}/\mu\text{m}$  以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、高純度化された酸化物半導体膜を上記トランジスタのチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が  $3\text{V}$  の場合に、数十  $\text{yA}/\mu\text{m}$  という、さらに小さいオフ電流が得られることが分かった。従って、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有する珪素を用いたトランジスタに比べて著しく小さい。

#### 【0062】

次に、半導体膜 102 上に導電膜を形成した後、当該導電膜をエッチング等により所望の形状に加工することで、ソース電極またはドレイン電極としての機能を有する導電膜 103a 及び導電膜 103b を形成する（図 2（B）参照）。導電膜 103a 及び導電膜 103b は、モリブデン、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、スカンジウム、ニオブ等の金属材料を用いた導電膜、これら金属材料を主成分とする合金材料を用いた導電膜を用いることができる。

#### 【0063】

次に、絶縁膜 120、半導体膜 102、導電膜 103a および導電膜 103b 上に、保護膜 104a、絶縁膜 104b、及び保護膜 104c を順に積層するように形成することで、ゲート絶縁膜 104 を形成する（図 2（C）参照）。

#### 【0064】

具体的に、保護膜 104a または保護膜 104c として、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化窒化アルミニウムなどを含む絶縁膜を用いることができる。保護膜 104a 及び保護膜 104c は、スパッタリング法、または CVD 法などを適宜用いて形成することができる。

#### 【0065】

また、絶縁膜 104b には、半導体膜 102 に含まれるインジウムなどの金属が少量混入したとしても、十分に高い絶縁耐圧を維持することができる金属酸化物を用いる。上記金属酸化物として、例えば、酸化ガリウム、酸化ジルコニウム、または酸化ハフニウムなどが望ましい。また、Ga-Zn 系酸化物のように、ガリウム、ジルコニウム、またはハフニウムに加えて、亜鉛を含む酸化物であっても良い。

#### 【0066】

絶縁膜 104b は、スパッタリング法、または CVD 法などを適宜用いて形成することができる。

#### 【0067】

そして、保護膜 104a、絶縁膜 104b、及び保護膜 104c は、大気にさらすことなく連続的に形成することが、各膜どうしの界面に不純物が混入するのを防ぐことができるるので、好ましい。

#### 【0068】

例えば、酸化珪素を用いて保護膜 104a を、酸化ガリウムを用いて絶縁膜 104b を、

10

20

30

40

50

酸化珪素を用いて保護膜 104c を形成する場合の、具体的な作製方法の一例について述べる。まず、酸化珪素をターゲットして用い、酸素の流量 50 sccm、成膜圧力 0.4 Pa、13.56 MHz である RF 電源の電力を 1.5 kW、基板温度 100°、基板とターゲット間の距離を 60 mm とし、スパッタリング法を用いて酸化珪素を含む膜厚 10 nm の保護膜 104a を形成する。次いで、酸化ガリウムをターゲットして用い、酸素の流量 50 sccm、成膜圧力 0.4 Pa、13.56 MHz である RF 電源の電力を 1 kW、基板温度 350°、基板とターゲット間の距離を 60 mm とし、スパッタリング法を用いて酸化ガリウムを含む膜厚 100 nm の絶縁膜 104b を形成する。次いで、酸化珪素をターゲットして用い、酸素の流量 50 sccm、成膜圧力 0.4 Pa、13.56 MHz である RF 電源の電力を 1.5 kW、基板温度 100°、基板とターゲット間の距離を 60 mm とし、スパッタリング法を用いて酸化珪素を含む膜厚 10 nm の保護膜 104c を形成する。上記作製方法により、ゲート絶縁膜 104 を形成することができる。

#### 【0069】

そして、導電膜 103a、導電膜 103b、または、後に形成される導電膜 105 によって、絶縁膜 104b から酸素が引き抜かれるのを防ぐためには、保護膜 104a 及び保護膜 104c の膜厚は、5 nm 以上、より好ましくは 10 nm 以上であることが望ましい。また、ゲート絶縁膜 104 の耐圧性を確保するためには、絶縁膜 104b の膜厚は 5 nm 以上、より好ましくは 10 nm 以上であることが望ましい。そして、ゲート絶縁膜 104 の膜厚は、15 nm 以上 500 nm 以下、好ましくは 30 nm 以上 300 nm 以下となるように、保護膜 104a、絶縁膜 104b、及び保護膜 104c の膜厚を、それぞれ定めれば良い。

#### 【0070】

次いで、第 2 の加熱処理を行うことが好ましい。第 2 の加熱処理は、第 1 の加熱処理と同様の条件で行うことができる。第 2 の加熱処理により、半導体膜 102 から、さらに水素や水などの不純物を除去することができる。また、ゲート絶縁膜 104 膜中から、水素、水分等を除去することができ、緻密なゲート絶縁膜 104 を形成することができる。なお、第 2 の加熱処理は、導電膜 103a 及び導電膜 103b を形成した後、ゲート絶縁膜 104 を形成する前に行っても良い。

#### 【0071】

次いで、ゲート絶縁膜 104 上に、スパッタリング法などにより導電膜を形成した後、当該導電膜をエッチング等により所望の形状に加工することで、ゲート電極としての機能を有する導電膜 105 を形成する。導電膜 105 としては、アルミニウム、チタン、クロム、コバルト、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、タンタル、タンクステン、またはこれらを主成分とする合金材料を用いることができる。

#### 【0072】

次いで、ゲート絶縁膜 104、および導電膜 105 上に、絶縁膜 106 を形成する（図 2 (D) 参照）。絶縁膜 106 としては、酸素の拡散または移動が少ない材料を用いると良い。また、絶縁膜 106 は、水素の含有量が少ない材料を用いると良い。絶縁膜 106 中の水素の含有量としては、好ましくは  $5 \times 10^{-9} \text{ cm}^{-3}$  未満、さらに好ましくは  $5 \times 10^{-8} \text{ cm}^{-3}$  未満とする。絶縁膜 106 中の水素の含有量を上記数値とすることによって、トランジスタ 100 のオフ電流を低くすることができる。

#### 【0073】

例えば、絶縁膜 106 としては、窒化珪素膜、窒化酸化珪素膜を用いるとよい。また、絶縁膜 106 は、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて形成することができる。とくに、絶縁膜 106 は、スパッタリング法を用いて窒化珪素膜を形成すると、膜中の水、水素の含有量が少ないため、好ましい。

#### 【0074】

以上の工程により、図 1 に示すトランジスタ 100 を作製することができる。

#### 【0075】

10

20

30

40

50

## 半導体膜の構造について

次いで、半導体膜 102 の構造の一例について、詳しく述べる。

### 【0076】

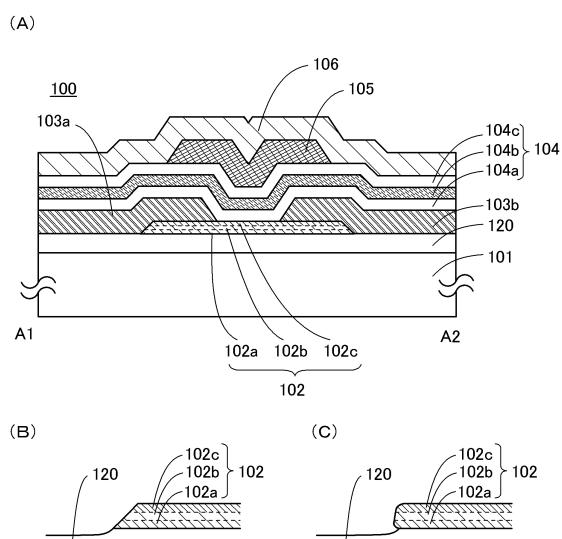

半導体膜 102 は、単数の酸化物半導体膜で構成されているとは限らず、積層された複数の酸化物半導体膜で構成されていても良い。半導体膜 102 が、酸化物半導体膜 102a 乃至酸化物半導体膜 102c で構成されている場合の、トランジスタ 100 の構成例を、図 3 に示す。

### 【0077】

図 3 (A) に示すトランジスタ 100において、酸化物半導体膜 102a 乃至酸化物半導体膜 102c は、絶縁膜 120 側から順に積層されている。

10

### 【0078】

そして、酸化物半導体膜 102a 及び酸化物半導体膜 102c は、酸化物半導体膜 102b を構成する金属元素の少なくとも 1 つを、その構成要素に含み、伝導帯下端のエネルギーが酸化物半導体膜 102b よりも 0.05 eV 以上、0.07 eV 以上、0.1 eV 以上または 0.15 eV 以上、かつ 2 eV 以下、1 eV 以下、0.5 eV 以下または 0.4 eV 以下、真空準位に近い酸化物膜である。さらに、酸化物半導体膜 102b は、少なくともインジウムを含むと、キャリア移動度が高くなるため好ましい。

### 【0079】

上記構成をトランジスタ 100 が有する場合、ゲート電極としての機能を有する導電膜 105 に電圧を印加することで、半導体膜 102 に電界が加わると、半導体膜 102 のうち、伝導帯下端のエネルギーが小さい酸化物半導体膜 102b にチャネル領域が形成される。即ち、酸化物半導体膜 102b とゲート絶縁膜 104 との間に酸化物半導体膜 102c が設けられていることによって、ゲート絶縁膜 104 と離隔している酸化物半導体膜 102b に、チャネル領域を形成することができる。

20

### 【0080】

また、酸化物半導体膜 102c は、酸化物半導体膜 102b を構成する金属元素の少なくとも 1 つをその構成要素に含むため、酸化物半導体膜 102b と酸化物半導体膜 102c の界面では、界面散乱が起こりにくい。従って、当該界面においてキャリアの動きが阻害されにくいため、トランジスタ 100 の電界効果移動度が高くなる。

### 【0081】

30

また、酸化物半導体膜 102b と酸化物半導体膜 102a の界面に界面準位が形成されると、界面近傍の領域にもチャネル領域が形成されるために、トランジスタ 100 のしきい値電圧が変動してしまう。しかし、酸化物半導体膜 102a は、酸化物半導体膜 102b を構成する金属元素の少なくとも 1 つをその構成要素に含むため、酸化物半導体膜 102b と酸化物半導体膜 102a の界面には、界面準位が形成されにくい。よって、上記構成により、トランジスタ 100 のしきい値電圧等の電気的特性のばらつきを、低減することができる。

### 【0082】

また、酸化物半導体膜間に不純物が存在することによって、各膜の界面にキャリアの流れを阻害する界面準位が形成されることがないよう、複数の酸化物半導体膜を積層させることができ望ましい。積層された酸化物半導体膜の膜間に不純物が存在していると、酸化物半導体膜間における伝導帯下端のエネルギーの連続性が失われ、界面近傍において、キャリアがトラップされるか、あるいは再結合により消滅してしまうからである。膜間における不純物を低減させることで、主成分である一の金属を少なくとも共に有する複数の酸化物半導体膜を、単に積層させるよりも、連続接合（ここでは特に伝導帯下端のエネルギーが各膜の間で連続的に変化する U 字型の井戸構造を有している状態）が形成されやすくなる。

40

### 【0083】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純

50

物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気( $1 \times 10^{-4}$  Pa ~  $5 \times 10^{-7}$  Pa程度まで)することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。

#### 【0084】

高純度の真性な酸化物半導体を得るために各チャンバー内を高真空排気するのみならず、スパッタリングに用いるガスの高純度化も重要である。上記ガスとして用いる酸素ガスやアルゴンガスの露点を、-40以下、好ましくは-80以下、より好ましくは-100以下とし、使用するガスの高純度化を図ることで、酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

10

#### 【0085】

例えば、酸化物半導体膜102aまたは酸化物半導体膜102cは、アルミニウム、シリコン、チタン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、スズ、ランタン、セリウムまたはハフニウムを、酸化物半導体膜102bよりも高い原子数比で含む酸化物膜であればよい。具体的に、酸化物半導体膜102aまたは酸化物半導体膜102cとして、酸化物半導体膜102bよりも上述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物膜を用いると良い。前述の元素は酸素と強く結合するため、酸素欠損が酸化物膜に生じることを抑制する機能を有する。よって、上記構成により、酸化物半導体膜102aまたは酸化物半導体膜102cを、酸化物半導体膜102bよりも酸素欠損が生じにくい酸化物膜にすることができる。

20

#### 【0086】

具体的に、酸化物半導体膜102bと、酸化物半導体膜102aまたは酸化物半導体膜102cとが、共にIn-M-Zn系酸化物膜である場合、酸化物半導体膜102aまたは酸化物半導体膜102cの原子数比を $In : M : Zn = x_1 : y_1 : z_1$ 、酸化物半導体膜102bの原子数比を $In : M : Zn = x_2 : y_2 : z_2$ とすると、 $y_1 / x_1$ が $y_2 / x_2$ よりも大きくなるように、その原子数比を設定すれば良い。なお、元素MはInよりも酸素との結合力が強い金属元素であり、例えばAl、Ti、Ga、Y、Zr、Sn、La、Ce、NdまたはHf等が挙げられる。好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも1.5倍以上大きくなるように、その原子数比を設定すれば良い。さらに好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも2倍以上大きくなるように、その原子数比を設定すれば良い。より好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも3倍以上大きくなるように、その原子数比を設定すれば良い。さらに、酸化物半導体膜102bにおいて、 $y_1$ が $x_1$ 以上であると、トランジスタ100に安定した電気的特性を付与できるため好ましい。ただし、 $y_1$ が $x_1$ の3倍以上になると、トランジスタ100の電界効果移動度が低下してしまうため、 $y_1$ は $x_1$ の3倍未満であると好ましい。

30

#### 【0087】

酸化物半導体膜102a及び酸化物半導体膜102cの厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、酸化物半導体膜102bの厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下であり、さらに好ましくは3nm以上50nm以下である。

40

#### 【0088】

3層構造の半導体膜102において、酸化物半導体膜102a乃至酸化物半導体膜102cは、非晶質または結晶質の両方の形態を取りうる。ただし、チャネル領域が形成される酸化物半導体膜102bが結晶質であることにより、トランジスタ100に安定した電気的特性を付与することができるため、酸化物半導体膜102bは結晶質であることが好ましい。

#### 【0089】

なお、チャネル形成領域とは、トランジスタの半導体膜のうち、ゲート電極と重なり、かつソース電極とドレイン電極に挟まれる領域を意味する。また、チャネル領域とは、チャネル形成領域において、電流が主として流れる領域をいう。

50

**【 0 0 9 0 】**

例えは、酸化物半導体膜 102a 及び酸化物半導体膜 102c として、スパッタリング法により形成した In - Ga - Zn 系酸化物膜を用いる場合、酸化物半導体膜 102a 及び酸化物半導体膜 102c の成膜には、In - Ga - Zn 系酸化物 (In : Ga : Zn = 1 : 3 : 2 [原子数比]) であるスパッタリング用ターゲットを用いることができる。成膜条件は、例えは、成膜ガスとしてアルゴンガスを 30 sccm、酸素ガスを 15 sccm 用い、圧力 0.4 Pa とし、基板温度を 200 とし、DC 電力 0.5 kW とすればよい。

**【 0 0 9 1 】**

また、酸化物半導体膜 102b を CAAc - OS 膜とする場合、酸化物半導体膜 102b の成膜には、In - Ga - Zn 系酸化物 (In : Ga : Zn = 1 : 1 : 1 [原子数比]) であり、多結晶の In - Ga - Zn 系酸化物を含むスパッタリング用ターゲットを用いることが好ましい。成膜条件は、例えは、成膜ガスとしてアルゴンガスを 30 sccm、酸素ガスを 15 sccm 用い、圧力を 0.4 Pa とし、基板の温度 300 とし、DC 電力 0.5 kW とすることができる。

**【 0 0 9 2 】**

なお、図 3 (A) では、平坦な絶縁膜 120 上に半導体膜 102 が設けられている構造を示している。しかし、本発明の一態様では、図 3 (B) に示すように、エッチングにより半導体膜 102 を形成する際に、絶縁膜 120 の一部も共にエッチングされていても良い。この場合、絶縁膜 120 が、半導体膜 102 の下に位置する領域に凸部を有することとなる。

**【 0 0 9 3 】**

また、図 3 (A) では、半導体膜 102 の端部が傾斜している構造を示している。しかし、本発明の一態様では、図 3 (C) に示すように、半導体膜 102 の端部が丸みを帯びる構造を有していても良い。

**【 0 0 9 4 】**

なお、図 3 (B) 及び図 3 (C) では積層構造の半導体膜 102 を例示しているが、図 3 (B) に示した絶縁膜 120 の構造と、図 3 (C) に示した半導体膜 102 の端部の構造については、半導体膜 102 が単層構造を有する場合にも、適用させることができる。

**【 0 0 9 5 】****トランジスタの構造例 2**

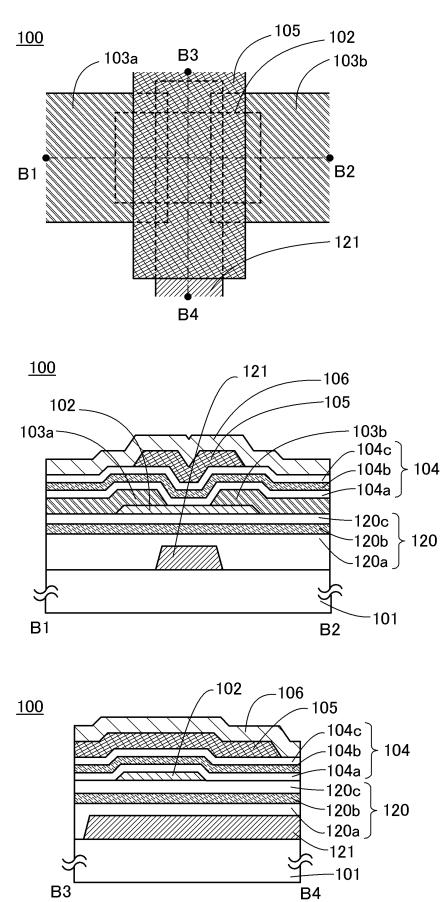

次いで、図 4 を用いて、図 1 に示したトランジスタ 100 に、半導体膜 102 を間に挟んで導電膜 105 と対峙する位置に、ゲート電極としての機能を有する導電膜が設けられた構造を有する、トランジスタ 100 の構成例について説明する。

**【 0 0 9 6 】**

図 4 (A) は、トランジスタ 100 の上面図である。また、図 4 (B) は、図 4 (A) に示したトランジスタ 100 の、鎖線 B1 - B2 における断面図に相当し、図 4 (C) は、鎖線 B3 - B4 における断面図に相当する。ただし、図 4 (A) では、トランジスタ 100 のレイアウトを明確にするために、ゲート絶縁膜を含む各種絶縁膜を省略した上面図を示す。

**【 0 0 9 7 】**

図 4 に示すトランジスタ 100 では、基板 101 と絶縁膜 120 との間に、ゲート電極としての機能を有する導電膜 121 が設けられている。また、導電膜 121 は、絶縁膜 120、半導体膜 102、及びゲート絶縁膜 104 を間に挟んで、導電膜 105 と重なっている。なお、図 4 では、基板 101 上に接するように導電膜 121 が設けられている場合を例示しているが、基板 101 と導電膜 121 の間に、絶縁膜が設けられていても良い。

**【 0 0 9 8 】**

また、図 4 では、絶縁膜 120 が、順に積層された保護膜 120a と、金属酸化物を含む絶縁膜 120b と、保護膜 120c とを有する場合を例示している。すなわち、絶縁膜 120 は、絶縁膜 120b が保護膜 120a と保護膜 120c に挟まれた構造を有する。そ

10

20

30

40

50

のため、トランジスタ 100 では、絶縁膜 120b と導電膜 121 の間に保護膜 120a が存在しており、絶縁膜 120b は導電膜 121 に接していない。また、トランジスタ 100 では、絶縁膜 120b と導電膜 103a 及び導電膜 103b の間に保護膜 120c が存在しており、絶縁膜 120b は導電膜 103a 及び導電膜 103b に接していない。

#### 【0099】

絶縁膜 120b は、半導体膜 102 に含まれるインジウムなどの金属が少量混入したとしても、十分に高い絶縁耐圧を維持することができる金属酸化物を用いる。上記金属酸化物として、例えば、酸化ガリウム、酸化ジルコニウム、または酸化ハフニウムなどが望ましい。また、Ga-Zn 系酸化物のように、ガリウム、ジルコニウム、またはハフニウムに加えて、亜鉛を含む酸化物であっても良い。上記構成を有する絶縁膜 120b を絶縁膜 120 に用いることで、保護膜 120a または保護膜 120c を介してインジウムなどの金属が、絶縁膜 120b に混入しても、絶縁膜 120b の絶縁耐圧が低下するのを防ぐことができる。10

#### 【0100】

また、保護膜 120a 及び保護膜 120c には、絶縁膜 120b に含まれる酸素が、導電膜 103a、導電膜 103b、または導電膜 121 によって引き抜かれるのを防ぐことができる絶縁膜を用いる。例えば、保護膜 120a 及び保護膜 120c として、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化窒化アルミニウムなどを含む絶縁膜を用いることができる。

#### 【0101】

金属酸化物を含む絶縁膜 120b は、酸素の含有量が低下すると酸素欠損量が増加するため、酸素欠損により生成されるドナーの数も増え、絶縁耐圧が低下しやすくなる。しかし、本発明の一態様では、絶縁膜 120b と導電膜 121 の間に保護膜 120a を設け、絶縁膜 120b と導電膜 103a 及び導電膜 103b の間に保護膜 120c を設けることで、絶縁膜 120b に含まれる酸素が引き抜かれるのを防ぐことができ、上記絶縁膜 120b の絶縁耐圧が低下するのを防ぐことができる。20

#### 【0102】

したがって、本発明の一態様では、絶縁膜 120 が、順に積層された保護膜 120a と、絶縁膜 120b と、保護膜 120c とを少なくとも有することで、酸化珪素膜など、インジウムの混入により絶縁耐圧が低下する絶縁膜だけでゲート絶縁膜が構成されているトランジスタに比べて、絶縁耐圧の高いトランジスタ 100 を得ることができる。30

#### 【0103】

なお、絶縁膜 120 は、必ずしも上述した構成を有する必要はなく、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化窒化アルミニウムなどを含む単層の絶縁膜で構成されていても良い。

#### 【0104】

##### トランジスタの構造例 3

次いで、図 5 を用いて、本発明の一態様に係る半導体装置が有する、トランジスタの別の構成例について説明する。

#### 【0105】

図 5 (A) は、トランジスタ 200 の上面図である。また、図 5 (B) は、図 5 (A) に示したトランジスタ 200 の、鎖線 C1-C2 における断面図に相当し、図 5 (C) は、鎖線 C3-C4 における断面図に相当する。ただし、図 5 (A) では、トランジスタ 200 のレイアウトを明確にするために、ゲート絶縁膜を含む各種絶縁膜を省略した上面図を示す。40

#### 【0106】

図 5 に示すトランジスタ 200 は、基板 101 上に、ゲート電極としての機能を有する導電膜 105 と、導電膜 105 上のゲート絶縁膜 104 と、ゲート絶縁膜 104 上において導電膜 105 と重なるように位置する、酸化物半導体を含む半導体膜 102 と、半導体膜 102 に接するように半導体膜 102 上に位置し、一方がソース電極、他方がドレイン電50

極としての機能を有する、導電膜 103a 及び導電膜 103b と、を有する。

【0107】

図 5 (B) 及び図 5 (C) では、トランジスタ 200 上に絶縁膜 106 が設けられている構成を例示している。トランジスタ 200 は、絶縁膜 106 をその構成要素に含んでいても良い。

【0108】

また、図 5 では、基板 101 上に接するように導電膜 105 が設けられている場合を例示しているが、基板 101 と導電膜 105 の間に絶縁膜が設けられていても良い。

【0109】

そして、図 5 に示すトランジスタ 200 も、図 1 に示すトランジスタ 100 と同様に、ゲート絶縁膜 104 が、順に積層された保護膜 104a と、金属酸化物を含む絶縁膜 104b と、保護膜 104c とを少なくとも有する。そして、図 5 に示すトランジスタ 200 の場合、絶縁膜 104b と導電膜 105 の間に保護膜 104a が存在しており、絶縁膜 104b は導電膜 105 に接していない。また、トランジスタ 200 では、絶縁膜 104b と導電膜 103a 及び導電膜 103b の間に保護膜 104c が存在しており、絶縁膜 104b は導電膜 103a 及び導電膜 103b に接していない。

【0110】

本発明の一態様では、ゲート絶縁膜 104 が、順に積層された保護膜 104a と、絶縁膜 104b と、保護膜 104c とを少なくとも有することで、酸化珪素膜など、インジウムの混入により絶縁耐圧が低下する絶縁膜だけでゲート絶縁膜が構成されているトランジスタに比べて、絶縁耐圧の高いトランジスタ 200 を得ることができる。

【0111】

また、酸化ガリウム、酸化ジルコニウム、及び酸化ハフニウムは、酸化珪素よりも比誘電率が高いため、トランジスタ 200 の微細化に伴い、ゲート絶縁膜を介してゲート電極と半導体膜の間に流れる電流（リーク電流）が増加するのを抑えることができる。特に、酸化ジルコニウム及び酸化ハフニウムは酸化珪素に比べて比誘電率が著しく高いため、酸化珪素膜だけでゲート絶縁膜が構成されているトランジスタに比べて、微細化に伴うリーク電流の増加を抑制する効果が高い。

【0112】

(実施の形態 2)

本実施の形態では、本発明の半導体装置の一つに相当する半導体表示装置の、構成例について説明する。

【0113】

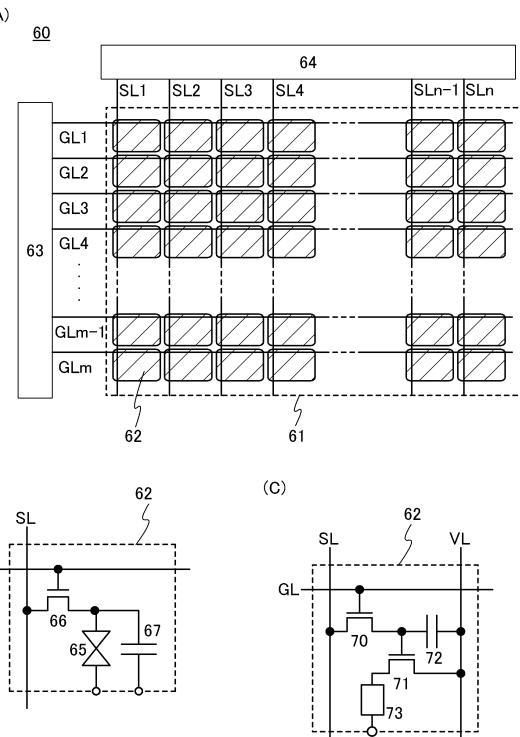

図 6 (A) に示すパネル 60 には、画素部 61 に、複数の画素 62 と、画素 62 を行毎に選択するための、走査線 GL1 乃至走査線 GLm (m は自然数) で示される走査線 GL と、選択された画素 62 に画像信号を供給するための、信号線 SL1 乃至信号線 SLn (n は自然数) で示される信号線 SL とが、設けられている。走査線 GL への信号の入力は、走査線駆動回路 63 により制御されている。信号線 SL への画像信号の入力は、信号線駆動回路 64 により制御されている。複数の画素 62 は、走査線 GL の少なくとも一つと、信号線 SL の少なくとも一つとに、それぞれ接続されている。

【0114】

なお、画素部 61 に設けられる配線の種類及びその数は、画素 62 の構成、数及び配置によって決めることができる。具体的に、図 6 (A) に示す画素部 61 の場合、n 列 × m 行の画素 62 がマトリクス状に配置されており、信号線 SL1 乃至信号線 SLn、走査線 GL1 乃至走査線 GLm が、画素部 61 内に配置されている場合を例示している。

【0115】

また、図 6 (B) に、画素 62 の構成を一例として示す。各画素 62 は、液晶素子 65 と、当該液晶素子 65 への画像信号の供給を制御するトランジスタ 66 と、液晶素子 65 の画素電極と共に通電極間の電圧を保持するための容量素子 67 とを有する。液晶素子 65 は、画素電極と、共通電極と、画素電極と共に通電極の間の電圧が印加される液晶材料を含ん

10

20

30

40

50

だ液晶層と、を有している。

【0116】

トランジスタ66は、液晶素子65の画素電極に、信号線SLの電位を与えるか否かを制御する。液晶素子65の共通電極には、所定の電位が与えられている。

【0117】

以下、トランジスタ66と液晶素子65の具体的な接続関係について説明する。図6(B)では、トランジスタ66のゲート電極が、走査線GL1から走査線GLmのいずれか1つに接続されている。トランジスタ66のソース電極及びドレイン電極の一方は、信号線SL1から信号線SLnのいずれか1つに接続され、トランジスタ66のソース電極及びドレイン電極の他方は、液晶素子65の画素電極に接続されている。

10

【0118】

なお、本明細書において接続とは電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、抵抗、ダイオード、トランジスタなどの素子を介して電気的に接続している状態も、その範疇に含む。

【0119】

図6(B)では、画素62において、画像信号の画素62への入力を制御するスイッチとして、一のトランジスタ66を用いる場合を例示している。しかし、一のスイッチとして機能する、複数のトランジスタを、画素62に用いていても良い。

20

【0120】

本発明の一態様では、トランジスタ66として、実施の形態1で示したようなトランジスタ100を用いることで、半導体表示装置の信頼性を高めることができる。また、トランジスタ100はオフ電流が著しく小さいため、トランジスタ100をトランジスタ66として用いると、トランジスタ66を介して電荷がリークするのを防ぐことができる。よって、液晶素子65及び容量素子67に与えられた画像信号の電位をより確実に保持することができるので、1フレーム期間内において電荷のリークにより液晶素子65の透過率が変化するのを防ぎ、それにより、表示する画像の質を向上させることができる。また、トランジスタ66のオフ電流が小さい場合、トランジスタ66を介して電荷がリークするのを防ぐことができるため、容量素子67の面積を小さく抑えることができる。よって、パネル60の透過率を高め、それにより、バックライトやフロントライトなどの光供給部から供給される光の、パネル60の内部における損失を低減し、液晶表示装置の消費電力を低減させることができる。或いは、静止画を表示する期間において、走査線駆動回路63及び信号線駆動回路64への電源電位または信号の供給を停止しても良い。上記構成により、画素部61への画像信号の書き込み回数を少なくし、半導体表示装置の消費電力を低減させることができる。

30

【0121】

次いで、図6(C)に、画素62の別の一例を示す。画素62は、画素62への画像信号の入力を制御するトランジスタ70と、発光素子73と、画像信号に従って発光素子73に供給する電流値を制御するトランジスタ71と、画像信号の電位を保持するための容量素子72と、を有する。

40

【0122】

発光素子73のアノードとカソードのいずれか一方は、画素62に入力される画像信号に従ってその電位が制御される。発光素子73のアノードとカソードのいずれか他方には、所定の電位が与えられる。そして、発光素子73の輝度は、アノードとカソード間の電位差によって定まる。画素部が有する複数の画素62のそれぞれにおいて、発光素子73の輝度が画像情報を有する画像信号に従って調整されることで、画素部61に画像が表示される。

【0123】

次いで、画素62が有する、トランジスタ70、トランジスタ71、容量素子72、発光

50

素子 73 の接続構成について説明する。

【0124】

トランジスタ 70 は、ソース電極またはドレイン電極の一方が信号線 S L に接続され、ソース電極またはドレイン電極の他方がトランジスタ 71 のゲート電極に接続されている。トランジスタ 70 のゲート電極は、走査線 G L に接続されている。トランジスタ 71 は、ソース電極またはドレイン電極の一方が電源線 V L に接続され、ソース電極またはドレイン電極の他方が発光素子 73 に接続されている。具体的に、トランジスタ 71 のソース電極またはドレイン電極の他方は、発光素子 73 のアノードとカソードのいずれか一方に接続されている。発光素子 73 のアノードとカソードのいずれか他方には、所定の電位が与えられる。

10

【0125】

なお、図 6 (C) では、画素 62 が容量素子 72 を有する場合を例示しているが、例えばトランジスタ 70 のゲート電極と半導体膜の間に形成されるゲート容量や、ゲート電極の寄生容量が十分大きい場合など、他の容量により画像信号の電位を十分保持できる場合には、必ずしも容量素子 72 を画素 62 に設ける必要はない。

【0126】

発光素子 73 は、LED (Light Emitting Diode) や OLEd (Organic Light Emitting Diode) などの、電流または電圧によって輝度が制御される素子をその範疇に含んでいる。例えば、OLEd は、EL 層と、アノードと、カソードとを少なくとも有している。EL 層はアノードとカソードの間に設けられた単層または複数の層で構成されており、これらの層の中に、発光性の物質を含む発光層を少なくとも含んでいる。

20

【0127】

なお、EL 層は、カソードとアノード間の電位差が、発光素子 73 の閾値電圧以上になつたときに供給される電流により、エレクトロルミネッセンスが得られる。エレクトロルミネッセンスには、一重項励起状態から基底状態に戻る際の発光 (蛍光) と三重項励起状態から基底状態に戻る際の発光 (リン光) とが含まれる。

【0128】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0129】

30

(実施の形態 3)

インジウムの酸化窒化珪素膜への拡散について

実際に、シリコン基板上に、膜厚 300 nm の酸化珪素膜、インジウムを含む膜厚 100 nm の酸化物半導体膜、膜厚 100 nm の酸化窒化珪素膜の順に形成し、酸化窒化珪素膜、及びインジウムを含む酸化物半導体膜について、SIMS (Secondary Ion Mass Spectrometry) 分析を行った。なお、インジウムを含む酸化物半導体膜は、原子数比が In : Ga : Zn = 1 : 1 : 1 のターゲットを用いて、基板温度を 200 とし、スペッタリング法により形成した。また、酸化窒化珪素膜は、基板温度を 400 とし、流量を SiH<sub>4</sub> = 1 sccm、N<sub>2</sub>O = 800 sccm として、プラズマ CVD 法で形成した。

40

【0130】

インジウムについての SIMS 分析の結果を、図 10 に示す。図 10 において、SiON で示される矢印は、酸化窒化珪素膜が存在する深さ方向の範囲を意味し、IGZO で示される矢印は、インジウムを含む酸化物半導体膜が存在する深さ方向の範囲を意味する。

【0131】

図 10 に示すように、インジウムを含む酸化物半導体膜と酸化窒化珪素膜との界面から約 40 nm 程度、 $1.0 \times 10^{15} \text{ atoms/cm}^3$  乃至  $1.0 \times 10^{18} \text{ atoms/cm}^3$  の濃度範囲でインジウムが酸化窒化珪素膜中に拡散している。図 10 から、酸化物半導体膜中に含まれていたインジウムが、酸化窒化珪素膜中に拡散する現象が確認された。よって、インジウムを含む酸化物半導体膜を設け、ゲート絶縁膜として当該酸化物半導

50

体膜上に珪素を含む絶縁膜を設けてトランジスタを作製した場合、同様にゲート絶縁膜中にインジウムが拡散されることが示唆された。

### 【0132】

#### (実施の形態4)

##### 液晶表示装置の構成

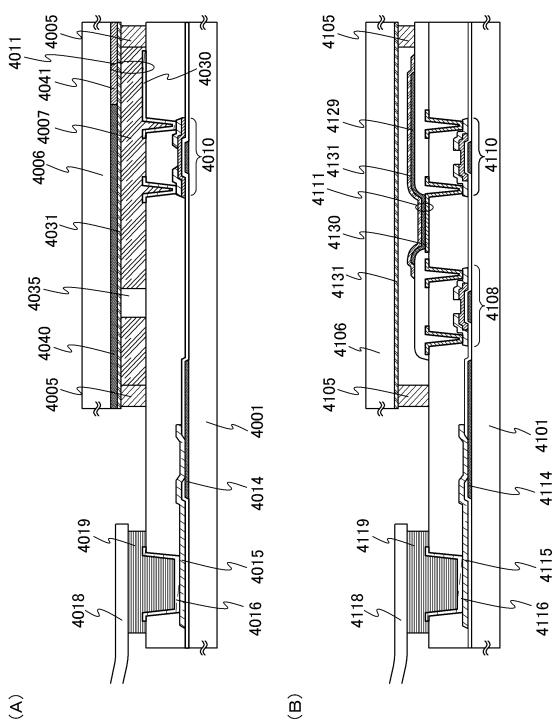

次いで、本発明の一態様に係る半導体装置の一つに相当する、液晶表示装置の構成について、図7(A)を用いて説明する。図7(A)は、基板4001と基板4006とをシール材4005によって接着させた液晶表示装置の断面図に相当する。

### 【0133】

図7(A)では、基板4001と基板4006の間ににおいて、シール材4005によって囲まれた領域に、液晶層4007が封止されている。また、図7(A)では、画素に含まれるトランジスタ4010を図示している。液晶素子4011が有する画素電極4030は、トランジスタ4010に接続されている。そして、液晶素子4011の共通電極4031は、基板4006に形成されている。画素電極4030と共に電極4031と液晶層4007とが重なっている部分が、液晶素子4011に相当する。

### 【0134】

なお、図7(A)では、共通電極4031が基板4006に設けられている場合を例示しているが、本発明の一態様に係る液晶表示装置では、共通電極4031が基板4001に設けられても良い。

### 【0135】

また、基板4006に形成されている遮蔽膜4040は、トランジスタ4010が形成されている領域と重なっている。また、基板4006には、カラーフィルタとして機能する、特定の波長領域の可視光のみを優先的に透過する着色層4041が形成されており、着色層4041は、液晶素子4011が形成されている領域と重なっている。

### 【0136】

赤、青、緑に対応する波長領域の光を、それぞれ優先的に透過するような着色層4041を画素ごとに設けることで、フルカラーの画像を表示することができる。この場合、白の光が得られるバックライトを用いることが、画像の有する色の純度を高める上で望ましい。白の光が得られるバックライトとして、例えば、赤の光源と青の光源と緑の光源を組み合わせた構成、黄または橙の光源と青の光源を組み合わせた構成、白の光源を単体で用いる構成、シアンの光源とマゼンタの光源と黄の光源を組み合わせた構成などを、用いることができる。

### 【0137】

あるいは、バックライトから、赤、青、緑に対応する波長領域の光を順に出力するようにしても良い。この場合、カラーフィルタを用いなくともフルカラーの画像を表示することができ、液晶表示装置の発光効率を高めることができる。

### 【0138】

また、バックライトに用いる光源として、冷陰極管の他、LED、OLEDなどの発光素子を用いることができる。ただし、光源によって得られる光の波長が異なるので、必要とする色に合わせて適宜用いる光源を選択すると良い。

### 【0139】

なお、図7(A)では、遮蔽膜4040と着色層4041とを、基板4006側に設けた場合を例示しているが、遮蔽膜4040または着色層4041を、基板4001側に設けても良い。液晶素子4011への光の入射方向と、液晶素子4011を透過した光の射出方向とに合わせて、適宜、遮蔽膜4040と着色層4041の設ける位置を定めることができる。

### 【0140】

また、スペーサ4035が、画素電極4030と共に電極4031との間の距離(セルギヤップ)を制御するために設けられている。なお、図7(A)では、スペーサ4035が、絶縁膜をパターニングすることで形成されている場合を例示しているが、球状スペーサ

10

20

30

40

50

を用いていても良い。

#### 【0141】

また、画素に与えられる各種信号及び電位は、配線4014及び配線4015を介して、端子4016から供給されている。端子4016は、FPC4018が有する端子と異方性導電膜4019を介して電気的に接続されている。

#### 【0142】

##### 発光装置の構成

次いで、本発明の一態様に係る半導体装置の一つに相当する発光装置の構成について、図7(B)を用いて説明する。図7(B)は、基板4101と基板4106とをシール材4105によって接着させた発光装置の断面図に相当する。

10

#### 【0143】

図7(B)では、基板4101と基板4106の間ににおいて、シール材4105で囲まれた領域に、充填材と共に発光素子4111が封止されている。充填材としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができる。シール材4105には、樹脂(紫外線硬化性樹脂、熱硬化性樹脂など)、またはガラスフリットなどを用いることができる。

#### 【0144】

また、図7(B)では、画素に含まれるトランジスタ4108及びトランジスタ4110を図示している。発光素子4111が有する画素電極4130は、トランジスタ4110に接続されている。画素電極4130と共に通電極4131とEL層4129とが重なっている部分が、発光素子4111に相当する。

20

#### 【0145】

本発明の一態様に係る発光装置では、白色などの単色の光を発する発光素子と、着色層を有するカラーフィルタとを組み合わせることで、フルカラー画像の表示を行う、カラーフィルタ方式を採用することができる。或いは、互いに異なる色相の光を発する複数の発光素子を用いて、フルカラー画像の表示を行う方式を採用することもできる。この方式は、発光素子が有する一対の電極間に設けられるEL層を、対応する色ごとに塗り分けるため、塗り分け方式と呼ばれる。

#### 【0146】

塗り分け方式の場合、EL層の塗り分けは、通常、メタルマスクなどのマスクを用いて、蒸着法で行われる。そのため、画素のサイズは蒸着法によるEL層の塗り分け精度に依存する。一方、カラーフィルタ方式の場合、塗り分け方式とは異なり、EL層の塗り分けを行う必要がない。よって、塗り分け方式の場合よりも、画素サイズの縮小化が容易であり、高精細の画素部を実現することができる。

30

#### 【0147】

また、トップエミッション構造の場合、発光素子から発せられる光を、配線、トランジスタ、容量素子などの各種素子によって遮られることがないため、ボトムエミッション構造に比べて、画素からの光の取り出し効率を高めることができる。よって、トップエミッション構造は、発光素子に供給する電流値を低く抑えても、高い輝度を得ることができるために、発光素子の長寿命化に有利である。

40

#### 【0148】

また、本発明の一態様に係る発光装置では、EL層から発せられる光を発光素子内で共振させる、マイクロキャビティ(微小光共振器)構造を有していても良い。マイクロキャビティ構造により、特定の波長の光について、発光素子からの取り出し効率を高めることができるので、画素部の輝度と色純度を向上させることができる。

#### 【0149】

また、画素に与えられる各種信号及び電位は、配線4114及び配線4115を介して、端子4116から供給されている。端子4116は、FPC4118が有する端子及び異方性導電膜4119を介して電気的に接続されている。

#### 【0150】

50

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0151】

(実施の形態5)

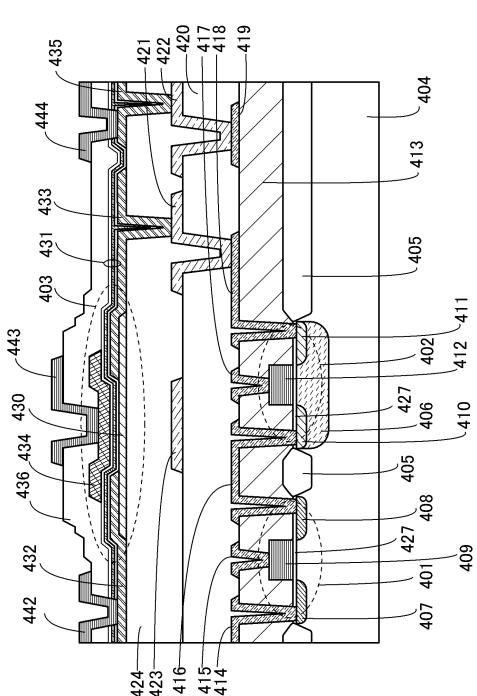

図8に、本発明の一態様に係る半導体装置の断面構造の一部を、一例として示す。

【0152】

本実施の形態では、pチャネル型のトランジスタ401及びnチャネル型のトランジスタ402が、単結晶のシリコン基板に形成され、酸化物半導体膜を用いたトランジスタ403がトランジスタ401及びトランジスタ402上に形成されている場合を例示している。トランジスタ401及びトランジスタ402は、非晶質、微結晶、多結晶または単結晶である、シリコン又はゲルマニウムなどの薄膜の半導体膜を用いていても良い。或いは、トランジスタ401及びトランジスタ402は、酸化物半導体膜を用いていても良い。全てのトランジスタが酸化物半導体膜を用いている場合、トランジスタ403はトランジスタ401及びトランジスタ402上に積層されていなくとも良く、同一の絶縁表面上に全てのトランジスタが形成されていても良い。10

【0153】

なお、薄膜のシリコンを用いてトランジスタ401及びトランジスタ402を形成する場合、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、単結晶シリコンウェハに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。20

【0154】

図8では、半導体基板404にトランジスタ401及びトランジスタ402が形成されている。

【0155】

半導体基板404は、例えば、n型またはp型の導電型を有する単結晶シリコン基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、ZnSe基板等)等を用いることができる。図8では、n型の導電型を有する単結晶シリコン基板を用いた場合を例示している。

【0156】

また、トランジスタ401とトランジスタ402とは、素子分離用絶縁膜405により、電気的に分離されている。素子分離用絶縁膜405の形成には、選択酸化法(LOCOS(Local Oxidation of Silicon)法)またはトレンチ分離法等を用いることができる。30

【0157】

トランジスタ402が形成される領域には、p型の導電性を付与する不純物元素を選択的に導入することにより、pウェル406を形成する。

【0158】

具体的に、トランジスタ401は、半導体基板404と、半導体基板404に形成されたソース領域またはドレイン領域として機能する不純物領域407及び不純物領域408と、ゲート電極409と、半導体基板404とゲート電極409の間に設けられたゲート絶縁膜427とを有する。ゲート電極409は、ゲート絶縁膜427を間に挟んで、不純物領域407と不純物領域408の間に形成されるチャネル形成領域と重なる。40

【0159】

また、トランジスタ402は、半導体基板404と、半導体基板404に形成されたソース領域またはドレイン領域として機能する不純物領域410及び不純物領域411と、ゲート電極412と、半導体基板404とゲート電極412の間に設けられたゲート絶縁膜427とを有する。ゲート電極412は、ゲート絶縁膜427を間に挟んで、不純物領域410と不純物領域411の間に形成されるチャネル形成領域と重なる。

【0160】

トランジスタ401及びトランジスタ402上には、絶縁膜413が設けられている。絶50

縁膜 413 には開口部が形成されており、上記開口部において、不純物領域 407 と、ゲート電極 409 と、不純物領域 408 及び不純物領域 410 と、ゲート電極 412 と、不純物領域 411 とにそれぞれ接する配線 414 乃至配線 418 が、絶縁膜 413 上に形成されている。さらに、絶縁膜 413 上には、配線 419 が形成されている。

**【0161】**

配線 414 乃至配線 419 上には、絶縁膜 420 が形成されている。絶縁膜 420 には開口部が形成されており、上記開口部において配線 418 に接続された配線 421 が、配線 419 に接続された配線 422 が、絶縁膜 420 上に形成されている。さらに、絶縁膜 420 上には、配線 423 が形成されている。

**【0162】**

配線 421 乃至配線 423 上には、絶縁膜 424 が形成されている。

10

**【0163】**

そして、図 8 では、絶縁膜 424 上にトランジスタ 403 が形成されている。

**【0164】**

トランジスタ 403 は、絶縁膜 424 上に、酸化物半導体を含む半導体膜 430 と、半導体膜 430 上の、ソース電極またはドレイン電極として機能する導電膜 432 及び導電膜 433 と、半導体膜 430 、導電膜 432 及び導電膜 433 上のゲート絶縁膜 431 と、導電膜 432 と導電膜 433 の間において、ゲート絶縁膜 431 を間に挟んで半導体膜 430 と重なっているゲート電極 434 と、を有する。

20

**【0165】**

ゲート絶縁膜 431 は、図 1 に示したトランジスタ 100 と同様に、順に積層された保護膜と、金属酸化物を含む絶縁膜と、保護膜とを少なくとも有する。

**【0166】**

そして、絶縁膜 424 には開口部が設けられており、上記開口部において導電膜 433 は、配線 421 に接している。また、絶縁膜 424 上には配線 435 が設けられており、上記開口部において配線 435 は配線 422 と接続されている。

**【0167】**

そして、トランジスタ 403 、及び配線 435 上に、絶縁膜 436 が設けられている。絶縁膜 436 及びゲート絶縁膜 431 には開口部が設けられており、上記開口部において導電膜 432 に接する配線 442 と、上記開口部においてゲート電極 434 に接する配線 443 と、上記開口部において配線 435 に接する配線 444 とが、絶縁膜 436 上に設けられている。

30

**【0168】**

なお、図 8 において、トランジスタ 403 は、配線 423 をゲート電極として機能させることもできる。

**【0169】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

**【0170】**

(実施の形態 6 )

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的には D V D : D i g i t a l V e r s a t i l e D i s c 等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ A T M ）、自動販売機などが挙げられる。これら電子機器の具体例を図 9 に示す。

40

**【0171】**

図 9 ( A ) は携帯型ゲーム機であり、筐体 5001 、筐体 5002 、表示部 5003 、表

50

示部 5004、マイクロホン 5005、スピーカー 5006、操作キー 5007、スタイルス 5008 等を有する。表示部 5003 または表示部 5004 に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることができる。なお、図 9 (A) に示した携帯型ゲーム機は、2つの表示部 5003 と表示部 5004 とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

#### 【0172】

図 9 (B) は表示機器であり、筐体 5201、表示部 5202、支持台 5203 等を有する。表示部 5202 に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることができる。なお、表示機器には、パーソナルコンピュータ用、TV 放送受信用、広告表示用などの全ての情報表示用表示機器が含まれる。

10

#### 【0173】

図 9 (C) はノート型パーソナルコンピュータであり、筐体 5401、表示部 5402、キーボード 5403、ポインティングデバイス 5404 等を有する。表示部 5402 に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることができる。

#### 【0174】

図 9 (D) は携帯情報端末であり、第 1 筐体 5601、第 2 筐体 5602、第 1 表示部 5603、第 2 表示部 5604、接続部 5605、操作キー 5606 等を有する。第 1 表示部 5603 は第 1 筐体 5601 に設けられており、第 2 表示部 5604 は第 2 筐体 5602 に設けられている。そして、第 1 筐体 5601 と第 2 筐体 5602 とは、接続部 5605 により接続されており、第 1 筐体 5601 と第 2 筐体 5602 の間の角度は、接続部 5605 により変更が可能となっている。第 1 表示部 5603 における映像を、接続部 5605 における第 1 筐体 5601 と第 2 筐体 5602 の間の角度に従って、切り替える構成としても良い。第 1 表示部 5603 または第 2 表示部 5604 に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることができる。なお、第 1 表示部 5603 及び第 2 表示部 5604 の少なくとも一方に、位置入力装置としての機能が付加された半導体装置を用いるようにしても良い。なお、位置入力装置としての機能は、半導体装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を半導体装置の画素部に設けることでも、付加することができる。

20

#### 【0175】

図 9 (E) はビデオカメラであり、第 1 筐体 5801、第 2 筐体 5802、表示部 5803、操作キー 5804、レンズ 5805、接続部 5806 等を有する。操作キー 5804 及びレンズ 5805 は第 1 筐体 5801 に設けられており、表示部 5803 は第 2 筐体 5802 に設けられている。そして、第 1 筐体 5801 と第 2 筐体 5802 とは、接続部 5806 により接続されており、第 1 筐体 5801 と第 2 筐体 5802 の間の角度は、接続部 5806 により変更が可能となっている。表示部 5803 における映像の切り替えを、接続部 5806 における第 1 筐体 5801 と第 2 筐体 5802 の間の角度に従って行う構成としても良い。表示部 5803 に、或いはその他の回路に、本発明の一態様に係る半導体装置を用いることできる。

30

#### 【0176】

図 9 (F) は携帯電話であり、筐体 5901 に、表示部 5902、マイク 5907、スピーカー 5904、カメラ 5903、外部接続部 5906、操作用のボタン 5905 が設けられている。携帯電話が有する回路に、本発明の一態様に係る半導体装置を用いることができる。また、本発明の一態様に係る半導体装置の 1 つである半導体液晶表示装置を、可撓性を有する基板に形成した場合、図 9 (F) に示すような曲面を有する表示部 5902 に当該半導体液晶表示装置を適用することが可能である。

40

#### 【0177】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【符号の説明】

#### 【0178】

50

|         |          |    |

|---------|----------|----|

| 6 0     | パネル      |    |

| 6 1     | 画素部      |    |

| 6 2     | 画素       |    |

| 6 3     | 走査線駆動回路  |    |

| 6 4     | 信号線駆動回路  |    |

| 6 5     | 液晶素子     |    |

| 6 6     | トランジスタ   |    |

| 6 7     | 容量素子     |    |

| 7 0     | トランジスタ   | 10 |

| 7 1     | トランジスタ   |    |

| 7 2     | 容量素子     |    |

| 7 3     | 発光素子     |    |

| 1 0 0   | トランジスタ   |    |

| 1 0 1   | 基板       |    |

| 1 0 2   | 半導体膜     |    |

| 1 0 2 a | 酸化物半導体膜  |    |

| 1 0 2 b | 酸化物半導体膜  |    |

| 1 0 2 c | 酸化物半導体膜  |    |

| 1 0 3 a | 導電膜      |    |

| 1 0 3 b | 導電膜      | 20 |

| 1 0 4   | ゲート絶縁膜   |    |

| 1 0 4 a | 保護膜      |    |

| 1 0 4 b | 絶縁膜      |    |

| 1 0 4 c | 保護膜      |    |

| 1 0 5   | 導電膜      |    |

| 1 0 6   | 絶縁膜      |    |

| 1 2 0   | 絶縁膜      |    |

| 1 2 0 a | 保護膜      |    |

| 1 2 0 b | 絶縁膜      |    |

| 1 2 0 c | 保護膜      | 30 |

| 1 2 1   | 導電膜      |    |

| 2 0 0   | トランジスタ   |    |

| 4 0 1   | トランジスタ   |    |

| 4 0 2   | トランジスタ   |    |

| 4 0 3   | トランジスタ   |    |

| 4 0 4   | 半導体基板    |    |

| 4 0 5   | 素子分離用絶縁膜 |    |

| 4 0 6   | p ウェル    |    |

| 4 0 7   | 不純物領域    |    |

| 4 0 8   | 不純物領域    | 40 |

| 4 0 9   | ゲート電極    |    |

| 4 1 0   | 不純物領域    |    |

| 4 1 1   | 不純物領域    |    |

| 4 1 2   | ゲート電極    |    |

| 4 1 3   | 絶縁膜      |    |

| 4 1 4   | 配線       |    |

| 4 1 8   | 配線       |    |

| 4 1 9   | 配線       |    |

| 4 2 0   | 絶縁膜      |    |

| 4 2 1   | 配線       | 50 |

|         |        |    |

|---------|--------|----|

| 4 2 2   | 配線     |    |

| 4 2 3   | 配線     |    |

| 4 2 4   | 絶縁膜    |    |

| 4 2 7   | ゲート絶縁膜 |    |

| 4 3 0   | 半導体膜   |    |

| 4 3 1   | ゲート絶縁膜 |    |

| 4 3 2   | 導電膜    |    |

| 4 3 3   | 導電膜    |    |

| 4 3 4   | ゲート電極  |    |

| 4 3 5   | 配線     | 10 |

| 4 3 6   | 絶縁膜    |    |

| 4 4 2   | 配線     |    |

| 4 4 3   | 配線     |    |

| 4 4 4   | 配線     |    |

| 4 0 0 1 | 基板     |    |

| 4 0 0 5 | シール材   |    |

| 4 0 0 6 | 基板     |    |

| 4 0 0 7 | 液晶層    |    |

| 4 0 1 0 | トランジスタ |    |

| 4 0 1 1 | 液晶素子   | 20 |

| 4 0 1 4 | 配線     |    |

| 4 0 1 5 | 配線     |    |

| 4 0 1 6 | 端子     |    |

| 4 0 1 8 | F P C  |    |

| 4 0 1 9 | 異方性導電膜 |    |

| 4 0 3 0 | 画素電極   |    |

| 4 0 3 1 | 共通電極   |    |

| 4 0 3 5 | スペーサ   |    |

| 4 0 4 0 | 遮蔽膜    |    |

| 4 0 4 1 | 着色層    | 30 |

| 4 1 0 1 | 基板     |    |

| 4 1 0 5 | シール材   |    |

| 4 1 0 6 | 基板     |    |

| 4 1 0 8 | トランジスタ |    |

| 4 1 1 0 | トランジスタ |    |

| 4 1 1 1 | 発光素子   |    |

| 4 1 1 4 | 配線     |    |

| 4 1 1 5 | 配線     |    |

| 4 1 1 6 | 端子     |    |

| 4 1 1 8 | F P C  | 40 |

| 4 1 1 9 | 異方性導電膜 |    |

| 4 1 2 9 | E L 層  |    |

| 4 1 3 0 | 画素電極   |    |

| 4 1 3 1 | 共通電極   |    |

| 5 0 0 1 | 筐体     |    |

| 5 0 0 2 | 筐体     |    |

| 5 0 0 3 | 表示部    |    |

| 5 0 0 4 | 表示部    |    |

| 5 0 0 5 | マイクロホン |    |

| 5 0 0 6 | スピーカー  | 50 |

|         |             |

|---------|-------------|

| 5 0 0 7 | 操作キー        |

| 5 0 0 8 | スタイルス       |

| 5 2 0 1 | 筐体          |

| 5 2 0 2 | 表示部         |

| 5 2 0 3 | 支持台         |

| 5 4 0 1 | 筐体          |

| 5 4 0 2 | 表示部         |

| 5 4 0 3 | キーボード       |

| 5 4 0 4 | ポインティングデバイス |

| 5 6 0 1 | 筐体          |

| 5 6 0 2 | 筐体          |

| 5 6 0 3 | 表示部         |

| 5 6 0 4 | 表示部         |

| 5 6 0 5 | 接続部         |

| 5 6 0 6 | 操作キー        |

| 5 8 0 1 | 筐体          |

| 5 8 0 2 | 筐体          |

| 5 8 0 3 | 表示部         |

| 5 8 0 4 | 操作キー        |

| 5 8 0 5 | レンズ         |

| 5 8 0 6 | 接続部         |

| 5 9 0 1 | 筐体          |

| 5 9 0 2 | 表示部         |

| 5 9 0 3 | カメラ         |

| 5 9 0 4 | スピーカー       |

| 5 9 0 5 | ボタン         |

| 5 9 0 6 | 外部接続部       |

| 5 9 0 7 | マイク         |

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【図7】

【 义 8 】

【図9】

【図10】

---

フロントページの続き

(56)参考文献 特開2007-073698(JP,A)

特開2011-181906(JP,A)

特開2012-216834(JP,A)

特開2010-283338(JP,A)

特開2010-056540(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786