(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4425897号

(P4425897)

(45) 発行日 平成22年3月3日(2010.3.3)

(24) 登録日 平成21年12月18日(2009.12.18)

(51) Int.Cl.

H03K 19/177 (2006.01)

F 1

H03K 19/177

請求項の数 20 (全 32 頁)

(21) 出願番号 特願2006-307333 (P2006-307333)

(22) 出願日 平成18年11月14日 (2006.11.14)

(65) 公開番号 特開2007-143151 (P2007-143151A)

(43) 公開日 平成19年6月7日 (2007.6.7)

審査請求日 平成21年10月30日 (2009.10.30)

(31) 優先権主張番号 60/737,868

(32) 優先日 平成17年11月17日 (2005.11.17)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 11/335,437

(32) 優先日 平成18年1月18日 (2006.1.18)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 597154922

アルテラ コーポレイション

Altera Corporation

アメリカ合衆国 95134 カリフォルニア州 サンホセ イノベーション ドライヴ 101

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】高電源レベルを有するプログラマブルロジックデバイスマモリ要素

## (57) 【特許請求の範囲】

## 【請求項 1】

コアロジック電源電圧において電力供給されたプログラマブルコアロジックと、該プログラマブルコアロジックを構成する出力を有するメモリ要素のアレイと、該アレイ内の該メモリ要素をアドレスするための複数のアドレスラインと、該メモリ要素にプログラマブルロジックデバイスコンフィギュレーションデータをロードするために、該コアロジック電源電圧より大きい電圧レベルを有するアドレス信号を該アドレスラインに印加するデータローディング・読み取り回路網とを備える、プログラマブルロジックデバイス集積回路。

## 【請求項 2】

前記メモリ要素に電力供給する時間変化メモリ要素電源電圧を提供する電力調節器回路網をさらに備え、前記データローディング・読み取り回路網が前記プログラマブルロジックデバイスコンフィギュレーションデータをロードするために前記アドレス信号を前記アドレスラインに印加した場合、該時間変化メモリ要素電源電圧は前記コアロジック電源電圧と等しく、該時間変化メモリ要素電源電圧は、通常動作の間、該コアロジック電源電圧より大きい、請求項 1 に記載のプログラマブルロジックデバイス集積回路。

## 【請求項 3】

前記メモリ要素の通常動作の間、前記コアロジックの正の電源電圧より大きいメモリ要素電源電圧において該メモリ要素に電力供給する電力調節器回路網をさらに備える、請求項 1 に記載のプログラマブルロジックデバイス集積回路。

## 【請求項 4】

前記メモリ要素の各々は相互結合インバータを含み、前記データローディング・読み取り回路網は該メモリ要素からプログラマブルロジックデバイスコンフィギュレーションデータを読み取るためにアドレス信号を前記アドレスラインに印加し、該プログラマブルロジックデバイスコンフィギュレーションデータを読み取るために使用される該アドレス信号は、該プログラマブルロジックデバイスコンフィギュレーションデータを該メモリ要素にロードするときに使用される該アドレス信号の電圧レベルより少ない電圧レベルを有する、請求項1に記載のプログラマブルロジックデバイス集積回路。

## 【請求項 5】

複数のアドレストランジスタをさらに備え、該アドレストランジスタの各々は、前記メモリ要素のアレイ内のそれぞれのメモリ要素に関連してかつゲートを有し、該ゲートは前記アドレスラインによって制御され、該ゲートは、前記プログラマブルロジックデバイスコンフィギュレーションデータが該メモリ要素にロードされるデータ書き取り動作の間に第1の電圧レベルにおいてアドレス信号を受信し、該プログラマブルロジックデバイスコンフィギュレーションデータが前記データローディング・読み取り回路網によって該メモリ要素から読み取られるデータ読み取り動作の間に第2の電圧レベルにおいてアドレス信号を受信し、該第1の電圧レベルは、前記コアロジック電源電圧より大きく、該第2の電圧レベルは、該コアロジック電源電圧と等しい、請求項1に記載のプログラマブルロジックデバイス集積回路。

## 【請求項 6】

複数のアドレストランジスタであって、該アドレストランジスタの各々は、前記メモリ要素のアレイ内のそれぞれのメモリ要素に関連してかつゲートを有し、該ゲートは前記アドレスラインによって制御され、該ゲートは、前記プログラマブルロジックデバイスコンフィギュレーションデータが該メモリ要素にロードされるデータ書き取り動作の間に第1の電圧レベルにおいてアドレス信号を受信し、該プログラマブルロジックデバイスコンフィギュレーションデータが前記データローディング・読み取り回路網によって該メモリ要素から読み取られるデータ読み取り動作の間に第2の電圧レベルにおいてアドレス信号を受信し、該第1の電圧レベルは、前記コアロジック電源電圧より大きく、該第2の電圧レベルは、該コアロジック電源電圧と等しい、複数のアドレストランジスタと、

該メモリ要素の通常動作の間、該第1の電圧レベルと等しい電源電圧において該メモリ要素に電力供給する電力調節器回路網と

をさらに備える、請求項1に記載のプログラマブルロジックデバイス集積回路。

## 【請求項 7】

データローディング動作の間にコンフィギュレーションデータが書き込まれ、コンフィギュレーションデータが読み取り動作の間に読み取られるプログラマブルロジックデバイスメモリ要素を有するプログラマブルロジックデバイス集積回路であって、該プログラマブルロジックデバイス集積回路は、

プログラマブルコアロジック電源電圧において電力供給されたプログラマブルコアロジックと、

該プログラマブルコアロジックを構成する通常動作の間、制御信号を該プログラマブルコアロジックに供給する該メモリ要素のアレイと、

読み取り動作の間とは異なる電圧レベルにおいてデータローディング動作の間に該メモリ要素をアドレスするアドレス信号を生成するデータローディング・読み取り回路網とを備える、プログラマブルロジックデバイス集積回路。

## 【請求項 8】

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、メモリ要素電源電圧において前記メモリ要素に電力供給する電力調節器回路網をさらに含む、請求項7に記載のプログラマブルロジックデバイス集積回路。

10

20

30

40

50

## 【請求項 9】

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、データローディング動作の間の該アドレス信号の該電圧レベルと等しいメモリ要素電源電圧において前記メモリ要素に電力供給する電力調節器回路網をさらに含む、請求項 7 に記載のプログラマブルロジックデバイス集積回路。

## 【請求項 10】

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、第 1 および第 2 の電圧レベルを有する時間変化メモリ要素電源電圧を生成するダイナミックな電力調節器回路網をさらに含み、該第 1 の電圧レベルは、データローディング動作の間に生成され、該第 2 の電圧レベルは、通常動作の間に生成され、該第 1 の電圧は、該プログラマブルコアロジック電源電圧と等しく、該第 2 の電圧レベルは、該第 1 の電圧より大きい、請求項 7 に記載のプログラマブルロジックデバイス集積回路。

10

## 【請求項 11】

プログラマブルロジックデバイス集積回路におけるプログラマブルロジックデバイスマモリ要素のアレイを使用する方法であって、プログラマブルロジックデバイスコンフィギュレーションデータは、データローディング動作の間に前記メモリ要素に書き込まれ、該プログラマブルロジックデバイスコンフィギュレーションデータは、データ読み取り動作の間に該メモリ要素から読み取られ、該方法は、

20

データローディング動作の間とデータ読み取り動作の間とで異なる電圧レベルを有する該プログラマブルロジックデバイスマモリ要素のアレイにアドレス信号を印加することと、

通常動作の間、該プログラマブルロジックデバイスマモリ要素が該プログラマブルロジックデバイスコンフィギュレーションデータを用いてロードされた後、該プログラマブルロジックデバイス集積回路上にプログラマブルコアロジックを構成するために該プログラマブルコアロジックに該プログラマブルロジックデバイスマモリ要素からの出力信号を印加することと

30

を包含する、方法。

## 【請求項 12】

前記アドレス信号を印加することは、データ読み取り動作の間の該アドレス信号の電圧レベルより大きい電圧レベルを有するアドレス信号をデータローディング動作の間に印加することを含む、請求項 1 1 に記載の方法。

## 【請求項 13】

前記アドレス信号を印加することは、第 1 の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第 2 の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第 1 の電圧レベルは、該第 2 の電圧レベルより大きく、前記方法は、

40

該第 2 の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することをさらに包含する、請求項 1 1 に記載の方法。

## 【請求項 14】

前記アドレス信号を印加することは、第 1 の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第 2 の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第 1 の電圧レベルは、該第 2 の電圧レベルより大きく、前記方法は、

該第 2 の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前

50

記メモリ要素に電力供給することと

をさらに包含する、請求項 1 1 に記載の方法。

【請求項 1 5】

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、請求項 1 1 に記載の方法。

【請求項 1 6】

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

10

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと、

データローディング動作の間、通常動作の間に該メモリ要素に電力供給するために使用される電源電圧より少ない電源電圧を用いて該メモリ要素に電力供給することと

をさらに包含する、請求項 1 1 に記載の方法。

【請求項 1 7】

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

20

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと、

データローディング動作の間、該プログラマブルコアロジック電源電圧と等しい電源電圧を用いて該メモリ要素に電力供給することと

をさらに包含する、請求項 1 1 に記載の方法。

【請求項 1 8】

前記メモリ要素の各々は、2つの相互結合されたインバータを含み、該インバータの各々は、正の電源端子と接地端子との間に直列に接続された p チャネル酸化金属半導体トランジスタおよび n チャネル酸化金属半導体トランジスタを有し、前記方法は、

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

30

通常動作の間、該正の電源端子においては正の電源電圧を、かつ該接地端子においては接地電圧を印加することによって、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することであって、データ書き込み動作の間の前記アドレス信号の前記電圧レベルは、該正の電源電圧と等しい、ことと

をさらに包含する、請求項 1 1 に記載の方法。

【請求項 1 9】

前記アドレス信号を印加することは、第 1 の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第 2 の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第 1 の電圧レベルは、該第 2 の電圧レベルより大きく、前記方法は、

40

プログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きく、該第 1 の電圧レベルと等しい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、請求項 1 1 に記載の方法。

【請求項 2 0】

前記アドレス信号を印加することは、第 1 の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第 2 の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第 1 の電圧レベルは、該第 2 の電圧レベルより大きく、前記方法は、

50

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きく、該第1の電圧レベルと等しい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、請求項1に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、本明細書においてその全容が参考により援用される、2005年11月17日に出願された仮特許出願第60/737,868号の利益を主張する。

10

【0002】

本発明は、メモリ要素に関し、より詳細には、プログラマブルロジックデバイスのような集積回路に対して高出力電圧を有する揮発性メモリ要素に関する。

【背景技術】

【0003】

集積回路は、多くの場合、揮発性メモリ要素を含む。一般的な揮発性メモリ要素は、相互結合インバータ（ラッチ）に基づき、データを格納するために使用される。各メモリ要素は、単一ビットのデータを格納できる。

【0004】

揮発性メモリ要素は、多くの場合、プログラマブルロジックデバイスにコンフィギュレーションデータを格納するために使用される。プログラマブルロジックデバイスは、所望のロジック設計をインプリメントするために比較的小さいバッチにおいてカスタマイズされ得る一種の集積回路である。典型的なシナリオにおいては、プログラマブルロジックデバイス製造者は、あらかじめカスタマイズされていないプログラマブルロジックデバイス集積回路を設計および製造する。後ほど、ロジック設計者は、カスタムロジック回路を設計するためにロジック設計システムを使用する。ロジック設計システムは、設計者が所定のプログラマブルロジックデバイスにおいて利用可能であるリソースを使用するロジック回路をインプリメントすることを補助するために、製造者のプログラマブルロジックデバイスのハードウェア能力についての情報を使用する。

20

【0005】

ロジック設計システムは、ロジック設計者のカスタム設計に基づいてコンフィギュレーションデータを生成する。コンフィギュレーションデータが複数のプログラマブルロジックデバイスの内の1つのプログラマブルロジックデバイスの複数のメモリ要素にロードされた場合、プログラマブルロジックデバイスが設計者のロジック回路をインプリメントするように、そのプログラマブルロジックデバイスのロジックをプログラムする。プログラマブルロジックデバイスの使用は、所望の回路設計をインプリメントするために必要とされる労力の量をかなり減少させ得る。

30

【0006】

従来のプログラマブルロジックデバイスマモリ要素は、正の電源電圧において電力供給される。従来のプログラマブルロジックデバイスマモリ要素に電力供給するために使用される正の電源電圧は、典型的にVccまたはVccコアと呼ばれ、プログラマブルロジックデバイスにおけるコアロジックに電力供給するために使用される電源電圧と同じである。

40

【0007】

Vccの低い値において動作するプログラマブルロジックデバイス集積回路のような集積回路は、Vccのより高い値において動作する集積回路より多くの便益を提供する。例えば、Vccにおける減少は通常、電力消費の低減を引き起こす。これらの便益のため、半導体産業は、Vccにおける減少をサポートする処理および回路設計を生成するために引き続き努力している。プログラマブルロジックデバイスの前の世代は、2.0ボルト、1.8ボルト、および1.5ボルトのVccレベルにおいて動作していた。近頃、プログ

50

ラマブルロジックデバイスにおいては、1.2ボルトのVccレベルが使用されている。未来のプログラマブルロジックデバイスが、1.2ボルトより低い（例えば、1.1ボルトまたは1.0ボルト）Vccレベルをサポートすることが期待される。

【0008】

プログラマブルロジックデバイスにおけるメモリ要素は、メモリ要素にロードされたコンフィギュレーションデータを反映する静的出力信号を生成する。静的出力信号は、nチャネルおよびpチャネル酸化金属半導体（MOS）トランジスタのゲートを駆動する。nチャネルトランジスタのような一部のトランジスタは、バストランジスタとして使用され、マルチプレクサおよび他のロジック構成要素に組み入れられる。pチャネルトランジスタは時々、電力が集積回路の未使用部分に印加されることを防ぐ電力ダウントランジスタとして使用される。nチャネルおよびpチャネルトランジスタの両方は、不十分な電圧において駆動されている場合、不完全に動作する。例えば、nチャネルバストランジスタのゲートが低すぎる電圧を受信した場合、トランジスタは正確にターンオンせず、トランジスタを通過しているロジック信号の質を低下させる。pチャネル電力ダウントランジスタのゲートが低すぎる場合、トランジスタは正確にターンオフせず、望まれない大きな漏れ電流を示す。

10

【発明の開示】

【発明が解決しようとする課題】

【0009】

従って、低コアロジック電源レベルにおいて正しく動作するプログラマブルロジックデバイス集積回路を提供することが望ましい。

20

【課題を解決するための手段】

【0010】

本発明に従うと、プログラマブルコアロジックを含むプログラマブルロジックデバイス集積回路が提供される。コンフィギュレーションデータは、メモリ要素のアレイにロードされる。ロードされたメモリ要素は、カスタムロジック機能を生成するためにコアロジックを構成する制御信号を生成する。

【0011】

データローディングおよび読み取り回路網は、アレイにおけるメモリ要素をアドレスするため使用される。メモリ要素のためのアドレストランジスタに関連するリアルエステート（real estate）要求を減らすため、および／またはメモリ要素の書き込みマージンを増加させるために、データ書き込み動作の間に使用されるアドレス信号は、プログラマブルコアロジック電源電圧より大きい電圧を有し得る。読み取り動作の間、アドレス信号は、プログラマブルコアロジック電源電圧のようなより低い電圧においてメモリ要素に印加され得る。

30

【0012】

通常動作の間、メモリ要素は、高電源電圧（elevated power supply voltage）を使用して電力供給され得る。データローディング動作の間、メモリ要素に対する電源レベルは、プログラマブルコアロジック電源電圧に下げられ得る。

40

【0013】

本発明の更なる特徴、その本質および様々な利点は、添付の図面および以下の詳細な説明から明らかになるであろう。

【0014】

本発明は、さらに、以下の手段を提供する。

【0015】

（項目1）

コアロジック電源電圧において電力供給されたプログラマブルコアロジックと、該プログラマブルコアロジックを構成する出力を有するメモリ要素のアレイと、該アレイ内の該メモリ要素をアドレスするための複数のアドレスラインと、該メモリ要素にプログラマブルロジックデバイスコンフィギュレーションデータをロー

50

ドするために、該コアロジック電源電圧より大きい電圧レベルを有するアドレス信号を該アドレスラインに印加するデータローディング・読み取り回路網とを備える、プログラマブルロジックデバイス集積回路。

## 【0016】

## (項目2)

前記メモリ要素に電力供給する時間変化メモリ要素電源電圧を提供する電力調節器回路網をさらに備え、前記データローディング・読み取り回路網が前記プログラマブルロジックデバイスコンフィギュレーションデータをロードするために前記アドレス信号を前記アドレスラインに印加した場合、該時間変化メモリ要素電源電圧は前記コアロジック電源電圧と等しく、該時間変化メモリ要素電源電圧は、通常動作の間、該コアロジック電源電圧より大きい、項目1に記載のプログラマブルロジックデバイス集積回路。

## 【0017】

## (項目3)

前記メモリ要素の通常動作の間、前記コアロジックの正の電源電圧より大きいメモリ要素電源電圧において該メモリ要素に電力供給する電力調節器回路網をさらに備える、項目1に記載のプログラマブルロジックデバイス集積回路。

## 【0018】

## (項目4)

前記メモリ要素の各々は相互結合インバータを含み、前記データローディング・読み取り回路網は該メモリ要素からプログラマブルロジックデバイスコンフィギュレーションデータを読み取るためにアドレス信号を前記アドレスラインに印加し、該プログラマブルロジックデバイスコンフィギュレーションデータを読み取るために使用される該アドレス信号は、該プログラマブルロジックデバイスコンフィギュレーションデータを該メモリ要素にロードするときに使用される該アドレス信号の電圧レベルより少ない電圧レベルを有する、項目1に記載のプログラマブルロジックデバイス集積回路。

## 【0019】

## (項目5)

複数のアドレストランジスタをさらに備え、該アドレストランジスタの各々は、前記メモリ要素のアレイ内のそれぞれのメモリ要素に関連してかつゲートを有し、該ゲートは前記アドレスラインによって制御され、該ゲートは、前記プログラマブルロジックデバイスコンフィギュレーションデータが該メモリ要素にロードされるデータ書き取り動作の間に第1の電圧レベルにおいてアドレス信号を受信し、該プログラマブルロジックデバイスコンフィギュレーションデータが前記データローディング・読み取り回路網によって該メモリ要素から読み取られるデータ読み取り動作の間に第2の電圧レベルにおいてアドレス信号を受信し、該第1の電圧レベルは、前記コアロジック電源電圧より大きく、該第2の電圧レベルは、該コアロジック電源電圧と等しい、項目1に記載のプログラマブルロジックデバイス集積回路。

## 【0020】

## (項目6)

複数のアドレストランジスタであって、該アドレストランジスタの各々は、前記メモリ要素のアレイ内のそれぞれのメモリ要素に関連してかつゲートを有し、該ゲートは前記アドレスラインによって制御され、該ゲートは、前記プログラマブルロジックデバイスコンフィギュレーションデータが該メモリ要素にロードされるデータ書き取り動作の間に第1の電圧レベルにおいてアドレス信号を受信し、該プログラマブルロジックデバイスコンフィギュレーションデータが前記データローディング・読み取り回路網によって該メモリ要素から読み取られるデータ読み取り動作の間に第2の電圧レベルにおいてアドレス信号を受信し、該第1の電圧レベルは、前記コアロジック電源電圧より大きく、該第2の電圧レベルは、該コアロジック電源電圧と等しい、複数のアドレストランジスタと、

該メモリ要素の通常動作の間、該第1の電圧レベルと等しい電源電圧において該メモリ要素に電力供給する電力調節器回路網と

10

20

30

40

50

をさらに備える、項目1に記載のプログラマブルロジックデバイス集積回路。

【0021】

(項目7)

データローディング動作の間にコンフィギュレーションデータが書き込まれ、コンフィギュレーションデータが読み取り動作の間に読み取られるプログラマブルロジックデバイスメモリ要素を有するプログラマブルロジックデバイス集積回路であって、該プログラマブルロジックデバイス集積回路は、

プログラマブルコアロジック電源電圧において電力供給されたプログラマブルコアロジックと、

該プログラマブルコアロジックを構成する通常動作の間、制御信号を該プログラマブルコアロジックに供給する該メモリ要素のアレイと、

読み取り動作の間とは異なる電圧レベルをデータローディング動作の間に該メモリ要素をアドレスするアドレス信号を生成するデータローディング・読み取り回路網とを備える、プログラマブルロジックデバイス集積回路。

【0022】

(項目8)

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、メモリ要素電源電圧において前記メモリ要素に電力供給する電力調節器回路網をさらに含む、項目7に記載のプログラマブルロジックデバイス集積回路。

【0023】

(項目9)

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、データローディング動作の間の該アドレス信号の該電圧レベルと等しいメモリ要素電源電圧において前記メモリ要素に電力供給する電力調節器回路網をさらに含む、項目7に記載のプログラマブルロジックデバイス集積回路。

【0024】

(項目10)

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、第1および第2の電圧レベルを有する時間変化メモリ要素電源電圧を生成するダイナミックな電力調節器回路網をさらに含み、該第1の電圧レベルは、データローディング動作の間に生成され、該第2の電圧レベルは、通常動作の間に生成され、該第1の電圧は、該プログラマブルコアロジック電源電圧と等しく、該第2の電圧レベルは、該第1の電圧より大きい、項目7に記載のプログラマブルロジックデバイス集積回路。

【0025】

(項目11)

プログラマブルロジックデバイス集積回路におけるプログラマブルロジックデバイスマモリ要素のアレイを使用する方法であって、プログラマブルロジックデバイスコンフィギュレーションデータは、データローディング動作の間に前記メモリ要素に書き込まれ、該プログラマブルロジックデバイスコンフィギュレーションデータは、データ読み取り動作の間に該メモリ要素から読み取られ、該方法は、

データローディング動作の間とデータ読み取り動作との間に異なる電圧レベルを有する該プログラマブルロジックデバイスマモリ要素のアレイをアドレス信号に印加することと、

通常動作の間、該プログラマブルロジックデバイスマモリ要素が該プログラマブルロジ

10

20

30

40

50

ックデバイスコンフィギュレーションデータを用いてロードされた後、該プログラマブルロジックデバイス集積回路上にプログラマブルコアロジックを構成するために該プログラマブルコアロジックに該プログラマブルロジックデバイスマモリ要素からの出力信号を印加することと

を包含する、方法。

【0026】

(項目12)

前記アドレス信号を印加することは、データ読み取り動作の間の該アドレス信号の電圧レベルより大きい電圧レベルを有するアドレス信号をデータローディング動作の間に印加することを含む、項目11に記載の方法。

10

【0027】

(項目13)

前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することをさらに包含する、項目11に記載の方法。

【0028】

(項目14)

20

前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

【0029】

30

(項目15)

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

【0030】

(項目16)

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

40

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと、

データローディング動作の間、通常動作の間に該メモリ要素に電力供給するために使用される電源電圧より少ない電源電圧を用いて該メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

【0031】

(項目17)

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前

50

記メモリ要素に電力供給することと、

データローディング動作の間、該プログラマブルコアロジック電源電圧と等しい電源電圧を用いて該メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

【0032】

(項目18)

前記メモリ要素の各々は、2つの相互結合されたインバータを含み、該インバータの各々は、正の電源端子と接地端子との間に直列に接続されたpチャネル酸化金属半導体トランジスタおよびnチャネル酸化金属半導体トランジスタを有し、前記方法は、

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該正の電源端子においては正の電源電圧を、かつ該接地端子においては接地電圧を印加することによって、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することであって、データ書き込み動作の間の前記アドレス信号の前記電圧レベルは、該正の電源電圧と等しい、ことと

をさらに包含する、項目11に記載の方法。

【0033】

(項目19)

前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

プログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きく、該第1の電圧レベルと等しい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

【0034】

(項目20)

前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きく、該第1の電圧レベルと等しい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

【発明の効果】

【0035】

本発明により、低コアロジック電源レベルにおいて正しく動作するプログラマブルロジックデバイス集積回路が提供され得る。

【発明を実施するための最良の形態】

【0036】

本発明は、メモリ要素およびメモリ要素を含む集積回路に関する。本発明は、メモリ要素にデータにロードし、データが正確にロードされたことを確認するための回路にも関する。メモリ要素を含む集積回路は、メモリチップ、メモリアレイを用いるデジタル信号処理回路、マイクロプロセッサ、メモリアレイを用いる特定用途向け集積回路、メモリ要素がコンフィギュレーションメモリのために使用されるプログラマブルロジックデバイス集積回路、または任意の他の適した集積回路であり得る。明確性のため、本発明は概して、

10

20

30

40

50

揮発性メモリ要素がコンフィギュレーションデータを格納するために使用される、プログラマブルロジックデバイス集積回路のコンテキストにおいて説明される。

【0037】

プログラマブルロジックデバイスのプログラミングの間、コンフィギュレーションデータは、メモリ要素にロードされる。プログラマブルロジックデバイスの動作の間、各メモリ要素は、静的出力信号を提供する。メモリ要素からの出力信号は、プログラマブルロジックに印加され、所望のロジック機能を実行するためにプログラマブルロジックをカスタマイズする。典型的な構成において、各静的出力信号は、nチャネルまたはpチャネル酸化金属半導体トランジスタのゲートに印加される制御信号として役に立つ。

【0038】

nチャネルおよびpチャネルトランジスタが含まれるプログラマブルロジックは、プログラマブルロジックデバイスのロジックコアの一部を生成し、従って、プログラマブルコアロジックと時々呼ばれる。コアロジックは、Vccと通常呼ばれる正の電源電圧およびVssと通常呼ばれる接地電圧を使用して電力供給される。

【0039】

電力消費を減少させるために、Vccの大きさを減少させるという進行中のトレンドが半導体産業にある。コアロジック電源電圧を減少させることは電力消費を減少させるが、設計の挑戦へつながり得る。例えば、プログラマブルコアロジックにおけるnチャネルトランジスタは、完全にターンオンすることが困難になり得、コアロジックにおけるpチャネルトランジスタは、完全にターンオフすることが困難になり得る。

【0040】

本発明に従って、高電源レベルは、プログラマブルロジックデバイス集積回路におけるプログラマブルメモリ要素に電力供給するために使用され得る。高電源は、Vcchgの正の電源電圧および接地電圧を使用する。1つの適切な構成を用いて、接地電源電圧は、コアロジックにおいて使用される値と同じであるVssである。

【0041】

通常のデバイス動作の間、正の電源電圧Vcchgは、Vcchg高の値において維持される。結果として、ロジック1を含むメモリ要素は、Vcchg高において出力信号を生成する。Vcchg高の値がVccより高いため、メモリ要素がVccにおいて電力供給された場合と比べ、プログラマブルコアロジックにおけるnチャネルトランジスタはより完全にターンオンされ、プログラマブルコアロジックにおけるpチャネルトランジスタはより完全にターンオフされる。

【0042】

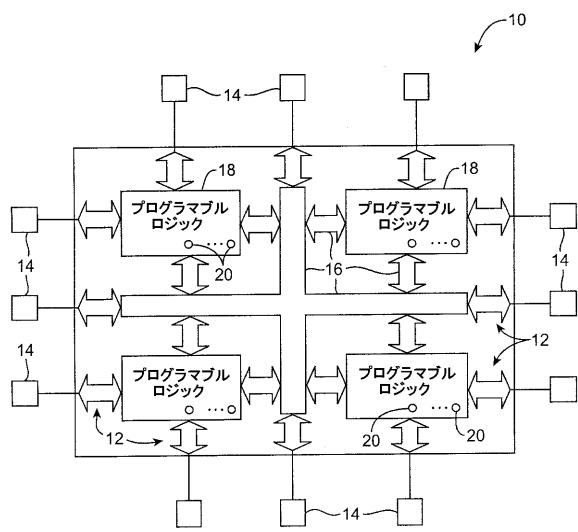

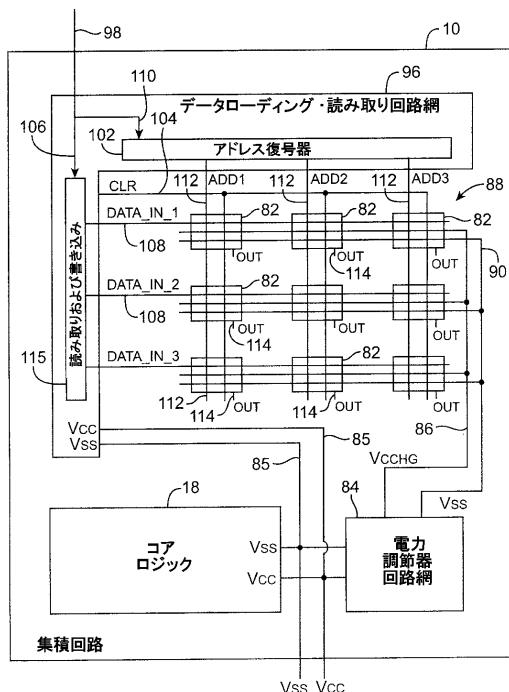

本発明に従う例示的なプログラマブルロジックデバイス10は、図1に示される。

【0043】

プログラマブルロジックデバイス10は、入力/出力ピン14を介してデバイス10から信号を駆動させるため、かつ他のデバイスから信号を受信するために入力/出力回路網12を有し得る。グローバルおよびローカルの垂直および水平導電性ラインのような相互接続リソース16は、デバイス10上の信号をルートするために使用され得る。相互接続リソース16は、固定相互接続器（導電性ライン）およびプログラマブル相互接続器（すなわち、それぞれの固定接続器間のプログラマブル接続）を含む。プログラマブルロジック18は、組み合わせおよび順序ロジック回路網を含み得る。プログラマブルロジック18は、カスタムロジック機能を実行するように構成され得る。相互接続リソースに関連するプログラマブル相互接続器は、プログラマブルロジック18の一部として考慮され得る。

【0044】

プログラマブルロジックデバイス10は、ピン14および入力/出力回路網12を使用してコンフィギュレーションデータ（プログラミングデータとも呼ばれる）によってロードされ得る揮発性メモリ要素20を含む。一度ロードされると、メモリ要素の各々は、プログラマブルロジック18における関連ロジック構成要素の状態を制御する、対応する静

10

20

30

40

50

的制御出力信号を提供する。典型的に、メモリ要素出力信号は、酸化金属半導体（MOS）トランジスタのゲートを制御するために使用される。これらのトランジスタの大半は、一般に、マルチプレクサのようなプログラマブル構成要素におけるnチャネル酸化金属半導体（NMOS）パストランジスタである。メモリ要素出力が高い場合、そのメモリ要素によって制御されているパストランジスタはターンオンされ、その入力からその出力へとロジック信号をパスする。メモリ要素出力が低い場合、パストランジスタはターンオフされ、ロジック信号をパスしない。

#### 【0045】

典型的なメモリ要素20は、相互結合インバータを形成するように構成された複数のトランジスタから形成される。1つの適したアプローチを用いて、相補的酸化金属半導体（CMOS）集積回路技術は、メモリ要素20を形成するために使用される。そのため、CMOSベースのメモリ要素インプリメンテーションは、例として本明細書中に説明される。プログラマブルロジックデバイス集積回路のコンテキストにおいて、メモリ要素はコンフィギュレーションデータを格納し、それによって時々、コンフィギュレーションランダムアクセスメモリ（CRAM）セルと呼ばれる。

#### 【0046】

メモリ要素は、任意の適したソースからロードされ得る。一例示的構成を用いて、メモリ要素は、ピン14および入力／出力回路網12を介して外部消去可能プログラマブル讀取専用メモリおよびコンフィギュレーションデバイスと呼ばれる制御チップからロードされる。ロードされたメモリ要素20からの出力信号は、それらの要素を制御するため（例えば、所定のトランジスタをターンオンまたはターンオフするため）、プログラマブルロジック18における回路要素（例えば、酸化金属半導体トランジスタ）の端子（例えば、ゲート）に印加され、それによって、プログラマブルロジック18においてロジックを構成する。回路要素は、パストランジスタのようなトランジスタ、マルチプレクサの一部、ルックアップテーブル、ロジックアレイ、AND、OR、NAND、およびNORロジックゲート等であり得る。

#### 【0047】

メモリ要素20は、一般に、アレイパターンにおいて構成される。典型的なモダンプログラマブルロジックデバイスにおいては、各チップ上に何百万ものメモリ要素20があり得る。プログラミング動作の間、メモリ要素のアレイはコンフィギュレーションデータを用いて提供される。コンフィギュレーションデータを用いて一度ロードされると、メモリ要素20は、プログラマブルロジック18における回路網の一部分を選択的に制御（例えば、ターオンオンおよびターンオフ）し、それによって、望まれたまま動作するようにその機能をカスタマイズする。

#### 【0048】

デバイス10の回路網は、任意の適したアーキテクチャを使用して編成され得る。例として、プログラマブルロジックデバイス10のロジックは、各々が複数のより小さなロジック領域を含んでいるより大きなプログラマブルロジック領域の一連の列および行において編成され得る。デバイス10のロジックリソースは、関連垂直および水平コンダクタのような相互接続リソース16によって相互接続され得る。これらのコンダクタは、デバイス10の実質的に全体に広がるグローバル導電性ライン、デバイス10の一部に広がるハーフラインまたはクオーターラインのような分数ライン、特定の長さ（例えば、いくつかのロジック領域に相互接続するために十分な）のスタガードライン、より小さなローカルライン、または任意の他の適した相互接続リソース構成を含み得る。望まれた場合、デバイス10のロジックは、複数の大きな領域がロジックの更に大きな部分を形成するために相互接続される、より多くのレベルまたは層において構成され得る。他のデバイス構成は、列および行において構成されていないロジックを使用し得る。

#### 【0049】

メモリ要素がアレイにおいて構成されている場合、水平および垂直コンダクタならびに関連ローディング回路網は、コンフィギュレーションデータを用いてメモリ要素をロード

10

20

30

40

50

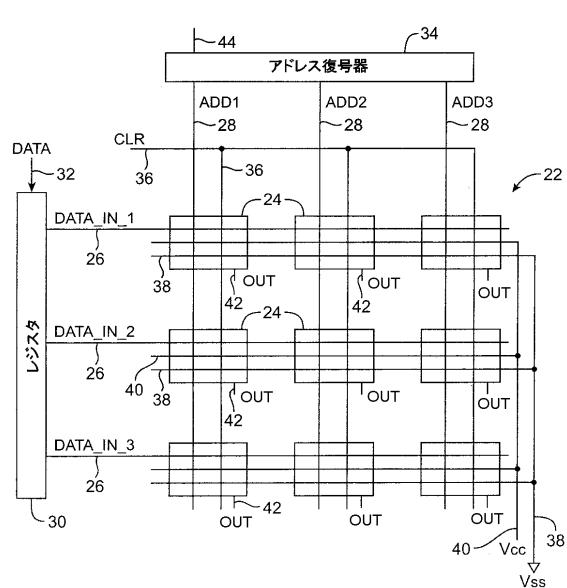

するために使用され得る。従来のデータローディング構成は、図2に示される。図2の構成は、メモリ要素24の3×3アレイ22を有する。(実際のメモリアレイは、典型的に、何百または何千の列および行を有するが、3×3アレイは例として使用される。)アレイ22は、正の電源ライン40および接地ライン38を介して電力を受ける。ライン40上の電圧Vccは典型的に1.2ボルトであり、接地ライン38上の電圧Vssは典型的に0ボルトである。

#### 【0050】

クリアライン36( CLRとしてラベル付けされる)は、メモリアレイ22のコンテンツをクリアするために使用される。アレイがクリアにされた後、コンフィギュレーションデータはロードされ得る。

10

#### 【0051】

コンフィギュレーションデータは、入力32を介してレジスタ30に直列に提供される。コンフィギュレーションデータは次いで、DATA\_IN\_1、DATA\_IN\_2、およびDATA\_IN\_3ライン26を介してアレイ22に並行に提供される。アドレス復号器34は、入力44を介してアドレス情報を受信する。それに応答して、アドレス復号器は、アドレスライン28の望まれる1つのもの(すなわち、ADD1、ADD2、またはADD3)をアサートする。アドレスラインが所定の列において示された場合、データライン26上のデータは、その列におけるメモリ要素24にロードされる。アレイは、アレイの列の各々におけるメモリ要素を組織的にローディングすることによって満たされる。アレイがコンフィギュレーションデータによって完全にロードされた後、各メモリ要素24の出力42は、プログラマブルロジックデバイスにおけるパストランジスタのゲートまたは他のロジック構成要素を制御するために、対応する静的制御信号を生成する。

20

#### 【0052】

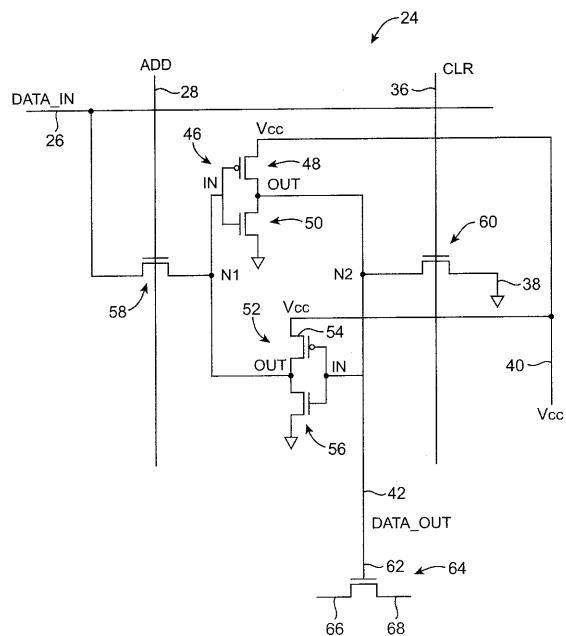

図2のアレイ22に使用される種類である、従来のメモリ要素24が図3に示される。図3に示されるように、メモリ要素24は、2つの相互結合インバータ(インバータ46およびインバータ52)から形成される。インバータ46は、pチャネル酸化金属半導体(PMOS)トランジスタ48およびnチャネル酸化金属半導体(NMOS)トランジスタ50を有する。インバータ52は、PMOSトランジスタ54およびNMOSトランジスタ56を有する。NMOSトランジスタ60は、クリアライン36をアクティブにすることによって、クリア動作の間ターンオンされる。これは、ノードN2を接地38に接続し、メモリ要素24をクリアにする。ライン42上のメモリ要素の出力(DATA\_OUT)は、ノードN2における信号によって決定される。

30

#### 【0053】

アドレスライン28が高められると、NMOSトランジスタ58はターンオンされ、データライン26上の信号はメモリ要素46へと駆動される。ライン26上の信号が高い場合、ノードN1は高いまま残り、メモリ要素24はその低い(クリアされた)状態のまま残る。出力DATA\_OUTは低い。ライン26上の信号が低い場合、ノードN1は下げられ、インバータ46による低いN1信号の反転によって、ノードN2における電圧は高められる。これは、出力DATA\_OUTを高くする。

#### 【0054】

40

DATA\_OUT信号は、パストランジスタ64のゲート62に印加される。DATA\_OUTが低い場合、パストランジスタ64はオフにされている。DATA\_OUTが高い場合、パストランジスタ64はオンされ、データはライン66とライン68との間ににおいて流れることが可能である。

#### 【0055】

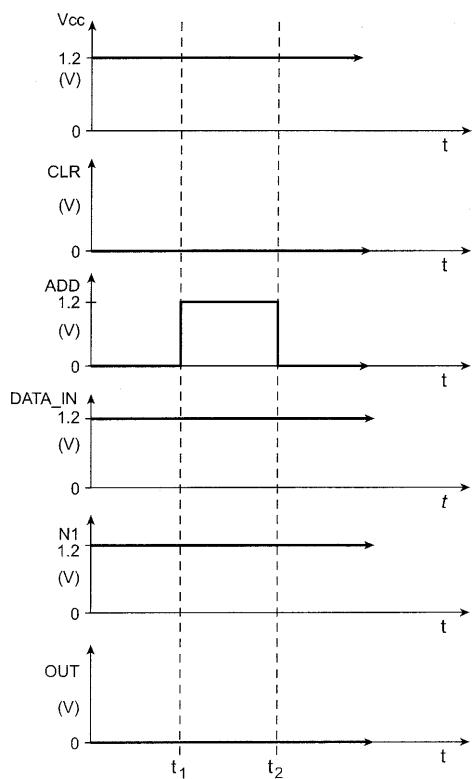

従来のメモリ要素24をロードすることに関連する動作を示す信号タイミング図は、図4および図5に示される。図4のトレースは、ロジック「1」をクリアされたメモリ要素24へとロードする処理を示す。図5のトレースは、ロジック「0」をクリアされたメモリ要素24へとロードする処理を示す。

#### 【0056】

50

図4の第1のトレースは、Vccライン40に印加された電圧Vccが1.2ボルトにおいて一定であることを示す。この正の電源電圧は、インバータ46および52に印加される。

【0057】

図4の第2のトレースは、クリアリング動作がシステム起動時に実行された後、ライン36上のクリア信号CLRは0ボルトにおいて一定であることを示す。

【0058】

図4の第3のトレースに示されるように、アドレスラインADDは時間t<sub>1</sub>においてアサートされ、時間t<sub>2</sub>においてデアサートされる。

【0059】

図4の第4のトレースは、ライン26上のDATA\_INの値がデータローディング動作の間、一定の低信号であることを示す。

【0060】

図4の第5のトレースにおける信号N1は、図3のノードN1における電圧を表す。

【0061】

図4の第6のトレースにおける信号DATA\_OUTは、ノードN2における電圧と同じであり、メモリ要素24のコンテンツを表す。メモリ要素がロジック1を格納している場合、ノードN2は高く、かつDATA\_OUTも高い。メモリ要素がロジック0を格納している場合、ノードN2は低く、かつDATA\_OUTも低い。

【0062】

図4に示されるように、t<sub>1</sub>の前の時間tにおいては、ADDは低く、よってトランジスタ58はオフである。ノードN1における電圧は高く、ノードN2における電圧は低い。出力DATA\_OUTは低い。この状態においては、メモリ要素がそのクリアされた状態にあるため、メモリ要素に格納されたデータはロジック0である。時間t<sub>1</sub>において、ADDは高くなり、それによってトランジスタ58をターンオンし、0ボルトにおけるDATA\_INラインをノードN1に接続し、N1を下げる。ノードN2における電圧が高くなるように、ノードN1における低電圧はインバータ46によって反転される。図4の第6のトレースは、これがDATA\_OUTをt<sub>1</sub>において高くすることを示す。この段階において、ロジック1はメモリ要素24に格納される。アドレスラインADDが時間t<sub>2</sub>においてデアサートされた場合、トランジスタ58はターンオフされ、それによってメモリ要素を絶縁し、更なる状態変化を防ぐ。図4の第6のトレースに示されるように、DATA\_OUT信号は時間t<sub>2</sub>において高いまま残る。

【0063】

図5のトレースは、ロジック「0」をクリアされたメモリ要素24(図3)にロードする処理を示す。この状況において、メモリ要素はロジック0を含み、ローディング処理はその状態を変化させない。

【0064】

図5の第1のトレースは、Vccライン40(図3)に印加された電圧Vccが1.2ボルトにおいて一定であることを示す。正の電源電圧Vccは、インバータ46および52に印加される。

【0065】

図5の第2のトレースに示されるように、クリアリング動作がシステム起動時に実行された後、ライン36上のクリア信号CLRは0ボルトにおいて一定である。

【0066】

図5の第3のトレースに示されるように、アドレスラインADDは時間t<sub>1</sub>においてアサートされ、時間t<sub>2</sub>においてデアサートされる。

【0067】

図5の第4のトレースは、ライン26上のDATA\_INの値がデータローディング動作の間、一定の高値である。図5のシナリオにおいては、ロジック0がメモリ要素24にロードされるため、DATA\_INは高い。図4のシナリオにおいては、ロジック1がメ

10

20

30

40

50

モリ要素 24 にロードされていたため、DATA\_IN は低い。

【0068】

図 5 の第 5 のトレースにおける信号 N1 は、図 3 のノード N1 における電圧を表す。既にクリアされたメモリ要素にゼロがロードされている場合、N1 は変化しない。

【0069】

ノード N2 における電圧と同じである、図 5 の第 6 のトレースにおける信号 DATA\_OUT は、メモリ要素 24 のコンテンツを表す。メモリ要素 24 がクリアされたため、DATA\_OUT は時間  $t_1$  より前において低い。時間  $t_1$  の後、ADD はアサートされ、それによってトランジスタ 58 をターンオンし、高 DATA\_IN 信号をノード N1 に接続する。N1 が既に高いため、高 DATA\_IN 信号をノード N1 に印加することは、図 5 の DATA\_OUT トレースに示されるように、メモリ要素 24 の状態を時間  $t_1$  において変化させることを引き起こさない。DATA\_OUT 信号も、ADD ラインが時間  $t_2$  においてデアサートされた後、その低値において固定されたまま残る。

【0070】

図 3 の従来のメモリ要素 24 のような従来のメモリ要素においては、アドレス、クリア、およびデータ信号は、0 ボルトのロジック低値から Vcc のロジック高値の間にある。

【0071】

本発明に従って、これらの信号の異なる値は性能を改良するために使用され得る。例えば、アドレス信号は、図 4 および図 5 と関連して示される種類のデータ書き込み動作の間に高くされ得、データ読み取り動作の間に下げられ得る。更に、メモリ要素電源レベルは高くされ得る。

【0072】

図 6 に示されるように、本発明に従うプログラマブルロジックデバイス集積回路 10 は、データローディング・読み取り回路網 96 を含む。メモリ要素 82 は、アレイ 88 において構成される。アドレスライン 112 およびデータライン 108 は、アレイをアドレスするために使用される。クリアライン 104 上のクリア信号 CLR は、データローディング動作に備えて、メモリ要素 82 をクリアするために使用される。各メモリ要素 82 は、対応するデータ出力ライン 114 において出力を生成する。

【0073】

プログラマブルロジックデバイス 10 は、コアロジック 18 を含む。コアロジック 18 は、正の電源電圧 Vcc および接地電圧 Vss において電力供給されたプログラマブルコアロジックを含む。一例示的構成において、正の電源電圧 Vcc は約 1.2 ボルトであり、接地電圧 Vss は 0 ボルトである。他の構成も使用され得る。例えば、Vcc は 1.2 ボルトより大きくまたは少なくなり得、Vss は 0 ボルトより大きくまたは少なくなり得る。1.2 ボルトの Vcc 値および 0 ボルトの Vss 値の使用は単に例示的である。

【0074】

Vcc および Vss のような電源電圧は、任意の適した構成を使用してデバイス 10 における回路網に供給され得る。例えば、電源電圧は、1 つ以上の外部電源ピンから受け取られ得る。外部供給された電源電圧より大きいまたは少ない電源電圧は、オンチップ回路網を使用して生成され得る。例えば、分圧器は、外部供給された電圧を減らすために使用され得、充電パンプまたは他の電圧ブースト回路は、外部供給された電源電圧より大きい電源電圧を生成するために使用され得る。

【0075】

図 6 の例示的構成においては、電力調節器回路網 84 は、外部電源電圧 Vcc および Vss を用いて供給される。電力調節器回路網 84 は、アレイ 88 におけるメモリ要素 82 のための電源電圧 Vss および Vchrg を生成するためにこれらの電圧を使用する。

【0076】

データローディング・読み取り回路網 96 は、アドレス、クリア、データ信号をアレイ 88 に提供する。1 つの適した構成においては、データローディング・読み取り回路網 96 は、Vcc より大きい電圧におけるこれらの信号の少なくとも 1 つを提供する。これら

の高電圧は、任意の適したソース（例えば、ピンまたは電力調節器回路網 8 4）から受け取られ得る。図 6 の実施例においては、データローディング・読み取り回路網 9 6 は、ライン 8 5 を通じて外部ピンから受け取られる電源電圧  $V_{ss}$  および  $V_{cc}$  から内部的に高電圧を生成する。電源電圧  $V_{ss}$  および  $V_{cc}$  は、コアロジック 1 8 にも提供される。

#### 【 0 0 7 7 】

コアロジック 1 8 は、n チャネルおよび p チャネル酸化金属半導体トランジスタならびにインバータ、マルチプレクサ、ロジックゲート、レジスタロジック、ルックアップテーブル等のような、n チャンルおよび p チャネル酸化金属半導体トランジスタから形成されたプログラマブルロジック構成要素を含む。典型的なシナリオにおいては、プログラマブルコアロジック 1 8 における回路または構成要素は、正の電源電圧  $V_{cc}$  を受け取る正の電源端子および接地電源電圧  $V_{ss}$  を受け取る接地電源端子を有する。

#### 【 0 0 7 8 】

電力調節器回路網 8 4 は、ライン 9 0 および 8 6 を使用して、アレイ 8 8 におけるメモリ要素 8 2 に接地電源電圧  $V_{ss}$  および正の電源電圧  $V_{cc hg}$  を供給する。一般に、任意の適した電源電圧は、要素 8 2 に電力供給するために使用され得る。電源電圧が高くされると（すなわち、正の電源電圧と接地電圧との間の差異が  $V_{cc}$  より大きい場合）、デバイス 1 0 の性能は強化される。特に、高電源電圧を使用することは、使用しない場合と比較し、メモリ要素 8 2 からの出力制御信号がコアロジック 1 8 における n チャネルトランジスタをより完全にターンオンし、コアロジック 1 8 における p チャネルトランジスタをより完全にターンオフすることを可能にする。

#### 【 0 0 7 9 】

一般に、高電源電圧は、増加された正の電源電圧および / または減少された接地電源電圧を使用してインプリメントされ得る。異なる電圧レベルを有する電源ラインのプログラマブルロジックデバイスアーキテクチャの導入は、複雑性を増す傾向がある。不必要的複雑性が増すことを回避するため、異なる電源電圧の使用を制限することが所望され得る。電源レベルの数を制限するための 1 つの適したアプローチは、コアロジック 1 8 ならびにデータローディング・読み取り回路網 9 6 に電力供給するために使用される接地電圧  $V_{ss}$  と同じものを、アレイ 8 8 に電力供給するために使用される。この構成の種類は例として説明される。望まれた場合、しかしながら、コアロジック 1 8 のための接地電圧がアレイ 8 8 のための接地電圧と異なるような他の構成が使用され得る。

#### 【 0 0 8 0 】

ライン 8 6 および 9 0 は、 $V_{cc hg}$  および  $V_{ss}$  をメモリ要素アレイ 8 8 におけるメモリ要素 8 2 の各々に分配するために使用される。図 6 の実施例においては、アレイ 8 8 に内にメモリ要素 8 2 の 3 つの行および 3 つの列がある。これは、単に例示的である。集積回路 1 0 のような集積回路は、メモリ要素 8 2 の任意の適した数を有し得る。典型的なメモリアレイは、例えば、数百個または数千個の列および行に構成された数千個または数百万のメモリ要素 8 2 を有し得る。

#### 【 0 0 8 1 】

信号  $V_{ss}$  は一定である。信号  $V_{cc hg}$  は、一定値  $V_{cc hg}$  高であり得る。例えば、 $V_{cc hg}$  高は、1.6 ボルトのような一定値であり得る。 $V_{cc hg}$  高の値は、 $V_{cc}$ （例えば、1.2 ボルト）より大きい。所望された場合、電力調節器回路網 8 4 は、データローディング動作を容易にするために、時間変化電源信号を生成し得る。例えば、電力調節器回路網 8 4 は、データローディング動作の間、 $V_{cc hg}$  の値を  $V_{cc hg}$  高から  $V_{cc hg}$  低の値に減らし得る。データローディング動作の間に  $V_{cc hg}$  を下げることは、メモリ要素 8 2 のための書き込みマージンを改良し、および / またはメモリ要素をロードするために使用されるアドレストランジスタに対するリアルエーステート要求を減らすために役に立つ。アレイ 8 8 における時間変化  $V_{cc hg}$  の使用は、例として本明細書中に説明される。

#### 【 0 0 8 2 】

コアロジック 1 8 に電力供給するために比較的低電源レベル  $V_{cc}$  を使用することは、

10

20

30

40

50

減少された電力消費のような利益を提供する。Vcchg高-VssがVcc-Vssより大きいため、メモリ要素82に電力供給するために使用される電源レベルは、コア電源レベルより大きい。しかしながら、アレイ88において高電源レベルを使用することにから生じる、アレイ88における電力消費効率の損失は、性能利益によってオフセットされる。

#### 【0083】

データローディング・読み取り回路網96は、アレイ88のためのクリアリングおよびデータローディング動作を制御する。データローディング・読み取り回路網96は、入力バス98を介して外部ソースからコンフィギュレーションデータを受信する。典型的なシステムにおいては、コンフィギュレーションデータは、メモリおよびデータローディング回路からプログラマブルロジックデバイスへとロードされる。コンフィギュレーションデバイスと時々呼ばれるこの種類の回路は、コンフィギュレーションデータを読み取り・書き込み回路網115内のレジスタにロードする。アドレス復号器102は、バス98および入力110を介して外部制御信号を受信し得、またはアドレス制御信号は、データローディング・読み取り回路網96において内部で生成され得る。

10

#### 【0084】

データローディング・読み取り回路網96は、クリアライン104上のクリア信号(CLRとラベル付けされた)を生成する。信号CLRを回路網96を用いてアサートすることは、メモリアレイ88のコンテンツをクリアにする。クリアリング動作は、概して、システム電力アップまたは再構成の間に実行される。アレイがクリアにされた後、CLR信号はデアサートされ、コンフィギュレーションデータはロードされる。

20

#### 【0085】

データローディング動作をサポートするため、コンフィギュレーションデータは、バス98および106を介して読み取り・書き込み回路網115内のレジスタにロードされ得る。レジスタは、DATA\_IN\_1、DATA\_IN\_2、およびDATA\_IN\_3ライン108を介してアレイ88と並列にコンフィギュレーションデータを印加する。アドレス復号器102は、外部ソースから、またはデータローディング・読み取り回路網96における回路網から、入力110を介してアドレス情報を受信する。アドレス復号器102は、組織的に、所望されたアドレスライン112(すなわち、ADD1、ADD2、またはADD3)をアサートおよびデアサートする。各列におけるアドレスラインがアサートされた場合、データライン108上のデータは、その列におけるメモリ要素82にロードされる。各列をこのような方法においてアドレスすることによって、アレイ88の全体は、コンフィギュレーションデータによってロードされる。

30

#### 【0086】

アレイがロードされた後、適切なデータローディングは、メモリ要素82にプログラムされたデータを読み出すために読み取り・書き込み回路網115の読み取り回路網を使用することによって確認され得る。データ確認またはデータ読み取りと時々呼ばれるこの動作は、ローディング処理の間エラーが生じていないことを保証するために使用される。アレイ88から読み出された確認データの値がデータローディングの間に使用された値と一致しない場合、エラーメッセージが生成され得、ローディング処理は繰り返され得、または他の適した訂正処置がとられ得る。

40

#### 【0087】

データ読み取り動作の間、データライン108は読み取りラインとして使用される。特に、DATA\_IN\_1、DATA\_IN\_2、およびDATA\_IN\_3ライン108は、アドレスされたメモリ要素82の列からのロードされたコンフィギュレーションデータ値を読み取り・書き込み回路網115に伝達するために使用される。

#### 【0088】

データローディング処理の成功確認が終了した後、ロードされたコンフィギュレーションデータはデバイス10におけるプログラマブルロジックの動作を制御するために使用され、それによってデバイス10はシステムにおいて使用され得る。通常動作の間、各メモ

50

リ要素 8 2 の出力 1 1 4 は、N M O S パストランジスタのようなN M O S トランジスタ、P M O S 電力ダウントランジスタのようなP M O S トランジスタ、またはプログラマブルロジックデバイス 1 0 のプログラマブルコアロジック 1 8 における他の回路構成要素のゲートを制御するために、対応する静的制御信号を生成する。

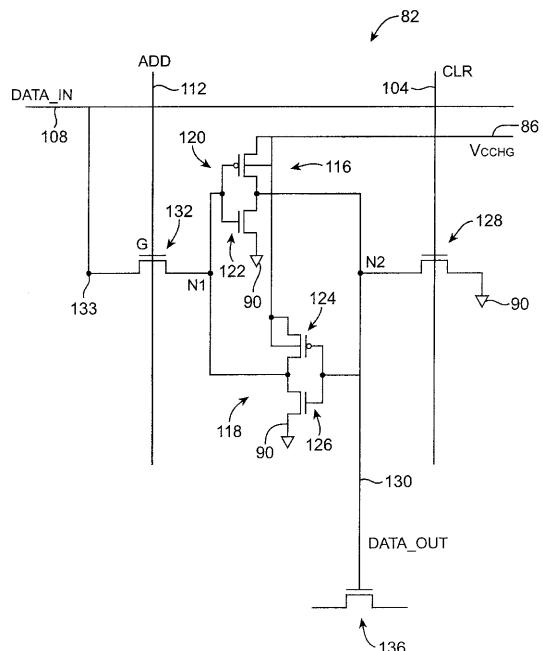

【 0 0 8 9 】

例示的メモリ要素 8 2 は、図 7 に示される。プログラミングの間、メモリ要素 8 2 は、D A T A \_ I N ライン 1 0 8 上にデータを受信する。データがアレイにロードされた後、データ確認動作は、データが適切にロードされたか否かを決定するために実行される。データ確認動作の間、D A T A \_ I N ラインは、検証経路として役に立つ。ローディングする場合、データは、図 6 のデータローディング・読み取り回路網 9 6 からライン 1 0 8 に沿ってアレイ 8 8 に流れる。データ確認動作を実行する場合、データは、アレイ 8 8 からライン 1 0 8 に沿って逆方向において図 6 のデータローディング・読み取り回路網 9 6 に流れる。 10

【 0 0 9 0 】

ローディングおよび読み取り動作の両方の間、アドレス信号 A D D は、組織的に、アドレスライン 1 1 2 においてアサートされる。これは、データローディング・読み取り回路網 9 6 ( 図 6 ) が、データ書き込みまたは読み取りのためにアレイ 8 8 の列をアドレスすることを可能にする。

【 0 0 9 1 】

図 7 のメモリ要素 8 2 は、2 つの相互結合インバータを有する。インバータ 1 1 6 は、トランジスタ 1 2 0 および 1 2 2 を有する。インバータ 1 1 8 は、トランジスタ 1 2 4 および 1 2 6 を有する。トランジスタ 1 2 0 および 1 2 4 は、p チャネル酸化金属半導体トランジスタである。トランジスタ 1 2 2 および 1 2 6 は、n チャネル酸化金属半導体トランジスタである。ノード N 1 および N 2 における電圧は、逆の極性を有する。N 1 が低い場合、N 2 は高く、メモリ要素 8 2 はプログラムされていると言われる。この状況におけるプログラムされたメモリ要素のコンテンツは、ロジック 1 である。N 1 が高く N 2 が高い場合、メモリ要素はロジック 0 を含み、クリアされていると言われる。 20

【 0 0 9 2 】

図 7 に示されるように、ノード N 2 における電圧は、D A T A \_ O U T 電圧と同じである。D A T A \_ O U T 信号は、ライン 1 3 0 のようなラインを通じてトランジスタ 1 3 6 のようなプログラマブルコアロジック構成要素に印加される ( 図 6 の出力 1 1 4 として示される )。 30

【 0 0 9 3 】

本発明に従って、ライン 1 1 2 上のアドレス信号 A D D の電圧は、書き込み動作の間比較的高い電圧を有し、データ確認 ( 読み取り ) 動作の間比較的低い電圧を有する。A D D 信号は、データローディング・読み取り回路網 9 6 ( 図 6 ) のアドレス復号器 1 0 2 によって生成される。1 つの適した構成において、アドレス信号は、データローディングの間 V s s の低値から V c c h g 高の高値の間にあり、データ読み取り動作 ( データ確認 ) の間 V s s の低値から V c c h g 低の高値 ( 例えば、V c c ) の間にある。 40

【 0 0 9 4 】

書き込み動作の間に使用されるアドレス電圧 ( この例において 1 . 6 ボルトである ) は、使用されない場合と比較してアドレストランジスタ 1 3 2 をより多くターンオンする。それによって、アドレストランジスタ 1 3 2 に対するリアルエステート要求を減らし、および / またはメモリ要素 8 2 のための書き込みマージンを増加させる。データ確認読み取り動作の間に使用される下げられたアドレス電圧 ( この例においては 1 . 2 ボルトである ) は、メモリ要素 8 2 の読み取りマージンを増加させる。

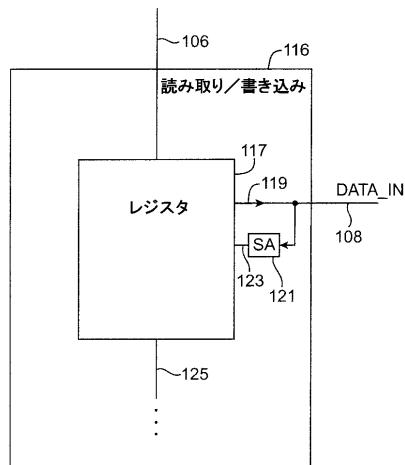

【 0 0 9 5 】

図 6 のデータローディング・読み取り回路網 9 6 に使用され得る例示的読み取り・書き込み回路網 1 1 5 は、図 8 に示される。図 8 に示されるように、読み取り・書き込み回路網 1 1 5 は、バス 1 2 5 のようなバスを使用して鎖状に接続されたレジスタ 1 1 7 を含む 50

。データローディング動作の間、レジスタ117の出力119はイネーブルされ、センス増幅器121はディセーブルされる。データがレジスタ117にシフトされた後、各レジスタは、対応する出力119においてコンフィギュレーションデータ出力信号を提供する。出力119の各々は、コンフィギュレーションデータをアレイ88のメモリ要素82(図6)にロードするためにそれぞれのDATA\_INライン108に接続される。コンフィギュレーションデータが正常にロードされたことを確認するために、データ読み取り動作はDATA\_INライン108を使用して実行される。データ読み取り動作の間、レジスタ出力119はディセーブルされ、センス増幅器121はイネーブルされる。この構成において、データは、アレイ88のアドレスされた列からDATA\_INライン108、センス増幅器121、および入力123を介してレジスタ117に流れる。

10

#### 【0096】

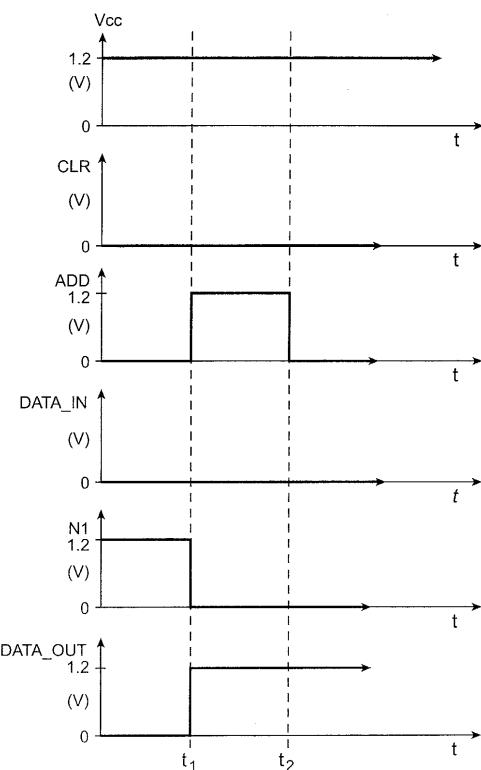

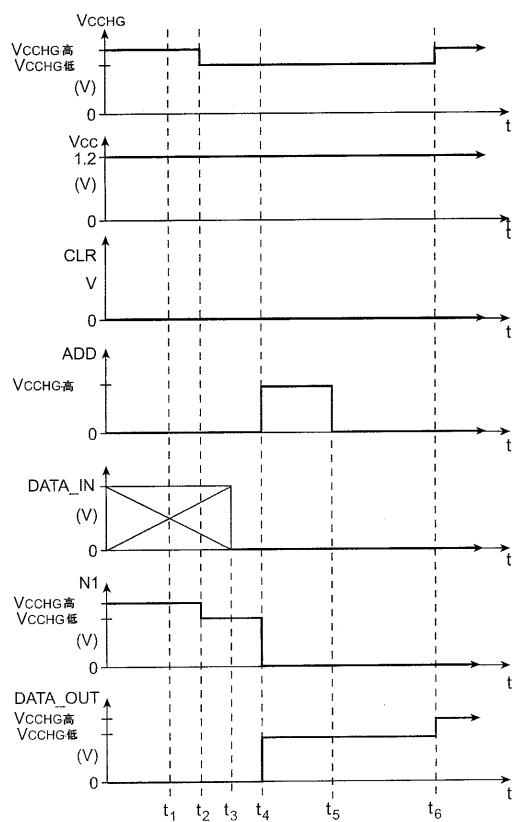

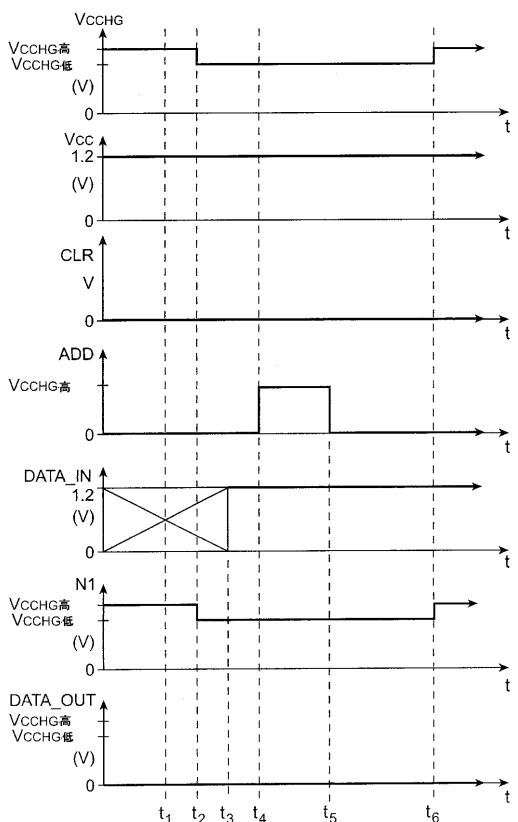

図9および図10は、書き込み動作の間に使用され得る例示的電圧を示す。図9および図10の実施例においては、アレイにおけるメモリ要素82のための正の電源電圧Vcchgは、アドレス信号がアサートされる期間の間、Vcchg高の高値(例えば、1.6ボルト)からVcchg低の低値(例えば、1.2ボルト)に下げられる。これは、メモリ要素82の性能を改良するのに役に立つ。図9は、ロジック1をメモリ要素に書き込むために含まれる信号を示す。図10は、ロジック0をメモリ要素に書き込むために含まれる信号を示す。

#### 【0097】

ライン108からのデータがメモリ要素82に駆動され得るように、成功のデータ書き込み動作は、アドレストランジスタ132がトランジスタ124およびインバータ118より強くあることを要求する。Vcchgが下げられた場合、トランジスタ124の強さは弱められる。その結果、アドレストランジスタ132は、そうでなければ要求されているように強くある必要はない。Vcchgを下げることは、従って、メモリ要素82のための書き込みマージンを増加させ、および/またはアドレストランジスタ132に対するリアルエステート要求を減らす。設計考慮によって、下げられたVcchg値は、設計者が各アドレストランジスタ132によって消費されるリアルエステートを減らすことを可能にするために使用され得(そのゲート幅を減らすことによって)、書き込みマージンを増加させるために使用され得(書き込みの間エラーが生じないことを確実にすることに役立たせるためにアドレストランジスタ132の改良された強さを使用することによって)、またはリアルエステートを減らし書き込みマージンを増加させるために使用され得る。

20

#### 【0098】

アドレス信号ADDがアサートされた場合、その電圧は0ボルト(Vss)から高レベルへと増加する。図9および図10の実施例においては、高レベルはVcchg高である(例えば、1.6ボルト)。書き込み動作の間の高アドレス信号の使用は、書き込みの間にアドレストランジスタ132のゲートGに印加される電圧の大きさを増加させる。本実施例においては、書き込み動作の間にアドレスされているアドレストランジスタ132のゲートに印加される電圧は、Vcchg高である(1.6ボルト)。トランジスタ132を制御するためのVcchg高の高値の使用は、Vccのより低い従来電圧の使用と比較してより多くトランジスタ132をターンオンする。Vcchg高の高アドレス信号値は、従って、所定のサイズ(ゲート幅)に対するトランジスタ132の強さを効率的に増加させるために役に立つ。

30

#### 【0099】

高アドレス信号レベルを使用して得られたアドレストランジスタ132の実効的な強さにおける増加は、メモリ要素82の書き込みマージンを更に増加させ、および/またはトランジスタ132に対するリアルエステート要求を減らすために役に立つ。

40

#### 【0100】

図9においては、メモリ要素82は、最初にクリアにされ、ロジック1を用いてロードされる。図9の最も下のトレースにおいて示されるように、アドレス信号ADDがアサートされた場合、DATA\_OUTライン上の信号は、従って、低から高へと上昇する。

50

## 【0101】

アレイ 88 の全体がこのような方法においてデータを用いてロードされた後、電圧  $V_{cchg}$  は、  $V_{ccchg}$  高のその高レベル（例えば、1.6 ボルト）に上昇され得る。これは、ロジック 1 を含むメモリ要素 82 の出力が、  $V_{cc}$  のプログラマブルコアロジック正の電源電圧より大きい電圧（例えば、1.2 ボルト）におけるプログラマブルコアロジックに提供されようにし、それによって性能を改良する。

## 【0102】

図 9 の第 1 のトレースは、アレイ 88 におけるメモリ要素 82 に電力供給するために電力調節器回路網 84（図 6）によってライン 86 に印加される電源電圧  $V_{ccchg}$  が、  $V_{ccchg}$  高の高値と  $V_{ccchg}$  低の減少した値との間において変化することを示す。  $V_{ccchg}$  低は、例えば、  $V_{cc}$  に対して等しくなり得る。正の電源電圧  $V_{ccchg}$  は、インバータ 116 および 118 に印加される。  $V_{ccchg}$  の値は、時間  $t_1$  においては高い（この実施例において）。コンフィギュレーションデータビットをメモリ要素 82 にロードすることが望まれた場合、電力調節器回路網 84 は、  $V_{ccchg}$  の値を  $V_{ccchg}$  高から  $V_{ccchg}$  低へと減らす（時間  $t_2$ ）。アレイ 88 の全ての列がコンフィギュレーションデータを用いてロードされた後、電力調節器回路網 84 は、  $V_{ccchg}$  の値を  $V_{ccchg}$  低へと上げる（時間  $t_6$ ）。  $t_6$  の後に時間において、集積回路 10 は正常に動作し、各メモリ要素 82 は  $V_{ss}$ （ロジック 0 が格納された場合）または  $V_{ccchg}$  高（ロジック 1 が格納された場合）の値において静的出力信号を生成している。

## 【0103】

図 9 の第 2 のトレースに示されるように、  $V_{cc}$  の値は、この実施例においては、1.2 ボルトのまま一定に残る。電源電圧  $V_{cc}$  は、例えば、プログラマブルコアロジック 18 のような電力回路網ならびにデータローディング・読み取り回路網 96（図 6）に使用され得る。望まれた場合、他の電源電圧がプログラマブルロジックデバイス 10 において使用され得る。例えば、より高い電圧  $V_{ccio}$  は、入力 - 出力回路網 12（図 1）に電力供給するために使用され得る。不必要的複雑性を回避するために、  $V_{ccio}$  のような電圧を供給する回路網は、他の高電圧を提供するために使用され得る。例えば、  $V_{ccchg}$  高および  $V_{ccio}$  は、同等の電源によって提供され得、またはその同等の電圧源から引き出され得る。

## 【0104】

図 9 の第 3 のトレースによって示されるように、クリアリング動作がシステム起動時の間に実行された後、ライン 104 上のクリア信号 CLR は 0 ボルトにおいて一定である。

## 【0105】

図 9 の第 4 のトレースは、アドレスライン ADD が時間  $t_4$  においてどのようにアサートされ、時間  $t_5$  においてどのようにデアサートされたかを示す。本発明に従って、アドレス信号は、  $V_{ss}$  の低い値から高値まで変化する。図 9 の実施例においては、高アドレス信号は、  $V_{ccchg}$  高の大きさを有する。

## 【0106】

図 9 の第 5 のトレースは、ライン 108 上の DATA\_IN の値が  $t_3$  の前の時間  $t$  において規定されていないことを示す。時間  $t_3$  において、データローディング回路網 96 は、低 DATA\_IN 信号（図 9 の実施例において）を生成する。

## 【0107】

アドレスライン ADD が  $t_4$  において高められると、トランジスタ 132（図 7）はターンオンされ、それによって低 DATA\_IN ライン 108 はノード N1 に接続される。ADD の高値は、時間  $t_4$  においてアドレストランジスタ 132 を強くターンオンすることに役に立つ。

## 【0108】

ノード N1 における電圧は、図 9 の第 6 のトレースにおいて示される。時間  $t_1$  において、インバータ 116 および 118 は、  $V_{ccchg}$  高（この実施例において）において電力供給され、ノード N1 における電圧は  $V_{ccchg}$  高である。時間  $t_2$  においては、電圧

10

20

30

40

50

$V_{cchg}$  は、 $V_{cchg}$  高から $V_{cchg}$  低まで下がる（トレース 1）。 $V_{cchg}$  におけるこの降下は、更に $V_{cchg}$  高から $V_{cchg}$  低に下がるノード N 1 における電圧に反映される。時間  $t_4$  においては、トランジスタ 132 が高 ADD 信号によってターンオンされ、低 DATA\_IN ラインがノード N 1 に接続された場合、ノード N 1 における電圧は下げられる。

#### 【0109】

ノード N 2 における電圧およびライン 130 上の出力電圧 (DATA\_OUT) が時間  $t_4$  において高められるように、ノード N 1 における低電圧は、インバータ 116 によって反転される。これは、メモリ要素の単一の列のプログラミングを完成させ、それによって ADD は時間  $t_5$  においてアサートされる。

10

#### 【0110】

$V_{cchg}$  のレベルは一般に、メモリ要素の各列がロードされる度に低いまま残る。メモリ要素 82 の全ての所望の列がコンフィギュレーションデータを用いてロードされた後、電力調節器回路網 84 は、 $V_{cchg}$  を $V_{cchg}$  低から $V_{cchg}$  高にまで上げる（時間  $t_6$ ）。

#### 【0111】

電源電圧  $V_{cchg}$  高がインバータ 116 および 118 に印加されると、ライン 130 上の DATA\_OUT 信号は  $V_{cchg}$  高の電圧レベルにある。DATA\_OUT 信号は高くされ（この例において  $V_{cchg}$  高は、 $V_{cc}$  および  $V_{cchg}$  低に対しては 1.2 ボルトであるのに比べ、1.6 ボルトである）、それによってトランジスタ 136（図 7）のような図 6 のプログラマブルコアロジック 18 の構成要素に印加される静的高出力信号は、これらの構成要素を満足に制御するのに十分に高い（例えば、n チャネルデバイスに対する抵抗は低く、p チャネルデバイスに対する漏れ電流は低い）。

20

#### 【0112】

アドレス信号 ADD が時間  $t_4$  においてアサートされた場合に使用される  $V_{cchg}$  の下げられた値（ $V_{cchg}$  低）および ADD の高値（ $V_{cchg}$  高）は、NMOS トランジスタ 132 および PMOS トランジスタ 124 の相対的強さにおける要求を緩和する。ADD が高くされなかつた場合（および  $V_{cchg}$  が下げられなかつた場合）、より大きい NMOS トランジスタ 132 およびより大きい付随の信号ラインは、PMOS トランジスタ 124 が克服され得ることを確実にし、データローディング動作に関連する IR 降下が過度にならないことを確実にするために要求されるはずである。アドレス信号が高くされ、データローディングの間に電源レベルが下げられた場合、NMOS トランジスタ 132 に対する強さ要求およびリアルエステート要求は減少される。

30

#### 【0113】

図 10 のトレースは、ロジック 0 をクリアされたメモリ要素 82（図 7）にロードする処理を示す。この状況において、メモリ要素 82 はロジック 0 を含み、それによってローディング処理はその状態を変化させない。

#### 【0114】

図 10 の第 1 のトレースは、電力調節器回路網 84（図 7）によってライン 86 に印加される電源電圧  $V_{cchg}$  が、図 9 に関連して説明されるように、 $V_{cchg}$  高の高値と  $V_{cchg}$  低の減少した値との間で変化することを示す。 $V_{cchg}$  の値は時間  $t_1$  において高い。時間  $t_2$  において、電力調節器回路網 84 は、コンフィギュレーションデータローディングに備えて  $V_{cchg}$  の値を  $V_{cchg}$  高から  $V_{cchg}$  低へと減少させる。時間変化電源電圧  $V_{cchg}$  は、アレイ 88（図 6）が完全にロードされるまで低いまま残り得る。アレイ 88 がコンフィギュレーションデータを用いてロードされた後、電力調節器回路網 84 は、 $V_{cchg}$  の値を  $V_{cchg}$  高に上げる（時間  $t_6$ ）。

40

#### 【0115】

図 10 の第 2 のトレースに示されるように、 $V_{cc}$  の値は 1.2 ボルトにおいて一定のまま残る（この実施例において）。

#### 【0116】

50

図10の第3のトレースによって示されるように、クリアリング動作がシステム起動時に実行された後、ライン104上のクリア信号CLRは0ボルトにおいて一定である。

【0117】

図10の第4のトレースは、アドレスラインADDがどのようにして時間 $t_4$ においてアサートされ、時間 $t_5$ においてデアサートされるかを示す。アドレス信号の値は、0ボルトの低い値(Vss)からVcchg高の高い値までの範囲にある。この高電圧を使用することは、アドレストランジスタ132を強くターンオンすることに役に立ち、それによってアドレストランジスタ132に対するリアルエステート要求を減少させ、および/またはメモリ要素に対する書き込みマージンを増加させる。

【0118】

図10の第5のトレースは、ライン108上のDATA\_INの値が $t_3$ の前の時間 $t$ において規定されていないことを示す。時間 $t_3$ において、データローディング回路網96は、高DATA\_IN信号を生成する。

【0119】

アドレスラインADDが時間 $t_4$ においてアサートされた場合、アドレス信号はVcchgのその高い値にまで上がる。これは、トランジスタ132(図7)をターンオンし、高DATA\_INライン108をノードN1に接続する。ノードN1における電圧は、図10の第6のトレースに示される。時間 $t_3$ において、メモリ要素32は、そのクリアされた状態にある。この状態において、ノードN2における電圧は接地にある。インバータ116および118は、時間 $t_3$ においてVcchg低の電圧にて電力供給され、それによってノードN1における反転されたN2電圧はVcchg低である。時間 $t_4$ において、アドレスラインがVcchg高に高められると、トランジスタ132はターンオンされ、高DATA\_INラインはノードN1に接続される。図10の第7のトレースに示されるように、ノードN1は既に高く、データ出力ラインDATA\_OUTの状態は低いまま残り、時間 $t_4$ においてその状態を変化させない。

【0120】

ロジック0ビットのメモリ要素82へのデータローディングは、時間 $t_5$ においてアドレスラインADDをデアサートすることによって完成される。アレイ88の全ての列がこの方法においてコンフィギュレーションデータを用いてロードされた後、電力調節器回路網84は、時間 $t_6$ においてVcchgをVcchg低からVcchg高まで上げる。

【0121】

デバイス10がこの分野において使用される前、コンフィギュレーションデータがアレイに適切にロードされたことを検証することが通常望まれる。データが適切にロードされたことを確認するため、データはライン108を通じてアレイから読み取られる。この方法において読み出されたデータがロードされたデータと同じであった場合、デバイスは適切にプログラムされ、システムにおいて使用され得る。読み出されたデータが意図されるコンフィギュレーションデータと異なる場合、エラーが生じている。

【0122】

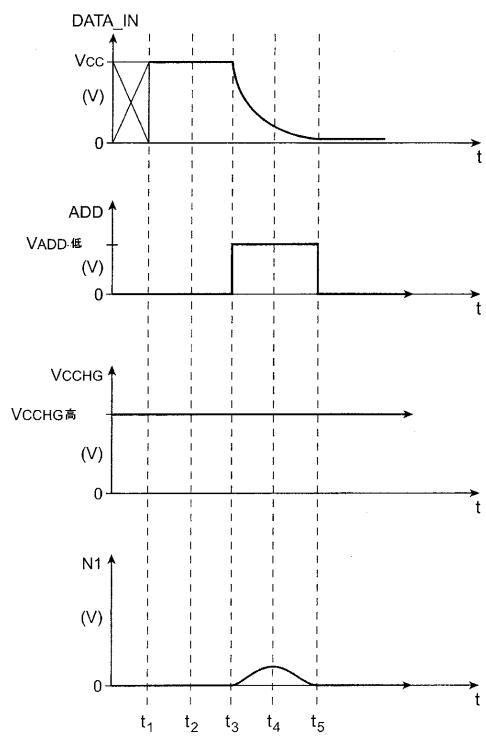

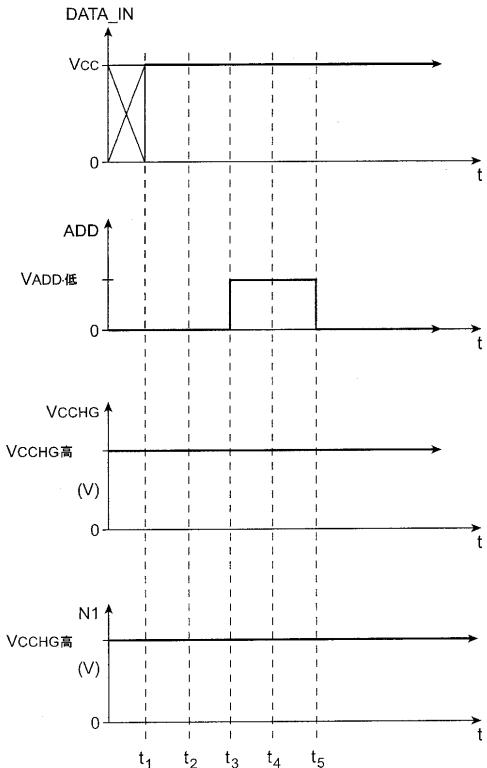

コンフィギュレーションデータが適切にロードされたことを確認する場合に実行され得るデータ読み取り動作は、図11および図12に示される。図11は、ロジック1を読み取るために含まれる動作を示す。図12は、ロジック0を読み取るために含まれる動作を示す。

【0123】

読み取り動作の間、アドレス信号ADDは、組織的に、アレイ88の列をアドレスするために高められる。読み取り動作の間に使用されるアドレス信号ADDは、好ましくは、メモリ要素の読み取りマージンを改良するために比較的低い(すなわち、ADDは書き込み動作の間より読み取り動作の間の方が小さい)。

【0124】

図11においては、メモリ要素はロジック1を含む(すなわち、N1は0であり、メモリ要素はプログラムされていることが想定される)。

10

20

30

40

50

## 【0125】

図11の第1の(最も上の)トレースに示されるように、信号DATA\_INの電圧は最初に、データ読み取り動作に備えてVccの高電圧(例えば、1.2ボルト)にある。時間t<sub>1</sub>の前の時間において、DATA\_IN信号は無効である。時間t<sub>1</sub>において、図6のデータローディング・読み取り回路網96は、DATA\_INを強く高める。時間t<sub>2</sub>において、データローディング・読み取り回路網96は、DATA\_INを高に緩く保つ。時間t<sub>3</sub>においては、図11の第2のトレースに示されるように、アドレス信号ADDは、ADDを0ボルトからVadd低にすることによってアサートされる。例えば、Vadd低の値は、1.2ボルトの電圧(Vcc)であり得る。図11の第3のトレースに示されるように、データ読み取り動作の間、メモリ要素82は、Vcchg高の高い正の電源電圧(例えば、1.6ボルト)を使用して電力供給され得る。

10

## 【0126】

ADDを時間t<sub>3</sub>において高めることは、トランジスタ132(図7)をターンオンする。t<sub>3</sub>とt<sub>5</sub>との間の時間において、トランジスタ132はオンのまま残り、それによってDATA\_INライン108上の緩く保たれた高電圧は、インバータ118の出力にさらされる。ノードN2は高く、それによってトランジスタ126はオンであり、インバータ118の出力はノードN1に低電圧を駆動させる。トランジスタ126(図7)は、DATA\_INライン108上に緩く保たれた「1」より強く、それによってDATA\_IN信号の値は、図11の第1のトレースに示されるように、約0ボルトにまで落ちる。時間t<sub>4</sub>において、データローディング・読み取り回路網96(図1)はDATA\_IN信号の低電圧を検出し、従ってN1における電圧が低く、かつメモリ要素がロジック1を含んでいたと推断し得る(この実施例において)。

20

## 【0127】

図11の第4のトレースに示されるように、ノードN1における電圧は、アドレストランジスタ132が時間t<sub>3</sub>においてADD信号によってターンオンされた場合、瞬間に増加される。図11の第4のトレースに示される、N1における上昇は望ましくない。この上昇が大きくなりすぎた場合、インバータ116はノードN2に「0」を駆動させ、メモリ要素82の状態はフリップする。ADD信号の電圧(すなわち、この例においては1.2ボルトの信号Vadd低)が比較的低いため、トランジスタ132は強すぎることなくターンオンされる。結果的に、電圧N1における望まれない上昇のピークは上手く制御され、フリップは生じない。

30

## 【0128】

図12において、メモリ要素はロジック0を含む(すなわち、N1は高く、N2は低く、メモリ要素はクリアされたと想定される)。

## 【0129】

図12における第1の(最も上の)トレースに示されるように、t<sub>1</sub>の前の時間においては、DATA\_IN信号は無効である。時間t<sub>1</sub>においては、図6のデータローディング・読み取り回路網96は、DATA\_INを強く高める。時間t<sub>2</sub>においては、データローディング・読み取り回路網96は、DATA\_INを高に緩く保つ。図12の第2のトレースに示されるように、時間t<sub>3</sub>において、アドレス信号ADDは、ADDを0ボルトからVadd低(例えば、Vcc)にすることによってアサートされる。図12の第3のトレースに示されるように、メモリ要素82は、Vcchg高の高い正の電源電圧(例えば、1.6ボルト)を使用して電力供給され得る。時間t<sub>3</sub>においてADDを高めるることは、トランジスタ132(図7)をターンオンする。

40

## 【0130】

nチャネル酸化金属半導体アドレストランジスタ132がt<sub>3</sub>とt<sub>5</sub>との間の時間にターンオンされた場合、信号はノードN1からノード133へ流れることが可能である(図7)。VcchgがVcchg高に上昇されるため、時間t<sub>3</sub>におけるノードN1の電圧は、DATA\_INライン108上の緩く保たれた電圧Vccより高いVcchg高である。アドレストランジスタ132のゲートGは、Vadd低のアドレス信号電圧(Vcc

50

)において維持される。トランジスタ 132 のような酸化金属半導体トランジスタの性質のため、ノード N1 および 133 における電圧が、アドレスライン 112 における電圧(ゲート G)から NMOS トランジスタ 132 のしきい値電圧  $V_t$  を引いたものより高い場合、トランジスタ 132 はオフされ、ノード N1 および 133 を絶縁する。 $t_3$  の前の時間における、緩く保たれた DATA\_IN ライン 108 の電圧レベルは、従って、時間  $t_3$  において変化しないまま残る。それによって、時間  $t_3$  において、ノード N1 の電圧における変化は無い。時間  $t_4$  において、データローディング・読み取り回路網 96(図 6)は、DATA\_IN 信号の高電圧を検出し、N1 における電圧が高く、かつメモリ要素がロジック 0 を含んでいたと推断する。図 12 の第 2 のトレースに示されるように、アドレス信号は時間  $t_5$  においてデアサートされる。

10

#### 【0131】

図 12 の第 4 のトレースに示されるように、ノード N1 における電圧は、アドレス信号が高いにも関らず、 $t_3$  から  $t_5$  の時間の間ににおいて一定の  $V_{cchg}$  高のまま残る。これは、ゲート電圧 G が  $V_{add}$  低の比較的低いアドレス信号電圧 ( $V_{cc}$ ) においてキャプされるためである。ゲート電圧 G に課された上限は、インバータ 118 によって出力ノード 133 に駆動される最大限の電圧を制限する。それによって、電圧 N1 は読み取り動作の間、上手く制御されている。

#### 【0132】

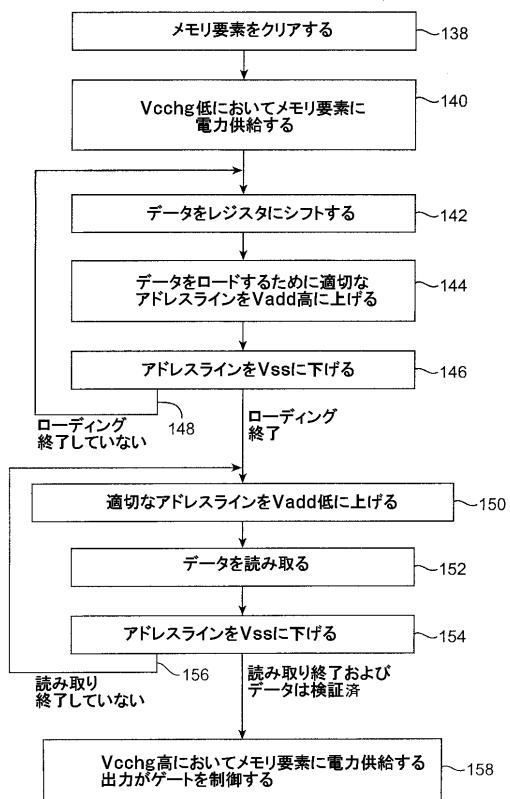

プログラマブルロジックデバイス集積回路 10 におけるメモリ要素 82 を動作するため 20 に含まれるステップのフローチャートは、図 13 に示される。

#### 【0133】

ステップ 138 において、メモリ要素は、クリアライン 104 を使用してデータローディングに備えてクリアされる。

#### 【0134】

ステップ 140 において、メモリ要素 82 は、 $V_{cchg}$  低のような電源電圧(例えば、1.2 ボルト)を使用して電力供給され得る。図 9 および図 10 の第 1 のトレースに示されるように、この値は、コンフィギュレーションデータローディング動作に備えて既存の  $V_{cchg}$  高の比較的高い値から減少され得る。代替的に、アレイ 88 は、 $V_{cchg}$  低の正の電源電圧を使用して電力供給され得る。アレイ 88 が  $V_{cchg}$  低を使用して電力供給された場合、この比較的低い正の電源電圧は、プログラミングを容易にするためにデータローディング動作の間、維持され得る。

30

#### 【0135】

ステップ 142 において、コンフィギュレーションデータは、入力 106 を介して読み取り・書き込み回路網 115 のレジスタ 117 にシフトされる(図 6)。

#### 【0136】

ステップ 144 において、制御信号は、入力 110 にて図 6 のアドレス復号器 102 に印加される。制御信号は、所望のアドレスライン 112 がアレイ 88 におけるメモリ要素の列をアドレスすることをアサートするようにアドレス復号器 102 に命令する。それに応答して、アレイにおけるアドレスライン 112 の 1 つは、アレイ 88 におけるメモリ要素 82 の対応する列をアドレスするようにアサートされる。アドレス信号 ADD は、好ましくは、図 9 および図 10 に関連して説明されるように、 $V_{ss}$  の低い値(例えば、0 ボルト)から  $V_{cchg}$  高の高値(例えば、1.6 ボルト)になる。

40

#### 【0137】

ステップ 144 の間に使用される高 ADD 信号電圧の比較的高い値(例えば、 $V_{cchg}$  高)およびメモリ要素アレイの正の電源電圧の比較的低い値(例えば、 $V_{cchg}$  低)は、アドレストランジスタ 132 に対するリアルエステート要求を減らし、および/またはメモリ要素のための書き込みマージンを増加させるのに役立つ。

#### 【0138】

ステップ 146 において、メモリ要素のアドレスされた列に対するコンフィギュレーションデータがデータライン 108 を介してアレイ 88 にロードされた後、アドレスライン

50

112はデアサートされる（例えば、図9および図10に関連して説明されるように、アドレスラインの電圧をそのV<sub>cchg</sub>高の高レベルからV<sub>ss</sub>の接地電圧に下げるこ<sub>10</sub>とによって）。

【0139】

ライン148によって示されるように、データローディング・読み取り回路網96がアレイ88における全てのアドレスライン112を組織的にアサートし、アレイ88の全てのメモリ要素82がロードされるまで、コンフィギュレーションデータローディング処理は続く。

【0140】

アレイ88がコンフィギュレーションデータを用いて完全にロードされた後、電力調節器回路網84は、データ確認動作に備えてメモリ要素の正の電源電圧をV<sub>cchg</sub>高に増加させ得る。

【0141】

ステップ150において、データローディング・読み取り回路網96は、アドレスライン112の1つをアサートする。アドレスライン112は、メモリ要素82の読み取りマージンを改良するのに役に立つため、好ましくは、その電圧をV<sub>ss</sub>から比較的低い値V<sub>add</sub>低（例えば、V<sub>cc</sub>）に上げられる。図11および図12に関連して説明されるように、メモリ要素のアドレスされた列にロードされたデータは、データローディング・読み取り回路網96によってメモリ要素から読み出される（ステップ152）。

【0142】

ステップ154において、アサートされたアドレスラインは、その電圧をV<sub>add</sub>低からV<sub>ss</sub>に減らすことによってデアサートされる。

【0143】

ライン156に示されるように、データローディング・読み取り回路網96がアレイ88から全てのロードされたコンフィギュレーションデータを組織的に読み出すまで、データ読み取り動作は続く。読み出されたデータは、ロードされたデータと比較される。ロードされたデータと読み出されたデータとの間に矛盾があった場合、訂正処置がとられ得る。

【0144】

データ確認処理が成功した場合、プログラマブルロジックデバイス集積回路10は、システム内の通常動作に使用され得る（ステップ158）。通常動作の間、電力調節器回路網84は、プログラマブルコアロジック18に電力供給するために使用される電源レベルよりも高い電源レベルにおいてアレイ88に電力供給する。例えば、メモリ要素82は、V<sub>cchg</sub>高およびV<sub>ss</sub>において電力供給され得る。このように電力供給された場合、ロジック0を含むメモリ要素82は、V<sub>ss</sub>におけるそれらのDATA\_OUT端子にて制御信号を生成し、ロジック1を含むメモリ要素82は、V<sub>cchg</sub>高におけるそれらのDATA\_OUT端子にて制御信号を生成する。V<sub>cchg</sub>高の大きさは、性能を強化するプログラマブルコアロジック18に電力供給するために使用される電圧V<sub>cc</sub>より大きい。

【0145】

図13に関連して説明される例示的構成においては、メモリアレイ88は、V<sub>cchg</sub>の時間変化する正の電源電圧およびV<sub>ss</sub>の接地電圧を提供するダイナミック電力調節器回路網によって電力供給される。電源電圧V<sub>cchg</sub>は、通常動作の間およびデータ読み取り動作の間、V<sub>cchg</sub>高に高くされる。電源電圧V<sub>cchg</sub>は、データ書き込み動作の間V<sub>cchg</sub>低に減少される。一般に、V<sub>cchg</sub>高およびV<sub>cchg</sub>低は、任意の適した電圧であり得る。V<sub>cchg</sub>低に対する1つの適した電圧は、すぐに利用可能な電源電圧V<sub>cc</sub>である。望まれた場合、しかしながら、V<sub>cchg</sub>低はV<sub>cc</sub>より低くまたは高くあり得る。V<sub>cchg</sub>低の値は、例えば、1.2ボルトであり得、もしくはより低いまたはより高い値が使用され得る。V<sub>cchg</sub>高は、1.6ボルトであり得（例えば、V<sub>cc</sub>が1.2ボルトであった場合）、1.2ボルトから1.4ボルトの間であり得、1.

10

20

30

40

50

2 ボルトから 1.6 ボルトの間であり得、1.6 ボルトより大きくあり得、または 1.2 ボルトより少なくあり得る（すなわち、V<sub>CC</sub> が 1.2 ボルトより少ない場合）。

#### 【0146】

V<sub>CCHG</sub> の値を必要に応じて上げること、および下げるとは、アレイにおけるアドレストランジスタに対する減少したリアルエステート要求および増加された書き込みマージンのような利益を提供する。望まれた場合、しかしながら、V<sub>CCHG</sub> の固定値が使用され得る。例えば、V<sub>CCHG</sub> の値は、V<sub>CC</sub> において固定され得、または高レベル（例えば、V<sub>CC</sub> が 1.2 ボルトにおいて固定されている場合、1.6 ボルト）において固定され得る。データ書き込み動作およびデータ読み取り動作の間にアドレス信号に対する異なる最大限電圧レベルを使用する利益は、どの種類のメモリ要素電源電圧スキームが使用されるにも関らずに得られうる。

#### 【0147】

適切なアドレス動作は、アドレス信号が所定の範囲内に入ることを要求する。データ書き込み動作の間の V<sub>CCHG</sub> 高の高アドレス信号およびデータ読み取り動作の間の V<sub>CC</sub> の低信号の使用は、単に例示である。

#### 【0148】

概して、2段階の電源電圧 V<sub>CCHG</sub> (V<sub>CCHG</sub> 高 / V<sub>CCHG</sub> 低) が使用された場合、V<sub>CCHG</sub> 高の高アドレス信号電圧は好都合である。なぜなら、V<sub>CCHG</sub> 高は、集積回路 10 において既に利用可能であるからである。望まれた場合、V<sub>CCHG</sub> 高より低いまたは高い高アドレス電圧 V<sub>ADD</sub> 高が使用され得る。同様に、V<sub>CCHG</sub> 低の値およびデータライン信号が V<sub>CC</sub> にある場合、V<sub>CC</sub> のデータ読み取りアドレス信号電圧の使用は好都合である。望まれた場合、V<sub>ADD</sub> 低は、V<sub>CC</sub> より低くまたは高くあり得る。書き込みマージン（および / またはアドレストランジスタリアルエステート要求）および読み取りマージンが同時に改良され得るように、V<sub>ADD</sub> 低は通常 V<sub>ADD</sub> 高より低い。

#### 【0149】

V<sub>CCHG</sub> 高の正の電源電圧および V<sub>SS</sub> の接地電圧を使用してメモリ要素電源を高くさせることは、通常満足のいくことである。望まれた場合、しかしながら、高電源電圧は、他の構成を使用して電力調節器回路網 84 によって提供され得る。例えば、高電源レベルは、V<sub>CC</sub> における正の電源電圧および V<sub>SS</sub> より少ない接地電源電圧を使用して提供され得る。この種類の構成において、メモリ要素電源電圧は、メモリ要素の正の電源電圧とメモリ要素接地との間の差異が V<sub>CC</sub> と V<sub>SS</sub> との間の差異より大きいため、高くされる（プログラマブルコアロジック 18 の回路網に電力供給するために使用される電源レベル）。集積回路 10 に使用される酸化金属トランジスタ（例えば、メモリ要素トランジスタ）のしきい値電圧は、望まれた場合、シフトされた正の電源電圧および接地電源電圧に適合するように修正され得る。

#### 【0150】

固定された、単一レベルの電源電圧 V<sub>CCHG</sub> がメモリアレイのために使用された場合、高アドレス信号 V<sub>ADD</sub> 高は、V<sub>CCHG</sub> より大きく、または V<sub>CCHG</sub> より小さくあり得る。メモリ要素電源電圧が V<sub>CC</sub> において固定された場合、データ書き込み動作の間に使用されるアドレス信号 V<sub>ADD</sub> 高は、V<sub>CC</sub> より大きくあり得る。アドレス信号 V<sub>ADD</sub> 低は、V<sub>ADD</sub> 高より通常少ない。電圧 V<sub>CC</sub> が集積回路においてすぐに利用可能であるため、V<sub>CC</sub> の V<sub>ADD</sub> 低レベルは通常適している。望まれた場合、しかしながら、V<sub>ADD</sub> 低は V<sub>CC</sub> より低くまたは高くあり得る。

#### 【0151】

D A T A \_ I N ライン 108 上のデータ信号のために使用される電圧は、典型的に V<sub>CC</sub> である。なぜなら、これがコアロジック 18 におけるロジック信号によって使用される電圧だからである。望まれた場合、データ信号は、より高いまたはより低い値を使用し得る。

#### 【0152】

メモリ要素のインバータにおいては、n チャネルおよび p チャネル酸化金属半導体トランジスタ

10

20

30

40

50

ンジスタに関連するしきい値電圧  $V_{t\ n}$  および  $V_{t\ p}$  がある。インバータの適切な動作は、インバータ電圧が  $V_{t\ n}$  と  $V_{t\ p}$  との総計を超えることを要求する。 $V_{t\ n}$  と  $V_{t\ p}$  との総計は、時々  $V_{function}$  と呼ばれる。一般に、 $V_{cch\ g}$  低は、メモリ要素が適切に動作するために  $V_{function}$  の上にあるべきである。 $V_{add}$  低の値は、好みしくは、 $V_{function}$  より大きく、 $V_{cch\ g}$  高より少ない。

#### 【0153】

上記記載は、本発明の原理の例示に過ぎず、様々な修正が本発明の範囲および精神から逸脱せずに当業者によって行われ得る。

#### 【0154】

プログラマブルロジックデバイス集積回路が提供される。プログラマブルロジックデバイス集積回路は、プログラマブルコアロジック電源電圧において電力供給されたプログラマブルコアロジックを含む。プログラマブルロジックデバイスコンフィギュレーションデータは、プログラマブルコアロジックがカスタムロジック機能を実行するように構成するためにメモリ要素にロードされる。通常動作の間、メモリ要素は、プログラマブルコアロジック電源電圧より大きい電源電圧を用いて電力供給され得る。データローディング動作の間、メモリ要素は、プログラマブルコアロジック電源電圧と等しい電源電圧を用いて電力供給され得る。データローディング・読み取り回路網は、メモリ要素にデータをロードし、メモリ要素からデータを読み取る。アドレス信号は、データローディング・読み取り回路網によって生成される。アドレス信号は、読み取り動作の間よりデータ書き込み動作の間においてより大きい電圧レベルを有し得る。

10

20

#### 【0155】

以上のように、本発明の好みしい実施形態を用いて本発明を例示してきたが、本発明は、この実施形態に限定して解釈されるべきものではない。本発明は、特許請求の範囲によつてのみその範囲が解釈されるべきであることが理解される。当業者は、本発明の具体的な好みしい実施形態の記載から、本発明の記載および技術常識に基づいて等価な範囲を実施することができることが理解される。

#### 【図面の簡単な説明】

#### 【0156】

【図1】本発明に従つた、例示的プログラマブルロジックデバイス集積回路の図である。

【図2】プログラマブルロジックデバイスマモリ要素の従来のアレイの図である。

30

【図3】従来のプログラマブルロジックデバイスマモリ要素の図である。

【図4】従来のプログラマブルロジックデバイスマモリセルがどのようにしてロジック1の値を有するコンフィギュレーションデータビットを用いてロードされるかを示すタイミング図である。

【図5】従来のプログラマブルロジックデバイスマモリセルがどのようにしてロジック0の値を有するコンフィギュレーションデータビットを用いてロードされるかを示すタイミング図である。

【図6】本発明に従つた、メモリ要素回路網を有する例示的プログラマブルロジックデバイスの図である。

【図7】本発明に従つた、図6に示される種類のプログラマブルロジックデバイス集積回路のような集積回路のための例示的メモリ要素の図である。

40

【図8】本発明に従つた、例示的読み取り・書き込み回路網の回路図である。

【図9】本発明に従つた、図7に示される種類のプログラマブルロジックデバイスマモリ要素がどのようにしてロジック1の値を有するコンフィギュレーションデータビットを用いてロードされるかを示すタイミング図である。

【図10】本発明に従つた、図7に示される種類のプログラマブルロジックデバイスマモリ要素がどのようにしてロジック0の値を有するコンフィギュレーションデータビットを用いてロードされるかを示すタイミング図である。

【図11】本発明に従つた、図7に示される種類のプログラマブルロジックデバイスマモリ要素がどのようにしてロジック1の値を有するコンフィギュレーションデータビットの

50

適切なローディングを確認するために読み取られるかを示すタイミング図である。

【図12】本発明に従った、図7に示される種類のプログラマブルロジックデバイスマモリ要素がどのようにしてロジック0の値を有するコンフィギュレーションデータビットの適切なローディングを確認するために読み取られるかを示すタイミング図である。

【図13】本発明に従った、図7に示される種類のプログラマブルロジックデバイスマモリ要素のアレイを使用することに含まれた例示的ステップのフローチャートである。

【符号の説明】

【0157】

10、18 プログラマブルロジック

20、82 メモリ要素

96 データローディング・読み取り回路網

10

【図1】

FIG. 1

【図2】

(従来技術)

FIG. 2

【図3】

(従来技術)

FIG. 3

【図4】

(従来技術)

FIG. 4

【図5】

(従来技術)

FIG. 5

【図6】

FIG. 6

【図7】

【図8】

【図9】

【図10】

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

FIG. 13

---

フロントページの続き

(72)発明者 リン - シー リュー

アメリカ合衆国 カリフォルニア 94539, フレモント, エクセルソ プレイス 436

54

(72)発明者 マーク ティー. チャン

アメリカ合衆国 カリフォルニア 95134, サン ホセ, デスカンソ ドライブ 80

ナンバー 1424

審査官 宮島 郁美

(56)参考文献 特開2003-218212(JP, A)

国際公開第2005/034175(WO, A1)

特開2002-107424(JP, A)

特開平10-144870(JP, A)

特開2002-368135(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K19/098-19/23

G11C11/34-11/40