(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4264866号

(P4264866)

(45) 発行日 平成21年5月20日(2009.5.20)

(24) 登録日 平成21年2月27日(2009.2.27)

(51) Int.Cl.

F 1

G 06 F 13/00 (2006.01)

H 04 L 29/06 (2006.01)G 06 F 13/00 353 C

H 04 L 13/00 305 A

請求項の数 28 (全 35 頁)

|               |                               |           |                                                                                              |

|---------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2000-568012 (P2000-568012)  | (73) 特許権者 | 501082978<br>アラクリテック・インコーポレイテッド<br>アメリカ合衆国, カリフォルニア州・95<br>012, サン・ノゼ, イースト・ギッシュ<br>・ロード・234 |

| (86) (22) 出願日 | 平成10年11月20日(1998.11.20)       | (74) 代理人  | 100098062<br>弁理士 梅田 明彦                                                                       |

| (65) 公表番号     | 特表2002-524005 (P2002-524005A) | (72) 発明者  | ブーチャー, ローレンス, ビー<br>アメリカ合衆国, カリフォルニア州・95<br>070, サラトガ, モントルボ・ドライブ<br>・20605                  |

| (43) 公表日      | 平成14年7月30日(2002.7.30)         | (72) 発明者  | ブライトマン, スチーブン, イー, ジェイ<br>アメリカ合衆国, カリフォルニア州・95<br>132, サン・ノゼ, アーレン・コート・<br>3733              |

| (86) 國際出願番号   | PCT/US1998/024943             |           |                                                                                              |

| (87) 國際公開番号   | W02000/013091                 |           |                                                                                              |

| (87) 國際公開日    | 平成12年3月9日(2000.3.9)           |           |                                                                                              |

| 審査請求日         | 平成17年11月21日(2005.11.21)       |           |                                                                                              |

| (31) 優先権主張番号  | 09/141,713                    |           |                                                                                              |

| (32) 優先日      | 平成10年8月28日(1998.8.28)         |           |                                                                                              |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                                              |

最終頁に続く

(54) 【発明の名称】通信を高速化するインテリジェントネットワークインターフェース装置及びシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

ハードウェアとプロセッサとプロトコル処理層のスタックとを有するホストコンピュータによりネットワーク通信を行うための方法であって、

ネットワークから前記ホストコンピュータによって、複数のヘッダと、前記ヘッダのプロトコル処理に従って前記ホストコンピュータの行先に配置するためのデータとを含むメッセージパケットを受信する過程と、

前記ハードウェアにより、前記ヘッダの要約を作成することを含めて、前記複数のヘッダをグループとして処理する過程と、

前記データを前記ホストコンピュータの行先に格納するために、前記要約に基づいて、前記プロトコル層によって前記パケットを処理するか、又は前記プロトコル層による処理を回避するかを選択する過程と、

前記データを前記ヘッダなしで前記要約に従って、前記プロトコル層により前記ヘッダを処理することなく、前記ホストコンピュータ上のアプリケーションにより提供される前記行先に転送する過程とを有することを特徴とする方法。

## 【請求項 2】

前記パケットに対応する伝送制御プロトコル(TCP)コネクションのための通信制御ブロックを作成する過程と、前記データを前記行先に送出するために、前記要約と前記通信制御ブロックとを整合させる過程とをさらに含むことを特徴とする請求項1に記載の方法。

10

20

## 【請求項 3】

前記パケットに対応する伝送制御プロトコル(ＴＣＰ)コネクションのための通信制御ブロックを作成する過程をさらに含み、前記データを前記行先に送出する過程は、前記通信制御ブロックによって前記データを誘導する過程を含むことを特徴とする請求項1に記載の方法。

## 【請求項 4】

前記通信制御ブロックを参照することにより、前記ホストコンピュータから前記ネットワークに第2のメッセージを伝送する過程をさらに含むことを特徴とする請求項3に記載の方法。

## 【請求項 5】

通信プロセッサを備える装置によりネットワークに接続され、プロトコル処理スタックを有するホストコンピュータにより通信を処理するための方法であって、

前記ホストコンピュータによって前記ネットワークから前記プロトコル処理スタックに対応する一連のヘッダとデータとを含むメッセージフレームを受信する過程と、

前記フレームについて発信元及び行先のインターネットプロトコル(ＩＰ)アドレスと発信元及び行先の伝送制御プロトコル(ＴＣＰ)ポートとを決定することを含めて、前記装置によって前記一連のヘッダをバイトのストリームとして解析する過程と、

前記装置により前記データを前記ヘッダなしで、前記IPアドレス及びTCPポートに基づいて、前記プロトコル処理スタックによって前記ヘッダを処理することなく、かつ前記ホストコンピュータによって前記データをコピーすることなく、前記ホストコンピュータ上で実行中のアプリケーションにより制御されるホストメモリ内の行先に送出する過程とを有することを特徴とする方法。

## 【請求項 6】

前記ホストメモリ内の行先に前記ヘッダなしで前記データを送出する前記過程が、前記ホストコンピュータによって、前記フレームを含むメッセージのための通信制御ブロックを作成する過程と、

前記装置に前記通信制御ブロックを格納する過程と、

前記IPアドレス及びTCPポートを前記通信制御ブロックと整合させる過程とをさらに含むことを特徴とする請求項5に記載の方法。

## 【請求項 7】

前記データを前記行先に送出する前に、前記IPアドレス及びTCPポートのハッシュを前記通信制御ブロックを識別するハッシュテーブルと比較する過程をさらに含むことを特徴とする請求項6に記載の方法。

## 【請求項 8】

前記装置を経由して、前記ホストコンピュータから前記ネットワークに送信データを伝送する過程をさらに含み、前記伝送する過程は、リモートホストへのネットワーク転送のために、前記送信データの前にいくつかのプロトコルプロトコルヘッダを同時に付加する過程を含むことを特徴とする請求項5に記載の方法。

## 【請求項 9】

プロセッサとプロトコル層の順次式スタックとを有し、ネットワークインタフェースによりネットワークに接続されたホストコンピュータにより通信を行うための方法であって、該方法は、

前記ネットワークから前記ネットワークインタフェースによって、それぞれにデータ部分と、前記プロトコル層の順次式スタックにより処理した場合には、前記データのための前記ホストコンピュータ内の上位層の行先に前記データ部分を格納させる、関連するヘッダのシーケンスとを含む多数のパケットを有するメッセージを受信する過程と、

前記ネットワークインタフェースによって、前記関連するヘッダなしで、かつ任意のホストCPUへの割り込みを発生することなく、複数の前記データ部分を前記行先に送出する過程とを有することを特徴とする方法。

## 【請求項 10】

10

20

30

40

50

前記データ部分を前記行先に送出する過程の前に、前記プロトコル層のスタックによって前記パケットを処理するか否かを選択する過程をさらに含むことを特徴とする請求項9に記載の方法。

【請求項11】

前記ヘッダを用いることなく前記データ部分を前記行先に送出する前に、前記ネットワークインターフェースで前記ヘッダを処理する過程をさらに含むことを特徴とする請求項9に記載の方法。

【請求項12】

前記ネットワークインターフェースを介して前記ホストから前記ネットワークにデータファイルを伝送する過程をさらに含み、前記伝送する過程は、前記データファイルを一連のデータユニットに分割する過程と、前記データユニットの前に前記ヘッダを付加し、それにより一連のネットワークフレームを作成する過程と、任意のホストCPUに割り込みを発生することなく、前記ネットワークフレームを前記ネットワークに配置する過程とを含むことを特徴とする請求項9に記載の方法。

10

【請求項13】

CPUと、メモリと、プロトコル層の順次式スタックとを備え、ネットワークインターフェース装置によりネットワークに接続されたホストコンピュータによって通信を行うための方法であって、

前記ネットワークインターフェース装置によって前記ネットワークから第1のパケットを受信する過程と、

20

前記ホストコンピュータによって、前記第1のパケットに対応する伝送制御プロトコル(TCP)状態を含む通信制御プロックを作成する過程を含めて、前記第1のメッセージを処理する過程と、

前記通信制御プロックを前記装置に転送する過程と、

前記ネットワークインターフェース装置によって前記ネットワークから、データとヘッダとを含み、かつ前記通信制御プロックに対応する第2のパケットを受信する過程と、

前記ネットワークインターフェース装置によって前記ヘッダのTCP部分を処理することを含めて、前記ネットワークインターフェース装置によって前記ヘッダを処理する過程と、

前記ネットワークインターフェース装置によって前記データを、前記ホストコンピュータにより前記ヘッダを処理することなく、前記プロトコル層のTCP層より上位にある上位層に、該上位層に適した形で送出し、前記通信制御プロックを用いて前記送出を誘導する過程とを有することを特徴とする方法。

30

【請求項14】

前記通信制御プロックに対応する第3のパケットを前記装置によって受信する過程と、前記装置から前記メモリに前記通信制御プロックの制御を渡す過程と、前記CPUにより前記第3のパケットを処理する過程とをさらに含むことを特徴とする請求項13に記載の方法。

【請求項15】

前記データを前記上位層に送出する前に、前記第2のパケットのIPアドレスとTCPポートとを前記通信制御プロックに整合させる過程をさらに含むことを特徴とする請求項13に記載の方法。

40

【請求項16】

前記ホストコンピュータから前記ネットワークに第3のパケットを伝送する過程をさらに含み、該過程は、前記通信制御プロックを参照し、かつ複数のプロトコル層ヘッダを含む送信ヘッダをホストソースから取得されるデータに付加することにより、前記装置を経由して前記第3のパケットを送出する過程を含むことを特徴とする請求項13に記載の方法。

【請求項17】

プロトコル処理装置によりネットワークに接続され、プロトコル処理スタックを有するローカルホストによりネットワーク通信を行うための方法であって、

50

前記プロトコル処理スタックにより、前記ローカルホストとリモートホストとの間の伝送制御プロトコル（TCP）コネクションを定義する通信制御ブロックを作成する過程と、

前記通信制御ブロックを前記プロトコル処理装置に渡し、それにより前記コネクションに関連しあつ前記ネットワークと前記ローカルホストとの間で転送されるメッセージパケットのTCP処理の制御を渡し、それにより、前記メッセージパケットを前記プロトコル処理スタックではなく、前記プロトコル処理装置によって処理する過程とを有することを特徴とする方法。

【請求項18】

前記ネットワークと前記ローカルホストとの間で転送されかつ前記コネクションに関連する第2のメッセージパケットが全般に前記プロトコル処理スタックによって処理されるように、前記通信制御ブロックの制御を前記ローカルホストに渡す過程をさらに含むことを特徴とする請求項17に記載の方法。 10

【請求項19】

前記プロトコル処理装置によって、前記ネットワークからメッセージフレームを受信する過程と、

前記プロトコル処理装置によって、前記メッセージフレームのヘッダを解析し、それにより前記メッセージフレームのTCP発信元ポート及び行先ポートを決定する過程と、

前記TCP発信元ポート及び行先ポートを前記通信制御ブロックと比較する過程とをさらに含むことを特徴とする請求項17に記載の方法。 20

【請求項20】

前記プロトコル処理装置によって、前記ネットワークにメッセージフレームを伝送する過程をさらに含み、前記伝送する過程は、前記通信制御ブロックに基づいてヘッダを形成する過程と、前記メッセージフレームの前に前記ヘッダを付加する過程とを含むことを特徴とする請求項17に記載の方法。

【請求項21】

ネットワークを経由してリモートホストに接続することができるローカルホストで用いるための装置であって、前記ローカルホストは、前記ローカルホストのアプリケーションと前記リモートホストのアプリケーションとの間のTCPコネクションを定義する通信制御ブロックを作成するプロトコル処理層のスタックを動作させるCPUを含み、

該装置は、

前記CPUと前記ネットワークとに接続され、前記プロトコル処理層によってネットワークメッセージを処理するか、前記プロトコル処理層を回避し、前記ネットワークと前記ローカルホストアプリケーションとの間で前記ネットワークメッセージに含まれるデータを転送するために前記通信制御ブロックを用いるかを選択するために構成されるプロセッサを有する通信処理機構を備えることを特徴とする装置。

【請求項22】

前記プロセッサは、前記通信制御ブロックをその前記メッセージの処理に基づいて更新するように構成されることを特徴とする請求項21に記載の装置。

【請求項23】

前記通信処理機構は、前記プロセッサに接続され、前記ネットワークから受信されるメッセージパケットの要約を生成するために構成される受信シーケンサを備え、前記メッセージパケットは、前記プロトコル層のスタックに対応する制御情報を含み、前記プロセッサは前記要約を前記通信制御ブロックと比較するように構成されていることを特徴とする請求項21に記載の装置。

【請求項24】

前記プロセッサは、前記通信制御ブロックに対応するヘッダを作成し、前記プロトコル処理層のいくつかに対応する制御情報を含み、前記ホストから前記リモートヘッダに前記メッセージを伝送するために前記データの前に前記ヘッダを付加し、前記通信制御ブロックを更新するように構成されることを特徴とする請求項21に記載の装置。 50

**【請求項 2 5】**

前記通信処理機構は、前記通信制御ブロックに基づいて、前記データに付随する全ゆるヘッダを用いることなく、前記通信処理機構から前記ホストアプリケーションに前記データを送出するためのダイレクトメモリーアクセスユニットを備えることを特徴とする請求項2\_1に記載の装置。

**【請求項 2 6】**

前記プロセッサは複数のマイクロプロセッサを備え、前記マイクロプロセッサのうちの少なくとも1つは主に、前記ネットワークから前記ホストによって受信されるメッセージを処理するように構成され、前記マイクロプロセッサのうちの第2のマイクロプロセッサは前記ホストから前記ネットワークに伝送されるメッセージを処理するように構成されることを特徴とする請求項2\_2に記載の装置。

10

**【請求項 2 7】**

前記マイクロプロセッサは、フェーズをローテーションする際に共有されるハードウェア機能を利用することを特徴とする請求項2\_6に記載の装置。

**【請求項 2 8】**

前記通信処理機構は、複数のキュー記憶ユニットにおいて情報をキューに入れるために構成されるキュー・マネージャを備え、前記キュー記憶ユニットのうちの少なくとも1つはS R A MおよびD R A Mを含むことを特徴とする請求項2\_1に記載の装置。

**【発明の詳細な説明】****【0 0 0 1】**

20

## (技術分野)

本発明は、一般的にコンピュータ又は他のネットワークに関するものであり、得にネットワークに接続されたコンピュータのようなホスト間で通信される情報の処理に関するものである。

**【0 0 0 2】**

## (背景技術)

ネットワークコンピューティングの利点はますます明らかとなってきている。パーソナルコンピュータや他のエンドユーザ装置において情報、通信、又は計算能力を個人に提供することがもたらす利便性及び能率のために、インターネット装置やアプリケーション及びインターネット等のネットワークコンピューティングが急速に成長することになった。

30

**【0 0 0 3】**

周知のように、大部分のネットワークコンピュータ通信は、ネットワークに接続されたホストコンピュータ間での情報の転送のための階層化ソフトウェアアーキテクチャの支援によって達成される。その層が、情報を処理可能なセグメントに分割することを助け、各層の一般的な機能は、多くの場合開放型システム間相互接続(O S I)と呼ばれる国際標準に準拠している。O S Iは7種の処理の層を規定しており、情報がホストによって受信されると、それはエンドユーザに提示できるようにするためにそれらの層の間をわたされる。同様に、ホストからネットワークへの情報の送信では、情報がそれらの7種の処理層を逆の順に通過し得る。1つの層による処理及びサービスの各ステップでは、処理された情報のコピーが行われる。T C P / I P (T C Pは伝送制御プロトコルを表し、I Pはインターネットプロトコルを意味する)と呼ばれる、広く実現されている別の参照モデルは、基本的にO S Iの7層のうち5層を利用する。

40

**【0 0 0 4】**

ネットワークは、例えば、それぞれが複数のホストを有する異なるローカルエリアネットワーク(L A N)間のイーサネット接続又はインターネット接続のような高速バス、又はホスト間のデータ伝送のための様々な他の既知の手段の何れかを含み得る。O S I標準によれば、物理層は各ホストにおいてネットワークに接続され、その物理層がネットワークを介しての生のデータビットの送信及び受信を提供する。データリンク層は、各ホストの物理層によりサービスされ、物理層から受け取ったデータのフレーム分割及び誤り訂正を提供するとともに、受信したホストによって送られた肯定応答フレームの処理を行う。各

50

ホストのネットワーク層は、各データリンク層によりサービスされ、主としてデータのパケットのサブネットのサイズ及び統合を制御する。

【0005】

トランスポート層は各ネットワーク層からサービスされ、セッション層は各ホスト内の各トランスポート層によりサービスされる。トランスポート層はそれらの各セッション層からデータを受け取り、そのデータを他のホストのトランスポート層へ送信するためのより小さいユニットに分割する。他のトランスポート層は、各プレゼンテーション層への提示のためそのデータを連結する。セッション層によってホスト間の機能強化された通信の制御が可能となる。プレゼンテーション層はそれらの各セッション層によりサービスされ、各ホスト固有であり得るデータセマンティクス及び構文と、データ表現の標準化された構造との間での変換を行う。データの圧縮及び／または暗号化も、プレゼンテーション層レベルで達成され得る。アプリケーション層は、各プレゼンテーション層によりサービスされ、個々のホストに特有のプログラムと、アプリケーション又はエンドユーザの何れかに對して提示するための標準化されたプログラムとの間の変換を行う。TCP/IP標準は、下位の4層及びアプリケーション層を含むが、セッション層及びプレゼンテーション層の機能は隣接する層に統合している。一般的に、アプリケーション層、プレゼンテーション層、及びセッション層は上位層と定義され、トランスポート層、ネットワーク層、及びデータリンク層は下位層と定義される。

10

【0006】

各層の規則及び規定はその層のプロトコルと呼ばれ、かつ各層のプロトコル及び一般的な機能は様々なホストにおいて概ね等しいことから、たとえ同位の層同士が情報を下位の各層を順次転送されることなく直接やり取りしないとしても、異なるホストの同一の層同士で直接行われる通信というものを考えることは有益である。各下位層は、通信される情報を処理を助けるべくその1つ上位の層にサービスする。各層は、処理及び次の層へのサービスの提供のため情報を保存する。一般的に用いられるハードウェア及びソフトウェアアーキテクチャや装置及びプログラムの多様性のために、各層は、介入し得るハードウェア及びソフトウェアの相違とは無関係に、データが適切な形式で目的の行先に到達し得ることを確実なものとする必要がある。

20

【0007】

第1のホストから第2のホストに送信するためのデータの準備において、その層のプロトコルに関連する第1のホストの各層で幾つかの制御データが付加されるが、その制御データはそのホストの全ての下位の層において元のデータ（ペイロードデータ）から識別可能なものある。従って、アプリケーション層はペイロードデータにアプリケーションヘッダを付加し、結合されたデータを送信側のホストのプレゼンテーション層に送る。プレゼンテーション層はその結合データを受け取り、それを処理してそのデータにプレゼンテーションヘッダを付加し、別の結合されたデータパケットが生成される。次に、ペイロードデータ、アプリケーションヘッダ、及びプレゼンテーションヘッダの結合によって生成されたデータをセッション層に渡し、セッション層は、そのデータへのセッションヘッダの付加や、生成されたデータの組み合わせのトランスポート層への提示等の必要な処理を行う。この処理は、情報が下位の層に移動する間継続され、それらの各層においてデータにトランスポートヘッダ、ネットワークヘッダ、及びデータリンクヘッダ、及びトレーラが付加され、各処理過程ではデータの転送及びコピーを行い、その後、データをビットパケットとしてネットワークを通して第2のホストに送信する。

30

【0008】

受信側のホストは一般的に上述のプロセスの逆を行い、ネットワークからのデータビットの受信に始まり、最下位の（物理）層から最上位の（アプリケーション）層まで順番にヘッダが除去され、データが処理されて、受信側ホストの行先への送信が行われる。受信側ホストの各層は、その層に関連するヘッダのみを認識し、処理する。その層からみて、より上位の層の制御データはペイロードデータに含められており、そこから識別できないからである。受信側ホストがそのデータをその目的の行先に適切な形式で渡すためには、複

40

50

数の割り込み、有効な中央処理装置（C P U）による処理時間、及び反復されるデータコピー処理も必要であり得る。

#### 【0009】

上述の階層化プロトコル処理の説明は、主としてこの主題について詳述された大学レベルの教科書、例えばAndrew S. TanenbaumによるComputer Networks, Third Edition (1996) が入手可能であることから、単純化されている。上記文献はこの引用により本明細書の一部とする。その文献に定義されているように、コンピュータネットワークとは、インターネットや、例えばローカルエリアネットワーク（L A N）、ワイドエリアネットワーク（W A N）、非同期転送モード（A T M）、リング又はトーカンリング、配線式、無線式、衛星、又は他の異なるプロセッサ間の通信能力を提供するための手段等のインターネットデバイスのような、相互接続された独立して操作されるコンピュータの集合体である。本明細書において、コンピュータは、データを処理するための論理機能とメモリ機能の両方を有する装置を含むものと定義されており、ネットワークに接続されたコンピュータ即ちホストは、それらが異なるオペレーティング装置に従って機能する場合、即ち異なるアーキテクチャを介して通信を行う場合、ヘテロジニアス（異種）であるという。

10

#### 【0010】

ネットワークがますます一般的となり、それによってやりとりされる情報がますます複雑化し内容豊富になるにつれて、そのようなプロトコル処理の必要性が高まってきた。ホストのC P Uの処理能力の大部分が、プロトコル処理の制御に充てられて、そのC P Uが他のタスクを行う能力は低下していると推定される。物理層やデータリンク層のような下位の層の補助のため、ネットワークインターフェースカードが開発されてきた。単に従来型の構成のC P Uにより大きい処理能力を付与することによって、プロトコル処理の速度を高めることも可能である。しかし、この解決方法は手際の良いものとは言えず、コストがかかる。しかし、様々なネットワーク、プロトコル、アーキテクチャ、オペレーティング装置、及びアプリケーションによって付与される複雑さによって、種々のネットワークホスト間での通信能力を与えるために大量の処理が要求されることになる。

20

#### 【0011】

##### （発明の開示）

本発明は、通信されるデータの転送の効率及びその処理速度を大幅に高める、ネットワーク通信の処理のための装置を提供する。本発明は、汎用プロセッサ上の階層化プロトコル処理を行うという、長年にわたって利用されてきた実施の形態を問い合わせすことによって達成されたものである。そのプロトコル処理方法と、その結果として形成されるアーキテクチャでは、例えばT C P / I Pのようなコネクションをベースにした階層化アーキテクチャの層を、所望の位置又はホスト上のバッファとの間で、より直接的にネットワークデータを送受信できる1層のより広い層に効果的にまとめる。この高速化処理はデータの送受信両方のためにホストに提供され、情報の交換に関するホストの両方がそのような特徴を有している場合も、その一方しかそのような特徴を有していない場合でも、処理能力を向上させる。

30

#### 【0012】

前記高速化処理では、その発信元において直接的にメッセージデータにアクセスしたりそれをその目的の行先に直接供給する高速バスを介してメッセージからのデータを処理できるようにする所定のメッセージに対応する制御命令を用いる。この高速バスは、データに付加されるヘッダの従来型のプロトコル処理をバイパスする。高速バスは、ネットワーク通信の処理のために設計された専用マイクロプロセッサを用いて、例えば反復されるコピー処理やC P Uへの割り込みのような、従来のソフトウェアの階層処理の遅れ及び問題点を回避している。要するに、前記高速バスは、従来型のネットワークスタックの複数の層において伝統的に見出される状態を、プロトコル層の厳格な区別及び分離を要求する従来の規定とは異なりこれらの層を全て包含する1個のステートマシンで置き換える。ホストは、高速バスコネクション又はメッセージ例外の処理をセットアップするために用いられる順次式プロトコル処理スタックを保持している。専用マイクロプロセッサ及びホスト

40

50

が、所定のメッセージまたはメッセージの一部分をそのマイクロプロセッサによって処理するか、ホストのスタックによって処理するかを、インテリジェントに選択する。

#### 【0013】

(発明の最良の実施の形態)

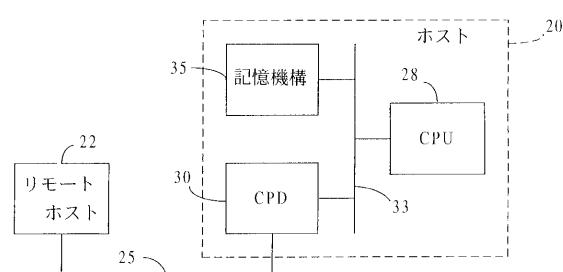

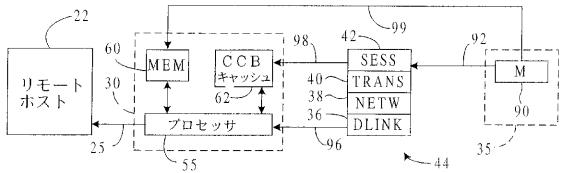

図1は、リモートホスト22にネットワーク25によって接続された本発明のホスト20を示す。本発明によって達成される処理速度の上昇は、既存のホストに容易に無理なく追加されるインテリジェントネットワークインターフェースカード(INIC)又はホストに統合される通信処理装置(CPD)によって提供され得、何れの場合もホストのCPUを大部分のプロトコル処理から解放し、そのCPUによって実行される他のタスクも改善することができる。第1の実施形態のホスト20は、PCIバス33によって接続されたCPU28及びCPD30を有する。CPD30はダイレクトメモリアクセス(DMA)ユニットによって制御されるメモリバッファ及び通信データの処理のために設計されたマイクロプロセッサを有する。例えば、半導体メモリ又はディスクドライブのような記憶機構35も、関連する制御機構とともにPCIバス33に接続されている。

10

#### 【0014】

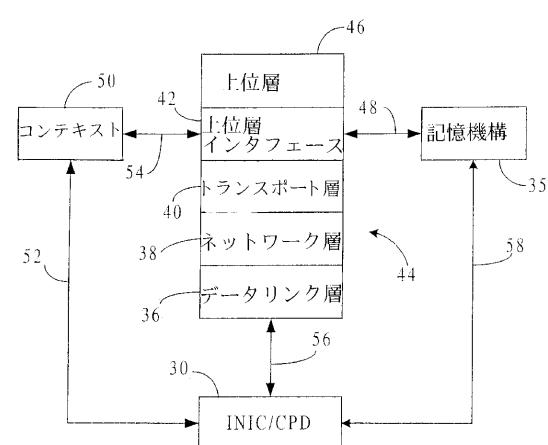

更に図2を参照すると、ホストのCPU28が記憶機構35に収容されたプロトコル処理スタック44を制御しており、前記スタックはデータリンク層36、ネットワーク層38、トランスポート層40、上位層46、及び上位層インターフェース42を有する。上位層46は、使用される特定のプロトコル及び通信されるメッセージに応じて、セッション層、プレゼンテーション層、及び/又はアプリケーション層を意味し得る。上位層インターフェース42は、CPU28及び関連するあらゆる制御機構と協働して、矢印48で示すように、上位層46又は記憶機構35へのファイルの転送及びそこからのファイルの取り出しを行える。コネクションコンテキスト50が生成されており、これは、後に説明するように、例えばプロトコルの種類及び各プロトコル層のための発信元及び行先アドレスのような様々なコネクションの特徴を要約する。そのコンテキストは、矢印52及び54で示すように、セッション層42のためのインターフェースとCPD30との間でやりとりされ得、CPD30又は記憶機構35の何れかに通信制御プロック(CCB)として格納される。

20

#### 【0015】

CPD30が特定のコネクションを確定するCCBを保持するとき、ネットワークからCPDによって受信されたそのコネクションに関連するデータはそのCCBによって参照され、次に高速バス58に従って記憶機構35に直接送信され得、データリンク層36、ネットワーク層38、及びトランスポート層40によって処理される順次式のプロトコルがバイパスされることになる。記憶機構35からリモートホスト22へのファイルの送信のようなメッセージの転送は高速バス58を介しても生じ得、その場合、トランスポート層40、ネットワーク層38、及びデータリンク層36による処理の間に、逐次ヘッダを付加するのではなく、CCBを参照するCPD30によってファイルデータのためのコンテキストが加えられる。CPD30のDMAコントローラが、これらのCPDと記憶機構35との間の転送を実行する。

30

#### 【0016】

CPD30は、それぞれが可能な分離した状態を有する複数のプロトコルスタックを、高速バス処理のための1個のステートマシンにまとめる。この結果、その1個のステートマシンにおいては準備されていない例外条件が生じ得る。これようにしているのは、主としてそのような条件がまれにしか生じず、CPD上でそれを処理することはコストに対して殆ど処理能力上の利点が得られないからである。そのような例外は、CPD30又はCPU28で生じたものであり得る。本発明の利点として、高速バスCCB上で生ずる予期しない状況が取り扱われる方式がある。CPD30は、これらのまれな状況を制御ネゴシエーションを介してホストのプロトコルスタック44にCCB及び関連するあらゆるメッセージフレームを戻す、即ちフラッシュすることによって処理する。次にその例外条件は、従来の方式でホストのプロトコルスタック44によって処理される。しばらく後に、通常

40

50

は例外条件の処理が終了し、高速バス処理が再開し得るようになった直後に、ホストのスタック44はCCBをCPDに戻す。

【0017】

このフォールバック能力によって、ホストのプロトコルの能力に影響を与える機能をCPDネットワークマイクロプロセッサが取り扱うことができるようになるとともに、全体の処理能力に無視できる程度の影響しか与えない程度にまれにしか生じない例外がホストのスタックによって取り扱われることになる。カスタム設計のネットワークプロセッサは、ネットワーク情報の送受信のための独立したプロセッサと、補助及びキューフォーマンスのための別のプロセッサとを備え得る。好ましいマイクロプロセッサの実施形態は、パイプライン型の3個1組の受信、送信、及びユーティリティプロセッサを備えるDMAコントローラがインプリメンテーションに組み入れられ、コントローラに隣接するバッファと長時間記憶機構のような他の位置との間でデータを迅速にやりとりさせるべく、ネットワークマイクロプロセッサと密接に協働する形で機能するものである。DMAコントローラに論理的に隣接するバッファを設けることによって、PCIバスに不必要的負荷が加わるのを避けられる。

【0018】

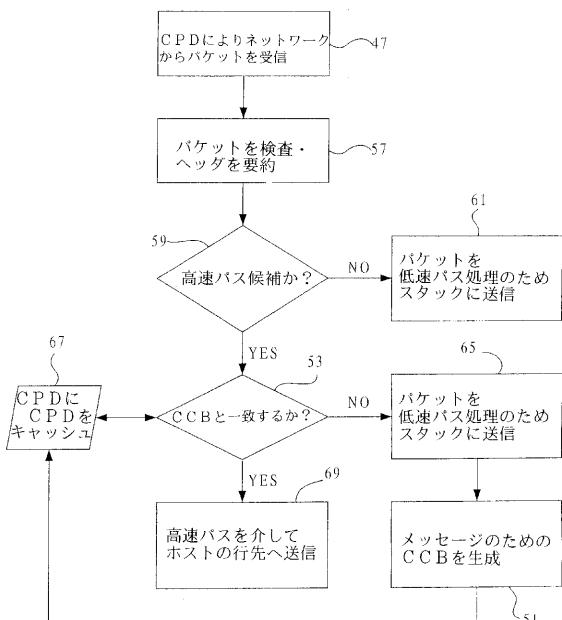

図3は、本発明によって受信されたメッセージの概略流れ図である。ファイル転送のような大きいTCP/IPメッセージは、多数の分離された約64KBの転送でネットワークからホストに受信され得るが、それぞれが多数の約1.5KBのフレーム即ちネットワーク上の転送するためのパケットに分割されてもよい。Internet Packet Exchange(IPX)上でSequential Packet Protocol(SPX)又はNetWare Core Protocol(NCP)を走らせるNovell社のNetWareプロトコルスイートは、同様の方式で機能する。高速バスによって取り扱われ得るデータ通信の他の形態は、Transaction TCP(以下T/TCP又はTTCPという)であり、これは、幾つかのメッセージ初期化ダイアログを介してコネクションを開始させて後のメッセージでデータを転送するのではなく、初期のトランザクションリクエストでコネクションを開始させ、その後データを含む応答がそのコネクションに従って送られるようなTCPのバージョンである。これらのプロトコルによって代表されるあらゆる転送において、各パケットは、従来通り転送されるデータの部分とともに、プロトコル層のそれぞれに対応するヘッダ及びそのメッセージの残りのパケット群に対するそのパケットを位置を決めるためのマーカを有する。

【0019】

CPDによってネットワークからメッセージパケット即ちフレームが受信されたとき(47)、ハードウェアの補助によりそれが初めに検査される。ここでは、様々な層のプロトコルの種類を決定し、関連するチェックサムを確認し、かつこれらの認識事項をステータスワードに要約する(57)。これらのワードに含められるのは、そのフレームが高速バスデータフローの候補であるか否かの表示である。高速バス候補の選択(59)は、そのホストがCPDによって取り扱われるそのメッセージコネクションから利益を得られるか否かに基いて行われ、そのパケットが例えばTCP/IP又はSPX/IPXのような特定のプロトコルを表示するヘッダバイトを有しているか否かの判定が行われる。小さいパーセンテージで存在する高速バス候補でないフレームは、低速バスプロトコル処理のためにホストのプロトコルスタックに送られる(61)。その後の各高速バス候補についてのネットワークプロセッサ作業は、TCP又はSPX CCBのような高速バスコネクションがその候補に対して常に現存しているか否か、又はその候補が、例えばTTCP/IPトランザクションのためのもののような新たな高速バスコネクションをセットアップするために用いられ得るか否かを決定する。CPDによって提供される妥当性検査が、或るフレームが高速バスで処理されるか、低速バスで処理されるかに関わらず、処理の高速化をもたらし、誤りのない場合にのみ、検査されたフレームが、たとえ低速バス処理の場合でもホストのCPUによって処理される。

【0020】

10

20

30

40

50

高速バスの候補となるものとして C P D ハードウェアの補助によって決定された受信されたメッセージフレームは全て、ネットワークマイクロプロセッサ又は I N I C 比較器回路によって調べられ(53)、それらが C P D によって保持された C C B に一致するか否かが判定される。そのような一致を確認する際、 C P D は下位層のヘッダを取り除き、 C P D のダイレクトメモリアクセス( D M A )ユニットを用いて、残りのアプリケーションデータをフレームから直接その最終行先に送信する(69)。この操作は、例えば T C P コネクションが既に存在しつつ行先バッファがネゴシエートされた場合には、メッセージパケットを受け取った直後に行われ得るが、初めに初期ヘッダを処理して、この転送のための最終行先アドレスの新たな組を取得することが必要なこともある。後者の場合には、 C P D は、行先アドレスを待つとともに後続のメッセージパケットをキューに入れ、次いでキューに入れられたアプリケーションデータをその行先に D M A 転送する。

#### 【 0 0 2 1 】

C C B に一致しない高速バス候補を用いて、そのフレームを順次プロトコル処理のためにホストに送信(65)することによって、新たな高速バスコネクションをセットアップすることができる。この場合、ホストはそのフレームを用いて C C B を生成し(51)、次いで C C B は C P D にわたされて、そのコネクションにおける後のフレームを制御する。 C C B は C P D にキャッシュされ(67)、従来通りのソフトウェア階層処理を使用している場合には、処理された全てのプロトコルに対して適切な制御及び状態情報を有する。 C C B はまた、後の関連するメッセージパケット内に含められたアプリケーションレベルのデータを、直接的な使用に利用可能な形態でホストのアプリケーションに直接わたすのを容易にするために用いられる、転送毎の情報のための記憶空間も有している。 C P D は、ホストからそのコネクションのための C C B を受け取ったとき、コネクション処理の指揮を取る。

#### 【 0 0 2 2 】

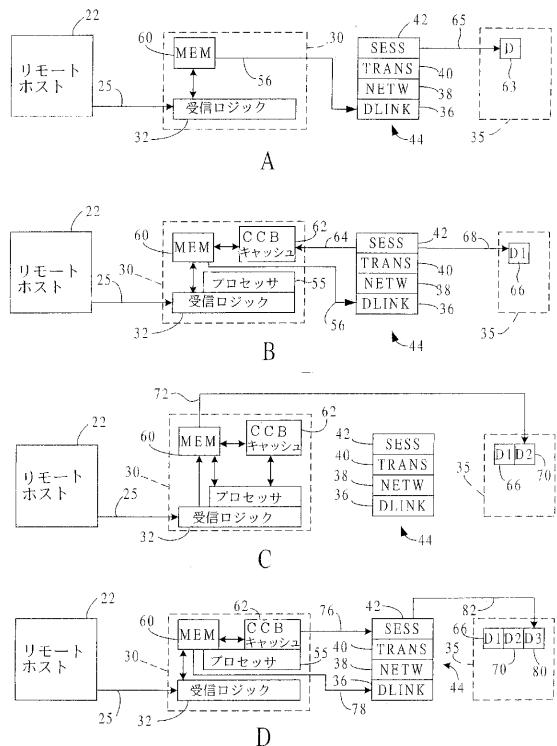

図 4 A により明確に示されているように、リモートホスト 2 2 からメッセージパケットがネットワーク 2 5 を介して受け取られたとき、そのパケットは C P D 3 0 のハードウェア受信ロジック 3 2 に入り、これがヘッダ及びデータを検査し、ヘッダを構文解析してメッセージパケット及びステータスを特定するワードを生成し、ヘッダ、データ、及びワードをメモリ 6 0 に一時的に格納する。パケットの検査と同時に、受信ロジック 3 2 は、そのパケットが高速バス処理の候補であるか否かを前記ワードを用いて示す。図 4 A は、そのパケットが高速バス候補でない場合を示しており、この場合 C P D 3 0 は、矢印 5 6 によって示されるように、ホストの C P U による処理のために、内部バスを通してメモリ 6 0 からデータリンク層 3 6 へ検査されたヘッダ及びデータを送信する。そのパケットは、データリンク層 3 6 、ネットワーク層 3 8 、トランスポート層 4 0 、及びセッション層 4 2 のホストのプロトコルスタック 4 4 によって処理され、次にパケットからのデータ( D ) 6 3 は、矢印 6 5 に示されるように、記憶機構 3 5 に送信され得る。

#### 【 0 0 2 3 】

図 4 B は、 C P D の受信ロジック 3 2 が、例えばパケットのヘッダからそのパケットが T C P / I P 、 T T C P / I P 、又は S P X / I P X メッセージに属すること導き出すことによってそのメッセージパケットが高速バス処理の候補であることを決定する場合を示す。次に、 C P D 3 0 におけるプロセッサ 5 5 は、高速バス候補を要約するワードがキャッシュ 6 3 に保持された C C B に一致するか否かを調べるためのチェックを行う。そのパケットに対して一致がみられないときは、 C P D は、ホストのプロトコルスタック 4 4 にメモリ 6 0 から検査されたパケットを処理のために送信する。ホストのスタック 4 4 は、そのパケットを用いて、パケットに関連するメッセージからのデータの行先を見出し、それを予約することを含むメッセージのコネクションコンテキストを生成することができ、そのコンテキストは C C B の形態を取る。本実施例は、高速バス及び非高速バスの候補の両方の処理のために一個の専用ホストスタック 4 4 を用いるが、以下に説明する実施例では、高速バスの候補は、非高速バスの候補とは異なるホストスタックによって処理される。その初めのパケットから幾つかのデータ( D 1 ) 6 6 が、矢印 6 6 で示すように、所望に

10

20

30

40

50

応じて記憶機構 3 5 における行先に送られ得る。次に C C D が、矢印 6 4 に示すように、キャッシュ 6 2 に保存される C P D 3 0 を送信する。例えば、T C P / I P に代表されるような伝統的なコネクションベースのメッセージの場合は、初めのパケットが、C C B が生成されて C P D 3 0 にわたされる前にホスト間で生ずるコネクション初期化ダイアログの一部であり得る。

【 0 0 2 4 】

ここで図 4 C を参照すると、初めのパケットと同一のコネクションからの後続のパケットが、C P D 3 0 によってネットワーク 2 5 から受信されたとき、パケットのヘッダ及びデータは、受信ロジック 3 2 によって検査され、そのヘッダは構文解析されて、メッセージパケットの要約及び対応する C C B を見つけるためのハッシュが生成され、その要約及びハッシュはワードに含められる。そのワードは、パケットとともにメモリ 6 0 に一時的に保存される。プロセッサ 5 5 は、キャッシュ 6 2 に保存された各 C C B とハッシュとの間の一致をチェックし、その一致を見出したときには、矢印 7 2 に示すように、高速バスを介して記憶機構 3 5 における行先に直接データ (D 2) 7 0 を送信し、セッション層 4 2 、トランスポート層 4 0 、ネットワーク層 3 8 、及びデータリンク層 3 6 はバイパスされる。メッセージからの残りのデータパケットは、D M A によって直接記憶機構に送信され得、C P U スタック 4 4 による比較的低速のプロトコル層処理及び反復されるコピー処理は回避される。

【 0 0 2 5 】

図 4 D は、例えば図 4 C に示されるような、それに対して高速バスがコネクションが確立されたメッセージが、C P D によって容易に取り扱われないパケットを有するときの稀な例を取扱うための手順を示す。この場合、そのパケットは、プロトコルスタックによって処理されるべく送信され、プロトコルスタックは、矢印 7 6 で示すように、C P D との制御ダイアログを介してキャッシュ 6 2 からのメッセージのために C C B にわたされ、そのメッセージの処理を引き継がせるために C P U に信号が送られる。次にプロトコルスタックによる低速バス処理によって、矢印 8 2 に示すように、そのパケットからのデータ (D 3) 8 0 が記憶機構 3 5 に送られることになる。一旦そのパケットが処理され、誤り状態が補正されると、C C B は制御ダイアログを介してキャッシュ 6 2 に戻され得、そのメッセージの後続のパケットからのペイロードデータは、同様に C P D 3 0 の高速バスを介して送信され得ることになる。従って、C P U 及び C P D は協働して、所定のメッセージが高速バスハードウェア処理に従って処理されるか、より一般的な C P U によるソフトウェア処理に従って処理されるのかを決定する。

【 0 0 2 6 】

リモートホスト 2 2 へ供給するためのホスト 2 0 からネットワーク 2 5 へのメッセージの送信も、図 5 に示すように、C P U を介した順次式プロトコルソフトウェア処理か、C P D 3 0 を介した高速化ハードウェア処理の何れかによって処理され得る。記憶機構 3 5 から C P U 2 8 によって選択されたメッセージ (M) 9 0 は、矢印 9 2 及び 9 6 によって示されるように、スタック 4 4 によって処理するためセッション層 4 2 に送信され得る。しかし、コネクションが存在し、かつ C P D 3 0 がそのメッセージのための適切な C C B を既に有している状況では、データパケットはホストスタック 4 4 をバイパスし、D M A によって直接メモリ 6 0 に送信され得る。このとき、プロセッサ 5 5 は、各データパケットに全ての適切なプロトコル層を含む 1 個のヘッダを加え、得られたパケットをリモートホスト 2 2 への送信のためネットワーク 2 5 に送る。この高速バス送信によって、たとえ 1 個のパケットのための処理でも非常に高速化することができ、より大きいメッセージの場合は大幅に高速化する。

【 0 0 2 7 】

高速バスコネクションのためのメッセージは現存しておらず、従って高速バス送信をガイドするための適切な制御及び状態情報と共に C C B を生成することによって利益が得られる。T C P / I P 又は S P X / I P X に代表される伝統的なコネクションベースのメッセージの場合、C C B は、コネクション初期化ダイアログの間に生成される。T T C P /

10

20

30

40

50

I P に代表されるような高速コネクションメッセージの場合、C C B はペイロードデータを送信する同じトランザクションで生成され得る。この場合、ペイロードデータの送信が高速バスコネクションをセットアップするために用いられたリクエストに対する応答であり得る。いずれの場合にも、C C B は、各プロトコル層に関連するプロトコル及びステータス情報を提供し、これには、ユーザが関与するもの及び1回の情報の転送のための記憶空間が含まれている。C C B は、プロトコルスタック 4 4 によって生成され、そのプロトコルスタックは、次に、矢印 9 8 によって示されるように、C P D のコマンドレジスタに書き込むことによってC C B をC P D 3 0 にわたす。C C B によってガイドされ、プロセッサ 5 5 は、ホストメモリ 3 5 における発信元からのデータのネットワークフレームサイズにされた一部分を、矢印 9 9 に示すように、D M A を用いてそれ自身のメモリ 6 0 に送る。次にプロセッサ 5 5 は、適切なヘッダ及びチェックサムをそのデータの一部分の先頭に付加し、得られたフレームを関連するプロトコルの規約に準拠させてネットワーク 2 5 に送信する。C P D 3 0 は、全てのデータがその行先に達したという確認応答を受信した後、C P D は応答バッファに書き込むことによってホスト 3 5 に通知する。

10

#### 【0028】

従って、データ通信の高速バス送信はまた、ホストをC P U のフレーム毎の処理から解放させる。データ送信の大部分は、高速バスによってネットワークに送信され得る。入出力の両方が高速バスであることによって、上位層レベル即ちセッション層レベル以上における機能による割り込みが大幅な低減を達成され、かつネットワークマイクロプロセッサとホストとの間の相互作用は上位層が作ろうとする全転送サイズを用いて行われることになる。高速バス通信の場合、割り込みは（その大部分が）上位層メッセージトランザクション全体の始まりと終わりにおいてのみ生じ、各階層の部分及びそのトランザクションのパケットの送受信において割り込みは生じない。

20

#### 【0029】

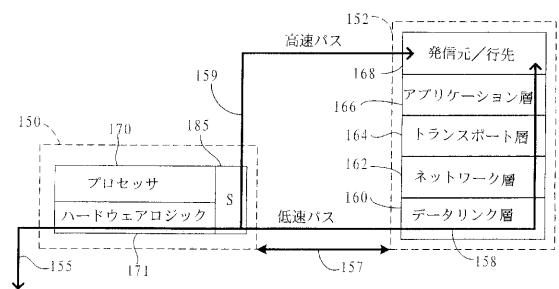

ホスト 1 5 2 に対するネットワークインターフェースを提供する、単純化されたインテリジェントネットワークインターフェースカード（I N I C ）1 5 0 が図 6 に示されている。I N I C 1 5 0 のハードウェアロジック 1 7 1 は、I N I C とホストとを接続する周辺バス（P C I ）1 5 7 でネットワーク 1 5 5 に接続されている。この実施例において、ホスト 1 5 2 はT C P / I P プロトコルスタックを有し、それはネットワーク 1 5 5 から受け取ったメッセージフレームの順次式ソフトウェア処理のための低速バス 1 5 8 を提供する。ホスト 1 5 2 のプロトコルスタックは、データリンク層 1 6 0 、ネットワーク層 1 6 2 、トランスポート層 1 6 4 、及びホスト 1 5 2 における通信データの発信元又は行先 1 6 8 を提供するアプリケーション層 1 6 6 を有する。図示されていない他の層、例えばセッション層やプレゼンテーション層もホストスタック 1 5 2 に含められ得、発信元又は行先はデータの性質に応じて変わり、実際にはアプリケーション層であり得る。

30

#### 【0030】

I N I C 1 5 0 は、ホストのプロトコルスタックを含む低速バス 1 5 8 に沿って処理するメッセージ、又はホストのプロトコルスタックをバイパスする高速 1 5 9 に沿って処理するメッセージとの間の選択を行うネットワークプロセッサ 1 7 0 を有する。受信されたパケットのそれぞれは、I N I C 1 5 0 に含められたフライバイ（fly by）ハードウェアロジック 1 7 1 上で処理され、従って或るパケットの全てのプロトコルヘッダは、プロトコル層の間でデータのコピー、移動、記憶させることなく処理され得る。ハードウェアロジック 1 7 1 は、パケットバイトがそのハードウェアを通過するときに、選択されたヘッダバイトを分類することによって1回で所定のパケットのヘッダを処理する。選択されたバイトの処理の結果は、チェックサム検査を含むパケットの要約が生成されるまで、パケットのどの他のバイトを分類するかを決定することとなる。次に受信されたパケットからのデータ及び処理されたヘッダが、そのパケットのヘッダ及びステータスを要約するワードとともにI N I C の記憶機構 1 8 5 に記憶される。ネットワーク記憶機構の構成のために、I N I C 1 5 0 はI D E 、S C S I 、又は類似のインターフェースを有するディスクドライブのような周辺記憶装置に接続され得、その記憶装置のためのファイルキャッシ

40

50

ユはINIC150のメモリ185上に存在する。そのようなネットワークインターフェースの幾つかは1つのホストのために存在し得、それぞれが関連する記憶装置を有する。

### 【0031】

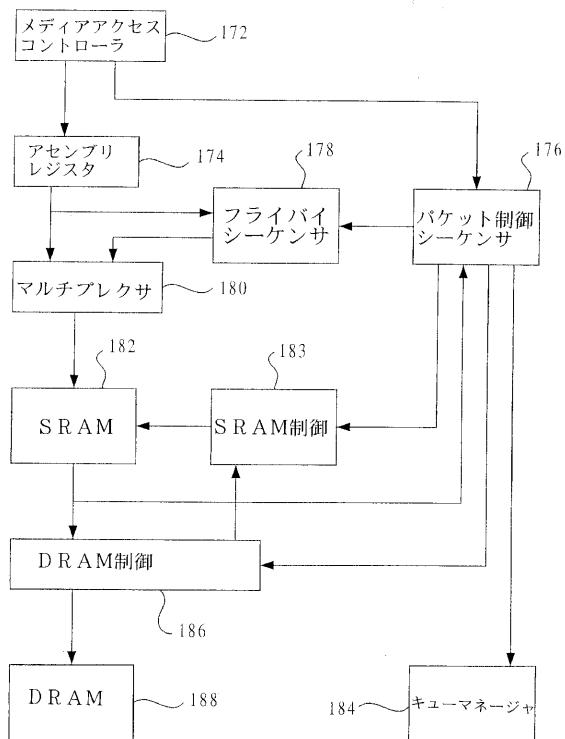

ネットワーク155からINIC150によって受信されたメッセージパケットのハードウェア処理は、図7により詳細に示されている。受信されたメッセージパケットは、初めにメディアアクセスコントローラ172に入り、そのメディアアクセスコントローラはネットワークへのINICのアクセス及びパケットの受信を制御し、かつネットワークプロトコル管理のための統計的情報を提供する。そこから1回に1バイトのデータがアセンブリレジスタ174に流れる。アセンブリレジスタ174は、この実施例では128ビットの幅を有する。そのデータはフライバイシーケンサ178によって分類されるが、後に図8を参照してより詳細に説明するように、フライバイシーケンサは、パケットのバイトを、それらが移動している(fly by)ときに調べ、パケットを要約するために用いられるそれらのバイトからステータスを生成する。生成されたそのステータスはマルチプレクサ180によってデータと併合され、得られたデータはSRAM182に格納される。パケット制御シーケンサ176は、フライバイシーケンサ178を監視し、メディアアクセスコントローラ172からの情報を調べ、データのバイトをカウントし、アドレスを生成し、ステータスを送り、かつアセンブリレジスタ174からSRAM182、更にはDRAM188へのデータの移動を管理する。パケット制御シーケンサ176は、SRAMコントローラ183を介してSRAM182におけるバッファを管理し、かつデータをSRAM182からDRAM188のバッファへ移動させる必要があるときにDRAMコントローラ186への表示も行う。一旦パケットのためのデータの移動が終了し、全てのデータがDRAM188のバッファに移動すると、パケット制御シーケンサ176は、フライバイシーケンサ178において生成されたステータスを、パケットデータの先頭に付加するべくDRAM188のバッファの先頭部及びSRAM182に動かす。次にパケット制御シーケンサ176は、受信バッファディスクリプタを受信キューに入れるようにキューマネージャに要求し、受信キューはプロセッサ170にパケットがハードウェアロジック171によって処理されたこと、及びその要約されたステータスを通知する。

### 【0032】

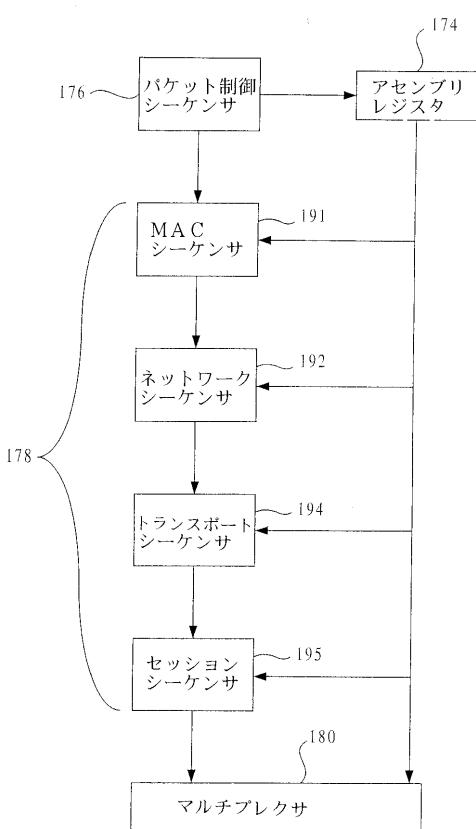

図8は、フライバイシーケンサ178が幾つかの段を有していることを示し、この段のそれぞれは通常パケットヘッダの特定の部分を集中して取扱い、従ってその段に関連するステータスを生成するため特定のプロトコル層を集中して取り扱う。この実施形態では、フライバイシーケンサ178が、メディアアクセス制御シーケンサ191、ネットワークシーケンサ192、トランスポートシーケンサ194、及びセッションシーケンサ195を有する。より高位のプロトコル層に関連するシーケンサを追加的に提供することもできる。フライバイシーケンサ178は、パケット制御シーケンサ176及びフライバイシーケンサに所定のバイトがアセンブリレジスタ174から利用可能であるか否かを伝えるパケット制御シーケンサによる所定のポインタによってリセットされる。メディアアクセス制御シーケンサ191は、バイト0-5を見ることにより、或るパケットが、別のホストではなくホスト152を、又は別のホストに加えてホスト152をアドレス指定されているかを決定する。パケットのオフセット12及び13もメディアアクセス制御シーケンサ191によって処理され、例えばそのパケットがイーサネット又は802.3であるか否かのタイプフィールドを決定する。そのタイプフィールドがイーサネットである場合、それらのバイトはメディアアクセス制御シーケンサ191にそのパケットのネットワークプロトコルの種類も伝える。802.3の場合は、それらのバイトは全フレームの長さを表示し、メディアアクセス制御シーケンサ191は更にパケット内の8個のバイトをチェックし、ネットワーク層の種類を決定する。

### 【0033】

大部分のパケットについて、ネットワークシーケンサ192は、受信されたヘッダ長が正しい長さを有していることを検査し、ネットワーク層のヘッダを検査する。高速バス候補について、ネットワーク層のヘッダは、メディアアクセス制御シーケンサ191によって

10

20

30

40

50

行われた解析から I P 又は I P X であることが判っている。例えば、タイプフィールドが 8 0 2 . 3 であり、ネットワークプロトコルが I P であると仮定すると、ネットワークシーケンサ 1 9 2 は I P の種類を決定するためにバイト 2 2 で始まるネットワークヘッダの初めのバイトを解析する。 I P ヘッダの初めのバイトは、ネットワークシーケンサ 1 9 2 によって処理され、そのパケットがどの I P の種類に関係しているかを決定する。そのパケットが、例えば I P バージョン 4 に関係するものであると決定することにより、ネットワークシーケンサ 1 9 2 による更なる処理が方向付けられ、ネットワークシーケンサはパケットのトランスポートヘッダプロトコルの表示のため I P ヘッダ内の 1 0 個のバイトに配置されたプロトコルのタイプを調べる。例えば、イーサネット上の I P の場合、その I P ヘッダはオフセット 1 4 から始まり、プロトコルタイプのバイトは、オフセット 2 3 であり、それはネットワークロジックによって処理され、トランスポート層プロトコルが例えば T C P であるか否かが決定される。通常 2 0 - 4 0 バイトであるネットワークヘッダの長さから、ネットワークシーケンサ 1 9 2 が、トランスポート層ヘッダの検査のため、パケットのトランスポート層ヘッダの始まりを決定する。トランスポートシーケンサ 1 9 4 は、トランスポート層ヘッダ及びデータのためのチェックサムを生成してもよく、トランスポート層ヘッダ及びデータは、少なくとも T C P の場合に I P ヘッダからの情報を含み得る。

10

#### 【 0 0 3 4 】

T C P パケットの例について続けると、トランスポートシーケンサ 1 9 4 は、1 つにはそのメッセージのための T C P 発信元及び行先ポートを決定するため、例えばそのパケットが N e t B i o s か他のプロトコルであるかを決定するために、ヘッダのトランスポート層部分における初めの数バイトの解析も行う。 T C P ヘッダのバイト 1 2 が、トランスポートシーケンサ 1 9 4 によって処理され、 T C P ヘッダの長さが決定され、検査される。 T C P ヘッダのバイト 1 3 は、肯定応答 (ack) フラグ及びプッシュフラグを除いて、例えばリセットや終了のような、プロセッサにこのパケットを例外として分類させ得る予期しないオプションを表示し得るフラグを含む。 T C P オフセットバイト 1 6 及び 1 7 はチェックサムであり、それはハードウェアロジック 1 7 1 によって引き出されたり、格納されたりし、フレームの残りの部分はそのチェックサムに対して検査される。

20

#### 【 0 0 3 5 】

セッションシーケンサ 1 9 5 は、セッション層ヘッダの長さを決定し、セッション層ヘッダは、 N e t B i o s の場合には 4 バイトに過ぎず、そのうちの 2 バイトは N e t B i o s ペイロードデータの長さを通知するが、他のプロトコルの場合にはより長いこともあり得る。セッションシーケンサ 1 9 5 は、例えば読み出し又は書き込みとしてメッセージのタイプを分類するためにも用いられ得、そのために高速バスが特に有益なものとなり得る。メッセージの種類に応じて更なる上位層ロジックの処理が、フライバイシーケンサ 1 7 8 及びパケット制御シーケンサ 1 7 6 のハードウェアロジック 1 7 1 によって行われ得る。従って、ハードウェアロジック 1 7 1 はインテリジェントに 1 つのバイトストリームから選択されたバイトを分類することによってヘッダのハードウェア処理を誘導し、そのパケットのステータスが処理の進行中に決定された分類から構築される。一旦パケット制御シーケンサ 1 7 6 が全てのパケットがフライバイシーケンサ 1 7 8 によって処理されたことを検出すると、パケット制御シーケンサ 1 7 6 は、フライバイシーケンサ 1 7 8 によって生成されたステータス情報にパケット制御シーケンサ 1 7 6 によって生成されたステータス情報を加え、プロセッサ 1 7 0 によるパケットの取扱いにおける便宜のため、そのパケットにそのステータス情報を先頭付加（パケットの先頭部分への付加）する。パケット制御シーケンサ 1 7 6 によって生成された追加のステータス情報は、メディアアクセスコントローラ 1 7 2 のステータス情報及び発見された全ての誤り、又はアセンブリレジスタ若しくは D R A M バッファの何れかにおけるデータオーバーフロー、又はそのパケットに関連する他の種々雑多な情報を有する。パケット制御シーケンサ 1 7 6 は、キューマネージャ 1 8 4 を介して受信バッファキューリー及び受信統計的キューリーにエントリを入れることも行う。

30

40

50

## 【0036】

ハードウェアロジック171によりパケットを処理することの利点は、従来のような順次ソフトウェアプロトコル処理とは異なり、そのパケットが各プロトコル層ヘッダの処理のために記憶機構に格納されたり、転送されたり、コピーされたり、又は引き出されたりする必要がなく、処理効率を劇的に向上させ、各パケットの処理時間を短縮できる点にある。そのパケットはビットがネットワークから受信されるときのビットレート、例えば100BaseT接続の場合100メガビット/秒で処理され得る。従って、この速度で受信された60バイトの長さを有するパケットを分類する時間は、約5マイクロ秒である。ハードウェアロジック171でそのパケットを処理し、パケットデータを高速バスを介してそのホスト行先に送信するためにかかる全時間は、66MHzのPCIバスを用いた場合、約16マイクロ秒以下であり得るが、300MHzのPentiumII(登録商標)プロセッサによる従来通りのソフトウェアプロトコル処理では、使用中の装置において200マイクロ秒もの時間がかかり得る。従って、従来型の順次式ソフトウェアプロトコル処理を用いる高速CPUの場合と比較して、高速バス159によって1桁以上の処理時間の短縮が達成され得、CPUの割り込みの低減やホストのバスの大域幅の節約によってもたらされる追加の時間短縮を考慮しなくとも、ハードウェアロジック171及びプロセッサ170でプロトコルヘッダを処理することによって劇的な高速化が提供されることを立証している。

## 【0037】

プロセッサ170は、記憶機構185に保持された受信されたメッセージパケットのそれについて、そのパケットが高速バス159の候補であるか否かを選択し、そうである場合には、高速バスが既にそのパケットが属するコネクションに対してセットアップされているか否かを調べるためのチェックを行う。これを行うため、プロセッサ170は、初めにそのパケットヘッダが高速バス候補のために定義されたプロトコルのものであるか否かを決定するためにヘッダステータスの要約をチェックする。そうでない場合には、プロセッサ170は、INIC150におけるDMAコントローラに、そのパケットを低速バス158処理のためにホストに送信する命令を送る。メッセージが低速バス158処理される場合でも、INIC150は検査及びメッセージの種類の決定のような初期手順を実行し、検査されたメッセージを少なくともホストのデータリンク層160に送る。

## 【0038】

高速バス159の候補の場合、プロセッサ170は、そのヘッダステータスの要約がINICに保持されたCCBに一致するか否かを調べるためのチェックを行う。そうである場合には、パケットからのデータは高速バス159を通してホストの行先168に送信される。高速バス159の候補のパケット要約がINICに保持されたCCBに一致しない場合には、そのパケットは低速バス処理のためにホスト152に送信されて、そのメッセージのためのCCBが生成される。高速バス159を用いることは、断片化したメッセージの場合や他の複雑さのために必要でない、又は望ましいものではないこともある。しかし、大部分のメッセージについては、INICの高速バス159は、メッセージ処理を非常に高速化し得る。従ってINIC150は、従来のように所定のパケットの運命を決定するために幾つかのプロトコル層のそれぞれにおいてストートマシンを用いるのと異なり、処理進行中に収集される情報に基いてデータをその行先に直接送信するか否かを決定する1個のストートマシンプロセッサ170を提供するものである。

## 【0039】

ホスト152において受信された表示即ちパケットの処理において、ホストのプロトコルドライバは、その表示が高速バス又は低速バスの何れであるかに基いて処理経路を選択する。TCP/IP又はSPX/IPXメッセージは、そのドライバによって形成され、高速バスパケットとの一致をとの一致をとり、かつそれをコネクション行先168に導くために、INICに送られる。TTCP/IPメッセージの場合、ドライバは、初期リクエストパケットの処理から、そのトランザクションのためのコネクションコンテキストを生成することができる。この処理では、メッセージ行先168の位置指定を行い、次にその

行先からの応答のための高速パスを提供するために CCB の形態で INC にそのコンテキストを送る。CCB は、プロトコル層及びメッセージのパケットに関するコネクション及び状態情報を含む。従って CCB は、発信元及び行先メディアアクセス制御 (MAC) アドレス、発信元及び行先 IP 又は IPX アドレス、発信元及び行先 TCP 又は SPX ポート、タイマーのような TCP 変数、ウィンドウプロトコルをスライドさせるための受信及び送信ウインドウ、及びセッション層プロトコルを示す情報を有し得る。

#### 【 0040 】

INC におけるハッシュテーブルに CCB をキャッシュすることにより、そのパケットが高速パス 159 を介して処理され得るか否かを決定するべく入力されるパケットを要約するワードとの迅速な比較処理が行われるようになり、一方全ての CCB が処理のために INC にも保持される。この比較を高速化する他の方法としては、コンテンツのアドレス指定可能なメモリ (CAM) のようなハードウェア補助機構及び Bツリー のようなソフトウェア処理等が挙げられる。INC マイクロコード又は比較器回路が CCB との一致を検出すると、DMA コントローラは CPU による割り込み、プロトコル処理又はコピー処理を行うことなく、行先 168 にパケットからのデータをおく。受信したメッセージの種類に応じて、そのデータの行先は、ホスト 152 におけるセッション層、プレゼンテーション層、又はアプリケーション層、又はファイルバッファキャッシュであり得る。

#### 【 0041 】

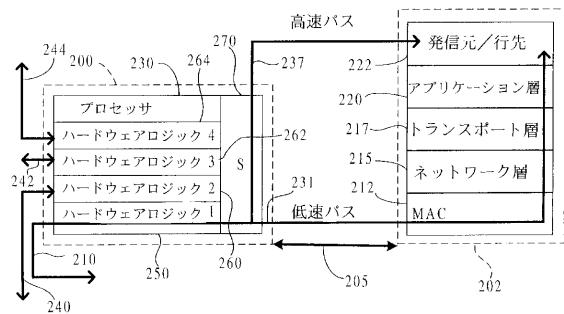

図 9 は、ファイルサーバとして用いられるホスト 202 に接続された INC 200 を示す。この INC は、一般にファスト・イーサネットとして知られる 802.3u 標準を用いる幾つかのネットワークコネクションのためのネットワークインターフェースを提供する。INC 200 は、PCI バス 205 によってサーバ 202 に接続されており、サーバ 202 は MAC 層 212、ネットワーク層 215、トランスポート層 217、及びアプリケーション層 220 を含む TCP/IP 又は SPX/IPX プロトコルスタックを有し、アプリケーション層の上に発信元 / 行先 222 が設けられているが、前に述べたように、アプリケーション層が発信元 / 行先であり得る。INC は、ネットワークライン 210、240、242、及び 244 にも接続されており、これらのネットワークラインは好みしくはファスト・イーサネット、ツイストペア、光ファイバー、同軸ケーブル、又は他の種類のラインであって、それぞれ 100 Mb/s のデータ転送が可能なものであるが、より高速又はより低速のデータレートも可能である。ネットワークライン 210、240、242、及び 244 は、それぞれハードウェア回路の専用の行に接続されており、前記ハードウェア回路はそれぞれのネットワークラインから受信されたメッセージパケットの検査及び要約を行うことができる。従って、ライン 210 は、シーケンサ 250 の第 1 の水平方向の行に接続され、ライン 240 は、シーケンサ 260 の第 2 の水平方向の行に接続され、ライン 242 は、シーケンサ 262 の第 3 の水平方向の行に接続され、ライン 244 は、シーケンサ 264 の第 4 の水平方向の行に接続される。パケットがその水平方向のハードウェアの行の 1 つによって検査、要約された後、そのパケットはそのステータス要約とともに記憶機構 270 に格納される。

#### 【 0042 】

ネットワークプロセッサ 230 は、INC 200 に格納されたその要約及び任意の CCB との比較に基いて、ホストによって処理される低速パス 231 を通してそのパケットを送信するか否かを決定する。大部分のパケットは、そのような順次処理を避けることができ、一致する CCB に従ってサーバ内のデータ行先に高速パス 237 を通して DMA により送信されるそのデータ部分を有する。同様に、高速パス 237 は、データをネットワーク送信のためにパケットに分割し、全てのヘッダを付加してプロセッサ 230 によって発信元 222 から任意のネットワークラインへ直接データを送信する経路を提供し、同様に CPU による処理及び割り込みを最小限にする。明示のため、水平シーケンサ 250 のみがアクティブ状態として示されているが、実際にはシーケンサ行 250、260、262、及び 264 のそれぞれが、他の全てのシーケンサ行と同時に全二重通信を提供する。専用 INC 200 は、メッセージパケットとともに動作するとき、ソフトウェアプロトコ

10

20

30

40

50

ルスタックに従ってそれらのヘッダを順次処理する高度な汎用ホストC P Uよりも非常に高速である。

#### 【 0 0 4 3 】

ファイル転送のような大きいメッセージのために最も一般的に用いられるネットワークプロトコルの1つは、T C P / I Pを通してのサーバメッセージブロック(S M B)である。S M Bはファイルが書き込まれるディスク又はプリンタのような特定の操作のために必要なリソースが、その操作が生成されるホストに存在するか、或いは結び付けられているか、又はファイルサーバのようなネットワークに接続された他のホストに存在するかを決定するリダイレクタソフトウェアとともに動作し得る。S M B及びサーバ/リダイレクタは、従来はトランスポート層によりサービスされるが、本発明ではS M B及びリダイレクタが、I N I Cによりサービスされ得る。この場合には、大きいS M Bトランザクションを受け取ったとき、I N I CバッファからD M Aコントローラによってデータを送信することにより、ホストが取り扱わなければならない割り込みが著しく低減し得る。更に、このD M Aは一般的にファイルデイバスキャッシュにあるその最終的な行先にデータを転送する。本発明のS M B送信は、基本的に上述のS M Bの受信を逆方向にたどるものであり、ホストからI N I Cにデータが転送され、バッファに格納されるとともに、関連するプロトコルヘッダがネットワークラインを介してのリモートホストへの転送のためにI N I Cにおけるデータの先頭に付加される。ホストの反復される割り込み無しに、カスタム設計のハードウェアを介しての複数のT C P / I P、N e t B i o s、及びS M Bプロトコル層及び複数のパケットのI N I Cによる処理によって、S M Bメッセージのネットワークラインへの送信速度を著しく高めることができる。

#### 【 0 0 4 4 】

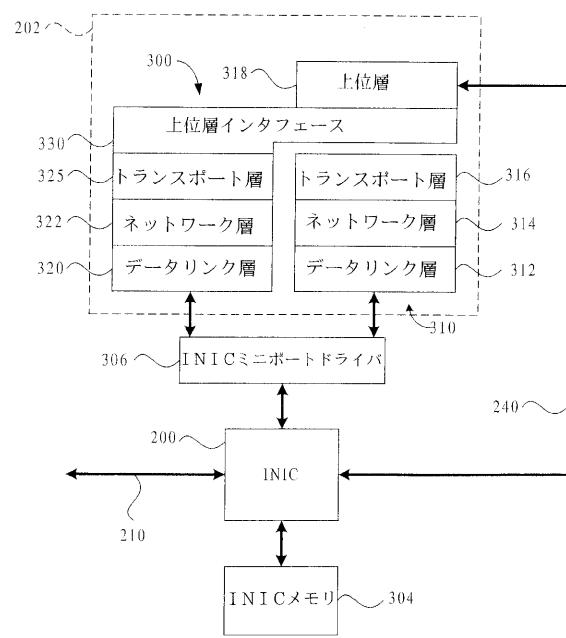

図10に示すように、所定のメッセージがホスト202によって処理されるか、又はI N I C200によって処理されるかを制御するために、メッセージコマンドドライバ300がホスト202にインストールされ、ホストプロトコルスタック310と協働して機能を果たす。コマンドドライバ300は、メッセージの受信又は送信に介入し、C C Bを生成し、I N I C200からC C Bを送受信することができ、従って処理能力の向上を除いて、I N I Cの機能はユーザからは透過的なものとなる。また、図面にはI N I Cメモリ304及びI N I Cミニポートドライバ306が示されており、I N I Cミニポートドライバはネットワーク210から受信したメッセージパケットを、そのパケットが高速バス候補としてのラベル付けされているか否かに応じて、従来通りのプロトコルスタック310又はコマンドプロトコルスタック300の何れかへ誘導することができる。従来通りのプロトコルスタック310は、高速バス候補としてラベル付けされておらず、従ってコマンドスタック300によって処理されないメッセージの従来通りの下位層の処理のために、データリンク層312、ネットワーク層314、及びトランスポート層316を有する。下位層スタック310の上に存在するのは上位層318であり、これはやりとりされるメッセージに応じて、セッション層、プレゼンテーション層、及び/又はアプリケーション層を表す。コマンドドライバ300は、同様にデータリンク層320、ネットワーク層322、及びトランスポート層325を有する。

#### 【 0 0 4 5 】

ドライバ300は、メッセージをネットワーク210に送信するために、上位層318から送信されたメッセージが、コマンドスタック300、それに続けてI N I C高速バスによって処理されるか、従来通りのスタック310によって処理されるかを決定する上位層インターフェース330を有する。その上位層インターフェース330が、従来通りホストのプロトコルスタックによるプロトコル処理の後のネットワークへの送信を目的とする上位層318から適切なメッセージを受け取ったとき、そのメッセージはドライバ300に送られる。次にI N I Cが、I N I C D M Aユニットを介しての送信のために、メッセージデータのネットワークサイズにされた一部分を得て、そのデータの一部分の先頭にヘッダを付加し、形成されたメッセージパケットをワイヤを通して送信する。逆に、T C P、T T C P、S P X、又は類似のメッセージパケットを、高速バスコネクションのセットア

10

20

30

40

50

ップにおいて用いられるようにネットワーク210から受け取ったとき、ミニポートドライバ306は、そのメッセージパケットをコマンドドライバ300に処理するために転送する。ドライバ300は、そのメッセージパケットを処理してそのメッセージのためのコンテキストを生成し、ドライバ302は、そのコンテキスト及びコマンド命令を、高速バスを通しての同一のコネクションにおいて後のメッセージのデータを送信するためのCCBとして、INIC200に戻す。INICによって、数百のTCP、TTCp, SPX、又は類似のCCBコネクションは、その数に限界なく維持され得るが、INICキャッシュが一杯になった場合のため、最小使用頻度(LRU)アルゴリズムが用いられる。ドライバ300は、CCBとしてINIC200に送られるTTCpリクエストのためのコネクションコンテキストも生成することができ、これよってそのリクエストに対するTTCp応答の高速バス転送が可能となる。高速化されていないプロトコルを有するメッセージは、プロトコルスタック310によって従来通りに処理され得る。

10

#### 【0046】

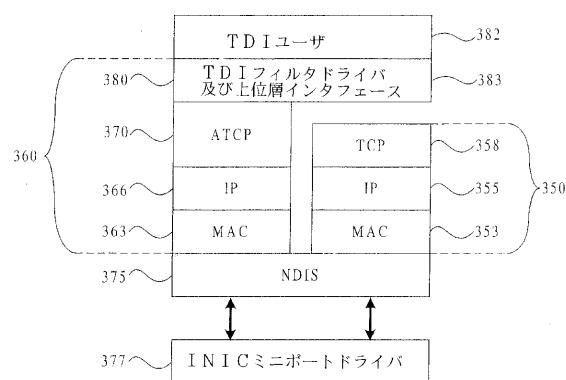

図11は、Microsoft(登録商標)プロトコルメッセージのためのコマンドドライバソフトウェアのTCP/IPインプリメンテーションを示す。従来通りのホストプロトコルスタック350は、MAC層353、IP層355、及びTCP層358を有する。コマンドドライバ360は、ホストスタック350と協働して働き、ネットワークメッセージを処理する。コマンドドライバ360は、MAC層363、IP層366、及びAlacrityec TCP(ATCP)層373を有する。従来型スタック350及びコマンドドライバ360は、ネットワークドライバインターフェース仕様(NDIS)層375を共有しており、これはINICミニポートドライバ306を相互作用する。INICミニポートドライバ306は、従来通りのホストスタック350又はATCPドライバ360の何れかによって処理するため受信した表示をソートする。TDIフィルタドライバ及び上位層インターフェース380は、同様に、TDIユーザ382からネットワークに送られたメッセージが、コマンドドライバに送られてINICの高速バスに転送されたか、或いはホストスタックによって処理されたかを判定する。

20

#### 【0047】

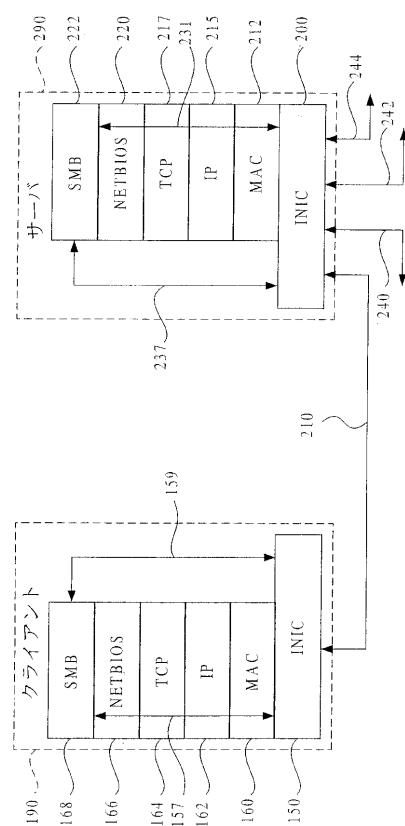

図12は、典型的なクライアント190とサーバ290との間のSMB交換を示す図であり、クライアントとサーバの両方は本発明の通信装置を有し、その通信装置はそれぞれデータの高速バス転送のためのそれらのコネクションを確定するCCBを有する。クライアント190は、INIC150、802.3準拠のデータリンク層160、IP層162、TCP層164、NetBios層166、及びSMB層168を有する。クライアントは、通信処理のための低速バス157及び高速バス159を有する。同様にサーバ290は、INIC200、802.3準拠のデータリンク層212、IP層215、TCP層217、NetBios層220、及びSMB層222を有する。サーバはネットワークライン240、242、及び244に接続されているとともに、クライアント190に接続されたライン210にも接続されている。サーバも通信処理のための低速バス231及び高速バス237を有する。

30

#### 【0048】

クライアント190がサーバ290上の100KBのファイルの読み出しを行おうとしている場合、クライアントは、ネットワーク210を介して読み出しブロック行(RBR)SMBを送信することによって、サーバ290上のそのファイルの最初の64KBを要求することを開始し得る。RBRコマンドは、例えば76バイトに過ぎない大きさであり得、従ってサーバ上のINIC200は、メッセージタイプ(SMB)及び比較的小さいメッセージサイズを認識し、かつその76バイトを高速バスを介してサーバのNetBiosに直接送信する。NetBiosは、SMBにデータをわたし、SMBは読み出しリクエストを処理し、データの64KBを取り出して、サーバのデータバッファに入れる。次にSMBは、NetBiosを呼出してそのデータを送信し、NetBiosはそのデータをクライアントのために出力する。従来型のホストでは、NetBiosがTCP出力を呼び出し、64KBをTCPにわたし、TCPはそのデータを1460バイトの

40

セグメントに分割し、各セグメントをIP及び最終的にMAC(低速バス231)を介して出力する。本発明の場合には、その64KBのデータは、クライアント-サーバSMBコネクションに関する表示とともにATCPドライバに向かい、前記表示はINICによって保持されているCCBを示す。次にINIC200は、ホストバッファから1460バイトのセグメントをDMA送信し、TCP、IP及びMACのための適切なヘッダを一度に付加し、かつ完成したパケットをネットワーク210(高速バス237)上に送信する。INIC200は、この処理を64KBの転送の全てが送信されるまで反復する。通常、クライアントからその64KBのを受信したという確認応答を受信した後、INICは残りの36KBも高速バス237によって送信する。

## 【0049】

10

INIC150は、その応答が着信したとき、クライアント190上で動作しており、INIC150は、受信された第1のフレームからそのコネクションが受信高速バス159処理(ATCP/IP, NetBios, CCBとの一致)であることを認識し、ATCPは、その第1フレームを用いてそのメッセージのためのバッファ空間を確保し得る。後者の場合には、フレームのNetBios部分の初めの128バイトをATCP高速バスを介して、ホストのNetBiosに直接わたすことによって達成され、これによりNetBios/SMBに全てのフレームのヘッダがわたされる。NetBios/SMBは、これらのヘッダを解析し、リクエストIDとの一致によってこれが元の行読み出しコネクションに対する応答であることを認識し、データを置くべき64KのバッファのリストをATCPにわたす。この段階において、ただ1個のフレームが着信しているが、この処理が生じている間に複数のフレームが着信し得る。クライアントバッファリストがATCPにわたされると直ぐに、それはその転送情報をINIC150にわたし、INIC150はそれらのバッファに蓄積された任意のフレームデータのDMA送信を開始する。

## 【0050】

20

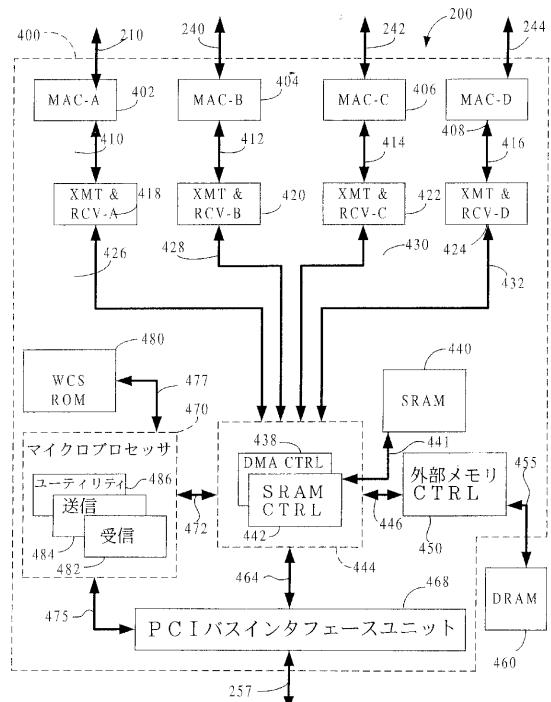

図13は、INIC200を単純化して示した図であり、INIC200はネットワークインターフェースコントローラとプロトコルプロセッサの機能を一個のASICチップ400に結合したものである。この実施形態におけるINIC200は、全二重4チャネル10/100メガビット/秒(Mbps)のインテリジェントネットワークインターフェースコントローラを提供し、このコントローラはサーバアプリケーションのための高速プロトコル処理のために設計されている。特にサーバの用途のために設計されているが、INIC200は、パーソナルコンピュータ、ワークステーション、ルータ、又は他のTCP/IP、TTCP/IP、又はSPX/IPXプロトコルが用いられているあらゆる他のホストに接続され得る。

## 【0051】

30

INIC200は、4つのネットワークライン210、240、242、及び244に接続されており、これらのラインは例えばツイストペア、同軸ケーブル、又は光ファイバーのような複数の異なる経路に沿ってデータを転送することができ、そのコネクションはそれぞれ市販の物理層チップ、例えばSEEQ Technology Incorporated, 47200 Bayside Parkway, Fremont, CA94538製のmodel 80220/80221 Ethernet Media Interface Adapterを介してのメディア独立インターフェース(MII)を提供する。そのラインは、好ましくは802.3準拠であり、INICとともに4つの完全なイーサネットノードを構成し、INICは10Base-T、10Base-T2、100Base-TX、100Base-FX、及び100Base-T4とともに将来のインターフェース標準をサポートしている。物理層の特定及び初期化は、ホストドライバ初期化ルーチンによって達成される。ネットワークライン210、240、242、及び244とINIC200との間のコネクションは、MACユニットのMAC-A 402、MAC-B 404、MAC-C 406、及びMAC-D 408によって制御され、これらのMACユニットはINICがネットワークライン210、240、242、及び244にアクセスするときに必要な制御を行うMACサブレイヤの基本的な機能を実行するための論理回路を含む。MACユニット402～408は、無差別でマルチキャスト又はユニキャストモードで動作すること

40

50

ができ、これによってINICがネットワークモニタとして機能し、ブロードキャスト及びマルチキャストパケットを受信し、かつ各ノードに対して複数のMACアドレスをインプリメントすることが可能になる。MACユニット402～408は、シンプルネットワーク管理プロトコル(SNMP)のために用いられ得る統計的情報も提供する。

#### 【0052】

MACユニット402、404、406、及び408は、それぞれ送受信シーケンサ、XMT&RCV-A418、XMT&RCV-B420、XMT&RCV-C422、及びXMT&RCV-D424にそれぞれ配線410、412、414、及び416によって接続されている。各送受信シーケンサは、メッセージフレームがそのシーケンサを通過するとき、処理進行中に幾つかのプロトコル処理ステップを実行し得る。MACユニットと組み合わせて、この送受信シーケンサ418～422は、ハードウェア上のデータリンク層、ネットワーク層、トランスポート層、セッション層、及び使用する場合にはプレゼンテーション層及びアプリケーション層のプロトコルのためにパケットステータスをコンパイルして、従来型の順次式ソフトウェアエンジンと比較してそのようなプロトコル処理のための時間を非常に短縮させることができる。送受信シーケンサ410～414は、ライン426、428、430、及び432によってSRAM及びDMAコントローラに444に接続されており、DMAコントローラ444はDMAコントローラ438及びSRAMコントローラ442を有する。スタティックランダムアクセスメモリ(SRAM)バッファ440は、ライン441によってSRAMコントローラ442に接続されている。SRAM及びDMAコントローラ444は、ライン446を介して外部メモリ制御機構450と相互作用し、外部メモリバス455を介してダイナミックランダムアクセスメモリ(DRAM)バッファ460とフレームの送受信を行う。DRAMバッファ460は、I Cチップ400に隣接して配置される。DRAMバッファ460は、4MB、8MB、16MB、又は32MBとして構成され得、かつ所望に応じてチップ上に配置され得る。SRAM及びDMAコントローラ444はライン464を介してPCIバスインターフェースユニット(BIU)468に接続されており、BIU468はINIC200とPCIインターフェースバス257との間のインターフェースを管理する。64ビットの多重化BIU468は、スレーブ及びマスター機能の両方についてPCIバス257に対する直接のインターフェースを提供する。INIC200は、64ビット又は32ビット何れかのPCI環境において動作し得、何れの構成においても64ビットのアドレス指定をサポートしている。

#### 【0053】

マイクロプロセッサ470はライン472によってSRAM及びDMAコントローラ444に接続され、かつライン475を介してPCI-BIU468に接続されている。マイクロプロセッサ470はチップ制御ストア480に存在するレジスタファイルに命令を送り、チップ制御ストアはSRAMの書き込み可能なオンチップ制御ストア(WCS)及び読み出し専用メモリ(ROM)を有し、かつライン477によってマイクロプロセッサに接続されている。マイクロプロセッサ470は入力されるフレームを処理し、ホストのコマンドを処理し、ネットワークトラフィックを誘導し、かつPCIバスストラフィックを誘導し得る、プログラム可能なストートマシンを提供する。3つのプロセッサは、各クロックサイクル毎に1個の命令を発して完了させる3つのレベルのパイプライン型アーキテクチャに、共通のハードウェアを用いてインプリメントされている。受信プロセッサ482は主として通信の受信のために用いられ、送信プロセッサ484は主として通信の送信のために用いられて、全二重通信を容易に行えるようにしてあり、一方ユーティリティプロセッサ486はPCIレジスタアクセスの監視及び制御を含む様々な機能を提供する。

#### 【0054】

3つのプロセッサ482、484、及び486に対する命令は、オンチップ制御ストア480に存在する。このため3つのプロセッサの機能は容易に定義しなおすことができ、従ってマイクロプロセッサ470は所定の環境に適合させることができる。例えば受信機能のために必要な処理の量は、送信機能及びユーティリティ機能の何れかのために要求され

10

20

30

40

50

るものを上回っていることがある。この状況では、幾つかの受信機能が送信プロセッサ 484 及び / 又はユーティリティプロセッサ 486 によって実行され得る。或いは、追加のレベルのパイプラインを生成して、3つではなく 4 以上の仮想プロセッサを生成し、その追加のレベルを受信機能専用にすることができる。

#### 【0055】

I N I C 2 0 0 は、この実施形態では D R A M 4 6 0 におけるテーブルに維持されている最大 256 個の C C B をサポートし得る。しかし、 S R A M 4 4 0 において、順次検索を保存するためのハッシュ順の C C B インデックスも存在する。一旦ハッシュが生成されると C C B は S R A M にキャッシュされ、この実施例では最大 16 個の C C B が S R A M にキャッシュされる。 S R A M にキャッシュされた 16 の C C B の割り当ては、以下に説明するように、最低使用頻度レジスタによって取り扱われる。これらのキャッシュ位置は、送信プロセッサ 484 と受信プロセッサ 486 との間で共有されており、従ってより重い負荷のかかるプロセッサがより多くのキャッシュバッファを使用することができる。また、シーケンサ間で共有される 8 個のコマンドバッファ及び 8 個のヘッダバッファも存在する。所定のヘッダ又はコマンドバッファは、所定の C C B バッファに静的にリンクされていない。そのリンクはフレーム毎に動的だからである。

#### 【0056】

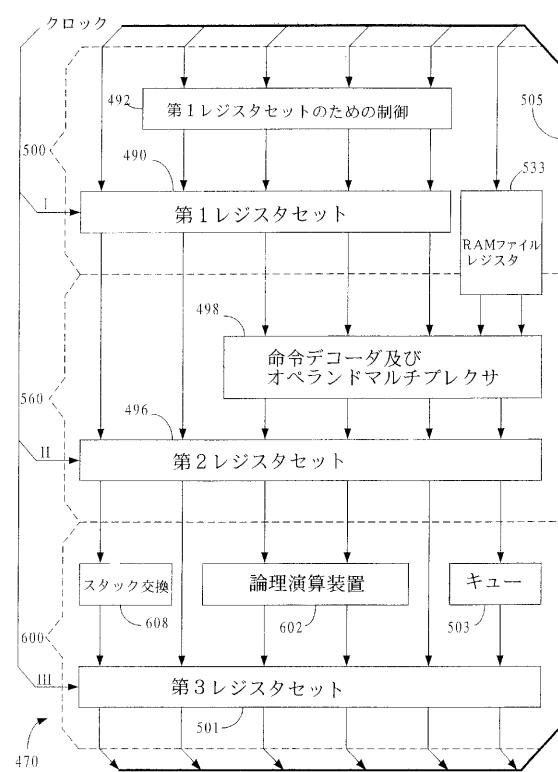

図 14 は、パイプライン型マイクロプロセッサ 470 の概要を示しており、このマイクロプロセッサでは受信、送信、及びユーティリティプロセッサのための命令が、クロックのインクリメント I、II、III に従って 3 つの交互のフェーズで実行され、そのフェーズはパイプライン段階のそれぞれに対応している。各フェーズは異なる機能を担っており、3 つのプロセッサのそれぞれは、各クロックインクリメントの間に異なるフェーズを占める。通常各プロセッサは、制御ストア 480 からの異なる命令ストリームに基いて動作し、それぞれそのフェーズを通してそれ自身のプログラムカウンタ及びステータスを有する。

#### 【0057】

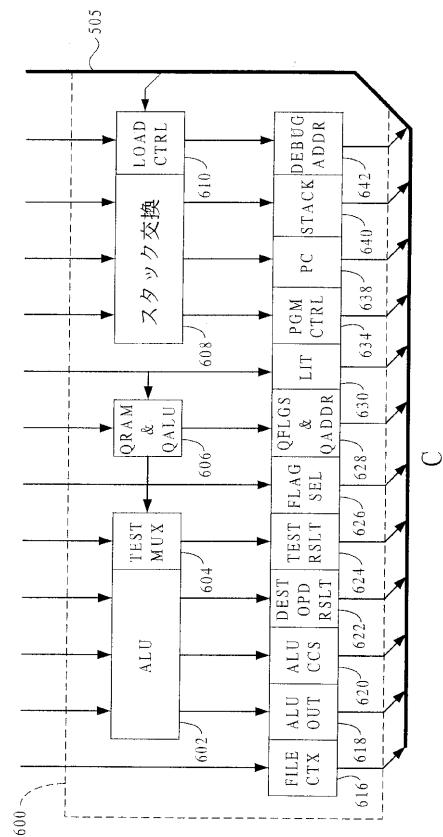

一般に、パイプライン型マイクロプロセッサの第 1 命令フェーズ 500 は、命令を終了し、その結果を行先のオペランドに格納し、次の命令を取り出し、かつその次の命令を命令レジスタに格納する。第 1 レジスタセット 490 は、命令レジスタを含む複数のレジスタを提供し、第 1 レジスタセットのための制御機構セット 492 は第 1 レジスタセット 490 に対する記憶機構のための制御を提供する。幾つかの項目が制御機構 492 によって変更されることなく第 1 フェーズを通過し、代わりに第 1 レジスタセット 490 又は R A M ファイルレジスタ 533 に単にコピーされる。第 2 命令フェーズ 560 は、第 1 レジスタセット 490 の命令レジスタに格納された命令をデコードし、生成された全てのオペランドを集める命令デコーダ及びオペランドマルチプレクサ 498 を有し、その収集されたオペランドは次に第 2 レジスタセット 496 のデコードレジスタに格納される。第 1 レジスタセット 490 、第 2 レジスタセット 496 、及び第 3 命令フェーズ 600 で用いられる第 3 レジスタセット 501 は、多くの同一のレジスタを有し、これは図 15 A 乃至図 15 C により詳細に示されている。命令デコーダ及びオペランドマルチプレクサ 498 は、 R A M ファイルレジスタ 533 のデータポート及び 2 つのアドレスから読み出しを行うことができ、 R A M ファイルレジスタは、第 1 フェーズ 500 及び第 2 フェーズ 560 の両方において動作する。プロセッサ 470 の第 3 フェーズ 600 は、第 2 レジスタセットからのオペランドに対する A L U 処理を行う論理演算装置 ( A L U ) 602 を有し、 A L U は処理の結果を第 3 レジスタセット 501 に含められた結果レジスタに格納する。スタック交換機構 608 は、レジスタスタックを順序付けしなおすことができ、キュー マネージャ 503 はプロセッサ 470 のためのキューを編成することができ、その結果は第 3 レジスタセットに格納される。

#### 【0058】

命令は、環状パイプライン 505 によって示されるように第 1 フェーズ、次にそれに続く第 3 フェーズをまで継続する。所定のフェーズ内での組み合わせによる遅れを最小限する

10

20

30

40

50

ために、命令実行の3つのフェーズにわたって様々な機能が分散されていることに注意されたい。この実施形態の66MHzの周波数で、各クロックインクリメントが終了するまでに15ナノ秒の時間がかかり、3つのプロセッサのそれぞれに対して1個の命令が完了するまで全体で45ナノ秒かかることになる。循環する命令フェーズは図15A乃至図15Cにより詳細に示されており、各フェーズが異なる図面において示されている。

#### 【0059】

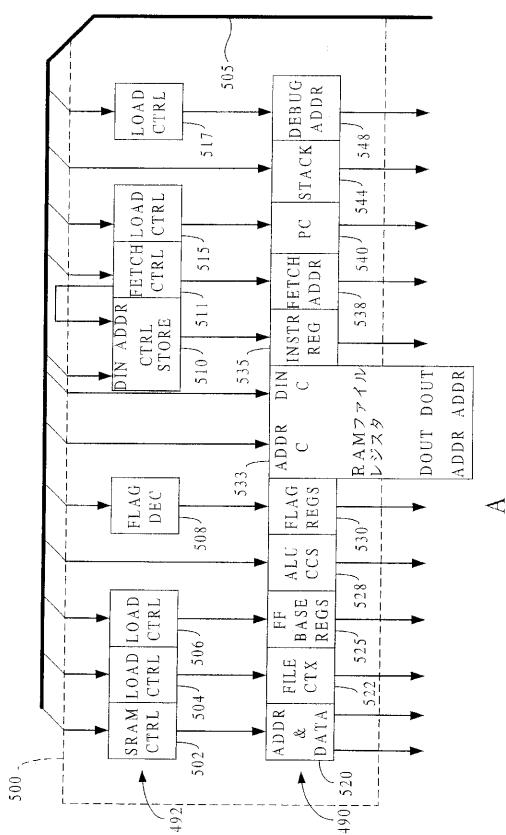

詳述すると、図15Aは第1レジスタセット490及び関連する制御機構492を有する第1フェーズ500の幾つかの特定のハードウェア機能を示す。第2レジスタセット492のための制御機構には、SRAM制御機構502が含まれ、これはアドレスをロードし、データをSRAMアドレス及びデータレジスタ520に書き込むための論理制御機構である。従って第3フェーズ600からのALU602の出力は、SRAM制御機構502によってSRAMアドレス及びデータレジスタ520のアドレスレジスタ又はデータレジスタに置かれ得る。ロード制御機構504は、同様にファイルコンテキストレジスタ522に或るファイルに対するコンテキストの書き込みのための制御を提供し、別のロード制御機構506は様々なデータをフリップフロップレジスタ525に格納するための制御を提供する。例えば、送られたビットがセットされたか否かを示すALU条件コードは、第1フェーズ500において実行される処理なしで、ALU条件コードレジスタ528にクロックに応じて入力される。フラグデコード508は、例えばロックの設定のようなフラグレジスタ530に格納された様々な機能を実行することができる。

#### 【0060】

RAMファイルレジスタ533は、アドレス及びデータのための1つの書き込みポート及びアドレス及びデータのための2つの読み出しポートを有し、従って2以上のレジスタが一度に読み出され得る。上述のように、RAMファイルレジスタ533は基本的に第1及び第2フェーズをまたいでおり、即ち第1フェーズ500において書き込みが行われ、第2フェーズ560において読み出しが行われる。制御ストア命令510によって制御ストア480から新たなデータが入ってくるため、図面には示されていないが、命令レジスタ535に格納された命令をプロセッサがプログラムしなおすことが可能となる。このためのアドレスは、フェッチアドレスレジスタ538に格納されたアドレスのうちどのアドレスを取り出すかを決定するフェッチ制御レジスタにおいて生成される。ロード制御機構515は、プログラムカウンタのための命令を供給し、プログラムカウンタは制御ストアのためのフェッチアドレスの場合と概ね同様に動作する。3つのレジスタの後入先出スタック544は、このフェーズにおいて他の操作を受けずに第1レジスタセットにコピーされる。最後に、デバッグアドレス548のためのロード制御機構517が所望に応じて含まれるが、これによって生じ得る誤りの訂正が可能となる。

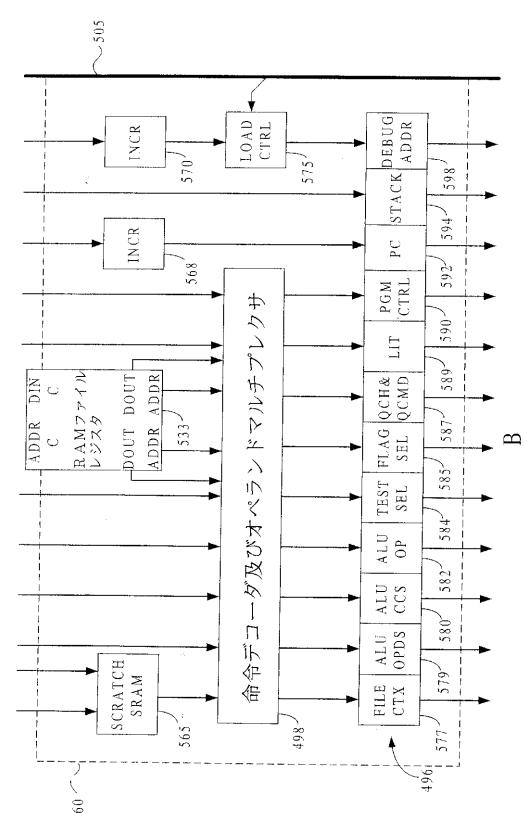

#### 【0061】

図15Bは、RAMファイルレジスタ533からのアドレス及びデータの読み出しを含む、第2マイクロプロセッサフェーズ560を示す。スクラッチSRAM565には、第3フェーズにインクリメントされるまで初めの2つのフェーズを通過するレジスタを有する第1レジスタセットのSRAMアドレス及びデータレジスタ520から書き込みが行われる。スクラッチSRAM565は、命令デコーダ及びオペランドマルチプレクサ498によって読み出される。これは、上述のように、スタック544、デバッグアドレス548、及びSRAMアドレス及びデータレジスタのような例外を除いて、第1レジスタセットの大部分のレジスタと同様である。命令デコーダ及びオペランドマルチプレクサ498は、セット490の様々なレジスタ及びSRAM565を参照して命令をデコードし、次のフェーズにおける処理のためのオペランドを収集する。特に、以下のALU602に提供するオペランドを決定する。命令デコーダ及びオペランドマルチプレクサ498の出力は、ALUオペランド579及び582、ALU条件コードレジスタ580、及びこの実施形態では32のキューを制御し得るキュー・チャネル及びコマンド587レジスタを含む第2レジスタセット496における多数のレジスタに格納される。セット496における幾つかのレジスタは、プログラム制御機構590、リテラルフィールド589、テスト選択5

10

20

30

40

50

84、及びフラグ選択 585 を含む、デコーダ 498 によって実質的にデコードされることなく命令レジスタ 535 から直接ロードされる。第 1 フェーズ 500 のファイルコンテキスト 522 のような他のレジスタは、第 2 フェーズ 560 のファイルコンテキスト 577 に常に格納されるが、マルチプレクサ 572 によって集められたオペランドとしても取り扱われる。スタックレジスタ 544 は、スタックレジスタ 594 に単にコピーされる。プログラムカウンタ 540 は、このフェーズにおいてインクリメントされ(568)、レジスタ 592 に格納される。同様に、オプションのデバッグアドレス 548 もインクリメントされ(570)、ロード制御機構 575 は、この時点で、各フェーズにおける誤り制御を可能にするためにパイプライン 505 から供給され得、その結果はデバッグアドレス 598 に格納される。

10

### 【0062】

図 15C は、ALU 及びキュー操作を含む、第 3 のマイクロプロセッサフェーズ 600 を示す。ALU 602 は、加算器、優先エンコーダ、及び他の標準的な論理機能を有する。ALU の結果は、レジスタである ALU 出力 618、ALU 条件コード 620、及び行先オペランド結果 622 に格納される。ファイルコンテキストレジスタ 616、フラグ選択レジスタ 626、及びリテラルフィールドレジスタ 630 は、単に前のフェーズ 560 からコピーされる。テストマルチプレクサ 604 は、条件ジャンプがジャンプを生ずるか否かを決定するために設けられ、その結果はテスト結果レジスタ 624 に格納される。テストマルチプレクサ 604 は、フェッチ制御機構 511 のような類似の判断とともに、第 1 フェーズ 500 において実行され得る。スタック交換 608 は、スタック 594 からプログラムカウンタをフェッチすることにより、又はプログラムカウンタをそのスタックに入れることによってスタックを上限に移動させ、その結果はプログラム制御機構 634、プログラムカウンタ 638、及びスタック 640 レジスタに格納される。SRAM アドレスは所望に応じてこのフェーズ 600 においてインクリメントされ得る。別のデバッグアドレス 642 のための別のロード制御機構 610 は、このフェーズにおいても誤り制御を可能にするために、この時点でパイプライン 505 から強制的にわたされる。図面では一体に示されている QRAM 及び QALU 606 は、キュー チャネル及びコマンド レジスタ 587 から読み出され、SRAM に格納され、キューを再編成し、必要に応じてデータ及びポインタを加えたり取り除いたりして、データのキューを管理し、その結果をテストマルチプレクサ 604、及びキュー フラグ及びキュー アドレス レジスタ 628 に送る。従って、QRAM 及び QALU 606 は、3 つのプロセッサのためのキューを管理する任務、ソフトウェアによって CPU 上で順次実行される従来通りのタスクを想定しており、キューマネージャ 606 は、代わりに高速化した実質的に同時並行のハードウェア キュー イングを提供する。

20

### 【0063】

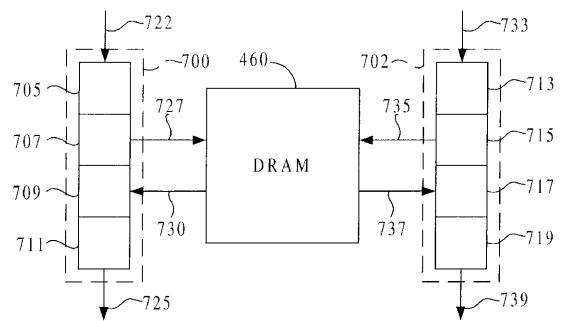

図 16 は、キューマネージャ 606 によって管理される 32 のハードウェア キューの 2 つを示しており、そのキューのそれぞれは、SRAM ヘッド、SRAM テール、及び DRAM ボディにおいて情報をキューに入れる能力を有しており、これによって各キューの拡張及び個別の編成が可能となる。従って FIFO 700 は、SRAM 記憶ユニット 705、707、709、及び 711 を有し、それぞれが全部で 32 個のバイトに対して 8 個のバイトを含んでいるが、これらのユニットの数及び処理能力は、実施形態によって変えることができる。同様に、FIFO 702 は SRAM 記憶ユニット 713、715、717、及び 719 を有している。SRAM ユニット 705 及び 707 は、FIFO 700 のヘッドであり、ユニット 709 及び 711 は FIFO のテールであり、ユニット 713 及び 715 は FIFO 702 のヘッドであり、ユニット 717 及び 719 はその FIFO のテールである。FIFO 700 の情報は、矢印 722 で示すように、ヘッドユニット 705 又は 707 に書き込まれ得、矢印 725 で示すように、テールユニット 711 又は 709 から読み書きの両方が行われ得、又はテールユニット 709 又は 741 から読み書きの両方が行われ得、データ転送及びラテンシーが最小限にされている。同様に、FIFO 702 のため

30

40

50

の情報は、一般的に、矢印 733 で示すように、ヘッドユニット 713 又は 715 に書き込まれ、矢印 739 で示すように、テールユニット 717 又は 719 から読み出されるが、それが書き込まれた同一のヘッド又はテールユニットから読み出されることもある。

#### 【0064】

SRAM FIFO 700 及び 702 は、共に DRAM 460 に接続されており、この DRAM 460 によって、これらの FIFO を無限に拡張し SRAM ヘッド及びテールが一杯になった状況を取り扱うことが可能となる。例えば、32 個のキューのうちの、Q(0) とラベル付けされた第 1 のキューは、矢印 727 で示すように、FIFO 700 のヘッド又はテールにキューを入れる代わりにキーマネージャの指示の下で動作する DMA ユニットによって DRAM 420 においてエントリをキューに入れることができる。DRAM 460 に格納されたエントリは、矢印 730 で示されるように、SRAM ユニット 709 に戻され、その FIFO の長さ及び終了時間が延長される。SRAM から DRAM への転換は、一般的に SRAM が一杯になったときのために準備されている。DRAM はより低速であり、DMA 転送によって更なるラテンシーが生ずるからである。従って Q(0) は、FIFO 700 及び DRAM 460 の両方におけるキーマネージャ 600 によって格納されたエントリを含み得る。同様に、FIFO 702 に向かう情報は、例えば Q(27) に対応するものであり得、矢印 735 で示すように、DMA によって DRAM 460 に転送され得る。より低速の DRAM 460 にも関わらず、費用的に有効にキューを作成する能力は、初期化の間にユーザが決定でき、これにより所望に応じてキューのサイズを変更することが可能となる。DRAM 460 にキューイングされた情報は、矢印 737 に示すように、SRAM ユニット 717 に戻される。

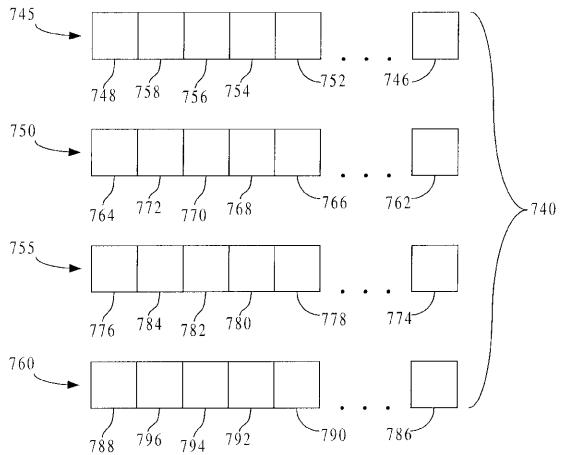

#### 【0065】

32 のハードウェアキューのそれぞれのステータスは、従来通り図 17 に示すように、4 つの 32 ビットのレジスタのセット 740 に維持され、そこからアクセスされる。各レジスタにおける特定のビットは特定のキューに対応する。そのレジスタは、Q-Out\_Ready 745、Q-In\_Ready 750、Q-Empty 755、及び Q-Full 1760 とラベル付けされている。特定のビットが Q-Out\_Ready レジスタ 750 にセットされた場合、そのビットに対応するキューは読み出される状態となった情報を含み、Q-In\_Ready 752 レジスタにおける同一のビットがセットされることは、そのキューが書き込み可能な状態となったことを意味する。同様に Q-Empty レジスタ 755 における特定のビットを正値にセットすることは、そのビットが空になったことに対応するキューを意味し、Q-Full 1 レジスタ 760 の特定のビットが正値にセットされることは、そのビットが一杯になったことに対応するキューを意味する。従って Q-Out\_Ready 745 は、ビット(27)752、ビット(28)754、ビット(29)756、及びビット(30)を含むビット(0)746～ビット(31)748 を含む。Q-In\_Ready 752 は、ビット(27)766、ビット(28)768、ビット(29)770、及びビット(30)772 を含むビット(0)762～ビット(31)764 を含む。Q-Empty 755 は、ビット(27)778、ビット(28)780、ビット(29)782、及びビット(30)784 を含むビット(0)774～ビット(31)776 を含み、Q-Full 1760 は、ビット(27)790、ビット(28)792、ビット(29)794、ビット(30)796 を含むビット(0)786～ビット(31)788 を含む。

#### 【0066】

FIFO 700 に対応する Q(0) は、フリーのバッファキューであり、全ての利用可能なバッファであるアドレスのリストを保持する。このキューは、マイクロプロセッサ又は他のデバイスがフリーバッファアドレスを必要とするときにアドレス指定され、従って共通に感知できる DRAM 460 を含む。従って、フリーバッファアドレスを必要とするデバイスは、Q(0) をチェックし、そのアドレスを得る。FIFO 702 に対応する Q(27) は、受信バッファディスクリプタキューである。受信シーケンサによって受信されたフレームが処理された後、そのシーケンサはそのフレームのためのディスクリプタを Q

10

20

30

40

50

(27)に格納しようとする。このようなディスクリプタの位置がS R A Mにおいて即座に利用可能である場合は、Q - I n \_ R e a d y 7 5 0のビット(27)766がセットされる。そうでない場合は、そのシーケンサはキューマネージャがS R A MからD R A MへD M A転送を開始させて、受信ディスクリプタを格納するための空間を空けるのを待たなければならない。

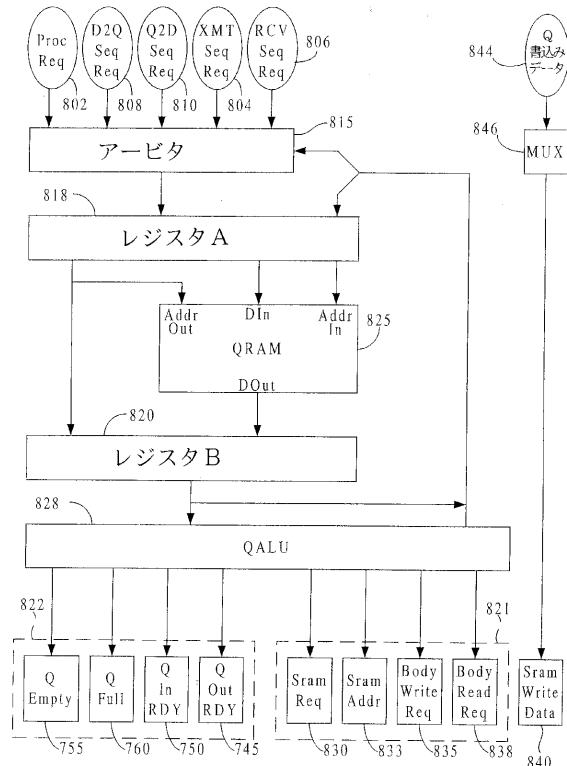

#### 【0067】

S R A Mとプロセッサとの間でのキューエントリの移動、受信及び送信シーケンサ間のキューエントリの移動、及びS R A MとD R A M間のキューエントリの移動を管理するキューマネージャの動作は、図18により詳細に示されている。キューを利用するリクエストとしては、プロセッサリクエスト802、送信シーケンサリクエスト804、及び受信シーケンサリクエスト806がある。そのキューのための他のリクエストは、D R A MからS R A Mへのリクエスト808及びS R A MからD R A Mへのリクエスト810であり、これはキューのD R A M及びS R A Mヘッド又はテール間でデータをやりとりする際にキューマネージャの代わりに作用する。これらの様々なリクエストの何れが次のサイクルにおいてキューマネージャを用いるかの決定は、優先ロジックアービタ815によって取り扱われる。高い周波数での動作を可能にするため、キューマネージャはパイプライン型で、レジスタA818及びレジスタB820が一時的な記憶機構を提供するとともに、ステータスレジスタ822が次の更新までステータスを維持する。キューマネージャはD M A、受信及び送信シーケンサリクエストのために偶数番目のサイクルを予約し、プロセッサリクエストのために奇数番目のサイクルを予約する。二重ポートQ R A M 8 2 5は、各キューに関連する変数を格納し、各キューのための変数としては、キューのS R A M条件に対応するヘッド書き込みポインタ、ヘッド読み出しポインタ、テール書き込みポインタ、及びテール読み出しポインタと、キューのD R A M条件及びキューのサイズに対応するボディ書き込みポインタ及びボディ読み出しポインタとが挙げられる。

10

20

#### 【0068】

アービタ815が実行される次の処理を選択した後、Q R A M 8 2 5の変数がフェッチされ、Q A L U 8 2 8によって選択された処理に従って変更され、S R A M読み出しリクエスト830又はS R A M書き込みリクエスト840が生成され得る。その変数は更新され、更新されたステータスは、ステータスレジスタ822及びQ R A M 8 2 5に格納される。ステータスはアービタ815にも供給されて、以前にリクエストされた処理が完了したことと示す信号を供給して、リクエストの重複を防止する。ステータスレジスタ822は、4つのキューレジスタQ - O u t \_ R e a d y 7 4 5、Q - I n \_ R e a d y 7 5 0、Q - E m p t y 7 5 5、及びQ - F u l l 7 6 0を更新して、アクセスされたキューの新たなステータスを反映するようとする。同様に更新されるのは、S R A Mアドレス833、ボディ書き込みリクエスト835及びボディ読み出しリクエスト838であり、これらはD M Aを介してそのキューのためにS R A Mヘッド及びテールとやりとりする。或いは、様々なプロセスが、Q書き込みデータ844によって示されるように、キューへの書き込みを行おうとすることもあり得、そのプロセスはマルチプレクサ846によって選択され、S R A M書き込みリクエスト840にパイプライン処理される。S R A Mコントローラは、アクセスされたキューのテールの書き込み又はヘッドの読み出し及び確認応答を戻すことによって、読み出し及び書き込みリクエストをサービスする。このようにして、様々なキューが利用され、それらのステータスが更新される。

30

40

#### 【0069】

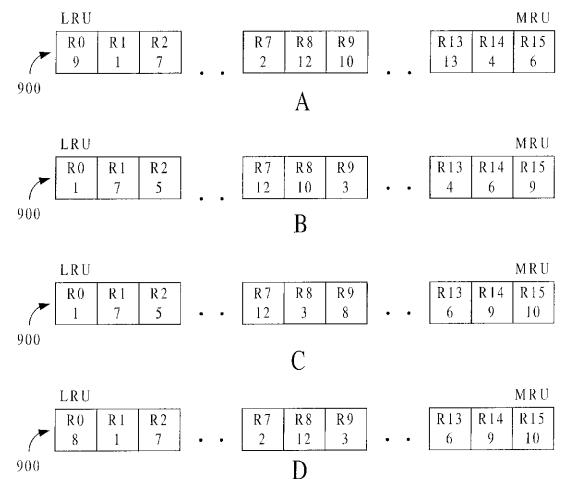

図19A乃至図19Cは、I N I C キャッシュメモリに維持するコンテキスト又はC C Bを選択するために用いられる最低使用頻度レジスタ900を示す。この実施形態におけるI N I Cは、所定の時間においてS R A Mに最大16のC C Bをキャッシュでき、新たなC C Bがキャッシュされるときには、古いものが破棄されなければならないことが多く、破棄されるC C Bは、通常、このレジスタ900に従って最小使用頻度のC C Bとして選択されたものである。この実施形態では、最大256のC C BのためのハッシュテーブルがS R A Mに維持されており、一方最大256の全C C BがD R A Mに保持されている。

50

最小使用頻度レジスタ900は、R0 - R15とラベル付けされた16個の4ビットブロックを有し、各ブロックはSRAMのキャッシュユニットに対応する。初期化の際、そのブロックは0 - 15に番号付けされ、番号0は、最小使用頻度(LRU)キャッシュユニットを表すブロックに格納され、番号15は、最大使用頻度(MRU)キャッシュユニットを表すブロックに格納される。図19Aは、LRUブロックR0が番号9を保持しており、MRUブロックR15が番号6を保持している、任意の時点におけるレジスタ900を示す。

#### 【0070】

現在SRAMに保持されているものとは異なるCCBがキャッシュされたとき、図19Aでは、番号9を保持しているLRUブロックR0が読み出され、新たなCCBが番号9に対応するSRAMキャッシュユニットに格納される。番号9に対応する新たなCCBが現時点で最も使用頻度の高いCCBであることから、番号9は、図19Bに示すように、MRUブロックに格納される。他の番号は全て1個左のレジスタブロックにシフトされ、LRUブロックに番号1が残る。以前に番号9に対応するSRAMユニットにキャッシュされたCCBは、よりゆっくりとではあるが、よりコストパフォーマンスの良い形でDRAMに移されている。

#### 【0071】

図19Cは、次に使用されるCCBが常にSRAMにキャッシュされたときの結果を示す。この例では、CCBが番号10に対応するSRAMユニットにキャッシュされており、そのCCBを使用した後、番号10にMPUブロックに格納される。番号10以外の最近使用された番号のみ(レジスタブロックR9 - R15)が左側にシフトされ、LRUブロックには番号1が残る。このようにして、INITはSRAMキャッシュに最もアクティブなCCBを維持する。

#### 【0072】

場合によっては、使用されているCCBが、限定されたキャッシュメモリに保持することが望ましくないものであることがある。例えば、終了したことが判っているコンテキストのためのCCBは、キャッシュせずに、他のキャッシュされたCCBがSRAMに長く残るようにすることが好ましい。この場合、デキャッシュ可能なCCBを保持するキャッシュユニットを表す番号が、MRUブロックR15でないMRUブロックR0に格納され、従ってデキャッシュ可能なCCBがLRUブロックR0に保持された番号に対応するSRAMユニットにキャッシュされる新たなCCBが使用されるとすぐに置きかえられる。図19Dは、番号8(図19CにおけるブロックR9にあったもの)が、使用され次に終了されるCCBに対応する場合を示す。この場合では、番号8がブロックR6から取り除かれ、LRUブロックR0に格納される。次いでブロックR9の左側(R1 ~ R8)に以前に格納された全ての番号は、1個右側のブロックにシフトされる。

#### 【0073】

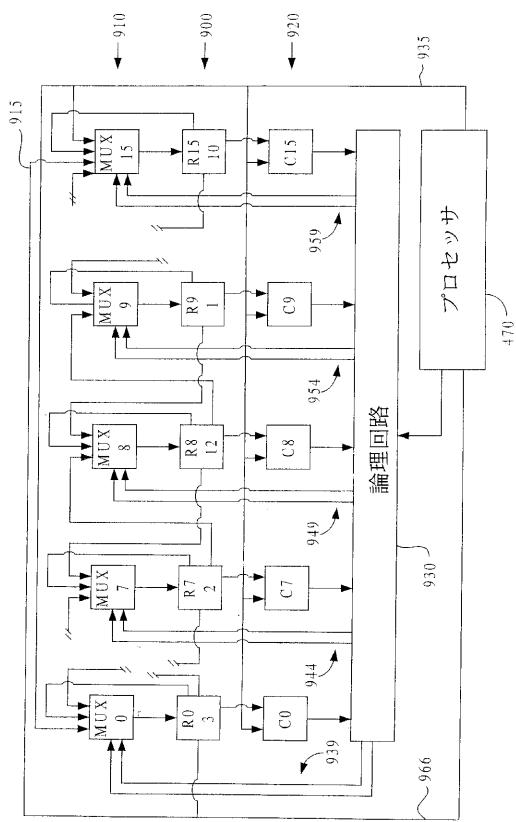

図20は、最低使用頻度レジスタ900を操作するために用いられる論理ユニットをいくつか示す。16個の3又は4入力マルチプレクサ910のアレイ(明示のため、そのうちマルチプレクサMUX0、MUX7、MUX8、MUX9、及びMUX15のみが示されている)は、最低使用頻度レジスタ900の対応する16個のブロックに供給される出力を有する。例えば、MUX0の出力は、ブロックR0に格納され、MUX7の出力はブロックR7に格納される等である。レジスタブロックのそれぞれの値は、対応するマルチプレクサのための入力に接続されており、かつブロック番号のシフトの際に使用するために両隣のマルチプレクサの入力にも接続されている。例えば、R8に格納された番号は、MUX7、MUX8、及びMUX9の入力に供給される。MUX0及びMUX15のそれぞれは、ただ1つの隣接ブロックしか有しておらず、それらのマルチプレクサのための別の入力がLRU及びMRUブロックの選択のためにそれぞれ用いられる。MUX15は、4入力マルチプレクサとして図示されており、入力915はR0に格納された番号を供給する。

#### 【0074】

10

20

30

40

50

16個の比較器920のアレイのそれぞれが、最低使用頻度レジスタ900の対応するブロックに格納された値を受け取る。各比較器は、ライン935を介してプロセッサ470からの信号を受け取り、従ってプロセッサ470によって送られた一致する番号を有するレジスタブロックが、論理回路930に真の値を出力し、一方他の15個の比較器は偽の値を出力する。論理回路930は、マルチプレクサへの入力を選択するためにマルチプレクサのそれぞれに接続された一対の選択ラインを制御し、従ってレジスタブロック番号のシフトを制御する。従って選択ライン939はMUX0を制御し、選択ライン944はMUX7を制御し、選択ライン949はMUX8を制御し、選択ライン954はMUX9を制御し、選択ライン959はMUX15を制御する。

## 【0075】

10

CCBが使用されるとき、プロセッサ470は、そのCCBが16個のキャッシュユニットの1つを現在保持されているCCBに一致するか否かを調べるためのチェックを行う。一致が見出された場合は、そのプロセッサは、ライン935を通してそのキャッシュユニットに対応するブロック番号、例えば番号12を有する信号を送る。比較器920は、そのライン935からの信号とブロック番号とを比較し、比較器C8はその信号に一致するブロックR8に真の出力を供給し、他の全ての比較器は偽の値を出力する。論理回路930はプロセッサ470からの制御の下で、選択ライン959を用いてMUX15のためライン935からの入口クを選択し、MRUブロックR15に番号12を格納する。論理回路930も、MUX15を除いて、MUX8及びより高位のマルチプレクサのための対になつた選択ラインを通して信号を送り、各マルチプレクサMUX8及びそれより上位のマルチプレクサへの入力として、1個右側のレジスタブロック(R9-R15)に格納された値を選択することにより、それらの出力を1ブロック左にシフトさせる。MUX8の左側のマルチプレクサの出力は一定に選択される。

20

## 【0076】

一方プロセッサ470が16個のキャッシュユニットのなかでCCBについて一致を見出せなかつた場合は、プロセッサは、ライン966を通してLRUブロックR6から読み出しを行い、LRUブロックに対応するキャッシュを特定し、そのキャッシュに格納されたデータをDRAMに書き込む。この場合では番号3であるR0に格納された番号は、MRUブロックR5における記憶機構のためにMUX15への入力915としてライン959を選択することによって選び出される。他の15個のマルチプレクサは、それらの各レジスタブロックにそれぞれの右隣のレジスタブロックに格納されていた番号を出力する。

30

## 【0077】

プロセッサが、使用後にキャッシュからCCBを取り除こうとしている状況では、MRUブロックR5ではなく、LRUブロックR0がそのCCBを維持するキャッシュユニットに対応する番号の置き換えのために選択される。SRAMから除去するためにLRUブロックR0に置かれるCCBに対応する番号(例えばブロックR9に保持されている番号1)は、ライン935を通してプロセッサ470に送られ、それは比較器C9によって一致を取られる。プロセッサは、論理回路930にMUX0への入力935としてライン939を選択することにより、番号1をR0に入力するように命令する。MUX9への選択ライン954は、入力としてレジスタブロックR8に保持された番号を選択し、従ってR8からの番号はR9に格納される。R0~R9の間の他のレジスタブロックによって保持された番号は、同様に右側にシフトされ、R9の右側のレジスタブロックにおける番号は一定に維持される。これによって、多くのサイクルにわたつて使用されなくなつたCCBが限りのあるキャッシュメモリに維持されることがなくなるとともに、それらの特定する番号がMRUからLRUブロックにレジスタブロックを通して動くことになる。

40

## 【0078】

既に述べたように、上述のデータ通信の処理のための装置及びシステムは、大きなコネクションベースのメッセージを処理するために必要な時間を劇的に短縮させる。プロトコル処理速度は、専用に設計されたプロトコル処理ハードウェアによって汎用CPUが従来のプロトコルソフトウェアを実行する場合と比較して非常に高速化され、かつホストのCP

50

Uへの割り込みも実質的に低減する。これらの利点は、インテリジェントネットワークインターフェースカード（INIC）を追加することによって既存のホストにもたらすことができるが、或いはプロトコル処理ハードウェアをCPUに組み込んでもよい。何れの場合も、プロトコル処理ハードウェア及びCPUは、インテリジェントに与えられたメッセージを処理するデバイスを決定し、メッセージの条件に基いてその処理の割り当てを変更することができる。

【図面の簡単な説明】

【図1】 ネットワーク通信を高速化するための通信処理装置を有するホストコンピュータを備えた、本発明の装置の平面図。

【図2】 高速バス、低速バス、及び高速バスと低速バスとの間のコネクションコンテキストの転送を含む、ネットワーク通信の処理における図1のホストの情報の流れを示す図。

10

【図3】 本発明によるメッセージ受信の流れ図。

【図4】 A図は、低速バスによって処理される初めのメッセージパケットを受信した、図1のホストにおける情報の流れを示す図、B図は、高速バスによって処理される初めのメッセージパケットを受信した、図1のホストにおける情報の流れを示す図、C図は、高速バスによって処理される順次式のメッセージパケットを受信した、図4Bのホストにおける情報の流れを示す図、D図は、低速バスに戻すための処理を生じさせる誤りを有するメッセージパケットを受信した、図4Cのホストにおける情報の流れを示す図。

【図5】 高速バス又は低速バスの何れかによってメッセージを転送する、図1のホストにおける情報の流れを示す図。

20

【図6】 TCP/IP処理スタックを有するクライアントに関するインテリジェントネットワークインターフェースカード（INIC）の第1の実施形態における情報の流れを示す図。

【図7】 パケット制御シーケンサ、フライバイシーケンサを含む、図6に示すINICの実施形態のためのハードウェアロジックを示す図。

【図8】 INICによって受信されたときにヘッダバイトを解析する、図7のフライバイシーケンサを示す図。

【図9】 TCP/IP処理スタックを有するサーバに関するINICの第2の実施形態における情報の流れを示す図。

30

【図10】 高速バスのための通信制御ブロックを生成し制御するための、図9にインストールされたコマンドドライバを示す図。

【図11】 NetBios通信のために構成された図10のコマンドドライバ及びTCP/IPスタックを示す図。

【図12】 図6のクライアントと図9のサーバとの間の通信の交換を示す図。

【図13】 図9のINICに含められたハードウェア機構を示す図。

【図14】 各フェーズに1個のプロセッサがある3つのフェーズを含む、図13のINICに含められた3個1組のパイプライン型マイクロプロセッサを示す図。

【図15】 A図は図14のパイプライン型マイクロプロセッサの第1フェーズを示す図、B図は図14のパイプライン型マイクロプロセッサの第2フェーズを示す図、C図は図14のパイプライン型マイクロプロセッサの第3フェーズを示す図。

40

【図16】 図14のマイクロプロセッサと相互作用し、かつSRAM及びDRAMを備えた複数のキュー記憶ユニットを示す図。

【図17】 図16のキュー記憶ユニットのための、1組のステータスレジスタを示す図。

。

【図18】 図16及び図17のキュー記憶ユニット及びステータスレジスタと相互作用する、キーマネージャを示す図。

【図19】 A図はキャッシュメモリの割り当てのために用いられる最低使用頻度レジスタの様々な動作段階の1つを示す図、B図はキャッシュメモリの割り当てのために用いられる最低使用頻度レジスタの様々な動作段階の1つを示す図、C図はキャッシュメモリの

50

割り当てのために用いられる最低使用頻度レジスタの様々な動作段階の1つを示す図、D図はキャッシュメモリの割り当てのために用いられる最低使用頻度レジスタの様々な動作段階の1つを示す図。

【図20】 図19A乃至図19Dの最低使用頻度レジスタを操作するための用いられるデバイスを示す図。

【図1】

【図2】

【図3】

【 図 4 】

【図5】

【 図 6 】

【 図 7 】

【 四 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

A

B

【図 1 6】

【図 1 7】

【図 1 8】

【図 1 9】

【図20】

---

フロントページの続き

- (72)発明者 クラフト, ピーター, ケイ

アメリカ合衆国, カリフォルニア州・94114, サンフランシスコ, ヘンリー・ストリート・1

56

- (72)発明者 ヒギン, デヴィッド, エー

アメリカ合衆国, カリフォルニア州・95070, サラトガ, ロス・アラモス・ドライブ・178

80

- (72)発明者 フィルブリック, クライヴ, エム

アメリカ合衆国, カリフォルニア州・95125, サンノゼ, ロイコット・ウェイ・1170

- (72)発明者 スター, ダリル

アメリカ合衆国, カリフォルニア州・95035, ミルピタス, フォルソム・コート・446

審査官 小曳 満昭

- (56)参考文献 特開平02-238544 (JP, A)

特開平09-128314 (JP, A)

特開平03-250946 (JP, A)

特開平02-137555 (JP, A)

特開昭62-038060 (JP, A)

特開平01-256248 (JP, A)

向井伸一郎, LANカード周辺ハードウェア動作概要と機能評価, インターフェース, CQ出版

株式会社, 1992年 4月 1日, 第18巻, 第4号, p.223~237

陣崎 明 外3名, 大規模広域並列分散システムの実現を目指す超高速インターネットの構想,

電子情報通信学会技術研究報告 CPSY97-61, 社団法人電子情報通信学会, 1997年

8月20日, 第97巻, 第226号, p.75~82

(58)調査した分野(Int.Cl., DB名)

G06F 13/00、

H04L 12/00-12/26、12/50-13/18、

29/00-29/12