(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4689440号

(P4689440)

(45) 発行日 平成23年5月25日(2011.5.25)

(24) 登録日 平成23年2月25日(2011.2.25)

(51) Int.Cl.

H04N 5/225 (2006.01)

F 1

H04N 5/225

F

請求項の数 10 (全 33 頁)

(21) 出願番号 特願2005-321230 (P2005-321230)

(22) 出願日 平成17年11月4日 (2005.11.4)

(65) 公開番号 特開2007-129573 (P2007-129573A)

(43) 公開日 平成19年5月24日 (2007.5.24)

審査請求日 平成20年10月31日 (2008.10.31)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 福井 俊之

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 金子 秀彦

最終頁に続く

(54) 【発明の名称】撮像装置、及び処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

撮像手段により得られた映像を処理してクライアントへ送信する撮像装置であって、

前記クライアントからの映像要求のパラメータに応じた処理映像を生成するための処理

を前記撮像手段により得られた映像に対して行う処理手段と、

第1のクライアントからの映像要求の第1のパラメータに応じた第1の処理映像を生成

するための処理を前記撮像手段により得られた映像に対して前記処理手段が行っていると

きに、第2のクライアントから第2のパラメータの映像要求を受信した場合、前記撮像手

段により得られた1フレームの映像から、前記第1のパラメータに応じた前記第1の処理

映像と前記第2のパラメータに応じた第2の処理映像とを生成するための処理をフレーム

レートに応じた1映像期間内にできるか否かを判定する判定手段とを有し、

前記処理手段は、前記撮像手段により得られた1フレームの映像から前記第1の処理映

像及び前記第2の処理映像を生成するための処理を前記1映像期間内にできると前記判定

手段により判定された場合、前記映像に対して前記第1の処理映像及び前記第2の処理映

像を生成するための処理を行うことを特徴とする撮像装置。

## 【請求項 2】

前記処理手段は、前記1映像期間内に前記第1の処理映像及び前記第2の処理映像を生

成するための処理ができないと前記判定手段により判定された場合、前記第2の処理映像

を生成するための処理をせず、前記第2のクライアントに対して拒否回答を送信すること

を特徴とする請求項1に記載の撮像装置。

**【請求項 3】**

前記判定手段は、前記第1の処理映像及び前記第2の処理映像を生成するための処理が前記1映像期間内にできるか否かを、前記映像のデータ量と前記第1のパラメータ及び前記第2のパラメータとに基づいて判定することを特徴とする請求項1又は2に記載の撮像装置。

**【請求項 4】**

前記第1のパラメータ及び前記第2のパラメータには圧縮率に関するパラメータが含まれることを特徴とする請求項1乃至3のうちいずれか1項に記載の撮像装置。

**【請求項 5】**

前記第1のパラメータ及び前記第2のパラメータには解像度に関するパラメータが含まれることを特徴とする請求項1乃至3のうちいずれか1項に記載の撮像装置。

10

**【請求項 6】**

前記第1のパラメータ及び前記第2のパラメータには、前記撮像装置により得られた映像内の指定領域に関するパラメータが含まれることを特徴とする請求項1乃至3のうちいずれか1項に記載の撮像装置。

**【請求項 7】**

前記第1のパラメータに第1の圧縮率と第1の解像度とに関するパラメータが含まれ、前記第2のパラメータに第2の圧縮率と前記第1の解像度とに関するパラメータが含まれる場合、前記処理手段は、前記撮像手段により得られた映像に対して前記第1の解像度に応じた一の解像度変換を行い、当該一の解像度変換後の映像に対して前記第1の圧縮率に応じた圧縮処理と、前記第2の圧縮率に応じた圧縮処理とを行って前記第1の処理映像及び前記第2の処理映像を生成することを特徴とする請求項1乃至3のうちいずれか1項に記載の撮像装置。

20

**【請求項 8】**

前記撮像手段により得られた映像を圧縮処理するための圧縮パラメータが前記第1のパラメータに含まれ、前記圧縮パラメータと前記映像について解像度変換処理するための解像度パラメータとが前記第2のパラメータに含まれる場合、前記処理手段は、前記撮像手段により得られた映像に対する前記解像度変換処理と前記映像に対する前記圧縮処理とを並列に行うことの特徴とする請求項1乃至3のうちいずれか1項に記載の撮像装置。

30

**【請求項 9】**

撮像手段により得られた映像を処理してクライアントへ送信する撮像装置が行う処理方法であって、

前記クライアントからの映像要求のパラメータに応じた処理映像を生成するための処理を前記撮像手段により得られた映像に対して行う処理工程と、

第1のクライアントからの映像要求の第1のパラメータに応じた第1の処理映像を生成するための処理を前記撮像手段により得られた映像に対して前記処理工程が行っているときに、第2のクライアントから第2のパラメータの映像要求を受信した場合、前記撮像手段により得られた1フレームの映像から、前記第1のパラメータに応じた前記第1の処理映像と前記第2のパラメータに応じた第2の処理映像とを生成するための処理をフレームレートに応じた1映像期間内にできるか否かを判定する判定工程とを有し、

40

前記処理工程では、前記撮像手段により得られた1フレームの映像から前記第1の処理映像及び前記第2の処理映像を生成するための処理を前記1映像期間内にできると前記判定工程により判定された場合、前記映像に対して前記第1の処理映像及び前記第2の処理映像を生成するための処理を行うことを特徴とする処理方法。

**【請求項 10】**

前記処理工程では、前記1映像期間内に前記第1の処理映像及び前記第2の処理映像を生成するための処理ができないと前記判定工程により判定された場合、前記第2の処理映像を生成するための処理をせず、前記第2のクライアントに対して拒否回答を送信することを特徴とする請求項9に記載の処理方法。

**【発明の詳細な説明】**

50

**【技術分野】****【0001】**

本発明は、動画像データをネットワーク上に送出する撮像装置、及び処理方法に関するものである。

**【背景技術】****【0002】**

近年、インターネットが普及し、WWW (World Wide Web) 等による情報発信が一般的に行なわれるようになってきた。その様な中で、リアルタイムに映像を撮影し、その映像(動画像)をネットワーク上に発信する機能を有する撮像装置が出現している。キヤノン社製のネットワークカメラサーバVB-C10はその好例である。

10

**【0003】**

一方、ネットワークを介してユーザにサービスを提供しようとすると、ユーザの要求は多岐にわたるため、ある時点で撮影された1つの入力画像に対して、複数の異なるパラメータで処理した符号化データを要求される場合がある。このような要求に対応しようとした画像処理装置の第1の例としては、符号化処理部を複数持つことにより、対応しようとするものが存在する(例えば、特許文献1参照)。

**【0004】**

また、画像処理装置の第2の例としては、予めROMに格納している各種変換アルゴリズムを必要に応じて読み出し、DSPにそのアルゴリズムの処理を行わせることによってユーザの多様な要求に答えようとするものが存在する(例えば、特許文献2参照)。

20

**【0005】**

**【特許文献1】**特開2003-309853号公報(第19頁、図1及び図6、第20頁、図3)

**【特許文献2】**特開平6-125411号公報(第8頁、図1、第10頁、図4)

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

特許文献1に記載の技術のように、符号化処理部を複数持つことで複数の画像処理の要求に対応しようとする場合は、その処理ユニット数によってサービスできる内容の制限を受けることになる。処理ユニットの数を増やせば制限は緩くなるが、映像配信システムの撮影側機能をもつネットワークカメラサーバなどは一般に小型化を要求されるものである。そして、そこに実装できる処理ユニットの数は、基板/チップ面積や発熱量などによって制限を受けるので、実際には処理ユニットの数は限られたものになるという課題がある。

30

**【0007】**

一方、リアルタイムに映像を撮影し、その映像を監視用途などに蓄積及び配信に利用する場合には、撮像装置から入ってくる映像を取りこぼすことは許されない。例えば、1秒間に30フレームの映像を撮影するビデオカメラ入力から映像入力を得る場合、あるフレームに関する処理を行うことが許される時間は1枚のフレーム画像の入力に要する時間である原則1/30秒である。この1枚のフレーム画像の入力に要する時間を「1映像期間」と呼ぶことにする。その中で先に述べた多種多様なユーザの要求に応えることがシステムに求められる。また、映像撮影部を遠隔から操作できることのできるネットワークカメラにおいては、リアルタイム性、及び低遅延であることが求められる。

40

**【0008】**

特許文献2に記載の技術は、単純に複数の画像処理をアルゴリズムに従ってDSPが時分割的に並行して実施するのみであり、1映像期間内に処理が完了する保証がないという課題がある。

**【0009】**

即ち、動画像データをネットワーク上に送出する従来の撮像装置では、当該ネットワーク上で様々な要求を行うユーザに対して、実時間性を守って複数のサービスを提供するこ

50

とが困難であるという課題があった。

【0010】

本発明は上述の問題点にかんがみてなされたものであり、ネットワーク上で様々な要求を行うユーザに対して、実時間性を守って複数のサービスを提供することを可能とする撮像装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

前記課題を解決するために本発明に係る撮像装置は、撮像手段により得られた映像を処理してクライアントへ送信する撮像装置であって、前記クライアントからの映像要求のパラメータに応じた処理映像を生成するための処理を前記撮像手段により得られた映像に対して行う処理手段と、第1のクライアントからの映像要求の第1のパラメータに応じた第1の処理映像を生成するための処理を前記撮像手段により得られた映像に対して前記処理手段が行っているときに、第2のクライアントから第2のパラメータの映像要求を受信した場合、前記撮像手段により得られた1フレームの映像から、前記第1のパラメータに応じた前記第1の処理映像と前記第2のパラメータに応じた第2の処理映像とを生成するための処理をフレームレートに応じた1映像期間内にできるか否かを判定する判定手段とを有し、前記処理手段は、前記撮像手段により得られた1フレームの映像から前記第1の処理映像及び前記第2の処理映像を生成するための処理を前記1映像期間内にできると前記判定手段により判定された場合、前記映像に対して前記第1の処理映像及び前記第2の処理映像を生成するための処理を行うことを特徴とする。

10

20

【発明の効果】

【0012】

本発明によれば、ネットワーク上で様々な要求を行うユーザに対して、実時間性を守って複数のサービスを提供することが可能となる。

【発明を実施するための最良の形態】

【0021】

以下、添付図面を参照して、本発明の好適な実施形態を詳細に説明する。

【0022】

(第1の実施形態)

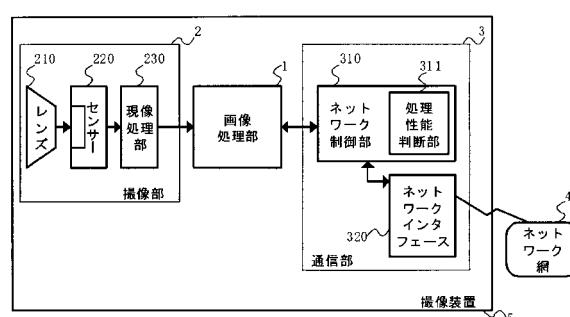

図1は、本発明の第1の実施形態に係る撮像装置示すブロック図である。

30

図1において撮像装置5には画像処理部1、撮像部2、及び通信部3の大きく分けて3つの構成要素が存在する。撮像部2は、映像が入射されるレンズ210、レンズで集められた光を電気信号に変換するセンサー220、センサー220から得られる信号を現像する現像処理部230からなる。

【0023】

現像された信号は画像データとして画像処理部1に与えられ、そこで符号化などの処理を経た後、通信部3に符号化データとして与えられる。通信部3では、ネットワーク制御部310が入力された符号化データを送出するネットワークの形態に応じてパケット化するなどの処理を行い、ネットワークインターフェース320に対して送信用データとして受け渡す。ネットワークインターフェース320はネットワーク網4に対してそのネットワークの形態に応じた形でデータを送出する。ネットワーク網4はEthernet(登録商標)等の有線LAN、IEEE802.11b等に代表される形式の無線LAN、もしくはISDN等の公衆回線網などを代表的なものとして想定することができる。

40

【0024】

なお、本実施形態では図1において画像処理部1、撮像部2、通信部3はそれぞれ別のブロックとして記述しているが、本実施形態を実ハードウェアで構成する際には、これらのブロックをそれぞれ別のICとして実現する、もしくは各部のいくつかの部分(例えば現像処理部230と画像処理部1とネットワーク制御部310)をまとめて1チップ上に実現するなどの様々な実現形態が可能であり、その形態は本実施形態において制限されるものではない。

50

## 【0025】

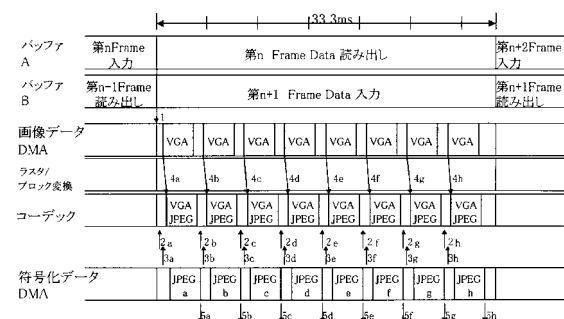

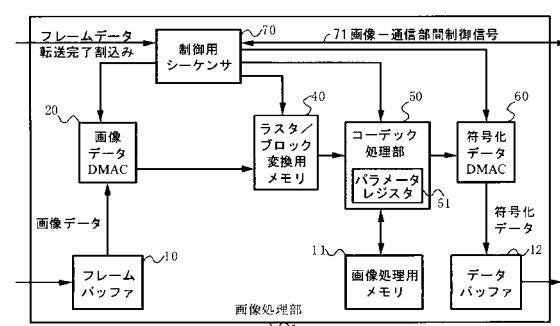

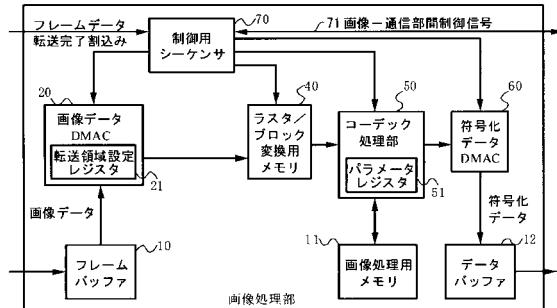

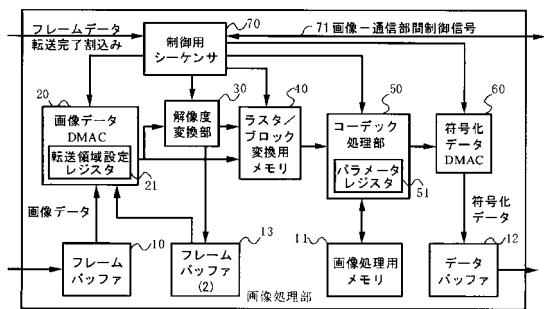

図2は、画像処理部1の詳細な構成を示すブロック図である。

図2において、画像処理部1にはフレームバッファ10、画像データDMA(ダイレクトメモリアクセス・コントローラ)20、ラスター/ブロック変換用メモリ40、コーデック処理部50、符号化データDMA60、制御用シーケンサ70、画像処理用メモリ11、データバッファ12がそれぞれ示されている。制御用シーケンサ70は、この画像処理部1の中の画像データDMA20、ラスター/ブロック変換用メモリ40、コーデック処理部50、符号化データDMA60とそれぞれ制御用信号線で接続されており、これらの各ユニットの制御を実施する。更に、現像処理部230とは、フレームデータ転送完了割込み信号線、通信部3とは画像-通信部間制御信号71で接続され、相互に信号をやり取りして動きを制御する。また、コーデック処理部50は、画像処理用メモリ11と接続され、このメモリを利用して各種画像処理を実施する。更に、コーデック処理部50は内部にパラメータレジスタ51を持っており、このパラメータレジスタに対して制御用シーケンサ70が書き込んだ値に従って、各種画像処理を実施するものとする。

## 【0026】

なお、フレームバッファ10、画像処理用メモリ11、データバッファ12のそれぞれは画像処理部のそれ以外の構成要素が1つのICの中で実現される場合に、それらと同一のIC上のオンチップメモリとして構成することや、ICの外部でそのICと接続されるメモリデバイス(例えばSDR(Single Data Rate)又はDDR(Double Data Rate)のSDRAM(シンクロナスDRAM)など)として実現することが可能である。また、そのメモリもそれを別のメモリデバイス上に配することや1つの同じメモリデバイス上に配置するなど、様々な構成をとることが可能である。

## 【0027】

以下、撮像装置5の基本動作等について図1、2を用いて詳細に説明する。

図1において、まず、撮影部2のレンズ210によって集められた光の画像情報がセンサー220によって電気信号として取り込まれる。このセンサー220はCCDイメージセンサー、又はCMOSイメージセンサーなどを利用することが可能である。本実施形態においては、正方画素のプログレッシブ形式のCCDであるとする。また、その有効画素数は $640 \times 480$ のいわゆるVGAサイズであり、1/30秒毎に1フレームのVGA画像を出力することができるものとする。即ち、本実施形態での1映像期間は1/30秒(およそ33.3ms)であるとする。センサー220で光電変換されて電気信号として取り込まれた画像データは、順次読み出され現像処理部230に渡される。現像処理部230では、センサー220から得られた画像データを信号処理して、輝度信号と色差信号を作り出し、後段で処理しやすい形式にして出力する。仮にここでは、YUV422形式で出力されるものとする。

## 【0028】

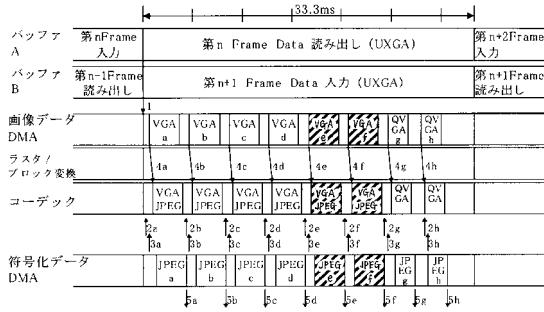

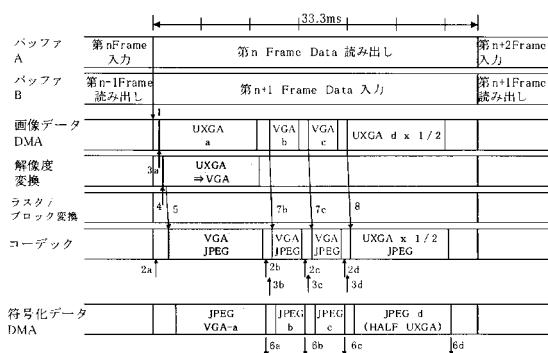

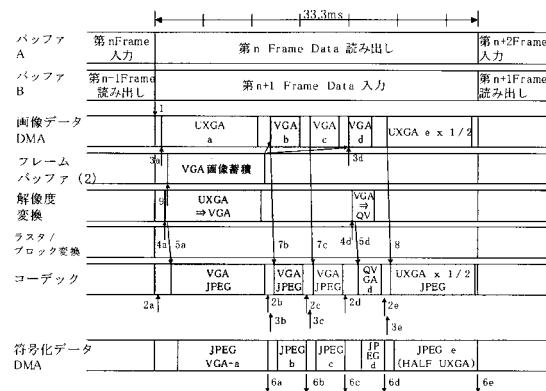

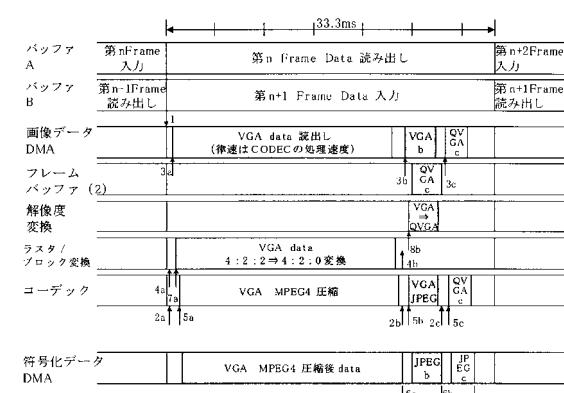

撮像部2の現像処理部230でYUV422形式にされた画像データは画像処理部1のフレームバッファ10にフレーム単位で格納される。その後の動作を図2及び図3のタイミングチャートを用いて説明する。

## 【0029】

現像処理部230から出力されたデータはフレームバッファ10にフレーム単位で格納される。フレームバッファ10は図3に示すように内部はダブルバッファ形式になっており、第n番目のフレームと第n+1番目のフレームの画像データがそれぞれ別の領域(バッファA及びB)に格納されるようになっている。そのため、第nフレームの画像データがある映像期間に例えばバッファAに蓄えられた場合、それを読み出して次の映像期間で利用している間に、第n+1フレームの画像データをバッファBに蓄えていくことが可能になる。

## 【0030】

今、第nフレームのフレームバッファ10のバッファAへの蓄積が完了したとする。すると、現像処理部230から制御用シーケンサ70に対してフレームデータの転送完了割

10

20

30

40

50

込みが発生する（図3矢印1）。

【0031】

転送完了割込みを受けて、制御用シーケンサ70は、まずコーデック処理部51のパラメータレジスタ51に対してどのような処理をコーデック処理部でおこなうかを指示するためのパラメータをセットする（図3矢印2a）。本実施形態では、このコーデック処理部はJPEGの圧縮処理をおこなうものとする。その場合、例えば映像の圧縮の度合いを示すQ値などがその圧縮のパラメータの代表的な例となる。

【0032】

パラメータレジスタ51へのパラメータのセットが終了すると、次いで制御用シーケンサ70は画像データDMAC20に対して、第nフレームの画像データをフレームバッファ10のバッファAから読み出して、コーデック処理部50に対してデータを供給するための転送を開始するように指示をする（図3矢印3a）。

10

【0033】

指示を受けた画像データDMAC20はフレームバッファ10のバッファAから第nフレームの画像データを順に読み出して、ラスタ／ブロック変換用メモリ40に供給する。コーデック処理部50でJPEGの処理をおこなうためには、8×8の画素のブロック単位でデータを供給する必要があるので、このラスタ／ブロック変換用メモリ40でそのようにデータを変換してコーデック処理部50に供給する（図3矢印4a）。

【0034】

コーデック処理部50はラスタ／ブロック変換用メモリ40から与えられた画像データをパラメータレジスタ51に設定されたパラメータの値に従ってJPEG圧縮し、符号化データJPEGaとする。なお、本実施形態のこの最初の圧縮ではQ値=Qaとして圧縮しているとする。コーデック処理部50によって圧縮された符号化データは順次符号化データDMAC60に受け渡され、符号化データDMAC60はデータバッファ12に対して一定の単位で符号化データを転送する。そして第nフレームの画像データより作成された全ての符号化データの転送を完了した時点で、制御用シーケンサ70は通信部3に対して符号化データの転送完了割込みを送出する（図3矢印5a）。この割り込み通知は画像-通信部間制御信号71を介して伝達される。

20

【0035】

通信部3では符号化データの転送完了割込みを受けて、ネットワーク制御部310がデータバッファ12から符号化データを読み出し、その符号化データを送出するネットワークの形態に応じてパケット化するなどの処理を行い、ネットワークインターフェース320に対して受け渡す。ネットワークインターフェース320はネットワーク網4に対してそのネットワークの形態に応じた形でデータを送出する。

30

【0036】

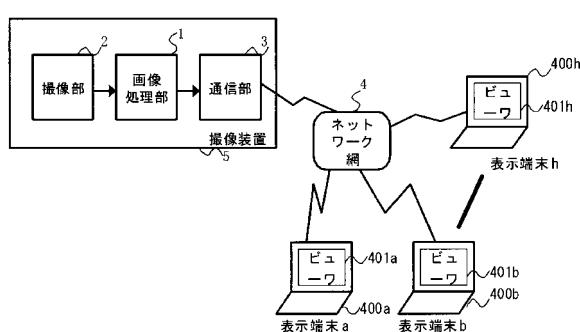

図4は、本実施形態に係る撮像装置5を用いたシステムの構成例を示した図である。

ネットワーク網4には表示端末400が接続され、端末上のビューワ401を利用してユーザは撮像装置5が撮影した画像を表示する。図4では400aから400hまで合計8つの表示端末が存在し（うち5つは図示せず）、それぞれの表示端末上でビューワ401aから401hが動作し、各ユーザがそれを利用しているものとする。

40

【0037】

図4に示すようなシステムにおいて、ユーザが接続されるネットワーク環境及びユーザが必要とする画像品質等は様々である。もし、ユーザの求める画像品質がコーデック処理部50のパラメータレジスタ51に対して与えるパラメータの観点から見て同一のパラメータで実現できるようであれば、撮像装置5の通信部3のネットワーク制御部310が個々のユーザの端末に向けてデータを送出するようにする際に、同一の符号化データをコピーしてネットワークインターフェース320に受け渡すことによって複数のユーザに映像データをサービスすることが可能である。

【0038】

しかし、各ユーザが異なる画像品質のパラメータを要求するような場合においては、そ

50

のようにコピーするだけでは実現できない。また、ユーザの表示端末 400 上でコマ落ちさせることなく滑らかに動画像を表示させるようにするために、1 映像期間内（本実施形態では 1 / 30 秒（約 33.3 ms））の中で各ユーザが求める画像処理をそれぞれ行う必要がある。以下、そのような場合の撮像装置 5 の動作について図 1～4 を用いながら説明する。先に図 2、3 を用いてその動作の基本は説明しているので、複数ユーザからの要求に答えるための動作と、それを受けた一連の動作の流れを説明する。

#### 【0039】

いま、図 4において表示端末 400a から 400h を利用している各ユーザが、それぞれ、 $Q = Q_a \sim Q_h$  で表される  $Q$  値を持つ JPEG 画像を欲しているものとする。通信部 3 のネットワーク制御部 310 の中にある処理性能判断部 311 は、各端末から要求の出ている処理の内容を、1 映像期間内に全て画像処理部で処理させることができるとどうかの判断を行う。本実施形態では、予め処理内容（処理の種類、扱うデータ量、圧縮度など）から画像処理部の処理性能を評価するテーブルを引き、その結果  $Q = Q_a \sim Q_h$  で表されるそれぞれの  $Q$  値を持つ JPEG 画像の処理を行うことが問題ないと判断し、画像処理部に対して処理の指示を出す。この指示は、図 2 の画像 - 通信部間制御信号 71 を利用して画像処理部 1 の制御用シーケンサ 70 に対して伝達される。

10

#### 【0040】

なお、本実施形態において処理性能判断部 311 は、通信部 3 のネットワーク制御部 310 の中にあるとしたが、例えば、画像処理部 1 の中に配することや、画像処理部 1 の制御用シーケンサ 70 に組み込まれた機能の一部として実装することも可能であり、その機能実現のためには、その位置は基本的には本実施形態において制限されるものではない。

20

#### 【0041】

仮に、処理性能判断部 311 が制御用シーケンサ 70 に組み込まれていた場合には、各端末から要求の出ている処理内容がネットワーク制御部 310 を経由して、画像 - 通信部間制御信号 71 を介して制御用シーケンサ 70 内の処理性能判断部 311 に伝達され、その情報を用いて上記判断を実施することになる。但し、この場合は、既に処理性能判断部 311 が圧縮処理等の画像処理をこれ以上受け入れられないと判断している場合であっても、その判断部は制御用シーケンサ 70 内部にあるため、新規のユーザ要求が画像 - 通信部間制御信号 71 を介して制御用シーケンサ 70 内の処理性能判断部 311 にまで伝達され、そのユーザ要求への拒否回答が同じ経路を帰っていくことになる。また、ネットワーク上のユーザからの要求は映像期間とは同期せずに不定期に送付されてくるため、制御用シーケンサ 70 にもデータが不定期に送信されることになり、制御用シーケンサが予期せぬタイミングの要求に対応しなくてはならなくなるなど、結果として画像処理部 1 の制御に悪影響を及ぼす可能性がある。

30

#### 【0042】

一方、処理性能判断部 311 がネットワーク制御部 310 の中にある場合はユーザ要求に対しての処理は基本的にネットワーク制御部 310 の中に判断され、必要のある場合のみ画像 - 通信部間制御信号 71 を介して制御用シーケンサ 70 に対して要求が伝達される。また、そのデータの伝達タイミングも映像期間と同期した一定のタイミングで与えることが可能である。このように必要なデータ伝送のみを実施してなるべく全体の処理負荷を減らすという観点から考えると、本実施形態のように処理性能判断部 311 は通信部 3 のネットワーク制御部 310 の中にあるほうが好ましい。

40

#### 【0043】

図 3において、 $Q = Q_a$  の圧縮パラメータを用いた画像圧縮処理が終了し、JPEG a の符号化データの転送完了割込みを送出した（図 3 矢印 5a）ことを制御用シーケンサ 70 が認識すると、制御用シーケンサ 70 は次に求められている画像処理のパラメータを調べる。そして、図 3 のように次に求められている圧縮に利用すべきパラメータ  $Q = Q_b$  をコードック処理部 50 のパラメータレジスタ 51 に対して設定する（図 3 矢印 2b）。

#### 【0044】

それ以降の動作は  $Q = Q_a$  の時と同様であり、パラメータレジスタ 51 へのパラメータ

50

のセットが終了すると、次いで制御用シーケンサ 70 は画像データ D M A C 20 に対して、第 n フレームの画像データをフレームバッファ 10 のバッファ A から読み出して、コーデック処理部 50 に対してデータを供給するための転送を開始するように指示をする（図 3 矢印 3 b）。次いで指示を受けた画像データ D M A C 20 はフレームバッファ 10 のバッファ A から第 n フレームの画像データを順に読み出して、ラスター／ブロック変換用メモリ 40 に供給し、8 × 8 の画素のブロック単位に変換されて画像データはコーデック処理部 50 に供給される（図 3 矢印 4 b）。

#### 【 0 0 4 5 】

コーデック処理部 50 は、ラスター／ブロック変換用メモリ 40 から与えられた画像データをパラメータレジスタ 51 に設定されたパラメータの値（この時点では  $Q = Q_b$ ）に従って J P E G 壓縮し、符号化データ J P E G b とする。コーデック処理部 50 によって圧縮された符号化データは順次符号化データ D M A C 60 に受け渡され、符号化データ D M A C 60 はデータバッファ 12 に対して一定の単位で符号化データを転送する。そして第 n フレームの画像データより作成された  $Q = Q_b$  時のすべての符号化データ転送を完了した時点で、制御用シーケンサ 70 は通信部 3 に対して  $Q = Q_b$  時の J P E G b の符号化データ転送完了割込みを送出する（図 3 矢印 5 b）。

#### 【 0 0 4 6 】

通信部 3 では  $Q = Q_b$  時で処理を行った符号化データの転送完了割込みを受けて、ネットワーク制御部 310 がデータバッファ 12 から符号化データを読み出し、 $Q = Q_b$  での処理要求を出していた表示端末 400 b に対して符号化データを送出するようにアドレス処理等を実施する。ネットワークインターフェース 320 はネットワーク網 4 を介して表示端末 400 b に対してデータを送出する。

#### 【 0 0 4 7 】

この一連の動作が個々のユーザが要求する異なる Q 値に応じて複数回 1 映像期間内に繰り返される。本実施形態では、処理性能判断部 311 が 1 映像期間内に実現可能であると判断した  $Q_a$  から  $Q_h$  に対応する合計 8 回のパラメータ設定とそれに伴う画像圧縮処理が 1 映像期間内に実施されている。このようにすることによって、複数の処理ユニットを並列に実装すること無しに 1 つのコーデックを用いて 1 映像期間内に複数回の画像圧縮処理が可能になり、ネットワークの先の様々な要求を持つユーザに対して実時間性を守って複数のサービスを提供することが可能になる。

#### 【 0 0 4 8 】

例えば、複数のユーザの表示端末上でコマ落ちさせることなく滑らかに異なる品質の動画像を表示させることができになる。また、複数の処理ユニットを並列に実装する必要がなくなることから、基板もしくはチップ面積を小さくし、消費電力等も削減できるので、結果として小型のネットワークカメラを提供できるようになる。

#### 【 0 0 4 9 】

また、特に処理性能判断部 311 が的確に判断することによって、画像圧縮処理などのユニット性能をその性能の極限まで無駄なく利用することができるようになり、1 つのコーデックを用いて 1 映像期間内により多くのユーザに実時間性を守って複数のサービスを提供することができるようになる。更に、処理性能判断部 311 をネットワーク制御部 310 の中に配することによって、より内部のデータ通信を減らしながら、上記機能を実現することができるようになり、全体としての処理性能の向上や消費電力の削減などの効果がある。

#### 【 0 0 5 0 】

##### （第 2 の実施形態）

第 1 の実施形態においては、ユーザの要求する画像処理の相違は Q 値であるとした。しかし、別の局面ではユーザの要求する画像処理は Q 値だけにとどまらない場合がある。そのような場合について図 1、図 4、及び図 5 から図 7 を用いて説明する。図 1、図 4 は図としての構成要素は同一であるので第 1 の実施形態のものを流用する。

#### 【 0 0 5 1 】

図 1 において、本実施形態では、撮像部 2 のセンサー 220 は、全画素読み出し方式の C

10

20

30

40

50

MOSセンサーであり、その有効画素数は $1600 \times 1200$ のいわゆるUXGAサイズであるとする。そして、その画素形態は正方画素であり1/30秒毎に1フレーム分のUXGA画像を出力することができるものとする。即ち、本実施形態での1映像期間は1/30秒(およそ33.3ms)であるとする。

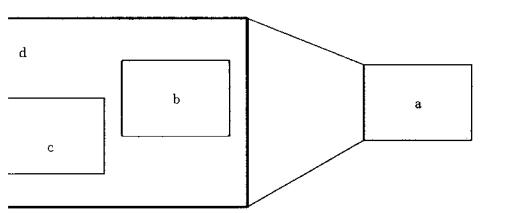

#### 【0052】

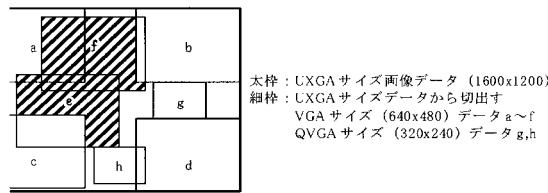

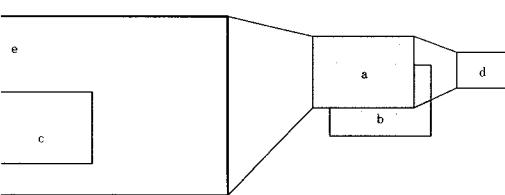

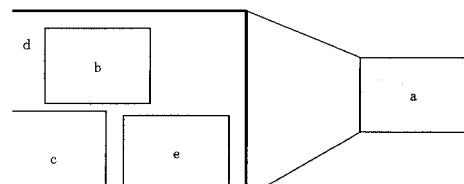

このような条件下で、図4における各ユーザは、UXGAの画像の内部で任意のVGAサイズ以下の画像領域を設定し、その部分画像を切出して利用しているものとする。UXGAの画像サイズの中でどの部分の画像を切出して利用しているかの例を図5に示す。

#### 【0053】

図5では、図4の表示端末400aのビューワ401aに表示される画像領域をa、表示端末400bのビューワ401bに表示される画像領域をbというようにして表示端末400hに対応する画像領域hまでが示されている。ここでは、表示端末400aから400fまでのユーザがVGAサイズ( $640 \times 480$ )、表示端末400g及び400hのユーザがQVGAサイズ( $320 \times 240$ )の画像サイズの映像データを利用している。

#### 【0054】

また、通信部3のネットワーク制御部310の中にある処理性能判断部311は、各端末から要求の出ている処理の内容を、1映像期間内に全て画像処理部で処理させることができあるかどうかの判断を行う。本実施形態では、図5で示されている画像領域の全ての切出し処理、及びその映像を利用した画像処理部におけるJPEG画像の処理を行うことが問題ないと判断し、画像処理部に対して処理の指示を出すものとする。

#### 【0055】

なお、本実施形態において処理性能判断部311は通信部3のネットワーク制御部310の中にあるとしたが、第1の実施形態と同様に例えば、画像処理部1の中に配することや、画像処理部1の制御用シーケンサ70に組み込まれた機能の一部として実装することも可能であり、その位置は本実施形態において制限されるものではない。但し、第1の実施形態と同様に必要なデータ伝送のみを実施してなるべく全体の処理負荷を減らすという観点から考えると、本実施形態のように処理性能判断部311は通信部3のネットワーク制御部310の中にあるほうが好ましい。

#### 【0056】

このような前提の下で、本実施形態における画像処理部1の動作を図1及び図4、5を参照しながら図6及び図7を用いて説明する。

#### 【0057】

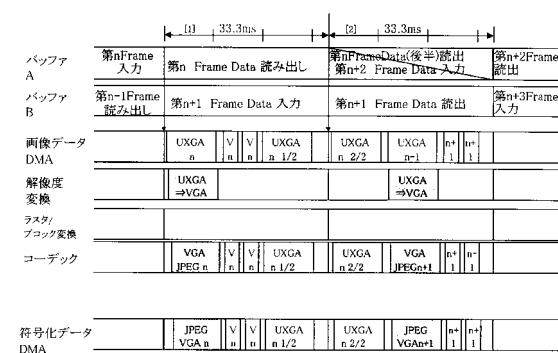

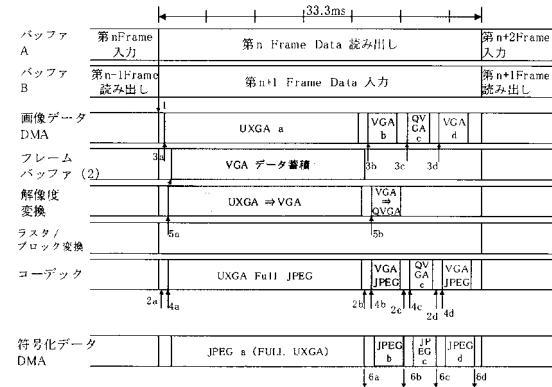

図6において、現像処理部230から出力されたUXGAサイズの画像データは、フレームバッファ10にフレーム単位で格納される。フレームバッファ10は、図7に示すように内部はダブルバッファ形式になっており、第n番目のフレームと第n+1番目のフレームの画像データがそれぞれ別の領域(バッファA及びB)に格納されるようになっている。

#### 【0058】

今、第nフレームのフレームバッファ10のバッファAへの蓄積が完了したとする。すると、現像処理部230から制御用シーケンサ70に対してフレームデータの転送完了割込みが発生する(図7矢印1)。

#### 【0059】

転送完了割込みを受けて、制御用シーケンサ70は、まず第1の実施形態と同様にコーデック処理部51のパラメータレジスタ51に対してどのような処理をコーデック処理部でおこなうかを指示するためのパラメータをセットする(図7矢印2a)。本実施形態では、このコーデック処理部はJPEGの圧縮処理をおこなうものとする。その場合、例えば映像の圧縮の度合いを示すQ値などがその圧縮のパラメータの代表的な例であり、この時点では表示端末400aが要求している $Q = Q_a$ が設定されたとする。

#### 【0060】

次いで制御用シーケンサ70は画像データDMA20に対して、第nフレームの画像

10

20

30

40

50

データをフレームバッファ 10 のバッファ A から読み出して、コーデック処理部 50 に対してデータを供給するための転送を開始するように指示をする（図 7 矢印 3a）。その際、制御用シーケンサ 70 は画像データ DMA C 20 の転送領域設定レジスタ 21 に対してフレームバッファ 10 に蓄えられた UXGA の画像データからどの領域を読み出してコーデック処理部 50 に与えるかを指示するための領域パラメータをセットする。

#### 【0061】

この領域パラメータは、図 6 の画像 - 通信部間制御信号 71 を利用して予め画像処理部 1 の制御用シーケンサ 70 に対してネットワーク上の各表示端末 400a ~ h より要求がなされているものとする。この時点では、表示端末 400a が要求している VGA サイズの画像（図 5 の領域 a）を示すように、コーデック処理部 50 に与えるデータの開始位置を示す座標データと、画像サイズ（VGA）を示すデータが制御用シーケンサ 70 に対して与えられ、制御用シーケンサ 70 はそれらのデータから求めた転送領域情報を領域パラメータとして転送領域設定レジスタ 21 に設定する。10

#### 【0062】

領域及びサイズの指示を受けた画像データ DMA C 20 は、フレームバッファ 10 のバッファ A から第 n フレームの指定領域の画像データを順に読み出して、ラスタ / ブロック変換用メモリ 40 に供給する。ラスタ / ブロック変換用メモリ部では  $8 \times 8$  のブロック単位にデータを変換してコーデック処理部 50 に供給する（図 7 矢印 4a）。

#### 【0063】

コーデック処理部 50 は、ラスタ / ブロック変換用メモリ 40 から与えられた画像データをパラメータレジスタ 51 に設定されたパラメータの値（ $Q = Q_a$ ）に従って JPEG 圧縮し、符号化データ JPEG a とする。コーデック処理部 50 によって圧縮された符号化データは順次符号化データ DMA C 60 に受け渡され、符号化データ DMA C 60 はデータバッファ 12 に対して一定の単位で符号化データを転送する。そして第 n フレームにおいて表示端末 400a が指定した領域を構成する画像データより作成されるすべての符号化データの転送を完了した時点で、制御用シーケンサ 70 は通信部 3 に対して符号化データの転送完了割込みを送出する（図 7 矢印 5a）。この割り込み通知は画像 - 通信部間制御信号 71 を介して伝達される。20

#### 【0064】

通信部 3 では、符号化データの転送完了割込みを受けて、ネットワーク制御部 310 がデータバッファ 12 から符号化データを読み出し、その符号化データを送出するネットワークの形態に応じてパケット化するなどの処理を行い、ネットワークインターフェース 320 に対して受け渡す。ネットワークインターフェース 320 はネットワーク網 4 に対してそのネットワークの形態に応じた形でデータを表示端末 400a に向けて送出する。表示端末 400a では受信したデータを展開し、VGA サイズのデータとしてビューワ 401a に表示する。30

#### 【0065】

一方、図 7 において、表示端末 400a 向けの領域パラメータと  $Q = Q_a$  の圧縮パラメータを用いた画像圧縮処理が終了し、JPEG a の符号化データの転送完了割込みを送出した（図 7 矢印 5a）ことを制御用シーケンサ 70 が認識すると、制御用シーケンサ 70 は次に求められている画像処理のパラメータを調べる。そして、図 7 のように次に求められている圧縮に利用すべきパラメータ  $Q = Q_b$  をコーデック処理部 50 のパラメータレジスタ 51 に対して設定する（図 7 矢印 2b）。

#### 【0066】

次いで、画像データ DMA C 20 に対して、第 n フレームの画像データをフレームバッファ 10 のバッファ A から読み出す際に、どの部分のデータをどのようなサイズで読み出すかを表示端末 400b からの指示に基づき画像データ DMA C 20 の転送領域レジスタ 21 に対して設定し、コーデック処理部 50 に対してデータを供給するための転送を開始するように指示をする（図 7 矢印 3b）。それ以降の動作は表示端末 400a に対して行った処理と同様である。40

## 【0067】

この一連の動作が個々のユーザが要求する異なるパラメータ（画像領域及びQ値等）に応じて複数回1映像期間内に繰り返される。本実施形態では、図5に示したように異なる切出し位置とサイズ及び圧縮パラメータの指定に基づき、合計8回のパラメータ設定とそれに伴う画像圧縮処理が1映像期間内に実施されている。このようにすることによって、1つのコーデックを用いて1映像期間内に複数の領域の画像圧縮処理が可能になり、ネットワークの先の様々な要求を持つユーザに対して実時間性を守って複数のサービスを提供することが可能になる。また、1つの高解像度の画像から任意の位置と任意のサイズを指定して複数の部分領域画像を作成し、1映像期間内におけるそれら複数の部分領域画像を用いた画像処理が可能となる。

10

## 【0068】

## (第3の実施形態)

第1及び第2の実施形態では撮影した元の画像と同じ解像度の画像を扱っている場合を例としたが、撮影した画像と同じ画角の映像を、解像度を落とすことにより小さな画面表示で利用したいという場合も考えられる。

## 【0069】

そのような場合について図1、図4、及び図8から図11を用いて説明する。図1、図4は図としての構成要素は同一であるので第1の実施形態のものを流用する。なお、本実施形態では第2の実施形態と同様、図1における撮像部2のセンサー220は、全画素読出し方式のCMOSセンサーであり、その有効画素数は $1600 \times 1200$ のいわゆるUXGAサイズであるとする。そして、その画素形態は正方画素であり1/30秒毎に1フレーム分のUXGA画像を出力することができるものとする。即ち、本実施形態での1映像期間は1/30秒（およそ33.3ms）であるとする。

20

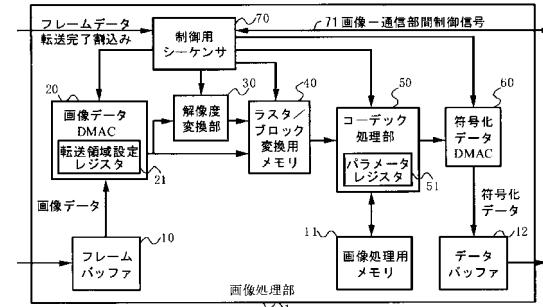

## 【0070】

図8は、画像処理部1の中に解像度変換部30が存在する場合の構成を示した図である。第2の実施形態の図6と比較すると画像データDMAC20とラスタ/ブロック変換用メモリ40との間のデータパスが2つに分かれ、その片方に解像度変換部が入っている。制御用シーケンサ70は必要に応じてデータパスを切り替え、解像度変換部30を通してデータを供給する。

## 【0071】

30

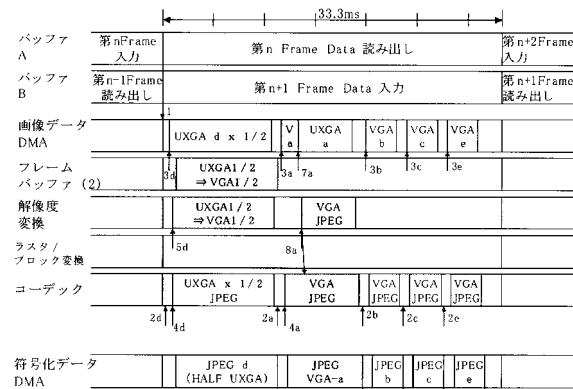

図9は、本実施形態における画像処理部の動作を示した図であり、図10は、本実施形態における要求されている画角と解像度を示した図である。

図10からわかるように、本実施形態ではUXGAサイズのデータから同じ画角でVGAサイズに変換した画像を圧縮したもの（データa）、UXGAサイズの元データからVGAサイズで切出した画像を圧縮したもの（データb及びc）、そしてUXGAサイズの画像をそのまま圧縮したもの（データd）が要求されているとする。ここでデータaからdは図4における端末400aから400dの要求に対応している。

## 【0072】

図8において、現像処理部230から出力されたUXGAサイズの画像データは、フレームバッファ10にフレーム単位で格納される。フレームバッファ10は、図9に示すように内部はダブルバッファ形式になっており、第n番目のフレームと第n+1番目のフレームの画像データがそれぞれ別の領域（バッファA及びB）に格納されるようになっている。

40

## 【0073】

今、第nフレームのフレームバッファ10のバッファAへの蓄積が完了したとする。すると、現像処理部230から制御用シーケンサ70に対してフレームデータの転送完了割込みが発生する（図9矢印1）。

## 【0074】

転送完了割込みを受けて、制御用シーケンサ70は、まず第2の実施形態と同様にコーデック処理部51のパラメータレジスタ51に対してどのような処理をコーデック処理部

50

でおこなうかを指示するためのパラメータをセットする（図9矢印2a）。本実施形態では、このコーデック処理部はJPEGの圧縮処理をおこなうものとする。その場合、例えば映像の圧縮の度合いを示すQ値などがその圧縮のパラメータの代表的な例であり、この時点では表示端末400aが要求しているQ=Qaが設定されたとする。

#### 【0075】

次いで、制御用シーケンサ70は解像度変換部30に対して、画像データDMAC20から入力されるUXGAサイズの画像データをVGAサイズに解像度変換するように指示をする（タイミング図示せず）。どのようなサイズに解像度変換するかについては図8の画像・通信部間制御信号71を利用して予め画像処理部1の制御用シーケンサ70に対してネットワーク上の表示端末400aより要求がなされているものとする。

10

#### 【0076】

次いで、制御用シーケンサ70は、画像データDMAC20に対して、第nフレームの画像データをフレームバッファ10のバッファAから読み出して、解像度変換部30を経由してコーデック処理部50に対してデータを供給するための転送を開始するように指示をする（図9矢印3a）。本実施形態のこの時点においては、UXGAの全データを読み出して解像度変換部30に入力する必要があるので、そのように領域パラメータを転送領域設定レジスタ21に設定する。本実施形態では特に説明しないが、もし、ここでUXGAの領域のうち部分的に領域を指定して転送領域設定レジスタ21に設定した場合には、その領域のデータを読み出して解像度変換部30に与えることによって、任意の領域の画像を解像度変換できるようにすることが可能である。

20

#### 【0077】

そのようにしてデータの転送が画像データDMAC20によりフレームバッファ10から解像度変換部30に対して開始されると、解像度変換部30は、UXGAからVGAへの解像度変換作業を開始する（図9矢印4）。そして、解像度変換を終了した画像データから順に、ラスター/ブロック変換用メモリ40に供給する。ラスター/ブロック変換用メモリ部では8×8のブロック単位にデータを変換してコーデック処理部50に供給する（図9矢印5）。

#### 【0078】

コーデック処理部50は、ラスター/ブロック変換用メモリ40から与えられた画像データをパラメータレジスタ51に設定されたパラメータの値（Q=Qa）に従ってJPEG圧縮し、符号化データとする。このデータaの符号化に要する時間が他のVGAの符号化処理に比べて多く要しているのは、本実施形態においては、VGAの元データとなるべきUXGAのデータをフレームバッファ10から読み出してVGAに解像度変換する部分が全体の処理速度を決める要因となっているからである。

30

#### 【0079】

コーデック処理部50によって圧縮された符号化データは、順次符号化データDMAC60に受け渡され、符号化データDMAC60はデータバッファ12に対して一定の単位で符号化データを転送する。そしてVGAを構成する全ての符号化データの転送を完了した時点で、制御用シーケンサ70は通信部3に対して符号化データの転送完了割込みを送出する（図9矢印6a）。この割り込み通知は画像・通信部間制御信号71を介して伝達される。

40

#### 【0080】

通信部3では、符号化データの転送完了割込みを受けて、ネットワーク制御部310がデータバッファ12から符号化データを読み出し、その符号化データを送出するネットワークの形態に応じてパケット化するなどの処理を行い、ネットワークインターフェース320に対して受け渡す。ネットワークインターフェース320はネットワーク網4に対してそのネットワークの形態に応じた形でデータを表示端末400aに向けて送出する。表示端末400aでは受信したデータを展開し、VGAサイズのデータとしてビューワ401aに表示する。

#### 【0081】

50

一方、図9において、表示端末400a向けの解像度変換と $Q = Q_a$ の圧縮パラメータを用いた画像圧縮処理が終了し、JPEG:VGA-aの符号化データの転送完了割込みを送出した（図9矢印6a）ことを制御用シーケンサ70が認識すると、制御用シーケンサ70は次に求められている画像処理のパラメータを調べる。そして、ここでは $Q = Q_b$ をコーデック処理部50のパラメータレジスタ51に対して設定する（図9矢印2b）。

#### 【0082】

次いで、画像データDMAC20に対して、第nフレームの画像データをフレームバッファ10のバッファAから読み出す際に、図10のbで示されるVGAデータの開始座標とサイズ（VGA）から求められる転送領域情報を、表示端末400bからの指示に基づき画像データDMAC20の転送領域レジスタ21に対して設定する。その上でコーデック処理部50に対して、データを供給するための転送を開始するように指示をする（図9矢印3b）。それ以降の動作は第2の実施形態の表示端末400aに対して行った処理と同様であり、それが端末400cに対する切出しVGA画像データcの圧縮に関しても同様に実施される。

#### 【0083】

図9において、表示端末400c向けの画像圧縮処理が終了し、JPEGcの符号化データの転送完了割込みを送出した（図9矢印6c）ことを制御用シーケンサ70が認識すると、制御用シーケンサ70は、次に求められている画像処理のパラメータを調べる。ここでは、次に要求されている動作は、UXGAサイズの画像データdをその解像度のままJPEG圧縮して端末400dに対して送ることである。

#### 【0084】

しかし、UXGAの画像データをそのまま圧縮して送ることは全体のシステム、特にコーデック処理等に非常に負荷をかけるので、本実施形態では、UXGA画像の1/2だけをこの1映像期間内に処理して、残りの1/2に関しては次の映像期間に実施することにしている。この判断は、予め通信部3のネットワーク制御部310の中にある処理性能判断部311によって判断され、その条件でなければサービスを開始することを表示端末400dのユーザに通知し、また、この映像を要求している端末400dのユーザもその条件を了解しているものとする。

#### 【0085】

その処理の手順は、他の画像の処理と同様に、圧縮に利用すべきパラメータ $Q = Q_d$ のコーデック処理部50のパラメータレジスタ51に対する設定（図9矢印2d）、画像データDMAC20に対する転送領域レジスタ21の設定及び画像データの転送開始指示（図9矢印3d）となる。そして、画像データの転送が開始されると（図9矢印8）、コーデック処理部50は、指示されたパラメータを用いてJPEG圧縮を開始する。そしてUXGAの1/2のデータを圧縮してデータバッファ12に転送し終えた時点において、制御用シーケンサ70はデータバッファ通信部3に対してJPEGdの符号化データの転送完了割込みを送出する（図9矢印6d）。

#### 【0086】

このように1枚分のデータが完成する前に一旦処理を中断してその処理を通信部3に渡すことによって、データ通信における負荷の平準化などを通信部3側で考慮して配送することが可能になる。

#### 【0087】

図11は、UXGAサイズの画像をJPEG圧縮する際に、連続する2つの映像期間を利用して実施する場合の動作を示した図である。

映像期間[1]は、図9の内容と同一である。映像期間[1]の後半でUXGAサイズデータのJPEG圧縮のうち1/2を行った場合、続く映像期間[2]でUXGAサイズデータのJPEG圧縮の残りを実施する必要がある。この場合、圧縮に利用する画像データは第nフレームのものであるが、その第nフレームの画像データはフレームバッファ10を構成するダブルバッファのうちバッファAに保存されているものである。

#### 【0088】

10

20

30

40

50

映像期間 [ 2 ]においてバッファ A は、基本的には第  $n + 2$  フレームのデータが入力されてくる領域であるので、第  $n + 2$  フレームのデータによって第  $n$  フレームのデータが書き潰されないうちに UXGA サイズデータの JPEG 圧縮の残り 1 / 2 を実施しなければならない。そのため、この圧縮の処理は映像期間 [ 1 ] と違って映像期間 [ 2 ] の先頭に位置するようにしている。また、このような順序で処理することによって、通信部 3 へのデータの受け渡しも連続したものとなり、その扱いがより簡単化される。

#### 【 0 0 8 9 】

なお、本実施形態において処理性能判断部 311 は、通信部 3 のネットワーク制御部 310 の中にあるとしたが、第 1 の実施形態と同様に例えば、画像処理部 1 の中に配することや、画像処理部 1 の制御用シーケンサ 70 に組み込まれた機能の一部として実装することも可能であり、その位置は本実施形態において制限されるものではない。もし、処理性能判断部 311 が制御用シーケンサ 70 に組み込まれていた場合には、各端末から要求の出ている処理内容がネットワーク制御部 310 を経由して、画像 - 通信部間制御信号 71 を介して制御用シーケンサ 70 に伝達され、その情報を用いて上記判断を実施することになる。そして、判断結果のサービス提供の可否は画像 - 通信部間制御信号 71 を介してネットワーク制御部 310 に伝達され、ネットワーク制御部 310 が各端末にその情報を送信することになる。

#### 【 0 0 9 0 】

但し、第 1 の実施形態と同様に必要なデータ伝送のみを実施してなるべく全体の処理負荷を減らすという観点から考えると、本実施形態のように処理性能判断部 311 は通信部 3 のネットワーク制御部 310 の中にあるほうが好ましい。

#### 【 0 0 9 1 】

このようにすることによって、1つのコーデックを用いて1映像期間内に複数の領域の画像圧縮処理、及び、複数の解像度を持つ画像の画像圧縮処理を行うことができる。特に、高解像度の撮影画像の任意領域を切出して解像度変換することによって得られる画像、及び部分的に切出して解像度変換はしない画像など、高解像度の映像からユーザの希望に基づく任意の画角と解像度にした画像を1つのコーデックを用いて1映像期間内に複数ユーザに対して処理することが可能になる。

#### 【 0 0 9 2 】

また、本実施形態では、複数の映像期間を利用した高解像度データの処理を可能にしている。特に、本実施形態では UXGA サイズの JPEG 圧縮を連続する 2 映像期間に割り当て、かつその処理が時間的に連続するように処理順序を制御してサービスをしている。このようにすることによって、複数の映像期間に跨って高解像度データを保持するためのフレームバッファをその処理専用に持たなくともすむようになり、メモリサイズを節約できるなどの効果がある。

#### 【 0 0 9 3 】

但し、この処理順序の割り当て方法等は固定的なものではなく、他の処理に先んじて1映像区間の先頭で処理するなどユーザへのサービスポリシなどに応じて変更され得るものである。

#### 【 0 0 9 4 】

また、2以上の期間に跨って処理が必要になる場合は、複数映像期間に跨ってフレームデータが保持できるように、フレームバッファを構成することも可能であり、その持ち方はこの実施形態により制限されるものではない。

#### 【 0 0 9 5 】

##### ( 第 4 の実施形態 )

第 3 の実施形態では、解像度変換を行った画像をそのまま順次圧縮処理していたため、解像度変換後の画像は1回しか利用できなかったが、場合によっては元画像に同じ解像度変換を行った画像に対して、異なる圧縮のパラメータで圧縮したいという要求がくることも考えられる。その場合、同じ解像度変換を2回実施することも一手法であるが、特に元データの画像解像度が高い場合には、その元画像のフレームバッファからの読み出し及び解

10

20

30

40

50

像度変換に時間をおこすことになり、1映像期間内に処理できる性能を下げるこことなる。

【0096】

それを避けるために、後続の処理で同一の解像度変換処理を必要とする場合、もしくは一旦解像度変換した画像を利用して更なる解像度変換処理を実施することが有効である場合には、解像度変換した後の画像をコーデック処理部への処理に向けると同時に、一旦フレームバッファに貯めて後の処理で利用することが考えられる。そのような場合に関して図1、図4、及び図12から図14を用いて説明する。

【0097】

図1、図4は図としての構成要素は同一であるので第1の実施形態のものを流用する。

なお、本実施形態では第2の実施形態と同様、図1における撮像部2のセンサー220は、全画素読出し方式のCMOSセンサーであり、その有効画素数は $1600 \times 1200$ のいわゆるUXGAサイズであるとする。そして、その画素形態は正方画素であり1/30秒毎に1フレーム分のUXGA画像を出力することができるものとする。即ち、本実施形態での1映像期間は1/30秒(およそ33.3ms)であるとする。

10

【0098】

図12は、画像処理部1の中に解像度変換部30の処理後のデータを一旦蓄積するためのフレームバッファ(2)13が存在する場合の構成を示した図である。第3の実施形態の図8と比較すると、フレームバッファ(2)13が機能ブロックとして追加され、解像度変換部30からのデータパスと画像データDMA20へのデータパスが追加されている。

20

【0099】

なお、このフレームバッファ(2)13は、フレームバッファ10、画像処理用メモリ11、データバッファ12と同様に、画像処理部のそれ以外の構成要素が1つのICの中で実現される場合に、それらと同一のIC上のオンチップメモリとして構成することや、ICの外部でそのICと接続されるメモリデバイス(例えばSDR又はDDRのSDRAMなど)として実現することが可能である。また、そのメモリもそれぞれを別のメモリデバイス上に配することや1つの同じメモリデバイス上に配置するなど、様々な構成をとることが可能である。

【0100】

30

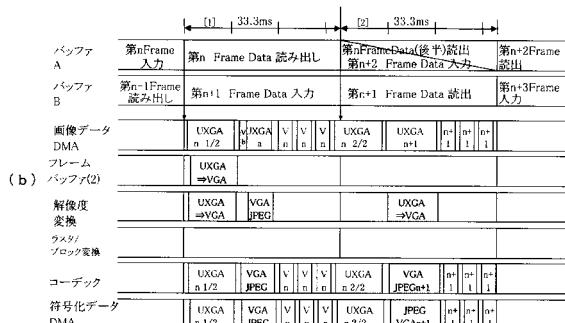

図13は、本実施形態における画像処理部の動作を示す図であり、図14は、本実施形態における要求されている画角と解像度を示す図である。図14からわかるように、本実施形態では、UXGAサイズのデータから同じ画角でVGAサイズに変換した画像を異なる2種の圧縮パラメータで圧縮するもの(データa、b)、更に、それと同じ画角でQVGAサイズの画像(データd)、UXGAサイズの元データからVGAサイズで切出した画像を圧縮したもの(データc)、そしてUXGAサイズの画像をそのまま圧縮したもの(データe)が要求されているとする。ここでデータaからeは図4における端末400aから400eの要求に対応している。

【0101】

図13において、画像の処理の流れは途中までは第3の実施形態の図9と同じである。

異なるのは、解像度変換部30がUXGAからVGAへの解像度変換作業を開始すると(図13矢印4a)、解像度変換を終了した画像データから順に、ラスター/ブロック変換用メモリ40に供給すると同時に、フレームバッファ(2)13に転送してVGA画像の蓄積を開始することである。図13矢印9)。解像度変換した画像をフレームバッファ(2)13に蓄積するかどうかの判断に関しては、ネットワーク上の各表示端末からの要求に基づいて、ネットワーク制御部310から画像・通信部間制御信号71を利用して予め画像処理部1の制御用シーケンサ70に対して設定がなされているものとする。

40

【0102】

コーデック処理部50は、ラスター/ブロック変換用メモリ40から与えられた画像データ(図13矢印5a)をパラメータレジスタ51に設定されたパラメータの値( $Q = Q_a$ )

50

) に従って J P E G 圧縮して符号化データ J P E G : V G A - a とし、それを符号化データ D M A C 6 0 が順次データバッファ 1 2 に転送する。そして、すべての符号化データの転送を完了した時点で、制御用シーケンサ 7 0 は、データバッファ通信部 3 に対して符号化データの転送完了割込みを送出する。(図 1 2 矢印 6 a) この割り込み通知は画像・通信部間制御信号 7 1 を介して伝達される。この画像は、通信部 3 が端末 4 0 0 a に対して送信する。

#### 【 0 1 0 3 】

次いで、制御用シーケンサ 7 0 は、次に求められている画像処理のパラメータ及び画角、解像度を調べる。そして、次に求められている圧縮に利用すべきパラメータ  $Q = Q b$  をコードック処理部 5 0 のパラメータレジスタ 5 1 に対して設定する(図 1 2 矢印 2 b)。

10

#### 【 0 1 0 4 】

次いで、画像データ D M A C 2 0 に対して、先に V G A に解像度変換したデータを利用して画像の圧縮処理をするべく、転送領域レジスタ 2 1 に対してデータの転送元をフレームバッファ(2)13に設定し、コードック処理部 5 0 に対してデータを供給するための転送を開始するように指示をする(図 1 2 矢印 3 b)。画像データ D M A C 2 0 は、フレームバッファ(2)13より V G A データを読み出し、それをラスター/ブロック変換用メモリ 4 0 を経由してブロック化したのち、コードック処理部 5 0 に供給する。コードック処理部 5 0 は設定されているパラメータ  $Q b$  を利用して圧縮処理を実施していく。

#### 【 0 1 0 5 】

その後、一旦 V G A サイズの切出し画像の圧縮を行った後、次に元の U X G A 画像と同じ画角で Q V G A サイズの画像データ(データ d)の処理を要求されている。既に同じ画角の V G A 画像がフレームバッファ(2)13に蓄えられており、要求されている Q V G A 画像は蓄えられている V G A 画像を利用して解像度変換することで容易に作成することができる。

20

#### 【 0 1 0 6 】

そこで、制御用シーケンサ 7 0 は、まず、解像度変換部 3 0 に対して V G A → Q V G A 変換を実施するように指示をする(タイミング図示せず)。次いで、画像データ D M A C 2 0 に対して、既に V G A に解像度変換したデータを利用して画像の解像度変換をするように、転送領域レジスタ 2 1 に対してデータの転送元をフレームバッファ(2)13に設定し、解像度変換部 3 0 に対してデータを供給するための転送を開始するように指示をする(図 1 2 矢印 3 d)。

30

#### 【 0 1 0 7 】

画像データ D M A C 2 0 は、フレームバッファ(2)13より V G A データを読み出し、それを解像度変換部 3 0 に供給する。解像度変換部 3 0 で V G A から Q V G A に変換された画像データは、ラスター/ブロック変換用メモリ 4 0 を経由してブロック化されたのち、コードック処理部 5 0 に供給される(図 1 2 矢印 5 d)。コードック処理部 5 0 は設定されているパラメータ  $Q d$  を利用して圧縮処理を実施していく。以降は、第 3 の実施形態と同様であるので、説明を省略する。

#### 【 0 1 0 8 】

なお、本実施形態においても処理性能判断部 3 1 1 は、通信部 3 のネットワーク制御部 3 1 0 の中にあるとしたが、第 1 の実施形態と同様に、例えば、画像処理部 1 の中に配することや、画像処理部 1 の制御用シーケンサ 7 0 に組み込まれた機能の一部として実装することも可能であり、その位置は本実施形態において制限されるものではない。但し、第 1 の実施形態と同様に、必要なデータ伝送のみを実施してなるべく全体の処理負荷を減らすという観点から考えると、本実施形態のように処理性能判断部 3 1 1 は、通信部 3 のネットワーク制御部 3 1 0 の中にあるほうが好ましい。

40

#### 【 0 1 0 9 】

このようにすることによって、第 3 の実施形態での効果に加えて、1つのコードックを用いて1映像期間内に複数の領域の画像圧縮処理を効率よく実施することが可能になる。特に、解像度変換した画像をコードック処理部で利用するのと並行してフレームバッファ

50

に蓄積することができるようになりますことで、同一画角の画像の解像度変換処理を複数の表示側端末から要求されるような場合に、同じ解像度変換を繰り返したりすることや、必要以上に詳細なデータを元に圧縮することをせずにすむようになります、1映像期間内における処理性能を向上させ、より多くのユーザからの異なる要求に対応した処理を行うことが可能になる。

#### 【0110】

##### (第5の実施形態)

第4の実施形態では、UXGA画像からVGA画像を作り、その作ったVGAの画像をコーデック処理用にラスター/ブロック変換用メモリ40に渡すと同時に、別途フレームバッファ(2)に蓄積をしていた。この場合、処理の流れとしては、解像度変換とブロック化及びコーデック処理とは時間的に直列に処理されている。一方、UXGAの画像と、それと同じ画角でVGAサイズに解像度変換をした2つの画像のデータ処理が同じ映像期間内に求められるような場合では、UXGAの画像圧縮を行った後で、解像度変換のために再度UXGAのデータをフレームバッファから読み出していたのでは、フレームバッファからUXGA画像データの読み出しを繰り返すことになり、非常に効率が悪いものとなる。

10

#### 【0111】

そこで、ある画角の映像のコーデック処理が求められ、同じ画角の映像を解像度変換して得られる画像のコーデック処理をそれと同じ映像期間内に実施することを必要とする場合に、解像度処理とコーデック処理とを時間的に並列に処理することで、フレームバッファからのデータの読み出しを1回に押さえながらコーデック処理と解像度処理を行えるようになります。本実施形態では、そのような場合に関して図1、図4、図12及び図15から図20を用いて説明する。

20

#### 【0112】

図1、図4は図としての構成要素は同一であるので第1の実施形態のものを流用する。また、図12は第4の実施形態のものを流用する。なお、本実施形態では第2の実施形態と同様、図1における撮像部2のセンサー220は、全画素読み出し方式のCMOSセンサーであり、その有効画素数は $1600 \times 1200$ のいわゆるUXGAサイズであるとする。そして、その画素形態は正方画素であり1/30秒毎に1フレーム分のUXGA画像を出力することができるものとする。即ち、本実施形態での1映像期間は1/30秒(およそ33.3ms)であるとする。また、図12に関する説明は構成ブロック的には、第4の実施形態と同一であるでその詳細は省略する。

30

#### 【0113】

図15は、本実施形態における画像処理部の動作を示す図であり、図16に本実施形態における要求されている画角と解像度を示す図である。

図16からわかるように、本実施形態では、UXGAサイズの画像データを圧縮したもの(データa)、UXGAサイズの画像と同じ画角でVGAサイズに変換した画像を圧縮するもの(データb)、更にそれと同じ画角でQVGAサイズの画像(データc)、UXGAサイズの元データからVGAサイズで切出した画像を圧縮したもの(データd)が要求されている。ここでデータaからdは、図4における端末400aから400dの要求に対応している。

40

#### 【0114】

処理性能判断部311は、重複している画角や並列化動作させることができる部分がどこにあるかを判断して、画像処理部1の能力を最大限発揮できるような形で画像処理部1の動作シーケンスを決定し、画像-通信部間制御信号71を利用して制御用セシーケンサ70に対して動作の指示をする。以下、その画像制御部1の動作について説明する。

#### 【0115】

図12において、現像処理部230から出力されたUXGAサイズの画像データは、フレームバッファ10にフレーム単位で格納される。フレームバッファ10は、図15に示すように内部はダブルバッファ形式になっており、第n番目のフレームと第n+1番目のフレームの画像データがそれぞれ別の領域(バッファA及びB)に格納されるようになつ

50

ている。

【0116】

今、第nフレームのフレームバッファ10のバッファAへの蓄積が完了したとする。すると、現像処理部230から制御用シーケンサ70に対してフレームデータの転送完了割込みが発生する(図15矢印1)。

【0117】

転送完了割込みを受けて、制御用シーケンサ70は、まずコーデック処理部51のパラメータレジスタ51に対してどのような処理をコーデック処理部でおこなうかを指示するためのパラメータをセットする(図15矢印2a)。本実施形態では、このコーデック処理部はJPEGの圧縮処理を行うものとする。その場合、例えば映像の圧縮の度合いを示すQ値などがその圧縮のパラメータの代表的な例であり、この時点では表示端末400aが要求しているQ = Qaが設定されたとする。

10

【0118】

次いで、制御用シーケンサ70は、解像度変換部30に対して、画像データDMAC20から入力されるUXGAサイズの画像データをVGAサイズに解像度変換するように指示をする。これはデータaの圧縮用に読み出されたUXGAのデータを利用してデータbの解像度変換も同時に行うためのものである(タイミング図示せず)。本実施形態では、画像圧縮処理と解像度変換処理とを並列的に行う必要があるが、その動作の並列処理の必要性などに関しては、ネットワーク上の各表示端末からの要求に基づいて、ネットワーク制御部310から画像・通信部間制御信号71を利用して予め画像処理部1の制御用シーケンサ70に対して設定がなされているものとする。

20

【0119】

次いで、制御用シーケンサ70は、画像データDMAC20に対して、第nフレームの画像データをフレームバッファ10のバッファAから読み出して、データを供給するための転送を開始するように指示をする(図15矢印3a)。本実施形態では、フレームバッファ10から読み出したデータを解像度変換部30とラスタ/ブロック変換用メモリ40に並列に供給する必要があるので、そのようにパラメータを転送領域設定レジスタ21に設定する。

【0120】

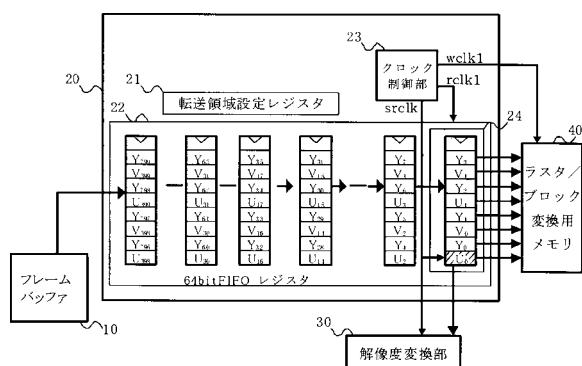

ここで画像データDMAC20の動作の詳細を図17、18を用いて説明する。

30

ここで、画像データはYUV422形式で入力されているものとし、U<sub>0</sub>Y<sub>0</sub>V<sub>0</sub>Y<sub>1</sub>U<sub>1</sub>Y<sub>2</sub>V<sub>1</sub>Y<sub>3</sub>…のような順序でフレームバッファ10上に格納されているとする。Y、U、Vのそれぞれのデータは各8ビットである。図17において画像データDMACはそのデータを64ビット単位でフレームバッファ10から読み出し、64bit FIFOレジスタ22に格納する。

【0121】

64bit FIFOレジスタ22には、データが8Byte単位で格納される。64bit FIFOレジスタ22の読み出し側は、その出力先が2系統に分かれている。1つはラスタ/ブロック変換用メモリ40であり、こちらは1クロックで8Byte幅のデータを読み込むことができる。2つ目は解像度変換部30であり、こちらはY、U、Vの各sample単位(8ビット)でデータを受信していく。

40

【0122】

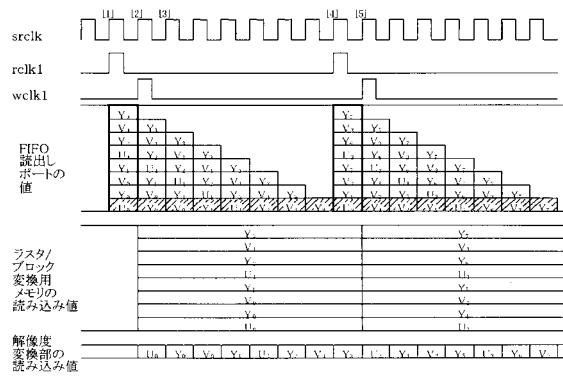

図18は、64bit FIFOレジスタ22とそのデータの出力先であるラスタ/ブロック変換用メモリ40及び解像度変換部30とのデータのやり取りを示した図である。

64bit FIFOレジスタ22は、基本的にはrclk1の立ち上がりエッジで新しいデータがその FIFOの読み出しポート24に64bit幅単位で読み出されるようになっている。例えば、図18の[1]及び[4]のタイミングで FIFO読み出しポート24に新しい値が更新されている。

【0123】

ラスタ/ブロック変換用メモリ40は、 FIFOの読み出しポートの値が更新されると、

50

wclk1 の立ち上がりエッジでその内部にデータを取り込む。ここでは、図 18 の [ 2 ] 及び [ 5 ] のタイミングでデータが読み込まれている。

#### 【 0 1 2 4 】

一方、解像度変換部 30 は、データを各sample単位 ( Y、U、V のいずれか) を構成する 8 bit 深さのデータ) 単位で受信する必要がある。ここでは、図 17 及び 18 中の FIFO の読み出しポート 24 の中に斜線で示した部分が解像度変換部 30 への出力ポートであるとする。解像度変換部 30 は、srcclk の立ち上がりエッジごとに 8 bit 単位でこのポートから画像データを読み込んでいく。

#### 【 0 1 2 5 】

例えば、[ 2 ] の立ち上がりエッジでは U0 を、[ 3 ] では Y0 を読み込んでいる。同時に FIFO の読み出しポートでは、srcclk 毎にデータが図の下方向に 8 bit 単位でシフトされ、次の読み出しに備えてデータが更新される。srcclk、rclk1、wclk1 それぞれのタイミングの関係は、図 18 に示したとおりである。このようにすることによって、一度のフレームバッファからの読み出しでラスタ / ブロック変換処理及びコーデック処理と解像度処理を行えるようにすることができる。

#### 【 0 1 2 6 】

なお、これらのsrcclk、rclk1、wclk1 は、それぞれ図 17 に示すように画像データ DMA C 20 の中のクロック制御部 23 によって制御される信号である。クロック制御部は、制御用シーケンサ 70 によって、どのようなクロックタイミングで各クロックを動かすのが一番効率的かの指示を受け、本実施形態においては、図 18 に示したような位相関係を持って 64 bit FIFO レジスタ 22 とそのデータの出力先であるラスタ / ブロック変換用メモリ 40 及び解像度変換部 30 とのデータのやり取りを制御している。

#### 【 0 1 2 7 】

以上のようにして、データの転送が画像データ DMA C 20 によりフレームバッファ 10 からラスタ / ブロック変換用メモリ 40 に供給されると、ラスタ / ブロック変換用メモリ部では  $8 \times 8$  のブロック単位にデータを変換してコーデック処理部 50 に供給し、コーデック処理部は圧縮処理を開始する (図 15 矢印 4a)。

#### 【 0 1 2 8 】

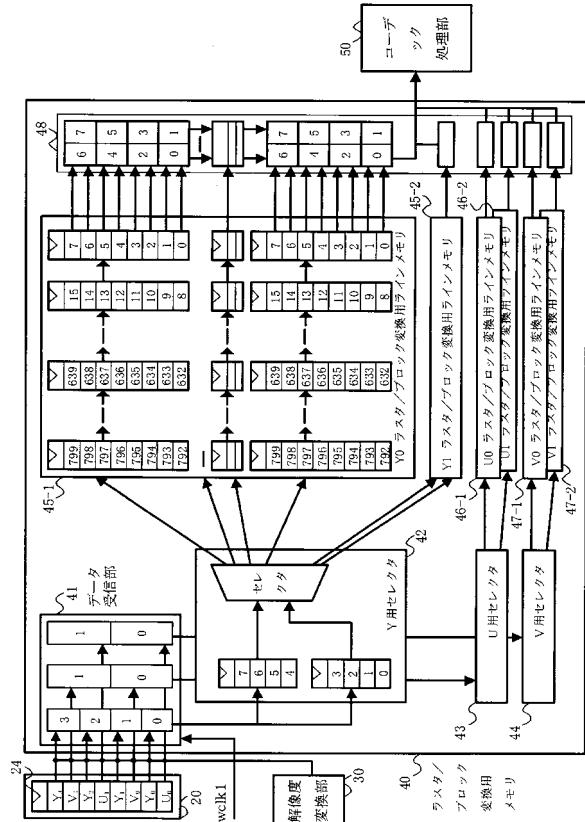

図 19 は、ラスタ / ブロック変換用メモリ 40 の構成を示した図である。

まず、画像データ DMA C 20 の 64 bit FIFO レジスタ 22 の読み出しポート 24 から、wclk1 信号に同期してラスタ形式の画像データがデータ受信部 41 に格納される。データ受信部で Y、U、V の各信号に分離されたデータは、それぞれの信号用のセレクタ 42、43、44 へ送られる。

#### 【 0 1 2 9 】

各信号用のセレクタ内部では、分離されたデータを、ブロックの横方向単位 (8 sample) になるようにそれぞれ結合し、8 sample 分のデータがたまるとそれぞれのラスタ / ブロック変換用ラインメモリに送付する。それぞれ、Y0 ラスタ / ブロック変換用ラインメモリ 45-1 及び Y1 ラスタ / ブロック変換用ラインメモリ 45-2、U0 ラスタ / ブロック変換用ラインメモリ 46-1 及び U1 ラスタ / ブロック変換用ラインメモリ 46-2、V0 ラスタ / ブロック変換用ラインメモリ 47-1 及び V1 ラスタ / ブロック変換用ラインメモリ 47-2 のダブルバッファ構成になっており、それぞれのラインメモリは、64 bit 幅のメモリが 8 ライン分束になった形で構成されている。

#### 【 0 1 3 0 】

コーデック処理部 50 にデータを転送する際は、Y、U、V 各ラインメモリのうちのそれぞれ片方が 8 ライン分全て充填された段階で、右端から順に読み出していく。その際はまずマクロブロック転送用バッファ 48 に各ラインから右端に来ているデータを一列分読み出す。この段階で 1 つのブロックを構成する横方向 8 sample、縦方向 8 ライン分の合計 64 sample 分のデータが準備できることになる。そして Y 信号のブロック 2 ブロック、U 信号のブロック 1 ブロック、V 信号のブロック 1 ブロックの順で繰り返し読み出してコーデック処理部 50 にデータを転送する。このコーデック処理部 50 への読み出しの最中にお

10

20

30

40

50

いても、ダブルバッファ構成をとっているため、読み出していない各ラインメモリへのデータ充填が可能となっている。コーデック処理部は、圧縮処理を開始すると同時に、解像度変換部も解像度変換処理を開始する（図15矢印5a）。

#### 【0131】

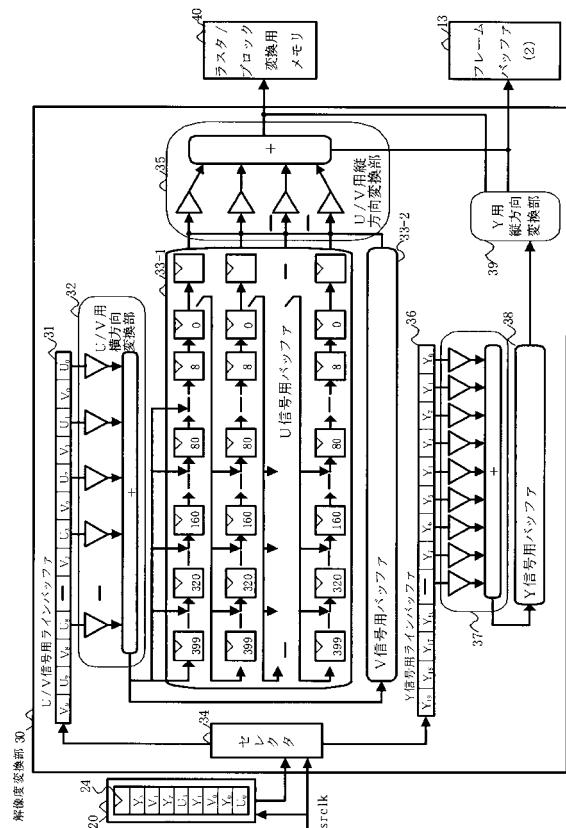

図20は、解像度変換部30の構成を示した図である。

解像度変換部30には、srclkに従って、8bit幅のY、U、Vの各信号がU<sub>0</sub>Y<sub>0</sub>V<sub>0</sub>Y<sub>1</sub>U<sub>1</sub>Y<sub>2</sub>V<sub>1</sub>Y<sub>3</sub>…のような順番で入力される。その信号を受けて、まずセレクタ34が信号をY信号とU/V信号の2つに振り分ける。そして、Y信号はY信号用ラインバッファ36に、U/V信号はU/V信号用ラインバッファ31にそれぞれ入力される。各ラインバッファは1クロックごとにデータが8bit(1sample分)だけシフトしていく。

10

#### 【0132】

そして、U/V信号に関しては、横方向変換部への入力位置にあるレジスタ位置までシフトしてきたあるタイミングで、U<sub>0</sub>U<sub>1</sub>U<sub>2</sub>…(利用するsample数は必要となる解像度変換によって変わる。以下同様)のデータをU/V用横方向変換部32にかけて、その演算結果をU信号用バッファ33-1に格納する。その次のタイミングでは、レジスタが1つシフトするのでV<sub>0</sub>V<sub>1</sub>V<sub>2</sub>…のデータをU/V用横方向変換部32にかけて、その演算結果をV信号用バッファ33-2に格納する。そしてその次は、U<sub>1</sub>U<sub>2</sub>U<sub>3</sub>…というようにUとVのデータを交互に処理していく。

#### 【0133】

一方、Y信号に関しては、あるタイミングでY<sub>0</sub>Y<sub>1</sub>Y<sub>2</sub>Y<sub>3</sub>…のデータをY用横方向変換部37にかけて、その演算結果をY信号用バッファ38に格納する。その次のタイミングではY<sub>1</sub>Y<sub>2</sub>Y<sub>3</sub>Y<sub>4</sub>…のデータを処理するというように、U/Vのデータをそれぞれ1画素分処理していく間に、Yのデータは2画素分の処理を実行していく。このようにしてU/VとYの信号を並列処理していくことによって、YUV422の形式のデータを信号間のタイミングを合わせながら解像度変換をしていくことが可能になる。

20

#### 【0134】

その後、縦方向のU信号用バッファ33-1、V信号用バッファ33-2、及びY信号用バッファ38に横方向解像度変換処理を済ませた各データが溜まつてくると、今度はそれを縦方向の解像度変換器にかけて縦方向の解像度変換を行う。U/V用縦方向変換部35は、U及びVのデータを交互に処理していく。横方向と同様に、Y用縦方向変換部39は、U/V用縦方向変換部35がU/Vのデータを各1画素分処理していく間に、Yのデータ2画素分の処理を実行する。

30

#### 【0135】

このようにして解像度変換された画像データは、本実施形態においては、フレームバッファ(2)13に送られて、次の圧縮処理を待つことになる。第4の実施形態で示したように、もし解像度変換を行ったデータを蓄積すると同時に、圧縮処理にも利用するのであれば、処理をしたデータはラスター/ブロック変換用メモリ40に向けて出力することになる。

#### 【0136】

再び図15において、上記のようにしてラスター/ブロック変換及びコーデック処理と解像度変換処理が並行して実施される。作成されたVGAのデータは、フレームバッファ(2)13に蓄積され、次のVGAデータを利用した処理の開始を待つ。一方、コーデック処理部50はラスター/ブロック変換用メモリ40から与えられた画像データをパラメータレジスタ51に設定されたパラメータの値(Q=Qa)に従ってJPEG圧縮し、圧縮された符号化データJPEGaは順次符号化データDMAC60に受け渡され、符号化データDMAC60はデータバッファ12に対して一定の単位で符号化データを転送する。

40

#### 【0137】

そしてすべての符号化データの転送を完了した時点で、制御用シーケンサ70は、通信部3に対して符号化データの転送完了割込みを送出する。（図15矢印6a）この割り込み通知は画像-通信部間制御信号71を介して伝達される。通信部3はこの割り込みを受

50

けて JPEGa のデータを端末 400a に向けて送信する。

【0138】

UXGA の画像圧縮が終了すると、今度は先に解像度変換してフレームバッファ(2)13に蓄積されたVGA サイズの画像データを用いた処理が開始される。画像データ DMA C20 は、VGA サイズの画像データをフレームバッファ(2)13から読み出して処理を開始する(図15矢印3b)。今度も、このVGA データを利用してコーデック処理部50での処理と、解像度変換部30によるVGA → VGA データの解像度変換処理が並行して実施される(図15矢印4b、5b)。解像度変換部30で作成されたVGA データはフレームバッファ(2)13に蓄積され、その次の圧縮処理に利用される。これ以降の処理に関しては、先に説明した部分と同じ動作であるので説明を省略する。

10

【0139】

なお、本実施形態において処理性能判断部311は、通信部3のネットワーク制御部310の中にあるとしたが、第1の実施形態と同様に例えば、画像処理部1の中に配することや、画像処理部1の制御用シーケンサ70に組み込まれた機能の一部として実装することも可能であり、その位置は本実施形態において制限されるものではない。但し、第1の実施形態と同様に必要なデータ伝送のみを実施してなるべく全体の処理負荷を減らすという観点から考えると、本実施形態のように処理性能判断部311は、通信部3のネットワーク制御部310の中にあるほうが好ましい。

【0140】

このようにすることによって、第4の実施形態での効果に加えて、1つのコーデックを用いて1映像期間内に複数の領域の画像圧縮処理を効率よく実施することが可能になる。特に、フレームバッファから読み出した映像をコーデック処理部と解像度変換部とで並列して利用することで、同一の画角で、異なる解像度の画像を同一映像期間内に処理することを複数の表示側端末から要求される場合に、解像度変換前の元データの読み出し回数を削減することが出来、その分のメモリやバスの帯域性能を有効利用できるようになり、1映像期間内における複数画像を処理する場合に、その処理性能をより向上させることが可能になる。その結果、より多くのユーザからの異なる要求に対応した処理を行うことが可能になる。

20

【0141】

(第6の実施形態)

30

第3の実施形態においては、1映像期間内においてUXGA サイズの1/2 及びUXGA 画像と同一の画角でVGA の解像度に解像度変換した画像、UXGA サイズの画像からVGA サイズで切出した画像2種の処理を実施するものであった。第3の実施形態においては解像度変換部とコーデック処理部が並列に動くことは想定していなかったが、第5の実施形態に示したように解像度変換部とコーデック処理部が並列に動くことが可能な場合には、更に解像度変換を複数回に分離して実施する機能、及び部分画像の処理を連続的に行う場合に、複数の映像期間にまたがった処理を実施する機能を付け加えることにより、更に処理能力を向上させることが可能になる。

【0142】

そのような場合に関して図1、図4、図12及び図21から図23(a)及び(b)を用いて説明する。

40

図1、図4は、図としての構成要素は同一であるので第1の実施形態のものを流用する。また、図12は図としての構成要素は同一であるので第4の実施形態のものを流用する。なお、本実施形態では第2の実施形態と同様、図1における撮像部2のセンサー220は、全画素読み出し方式のCMOS センサーであり、その有効画素数は  $1600 \times 1200$  のいわゆるUXGA サイズであるとする。そして、その画素形態は正方画素であり1/30秒毎に1フレーム分のUXGA 画像を出力することができるものとする。即ち、本実施形態での1映像期間は1/30秒(およそ33.3 ms)であるとする。

【0143】

図21は、本実施形態における要求されている画角と解像度を示した図である。

50

基本的に要求されている画像は第3の実施形態(図10)と同じであるが、本実施形態では処理性能が向上するので、処理性能判断部311は新たにUXGAサイズの元データからVGAサイズで切出した画像データeを処理対象として加わえている。また、UXGAサイズの画像をそのまま圧縮したもの(データd)は他の画像に比べて1/2のフレームレートでの処理が要求されているとする。ここでデータaからeは図4における端末400aから400eの要求に対応している。

#### 【0144】

図22にその処理の流れを示す。本実施形態においては、処理性能判断部311は、同一の画角の画像で解像度が異なる画像の処理を要求された場合、1回のフレームバッファからの読み出しを利用してコーデック処理と解像度変換処理が並列にできる部分がないかを調べる。そして、並列にできる部分があった場合には、その並列化して実施できる部分が部分画像であるかどうかを調べる。

10

#### 【0145】

例えば、本実施形態のように、第1の映像期間中に1/2UXGAサイズの画像データ(データd)の圧縮と、UXGAサイズの元データの画像からVGAサイズの画像に解像度変換した画像(データa)の圧縮を要求されている場合、1/2UXGAサイズの画像データの圧縮を行う際にフレームバッファから読み出す画像データを用いて、並列にUXGA/VGAの解像度変換のうち前半半分を実施することが可能である。そのような場合、処理性能判断部311は制御用シーケンサ70に対して、並列にできる部分を並列に実行し、その結果を受けて、残りの処理を補完させるように指示をする。

20

#### 【0146】

以下、その指示内容に従って制御用シーケンサ70が画像処理部1の各構成要素を制御して処理を実行する様子について説明する。

基本的な処理の流れは第5の実施形態とほぼ同じであるが、今回は最初に圧縮される画像がUXGAサイズの1/2の画像であり、その処理と並行して後続の処理で必要となるUXGA/VGA画像の解像度変換のうち、圧縮用に読み出される1/2UXGA画像のデータを処理して作ることのできる1/2VGAサイズに対応する処理が実施されている(図22矢印5d)。作成された1/2VGA画像はフレームバッファ(2)13へ保存される。

30

#### 【0147】

そして、UXGA1/2分の処理が終わると、(図22矢印6d)制御用シーケンサ70は次いでUXGAサイズの画像dと同じ画角をもつVGAサイズ画像aの処理を開始する。まず、制御用シーケンサ70はフレームバッファ(2)13から画像を読み出して、既に解像度変換が終了した1/2VGAの部分に関してコーデック処理を行うようにするために、画像データDMAC20に対して転送の指示を出す(図22矢印3a)。その転送を受けてコーデック処理部50圧縮処理を開始する(図22矢印4a)。

30

#### 【0148】

フレームバッファ(2)13に蓄えられていた1/2VGAの部分を利用した処理が終了すると、次いで制御用シーケンサ70は、後半1/2分のVGA画像を作り圧縮処理を行うため、画像データDMAC20に対して解像度変換の元データとなるべき後半の1/2UXGAのデータを解像度変換部30に対して転送するように指示を出す(図22矢印7a)。そして後半1/2UXGAのデータを受けて、解像度変換部30は残りのUXGA/VGA変換を開始する(図22矢印8a)。

40

#### 【0149】

解像度変換された画像データは、ラスタブロック変換を経てコーデック処理部50に送られ、コーデック処理部はVGAデータの後半部の圧縮処理を実施する。その後の処理は今までの実施形態における説明と重複するのでここでは省略する。

#### 【0150】

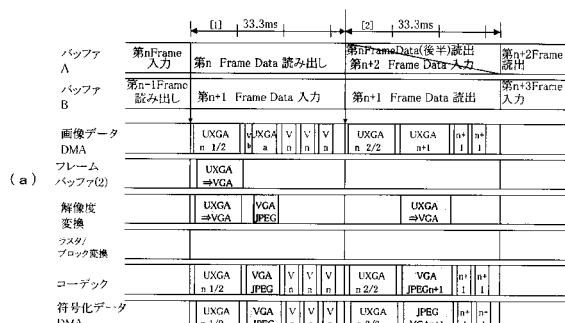

次に、連続した2映像区間に渡ってこの処理を行う場合の図を図23に示す。ここではUXGAの画像を1/2ずつ2つの連続する映像区間で処理することが要求されているの

50

でそのように処理をしている。図23(a)では、この処理をそれぞれ1映像期間の区切りの範囲内で実施するようにスケジュールした場合を示している。

#### 【0151】

図23(a)の[1]の映像期間は図22と同一の内容を示している。この場合、[2]の映像期間では、[1]の映像期間で行った第nフレームのUXGA画像の後半1/2の圧縮処理を行うことになるが、この画像は[2]の映像期間で要求されている第n+1フレームのVGA画像とは異なるものであるので、解像度変換処理とコーデック処理とを並列に実行することができない。そのため、[2]の映像期間では別途0の状態からVGA画像用の解像度変換処理を実施することが必要になるので、その分余計に処理時間がかかり、[2]の映像期間内ではVGA切出し画像処理(データeに対応)が[1]の映像期間に比べて少なくしか出来ない事態になっている。

10

#### 【0152】

しかし、実際には[2]の映像期間内で行っているUXGA画像の後半1/2の処理は、[2]の時間内に限って処理する必要はないものである。既にデータはフレームバッファ10のバッファA内にあるのであるから、[1]の映像期間内に処理能力に余裕があるようであれば、連続する2つの映像期間を1つのものとして考えて、[1]と[2]の映像期間にまたがって処理しても問題はない。そのような場合を図23(b)に示す。

#### 【0153】

ここでは、[1]の映像期間の処理の余裕時間用いてUXGA画像の後半1/2の処理を先行して実施している。そのことにより、[2]の映像期間においても処理時間に余裕ができ、図23(a)に比べてVGA切出し画像処理を1つ多く実行することができるようになり、[1]の映像期間との間での画像処理能力の差を無くすことに成功している。

20

#### 【0154】

なお、本実施形態において処理性能判断部311は、通信部3のネットワーク制御部310の中にあるとしたが、第1の実施形態と同様に例えば、画像処理部1の中に配することや、画像処理部1の制御用シーケンサ70に組み込まれた機能の一部として実装することも可能であり、その位置は本実施形態において制限されるものではない。もし、処理性能判断部311が制御用シーケンサ70に組み込まれていた場合には、各端末から要求の出ている処理内容がネットワーク制御部310を経由して、画像-通信部間制御信号71を介して制御用シーケンサ70に伝達され、その情報を用いて上記判断を実施することになる。

30

#### 【0155】

そして、判断結果のサービス提供の可否は画像-通信部間制御信号71を介してネットワーク制御部310に伝達され、ネットワーク制御部310が各端末にその情報を送信することになる。但し、第1の実施形態と同様に必要なデータ伝送のみを実施してなるべく全体の処理負荷を減らすという観点から考えると、本実施形態のように処理性能判断部311は通信部3のネットワーク制御部310の中にあるほうが好ましい。

#### 【0156】

このようにして、第5の実施形態での効果に加えて、部分的であっても処理の並列化できる部分を並列化すること、及び並列化を実施する上で本来必要となる処理が部分的に処理された場合には、その処理を補完することができるような仕組みを持つことによって、1映像期間内に1つの処理装置によって処理することのできる処理能力を高めることができる。本実施形態では、第3の実施形態に比べてVGA画像の処理を更に1画像分多く処理することが可能になっている。その結果、1映像期間内に1つの処理装置によってより多くのユーザからの異なる要求に対応した処理を行うことが可能になる。

40

#### 【0157】

また、部分画像の処理を複数の映像期間で連続的に行う場合に、複数の映像期間にまたがった処理を実施する機能を付け加えることにより、更に処理能力を向上させることができなり、複数の映像期間における実行並列度の差による処理能力のばらつきを小さくす

50

ることが可能になる。

【0158】

(第7の実施形態)

第1から第6までの実施形態では、コーデックの処理は、基本的にJPEG圧縮の処理を例にしていた。しかし、コーデックの処理はJPEGの圧縮処理だけに限らない。そのように複数の方式での圧縮処理を1つの映像区間に内に複数回実施する場合の例を図1、図12、図19、及び図24、図25を用いて説明する。

【0159】

図1は図としての構成要素は同一であるので第1の実施形態のものを流用する。また、図12は図としての構成要素は同一であるので第4の実施形態のものを流用する。更に図19は図としての構成要素は同一であるので第5の実施形態のものを流用する。なお、本実施形態では、第1の実施形態と同様、図1における撮像部2のセンサー220は、正方画素のプログレッシブ形式のCCDであるとする。また、その有効画素数は $640 \times 480$ のいわゆるVGAサイズであり、1/30秒毎に1フレームのVGA画像を出力することができるものとする。即ち、本実施形態での1映像期間は1/30秒(およそ33.3ms)であるとする。

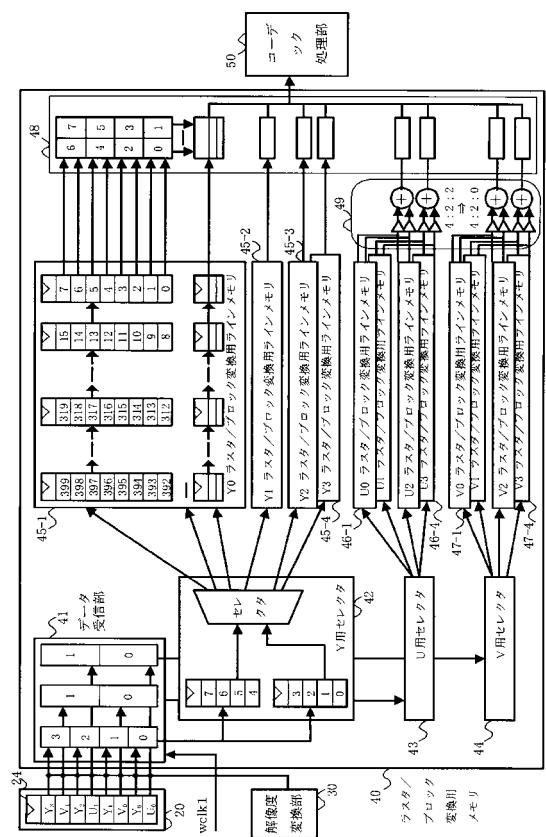

【0160】

図24は、コーデックにおける圧縮処理にJPEGとMPEG4の2通りの処理が入る場合の処理の流れを示した図である。また、図25は、MPEG4圧縮を実施する際に必要になるYUV422からYUV420への変換機能を備えたラスタブロック変換用ラインメモリ40を示した図である。図25は、構成要素的には第5の実施形態に示した図19と似ているが、図19に比べて各ラスタ/ブロック変換用ラインメモリのライン長が半分になり、その代わりライン数が2倍になるように組替えられている。これは、本実施形態におけるコーデック処理部50がMPEG4を扱う場合に、扱うデータの単位がY信号に関して $16 \times 16$ sampleのものであるため、そのデータが供給しやすいうように各ラスタ/ブロック変換用ラインメモリを構成するメモリモジュールの利用法を図19の場合から変更したものである。

【0161】

また、U/Vそれぞれのラスタブロック変換用ラインメモリ46-1~4及び47-1~4の出口にはYUV422のデータからYUV420のデータに変換するためのデータ変換部49が追加されている。このデータ変換部も図19の場合からメモリモジュールの利用法を変更したことに付随して追加接続された機能ブロックであり、この処理を必要としない場合にはスルーする機能をもつものである。

【0162】

図25内部の動作は、基本的には図19の動作と同じである。異なるのはデータの転送単位は16ラインを基本に考えるので、Y信号のラスタブロック変換用ラインメモリは45-1と45-2の組を1つの16ラインのバッファ、45-3と45-4の組をもう1つの16ラインのバッファと考えるダブルバッファ構成とみなす点である。

【0163】

U/V信号用のラスタ/ブロック変換用ラインメモリ46-1~4及び47-1~4に關しても同様に46-1、2と46-3、4、47-1、2と47-3、4のダブルバッファとみなす。更にYUV422からYUV420への信号の変換動作が必要になる場合には、ラインメモリの出口にあるデータ変換部49で元の画像上で上下に隣接する2ラインのデータから新しいデータが作成される。

【0164】

ラスタ/ブロック変換用メモリ40は、図19に示した構成から図25のような構成にデータパスを切り替えることによって組みなおすことが可能である。本実施形態においては、圧縮するデータの特性に応じてデータバスの設定を変更することによってこれらを切り替えている。

【0165】

10

20

30

40

50

以上説明したようなラスタ / ブロック変換用メモリ 40 を含む画像処理部 1 の動作の流れについて、図 12 を参照しながら図 24 を用いて説明する。

【0166】

図 12において、現像処理部 230 から出力された V G A サイズの画像データはフレームバッファ 10 にフレーム単位で格納される。フレームバッファ 10 は、図 24 に示すように内部はダブルバッファ形式になっており、第 n 番目のフレームと第 n + 1 番目のフレームの画像データがそれぞれ別の領域 (バッファ A 及び B) に格納されるようになっている。

【0167】

今、第 n フレームのフレームバッファ 10 のバッファ A への蓄積が完了したとする。すると、現像処理部 230 から制御用シーケンサ 70 に対してフレームデータの転送完了割込みが発生する (図 24 矢印 1)。 10

【0168】

転送完了割込みを受けて、制御用シーケンサ 70 は、まずコーデック処理部 50 のパラメータレジスタ 51 に対してどのような処理をコーデック処理部でおこなうかを指示するためのパラメータをセットする (図 24 矢印 2a)。本実施形態では、最初の圧縮処理として M P E G 4 を用いた圧縮が要求されているとする。ここでは、制御用シーケンサ 70 は M P E G 4 処理をコーデック処理部 50 に実施させるための複数のパラメータをパラメータレジスタ 51 に設定し、コーデック処理部 50 の処理モードを M P E G 4 処理モードに設定する。 20

【0169】

次いで、制御用シーケンサ 70 は、ラスタ / ブロック変換用メモリ 40 に対して、画像データ D M A C 20 から入力される Y U V 4 2 2 形式の V G A サイズの画像データを Y U V 4 2 0 形式に変換し、M P E G 4 モードでコーデック処理部 50 にデータを提供するように指示をする (図 24 矢印 4a)。指示を受けたラスタ / ブロック変換用メモリ 40 は、先に図 25 で示したようにデータパスの構成を組替え、M P E G 4 モードで動作できるようにした後、データの転送が開始されるのを待つ。

【0170】

次いで、制御用シーケンサ 70 は、画像データ D M A C 20 に対して、第 n フレームの画像データをフレームバッファ 10 のバッファ A から読み出して、ラスタ / ブロック変換用メモリ 40 に対してデータを供給するための転送を開始するように指示をする (図 24 矢印 3a)。指示を受けた画像データ D M A C 20 は、画像データをフレームバッファ 10 から読み出して、ラスタ / ブロック変換用メモリ 40 に供給する。 30

【0171】

画像データの供給を受けたラスタ / ブロック変換用メモリ 40 は、Y U V 4 2 2 → Y U V 4 2 0 の変換を開始し (図 24 矢印 7a)、ブロック化したデータを所定の順序でコーデック処理部 50 に提供する。ブロック化された画像データの提供を受けたコーデック処理部 50 は M P E G 4 形式での画像圧縮を実施し、順次符号化データを符号化データ D M A C 6 0 に受け渡す。符号化データ D M A C 6 0 は、データバッファ 12 に対して一定の単位で符号化データを転送する。そして第 n フレームにおいて画像を構成するすべての符号化データの転送を完了した時点で、制御用シーケンサ 70 はデータバッファ通信部 3 に対して符号化データの転送完了割込みを送出する (図 24 矢印 6a)。この割り込み通知は画像 - 通信部間制御信号 71 を介して伝達される。 40

【0172】

図 24において、M P E G 4 の符号化データの転送完了割込みを送出した (図 24 矢印 6a) ことを制御用シーケンサ 70 が認識すると、制御用シーケンサ 70 は次に求められている画像処理のパラメータを調べる。ここでは、次に要求されている動作は V G A サイズの画像データをその解像度のまま J P E G 圧縮することが求められているとする。また、同じ画角のデータを Q V G A に解像度変換したデータを用いた J P E G 処理がその後続にあることもわかっているので、画像圧縮処理と解像度変換処理とを並列的に行うことも 50

設定が必要になる。

【0173】

そこで制御用シーケンサ70は、まず、JPEG処理をコーデック処理部50に実施させるための複数のパラメータをパラメタレジスタ51に設定し、コーデック処理部50の処理モードをJPEG処理モードに設定する(図24矢印2b)。

【0174】

次いで、制御用シーケンサ70は、ラスタ/ブロック変換用メモリ40に対して、ブロック化の処理モードをJPEG用に変更するように指示をする(図24矢印4b)。指示を受けたラスタ/ブロック変換用メモリ40は図25に示したような構成から図19で示したようにデータバスの構成を組替え、JPEGモードで動作できるようにした後、データの転送が開始されるのを待つ。

【0175】

次いで、制御用シーケンサ70は、解像度変換部30に対して、画像データDMAC20から入力されるVGAサイズの画像データをQVGAサイズに解像度変換するように指示をする(タイミング図示せず)。

【0176】

次いで、制御用シーケンサ70は、画像データDMAC20に対して、第nフレームの画像データをフレームバッファ10のバッファAから読み出して、コーデック処理部50に対してデータを供給するための転送を開始するように指示をする(図24矢印3b)。

【0177】

本実施形態では、フレームバッファ10から読み出したデータを解像度変換部30とラスタ/ブロック変換用メモリ40に並列的に供給する必要があるので、そのようにパラメータを転送領域設定レジスタ21に設定する。

【0178】

画像データDMAC20がデータの転送を開始すると、解像度変換部30は、VGA QVGAの画像変換を開始し(図24矢印8b)、そのデータをフレームバッファ(2)13に蓄積する。一方、コーデック処理部は、ラスタ/ブロック変換用メモリ40によってブロック化された画像データを受けてJPEG方式での圧縮を開始し(図24矢印5b)、順次JPEG方式で圧縮された符号化データJPEGbを符号化データDMAC60に受け渡す。

【0179】

符号化データDMAC60は、データバッファ12に対して一定の単位で符号化データを転送する。そして第nフレームにおいて符号化データJPEGbの転送を完了した時点で、制御用シーケンサ70はデータバッファ通信部3に対して符号化データの転送完了割込みを送出する(図24矢印6b)。この割り込み通知は画像-通信部間制御信号71を介して伝達される。そして、その次は、フレームバッファ(2)に蓄積されたQVGAに解像度変換された画像データを利用して、JPEGの圧縮処理が開始されることになる。これ以降の処理に関してはこれまでの実施形態と同一であるので説明の詳細は省略する。

【0180】

なお、本実施形態においても処理性能判断部311は、通信部3のネットワーク制御部310の中にあるとしたが、第1の実施形態と同様に例えば、画像処理部1の中に配することや、画像処理部1の制御用シーケンサ70に組み込まれた機能の一部として実装することも可能であり、その位置は本実施形態において制限されるものではない。但し、第1の実施形態と同様に必要なデータ伝送のみを実施してなるべく全体の処理負荷を減らすという観点から考えると、本実施形態のように処理性能判断部311は、通信部3のネットワーク制御部310の中にあるほうが好ましい。

【0181】

このようにすることによって、これまでに説明した第1から第6の実施形態までの効果に加えて、1つのコーデックを用いて1映像期間内に複数の符号化方式による画像圧縮処理を効率よく実施することが可能になる。特に、圧縮方式に応じてデータバスを動的に

10

20

30

40

50

切り替えるような機構をもつことによって、内部のメモリを無駄なく利用することが可能になり、I C 内部の資源の有効活用を図りながら、処理性能の向上を図ることが可能になる。

【図面の簡単な説明】

【0182】

【図1】本発明の第1の実施形態に係る撮像装置の構成を示す図である。

【図2】本発明の第1の実施形態における画像処理部の詳細を示す図である。

【図3】本発明の第1の実施形態における画像処理部の動作の流れを示す図である。

【図4】本発明の第1の実施形態に係る撮像装置を用いたシステムの構成例を示す図である。

10

【図5】本発明の第2の実施形態におけるビューワ側で要求する画像の画角と解像度を示す図である。

【図6】本発明の第2の実施形態における画像処理部の詳細を示す図である。

【図7】本発明の第2の実施形態における画像処理部の動作の流れを示す図である。

【図8】本発明の第3の実施形態における画像処理部の詳細を示す図である。

【図9】本発明の第3の実施形態における画像処理部の動作の流れを示す図である。

【図10】本発明の第3の実施形態におけるビューワ側で要求する画像の画角と解像度を示す図である。

【図11】本発明の第3の実施形態における連続する2映像期間での画像処理部の動作の流れを示す図である。

20

【図12】本発明の第4の実施形態における画像処理部の詳細を示す図である。

【図13】本発明の第4の実施形態における画像処理部の動作の流れを示す図である。

【図14】本発明の第4の実施形態におけるビューワ側で要求する画像の画角と解像度を示す図である。

【図15】本発明の第5の実施形態における画像処理部の詳細を示す図である。

【図16】本発明の第5の実施形態におけるビューワ側で要求する画像の画角と解像度を示す図である。

【図17】本発明の第5の実施形態における画像データDMAの詳細を示す図である。

【図18】本発明の第5の実施形態における画像データDMAと解像度変換部及びラスター/ブロック変換用メモリとの間のデータの受け渡しタイミングを示す図である。

30

【図19】本発明の第5の実施形態におけるラスター/ブロック変換用メモリの詳細を示す図である。

【図20】本発明の第5の実施形態における解像度変換部の詳細を示す図である。

【図21】本発明の第6の実施形態におけるビューワ側で要求する画像の画角と解像度を示す図である。

【図22】本発明の第6の実施形態における画像処理部の動作の流れを示す図である。

【図23】本発明の第6の実施形態における連続する2映像期間での画像処理部の動作の流れを示す図である。

【図24】本発明の第7の実施形態における画像処理部の動作の流れを示す図である。

【図25】本発明の第7の実施形態におけるラスター/ブロック変換用メモリの詳細を示す図である。

40

【符号の説明】

【0183】

1：画像処理部

2：撮像部

3：通信部

4：ネットワーク網

5：撮像装置

10：フレームバッファ

11：画像処理用メモリ

50

- 1 2 : データバッファ

1 3 : フレームバッファ(2)

2 0 : 画像データDMA (ダイレクトメモリアクセス・コントローラ)

2 1 : 転送領域設定レジスタ

2 2 : 64bit FIFOレジスタ

2 3 : クロック制御部

2 4 : FIFO読み出しポート

3 0 : 解像度変換部

4 0 : ラスター/ブロック変換用メモリ

5 0 : コーデック処理部 10

5 1 : パラメータレジスタ

6 0 : 符号化データDMA

7 0 : 制御用シーケンサ

7 1 : 画像 - 通信部制御信号

2 1 0 : レンズ

2 2 0 : センサー

2 3 0 : 現像処理部

3 1 0 : ネットワーク制御部

3 1 1 : 処理性能判断部

3 2 0 : ネットワークインターフェース 20

4 0 0 : 表示端末

4 0 1 : ビューワ

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

: UXGA サイズ画像データ (1600x1200) 画像データ d

: UXGA サイズデータから切出す VGA サイズ (640x480) データ b,c

UXGA サイズデータから解像度変換した VGA サイズ (640x480) データ a

【図12】

【図13】

【図14】

: UXGA サイズ画像データ (1600x1200) 画像データ e

: UXGA サイズデータから切出す VGA サイズ (640x480) データ c

UXGA サイズデータから解像度変換した VGA サイズ (640x480) データ a,b

UXGA サイズデータから解像度変換した QVGA サイズ (320x240) データ d

【図15】

【図16】

: UXGA サイズ画像データ (1600x1200) 画像データ a

: UXGA サイズデータから切出す VGA サイズ (640x480) データ d

UXGA サイズデータから解像度変換した VGA サイズ (640x480) データ b

UXGA サイズデータから解像度変換した QVGA サイズ (320x240) データ c

【図17】

【図18】

【図19】

【図20】

【図21】

: UXGA サイズ画像データ (1600x1200) 画像データ d

: UXGA サイズデータから切出す VGA サイズ (640x480) データ b,c,e

UXGA サイズデータから解像度変換した VGA サイズ (640x480) データ a

【図22】

【図23】

【図24】

## 【図25】

---

フロントページの続き

(56)参考文献 特開2005-051664(JP, A)

特開2005-006239(JP, A)

特開2004-266768(JP, A)

実用新案登録第3060839(JP, Y2)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225