(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6204718号

(P6204718)

(45) 発行日 平成29年9月27日(2017.9.27)

(24) 登録日 平成29年9月8日(2017.9.8)

|              |                    |

|--------------|--------------------|

| (51) Int.Cl. | F 1                |

| B 41 J 2/015 | (2006.01)          |

| B 41 J 2/01  | (2006.01)          |

| B 41 J 2/14  | (2006.01)          |

| B 41 J 2/05  | (2006.01)          |

|              | B 41 J 2/015 1 O 1 |

|              | B 41 J 2/01 4 O 3  |

|              | B 41 J 2/14 6 1 1  |

|              | B 41 J 2/05        |

請求項の数 13 (全 22 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2013-138440 (P2013-138440) |

| (22) 出願日  | 平成25年7月1日(2013.7.1)          |

| (65) 公開番号 | 特開2015-9529 (P2015-9529A)    |

| (43) 公開日  | 平成27年1月19日(2015.1.19)        |

| 審査請求日     | 平成28年6月21日(2016.6.21)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】 素子基板、記録ヘッド及び記録装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の記録素子と、

前記複数の記録素子に対応して備えられ前記複数の記録素子を駆動する複数の駆動素子と、

1つの基準電圧と傾きが異なる2つのランプ波とを入力してダブルパルスを生成し、前記ダブルパルスを前記複数の駆動素子に印加して前記複数の駆動素子を駆動する駆動回路とを有し、

前記駆動回路は、

前記1つの基準電圧と前記傾きが異なる2つのランプ波それぞれとを生成する生成回路と、

前記1つの基準電圧と前記傾きが異なる2つのランプ波それぞれとを比較する比較回路とを有し、

前記比較回路における比較の結果からパルス幅の異なるダブルパルスを生成することを特徴とする素子基板。

## 【請求項 2】

前記ダブルパルスはプレパルスとインターバル時間とメインパルスとから構成され、

前記駆動回路において生成されるダブルパルスにおいて、各パルス幅は異なっても前記プレパルスの幅と前記インターバル時間と前記メインパルスの幅とのトータル時間は一定であることを特徴とする請求項1に記載の素子基板。

**【請求項 3】**

前記生成回路は、デジタル／アナログ変換器であり、

前記デジタル／アナログ変換器は、

複数のカレントミラー回路と、

前記複数のカレントミラー回路それぞれの出力に直列に接続され、前記複数のカレントミラー回路からの出力をON／OFFする複数のスイッチと、

前記複数のスイッチを並列に接続し、前記複数のスイッチをON／OFFすることで異なる電圧を出力する出力部とを有し、

前記出力部は、

互いに抵抗値の異なる複数の抵抗と、

前記複数の抵抗それぞれに直列に接続された複数のスイッチとを有し、

前記出力部の複数のスイッチをON／OFFすることで前記ランプ波の傾きを異ならせることを特徴とする請求項1又は2に記載の素子基板。

**【請求項 4】**

前記生成回路は、デジタル／アナログ変換器であり、

前記デジタル／アナログ変換器は、

複数のカレントミラー回路と、

前記複数のカレントミラー回路それぞれの出力に直列に接続され、前記複数のカレントミラー回路からの出力をON／OFFする複数のスイッチと、

前記複数のスイッチを並列に接続し、前記複数のスイッチをON／OFFすることで異なる電圧を出力する出力部と、

前記複数のカレントミラー回路に電流を供給する電流源と、

前記電流源に接続され、互いにミラー比が異なる別の複数のカレントミラー回路と、

前記別の複数のカレントミラー回路それぞれに接続された別の複数のスイッチとを有し、

前記別の複数のスイッチをON／OFFすることで前記ランプ波の傾きを異ならせることを特徴とする請求項1又は2に記載の素子基板。

**【請求項 5】**

前記比較回路は、

前記基準電圧を記憶する第1のコンデンサと、

前記第1のコンデンサに対して直列に接続される、互いに容量の異なる複数の第2のコンデンサと、

前記複数の第2のコンデンサそれぞれに直列に接続された複数のスイッチとを有し、

前記複数のスイッチをON／OFFすることで前記ランプ波の傾きを異ならせることを特徴とする請求項1乃至4のいずれか1項に記載の素子基板。

**【請求項 6】**

前記生成回路は、

前記プレパルスを生成するために用いるランプ波と前記メインパルスを生成するために用いるランプ波とが共に、時間とともに立ち上がる波形をもつように生成することを特徴とする請求項2に記載の素子基板。

**【請求項 7】**

前記生成回路は、

前記プレパルスを生成するために用いるランプ波が時間とともに立ち上がる波形をもつように生成する一方、前記メインパルスを生成するために用いるランプ波とが時間とともに立ち下がる波形をもつように生成することを特徴とする請求項2に記載の素子基板。

**【請求項 8】**

前記生成回路はさらに、

前記プレパルスを生成するために用いるランプ波の立ち上りにおける電圧が前記1つの基準電圧より高くなり前記メインパルスを生成するために用いるランプ波の立ち下りにおける電圧が前記1つの基準電圧より低くなるまでの時間が前記インターバル時間を

10

20

30

40

50

規定するように前記傾きが異なる2つのランプ波を生成することを特徴とする請求項7に記載の素子基板。

【請求項9】

前記複数の記録素子は、時分割駆動のために互いに近傍に配置される複数の記録素子から構成される複数のグループに分割され、

前記複数のグループそれぞれに、前記比較回路が1つずつ備えられることを特徴とする請求項1乃至8のいずれか1項に記載の素子基板。

【請求項10】

前記複数の記録素子それぞれにインクを供給するインク供給口をさらに有することを特徴とする請求項1乃至9のいずれか1項に記載の素子基板。 10

【請求項11】

請求項10に記載の素子基板を複数、前記複数の記録素子の配列方向に配置して記録媒体の幅に対応した記録幅としたフルライン記録ヘッドを構成することを特徴とする記録ヘッド。

【請求項12】

前記フルライン記録ヘッドは、インクを吐出して記録媒体に記録を行うインクジェット記録ヘッドであることを特徴とする請求項11に記載の記録ヘッド。

【請求項13】

請求項12に記載の記録ヘッドを用いて記録を行う記録装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は素子基板、記録ヘッド及び記録装置に関し、特に、例えば、素子基板を組み込んだインクジェット方式に従って記録を行うフルライン記録ヘッド及びこれを用いて記録を行う記録装置に関する。また、本発明はより詳細には、複数の記録素子と、各記録素子を駆動するための駆動回路とが同一の素子基板上に設けられた素子基板を搭載する記録ヘッド及び記録装置に関する。

【背景技術】

【0002】

例えば、ワードプロセッサ、パーソナルコンピュータ、ファクシミリなどの情報出力装置として、所望の文字や画像等の情報を用紙やフィルム等シート状の記録媒体に記録を行うインクジェット記録装置（以下、記録装置）が一般的に広く用いられている。 30

【0003】

一般に、記録装置に搭載される記録ヘッドの電気熱変換素子（ヒータ）とその駆動回路は、例えば、特許文献1に示されているように半導体プロセス技術を用いて同一基板上に形成されている。この一形態として、インク供給口が基板の中央付近にあり、これを挟んだ位置にヒータが相対する構成の素子基板を実装した記録ヘッドが提案されている。

【0004】

また、例えば、特許文献2には温度に対する記録ヘッドの吐出特性のばらつきを補正する方法が開示されている。 40

【0005】

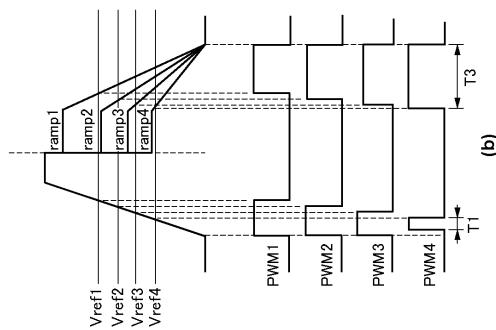

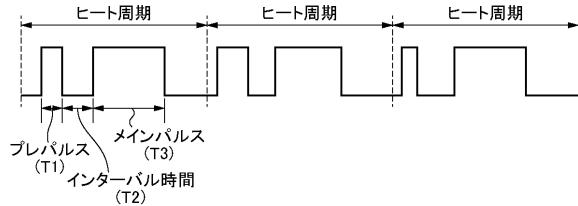

図22はダブルパルスの構成を示す図である。

【0006】

図22に示すように、ダブルパルスでは、メインパルスの吐出タイミングの前に記録ヘッドに対する予熱信号（プレパルス）を発生させ、さらに、メインパルスとプレパルスとの間にインターバル時間を発生させる。これらのパルスの各時間において、記録ヘッドの温度補正、温度センサの感度のばらつきによる補正、ノズル毎の温度-吐出特性のばらつきによる補正等を反映させる。なお、メインパルスのパルス幅とインターバル時間とプレパルスのパルス幅はそれぞれ、T1、T2、T3とし、以下の説明でも同じ参照符号を用いる。 50

**【0007】**

例えば、特許文献3では、環境温度に対してダブルパルスの各時間を調節する構成が開示されている。

**【0008】**

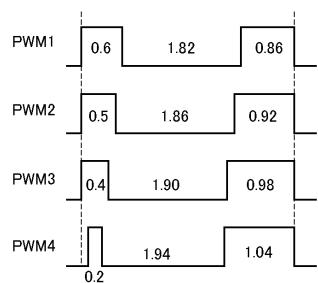

図23は、特許文献3に開示する構成に基づいた、環境温度に対してダブルパルスの各時間を調節する例を示す図である。

**【0009】**

図23によれば、例えば、環境温度( $e n v T$ )が28度以上のときに駆動パルスとしてはPWM4が選択される。この場合、他の3つのパルス(PWM1～PWM3)に比べて、パルスのスタート時間が遅れるが、原則としてダブルパルスのトータル時間は一定である。特に、メインパルスの立下りは吐出タイミングを揃えるために一定となっている。10

**【先行技術文献】****【特許文献】****【0010】**

【特許文献1】特開2007-022069号公報

【特許文献2】特開平10-119273号公報

【特許文献3】特開2008-302691号公報

**【発明の概要】****【発明が解決しようとする課題】****【0011】**

以上説明したような従来例の構成をとると、HE信号のパルス幅を任意に設定可能である。しかしながら、同一のヒート周期で複数回ヒータを駆動する場合、即ち、図22に示すようにHE信号パルスを複数回、与える場合には、複数のパルス時間分の基準電圧設定データが必要となるためデータ数が増加してしまう。その結果、記録装置の本体部から記録ヘッドへのデータ転送速度を上げたり、データを分割する等の対策が必要となる。これは、記録動作の信頼性の低下や、記録ヘッドの素子基板における端子数の増加という問題を生じさせる。また、複数のパルス幅データを設定しておくメモリも複数必要になるため回路規模も増大してしまう。

**【0012】**

本発明は上記従来例に鑑みてなされたもので、より信頼性の高い記録動作を実現するとともに、素子基板のサイズの削減や、構成の簡素化を図った素子基板とこれを用いた記録ヘッドとその記録ヘッドを搭載した記録装置を提供することを目的とする。30

**【課題を解決するための手段】****【0013】**

上記目的を達成するために本発明の素子基板は次のような構成からなる。

**【0014】**

即ち、複数の記録素子と、前記複数の記録素子に対応して備えられ前記複数の記録素子を駆動する複数の駆動素子と、1つの基準電圧と傾きが異なる2つのランプ波とを入力してダブルパルスを生成し、前記ダブルパルスを前記複数の駆動素子に印加して前記複数の駆動素子を駆動する駆動回路とを有し、前記駆動回路は、前記1つの基準電圧と前記傾きが異なる2つのランプ波それぞれとを生成する生成回路と、前記1つの基準電圧と前記傾きが異なる2つのランプ波それぞれとを比較する比較回路とを有し、前記比較回路における比較の結果からパルス幅の異なるダブルパルスを生成することを特徴とする。40

**【0015】**

また本発明を別の側面から見れば、上記構成の素子基板を用いた記録ヘッド、特にインクジェット方式に従ってインクを吐出して記録を行うフルラインのインクジェット記録ヘッドを備える。

**【0016】**

さらに本発明を別の側面から見れば、上記のフルライン記録ヘッドを用いて記録を行う記録装置を備える。

10

20

30

40

50

**【発明の効果】****【0017】**

従って本発明によれば、1つの基準電圧から複数のダブルパルスを生成することができるという効果がある。これにより、複数のダブルパルスの生成のために多くのデータを用いる必要もないので、多くのデータの転送や制御に必要であった構成をなくすことができる。これは素子基板のサイズの削減や簡素化、記録動作の高信頼性に資するものとなる。

**【図面の簡単な説明】****【0018】**

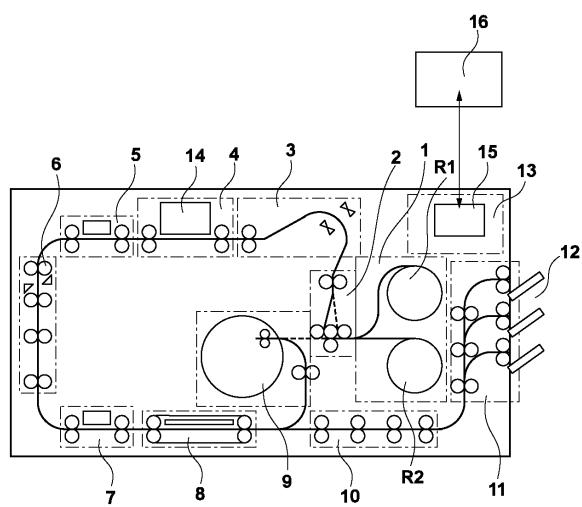

**【図1】**本発明の代表的な実施例であるインクジェット記録装置の内部構成を示す概略側断面図である。10

**【図2】**図1に示す記録装置における片面記録時の動作を説明するための図である。

**【図3】**図1に示す記録装置における両面記録時の動作を説明するための図である。

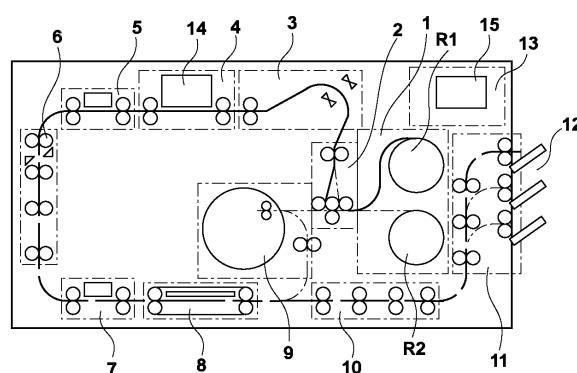

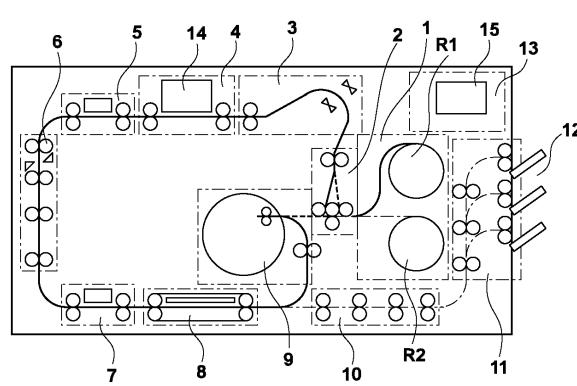

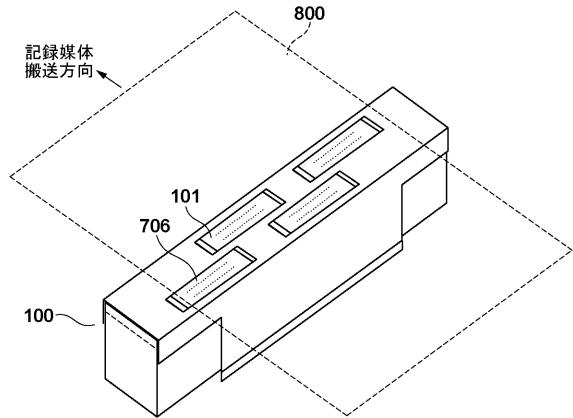

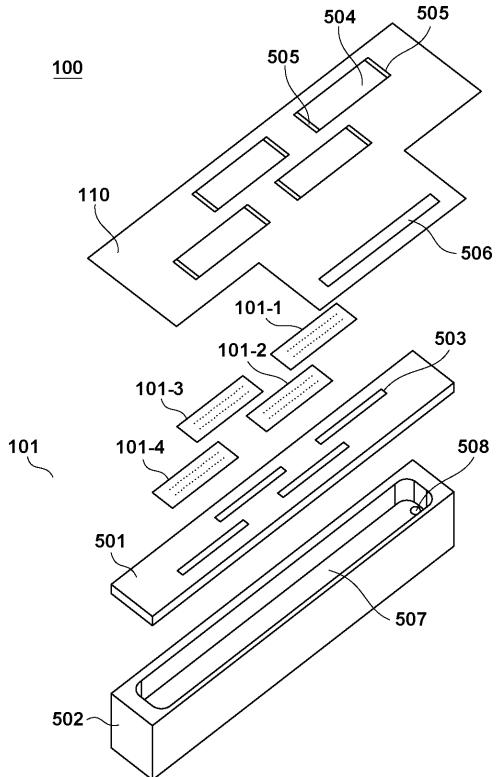

**【図4】**フルライン記録ヘッドの斜視図である。

**【図5】**フルライン記録ヘッドの分解斜視図である。

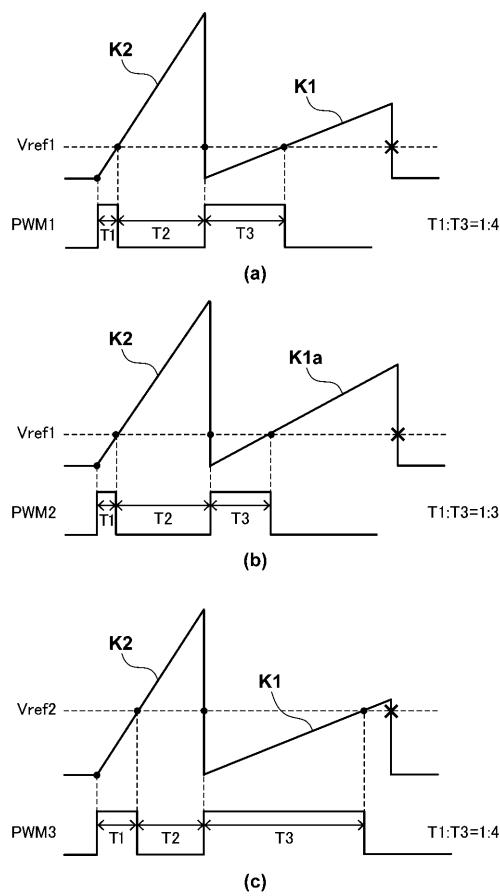

**【図6】**実施例1に従ってダブルパルスのヒートイネーブル(HE)信号を生成する様子を示すタイムチャートである。

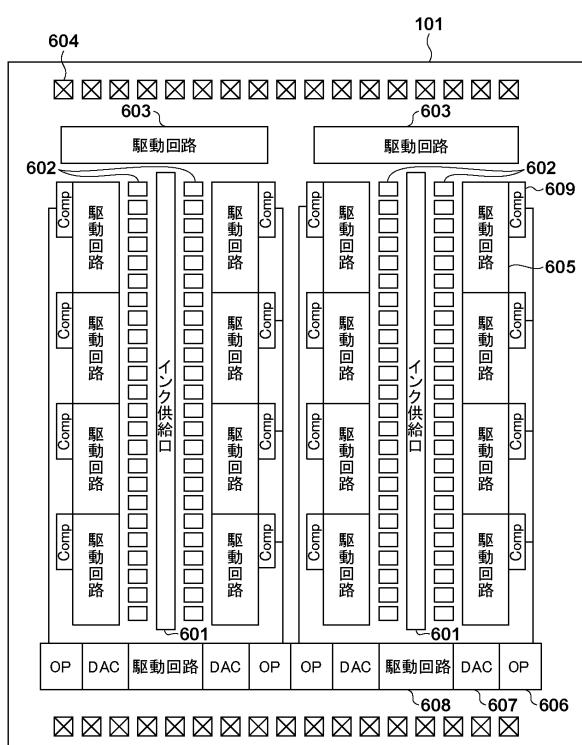

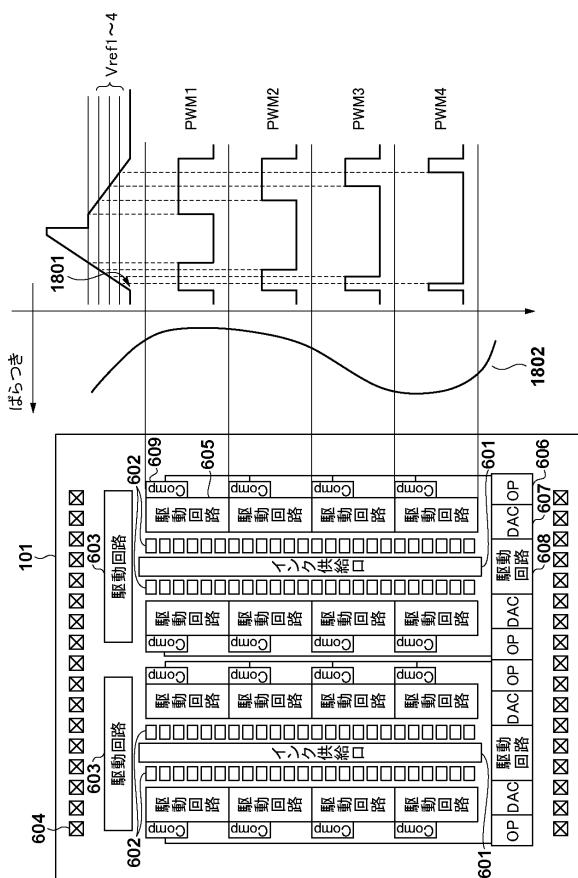

**【図7】**記録ヘッドの素子基板のレイアウトを模式的に示す図である。

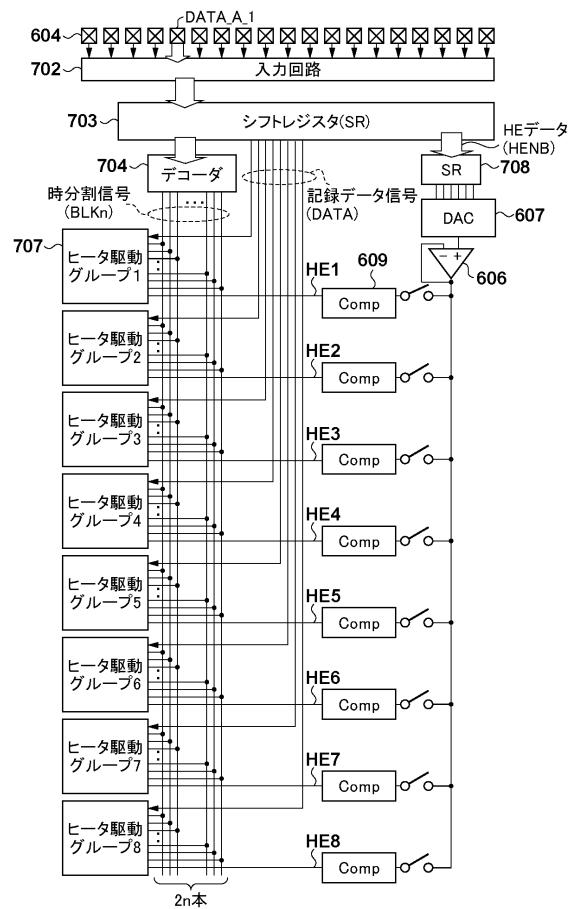

**【図8】**図7に示す回路レイアウトの一部の回路構成の詳細と信号の流れを模式的に示す図である。

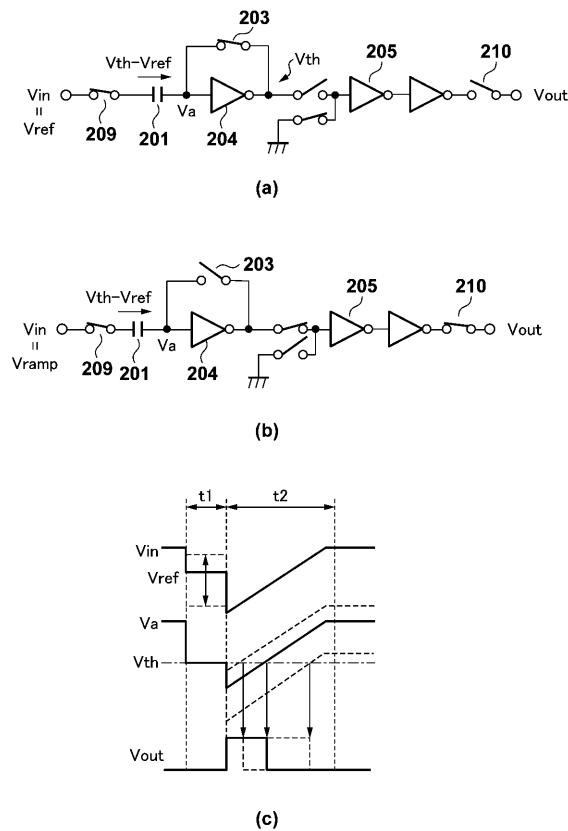

**【図9】**コンパレータ609の動作を説明する図である。20

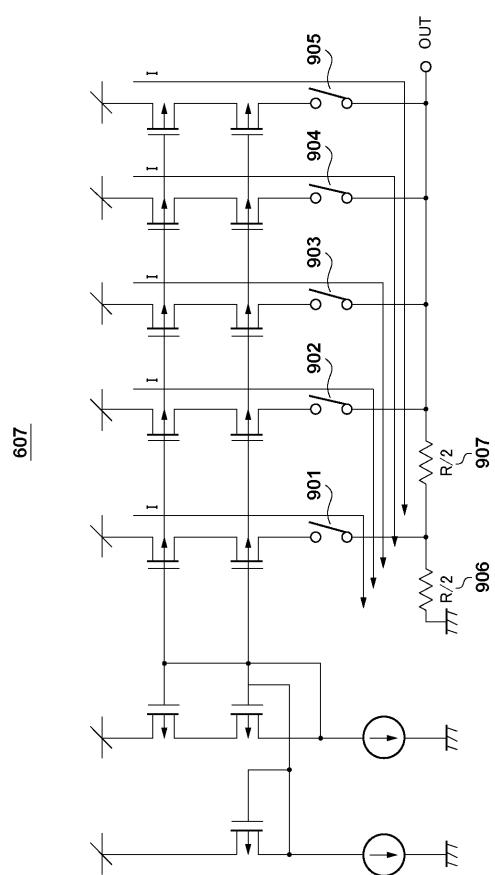

**【図10】**ランプ波と基準電圧(Vref)を生成するDAC607の構成を示す回路図である。

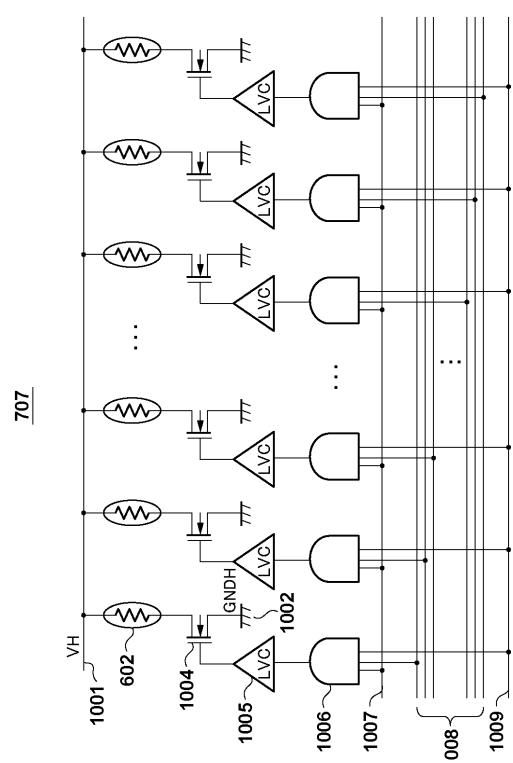

**【図11】**ヒータ駆動グループ707の内部構成を示す回路図である。

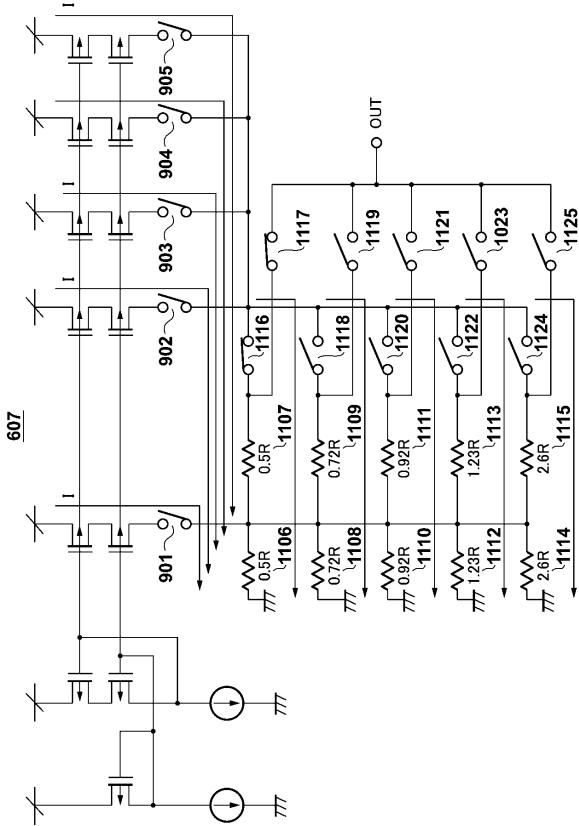

**【図12】**抵抗を切り替える構成を備えたDAC607の回路図である。

**【図13】**カレントミラーリー比を切り替える構成を備えたDAC607の回路図である。

**【図14】**容量を切り替える構成を備えたコンパレータ609の回路図である。

**【図15】**実施例2に従ってダブルパルスのヒートイネーブル(HE)信号を生成する様子を示すタイムチャートである。

**【図16】**実施例3に従ってダブルパルスのヒートイネーブル(HE)信号を生成する様子を示すタイムチャートである。30

**【図17】**実施例3に従った駆動パルスPWM1～4の生成の様子を示す図である。

**【図18】**プレパルスを基準としてメインパルス用ランプ波の傾きを変化させて異なる駆動パルスPWM1～4を求める場合に3つの異なる方法を用いる際に必要な値をまとめた表を示す図である。

**【図19】**素子基板においてヒータ列方向に膜厚、抵抗等のばらつきがあったときに適用される駆動パルスの変更を示す図である。

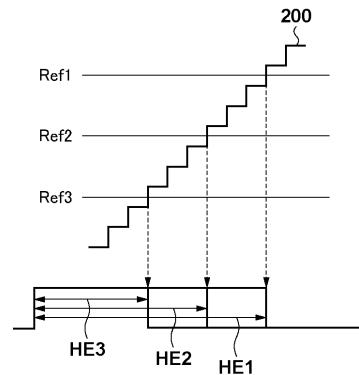

**【図20】**ランプ波と基準電圧(Ref)を比較することでパルス幅を変調する方法について説明する図である。

**【図21】**基準電圧とランプ波とを比較するコンパレータの構成を示す図である。

**【図22】**ダブルパルスの構成を示す図である。40

**【図23】**特許文献3に開示する構成に基づいた、環境温度に対してダブルパルスの各時間を調節する例を示す図である。

**【発明を実施するための形態】****【0019】**

以下添付図面を参照して本発明の好適な実施例について、さらに具体的かつ詳細に説明する。なお、既に説明した部分には同一符号を付し重複説明を省略する。

**【0020】**

なお、この明細書において、「記録」(「プリント」という場合もある)とは、文字、図形等有意の情報を形成する場合のみならず、有意無意を問わない。また人間が視覚で知覚し得るよう顕在化したものであるか否かを問わず、広く記録媒体上に画像、模様、パ

ターン等を形成する、または媒体の加工を行う場合も表すものとする。

【0021】

また、「記録媒体」とは、一般的な記録装置で用いられる紙のみならず、広く、布、プラスチック・フィルム、金属板、ガラス、セラミックス、木材、皮革等、インクを受容可能なものを表すものとする。

【0022】

さらに、「インク」(「液体」と言う場合もある)とは、上記「記録(プリント)」の定義と同様広く解釈されるべきものである。従って、記録媒体上に付与されることによって、画像、模様、パターン等の形成または記録媒体の加工、或いはインクの処理(例えば記録媒体に付与されるインク中の色剤の凝固または不溶化)に供され得る液体を表すものとする。10

【0023】

またさらに、「ノズル」とは、特にことわらない限り吐出口ないしこれに連通する液路およびインク吐出に利用されるエネルギーを発生する素子を総括して言うものとする。

【0024】

以下に用いる記録ヘッド用の素子基板(ヘッド基板)とは、シリコン半導体からなる單なる基体を指し示すものではなく、各素子や配線等が設けられた構成を差し示すものである。

【0025】

さらに、基板上とは、単に素子基板の上を指し示すだけでなく、素子基板の表面、表面近傍の素子基板内部側をも示すものである。また、本発明でいう「作り込み(built-in)」とは、別体の各素子を単に基体表面上に別体として配置することを指し示している言葉ではなく、各素子を半導体回路の製造工程等によって素子板上に一体的に形成、製造することを示すものである。20

【0026】

次に、インクジェット記録装置の実施例について説明する。この記録装置は、ロール状に巻かれた連続シート(記録媒体)を使用し、片面記録及び両面記録の両方に対応した高速ラインプリンタであり。例えば、プリントラボ等における大量枚数のプリント分野に適している。

【0027】

図1は本発明の代表的な実施例であるインクジェット記録装置(以下、記録装置)の内部概略構成を示す側断面図である。装置内部は大きくは、シート供給部1、デカール部2、斜行矯正部3、記録部4、クリーニング部(不図示)、検査部5、カッタ部6、情報記録部7、乾燥部8、シート巻取部9、排出搬送部10、ソータ部11、排出トレイ12、制御部13などに分けられる。シートは、図中の実線で示したシート搬送経路に沿ってローラ対やベルトからなる搬送機構で搬送され、各ユニットで処理がなされる。30

【0028】

シート供給部1はロール状に巻かれた連続シートを収納して供給するユニットである。シート供給部1は、2つのロールR1、R2を収納することが可能であり、逐一的にシートを引き出して供給する構成となっている。なお、収納可能なロールは2つであることには限定はされず、1つ、あるいは3つ以上を収納するものであってもよい。デカール部2は、シート供給部1から供給されたシートのカール(反り)を軽減させるユニットである。デカール部2では、1つの駆動ローラに対して2つのピンチローラを用いて、カールの逆向きの反りを与えるようにシートを湾曲させてしごくことでカールを軽減させる。斜行矯正部3は、デカール部2を通過したシートの斜行(本来の進行方向に対する傾き)を矯正するユニットである。基準となる側のシート端部をガイド部材に押し付けることにより、シートの斜行が矯正される。40

【0029】

記録部4は、搬送されるシートに対して記録ヘッド部14によりシートの上に画像を形成するユニットである。記録部4は、シートを搬送する複数の搬送ローラも備えている。50

記録ヘッド部 14 は、使用が想定されるシートの最大幅をカバーする範囲でインクジェット方式のノズル列が形成されたフルライン記録ヘッド（インクジェット記録ヘッド）を有する。記録ヘッド部 14 は、複数の記録ヘッドがシートの搬送方向に沿って平行に配置されている。この実施例では K（ブラック）、C（シアン）、M（マゼンタ）、Y（イエロー）の 4 色に対応した 4 つの記録ヘッドを有する。記録ヘッドの並び順はシート搬送上流側から、K、C、M、Y となっている。なお、インク色数及び記録ヘッドの数は 4 つには限定はされない。また、インクジェット方式としては、発熱素子を用いた方式、ピエゾ素子を用いた方式、静電素子を用いた方式、MEMS 素子を用いた方式等を採用することができる。各色のインクは、インクタンクからそれぞれインクチューブを介して記録ヘッド部 14 に供給される。

10

#### 【0030】

検査部 5 は、記録部 4 でシートに記録された検査パターンや画像を光学的に読み取って、記録ヘッドのノズルの状態、シート搬送状態、画像位置等を検査するユニットである。検査部 5 は実際に画像を読み取り画像データを生成するスキャナ部と読み取った画像を解析して記録部 4 へ解析結果を返す画像解析部より構成されている。検査部 5 は CCD ラインセンサであり、シート搬送方向と垂直な方向にセンサが並べられている。

#### 【0031】

なお、上述のように図 1 に示した記録装置は、片面記録及び両面記録の両方に対応しているが、図 2 と図 3 とはそれぞれ、図 1 に示す記録装置において片面記録時の動作と両面記録時の動作を説明するための図である。

20

#### 【0032】

図 4 は記録ヘッド部 14 に搭載されるフルライン記録ヘッド 100 と記録媒体 800 の搬送方向の関係を示した図である。

#### 【0033】

記録動作を行う際には、フルライン記録ヘッド 100 は記録装置に固定されており、記録媒体 800 が搬送され、素子基板 101 に設けられた複数の吐出口 706 からインクが吐出され、記録媒体 800 に画像が形成される。

#### 【0034】

この図から分かるように、この例では、フルライン記録ヘッド 100 は 4 つの素子基板 101 を実装して構成されている。

30

#### 【0035】

図 5 はフルライン記録ヘッドの分解斜視図である。

#### 【0036】

フルライン記録ヘッド 100 は 4 つの素子基板 101-1、101-2、101-3、101-4、支持部材 501、プリント配線板 110、インク供給部材 502 等を備えている。図 5 に示すように、フルライン記録ヘッド 100 には 4 つの素子基板が千鳥状に配置されている。なお、搭載する素子基板 101 の数を増やすことでさらに記録幅の長い記録ヘッドを構成することが可能である。また、4 つの素子基板を個別に特定せずに説明する場合には、単に素子基板 101 として言及する。

#### 【0037】

図 5 から分かるように、プリント配線板 110 は基本的には矩形形状、素子基板 101 は矩形形状をしている。そして、素子基板 101 の長手方向に複数の吐出口 706 が配列される。また、素子基板 101 の長手方向。つまり、複数の吐出口の配列方向がプリント配線板 110 の長手方向となるように配置される。

40

#### 【0038】

次に、上記構成の記録装置に搭載するフルライン記録ヘッドに実装される素子基板についていくつかの実施例を説明する。

#### 【実施例 1】

#### 【0039】

この実施例を説明する前提として、次のような HE 信号を考慮する。

50

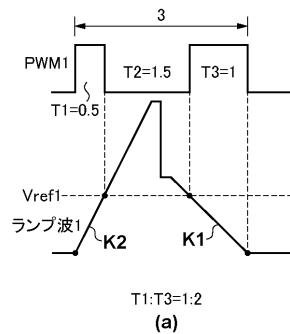

**【0040】**

図20はランプ波と基準電圧( $R_{ef}$ )を比較することで、インクジェット記録ヘッド(以下、記録ヘッド)ではヒータを駆動する期間を決める信号であるヒートイネーブル(HE)信号パルスの変調に適用する。

**【0041】**

図20において、200は時間に比例して(時間の経過とともに)電圧が上昇する波形をもつランプ波、 $R_{ef1} \sim R_{ef3}$ は任意に設定可能な基準電圧( $R_{ef}$ )である。ランプ波200と基準電圧( $R_{ef1} \sim R_{ef3}$ )を比較し、両方の電圧が等しくなったところでパルスが立ち下がるようにしておくと設定した基準電圧によってパルス幅を変えることができる。例えば、基準電圧( $R_{ef1}$ )を設定したときはHE信号のパルス幅はHE1となり、基準電圧( $R_{ef2}$ )のときはHE2、基準電圧( $R_{ef3}$ )のときはHE3のパルス幅となる。このようにランプ波と基準電圧とを比較することによってパルス幅を任意に設定することができる。10

**【0042】**

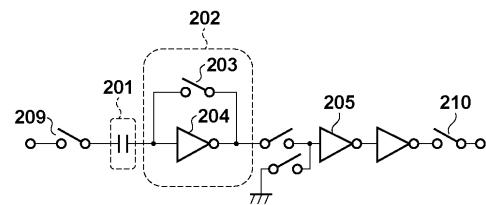

図21は基準電圧とランプ波とを比較するコンパレータの構成を示す図である。

**【0043】**

このコンパレータは、コンデンサから成るメモリ部201と、スイッチ203とインバータ204から成る比較部202と、波形を出力するためのバッファ205とから構成される。このコンパレータは、メモリ部201に基準電圧( $R_{ef}$ )を記憶し、その後、入力されたランプ波と比較する。なお、このコンパレータの入力部と出力部とにはそれぞれスイッチ209、210が設けられる。20

**【0044】**

即ち、図22に示すような、一ヒート周期にプレパルス、インターバル時間、メインパルスを含むダブルパルスのHE信号を用いる。また、図23に示した特許文献3に開示されているPWM1～4のように、プレパルス(T1)とインターバル時間(T2)とメインパルス(T3)とからなるダブルパルスのトータル時間は固定(即ち、 $T_1 + T_2 + T_3$ は一定)であるとする。また、例えば、PWM4ではPWM1～3と比べて、プレパルスの立ち上がりが少し遅れるが、吐出タイミングを揃えるためにメインパルスの立下りは固定である。

**【0045】**

次に、以上のような構成を前提として、ダブルパルスのHE信号を1つの基準電圧で生成する方法を説明する。また、ここでは、素子基板内のばらつき(例えば、温度分布やヒータ抵抗ばらつき、保護膜の膜厚分布等)に応じてヒータ(記録素子)毎にHE信号のパルス幅を制御してダブルパルスを生成する方法について述べる。実際は、DACを用いて階段波を生成するが、ここでは説明を簡単にするために一定の傾きをもつランプ波を用いる。

**【0046】**

図6は、この実施例に従ってダブルパルスのヒートイネーブル(HE)信号を生成する様子を示すタイムチャートである。

**【0047】**

まず、図6(a)はプレパルス幅( $T_1$ )とメインパルス幅( $T_3$ )の比を1:4に設定する場合を示す。基準電圧が $V_{ref1}$ の場合、メインパルスのランプ波の傾きK1を基準とすると、プレパルス幅を作る場合は4倍の傾きK2のランプ波を入力する。パルスの時間の絶対値は、基準電圧 $V_{ref1}$ で決定する。時間傾きK2のランプ波が基準電圧を超えてから、傾きK2のランプ波の立下りのタイミングまでの時間がインターバル時間( $T_2$ )である。この実施例では、傾きK2のランプ波の立下りのタイミングを、メインパルスの開始タイミングに一致させている。メインパルスランプ波が終わり、次のランプ波が入力されるまでコンパレータのスイッチ209をOFFしておけばよい。なお、コンパレータは比較回路とも呼ばれる。40

**【0048】**

10

20

30

40

50

次に、プレパルス幅（T1）とメインパルス幅（T3）の比を1：3に設定する場合を図6（b）に示す。基準電圧をVref1、プレパルスのランプ波の傾きをK2のまま、メインパルスのランプ波の傾きをK1aとする。この傾きK1aは傾きK2の3分の1である。これにより、プレパルス幅（T1）とインターバル時間（T2）を一定にしたまま、メインパルスのパルス幅を短くすることができる。

#### 【0049】

次に、プレパルス幅（T1）とメインパルス幅（T3）の比は1：4のままプレパルス幅（T1）とメインパルス幅（T3）の絶対値を大きくする場合を図6（c）に示す。この場合には、基準電圧をVref1より高い電圧であるVref2に設定する。メインパルスのランプ波の傾きはK1、プレパルス幅のランプ波の傾きはK2とする。

10

#### 【0050】

このように、設定した1つの基準電圧（Vref）に対してランプ波の傾きを変えること、ランプ波の傾きを変えずに基準電圧（Vref）を変えることで任意のダブルパルスを生成することができる。なお、補足すると、プレパルスのランプ波は、後述する基準電圧の入力に続いて行われる。

#### 【0051】

ここで、ヒータ毎に個別にパルス幅を調整する方法について説明する。

#### 【0052】

図7は記録ヘッドの素子基板のレイアウトを模式的に示す図である。

#### 【0053】

20

図7に示す例では、素子基板101には2つのインク供給口601が形成され、各インク供給口に対応した回路ブロックには、そのインク供給口を挟んで対向する位置にヒータ602を列状に配置している。さらに、このヒータ列のヒータを選択駆動する駆動回路605がヒータ602に対応して配置されている。また、これらのヒータや駆動回路への電源供給や信号印加を行うパッド604が素子基板101の上下端部に配置されている。

#### 【0054】

また、素子基板101の上辺に沿ったパッド604とインク供給口601、ヒータ列との間には、駆動回路603が配置される。さらに、ヒータ602の背後に設けられた駆動回路605の近傍にはコンパレータ609が配置される。

#### 【0055】

30

一方、素子基板101の下辺に沿ったパッドと、インク供給口601、ヒータ列との間には、OPアンプ606、DAC（デジタル／アナログ変換器）607が配置される。このような回路レイアウト構成をとることで、ヒータ毎に個別にHE信号のパルス幅を設定できるようになり、ヒータ毎に適正なエネルギーを与えることが可能である。

#### 【0056】

図8は図7に示す回路レイアウトの一部の回路構成の詳細と信号の流れを模式的に示す図である。

#### 【0057】

パッド604に印加されるデータ信号（DATA\_A\_1）はクロック信号（CLK）、ラッチ信号（LT）、記録データ信号（DATA）などを含んでおり、入力回路702を介して内部回路を構成するシフトレジスタ703やデコーダ704へと入力される。ここで、記録データ信号（DATA）はあるヒート期間で駆動するヒータを選択する信号である。

40

#### 【0058】

また、データ信号として、各回路ブロックによって異なるパッドより別の信号が入力される。入力されたデータ信号はシフトレジスタ703で展開され、その一部は記録データ信号（DATA）として複数配置されたヒータ駆動グループ707へと入力され、ヒータ駆動グループの有効・無効を選択する。また、展開されたデータ信号の別の一部は、デコーダ704へと入力される。デコーダ704は、ヒータ駆動グループ内で駆動するヒータを順次切替える時分割信号（BLKn）706を出力する。ここで、1グループ内に含ま

50

れるヒータの個数を  $2^n$  個とすると、 $2^n$  個の時分割信号が必要となる。

#### 【0059】

ここで、1つのヒータ駆動グループにはヒータ列の中で近接して連続して素子基板上に設けられる  $2^n$  個のヒータが含まれる。この  $2^n$  個が時分割駆動される。そして、このグループ単位にコンパレータ（比較回路）が1つずつ備えられる。

#### 【0060】

さらに、データ信号のさらに別の一部である HE データ（H E N B）が D A C 用シフトレジスタ 708、D A C 607、O P アンプ 606 を経て、コンパレータ（C O M P）711 へと供給される。そして、コンパレータ 609 でヒートイネーブル（H E n）信号が生成される。図 8 の例では 8 つの H E 信号（H E 1 ~ 8）が生成される。

10

#### 【0061】

D A C 607 はディジタルデータで設定したアナログ電圧値を生成できる回路（生成回路）である。この実施例では任意の電圧値を生成できることを利用して、D A C 607 を基準電圧（R e f）とランプ波の生成に用いている。シフトレジスタ 708 はデータ信号に含まれる H E パルス幅を決める H E データ（H E N B）をシフトレジスタ 703 から受信し、D A C 607 へ転送する。D A C 607 には O P アンプ 606 を介して複数グループのコンパレータ（C o m p）609 が接続される。

#### 【0062】

コンパレータ（C o m p）609 は D A C 607 の負荷として作用するため、直接接続すると応答速度が遅くなり出力波形が鈍ってしまう。一方、O P アンプ 606 は負帰還をかけると入力と出力を等しくしようと動作する。これをを利用して D A C 607 とコンパレータ 609 との間に O P アンプ 606 を挿入する。これにより、D A C 607 の負荷は O P アンプ 606 だけとなり、D A C 607 の出力と同様な波形をコンパレータ 609 へ出力することができる。この様にして、基準電圧とランプ波を D A C 607 で生成し、コンパレータ 609 へ転送する。

20

#### 【0063】

図 9 はコンパレータ 609 の動作を説明する図である。

#### 【0064】

図 9 に示すコンパレータ 609 の回路構成は、図 21 で説明したものと同じなので、ここでは同じ参照番号を付して、その説明は省略する。図 9 (a) はスイッチ 203 が閉じている状態を示し、図 9 (b) はスイッチ 203 が開いている状態を示す。次に、コンパレータ 609 の動作を図 9 (c) を参照して説明する。図 9 (c) にはコンパレータ 609 の入力電圧 V i n、インバータ 204 の入力電圧 V a、コンパレータ 609 の出力電圧 V o u t の電圧の時間変化が示されている。

30

#### 【0065】

まず、期間 t1 において、スイッチ 203 とスイッチ 209 を閉じる。スイッチ 203 を閉じることによって、インバータ 204 の入力と出力が短絡され、コンデンサ 201 のインバータ 204 側の電極の電位 V a が V t h となる。V t h は、インバータ 204 の閾値電圧である。スイッチ 209 を閉じることで、コンデンサ 201 のスイッチ 209 側の電極の電位が V r e f となる。これにより、コンデンサ 201 には V t h - V r e f に相当する電荷が充電される（別の表現をするとコンデンサ 201 には V t h - V r e f の電位差がかかる）。

40

#### 【0066】

次に、期間 t2 において、スイッチ 203 を開く。メモリ部 201 のコンデンサの両端には V t h - V r e f の電位差が維持される。スイッチ 209 を閉じて（図 9 (b)）、V i n としてランプ波 V r a m p（図 9 (c)）を入力する。ランプ波 V r a m p の入力によって、 $V a = V r e f - V t h + V r a m p$  となる。ここで、入力されるランプ波 V r a m p の電位は、当初 V r e f の電位より低く設定されているので、V a はインバータ 204 の閾値電圧 V t h より低くなる。このため、インバータ 204 は H レベルを出力する。これにより、V o u t が立ち上がる。ランプ波 V r a m p の電位は、時間の経過とともに

50

に徐々に高くなっていくが、ランプ波 V r a m p の電位は V r e f の電位より低い間は、インバータ 204 は H レベルを出力する。そして、ランプ波 V r a m p の電位が V r e f の電位を超えたとき、V a の電位が V t h より高くなり、インバータ 204 は L レベルを出力する。これにより、V o u t が立ち下がる。以上のようにして、図 9 (c) に示すように、V o u t からパルスが出力される。

#### 【0067】

以上のように、コンパレータでは、メモリ部にチャージした基準電圧 V r e f とランプ波でパルス幅を調整する。このように、この実施例のコンパレータはメモリ部にコンデンサを備え、比較部にインバータを備える構成であるので、回路規模が小さく基板面積を抑制するために有利である。

10

#### 【0068】

次に、D A C 6 0 7 について説明する。

#### 【0069】

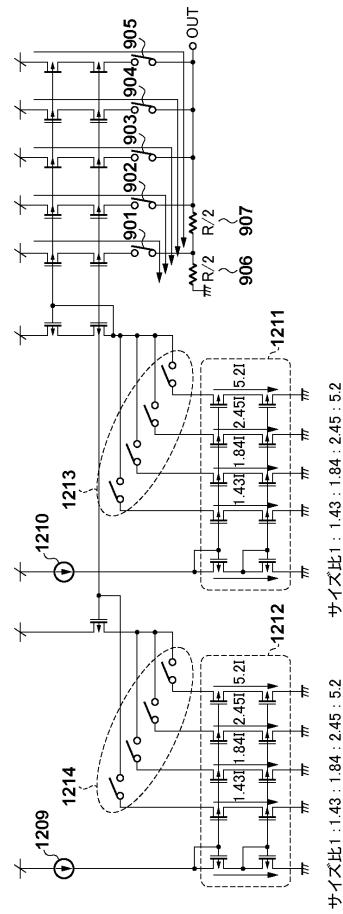

図 10 はランプ波と基準電圧 (V r e f) を生成する D A C 6 0 7 の構成を示す回路図である。図 10 は 4 ビット D A C の構成例を示しており、901 ~ 905 は各ビットを O N / O F F するスイッチで、906、907 は電圧に変換する抵抗である。

#### 【0070】

D A C 6 0 7 は複数のカレントミラー回路を並列に接続した構成を用い、各カレントミラー回路の出力部に設けられたスイッチ 901 ~ 905 を制御し、抵抗に流れる電流を調整することで任意の電圧を生成する。この構成では、スイッチ 902 ~ 905 からの出力が 4 ビットの各ビットに対応している。

20

#### 【0071】

さて、スイッチ 902 を O N すると電流 I が流れるため出力端子 O U T からは、 $(R/2 + R/2) \times I = RI$  の電圧が出力される。さらに、スイッチ 903 を O N すると  $2 \times RI$ 、スイッチ 904 を O N すると  $3 \times RI$ 、スイッチ 905 を O N すると  $4 \times RI$  が出力される。このようにスイッチを O N / O F F することで任意の電圧を生成することができる。

#### 【0072】

さて、この実施例では、基準電圧 (V r e f) とランプ波を共通の D A C で生成するので、1 つの D A C でランプ波と半階調ずらした基準電圧 (V r e f) を生成できるようにしたい。このような理由から、D A C 6 0 7 は、抵抗 R を抵抗 906 と 907 のように R / 2 ずつにわけ、その間にスイッチ 901 で制御される電流が流れるような構成となっている。従って、D A C を共通化しない場合はこのような構成を取る必要はない。また、M O S のサイズ比で電流の重みづけをする等、他の構成を取ることもできる。

30

#### 【0073】

図 11 はヒータ駆動グループ 707 の内部構成を示す回路図である。

#### 【0074】

なお、図 8 から分かるように、図 11 に示すのと同様のヒータ駆動グループが複数、素子基板 101 には実装される。

#### 【0075】

ヒータ駆動グループ 707 は、アレイ状に配置されたヒータ 602 に対応して配置される、駆動素子 1004、電圧変換回路 (L V C) 1005、ヒータ選択回路 1006 からなる。ヒータ電源配線 1001 は外部から供給されるヒータ電源電圧 (V H : 第 1 電源電圧) が印加されており、ヒータ 602 を通ってグランド (G N D H) 1002 へ電流が流れれる。

40

#### 【0076】

ここで、駆動素子 1004 はヒータ 602 に通電するかどうかの決めるスイッチ素子としての機能を果たす。記録データ信号線 1007、時分割信号 1008、ヒートイネーブル信号線 1009 からの信号はヒータ選択回路 1006 である A N D ゲートへと入力され、これら 3 つの信号が共にアクティブとなった場合にその A N D ゲートの出力がアクティ

50

ブとなる。このANDゲートの出力信号は、電圧変換回路1005によりその信号の電圧振幅を、入力回路702からヒータ選択回路1006までの駆動電圧(VDD第3電源電圧)よりも高い電源電圧(VHM:第2電源電圧)にレベル変換(昇圧)される。レベル変換された信号は、駆動素子1004のゲートに印加され、ゲート電圧が印加されたMOSトランジスタに接続されたヒータ602は通電、駆動されることとなる。

#### 【0077】

このようなヒータ毎に個別制御する構成で、図6に示した基準電圧(Vref)とランプ波を入力し、ダブルパルスを生成する。

#### 【0078】

まず、図8に示す例では、8つのヒータ駆動グループ707の基準電圧(Vref)をDAC607で生成し、スイッチを切り換えるながらコンパレータ609のメモリに順次記憶していく。全てのグループのコンパレータに基準電圧(Vref)を記憶させた後、全グループ同時にランプ波を入力する。同時入力することで同じタイミングでコンパレータ609によってランプ波と基準電圧(Vref)とが比較され、各グループに設定された基準電圧(Vref)に応じたHE信号パルスが生成される。10

#### 【0079】

この実施例ではダブルパルスを生成するので、図6に示すように2回のランプ波が入力される度にダブルパルスが生成される。

#### 【0080】

次に、ランプ波の傾きを変化させる3種類の方法について説明する。20

#### 【0081】

(1) 第1の方法(DACの抵抗を切り替える方法)

図12は抵抗を切り替える構成を備えたDAC607の回路図である。

#### 【0082】

電流をカレントミラー回路により生成する構成は図10と同じであるので、図12においても、図10で説明したのと同じ構成要素には同じ参照番号を付し、その説明は省略する。この構成では、図10に示した抵抗906、907の抵抗値をスイッチ1116～1125のON/OFFで選択できるようになっている。出力端子OUTには電流I×抵抗値の電圧が出力される。

#### 【0083】

従って、この抵抗値を切り換えることによってランプ波の傾きを変えることができる。例えば、スイッチ1116と1117をONしたときスイッチ902～905を順番にONしていくと3R×I、3R×2I、3R×3I、3R×4Iの電圧が順次出力されランプ波が生成される。次に、スイッチ1118と1119をONすると、2.1R×I、2.1R×2I、2.1R×3I、2.1R×4Iの電圧が順次出力されランプ波全体の電圧が圧縮される。クロック信号(CLK)に応じてスイッチ902～905がONされたため昇圧する時間は変わらないので、ランプ波の傾きが変わることになる。このように抵抗を切り替えることによってランプ波の傾きを変えることが可能となり、図12に示した抵抗比とすることによって図23に示した駆動パルスPWM1～4を生成することができる。30

#### 【0084】

(2) 第2の方法(DACのミラー比を切り替える方法)

図13はカレントミラー比を切り替える構成を備えたDAC607の回路図である。

#### 【0085】

電流をカレントミラー回路により生成する構成は図10と同じであるので、図13においても、図10で説明したのと同じ構成要素には同じ参照番号を付し、その説明は省略する。この構成では、電流源1209、1210の部分を1211、1212のようにカレントミラー構成とし、各MOSにサイズ比をつけスイッチ1213、1214で選択することでスイッチ902～905に流れる電流値を変更可能にしている。

#### 【0086】

50

20

30

40

50

出力端子OUTからは $R \times$ 電流値の電圧が出力されるので、例えば、カレントミラー部1211、カレントミラー部1212のサイズ比3のMOSFETがONしている場合、3Iの電流がミラーされる。この場合、スイッチ902～905にも3Iの電流が流れるので、出力端子OUTからは $R \times 3I \sim R \times 12I$ の電圧が出力される。これと比較し、サイズ比2.1のMOSFETを選択した場合、出力端子OUTからは $R \times 2.1I \sim R \times 8.4I$ の電圧が出力されランプ波全体の電圧が圧縮される。クロック信号(CLK)に応じてスイッチ902～905がONされるため昇圧する時間は変わらないので、ランプ波の傾きが変わることになる。また、図13のようなサイズ比とすることによって図23に示した駆動パルスPWM1～4を生成することができる。

## 【0087】

10

(3) 第3の方法(コンパレータの容量を切り替える方法)

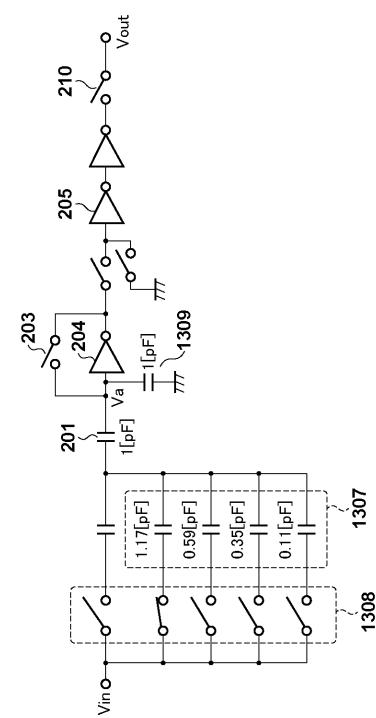

図14は容量を切り替える構成を備えたコンパレータ609の回路図である。

## 【0088】

なお、コンパレータの基本的な構成は図21に示したコンパレータと同じであるので、図14においても、図21で説明したのと同じ構成要素には同じ参照番号を付し、その説明は省略する。この構成では、Vinに入力された基準電圧(Vref)をメモリ(第1のコンデンサ)201にスイッチ203がONしている状態で記憶する。その後、スイッチ203をOFFに切り換えてランプ波を入力するとVramp = 基準電圧(Vref)となったところでインバータ204の出力が反転する。

## 【0089】

20

これに加え、この実施例では電圧可変用のメモリ1307、即ち、新たなコンデンサをメモリ部201として機能するコンデンサに直列となるように挿入する。また、説明のためにGND接地容量1309を挿入する。このようにすると、インバータ204の入力電圧Vaは、入力されたVinを電圧可変用メモリ1307とメモリ部201、GND接地容量1309で分圧した値となる。

## 【0090】

例えば、図14に示すようにメモリ部201とGND接地容量1309が1pFであり、図23に示す駆動パルスPWM1～4を生成する場合、電圧可変用メモリ1307を1.17pF、0.59pF、0.35pF、0.11pFに順次切り替えればよい。Vin = 1[V]とすると、電圧可変用メモリ1307が挿入されていないスイッチを選択すると、Va = 0.5[V]となる。これに対して、電圧可変用メモリ1307の容量が1.17pFのコンセンサを選択すると、Va = 0.35[V]となり電圧Vaが圧縮される。従って、Vinにランプ波が入力されるとVaでランプ波の傾きが変化する。

30

## 【0091】

このように、容量値が互いに異なるコンデンサ(第2のコンデンサ)を複数用いて電圧可変用メモリを構成し、スイッチ1308で選択することでランプ波の傾きを選択することができる。この容量を挿入する方法では直列にメモリ部201に直列に挿入するので合成容量が下がりランプ波の傾きが小さくなる。従って、この容量で調整する方法は傾きを小さくなる方向の調整となるため、ここでは、プレパルス幅(T1)を基準とし、メインパルスのランプ波の傾きを変更する場合を想定した容量比を説明した。

40

## 【0092】

従って以上説明した実施例に従えば、1つの基準電圧(Vref)から複数のパルス幅をもつパルスを生成することができる。この結果、複数のパルスを生成するのに多くのデータを用いる必要がない。そのため、データ転送速度を上げたり、データを分割して転送する等の対策も不要となる。また、メモリを増やす必要もないため回路規模の増大も防ぐことができる。

## 【実施例2】

## 【0093】

ここでは実施例1で示したのとは異なるランプ波を用いてダブルパルスを生成する例について説明する。

50

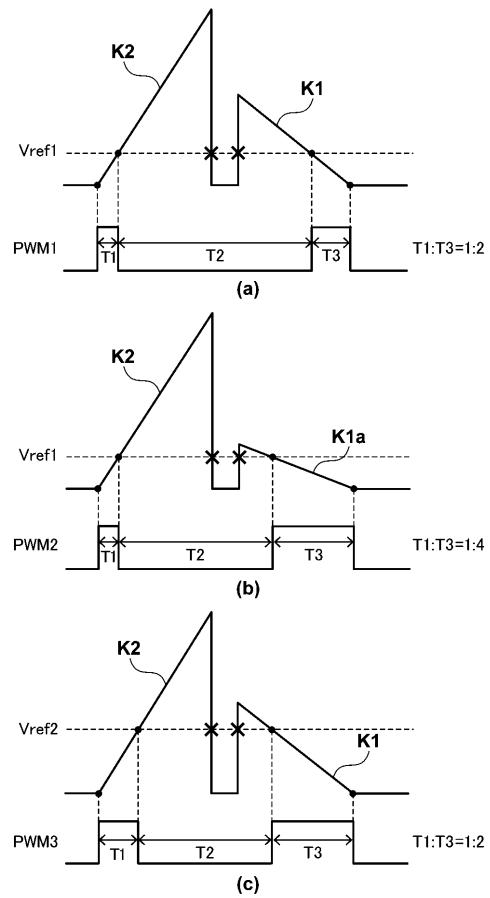

**【0094】**

図15は、この実施例に従ってダブルパルスのヒートイネーブル(HE)信号を生成する様子を示すタイムチャートである。プレパルス用のランプ波は、時間の経過とともに電圧の値が一定の割合で高くなり、メインパルス用のランプ波は、時間の経過とともに電圧の値が一定の割合で低くなる。図15と図6とを比較すると分かるように、この実施例では、メインパルス用ランプ波の波形がプレパルス用のランプ波のそれに対して反転している。

**【0095】**

まず、図15(a)はプレパルス幅(T1)とメインパルス幅(T3)の比を1:2に設定する場合を示す。基準電圧がVref1の場合において、メインパルスのランプ波の傾きK1を基準とすると、プレパルス幅を作る場合は2倍の傾きK2のランプ波を入力する。パルスの時間の絶対値は、基準電圧Vref1で決定する。傾きK2のランプ波が基準電圧を超えてから、傾きK1のランプ波が基準電圧を下回るまでの時間が、インターバル時間(T2)である。補足すると、プレパルスのランプ波の開始からメインパルスのランプ波の終了までの時間が、プレパルスの開始からメインパルスの終了までの時間を決定する。

10

**【0096】**

次に、図15(b)はプレパルス幅(T1)とメインパルス幅(T3)の比を1:4に設定する場合を示す。基準電圧をVref1、プレパルスのランプ波の傾きをK2のまま、メインパルスのランプ波の傾きをK1aとする。この傾きK1aは傾きK2の4分の1である。これにより、プレパルスの開始からメインパルスの終了までの時間を一定にしたまま、メインパルスのパルス幅を長くすることができる。

20

**【0097】**

さらに、図15(c)はプレパルス幅(T1)とメインパルス幅(T3)の比は1:2のままプレパルス幅(T1)とメインパルス幅(T3)の絶対値を大きくする場合を示す。この場合には、基準電圧をVref1より高い電圧であるVref2に設定する。メインパルスのランプ波の傾きはK1、プレパルス幅のランプ波の傾きはK2とする。

**【0098】**

このように、メインパルスを反転させると、その開始時間と終了時間をダブルパルスのトータル時間と合わせて固定することができるので、トータル時間が固定の場合、パルス幅に合わせてランプ波の傾きを変えるだけでよく制御が簡単になる。

30

**【0099】**

しかし、プレパルス用ランプ波が終了して立ち下がるときと、メインパルス用ランプ波の開始時に立ち上がるときにその電圧が基準電圧(Vref)を横切るためコンパレータからパルスが出力してしまう。従って、このときコンパレータのスイッチ210をOFFしておく必要がある。なお、補足すると、実施例1と同様にプレパルスのランプ波は、図9で説明したように基準電圧の入力に続いて行われる。

**【実施例3】****【0100】**

この実施例では実施例1、2で用いた波形パターン以外のランプ波を用いる例について説明する。

40

**【0101】**

図16はこの実施例に従ってダブルパルスのヒートイネーブル(HE)信号を生成する様子を示すタイムチャートである。

**【0102】**

この例は、プレパルス用ランプ波の波形に対してメインパルス用ランプ波の波形が反転し、プレパルス用ランプ波とメインパルス用ランプ波との間でランプ波を立ち下げない形のランプ波を用いる例である。図16(a)は基準電圧としてVref1を用いた例を示し、図16(b)はVref2を用いた例を示す。

**【0103】**

50

このランプ波は実施例2と同様にランプ波の開始時間と終了時間をダブルパルスのトータル時間と合わせて固定することができる、基準電圧( $V_{ref}$ )を変更するだけでプレパルス幅、インターバル時間、メインパルス幅を変更することができる。

#### 【0104】

例えば、図16(a)に示した基準電圧( $V_{ref1}$ )を図16(b)に示した基準電圧( $V_{ref2}$ )に変更すると実施例2と同様に $T_1 : T_3$ の比は一定で、 $T_1$ 、 $T_2$ 、 $T_3$ が基準電圧( $V_{ref}$ )に応じて変化する。これに加えて、この実施例に従うランプ波はプレパルス用ランプ波の終了後立ち下げるため基準電圧( $V_{ref}$ )を横切ることがない。従って、実施例2のようにコンパレータのスイッチをOFFする必要がなくなり制御がさらに簡単になる。また、プレパルス用ランプ波の終了からメインパルス用ランプ波の開始までにランプ波の傾きを切り替えるが、その切り替えタイミングは間に入っているればどこでもよく、図16ではダブルパルスの真ん中で切り替える例を示している。10

#### 【0105】

次に、図16に示したランプ波を用いて図23に示す駆動パルスPWM1～4を生成する方法について説明する。

#### 【0106】

図17はこの実施例に従った駆動パルスPWM1～4の生成の様子を示す図である。

#### 【0107】

図17(a)はメインパルス幅を基準にして駆動パルスを生成する様子を示し、図17(b)はプレパルス幅を基準にして駆動パルスを生成する様子を示している。20

#### 【0108】

図17(a)の例では、メインパルス幅( $T_3$ )を基準にして、メインパルス用ランプ波の傾きを基準に基準電圧 $V_{ref1} \sim V_{ref4}$ を決める。次に、プレパルス用ランプ波の傾きを基準電圧( $V_{ref}$ )とPWM1～4のプレパルス幅( $T_1$ )に応じて変化させると、ランプ波の電圧波形はramp1～ramp4のようになる。

#### 【0109】

また、図17(b)に示すように、プレパルス幅( $T_1$ )を基準にメインパルスのランプ波の傾きを変化させることもできる。また、プレパルス用ランプ波、メインパルス用ランプ波両方の傾きを変化させてもよい。なお、補足すると、実施例1、実施例2と同様に、プレパルスのランプ波は、図9で説明したように基準電圧の入力に続いて行われる。30

#### 【0110】

図18はプレパルスを基準としてメインパルス用ランプ波の傾きを変化させて異なる駆動パルスPWM1～4を求める場合に3つの異なる方法を用いる際に必要な値をまとめた表を示す図である。

#### 【0111】

図18では、(1)DACの抵抗比で変える方法、(2)DACのミラー比で変える方法、(3)コンパレータの容量比で変える方法のそれぞれの場合の比を示している。図18に示す比とすることで図23に示すPWM1～4を生成することができる。

#### 【0112】

図19は素子基板においてヒータ列方向に膜厚、抵抗等のばらつきがあったときに適用される駆動パルスの変更を示す図である。図19において、左側に示す回路レイアウトは図7に示すものと同じである。40

#### 【0113】

素子基板が図中央に示すように、ヒータ602の配列方向に膜厚、抵抗等に関し、ばらつき102がある場合、図右側に示すように、例えば、傾き1801をもつランプ波をヒータ列で共通で入力し、基準電圧 $V_{ref1} \sim 4$ をヒータ駆動グループ毎に設定する。このようにすることで、PWM1～PWM4のような駆動パルスが生成される。

#### 【0114】

従って以上説明した実施例に従えば、1つの基準電圧を設定し、ランプ波の傾きを切り替えるだけで、複数のパルス幅のパルスを生成することができる。また、ランプ波が基準

電圧を横切らないのでコンパレータのスイッチを切り替える制御が必要なくなり、より制御が簡単になるという利点がある。

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

Graph showing the relationship between the reference voltage  $V_{ref2}$  and the PWM signal  $PWM2$ . The graph illustrates the generation of a trapezoidal wave (ランプ波2) from a rectangular reference signal. Key points marked are  $K_2$  (at  $T_1=0.25$ ),  $V_{ref2}$ ,  $K_1$  (at  $T_3=0.5$ ), and a time interval of 3. The ratio  $T_1:T_3=1:2$  is indicated at the bottom.

【図17】

The diagram illustrates the generation of four PWM signals (PWM1, PWM2, PWM3, PWM4) from four reference signals (ref1, ref2, ref3, ref4) and four ramps (ramp1, ramp2, ramp3, ramp4). The reference signals are step functions that switch between high and low levels. The ramps are linear functions that transition between the high and low levels of the reference signals. The PWM signals are generated by comparing the reference signals with the ramps. When a ramp crosses a reference signal, it triggers a pulse. The width of each pulse is determined by the time interval between the crossing points of the ramp and the reference signal. The period of each PWM signal is determined by the time interval between consecutive crossings of the same reference signal by the ramp.

【 図 1 8 】

|      | 抵抗比 | ミラー比 | 容量比  |

|------|-----|------|------|

| Vref | 3   | 3    | なし   |

| PWM1 | 2.1 | 2.1  | 1.17 |

| PWM2 | 1.6 | 1.6  | 0.57 |

| PWM3 | 1.2 | 1.2  | 0.33 |

| PWM4 | 0.9 | 0.9  | 0.21 |

【図19】

【図20】

【図22】

【図21】

【図23】

| 環境温度 (envT)    | 駆動パルス | プレパルス [μs] | インターパル [μs] | メインパルス [μs] |

|----------------|-------|------------|-------------|-------------|

| envT<18°C      | PWM1  | 0.60       | 1.82        | 0.86        |

| 18°C≤envT<23°C | PWM2  | 0.50       | 1.86        | 0.92        |

| 23°C≤envT<28°C | PWM3  | 0.40       | 1.90        | 0.98        |

| 28°C≤envT      | PWM4  | 0.20       | 1.94        | 1.04        |

---

フロントページの続き

(72)発明者 工藤 智子

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 葛 西 亮

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 平山 信之

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 島 崎 純一

(56)参考文献 特開平07-101060(JP,A)

特開2007-022069(JP,A)

特開2003-054015(JP,A)

(58)調査した分野(Int.Cl., DB名)

B 41 J 2 / 01 - 2 / 215