(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5419354号

(P5419354)

(45) 発行日 平成26年2月19日(2014.2.19)

(24) 登録日 平成25年11月29日(2013.11.29)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| H01L 21/31   | (2006.01) |

| C23C 16/40   | (2006.01) |

| H01L 21/316  | (2006.01) |

| H01L 29/786  | (2006.01) |

| H01L 21/336  | (2006.01) |

|        |        |               |

|--------|--------|---------------|

| HO 1 L | 21/31  | E             |

| C 23 C | 16/40  | C             |

| H01L   | 21/316 | C 23 C 16/40  |

| H01L   | 21/316 | H01L 21/316 A |

| H01L   | 21/336 | H01L 21/316 X |

請求項の数 12 (全 23 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2007-541414 (P2007-541414)  |

| (86) (22) 出願日 | 平成17年11月15日 (2005.11.15)      |

| (65) 公表番号     | 特表2008-521218 (P2008-521218A) |

| (43) 公表日      | 平成20年6月19日 (2008.6.19)        |

| (86) 国際出願番号   | PCT/US2005/041231             |

| (87) 国際公開番号   | W02006/073568                 |

| (87) 国際公開日    | 平成18年7月13日 (2006.7.13)        |

| 審査請求日         | 平成20年11月14日 (2008.11.14)      |

| 審判番号          | 不服2012-12941 (P2012-12941/J1) |

| 審判請求日         | 平成24年7月6日 (2012.7.6)          |

| (31) 優先権主張番号  | 10/990,185                    |

| (32) 優先日      | 平成16年11月16日 (2004.11.16)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390040660<br>アプライド マテリアルズ インコーポレイテッド<br>A P P L I E D M A T E R I A L S, I<br>N C O R P O R A T E D<br>アメリカ合衆国 カリフォルニア州 95<br>054 サンタ クララ バウアーズ ア<br>ベニュー 3050 |

| (74) 代理人  | 100101502<br>弁理士 安齋 嘉章                                                                                                                                         |

| (72) 発明者  | ホワイト ジョン<br>アメリカ合衆国 カリフォルニア州 94<br>541 ヘイワード コロニー ビュー<br>プレイス 2811                                                                                             |

最終頁に続く

(54) 【発明の名称】低温ポリシリコンTFTのための多層高品質ゲート誘電体

## (57) 【特許請求の範囲】

## 【請求項 1】

プラズマ処理領域を形成する上部、底部及び1つ以上のチャンバ側壁部と、

RFエネルギーをプラズマ処理領域に伝達するために位置されたチャンバ側壁部内に配置されたRF伝達デバイスと、

プラズマ処理領域と連通した酸化ガス供給源と、

複数のガス流路が貫通して形成され、酸化ガス供給源から供給された処理ガスを複数のガス流路を通過してプラズマ処理領域に流す、前記上部に位置されたガス分布プレートと

、

プラズマ処理領域に取り付けられ、垂直方向の間隔を空けた第1及び第2プラズマ処理位置で基板を支持するよう用いられる基板支持部材と、

第1プラズマ処理位置はRF伝達デバイスの上方でガス分布プレートに近接してHDP

O処理を行うために画定され、第2プラズマ処理位置はRF伝達デバイスの下方でガス分布プレートから離れてPECVD処理を行うために画定されるように基板支持部材を垂直

方向に移動可能な昇降アセンブリと、

RF伝達デバイスに連結されたRF電源を含む、基板をプラズマ処理するためのチャンバ。

## 【請求項 2】

RF伝達デバイスが誘導結合RFエネルギー伝達デバイスである請求項1記載のチャンバ。

10

20

**【請求項 3】**

R F 伝達デバイスが容量結合 R F エネルギー伝達デバイスであり、プラズマ処理領域と接觸している接地表面の表面積とプラズマ処理領域と接觸している R F 伝達デバイスの表面積との比が 1 : 1 ~ 2 : 1 である請求項 1 記載の チャンバ。

**【請求項 4】**

R F 電源と 酸化ガス供給源に接続された制御装置を更に備え、制御装置は R F 伝達デバイスに供給される R F エネルギーと、酸化ガス供給源からプラズマ処理領域に供給されるガスを制御するよう用いられる請求項 1 記載の チャンバ。

**【請求項 5】**

10

プラズマ処理領域を形成する上部、底部及び 1 つ以上のチャンバ側壁部と、

プラズマ処理領域に取り付けられ、垂直方向の間隔を空けた少なくとも第 1 及び第 2 プラズマ処理位置で基板を支持するよう用いられる基板支持部材と、

R F エネルギーをプラズマ処理領域内の第 1 プラズマ処理位置に伝達するために位置された第 1 R F 伝達デバイスと、

第 1 R F 伝達デバイスに連結された第 1 R F 電源と、

プラズマ処理領域内の第 2 プラズマ処理位置に R F エネルギーを伝達するために位置されたチャンバ側壁部内に配置された第 2 R F 伝達デバイスと、

第 2 R F 伝達デバイスに連結された第 2 R F 電源と、

プラズマ処理領域と連通した酸化ガス供給源と、

複数のガス流路が貫通して形成され、酸化ガス供給源から供給された処理ガスを複数のガス流路を通過してプラズマ処理領域に流す、前記上部に位置されたガス分布プレートと、

20

第 1 プラズマ処理位置は第 1 R F 伝達デバイスの上方でガス分布プレートに近接して H D P O 処理を行うために画定され、第 2 プラズマ処理位置は第 1 R F 伝達デバイスの下方でガス分布プレートから離れて P E C V D 処理を行うために画定されるように基板支持部材を垂直方向に移動可能な昇降アセンブリと、

第 1 R F 電源、第 2 R F 電源、酸化ガス供給源に連結され、第 1 R F 伝達デバイスに供給される R F エネルギー、第 2 R F 伝達デバイスに供給される R F エネルギー、酸化ガス供給源からプラズマ処理領域に供給されるガスを制御するよう用いられる制御装置を備えた、基板をプラズマ処理するためのチャンバ。

**【請求項 6】**

プラズマ処理領域内の第 3 プラズマ処理位置に R F エネルギーを伝達するために位置された第 3 R F 伝達デバイスと、

第 3 R F 伝達デバイスに連結された第 3 R F 電源を更に備え、

該制御装置が第 1 R F 電源、第 2 R F 電源、第 3 R F 電源、酸化ガス供給源に連結されており、制御装置は第 1 R F 伝達デバイスに供給される R F エネルギー、第 2 R F 伝達デバイスに供給される R F エネルギー、第 3 R F 伝達デバイスに供給される R F エネルギー、酸化ガス供給源からプラズマ処理領域に供給されるガスを制御するよう用いられる請求項 5 記載の チャンバ。

**【請求項 7】**

40

第 1 R F 伝達デバイスが R F コイルであり、第 2 R F 伝達デバイスがガス分布プレートであり、第 3 R F 伝達デバイスが基板支持体である請求項 6 記載の チャンバ。

**【請求項 8】**

プラズマ処理領域を形成する上部、底部及び 1 つ以上のチャンバ側壁部と、

R F エネルギーをプラズマ処理領域に伝達するために位置された R F コイルと、

プラズマ処理領域と連通した酸化ガス供給源と、

複数のガス流路が貫通して形成され、酸化ガス供給源から供給された処理ガスを複数のガス流路を通過してプラズマ処理領域に流し、R F エネルギーをプラズマ処理領域に伝達するように、前記上部に位置されたガス分布プレートと、

プラズマ処理領域に取り付けられ、垂直方向の間隔を空けた第 1 及び第 2 プラズマ処理

位置で基板を支持するよう用いられる基板支持部材と、

第1プラズマ処理位置はRFコイルの上方でガス分布プレートに近接してHDP0処理を行うために画定され、第2プラズマ処理位置はRFコイルの下方でガス分布プレートから離れてPECVD処理を行うために画定されるように基板支持部材を垂直方向に移動可能な昇降アセンブリと、

RFコイルに連結された第1RF電源と、

ガス分布プレートに連結された第2RF電源を含む、基板をプラズマ処理するためのチャンバ。

#### 【請求項9】

RFコイルが単巻コイルである請求項8記載のチャンバ。

10

#### 【請求項10】

RFコイルに隣接しており、プラズマ処理領域で発生したプラズマからRFコイルを遮断可能なカバーを更に含む請求項8記載のチャンバ。

#### 【請求項11】

プラズマ処理領域を形成する上部、底部及び1つ以上のチャンバ側壁部と、

RFエネルギーをプラズマ処理領域に伝達するために位置されたRFコイルと、

RF電源と、

プラズマ処理領域と連通した酸化ガス供給源と、

複数のガス流路が貫通して形成され、酸化ガス供給源から供給された処理ガスを複数のガス流路を通過してプラズマ処理領域に流し、前記上部に取り付けられ、接地されたガス分布プレートと、

プラズマ処理領域に取り付けられ、垂直方向の間隔を空けた第1及び第2プラズマ処理位置で基板を支持するよう用いられ、RF電源からRFコイル及びプラズマ処理領域へとRFエネルギーを伝達するために位置された基板支持部材と、

第1プラズマ処理位置はRFコイルの上方でガス分布プレートに近接してHDP0処理を行うために画定され、第2プラズマ処理位置はRFコイルの下方でガス分布プレートから離れてPECVD処理を行うために画定されるように基板支持部材を垂直方向に移動可能な昇降アセンブリを含む、基板をプラズマ処理するためのチャンバ。

#### 【請求項12】

プラズマ処理領域と接触している接地表面の表面積と基板支持体の表面積との比が1：1～2：1である請求項11記載のチャンバ。

30

#### 【発明の詳細な説明】

##### 【発明の分野】

##### 【0001】

本発明の実施形態は、一般に、プラズマ処理システムを用いた電子機器の製造装置及び方法に関する。

##### 【関連技術の説明】

##### 【0002】

フラットパネルディスプレイ(FPD)、薄膜トランジスタ(TFT)、液晶セルの製造において、金属相互接続及びその他の構成はガラス基板上に導体、半導体、及び誘電材料の複数層を堆積、除去することで形成される。形成された様々な構成は、例えば、FPD上の個々の画素で表示状態が電気的に作り出されるアクティブラチクスディスプレイスクリーンの製造で集合的に使用するシステムに集積される。FPDを製造するために用いる処理技法には、プラズマ化学気相成長法(PECVD)、物理的気相成長法(PVD)、エッ칭等その他が含まれる。フラットパネルディスプレイの製造にはプラズマ処理が特によく適しており、これは膜を堆積するのに必要な処理温度が比較的低く、得られる膜の質が高いためである。

##### 【0003】

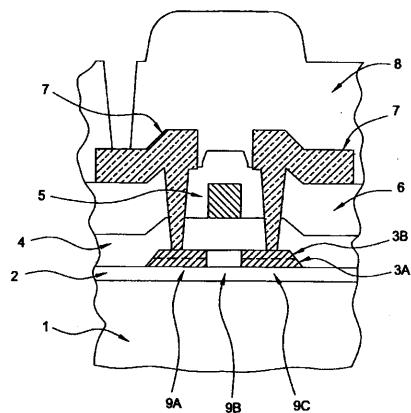

TFTディスプレイの製造で利用される一般的なFPDデバイスは図1の従来技術に示されるように低温ポリシリコン(LTPS)TFTデバイスである。LTPS TFTデ

40

50

バイスは光学的に透明な基板1上に形成したソース領域9A、チャネル領域9B、ドレイン領域9Cを備えたMOSデバイスである。ソース領域9A、チャネル領域9B、ドレイン領域9Cは、一般的に、アモルファスシリコンをまず堆積し、典型的には続いてアニーリングによりポリシリコン(p-Si)層を形成することで形成される。ソース、ドレイン、チャネル領域は光学的に透明な基板1上で領域のパターニングと、堆積した最初のa-Si層のイオンドーピングを行い、続いてアニーリングを行うことでポリシリコン層を形成することで形成することができる。次にゲート誘電体層4を堆積したp-Si層上に堆積し、ゲート5をチャネル、ソース、ドレイン領域から隔離する。ゲート5は、ゲート誘電体層4上に形成される。ゲート誘電体層4は一般的には二酸化ケイ素(SiO<sub>2</sub>)層から成ることからゲート酸化物層としても知られている。次に、絶縁層6及びデバイス接続を絶縁層を通して形成し、TFTデバイスを制御する。

#### 【0004】

p-Si TFTデバイスの性能は、MOS構造を形成するために堆積する膜の質に依存する。MOSデバイスにおいて要となる性能要素はp-Siチャネル層膜、ゲート誘電体層膜、p-Si / ゲート誘電体層インターフェースの質である。近年、p-Siチャネル層膜の質に注目が集まっているが、高品質のゲート誘電体層とp-Si / ゲート誘電体インターフェースの作製は達成が困難であった。ゲート誘電体層4はTFTデバイスの電気的性能に重要である。特に、望ましい電気的性能と高破壊電圧(V<sub>B</sub>)を備えたトランジスタを製造するために、ゲート誘電体層は高品質(例えば、低フラットバンド電圧(V<sub>fb</sub>))である必要性がある。ゲート酸化物の質がデバイス性能、ひいてはFPDの質と有用性に影響する。

#### 【0005】

典型的には、ゲート誘電体層4は例えばPECVD等の従来技法を用いて堆積した酸化物を含み、通例は約350～約450で堆積される。残念ながら、堆積された膜とp-Siチャネル層とのインターフェースの質は、TFTデバイスの性能を最高のものにするには不十分なことが多い。良好なインターフェースを堆積した膜とp-Siチャネル層との間に高温(例えば、>600)堆積法を使用して形成することは不可能なことが多く、これは高堆積温度によりすでに堆積された層におけるドーパントの相互拡散が促進され、またガラスが軟化して寸法的に安定しないことからその上に薄膜トランジスタが形成されるガラス基板と適合しないからである。

#### 【0006】

堅牢なLCD TFTゲート誘電体膜は低インターフェース捕獲電荷、誘電体層の低欠陥数、低固定酸化物電荷と低可動イオン密度を特徴とする高品質Si/SiO<sub>2</sub>インターフェースを有し、全て500未満の処理温度で形成される。

#### 【0007】

従って、上述の欠点を克服する薄膜トランジスタで使用するための高品質ゲート誘電体層を形成可能な方法及び装置が求められている。

#### 【発明の概要】

#### 【0008】

本発明は、概して、基板をプラズマ処理するためのプラズマチャンバを提供するものであり、プラズマ処理領域を形成する1つ以上の壁部、プラズマ処理領域内に取り付けられ、垂直方向の間隔を空けた複数位置で基板を支持するよう用いられる基板支持部材、RFエネルギーをプラズマ処理領域に伝達するために位置されたRF伝達デバイス、RF伝達デバイスに連結されたRF電源、プラズマ処理領域と連通した酸化ガス供給源を含む。

#### 【0009】

本発明は、概して、基板をプラズマ処理するためのプラズマチャンバを提供するものであり、プラズマ処理領域を形成する1つ以上の壁部、プラズマ処理領域内に取り付けられ、垂直方向の間隔を空けた複数位置で基板を支持するよう用いられる基板支持部材、RFエネルギーをプラズマ処理領域に伝達するために位置された第1RF伝達デバイス、RF伝達デバイスに連結された第1RF電源、プラズマ処理領域にRFエネルギーを伝達する

10

20

30

40

50

ために位置された第2RF伝達デバイス、RF伝達デバイスに連結された第2RF電源、プラズマ処理領域と連通した酸化ガス供給源、第1RF電源、第2RF電源、ガス供給源に連結された制御装置を含み、制御装置は第1RF伝達デバイスに供給されるRFエネルギー、第2RF伝達デバイスに供給されるRFエネルギー、酸化ガス供給源からプラズマ処理領域に供給されるガスを制御するよう用いられる。

#### 【0010】

本発明は、概して、基板をプラズマ処理するための方法を提供する。本方法は、プラズマ処理チャンバのプラズマ処理領域における複数の処理位置の第1位置への基板の移動、プラズマ処理領域への酸化ガス混合物の流入、約550以下の基板表面温度での、プラズマ処理領域におけるプラズマ発生による基板表面への酸化表面の形成、複数の処理位置の第2位置への基板の移動、基板表面上への誘電体層の形成による、厚さ約100～約6000を有するゲート誘電体層の形成を含む。10

#### 【0011】

本発明は、概して、基板をプラズマ処理するための方法を提供する。本方法は、プラズマ処理チャンバのプラズマ処理領域における複数の処理位置の第1位置への基板の移動、プラズマ処理領域への酸化ガス混合物の流入、第1RF伝達デバイスを用いての、約550以下の基板表面温度でのプラズマ処理領域におけるプラズマ発生、プラズマ処理チャンバのプラズマ処理領域における複数の処理位置の第2位置への基板の移動、誘電体層形成ガス混合物のプラズマ処理領域への流入、第2RF伝達デバイスを用いての、約550以下の基板表面温度でのプラズマ処理領域におけるプラズマ発生による基板表面上への誘電体層の形成を含む。20

#### 【0012】

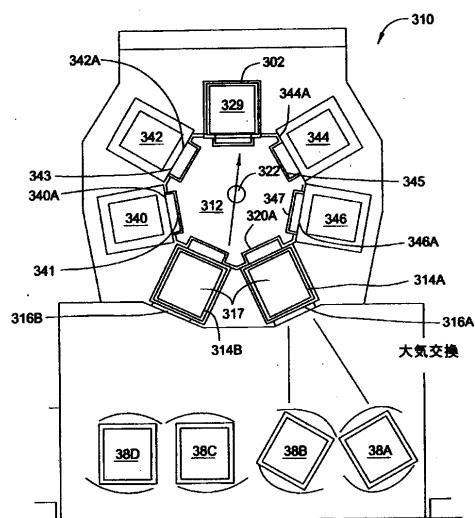

本発明は、概して、基板上に高品質ゲート酸化物層を形成するためのクラスタツールを提供する。クラスタツールは、基板上に酸化表面を形成し、また基板上に誘電体層を堆積してゲート誘電体層を形成するよう用いられる複数のプラズマ処理チャンバと、基板を約550以下に維持するよう構成された制御装置とを含む。

#### 【0013】

本発明は、概して、基板上に高品質ゲート酸化物層を形成するためのクラスタツールを提供する。クラスタツールは、基板上に約550以下の温度で酸化表面を形成するよう用いられる第1チャンバと、基板上の酸化表面上に約550以下で誘電体層を堆積するよう用いられる第2チャンバを含む。30

#### 【0014】

本発明は、概して、基板をプラズマ処理するためのプラズマチャンバを提供するものであり、プラズマ処理領域を形成する1つ以上の壁部、プラズマ処理領域内に取り付けられ、垂直方向の間隔を空けた複数のプラズマ処理位置で基板を支持するよう用いられる基板支持部材、RFエネルギーをプラズマ処理領域に伝達するために位置されたRFコイル、RFコイルに連結されたRF電源、RFエネルギーをプラズマ処理領域に伝達するために位置されたガス分布プレート、ガス分布プレートに連結されたRF電源、プラズマ処理領域と連通した酸化ガス供給源を含む。

#### 【0015】

本発明は、概して、基板をプラズマ処理するためのプラズマチャンバを提供するものであり、プラズマ処理領域を形成する1つ以上の壁部、プラズマ処理領域内に取り付けられ、垂直方向の間隔を空けた複数のプラズマ処理位置で基板を支持するよう用いられ、またRF電源から供給されるRFエネルギーをプラズマ処理領域に伝達するために位置された基板支持体、プラズマ処理領域に取り付けられ接地されたガス分布プレート、またプラズマ処理領域と連通した酸化ガス供給源を含む。40

#### 【詳細な説明】

#### 【0016】

本発明は、誘導結合高密度プラズマを用いて基板表面を処理するための装置と方法を提供する。概して、本発明の態様はフラットパネルディスプレイ加工、半導体加工、太陽電50

池加工、及びその他の基板加工に使用可能である。本発明を、カリフォルニア州サンタクララのアプライドマテリアル社の一事業部である A K T 社から入手可能なプラズマ化学気相成長システム ( P E C V D ) 等の大面積基板を処理するための化学気相成長システムを参照しながら、以下で具体的に説明する。しかしながら、本発明の装置と方法は、円形基板を処理するように構成されたシステムを含め、その他のシステム構成でも利用できることを理解しなくてはならない。

#### 【 0 0 1 7 】

図 1 は、薄膜トランジスタ構造の概略断面図である。光学的に透明な基板 1 は可視スペクトルで原則的に光学的に透明な材料、例えばガラス又は透明プラスチックを含んでいてもよい。光学的に透明な基板 1 の形状又は寸法は様々であってもよい。典型的には、TFT 用途としては、光学的に透明な基板 1 は表面積が約  $2\,0\,0\,0 \text{ cm}^2$  より大きいガラス基板である。

#### 【 0 0 1 8 】

バルク半導体層 3 A は光学的に透明な基板 1 上に形成される。バルク半導体層 3 A は多結晶シリコン ( ポリシリコン ) 又はアモルファスシリコン ( - Si ) 層を含んでいてもよく、当技術分野で周知の従来技法により P E C V D システムを用いて堆積することができる。バルク半導体層 3 A は厚さ約 100 ~ 3000 であってもよい。一実施形態において、バルク半導体層 3 A はドープ n 型又は p 型ポリシリコン又は - Si 層である。一実施形態においては、バルク半導体層 3 A 上に別のポリシリコン又は - Si 第 2 半導体層 3 B を約 100 ~ 約 3000 の厚さまで堆積する。

#### 【 0 0 1 9 】

光学的に透明な基板 1 とバルク半導体層 3 Aとの間には、任意の絶縁材料 2 、例えば二酸化ケイ素 ( SiO<sub>2</sub> ) 又は窒化ケイ素 ( SiN ) 層が存在してもよい。

#### 【 0 0 2 0 】

ゲート誘電体層 4 はバルク半導体層 3 A 上 ( 又は第 2 半導体層 3 B ) に形成される。本発明の一態様において、ゲート誘電体層 4 は、以下に記載の高密度プラズマ酸化 ( H D P O ) 処理を用いてすでに堆積したシリコン層の一部を消耗することで成長させた二酸化ケイ素から成る。別の実施形態においては、多層ゲート誘電体層は、H D P O 処理を用いて二酸化ケイ素膜を成長させ、続いてプラズマ化学気相成長で二酸化ケイ素、酸窒化ケイ素 ( SiON ) 、及び / 又は窒化ケイ素 ( SiN ) 膜を H D P O 処理膜上に堆積することで形成される。一実施形態においては、高密度プラズマ C V D 処理を利用して第 2 層を堆積する。総ゲート誘電体層 4 は、約 100 ~ 約 6000 の厚さに形成し得る。

#### 【 0 0 2 1 】

ゲート電極層 5 はゲート誘電体層 4 上に形成される。ゲート電極層 5 は TFT デバイス内における荷電担体の動きを制御する導電層を含む。ゲート電極層 5 は金属、例えば、中でもアルミニウム ( Al ) 、タンゲステン ( W ) 、クロム ( Cr ) 、タンタル ( Ta ) 、ポリシリコン、又はその組み合わせを含んでいてもよい。ゲート電極層 5 は従来の堆積、リソグラフィ、エッチャリング技法を用いて形成し得る。また、従来の堆積、リソグラフィ、エッチャリング技法を用いることにより、次に絶縁層 6 、電気的ソース及びドレイン接点 7 、不動態化層 8 をゲート電極層 5 上に形成する。

#### 【 0 0 2 2 】

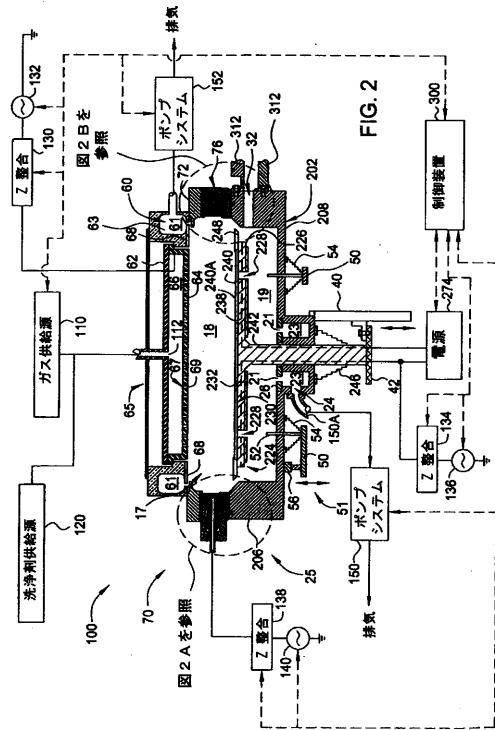

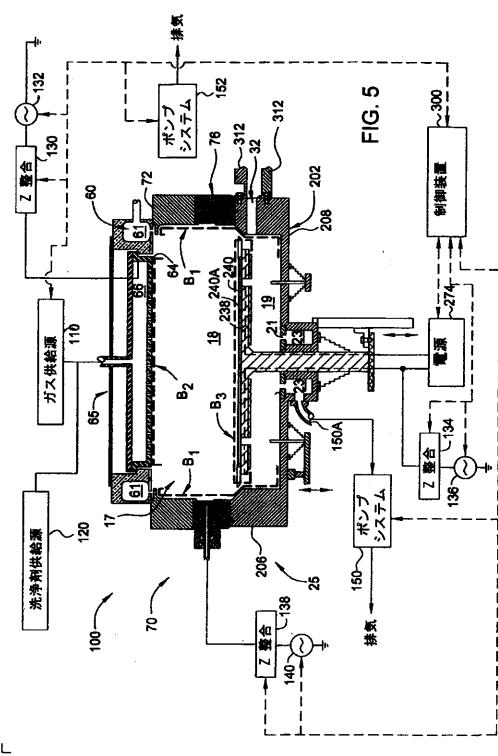

図 2 はプラズマ処理チャンバ 100 の概略断面図である。プラズマ処理チャンバ 100 は、概して、ガス分布アセンブリ 64 、誘導結合ソースアセンブリ 70 、下部チャンバアセンブリ 25 を含む。処理容量 18 と下部容量 19 とから成るチャンバ容量 17 はプラズマ処理チャンバ 100 内におけるプラズマ処理が生じる領域を形成し、ガス分布アセンブリ 64 、誘導結合ソースアセンブリ 70 、下部チャンバアセンブリ 25 によって包囲されている。

#### 【 0 0 2 3 】

下部チャンバアセンブリ 25 は、通常、基板昇降アセンブリ 51 、基板支持体 238 、処理チャンバ基部 202 を含む。処理チャンバ基部 202 はチャンバ壁部 206 と、下部

10

20

30

40

50

容量 19 を部分的に形成するチャンバ底部 208 を有する。処理チャンバ基部 202 にはチャンバ壁部 206 のアクセスポート 32 を通してアクセスする。アクセスポート 32 は、そこを通過させて基板 240 を処理チャンバ基部 202 に出し入れ可能な領域を形成する。チャンバ壁部 206 及びチャンバ底部 208 は、アルミニウム又は処理に耐え得るその他の材料の一体型ブロックから形成してもよい。

#### 【0024】

温度制御された基板支持体 238 は処理チャンバ基部 202 に連結されている。基板支持体 238 は、処理中、基板 240 を支持する。一実施形態において、基板支持体 238 は少なくとも 1 つの埋設されたヒータ 232 を包封するアルミニウム本体部 224 を含む。抵抗加熱素子等の埋設ヒータ 232 は基板支持体 238 内に配置される。埋設ヒータ 232 は電源 274 に連結されており、基板支持体 238 とその上の基板 240 を既定の温度まで制御装置 300 を用いて制御しながら加熱することが可能である。典型的には、大抵の CVD 処理において、埋設ヒータ 232 は基板 240 をプラスチック基板の場合の約 600 からガラス基板の場合の約 550 の均一な温度範囲に維持する。

10

#### 【0025】

一般的に、基板支持体 238 は裏面 226、正面 234、軸 242 を有している。正面 234 は基板 240 を支持し、一方、軸 242 は裏面 226 に連結されている。軸 242 に取り付けられた軸基部 242 は基板支持体 238 を図 2 ~ 4 に図示される様々な位置間で移動させるための昇降アセンブリ 40 に連結されている。図 4 に図示の搬送位置では、システムロボット（図示せず）は基板支持体 238 及び / 又は昇降ピン 52 を妨害することなくプラズマ処理チャンバ 100 内外を自由に出入りすることが可能となる。また、軸 242 は、基板支持体 238 とクラスタツール 310 のその他のコンポーネントとの間の導線・熱電対リード線用の管路としても機能する。昇降アセンブリはプラズマ処理チャンバ 100 が真空下にある場合に基板にかかる重力と大気圧に対抗するに必要な力を供給し、プラズマ処理チャンバ 100 内に支持アセンブリを正確に位置させるために当技術分野で一般的に使用される空気式又は電動リードスクリュー型昇降アセンブリを備えていてよい。

20

#### 【0026】

ベロー 246 は基板支持体 238（又は軸 242）と処理チャンバ基部 202 のチャンバ底部 208 の間に連結されている。ベロー 246 はチャンバ容量 17 と処理チャンバ基部 202 外部の大気との間を真空密封し、一方、基板支持体 238 の縦方向の動きを促進する。

30

#### 【0027】

基板支持体 238 は、さらに、基板 240 と外接するシャドーフレーム 248 を支持している。一般的に、シャドーフレーム 248 は基板 240 の縁部と基板支持体 238 上への堆積を防止する。一実施形態において、シャドーフレーム 248 は基板昇降アセンブリ 51 に取り付けた機構（図示せず）により基板 240 と基板支持体 238 から分離される。別の実施形態においては、シャドーフレーム 248 はプラズマ処理チャンバ 100 内に載置された捕捉機構（図示せず）上に溶着されているため、基板支持体が処理位置から下降するにつれ、基板支持体 238 を捕捉機構上にあるシャドーフレーム 248 から離すことが可能となる。捕捉機構の実施形態又は基板昇降アセンブリ実施形態に取り付けた機構により、基板支持体 238、ひいてはプラズマ処理チャンバ 100 からの基板 240 の除去が容易になる。

40

#### 【0028】

基板支持体 238 は複数の穴部 228 を有しており、そこに複数の昇降ピン 52 を通す。昇降ピン 52 は典型的にはセラミック、グラファイト、セラミック被覆金属、又はステンレススチールで形成されている。昇降ピン 52 を（図 2 に示す）後退位置から上昇位置（図示せず）に移動可能な昇降プレート 50 により、昇降ピン 52 を基板支持体 238 と処理チャンバ基部 202 に相対して作動させてもよい。昇降ピン 52 とチャンバ底部 208 のそれぞれに取り付けられた昇降ベロー 54 は、下部容量 19 をプラズマ処理チャンバ

50

100 外部の大気から隔離するために使用され、同時に、昇降ピン 52 の（図2に図示の）後退位置から上昇位置（図示せず）への移動を可能にする。昇降プレート 50 は昇降アクチュエータ 56 を用いて作動させる。昇降ピン 52 が上昇位置にあり、基板支持体 23 8 が搬送位置にある場合、基板 240 はアクセスポート 32 の上端より上に持ち上げられるため、システムロボットがプラズマ処理チャンバ 100 内外を出入り可能となる。

#### 【0029】

蓋アセンブリ 65 は、典型的には、ガス供給源 110 によって供給された処理ガスがそこを通ってガス分布プレート 64 を通過した後に処理容量 18 に導入される投入ポート 112 を含む。ガス供給源 110 から投入ポート 112 へのガス流の適切な制御と調節は質量流量制御装置（図示せず）と制御装置 300 によって行われる。ガス供給源 110 は質量流量制御装置（図示せず）を複数備えていてもよい。ここで使用する「質量流量制御装置」という用語はプラズマ処理チャンバ 100 に迅速かつ正確にガス流を供給可能な制御弁を指す。投入ポート 112 により、処理ガスはプラズマ処理チャンバ 100 に導入され、また均一に分布される。それに加え、投入ポート 112 を任意で加熱してマニホールド内における反応ガスの凝縮を防止してもよい。

#### 【0030】

また、投入ポート 112 は洗浄剤供給源 120 に連結されている。典型的には、洗浄剤供給源 120 は解離フッ素等の洗浄剤を供給し、洗浄剤は処理容量 18 内に導入され、先行の処理工程終了後に残留した堆積副生成物と逸脱して堆積された材料を除去する。

#### 【0031】

蓋アセンブリ 65 は処理容量 18 の上部境界線を形成する。典型的には、蓋アセンブリ 65 をチャンバ基部 202 及び / 又は誘導結合ソースアセンブリ 70 から外してプラズマ処理チャンバ 100 内のコンポーネントを補修することが可能である。典型的には、蓋アセンブリ 65 はアルミニウム（A1）又は陽極酸化アルミニウム体から製造される。

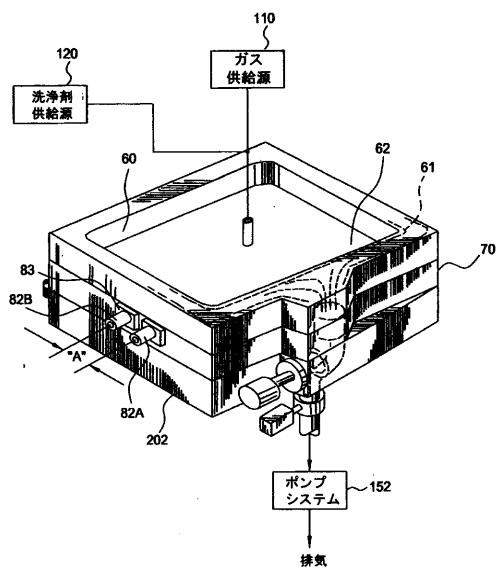

#### 【0032】

一実施形態において、蓋アセンブリ 65 は外部真空ポンプシステム 152 に連結されたポンププレナム 63 を含む。ポンププレナム 63 を利用して、処理容量 18 からガスと処理副生成物とを均一に排出する。ポンププレナム 63 は、概して、チャンバ蓋部 60 内部に形成又は取り付けられており、プレート 68 によって覆われてポンプチャネル 61 を構成する。処理容量 18 を確実に均一に排気するために、プレート 68 とチャンバ蓋部 60 との間に間隙を形成してポンプチャネル 61 へのガス流を若干制限する。一実施形態においては、誘導結合ソースアセンブリ 70 の蓋部支持部材 72 上に形成したシャドー機構 71 も用いてさらに制限することで、より確実に処理容量 18 を均一に排気する。一般に、所望のチャンバ処理圧に応じて、真空ポンプシステム 152 はターボポンプ、ラフポンプ、及び / 又はルーツプロワー（Roots Blower（商標名））等の真空ポンプを有する。

#### 【0033】

別の実施形態においては、真空ポンプシステム 150 を用いて、下部チャンバアセンブリ 25 のポンププレナム 24 を通してガスと処理副生成物を処理容量 18 から均一に排出する。ポンププレナム 24 は、概して、チャンバ底部 208 内部に形成又は取り付けられており、プレート 26 によって覆うことで封鎖ポンプチャネル 23 を構成してもよい。プレート 26 は、通常、ポンプチャネル 23 へのガス流に若干の制限を加えることでチャンバ容量 17 を確実に均一に排気するための複数の穴部 21（又はスロット）を備える。ポンプチャネル 23 はポンプポート 150A を通して真空ポンプシステム 150 に連結されている。一般に、所望のチャンバ処理圧に応じて、真空ポンプシステム 150 はターボポンプ、ラフポンプ、及び / 又はルーツプロワー（Roots Blower（商標名））等の真空ポンプを含む。図2～4に示されるように、一実施形態において、処理容量 18 からガスを確実に均等に排気するために、ポンププレナム 24 は処理チャンバ中央付近で対称的に配置される。別の実施形態において、ポンププレナム 24 は下部チャンバアセンブリ 25 において非対称的に位置されている（図示せず）。

10

20

30

40

50

## 【0034】

別の実施形態においては、ポンププレナム24とポンププレナム63の双方を用いて処理容量18の排気を行う。この実施形態においては、処理容量18と下部容量19からそれぞれ真空ポンプシステム152、150を用いて除去するガスの相対流量を最適化することでプラズマ処理の効果を改善し、プラズマと処理副生成物の下部容量19への漏れを軽減してもよい。プラズマと処理副生成物の漏れの軽減により、下部チャンバーアセンブリ25コンポーネント上への逸脱した堆積の量が低下し、こういった不要な堆積物を除去するための洗浄時間及び／又は洗浄剤供給源120の使用頻度が低下する。

## 【0035】

ガス分布プレート64は蓋アセンブリ65の上プレート62に連結されている。ガス分布プレート64の形状は、典型的には基板240の外形に実質的に沿うように構成されている。ガス分布プレート64は穿孔領域67を含み、ガス供給源110から供給された処理ガス及びその他のガスはそこを通過して処理容量18へと供給される。ガス分布プレート64の穿孔領域67は、ガス分布プレート64を通って処理容量18に流れ込むガスが均一に分散されるように構成されている。本発明で有益に使用し得るガス分布プレートは、共通して譲渡される2003年1月7日にプロニガンその他による米国特許出願第10/337483号、ホワイトその他に2002年11月12日に発行された米国特許第6477980号、チェその他によって2003年4月16日に出願された米国特許出願第10/417592号に記載されており、これらは引用により本願に組み込まれる。

## 【0036】

図2～4に示されるように、ガス分布プレート64は一つの一体型部材から形成してもよい。その他の実施形態において、ガス分布プレート64は2つ以上の別々の部材から形成可能である。複数のガス流路69がガス分布プレート64を貫通して形成され、これにより処理ガスを所望のガス分布でガス分布プレート64を通して処理容量18に流すことが可能となる。プレナム66はガス分布プレート64と上プレート62との間に形成される。プレナム66により、ガス供給源110からプレナム66に流入するガスがガス分布プレート64の幅全体にわたって均一に分散され、ガス流路69を均一に流れることが可能となる。ガス分布プレート64は、典型的には、アルミニウム(A1)、陽極酸化アルミニウム、又はその他のRF導電材料から作製される。ガス分布プレート64は、電気絶縁部品(図示せず)によってチャンバ蓋部60から電気的に隔離されている。

## 【0037】

図2、2A、2Bでは、誘導結合ソースアセンブリ70は、総じて、RFコイル82、支持構造体76、カバー80、様々な絶縁部品(例えば、内側絶縁体78、外側絶縁体90等)を収容する。支持構造体76は、通常、支持部材84と蓋部支持部材72を備え、これらは蓋アセンブリ65のコンポーネントを支持する接地金属部品である。RFコイル82は、RF電源140からコイルに供給されるRF電力の支持構造体76へのアーク放電を防止する又は接地されたチャンバコンポーネント(例えば、処理チャンバ基部202その他)への著しい損失を防ぐ数々の部品に支持され取り囲まれている。薄く切れ目のないリング、バンド、又は重なった一連の切片であるカバー80が支持構造体76コンポーネントに取り付けられている。カバー80はRFコイル82をプラズマ堆積化学作用との相互作用あるいはプラズマ処理中に発生したイオンや中性粒子の衝突から又はチャンバ洗浄化学反応に曝されるのを守るものである。カバー80はセラミック材料(例えば、アルミナ又はサファイア)又はその他の処理対応誘電体材料から形成される。また、様々な絶縁部品、例えば内部絶縁部品78及び外部絶縁部品90を用いてRFコイル82を支持し、また電気的に接地された支持構造体76から隔離する。絶縁部品は、通常、電気絶縁材料、例えばテフロン(商標名)又はセラミック材料から成る。真空フィードスルーブル83が支持構造体76に取り付けられており、RFコイル82を保持及び支持し、また排気した処理容量18への大気の漏れを防止している。支持構造体76、真空フィードスルーブル83、種々のOリング85、86、87、88、89は、RFコイル82とガス分布アセンブリ64を支持する真空気密構造体を構成し、RFコイル82は、RFによって発生

10

20

30

40

50

した磁界を阻害する導電性バリアなしで処理容量 18 と通ずることが可能となる。

#### 【0038】

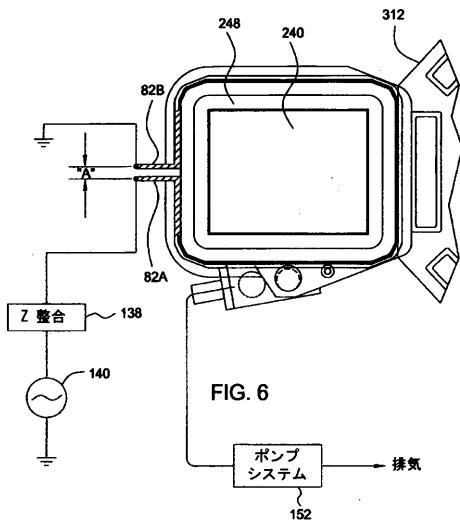

図 2 ~ 5 に示されるように、RF コイル 82 は RF インピーダンス整合回路 138 を通して RF 電源 140 に接続されている。この構成において、RF コイル 82 はプラズマの発生と処理容量 18 内で発生したプラズマの制御が可能な誘導結合 RF エネルギー伝達デバイスとして機能する。一実施形態においては、ダイナミックインピーダンス整合を RF コイル 82 に行なう。制御装置 300 を用いることで、処理容量 18 の周縁部に取り付けられた RF コイル 82 が基板表面 240A 近辺で発生するプラズマの制御、形状調整を行えるようになる。一実施形態において、図 2 ~ 5 に図示されるように、RF コイル 82 は単巻コイルであり、チャンバ容量 17 で発生するプラズマを制御するために使用する。別の実施形態においては、複巻コイルを用いてプラズマ形状と密度を制御する。10

#### 【0039】

構成によっては、単巻コイルのコイル端がプラズマ処理チャンバ 100 で発生するプラズマの均一性に影響する場合がある。コイルの端部を重ねることが実際的でない又は望ましくない場合、図 6 及び 7 に図示されるギャップ領域 A をコイル端部間に残してもよい。コイル長さの不足及びコイルの入力端 82A と出力端 82B での RF 電圧相互作用により、ギャップ領域 A 近辺の RF 発生磁場は弱くなる。この領域での磁場の弱さはチャンバ内のプラズマの均一性に悪影響を与える可能性がある。この問題を解決するため、可変インダクタを用いて処理中に RF コイル 82 とアースとの間のリアクタンスを継続的又は反復的に調整することが可能であり、RF コイル 82 に沿って RF 電圧分布、ひいては発生したプラズマをシフト又は回転させて不均一なプラズマを時間平均し、コイル端部での RF 電圧相互作用を軽減する。20 RF コイル 82 とアースとの間のリアクタンスを調整してコイルにおける RF 電圧分布をシフトさせるための模範方法は、1998 年 3 月 31 日出願の「コイルスパッタリング分布を制御するための回転コアを有する可変インピーダンスの使用」に詳細に記載されており、引用することで本願で請求の態様と開示に矛盾しない範囲で本願に組み込まれる。この結果、処理容量 18 で発生するプラズマは、RF 電圧分布を変化させることによるプラズマ分布の時間平均により更に均一かつ軸を中心に対称的に制御される。RF コイル 82 に沿った RF 電圧分布はプラズマ密度、RF 電位プロファイル、基板 240 を含むプラズマ露出表面のイオン衝撃を含む様々なプラズマ特性に影響を与える可能性がある。30

#### 【0040】

一実施形態においては、ガス分布プレート 64 は RF バイアス印加され、取り付けたインピーダンス整合素子 130、RF 電源 132、制御装置 300 を用いることで処理容量 18 で発生したプラズマを制御、形状調整することができる。RF バイアス印加されたガス分布プレート 64 は、処理容量 18 内でプラズマを発生、制御可能な容量結合 RF エネルギー伝達デバイスとして機能する。

#### 【0041】

別の実施形態において、RF 電源 136 は RF バイアス電力をインピーダンス整合素子 134 を通して基板支持体 238 に印加する。RF 電源 136、インピーダンス整合素子 134 と制御装置 300 の使用により、ユーザは処理容量 18 で発生するプラズマの制御、基板 240 のプラズマ照射の制御、基板表面 240A 上のプラズマシース厚を変えることができる。別の実施形態においては、RF 電源 136 及びインピーダンス整合素子 134 を 1 つ以上のアース接続（図示せず）で代替することで基板支持体 238 を接地する。40

#### 【0042】

プラズマ処理チャンバ 100、処理変数、コンポーネントをその他のクラスタツール 310 コンポーネントと共に制御するために、制御装置 300 を適合させて全基板処理シケンスの全ての側面を制御する。制御装置 300 は、インピーダンス整合素子（つまり、130、134、138）、RF 電源（つまり、132、136、140）、プラズマ処理チャンバ 100 のその他全ての要素を制御するよう用いられる。プラズマ処理チャンバ 100 のプラズマ処理変数は制御装置 300 の使用により制御され、典型的にはマイクロ50

プロセッサを用いた制御装置である。制御装置 300 は、ユーザ及び／又はプラズマ処理チャンバの様々なセンサからの入力を受信し、様々な入力及び制御装置のメモリに保持されたソフトウェア命令に従ってプラズマ処理チャンバコンポーネントを適切に制御するよう構成されている。制御装置 300 は、一般的にメモリと CPU を備え、制御装置はこれらを利用して様々なプログラムを保持、処理、また必要な際に実行する。メモリは CPU に連結されており、1つ以上の入手容易なメモリ、例えばランダムアクセスメモリ (RAM)、読み出し専用メモリ (ROM)、フロッピー（商標名）ディスク、ハードディスク、又はその他のいずれの形式のローカル又はリモートデジタルストレージでもあってもよい。ソフトウェア命令及びデータをコード化してメモリに記憶させ、CPU に命令することができる。慣用のやり方でプロセッサを支持するために、支持回路も CPU に接続する。支持回路は当技術分野で周知のキャッシュ、電力供給源、クロック回路、入力／出力回路、サブシステム等を含んでいてもよい。制御装置 300 で読み取り可能なプログラム（又はコンピュータ命令）がどのタスクをプラズマ処理チャンバで実行可能かを決定する。好ましくは、プログラムは制御装置 300 で読み取可能なソフトウェアであり、規定のルールと入力データに基づいてプラズマ処理をモニタ及び制御する命令を含む。

#### 【0043】

##### プラズマ処理

操作中、プラズマ処理チャンバ 100 を真空ポンプシステム 150 及び／又は真空ポンプシステム 152 を用いて既定の圧力／真空まで排気すると、プラズマ処理チャンバ 100 は同じく真空下にある中央搬送チャンバ 312 に取り付けられたシステムロボット（図示せず）から基板 240 を受け取り可能となる。基板 240 をチャンバに搬送するためにプラズマ処理チャンバ 100 を中央搬送チャンバ 312 から密閉するスリットバルブ（図 8 の 341、343、345、347 を参照のこと）が開くことで、システムロボットは処理チャンバ基部 202 のアクセスポート 32 を通って伸びることが可能となる。次に昇降ピン 52 が伸ばされたシステムロボットから基板 240 を取り除く。システムロボットは次にプラズマ処理チャンバ 100 から後退し、チャンバスリットバルブは閉鎖されてプラズマ処理チャンバ 100 は中央搬送チャンバ 312 から隔離される。基板支持体 238 は次に昇降ピン 52 から基板 240 を持ち上げて基板 240 を所望の処理位置へと移動させる。

#### 【0044】

基板 240 が一旦収容された後、以下の一般的なプラズマ処理工程を用いて基板 240 への処理シーケンスを完了させる。まず最初に、基板 240 を昇降ピンから持ち上げた後、基板支持体 238 を所望の処理位置へと移動し、またプラズマ処理チャンバを既定のベース圧まで排気する。既定のベース圧に一旦到達したら、真空ポンプシステムによりチャンバ容量 17 の排気を継続しながら、ガス供給源 110 から特定の流量の1つ以上の処理ガスをチャンバ容量 17 にガス分布プレート 64 を通して導入することで、平衡処理圧力を得る。真空ポンプシステム（つまり、150 及び／又は 152）の連通を絞る及び／又はガス供給源 110 から導入される処理ガスの流量を調節するのいずれかにより、制御装置 300 は処理圧力を調節する。所望の圧力とガス流量が一旦確立されると、各 RF 電力供給源を作動させて処理容量 18 内でプラズマを発生、また発生したプラズマを制御してもよい。電力は制御装置 300 により RF コイル 82、ガス分布プレート 64、及び／又は基板支持体 238 へと独立して供給可能である。RF コイル 82、ガス分布プレート 64 及び／又は基板支持体 238 への RF 電力を変化させることで、処理容量 18 内で発生するプラズマの密度を変えることができ、これはプラズマイオン密度は発生した磁場及び／又は電場の強度に直接影響を受けるからである。また、プラズマのイオン密度は、処理圧力や RF コイル 82 及び／又はガス分布プレート 64 に供給される RF 電力を調整することで増大又は低下させてもよい。以下に記載の様々なチャンバ処理工程を基板に施した後、昇降ピン 52 を上昇させ、基板支持体 238 を下降させて基板 240 を上昇させた昇降ピン 52 上に載せ、スリットバルブ（図示せず）を開閉し、システムロボットをチャンバ内に伸ばし、昇降ピン 52 を下降させて基板 240 をシステムロボットブレード（図示

10

20

30

40

50

せず) 上に載せ、続いてシステムロボットを後退させ、スリットバルブを閉鎖することでプラズマ処理チャンバ100から基板を除去する。

#### 【0045】

##### 高品質ゲート酸化物形成

本発明の実施形態は、安定した、再現性のある、望ましい電気的性能のTFTデバイスを確実に製造するための高品質ゲート誘電体層を形成するための方法を記載する。本発明の実施形態は、概して、上記のプラズマ処理チャンバ100において高品質ゲート誘電体層を形成するために使用する1つ以上の処理工程を記載する。

#### 【0046】

本発明の一実施形態においては、以下に記載の单一高密度プラズマ酸化処理(HDPO)を用いてゲート誘電体層を形成する。この実施形態におけるHDPO処理層は厚さ約20~1000オングストローム( )であってもよいが、好ましくは約50~約150である。

#### 【0047】

別の実施形態においては、まずHDPO処理を行い、次にCVD膜を最初のHDPO処理層上に形成することで二層膜を形成している。この実施形態において、CVD膜はPECVDテトラエチルオキシシラン(TEOS)(又はテトラエチルオルトシリケート(TEOS))型堆積処理を用いて堆積したSiO<sub>2</sub>である。この実施形態におけるHDPO処理層は厚さ約20~約500オングストローム( )であるが、好ましくは約50~約150である。ゲート誘電体層4の全体厚さは約100~約6000である。

#### 【0048】

##### 高密度プラズマ酸化処理

HDPO処理は、シリコン基板表面240Åをガス分布プレート64を通してガス供給源110から処理容量18に供給される酸素含有ガス又はガス混合物を用いて発生させたプラズマに曝露することで完了する。シリコンを酸化させるために使用する従来のサーマル型酸化処理では、通常>900である非常に高温を必要とすることが多い。従って、高品質ゲート誘電性層を形成するために必要な温度を最低限とするために、本発明の態様を低温(<550)で使用して高品質ゲート誘電体層を形成してもよい。典型的には、HDPO処理は約60~約550の温度で行う。従来のサーマル酸化処理においては、処理温度の低下により酸化物層の成長速度が低下し、チャンバ処理時間と一緒に伴ってシステムスループットが長くなる。成長速度を上げ、それに伴いチャンバ処理時間を短縮するために、HDPO処理ではRFエネルギーを利用してゲート酸化物成長速度を促進する。RFエネルギーの印加により(1)反応種の解離又はイオン化が促進、(2)反応種のエネルギー(又は活性)が増大、(3)イオン及び中性粒子衝突を通じた基板表面240Åへのエネルギー追加、(4)高密度プラズマの発生によって作り出された熱放射へ基板表面240Åが曝露されることから、HDPO処理は成長速度を上げることが可能だと思われる。

#### 【0049】

一実施形態において、HDPO処理には、RFコイル82に供給されるRF電力を制御して処理チャンバ18において基板表面240Å上で発生するプラズマのプラズマイオン密度を制御することを必要とする。典型的には、RFコイル82に供給されたRF電力は約0.3MHz~10GHzを越える周波数で約250~約25000ワット/m<sup>2</sup>である。好ましくは、RF周波数は約13MHz~約80MHzである。一実施形態においては、周波数、インピーダンス整合回路、又は順電力サーボでの周波数の調整により、RFコイル82のダイナミックインピーダンス整合を行う。

#### 【0050】

別の実施形態においては、ガス分布プレート64に供給されるRFエネルギーによりHDPO処理プラズマを発生、制御する。典型的には、ガス分布プレート64に供給されるRF電力は約0.3MHz~約10GHzを越える周波数で約250~約25000ワット/m<sup>2</sup>である。好ましくは、RF周波数は約13MHz~約80MHzである。一実施

10

20

30

40

50

形態においては、周波数、インピーダンス整合回路、又は順電力サーボでの周波数の調整による、ガス分布プレート64のダイナミックインピーダンス整合を行う。

#### 【0051】

別の実施形態においては、RFエネルギーをRFコイル82とガス分布プレート64に同時に供給することでHDP0処理を完了する。この場合、ガス分布プレート64とRFコイル82に供給されるRF電力は約0.3MHz～約10GHzを越える周波数で約250～約25000ワット/m<sup>2</sup>である。好ましくは、RF周波数は約13MHz～約80MHzである。RFコイル82とガス分布プレート64に供給されたRF電力の相互作用を回避するために、各デバイスに供給されるRF電力の周波数は意図的に若干異なるRF周波数にしてもよい。例えば、RFコイル82を約13.56MHzで作動させ、ガス分布プレートを約12.56MHz、あるいはその逆で駆動させる。

10

#### 【0052】

さらに別の実施形態において、RFエネルギーをRFコイル82及び／又はガス分布プレート64に供給しながら、基板238のRFバイアス印加又は接地を行う。この場合、ガス分布プレート64、RFコイル82、基板支持体238に供給されるRF電力は約0.3MHz～10GHzを越える周波数で約250～約25000ワット/m<sup>2</sup>である。好ましくは、RF周波数は約13MHz～約80MHzである。この場合、RFコイル82、基板支持体238、ガス分布プレート64に供給するRF電力を異なる周波数で駆動させることで、発生したRF磁場の相互作用によって引き起こされる望ましくない作用を軽減することも有益である。

20

#### 【0053】

HDP0処理中に発生したプラズマイオン密度は様々な処理パラメータ、例えば処理ガスやチャンバに導入されるガス混合物のタイプ、チャンバ圧、及び／又はガス又はガス混合物を励起するためにチャンバに供給するエネルギー（例えば、RF電力等）によって変化する。一実施形態において、HDP0処理ガスは酸素源を含有するガス、例えば純酸素ガス又はその他のガス、例えばヘリウム、水素、アルゴン、キセノン、クリプトン、又はその組み合わせと混合した酸素を含む。一実施形態においては、純粹酸素ガスのみを使用する。別の実施形態においては、H<sub>2</sub>Oをチャンバに注入し、酸化物成長過程を促進する。

30

#### 【0054】

一実施形態においては、HDP0処理中で使用する高密度プラズマを発生及び維持するために、酸素ガスと1つ以上のその他のガス（例えば、ヘリウム、アルゴン等）をチャンバ容量17に注入して約1mTorr～約0.5Torrのチャンバ圧を実現する。好ましくは、HDP0処理は酸素ガスとヘリウムを約3mTorr～約250mTorrで使用する。

#### 【0055】

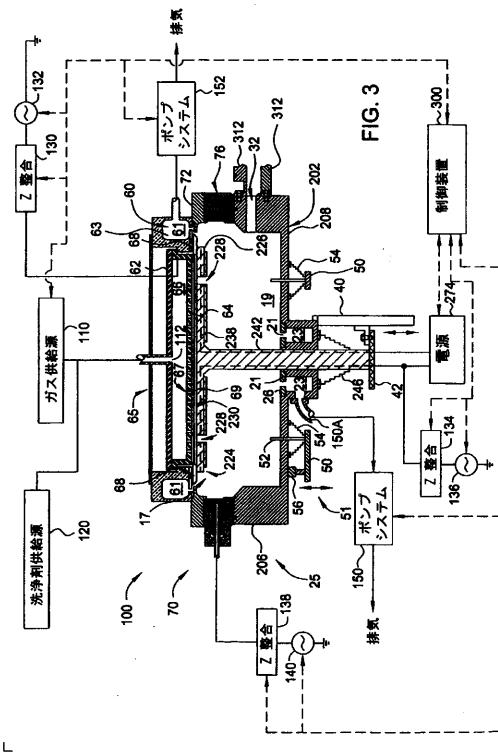

プラズマと基板表面240Aとの相互作用は、発生したプラズマ密度に影響される一方で、プラズマチャンバ内での位置や基板支持体238の非接地、接地、RFバイアス印加の影響も受ける。一般的に、プラズマ発生源から基板が遠ければ遠いほど、基板表面240Aの発生したプラズマとの反応は低い。高品質ゲート酸化物層を形成するのに最適な基板支持体の位置は基板表面でのプラズマ密度、基板表面に衝突するイオンエネルギー、処理温度、所望のチャンバ処理時間に依存する。図2はプラズマ処理チャンバの概略断面図であり、基板支持体は処理チャンバの中間位置にあり、これは一実施形態においてHDP0層を形成するに最適な位置である。図3はプラズマ処理チャンバの概略断面図であり、基板支持体はガス分布プレート64の表面に近接して位置されており、一実施形態においてはRF電力をガス分布プレート64に印加することで慣用のPECVD酸化物層を形成するに最適な位置である。HDP0層成長速度と処理の均一性は基板表面と発生したプラズマとの相互作用に影響されるため、基板支持体の処理位置はHDP0層処理处方で見出した処理変数に従って調整してもよい。最適なプラズマ処理位置はプラズマ処理チャンバの属性（例えば、チャンバサイズ、ポンプポートに対する基板位置その他）、基板表面に

40

50

相対した R F エネルギー伝達デバイスの構成に強く依存する。一実施形態においては、処理位置を、 H D P O 層処理工程中にプラズマイオン密度を調節するにつれ、処理位置を変える。図 2 は H D P O 酸化成長処理と H D P 堆積処理に好ましい位置を示す。図 3 は慣用の P E C V D 堆積処理に好ましい位置を示す。好ましい位置はチャンバ「間隔」としても知られる処理容量 18 の高さによって測定可能である。間隔は、例えば基板支持体 238 の基板支持表面 230 上に載置された基板 240 とガス分布プレート 240A との距離であるが、通常は基板表面 240A からガス分布プレート 64 (つまり、処理容量 18 の縁部) へ直角に測定した距離と定義される。一実施形態において、 H D P O 処理を 730 mm × 920 mm 基板上に施すために用いられる処理チャンバにおける間隔は、1 つ以上の R F エネルギー伝達デバイスを使用する場合、約 50 ~ 約 500 mm である。チャンバ間隔は基板サイズが上がるにつれ変化する。

10

#### 【 0056 】

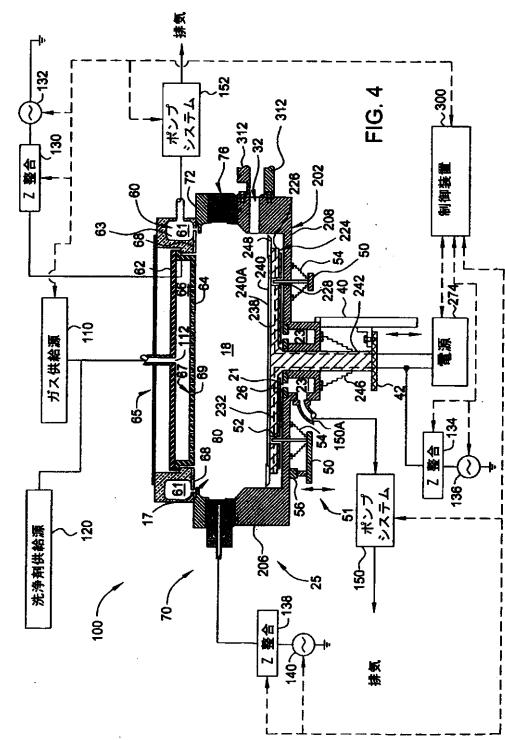

図 4 はプラズマ処理チャンバ 100 の一実施形態の概略断面図であり、基板支持体 238 はプラズマ処理チャンバの底部又はその近傍に位置している。この位置は、処理済みの基板を未処理のものと交換する際に使用する。

#### 【 0057 】

図 5 はプラズマ処理チャンバ 100 の一実施形態の概略断面図であり、処理チャンバ内の接地表面の表面積（基板支持体が接地された場合の接地チャンバ壁部表面 B1 と基板支持体表面 B3 を参照のこと）は、処理容量 18 と接觸している容量結合電極表面（つまり、 R F エネルギー伝達デバイス（ガス分布プレート表面 B2 及び / 又は基板支持体表面 B3 を参照のこと））に相対して増大しており、基板支持体が接地された場合に最適な基板バイアスを生み、発生したプラズマの均一性を改善し、基板を含む接地コンポーネントの衝突の強度を最小限とする。一実施形態において、基板支持体 238 は基板支持体 238 と R F 電源 136 との間に設置された阻止コンデンサ（図示せず）を有する R F 駆動電極である。この実施形態において、接地表面面積と R F 駆動電極表面面積との比は、 R F 駆動基板支持体を用いて H D P O 層を形成する又はプラズマ C V D 処理を用いて誘電体層を堆積する際に基板バイアスとプラズマ均一性が最適化されるように設計される。この実施形態において、ガス分布プレート 64 は接地され、接地した電極の総表面積と基板支持体表面積との比は好ましくは約 1 : 1 ~ 約 2 : 1 である。

20

#### 【 0058 】

半導体デバイスの製造における重要な要因は半導体デバイスの形成に関連する所有するコスト (cost of ownership:COO) である。 COO は数々の要因に影響されるが、チャンバのスループット又は単に高品質ゲート誘電体層の堆積に必要な処理時間に大きく影響される。ゲート酸化物層に必要な厚さは所望の T F T の電気的性能に依存する。特に、ゲート誘電体層は製造したトランジスタが所望の電気的性質を有するように高品質（例えば、フラットバンド電圧 ( $V_{fb}$ ) ）でなくてはならない。高品質なゲート誘電体層を実現するには、厚さ均一性が非常に高い (< 1 %) 良好的なゲート誘電体層を開発すること、及び所望のステップカバレッジの度合いと破壊電圧を得るに十分な厚みのゲート誘電体層を有することが重要である。所望のステップカバレッジと破壊電圧を実現するためのゲート誘電体層厚は典型的にはおよそ 1000 である。一実施形態において、 H D P O 処理成長速度は約 10 / 分である。従って、ありそうにないが成長速度を一定と仮定した場合、1000 の膜を成長させるには約 100 分かかる。100 分の処理時間ではプラズマ処理チャンバ 100 のスループットは認し難いほどに低くなり、その結果、クラスタツールの COO に悪影響を及ぼす。従って、ずっと薄い誘電体層を使用する、又は処理時間の短い多層スタックを使用する必要がある。

40

#### 【 0059 】

##### 化学気相成長処理

より採算に見合った高品質ゲート誘電体層を得るために、一部の実施形態においては、 H D P O 処理を行って良好なインターフェースを形成して、次に良好なバルク電気特性とより高い堆積速度を有する 1 つ以上の層を H D P O 層上に堆積する必要がある。一実施形

50

態においては、薄いH D P O処理層をチャネル上に形成して高品質の誘電体インターフェースを構成し、次に1つ以上の誘電体層をH D P O層上に堆積して高品質ゲート誘電体層を形成する。一実施形態においては、プラズマ処理チャンバのC O Oを最小限にするために、二段階ゲート酸化物形成処理を使用することができる。この実施形態においては、H D P O処理を行って良好なゲート誘電体層インターフェース(p-SiからH D P O層)を得た後に、H D P O処理より早い堆積速度を有する第2層をH D P O層上に堆積する。

#### 【0060】

一実施形態においては、高密度プラズマ(H D P) C V D堆積法を用いてゲート誘電体層4の残留厚さを堆積して、所望の物理的及び電気的要件を満たす膜を形成する。一実施形態においては、H D P C V D処理を完了するために、シリコン含有ガス又はガス混合物、及び酸素含有ガス又はガス混合物を図2に図示の構成のチャンバに導入する。次に、R Fコイル82と1つ又は双方のその他のR F源(例えば、ガス分布プレート64、基板支持体238等)を使用してH D P C V D酸化物膜を既存のH D P O層上に堆積する。別の実施形態においては、シリコン含有ガス(又はガス混合物)、酸素含有ガス及び/又は窒素含有ガスを用いてH D P処理を完了する。

#### 【0061】

一実施形態においては、T E O S堆積処理を用いてゲート誘電体層の残留厚さを堆積して所望の物理的及び電気的要件を満たす膜を形成する。730mm×920mmフラットパネルディスプレイ基板に使用する典型的なP E C V D T E O S処理の一例としては、約100sccmのキャリアガス(例えば、ヘリウム)と共に約600sccmのテトラエチルオキシシランと約7000sccmの酸素を総ガス圧約0.5~約3Tor r、基板温度約350~約550で流して発生させたプラズマに基板を曝露する方法が挙げられる。好ましくは、チャンバ圧は約1Tor rであり、基板温度は約400±50である。周波数約13.56MHzで約2000ワットのR F電力を基板処理間隔約10~約50mmで、約1500オングストローム/分の堆積速度を実現するには典型的にはガス分布プレート64から約15mmの間隔でガス分布プレートに供給する。T E O S堆積処理で形成した二酸化ケイ素は、一般的には半導体業界で金属間誘電膜として使用される。T E O S堆積処理は、典型的にはテトラエチルオルトリシリケート含有ガス混合物等の誘電体層形成ガスを用いて行って誘電体層を堆積する。T E O Sを用いて堆積するための典型的な方法の例が、1995年10月31日出願の米国特許第5462899号「SiO<sub>2</sub>を形成するための化学気相成長法」、及び2002年9月17日出願の米国特許第6451390号「パルスR Fプラズマを使用したT E O S酸化物堆積」にさらに記載されており、引用することで本願で請求の態様と開示に矛盾しない範囲で本願に組み込まれる。

#### 【0062】

図3はプラズマ処理チャンバ100の概略断面図であり、基板支持体238は基板240表面上へのプラズマC V D堆積を促進するためにガス分布プレート64に近接して位置されている。P E C V D又はH D P C V D堆積処理の均一性と堆積速度は基板表面と発生したプラズマとの相互作用に影響されるため、基板支持体の処理位置はプラズマC V D処理处方で見出した処理変数に従って調整してもよい。最適なプラズマ処理位置はプラズマ処理チャンバの属性(例えば、チャンバサイズ、ポンプポートに対する基板位置その他)、基板表面に相対したR Fエネルギー伝達デバイスの構成に強く依存する。一実施形態においては、プラズマイオン密度をプラズマ処理工程中に調整するにつれ、処理位置を変える。

#### 【0063】

アーク放電、プラズマによるチャンバコンポーネントの損傷を回避、及び/又は電力損失や基板支持体238及びチャンバ基部202への誘電体材料の不要な堆積を最小限にするためには、下部容量19におけるプラズマ発生又はコンポーネントとの相互作用を最小限にする必要がある。典型的には、プラズマ処理チャンバはチャンバ容量17における望ましくない領域でのプラズマ発生を防止するように設計されているが、一般的に用いられる技法はチャンバコンポーネント間又は大面積基板(例えば、>2000cm<sup>2</sup>)の処理

10

20

30

40

50

に使用するコンポーネント間での相対運動が可能なチャンバには適用できない。大面積基板には、大気と真空との界面にあるコンポーネントに高大気圧が与える影響、R F 設置によるチャンバ複雑度の上昇、及び基板サイズによる熱均一性への懸念、及び／又はこういった大コンポーネントの部品コスト高といった特有の問題がある。こういった問題を解決するために、一実施形態においては、基板支持体 238 とチャンバ基部 202 との相対運動が可能な物的障壁（図示せず）を取り付けることで下部容量 19 でのプラズマの漏れや発生を防止又は阻止している。この実施形態において、物的障壁はチャンバ底部 208 と可動式基板支持体 238 の表面に取り付け可能である。一実施形態において、物的障壁は導電性、好ましくは金属のベロー又は可撓性導線メッシュ又はグリッドであり、プラズマの発生を防止可能なように取り付けられている。別の実施形態においては、下部容量 19 の個々のコンポーネント（図示せず）の遮断がその表面への堆積やプラズマとの相互作用を最小限にするにあたって有益である。別の実施形態においては、真空ポンプシステム 152 及び／又は真空ポンプシステム 150 の排気速度（例えば、ポンプ速度と処理容量 18 と下部容量 19 との間のコンダクタンス）を制御して処理容量 18 から下部容量 19 へのガス流が最小限になるよう制御し、プラズマ衝突と化学反応の影響を最小限にする。

10

#### 【0064】

プラズマ処理チャンバ 100 における表面から不要な堆積物を除去するためには、投入ポート 112 に連結された洗浄剤供給源 120 からの洗浄ガスを用いてチャンバ容量 17 のコンポーネント上の堆積物を除去する。洗浄剤供給源 120 は、典型的には、解離フッ素等のチャンバ容量 17 に導入する洗浄剤を供給する。

20

#### 【0065】

##### クラスタツール装置及びウェハシーケンス

本発明の態様は、高品質ゲート誘電体層を堆積可能な少なくとも 1 つのプラズマ処理チャンバ 100 を含むクラスタツール 310 も提供する。クラスタツール 310 は基板の予備加熱、処理に先立っての基板表面の洗浄等の予備処理工程と、処理後のアニーリングや冷却といった後処理工程の双方を 1 つの制御環境内で全てサポートしている点で有利である。制御環境を使用してのゲート誘電体層の堆積は高品質ゲート誘電体層の形成における重要な側面であり、これは別々のチャンバ又は、さらに悪くは別々のシステムを用いて HDP O 層と誘電体層を堆積する場合、HDP O 層と誘電体層堆積工程間での基板表面の大気汚染への曝露が、形成されるゲート層の電気特性の劣化につながる可能性があるからである。また、アニーリング、予備洗浄及び／又は予備加熱チャンバ（全て以下にて記載）のクラスタツールへの組み込みにより、これらの処理を大気汚染源への曝露を伴わずに完了する、あるいは HDP O 層及び／又は誘電体層堆積処理の直前又は直後に完了するならば、形成されるゲート誘電体層 4 の欠陥の発生が軽減される。

30

#### 【0066】

図 8 は、プラズマ処理チャンバ 100 を組み込んだ代表的なクラスタツール 310 である。クラスタツール 310 は基板 240 を空気に曝露することなく処理するために使用可能なクラスタツールを表す。クラスタツール 310 は中央搬送チャンバ 312 を含み、中央搬送チャンバ 312 にはロードロック／冷却チャンバ 314A、314B、予備加熱チャンバ 302、処理チャンバ 340、342、344、346 が連結されている。中央搬送チャンバ 312、ロードロック／冷却チャンバ 314A、314B、予備加熱チャンバ 302、及び処理チャンバ 340、342、344、346 は共に密閉され閉鎖環境を形成し、システムは内部圧力約 10 mTorr ~ 約 1 Torr で作動される。ロードロック／冷却チャンバ 314A と 314B は、基板 240 をクラスタツール 310 に搬送するための、装填扉 316A、316B をそれぞれ備えた閉鎖可能な開口部を有している。基板 240 は基板格納位置 38A-D の 1 つからロードロック／冷却チャンバ 314A 又は 314B のいずれかへと大気口ボット（図示せず）を用いて搬送される。

40

#### 【0067】

ロードロック／冷却チャンバ 314A と 314B は、基板を支持、冷却するための複数の棚を取り付けたカセット 317 をそれぞれ備える。ロードロック／冷却チャンバ 314

50

のカセット317は棚一段の高さごとに徐々にカセット317を上昇・下降させるための昇降アセンブリ(図示せず)上に載置されている。チャンバ314に基板を装填するためには、装填扉を開放し、基板240をロードロック/冷却チャンバ314Aのカセット317の棚の1つに設置する。続いて、昇降アセンブリがカセット317を棚一段分上げることで、装填扉316Aに空の棚が対向する。別の基板を空の棚上に配置し、この工程をカセット317の全ての棚が埋るまで繰り返す。この時点では、装填扉316Aを閉鎖し、ロードロック/冷却チャンバ314Aをクラスタツール310の圧力まで排気する。

#### 【0068】

中央搬送チャンバ312に隣接した、ロードロック/冷却チャンバ314Aの内壁上のスリットバルブ320Aを次に開放する。基板240を中央搬送チャンバ312内のロボット322により予備加熱チャンバ302に搬送し、ここで基板を所望の温度にまで予備加熱する。一実施形態においては、基板240を予備加熱チャンバ302内で約250~約450まで加熱する。別の実施形態においては、基板240をロードロック/冷却チャンバ314で約250~約450まで予備加熱するため、予備加熱チャンバ302はこの機能を実行する必要がない。制御装置300によって制御されたロボット322を用いて、基板をロードロック/冷却チャンバ314Aのカセット317から引き出して予備加熱チャンバカセット329に挿入した後に撤退すると、予備加熱チャンバ302の棚上には基板が残る。典型的には、予備加熱チャンバカセット329は予備加熱チャンバ302内の昇降アセンブリ(図示せず)上に載置される。棚の一つに基板を装填後、予備加熱チャンバカセット329を上昇又は下降させて、ロボット322がアクセスする別の空の棚を表に出す。続いて、ロボット322はロードロック/冷却チャンバ314Aのカセット317から別の基板を回収する。

#### 【0069】

同様のやり方で、ロボット322は予備加熱チャンバカセット329から4つの処理チャンバ340、342、344、346のうちの1つへと全て又は一部の基板240を搬送する。各処理チャンバ340、342、344、346には、任意で、その内壁340A、342A、344A、346Aにそれぞれ関連するスリットバルブ341、343、345、又は347を処理ガスの隔離のために取り付けられている。一実施形態において、上述したように、処理チャンバ340、342、346はプラズマ処理チャンバ100である。この構成におけるプラズマ処理チャンバはHDP層の形成及び高品質ゲート酸化物層の慣用のPECVD堆積処理を全て同一のチャンバ内で行うことが可能である。この実施形態により基板のスループット(例えば、時間あたりの基板処理枚数)は向上し、これはクラスタツール310内のHDPとPECVDチャンバ間でのロボット322のハンドオフ回数が大幅に減少するからである。また、この実施形態は、多くの異なるタイプの処理チャンバと処理チャンバ構成をクラスタツール310に取り付けて、処理シーケンスのボトルネックの解消を促進することが可能である。別の実施形態においては、HDP処理をクラスタツールシステムの第1チャンバで完了し、第2誘電体堆積工程をクラスタツールシステムの第2処理チャンバで完了する。この実施形態においては、第1モジュール(例えば処理チャンバ340)は上述したHDP処理を実行するよう構成されており、第2モジュール(例えば、処理チャンバ342)は誘電体層を堆積するHDP-CVD又はPECVD反応装置として構成される。この実施形態においては、次のモジュール(例えば、処理チャンバ342)で基板240に誘電体層を適用する前に、HDP層を基板240上で成長させる。一実施形態においては、基板240を次のモジュール(例えば、処理チャンバ342)で処理するに先立って、基板240を第1モジュール(例えば、処理チャンバ340)から予備加熱チャンバ302へと搬送する。基板は、次のモジュールで処理する前に予備加熱チャンバで約250~約450に加熱される。

#### 【0070】

基板240を処理チャンバ340、342、344、346の少なくとも1つで処理した後、基板をロードロック/冷却チャンバ314Bのカセット317に搬送する。基板は、カセット317に載せられた基板から熱を取り除く冷却面の使用により冷却チャンバ内

10

20

30

40

50

で冷却される。冷却面は、冷却面に取り付けられた熱交換器を流れる慣用の熱交換流体を用いて冷却される。典型的には約20～約150の所望の温度に基板が一旦達したら、開放した装填扉316Bを通してチャンバ314Bから基板を除去し、基板格納位置38A-Dの1つに配置する。

#### 【0071】

クラスタツール310の一実施形態において、クラスタツール310は処理チャンバ340、342、344、346位置、又は予備加熱チャンバ329位置の1つに取り付けられた少なくとも1つの予備洗浄チャンバを含む。予備洗浄チャンバをシステムに加えることで、ゲート誘電体層4の堆積に先立って、不要な物質（例えば、表面酸化物、汚染物その他）を除去する。予備洗浄処理はプラズマ洗浄処理であり、酸化物及びその他の汚染物質は光スパッタエッチング及び/又はプラズマエッチング化学反応（例えば、NF<sub>3</sub>、CF<sub>3</sub>その他）の使用により基板表面から除去される。予備洗浄処理は、典型的には不活性ガス（例えば、アルゴン、キセノン、クリプトン等）を用いて、また約0.3MHz～10GHzを越えるRF周波数で駆動される誘導及び/又は容量結合プラズマを用いて完了する非選択的RFプラズマエッチング処理である。予備洗浄処理を行うために必要なRF電力は、チャンバのサイズ、所望の予備洗浄エッチング速度、基板バイアス電圧に強く依存する。予備洗浄処理は、予備加熱工程の前又は後であるがプラズマ処理工程に先立つてクラスタツール310処理シーケンスに追加してもよい。一実施形態においては、予備加熱及び予備洗浄処理を同一チャンバ内で完了される。別の実施形態においては、この予備加熱処理はプラズマ処理チャンバで完了され、予備洗浄工程は予備加熱工程に先立つて完了される。別の実施形態においては、予備洗浄処理は処理に先立つてプラズマ処理チャンバ100でインシチュで行われる。さらに別の実施形態においては、予備洗浄及び予備加熱処理は処理に先立つてプラズマ処理チャンバ100でインシチュで行われる。あるいは、別の実施形態においては、基板240を、クラスタツール310に挿入する前に、HF、NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>、HNO<sub>3</sub>又はHClを含有する水溶液又は弱アルカリ性溶液等の湿式化学洗浄剤を用いて洗浄することが可能である。クラスタツールの制御環境下における予備洗浄チャンバの使用は、高品質ゲート酸化物層の形成における重要な側面であり、これは予備洗浄処理を完了後かつHDP層形成前での、p-Siソース、ドレイン、チャネル表面の大気汚染への曝露がゲート層の電気特性の劣化にもつながり、結果として予備洗浄処理の目的が無と化す可能性があるからである。10

20

30

#### 【0072】

クラスタツール310の一実施形態において、クラスタツール310は、処理チャンバ340、342、344、346位置又は予備加熱チャンバ329位置の1つに取り付けられた少なくとも1つのアニーリングチャンバを含む。アニーリングチャンバをシステムに追加することで、ゲート誘電体層形成中に発生する欠陥数が低減される。アニーリング処理は熱処理であり、基板を約400～約550で所望の時間にわたってアニーリングチャンバで処理する。アニーリング工程は窒素、不活性ガス、又は窒素と水素の混合物、例えば窒素95%と水素5%を含有する雰囲気中で実施してもよい。また、アニーリング処理は真空下で行ってもよい。アニーリング工程は約5分～約30分、例えば約10分行ってもよい。スループットを向上させるために、2つ以上のアニーリングチャンバを設置することが望ましい。アニーリング工程完了後、基板240を冷却/ロードロックチャンバ314A-Bの1つに搬送して、取扱い温度まで冷却する。アニーリング処理を実施するための模範的な方法とクラスタツール内の模範ハードウェア構成は、2001年9月10日出願の米国特許第6610374号「大面積ガラス基板のアニーリング方法」にさらに記載されており、引用することで本願で請求の態様と開示に矛盾しない範囲で本願に組み込まれる。クラスタツールの制御環境下におけるアニーリングチャンバの使用は高品質ゲート酸化物層の形成における重要な側面であり、これはゲート誘電体層形成処理直後のアニーリング工程の実行により、ゲート誘電体層への内的応力と外的応力に起因する損傷を軽減することが可能なためである。40

#### 【0073】

上記は本発明の実施形態についてのものであるが、本発明の基本的な範囲から逸脱することなく本発明のその他及びさらに別の実施形態を考案することができ、本発明の範囲は特許請求の範囲に基づいて定められる。

【図面の簡単な説明】

【0074】

その幾つかは添付の図面で図示されている実施形態を参照して上記で簡単に概要を述べた本発明のさらに詳しい説明を得ることで、本発明の上述した特徴が詳細に理解可能であるものとする。しかしながら、添付の図面は本発明の典型的な実施形態を図示するに過ぎず、本発明はその他の同等に効果的な態様も認め得るため、本発明の範囲を制限するものと捉えられるものではないことに留意しなくてはならない。

10

【図1】従来の单一薄膜トランジスタ構造の概略図である。

【図2】本願に記載の実施形態を実施するために使用し得るプラズマ処理チャンバの断面図であり、基板支持体が低処理位置にある。

【図2A】～

【図2B】本願に記載の実施形態を実施するために使用し得る図2～4に図示の誘導結合ソースアセンブリの断面図である。

【図3】本願に記載の実施形態を実施するために使用し得るプラズマ処理チャンバの断面図であり、基板支持体が最上部処理位置にある。

【図4】本願に記載の実施形態を実施するために使用し得るプラズマ処理チャンバの断面図であり、基板支持体が基板交換位置にある。

20

【図5】本願に記載の実施形態を実施するために使用し得るプラズマ処理チャンバの断面図であり、プラズマ処理チャンバにおける接地表面の表面積が図2～4に図示の実施形態より広い。

【図6】本願に記載の実施形態を実施するために使用し得るプラズマ処理チャンバの上面図である。

【図7】本願に記載の実施形態を実施するために有用なチャンバの等角図である。

【図8】本発明の一実施形態による高品質ゲート酸化物層を処理するためのクラスタツールを示す図である。

【図1】

FIG. 1

(従来技術)

【図2】

【 义 3 】

【 四 4 】

【 义 5 】

【 义 6 】

【図7】

FIG. 7

【図8】

FIG. 8

---

フロントページの続き

(51)Int.Cl.

F I

H 01 L 29/78 617 U

H 01 L 29/78 617 V

合議体

審判長 鈴木 正紀

審判官 井上 茂夫

審判官 川端 修

(56)参考文献 特開平4-264715(JP,A)

特開2002-299339(JP,A)