DEUTSCHE DEMOKRATISCHE REPUBLIK

(12) Wirtschaftspatent

## PATENTSCHRIFT

(19) DD (11) 200 062 1

B1Teilweise bestätigt gemäß § 18 Absatz 1

Patentgesetz

4(51) H 03 M 7/12

## AMT FÜR ERFINDUNGS- UND PATENTWESEN

---

|      |                       |      |          |      |          |

|------|-----------------------|------|----------|------|----------|

| (21) | WP H 03 M / 231 350 8 | (22) | 01.07.81 | (45) | 12.03.86 |

|      |                       |      |          | (44) | 09.03.83 |

---

(71) siehe (72)

(72) Hempel, Wolf-Georg, Dipl.-Ing., 9044 Karl-Marx-Stadt, Stollberger Straße 62; Hoffmann, Steffen, DD

---

(54) Einrichtung zur Umsetzung einer Dualzahl

---

ISSN 0433-6461

6 Seiten

Vorlage nicht besser kopierfähig

b

**Erfindungsanspruch:**

1. Einrichtung zur Umsetzung einer Dualzahl in eine binär kodierte Dezimalzahl, mit einem als Umsetzungstabelle eingesetzten Speicher, dessen Speicherplätze über mehrere Eingabeleitungen durch einen von der Dualzahl bestimmten Eingabekode adressiert werden und anteilig in dem von der Dezimalzahl bestimmten Ausgabekode eine Speicherplatzgruppe bilden, und mit einer Mehrzahl von Ausgabeleitungen, denen jeweils eine Binärwertigkeit innerhalb einer Tetrade des Ausgabekodes zugeordnet ist, unter Verwendung eines Rechenwerks zur Addition zweier einstelligen binär kodierter Dezimalzahlen, mit einem ersten 4-Bit-Volladdierer, einer Übertragsschaltung, die den Dezimalübertrag bildet und ausgibt, und mit einem zweiten 4-Bit-Volladdierer, der bei vorhandenem Dezimalübertrag einen Korrektursummanden verrechnet, gekennzeichnet dadurch, daß die Eingabeleitungen für die Wertigkeiten  $2^0$  bis  $2^2$  der Dualzahl auf die Wertigkeitsgleichen ersten Summationseingänge des ersten 4-Bit-Volladdierers (3) geführt sind, die Ausgabeleitungen für die Dezimale  $10^0$  mit den Wertigkeitszugeordneten zweiten Summationseingängen des ersten 4-Bit-Volladdierers (3) verbunden sind, der für die Wertigkeit  $2^3$  zuständige erste Summationseingang des ersten 4-Bit-Volladdierers (3) ständig mit dem Summanden Null beaufschlagt ist, ein gesonderter Adressiereingang des Speichers (1) mit dem Ausgang der Übertragsschaltung (4) verbunden und parallel zu jeder durch die Dual-Eingänge des Speichers (1) adressierbaren Speicherplatzgruppe eine von diesem gesonderten Adressiereingang aktivierbare Übertrags-Speicherplatzgruppe vorgesehen ist.

2. Einrichtung nach Punkt 1, gekennzeichnet dadurch, daß die Speicherplatzgruppen und Übertrags-Speicherplatzgruppen auf mehrere Teilspeicher aufgeteilt sind.

3. Einrichtung nach den Punkten 1 und 2, gekennzeichnet dadurch, daß die in einem der Teilspeicher enthaltenen Teile der Speicherplatzgruppen und Übertrags-Speicherplatzgruppen mit den Ausgabeleitungen für zwei benachbarte Dezimalstellen der Dezimalzahl verbunden sind.

4. Einrichtung nach den Punkten 1 bis 3, gekennzeichnet dadurch, daß einer der Teilspeicher für einen wiederholt verwendbaren Komplex benachbarter Speicherplatzgruppen und Übertrags-Speicherplatzgruppen vorgesehen und in Abhängigkeit von der umzusetzenden Dualzahl ansteuerbar ist.

Hierzu 1 Seite Zeichnungen

**Anwendungsgebiet der Erfindung**

Das Anwendungsgebiet der Erfindung erstreckt sich auf die Umsetzung einer Dualzahl in eine binär kodierte Dezimalzahl mittels eines als Umsetzungstabelle eingesetzten Speichers. Die Speicherplätze des Speichers werden dabei über mehrere Eingabeleitungen durch den von der Dualzahl bestimmten Eingabekode adressiert und bilden anteilig in dem von der Dezimalzahl bestimmten Ausgabekode eine Speicherplatzgruppe. Jeder der Ausgabeleitungen ist eine Binärwertigkeit innerhalb einer Tetrade des Ausgangskodes zugeordnet. Verwendet wird außerdem ein Rechenwerk zur Addition zweier einstelligen binär kodierter Dezimalzahlen. Es enthält einen ersten 4-Bit-Volladdierer, eine Übertragsschaltung, die den Dezimalübertrag bildet und ausgibt, sowie einen zweiten 4-Bit-Volladdierer, der bei vorhandenem Dezimalübertrag einen Korrektursummanden verrechnet.

**Charakteristik der bekannten technischen Lösungen**

Aus DE-AS 2513262 ist bekannt, daß eine digitale Kode-Umwandlungsanordnung mittels eines Speichers ausgeführt werden kann, der als Umwandlungstabelle dient.

Der Speicher wird durch den Eingabekode adressiert, die gewünschten Ausgabekodes sind an den adressierten Stellen gespeichert.

Wird als Eingabekode eine Dualzahl verwendet, dann ist die Anzahl der darstellbaren unterschiedlichen Adressen von der kodeabhängig höchsten Dualzahl bestimmt. Beispielsweise sind für den dualen Zahlenbereich zwischen 00000 und LLLL entsprechend den zugehörigen Binärwertigkeiten  $2^0$  bis  $2^4$  insgesamt 32 unterschiedliche Adressen aufstellbar, mit denen 32 verschiedene Speicherplatzgruppen angesteuert werden können.

In jeder Speicherplatzgruppe kann ein Bitmuster beliebigen Umfangs gespeichert sein, das den Ausgabekode bildet. Wird als Ausgabekode der 1-2-4-8-BCD-Kode verwendet, dann ist er aus Tetraden zusammengesetzt. Bei einem umzusetzenden Zahlenbereich des genannten Umfangs kämen insgesamt zwei Tetraden in Betracht, mit denen die Dezimalstellen  $10^0$  und  $10^1$  erfaßt werden.

Jede Erweiterung der umzusetzenden Dualzahl um eine Binärwertigkeit verdoppelt die Anzahl der benötigten Speicherplatzgruppen und erhöht den Aufwand für die Adressenentschlüsselung. So ist es erklärlich, daß bei der Umsetzung schon einer Dualzahl mittlerer Größe in eine binär kodierte Dezimalzahl der Lösungsweg mittels Speicher als Umwandlungstabelle nur geringe praktische Bedeutung erlangte, obwohl mit dem gegebenen minimalen Umsetzungsweg eine kurze Umsetzzeit verbunden ist.

Weiterhin bekannt ist ein Rechenwerk zur Addition zweier einstelligen binär kodierter Dezimalzahlen. Die beiden Dezimalzahlen werden zunächst einem ersten 4-Bit-Volladdierer zugeführt. Eine Übertragsschaltung erkennt, ob die gebildete Summe einen Dezimalübertrag einschließt. Im zutreffenden Fall wird ihr Ausgangssignal dazu verwendet, zur gebildeten Summe einen Korrektursummanden hinzu zu addieren, wodurch die binär kodierte Dezimalzahl auch in der Tetrade für die Dezimale  $10^0$  richtig wird. Diesen letzten Teil des Vorgangs erledigt ein zweiter 4-Bit-Volladdierer (TTL-Handbuch).

**Ziel der Erfindung**

Als Ziel der Erfindung soll erreicht werden, daß die Umsetzung einer Dualzahl in eine binär kodierte Dezimalzahl kostengünstiger durchgeführt wird.

### Darlegung des Wesens der Erfindung

Der in der Charakteristik der bekannten technischen Lösungen beschriebene Mangel hat seine Ursache in der Behandlung der Dualzahl als einheitlicher, aus mehreren Binärwertigkeiten zusammengesetzter Block.

Um diese Ursache zu beseitigen, liegt der Erfindung die Aufgabe zugrunde, eine Einrichtung zur Umsetzung einer Dualzahl in eine binär kodierte Dezimalzahl, mit einem als Umsetzungstabelle eingesetzten Speicher, dessen Speicherplätze über mehrere Eingabeleitungen durch einen von der Dualzahl bestimmten Eingabekode adressiert werden und anteilig in dem von der Dezimalzahl bestimmten Ausgabekode eine Speicherplatzgruppe bilden, und mit einer Mehrzahl von Ausgabeleitungen, denen jeweils eine Binärwertigkeit innerhalb einer Tetrade des Ausgabekodes zugeordnet ist, unter Verwendung eines Rechenwerks zur Addition zweier einstelliger binär kodierter Dezimalzahlen, mit einem ersten 4-Bit-Volladdierer, einer Übertragsschaltung, die den Dezimalübertrag bildet und ausgibt, und mit einem zweiten 4-Bit-Volladdierer, der bei vorhandenem Dezimalübertrag einen Korrektursummanden verrechnet, zu schaffen, die bei gleichbleibend kurzer Umsetzzeit eine verringerte Anzahl von Speicherplätzen beansprucht.

Erfindungsgemäß wird das dadurch erreicht, daß die Eingabeleitungen für die Wertigkeiten  $2^0$  bis  $2^2$  der Dualzahl auf die wertigkeitsgleichen ersten Summationseingänge des ersten 4-Bit-Volladdierers geführt sind, die Ausgabeleitungen für die Dezimale  $10^0$  mit den wertigkeitszugeordneten zweiten Summationseingängen des ersten 4-Bit-Volladdierers verbunden sind, der für die Wertigkeit  $2^3$  zuständige erste Summationseingang des ersten 4-Bit-Volladdierers ständig mit dem Summanden Null beaufschlagt ist, ein gesonderter Adressiereingang des Speichers für die Übernahme des Dezimalübertrags verfügbar ist, zugehörig zu jeder Speicherplatzgruppe jeweils eine Übertrags-Speicherplatzgruppe vorgesehen ist, die Übertrags-Speicherplatzgruppe vom Dezimalübertrag anstelle der zugeordneten Speicherplatzgruppe adressierbar ist, die Speicherplatzgruppen mit einem durch die Zahlen  $(0 \dots n) \cdot 2^3$  bestimmten Inhalt versehen sind und jede Übertrags-Speicherplatzgruppe mit einem um 10 erhöhten Inhalt gegenüber dem Inhalt der zugeordneten Speicherplatzgruppe versehen ist.

Als vorteilhaft erweist sich, wenn die Speicherplatzgruppen und Übertrags-Speicherplatzgruppen auf mehrere Teilspeicher aufgeteilt sind.

Ein weiterer Vorteil besteht darin, daß die in einem der Teilspeicher enthaltenen Teile der Speicherplatzgruppen und Übertrags-Speicherplatzgruppen mit dem Inhalt zweier benachbarter Dezimalstellen der Dezimalzahl versehen sind. Schließlich wird eine besonders vorteilhafte Ausgestaltung der Lösung dadurch erreicht, daß die Anzahl der für die Dezimalstellen  $10^0$  und  $10^1$  zuständigen Teile der Speicherplatzgruppen und Übertrags-Speicherplatzgruppen durch die auszugebende Dezimalzahl 192 begrenzt, diese begrenzte Anzahl ab der auszugebenden Dezimalzahl 200 wiederholt verwendbar und eine Erkennungsschaltung zur Ansteuerung dieser Teile der Speicherplatzgruppen und Übertrags-Speicherplatzgruppen in Abhängigkeit von der umzusetzenden Dualzahl vorgesehen ist.

Die erfindungsgemäße Einrichtung reduziert die erforderliche Anzahl der Speicherplatzgruppen bei Anrechnung der Übertrags-Speicherplatzgruppen auf 25% des bisherigen Bedarfs.

### Ausführungsbeispiel

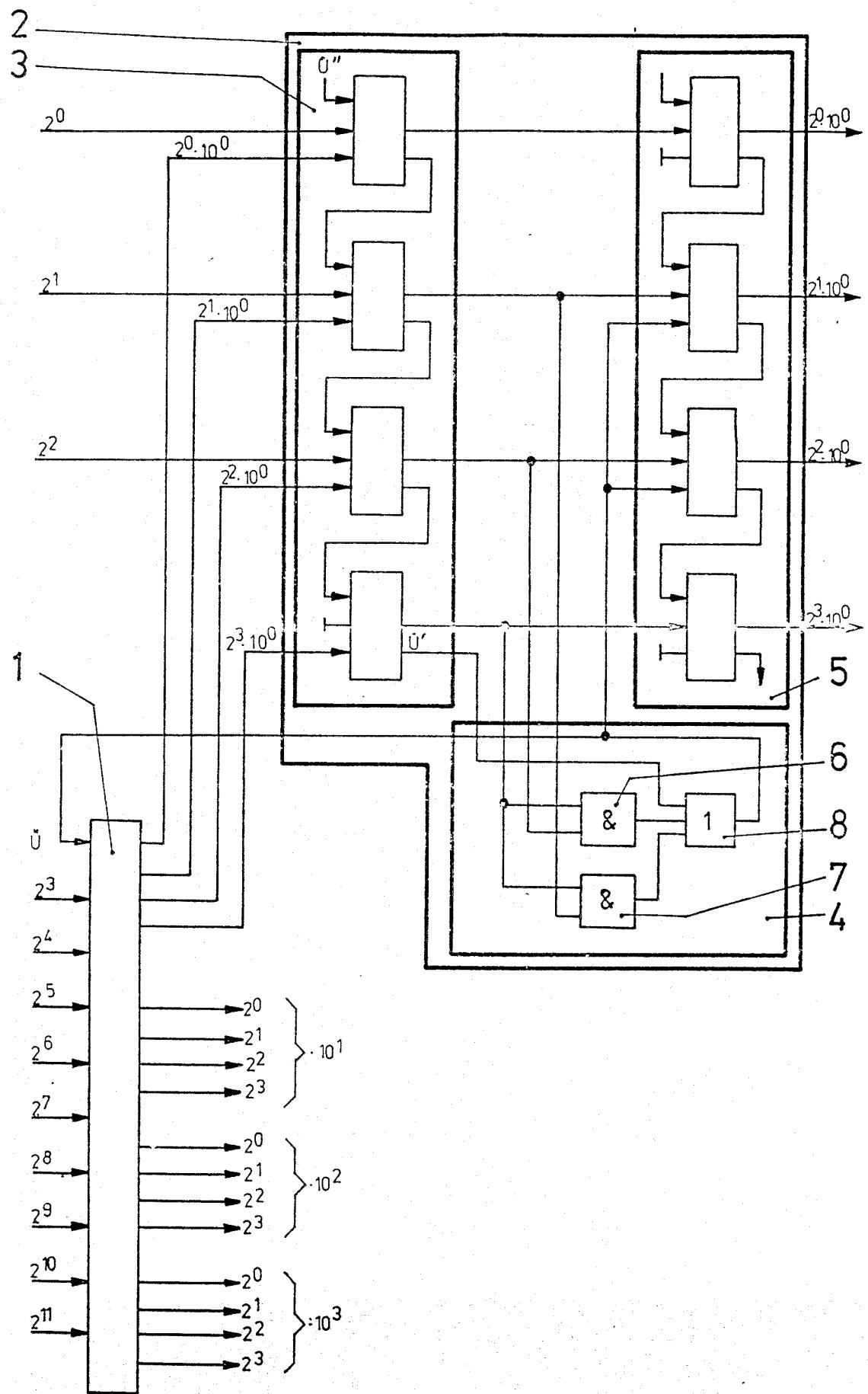

Die erfindungsgemäße Einrichtung wird anhand eines Ausführungsbeispiels näher erläutert, dessen zugehöriges Blockschaltbild in der Figur dargestellt ist.

Die Steuereinrichtung besteht aus einem Speicher 1 und aus einem Rechenwerk 2, das sich aus einem ersten 4-Bit-Volladdierer 3, einer Übertragsschaltung 4 und einem zweiten 4-Bit-Volladdierer 5 zusammensetzt. Die Übertragsschaltung 4 enthält ein erstes UND-Glied 6, ein zweites UND-Glied 7 und ein ODER-Glied 8.

Die zur Umsetzung beispielhaft vorgesehene Dualzahl umfaßt die Wertigkeiten  $2^0$  bis  $2^{11}$ . Jede dieser Wertigkeiten wird über je eine Eingabeleitung zugeführt. Die Eingabeleitungen für die Wertigkeiten  $2^3$  bis  $2^{11}$  verlaufen zum Speicher 1. Die Eingabeleitungen für die Wertigkeiten  $2^0$  bis  $2^2$  umgehen den Speicher 1 und sind statt dessen auf die wertigkeitsgleichen ersten Summationseingänge des ersten 4-Bit-Volladdierers 3 geführt.

Der für die Wertigkeit  $2^3$  vorgesehene erste Summationseingang des ersten 4-Bit-Volladdierers 3 ist ständig mit dem Summanden Null beaufschlagt.

Die im Ergebnis der Umsetzung entstandene Dezimalzahl ist in jeder Dezimale, deren Anzahl vom Umfang der Dualzahl abhängt und beim vorliegenden Umfang auf vier Dezimale begrenzt ist, mittels einer Tetrade binär kodiert. Die vom Speicher 1 ausgehenden vier Ausgabeleitungen der Tetrade für die Dezimale  $10^0$  sind mit den wertigkeitszugeordneten zweiten Summationseingängen des ersten 4-Bit-Volladdierers 3 verbunden.

Die Übertragsschaltung 4 ist nicht nur in bekannter Weise im Rechenwerk 2 eingebunden, sondern ausgangsseitig zusätzlich auf einen gesonderten Adressiereingang des Speichers 1 geführt.

Der Speicher 1 enthält eine Vielzahl von Speicherplatzgruppen. Ihre Anzahl ist für den gewählten Fall der eingangsseitig anliegenden Wertigkeiten  $2^3$  bis  $2^{11}$  für die Dualzahl gleich derjenigen Anzahl, die vom Wertigkeitsumfang  $2^0$  bis  $2^8$  erfaßt wird, also 512. Jeder Speicherplatzgruppe ist eine Übertrags-Speicherplatzgruppe zugeordnet, so daß außerdem 512 Übertrags-Speicherplatzgruppen existieren. Das sind 25% der für den umzusetzenden Dualzahlenumfang von  $2^{12} = 4096$  normalerweise erforderlichen Bedarf.

Die erste Speicherplatzgruppe enthält entsprechend der ersten umzusetzenden Dualzahl Null die binär kodierte Dezimalzahl Null. Die zweite Speicherplatzgruppe enthält die binär kodierte Dezimalzahl 8, jede weitere Speicherplatzgruppe die um jeweils 8 erhöhte binär kodierte Dezimalzahl.

Der Inhalt einer Übertrags-Speicherplatzgruppe ist für den Fall, daß zwischen dem Inhalt der zugeordneten Speicherplatzgruppe und dem Inhalt der nächstfolgenden Speicherplatzgruppe ein Dezimalübertrag vorliegt, gegenüber dem Inhalt der zugeordneten Speicherplatzgruppe um 10 erhöht. So beträgt die für die Speicherplatzgruppe mit dem Inhalt 24 der Inhalt der zugeordneten Übertrags-Speicherplatzgruppe 34. Liegt zwischen dem Inhalt einer Speicherplatzgruppe und dem Inhalt der nächstfolgenden Speicherplatzgruppe kein Dezimalübertrag vor, dann wird die Übertrags-Speicherplatzgruppe im Grunde genommen überhaupt nicht benötigt. Erfolgt ihr Einsatz trotzdem, aus welchen Gründen auch immer, dann beträgt ihr Inhalt Null. Das ist beispielsweise dann gegeben, wenn die zugeordnete Speicherplatzgruppe den Inhalt 40 aufweist.

Die nachfolgende Tabelle zeigt in der besser leserlichen nicht binär kodierten Dezimaldarstellung und eingeschränkt auf die drei kleinsten Dezimalen  $10^0$ ,  $10^1$  und  $10^2$  den Inhalt der ersten 30 Speicherplatzgruppen in den ungeradzahligen Spalten und den kleinsten Dezimalen  $10^0$ ,  $10^1$  und  $10^2$  den Inhalt der ersten 30 Speicherplatzgruppen in den geradzahligen Spalten. Inhalt der jeweils zugeordneten 30 Übertrags-Speicherplatzgruppen in den geradzahligen Spalten.

000 000 008 018 016 026 024 034 032 000

040 000 048 058 056 066 064 074 072 000

080 000 088 098 096 106 104 114 112 000

120 000 128 138 136 146 144 154 152 000

160 000 168 178 176 186 184 194 192 000

200 000 208 218 216 226 224 234 232 000

Es zeigt sich, daß in den beiden kleinsten Dezimalen  $10^0$  und  $10^1$  eine Wiederholung des Inhalts der Speicherplatzgruppen und zugeordneten Übertrags-Speicherplatzgruppen eintritt. Aus dieser Sachlage heraus ist es in einer speziellen Ausgestaltung des Ausführungsbeispiels möglich, den Speicher 1 in zwei Teilspeicher aufzuteilen, den ersten Teilspeicher für die Dezimalen  $10^0$  und  $10^1$  sowie den zweiten Teilspeicher für die Dezimalen  $10^2$  und  $10^3$  vorzusehen. Dabei kann der erste Teilspeicher auf je 25 Speicherplatzgruppen und Übertrags-Speicherplatzgruppen begrenzt werden. Notwendig wird dann eine Erkennungsschaltung, die aus der umzusetzenden Dualzahl die Mehrfachnutzung der Speicherplatzgruppen und Übertrags-Speicherplatzgruppen ableitet.

Die Wirkungsweise der Einrichtung ist wie folgt:

Soll erstens die Zahl 17 umgesetzt werden, dann lautet die Dualzahl unter vollständiger Berücksichtigung der Wertigkeiten  $2^0$  bis  $2^3$

00000000L000L

Dem Speicher 1 wird der um die drei kleinsten Wertigkeiten  $2^0$  bis  $2^2$  verminderte Eingabekode

00000000L0

zugeleitet. Dieser adressiert die Speicherplatzgruppe mit dem Inhalt 16, das heißt mit den Tetraden

|                               |                               |                               |                               |

|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| 0000                          | 0000                          | 000L                          | 0L00                          |

| $\underbrace{\phantom{0000}}$ | $\underbrace{\phantom{0000}}$ | $\underbrace{\phantom{000L}}$ | $\underbrace{\phantom{0L00}}$ |

| $10^3$                        | $10^2$                        | $10^1$                        | $10^0$                        |

Die Tetrade für die Dezimale  $10^1$  wird unmittelbar ausgegeben, die Tetrade für die Dezimale  $10^0$  den wertigkeitszugeordneten zweiten Summationseingängen des ersten 4-Bit-Volladdierers 3 zugeführt. Dort liegen an den freien ersten Summationseingängen die der Dualzahl entnommenen Wertigkeiten  $2^0$  bis  $2^2$  an, also die auch als binär kodiert auffaßbare einstellige Zahl 00L. Der erste 4-Bit-Volladdierer 3 nimmt die Addition vor und errechnet

$$\begin{array}{r} 0L00 \\ + \underline{00L} \\ \hline 0LLL \end{array}$$

Die Übertragsschaltung 4 bildet mit Hilfe des ersten UND-Glieds 6, des zweiten UND-Glieds 7 und des ODER-Glieds 8 einen Dezimalübertrag Ü in Abhängigkeit von den Ausgangsbelegungen des ersten 4-Bit-Volladdierers 3 gemäß der logischen Beziehung

$$\dot{U} = \dot{U}' \cdot 2^3 \cdot 2^2 \cdot 2^3 \cdot 2^1$$

Diese Bedingung ist nicht erfüllt. Ein Dezimalübertrag Ü unterbleibt. Die Adressierung der Speicherplatzgruppe mit dem Inhalt 16 wird aufrecht erhalten.

Die ermittelte Summe OLLL wird über den zweiten 4-Bit-Volladdierer 5 unverändert ausgegeben. Der Ausgabekode lautet damit

|                               |                               |                               |                               |

|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| 0000                          | 0000                          | 000L                          | 0LLL                          |

| $\underbrace{\phantom{0000}}$ | $\underbrace{\phantom{0000}}$ | $\underbrace{\phantom{000L}}$ | $\underbrace{\phantom{0LLL}}$ |

| $10^3$                        | $10^2$                        | $10^1$                        | $10^0$                        |

und ist somit die Zahl 17 in der binär kodierten Dezimaldarstellung.

Soll die Zahl 53 als zweites Beispiel umgesetzt werden, dann gilt die Dualzahl

000000L000L0

Der dem Speicher 1 zugeleitete Eingabekode lautet eingeschränkt

000000L0

Er adressiert zunächst die Speicherplatzgruppe mit dem Inhalt 48, das heißt mit den Tetraden

|                               |                               |                               |                               |

|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| 0000                          | 0000                          | 0100                          | 1000                          |

| $\underbrace{\phantom{0000}}$ | $\underbrace{\phantom{0000}}$ | $\underbrace{\phantom{0100}}$ | $\underbrace{\phantom{1000}}$ |

| $10^3$                        | $10^2$                        | $10^1$                        | $10^0$                        |

Der erste 4-Bit-Volladdierer 3 vollzieht wiederum die Addition der Tetrade für die Dezimale  $10^0$  mit den drei kleinsten Wertigkeiten der Dualzahl, also

$$\begin{array}{r} 1000 \\ + \underline{10L} \\ \hline 1L0L \end{array}$$

Bei dieser Summe ist die logische Beziehung für die Bildung des Dezimalübertrags  $\ddot{U}$  erfüllt. Die Folge davon tritt in zweierlei Hinsicht ein.

Zum ersten wird eine Änderung der Speicheradressierung derart vorgenommen, daß anstelle der Speicherplatzgruppe mit dem Inhalt 48 die zugeordnete Übertrags-Speicherplatzgruppe mit dem Inhalt 58 adressiert wird. Der Ausgabekode ändert sich in der Dezimale  $10^1$  von 0L0L in 0L0L.

Zum zweiten veranlaßt der Dezimalübertrag  $\ddot{U}$ , daß zur Summe LL0L, die der erste 4-Bit-Volladdierer 3 ausgibt, im zweiten 4-Bit-Volladdierer 5 die Korrekturzahl 6 hinzu addiert wird.

$$\begin{array}{r} \text{LL0L} \\ + \text{0L0L} \\ \hline \text{L00LL} \end{array}$$

Damit wird die entstandene Pseudotetradenbeseitigung und bezüglich der Dezimale  $10^0$  in 00LL verwandelt.

Der vollständige Ausgabekode lautet damit

$$\begin{array}{cccc} \underbrace{0000}_{10^3} & \underbrace{0000}_{10^2} & \underbrace{0L0L}_{10^1} & \underbrace{00LL}_{10^0} \end{array}$$

und stellt die Zahl 53 in der binär kodierten Dezimalform dar.

-1.JUL.1981\*944329