(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-512236

(P2005-512236A)

(43) 公表日 平成17年4月28日(2005.4.28)

(51) Int.Cl.<sup>7</sup>

G 06 F 17/50

F 1

G 06 F 17/50

テーマコード(参考)

6 6 8 K

5 B 0 4 6

審査請求 未請求 予備審査請求 未請求 (全 35 頁)

(21) 出願番号 特願2003-551710 (P2003-551710)

(86) (22) 出願日 平成14年12月6日 (2002.12.6)

(85) 翻訳文提出日 平成16年6月7日 (2004.6.7)

(86) 國際出願番号 PCT/US2002/038799

(87) 國際公開番号 WO2003/050724

(87) 國際公開日 平成15年6月19日 (2003.6.19)

(31) 優先権主張番号 60/339,235

(32) 優先日 平成13年12月7日 (2001.12.7)

(33) 優先権主張国 米国(US)

(71) 出願人 500547740

カデンス デザイン システムズ, イン

コーポレイテッド

アメリカ合衆国 カリフォルニア 951

34, サン ノゼ, シーリー アベニ

ュー 2655

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】タイミンググラフ縮小によるタイミングモデル抽出

## (57) 【要約】

タイミングモデルを抽出する方法およびシステムが開示されている。開示されている、タイミングモデルを抽出するためのアプローチの1つは、タイミンググラフを縮小することによるものである。元のタイミング挙動は、到着時間、スルー時間、タイミング違反、および、クロック波形から独立しているラッチ時間借用さえも含むタイミングモデルにおいて保存される。また、タイミング制約は、モデルにおいて捕捉され、そのモデルが用いられるときに自動的に適用され得る。アンカー点は、元のネットリストよりも小さいモデルを取得するように、自動的に識別され、保持される。

**【特許請求の範囲】****【請求項 1】**

タイミングモデルを抽出する方法であって、

タイミンググラフを受け取るステップと、

該タイミンググラフを縮小することによって縮小されたモデルグラフを生成するステップと、

該縮小されたモデルグラフから該タイミングモデルを抽出するステップと

を包含する、方法。

**【請求項 2】**

タイミンググラフ要素が保持のために識別される、請求項 1 に記載の方法。 10

**【請求項 3】**

前記タイミンググラフ要素はタイミングピンを含む、請求項 2 に記載の方法。

**【請求項 4】**

アンカー点の識別は、前記タイミンググラフ要素が保持されるか否かを判定する基準を含む、請求項 2 に記載の方法。

**【請求項 5】**

アンカー点は、該アンカー点が取り除かれる場合、利得値によって規定される、請求項 4 に記載の方法。

**【請求項 6】**

前記利得値は、

$Gain = (\# \text{入来遅延アーケ} \times \# \text{出て行く遅延アーケ}) - \# \text{入来遅延アーケ} - \# \text{出て}\text{行く遅延アーケ}$

として規定される、請求項 5 に記載の方法。 20

**【請求項 7】**

アンカー点が任意の正の利得値に関連付けられている、請求項 5 に記載の方法。

**【請求項 8】**

利得値の閾値は、パフォーマンス予測を変動させるように調節可能である、請求項 5 に記載の方法。

**【請求項 9】**

前記タイミンググラフ要素が保持されるか否かを判定する基準は、ラッチ入力ピン、ラッチ出力ピン、ゲーテッドクロック出力ピン、ゲーテッドクロック入力ピン、アサーションに関連付けられているピン、ラッティネーブルピン、ラッチクリアピン、ラッチプリセットピン、出力から出力へのパスに関連付けられているピン、取り除かれる場合モデルサイズの増大と関連付けられているピンからなる群から選択される、請求項 2 に記載の方法。

。

**【請求項 10】**

前記タイミンググラフにおけるピンは、BFS順序で処理されて、前記縮小されたモデルグラフが生成される、請求項 1 に記載の方法。

**【請求項 11】**

前記タイミンググラフにおける組み合わせ回路部分が縮小される、請求項 1 に記載の方法。 40

**【請求項 12】**

シリアルマージ動作は、前記組み合わせ回路部分に対して行われる、請求項 11 に記載の方法。

**【請求項 13】**

パラレルマージ動作は、前記組み合わせ回路部分に対して行われる、請求項 11 に記載の方法。

**【請求項 14】**

パラレルマージ動作は、シリアルマージ動作の直後に続く、請求項 11 に記載の方法。

**【請求項 15】**

50

前記タイミンググラフにおける連続的回路部分が縮小される、請求項 1 に記載の方法。

【請求項 1 6】

前進 s マージ動作は、前記連続的回路部分に対して行われる、請求項 1 5 に記載の方法

。

【請求項 1 7】

後進 s マージ動作は、前記連続的回路部分に対して行われる、請求項 1 5 に記載の方法

。

【請求項 1 8】

自己ループチェックアークが前記タイミンググラフにおいて処理される、請求項 1 に記載の方法。

10

【請求項 1 9】

前記タイミングモデルを抽出する行動は、前記タイミングモデルを書き込むステップを含む、請求項 1 に記載の方法。

【請求項 2 0】

前記タイミングモデルを抽出するため、ピンが反復的に取り除かれる、請求項 1 に記載の方法。

【請求項 2 1】

チェックアークが可能なスルーバル値全てに対して特徴付けられている、請求項 1 に記載の方法。

【請求項 2 2】

チェックアークは推定されたスルーバル値に対して特徴付けられている、請求項 1 に記載の方法。

20

【請求項 2 3】

挿入遅延はクロックソースポートへのパスをトレーシングすることによって計算される、請求項 1 に記載の方法。

【請求項 2 4】

前記タイミングモデルを抽出する行動は、モデル構成要素を識別するように、前記縮小されたモデルグラフをウォーキングさせる行動を含む、請求項 1 に記載の方法。

【請求項 2 5】

前記タイミングモデルを抽出する行動の間、遅延テーブルがソートされ、縮小される、請求項 2 4 に記載の方法。

30

【請求項 2 6】

前記モデル構成要素は、ピン、遅延アーク、およびチェックアークを含む、請求項 2 4 に記載の方法。

【請求項 2 7】

アサーションに関連付けられている前記タイミンググラフにおけるピンは、前記縮小されたモデルグラフ内に保持される、請求項 1 に記載の方法。

【請求項 2 8】

アサーションは、前記タイミングモデル内の対応するピンに自動的に関連付けられている、請求項 1 に記載の方法。

40

【請求項 2 9】

前記タイミングモデルは、前記タイミンググラフ内のピンに対応するアサーション情報を含む、請求項 1 に記載の方法。

【請求項 3 0】

階層アサーションは前記タイミングモデル内に自動的に含まれる、請求項 1 に記載の方法。

【請求項 3 1】

新たな内部ピンが、前記階層アサーションに関連付けられている前記縮小されたモデルグラフにおいて作製される、請求項 3 0 に記載の方法。

【請求項 3 2】

50

前記新たな内部ピンは、前記縮小されたモデルグラフ内に保持される、請求項30に記載の方法。

【請求項33】

ゼロ遅延アークが前記新たな内部ピンに対して作製される、請求項30に記載の方法。

【請求項34】

ポートアサーションが前記タイミングモデルに自動的に含まれる、請求項1に記載の方法。

【請求項35】

新たな内部ピンは、前記ポートアサーションに関連付けられている前記縮小されたモデルグラフにおいて作製される、請求項34に記載の方法。

10

【請求項36】

ゼロ遅延アークが前記新たな内部ピンに対して作製される、請求項34に記載の方法。

【請求項37】

タイミングモデルを抽出するシステムであって、

タイミンググラフを受け取る手段と、

該タイミンググラフを縮小することによって縮小されたモデルグラフを生成する手段と

20

、該縮小されたモデルグラフから該タイミングモデルを抽出する手段と

を備える、システム。

【請求項38】

タイミングモデルを抽出するプロセスを実行する実行可能なコードを有するコンピュータ使用可能媒体を含むコンピュータプログラム製品であって、該プロセスは、

タイミンググラフを受け取るステップと、

該タイミンググラフを縮小することによって縮小されたモデルグラフを生成するステップと、

該縮小されたモデルグラフから該タイミングモデルを抽出するステップと

を含む、コンピュータプログラム製品。

【請求項39】

タイミング解析のシステムであって、

タイミンググラフに基づいて、モデルグラフを生成するモデルグラフビルダと、

30

タイミングモデルを書くモデルライタと、

該モデルグラフを減少させるモデルグラフリデューサと

を含む、システム。

【請求項40】

アサーションハンドラをさらに含み、該アサーションハンドラは、前記タイミングモデルのアサーションを処理する、請求項39に記載のシステム。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願の相互参照)

40

本願は、2001年12月7日に出願された米国仮出願番号第60/339,235号の優先権を主張し、その全体において参考として援用される。

(著作権表示)

本発明文書の一部の開示には、著作権保護の対象になる資料を含む。著作権所有者は、特許商標局の特許ファイルおよび記録に記載されるように特許文書および特許開示の、誰かによる複製に反対はないが、さもなければ、全ての他の著作権を確保する。

【背景技術】

【0002】

本発明は、電子回路設計の分野に関し、より詳細には、タイミングモデル抽出の分野に関する。

50

## 【0003】

タイミング抽出またはブロックの特徴付けは、例えば、静的タイミング分析器といったタイミング分析器を用いる用途のためのデジタル回路のタイミングモデルを生成するプロセスについて言う。タイミング抽出は、タイミング検証の複雑性を縮小し、かつ、IPブロックの実行の詳細を隠す抽象化レベルを供給することによって、階層的なトップダウンフローおよびボトムアップIPオーサリングフローにおける重要な役割を果たす。タイミング抽出における3つの所望の特徴は、精度、効率、および有用性である。

## 【0004】

抽出されたモデルは、オリジナル回路のタイミング行動を保護し、正しい透明なラッチ動作およびタイミング違反を含む正確な結果を作成する。モデルはまた、モデルを生成するために必要とされるリソースの点について、かつ、最終モデルのサイズの点について効果的になる必要がある。モデルはまた、既存の静的タイミング分析器を用い易くなる。これは、モデルの具体化、オリジナルタイミング制約の転換、および分かりやすいタイミングレポートを含む。

## 【0005】

タイミングモデルは、しばしば2つのタイプ（ブラックボックスモデルおよびグレーボックスモデル）に分類され得る。ブラックボックスモデルは、ブロック中に内部視認性がなく、タイミング情報は、全てブロックの境界におけるピンに通じる。一方、グレーボックスモデルは、内部ピンを有する。内部ピンは、複数のラッチにわたって、タイム借用のような動作をモデリングさせることを可能にする。このような内部ピンは、モデルサイズを縮小する性質およびオリジナルタイミング制約またはアサーションを適用する性質といった利点を提供する。

## 【0006】

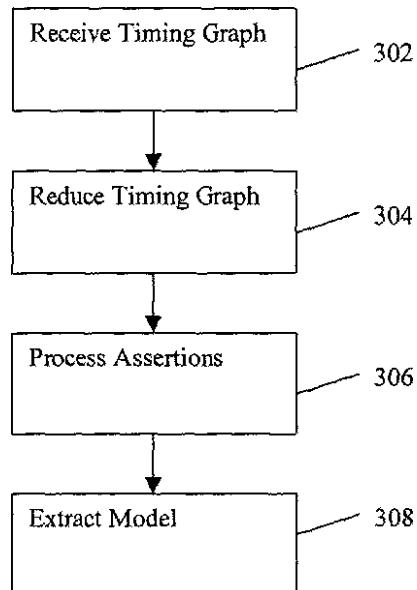

ブラックボックスモデルをインプリメントするための1つのアプローチにおいて、ユーザは、入力スルーブル（*slow*）値および出力負荷値のセットを供給し、ツールは、全てのポートツーポートのバス遅延および関連するタイミングチェックを決定するようにパストレーシングを実行する。ブラックボックスモデルが広範に用いられたが、このモデルは、著しい欠点で苦しむ。例えば、タイミンググラフにおけるそれぞれ可能なパスのトレーシングは、潜在的に複雑なタスクである。潜在的に複雑なタスクは、計算リソースのかなりの量を消費し、しばしば、モデルを抽出するために完全なタイミング分析プロセスを必要とする。さらに、このアプローチにおいて結果として生じるモデルサイズは、実際は、オリジナルタイミンググラフサイズよりも結局大きくなり得る。これは図1に示され、図1において、パストレーシングを使用して、タイミンググラフ100からブラックボックスモデル140を得る。このアプローチにおいて、全てのポテンシャルパスは、個々の入力ポートから個々の出力ポートにトレーシングすることによって識別される。従って、オリジナルタイミンググラフ100におけるアーケ102およびアーケ108を介するパスは、ピン150を介してトレースされ、ブラックボックスモデル140においてパス120を形成する。それぞれ可能なパスのトレーシングにより、結果として生じるタイミングモデル140に、9つのアーケまたはパスを生じる（アーケ120、122、124、126、128、130、132、134、および136）。示され得るように、オリジナルタイミンググラフ100において6つのアーケがある（アーケ102、104、106、108、110、および112）。従って、ブラックボックスモデル140は、実際に、オリジナルタイミンググラフ100よりも大きい。

## 【0007】

公知のブラックボックスモデルを有する別の欠点は、限定されたラッチ動作のみがモデル化され得るということである。モデルは、いくつかの所与のクロック波形に対してオリジナルのネットリストのラッチタイム借用動作を取り込み得る。モデルが抽出された後に、クロック波形が変化する場合、モデルは無効になる。さらに、ブラックボックスにおけるアサーションに対するサポートが、ブロックに完全に含まれるそれらのアサーション（assertion）に対するサポートは、例え境界ポートから始まるか、または境界波形

10

20

30

40

50

ートで終端しても限定される。境界ポートから始まるか、または境界ポートで終端するアサーションだけが、完全にサポートされ得る。例えば、境界ポートから始まらないか、または境界ポートで終端しないアサーションは、サポートされ得ない。また、複数のブロックにかかるアサーションは、サポートされ得ない。例えば、ブロックAから始まり、かつ、ブロックBの中間で終端するマルチサイクルパスを考慮する。ブロックBのブラックボックスモデルは、このマルチサイクルパスのアサーションをサポートし得ない。

#### 【0008】

グレー ボックスのモデリングに対する対処法もまた、欠点に苦しむ。従来のグレー ボックスは、ラッチにおける任意の透明レベルを適切に対処し得ない。ラッチは、レジスタまたは組み合わせゲートに変化され得るが、このような変化は極めて保守的であり、かつ、タイム借用を可能にしないモデルを結果として導く。あるアプローチは、個々のラッチの代わりにラッチパスを崩壊させるラッチパス圧縮動作を提供する。この動作において、圧縮の及ぶ限りは、所望のラッチ透明レベルを明確にすることによってコントロールされる。しかし、このアプローチは、モデルサイズの縮小を保証し得ず、時には、モデルサイズは、実際に、ラッチ圧縮の後に増加する。さらに、その方法は、ラッチパスの数またはラッチ透明レベルを用いてうまくスケーリングしない。

#### 【発明の開示】

##### 【課題を解決するための手段】

#### 【0009】

タイミンググラフを縮小することによってタイミングモデルを生成するための方法およびシステムが開示される。本方法は、明確な許容内にある正確さであり、非常に効率的であるモデルを生成し得る。また、タイミング制約/アサーションをモデルに対して持続し、適用するためのアプローチが開示される。ある実施形態において、タイミング制約/アサーションは、一部のモデルとして観測され、生成され得る新しいタイミング制約のセットが、モデル抽出プロセスの一部として自動的に適用される。オリジナルアサーションのアプリケーションのためのラッチタイミング借用およびサポートは、いくつかの中間ピンを維持することによって達成され得る。本発明のさらなる、かつ追加のオブジェクト、詳細、および利点は、図面および以下のテキストに記載される。

#### 【発明を実施するための最良の形態】

#### 【0010】

##### (概要)

本発明の開示される実施形態は、タイミンググラフを縮小することによってタイミングモデルを生成するための方法およびシステムに向けられる。本方法は、明確な許容内にある正確さがあり、かつ極めて効率的であるモデルを生成し得る。タイミング制約/アサーションをモデルに対して持続し、適用するためのアプローチがさらに開示される。ある実施形態において、タイミング制約/アサーションは、一部のモデルとして観測され、新しいタイミング制約のセットは、一部のモデル抽出プロセスとして自動的に生成され得る。オリジナルアサーションのアプリケーションに対するラッチタイミング借用およびサポートは、いくつかの中間ピンによって達成され得る。

#### 【0011】

本発明の実施形態において、モデル抽出は、オリジナルタイミンググラフを簡略化することによって実行される。簡略化は、タイミングピンをタイミンググラフに反復的に移動し、タイミングアークを結合することによって達成される。これにより、モデルサイズおよびCPU/メモリリソースのトレードオフを可能にするモデルのスペクトルを結果的に生じる。説明のため、3つのタプル  $G = (P, D, C)$  としてタイミンググラフ  $G$  を考慮すると、 $P$  はピンのセットであり、 $D$  は遅延アークのセットであり、 $C$  はチェックアークのセットである。遅延アークは、ピン  $D$  ( $P \times P$ ) で始まり、チェックアークは、 $C$  ( $P \times P$ ) で終端する。各遅延アークと共に、ソースピンとシンクピンとの間の有効な遷移を定義する遷移行列が関連付けられる。各チェックアークと共に、信号ピンと基準ピンとの間の有効な起伏遷移または降下遷移を定義する遷移行列が関連付けられる。各チェック

10

20

30

40

50

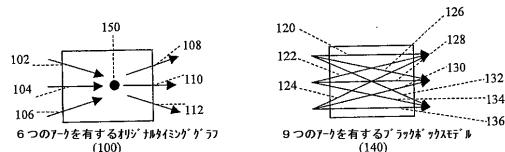

クアークは、例えば、セットアップ、ホールド、リカバリ、除去といったタイプを有する。本発明に用いられる専門用語および従来技術を説明するために、単純なD型レジスタを表すタイミンググラフの例が図2aに示される。遅延アーク202は実線矢印のように表され、チェックアーク204は点線矢印のように表される。CLK Qの遅延アークに対する遷移行列の例は、図2bに示される。この行列は、入力および出力遷移上にチェックアークと遅延アークとの間の遷移関係を特定する。遅延/チェック値は、遅延/チェックアークと関連付けられる。遅延またはチェック値は、例えば、線形関数、ルックアップテーブル、または遅延方程式であり得る。

#### 【0012】

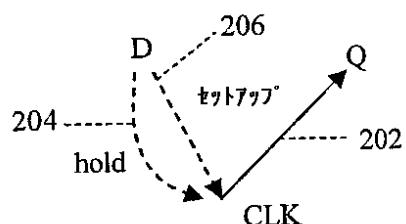

図3aは、本発明の実施形態に従ってタイミングモデル抽出するためのプロセスのフローチャートを示す。302において、プロセシングに対してタイミンググラフが受け取られる。ある実施形態において、この動作は、タイミングエンジンによって生成されるオリジナルタイミンググラフを新しいモデルグラフにコピーすることによって達成される。任意のタイミング分析ツール（例えば、カリフォルニア州サンノゼのCadence Design Systemsから市販されるBuild Gatesタイミング分析ツール）を使用して、このタイミンググラフを生成し得る。ある実施形態において、所与のタイミンググラフは、周期的になるように想定される。304において、モデルグラフは、タイミングピンを移動させ、タイミングアークに結合することによって縮小される。306において、タイミンググラフ内のアサーションは、抽出されたモデルで自動的に処理され、かつ再現される。オリジナル回路におけるアサーションは、さらに詳細に以下で記載されるように、中間ピンを用いるモデルグラフにおけるアサーションに対して、自動的にマッピングされる。308において、タイミングモデルは、モデルグラフから抽出される。

#### 【0013】

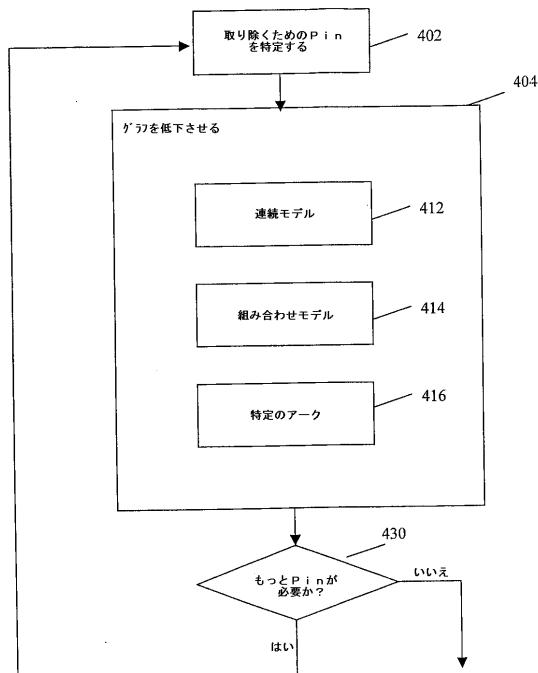

図3bは、図3aのモデルグラフ縮小動作304をインプリメントするためのプロセスの実施形態のフローチャートを示す。402において、処理するためのタイミングピンの特定、およびモデル縮小動作から排除するためのタイミンググラフエレメントの特定が為される。縮小からできる限り排除するためのピン/エレメントの例は、アンカーポイント、ラッチポイント、およびアサーションポイントを含む。アンカーポイントは、アンカーポイントが除去される場合、ピンに対して、モデルグラフがオリジナルタイミンググラフよりも大きくなるようなピンである。アンカーピンが、例えば、図1のピン150によって示される。ラッチポイントは、縮小から排除され、ラッチ挙動の維持を保証する。排除されるラッチポイントの例は、ラッチエレメントの、クロックピンではなく、入力および出力ピンを含む。アサーションまたは制約に関連付けられるピンは、縮小から排除され、オリジナル制約を持続し、かつ適用する。

#### 【0014】

402における除外について識別されるエレメントおよびピンに関するのを除いて、404において、タイミンググラフ部分は、起こり得る縮小に対して処理される。説明のために、タイミングモデルは、遅延アークの間の相互作用を扱い、かつ組み合わせモデル412に取り込まれる組み合わせ部分と、遅延アークとチェックアークとの間の相互作用を扱い、かつシーケンシャルモデル414に取り込まれるシーケンシャル部分とを含む少なくとも2つの部分に分割される。特別なプロセスがさらに定義され、標準モデルを用いて適切に縮小され得ない特別なタイプのアーク416を扱い得る。例えば、セルフループアークは、個々のプロセスが縮小に対して使用され得る特別なタイプのアークの例である。タイミンググラフにおけるピンおよびアークは、さらなるピン430が処理のために残らなくなるまで、BFS（幅優先探索）の順序を用いて処理される。縮小プロセスの複数の反復は、タイミンググラフの全てまたは一部について実行され得る。

#### 【0015】

具現化されるタイミングモデル抽出プロセスは、静的タイミング分析器で用いるためのデジタル回路タイミングモデルを構築する。この静的タイミング分析器において、グレーボックスタイミングモデルは、タイミンググラフを縮小することによってゲートレベルネ

10

20

30

30

40

50

ットリストから生成される。これにより、任意のレベルのラッチタイム借用、セルフループタイミングチェックに対する正確なサポート、およびオリジナルタイミング制約を保証するための機能を含むモデルの精度が提供される。さらに、モデルを生成するために必要とされるC P Uおよびメモリリソースは、回路のサイズを用いてうまくスケーリングする。

#### 【 0 0 1 6 】

10 例えれば、オリジナル回路の最も悪い場合の挙動がモデルにおいて精度よく保証される場合、モデル抽出プロセスは正確である。オリジナル回路で生じる任意のタイミング違反は、モデルにおいて再現可能である。さらに、入力スルーバリューにおける変化について変化する重要なパスは、モデルにおいて精度よく反映される。これにより、重要なパスが、ある特定の入力スルーバリューを用いて定義され、かつ入力スルーバリューおよび出力ロードバリューの組み合わせについて後に再び特徴付けられる前のアプローチよりもさらに良い精度が提供される。さらに、例えれば周期および最小パルス幅チェックといったセルフループタイミングチェックも保証される。さらに、具現化されたアプローチにおいて、モデルを抽出するためにフルダウントiming分析が本質的に必要とされる前のアプローチではなく、単純なグラフ制約について、抽出に準拠されるので、モデル抽出プロセスは、さらに効率よく適用され得る。また、モデルサイズは、例えれば、アンカーポイントを持続することによって、顕著に縮小され得る。グレーボックスモデルを生成するステップはまた、ブラックボックスモデルリングアプローチに比較されるように回路における中間ピンにさらに明白に提供する。中間ピンは、ラッチタイミング借用挙動およびレジスタツーレジスタの正確なモデルリングを可能にする。具現化されるグレーボックスモデルは、クロックコンテキストの独立性（モデルを構築するために用いられる波形とは異なるクロック波形に対して有効である）であるモデルを作成する。開示される実施形態において、パス遅延は、入力スルーバリューおよび出力ロードバリューについて特徴付けられ得るが、タイミングチェックは、入力スルーバリューおよびクロックスルーバリューについて特徴付けられる。

#### 【 0 0 1 7 】

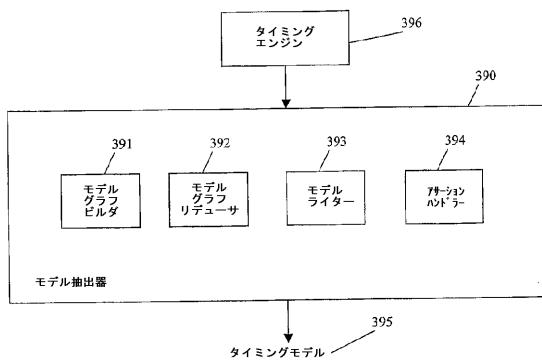

20 図3cは、本発明によるモデル抽出メカニズム390のアーキテクチャの実施形態を示す。モデル抽出メカニズム390は、4つの基本的なコンポーネントを含む。モデルグラフビルダ391は、タイミングエンジン396から新しいモデルグラフにオリジナルタイミンググラフを複製する。モデルグラフリデューサ392は、モデルグラフを単純化するエキストラクタのコアエンジンである。モデルライタ394は、オリジナルタイミング制約を管理する。モデルライタ393は、縮小したモデルグラフからのタイミングモデルを書き改める。アサーションハンドラ394は、オリジナルタイミング制約を管理する。これらの機能のコンポーネントの各々は、より詳細に以下に記載される。

#### （モデルグラフビルダ）

30 このセクションは、モデルグラフを構築するためのプロセスおよびメカニズムの実施形態を記載する。このアプローチでは、オリジナルタイミンググラフにおける全てのチェックアークは、新しいモデルグラフに追加される。オリジナルタイミンググラフにおける遅延アークのほとんどまたは全ては、モデルグラフに複製される。例えば、（a）ラッチD->Qフラッシュアーク、および（b）クロックゲーティングアーク（クロックゲート入力ピンからクロックゲート出力ピンまでの全てのアーク）。この実施形態において、例えば、set\_disable\_timingといった遅延アークおよびチェックアークは、モデルグラフに含まれない。

#### 【 0 0 1 8 】

40 モデルグラフは、ピン、遅延アーク、およびチェックアークに関連付けられたオブジェクトから成る。これらのオブジェクトの各々は、オリジナルタイミンググラフにおける対応するオブジェクトへのポインタを有する。入力から出力へ、BFS順序にソートされるピンのアレイを戻すBFSトラバーサルルーチンが使用される。オリジナルタイミンググラフに存在しなかったサイクルを導入することを避けるために、BFSグラフトラバーサルルーチンは、ラッチフラッシュアークおよびクロックゲーティングアークに配慮する。

## (モデルグラフリデューサ)

図4 aは、グラフ縮小を実行するためのプロセスおよびメカニズムの実施形態について擬似コードを示す。このアプローチにおいて、タイミンググラフは、幅優先検索(BFS)順序において各中間ピンにアクセスすることによって時間におけるあるピンを縮小させる。縮小は、さらなる変化が可能にならなくなるまで繰り返される。BFSトラバーサルを用いるための理由は、ピンが取り除かれる以前に、ピンに遅延アークを入来することがすでに処理されたこと、および遅延アークが入力スルーバリューの最小数に関して特徴付けられることを保証することを含む。removePin()は、マージ動作を実行するメインルーチンである。postProcess()ルーチンは、初期入力ピン(または持続された中間ピン)から始まり、かつ初期出力ピン(または持続された中間ピン)で終端する遅延アークまたはチェックアークを管理する。このようなアークについて、値ラン計算ルーチンは、ピンの移動がこのようなアークに対して実行されないので、明白になり得る。

## 【0019】

removePin()ルーチンの実施形態に対する擬似コードが図4 bに示される。セクション472は、特定のピンがモデルから移動されるか、または縮小プロセスから排他されるかどうかの決定が為される。セクション472のretainPin()ルーチンの実施形態に対する擬似コードが図4 cに示される。セクション474、476、および478は、タイミンググラフの対象部分を縮小するための擬似コードを含む。説明のため、タイミングモデルは、少なくとも2つの部分に分割される。組み合わせ部分は、遅延アークの間の相互作用に対処して、組み合わせモデルにおいて取り込まれる。シーケンシャル部分は、遅延アークとチェックアークとの間の相互作用に対処し、シーケンシャルモデルに取り込まれる。図4 bにおける擬似コードのセクション474は、「sマージ」および「pマージ」動作を用いる縮小する組み合わせモデルに向けられる。セクション476は、「backward-s-merge」動作を用いて連続モデルを減少させることに関する。セクション478は、「前方sマージ」操作を用いる縮小するシーケンシャルモデルに向けられる。これらの操作の各々は、以下にさらに詳細に記載される。

## (縮小するか、縮小から排他するためのタイミンググラフエレメントを識別すること)

このセクションは、特定のタイミンググラフエレメントがモデル縮小プロセスに含まれるか、またはモデル縮小プロセスから排他されるかどうかを決定するためのプロセスおよび機構の実施形態を記載する。

## 【0020】

タイミンググラフにおけるピンおよびアークは、さらなるピンが処理するために保持しなくなるまでBFS順序を用いて処理される。各エレメントは、縮小プロセスから排他されない限り、縮小の対象になる。タイミンググラフエレメントは、例えば、結果として生じるタイミングモデルにおけるある識別されたタイプの挙動/情報を維持するために、あるいは、縮小プロセスがタイミングモデルのサイズを不利益に増大しないことを保証するために、多様な理由のための縮小の適性から排他され得る。本アプローチは、経験則を用いて、例えばモデルサイズがオリジナル回路サイズ以下になるようなモデルサイズにおけるプローアップを避け得る。

## 【0021】

縮小から排他するためのタイミンググラフエレメントの例示的エレメントの第1のセットは、ラッチに対するタイミングピンである。タイミングモデルにおける移動からラッチタイミングピンを排他することは、ラッチ挙動を持続するために役立つ。このことは、ラッチに関連付けられた透明度の感度が「time-borrowing(時間借用)」に有益であり得るので、一部において生じる。「時間借用」は、ラッチエレメントの入力および出力ピンが縮小プロセスから排他される場合、持続される。本発明の実施形態において、ラッチのクロックピンが縮小の適性から排他されないことに留意されたい。ラッチポイントは、設計における構造情報にアクセスすることを含む多くの教示によって、あるいは、タイミンググラフにおけるラッチプロファイルの分析によって特定される。多くのラッチツーラッチ接続を有するラッチベースの設計は、この最適化から最も利益を得るよう

10

20

30

40

50

に期待される。

【0022】

他のこののようなピンは、縮小から排他され、オリジナルタイミング挙動を持続し得る。このようなピンの例示は、ラッチ入力ピン、ラッチ出力ピン、ゲートとクロック出力ピン、ゲートとクロック入力ピン、アサーションに関連付けられたピン、および出力ツー出力パスに関連付けられたピンを含む。

【0023】

ピンが持続されるとき、入力遅延アークからピンに来るスルーバリューを用いて、ピンから生じるアークを横切って遅延を計算する。出力ツー出力に関連付けられたピンは、「ネットピン」によって供給された全ての中間ピンを参照する。ネットピンは、ネットアークを介して初期出力（「P0」）ポートに接続するピンである。この持続を用いて、出力ツー出力による正確な出力ローディングを取り込んで、正確な遅延アクロスネットアークを明らかにする。

【0024】

別の例として、アサーションに関連付けられたタイミングピンはまた、縮小から排他し得る。以下にさらに詳細に説明されるように、アサーションは、タイミングモデルに直接組み込まれ、個々のタイミングモデルエレメントに関連付けられ得る。これらのエレメントを縮小のための適性から排他することは、アサーションとそれに関連付けられたタイミンググラフエレメントとの間の関連性の維持に役立つ。

【0025】

モデル抽出の目的は、オリジナル回路より小さいモデルを生成することである。しかし、いくつかの場合、あるタイミングピンの移動は、タイミングアークの数におけるジオメトリックプロファイリングを導く。「アンカーポイント」は、移動した場合、モデルサイズにおける増大を導き得る既存のピン（例えば、中間ピン）について言う。タイミングモデルを有することを避けるためには、オリジナルタイミンググラフより大きくなり、このようなアンカーポイントが縮小プロセスから排他され得る。遅延アークの数を用いて、モデルサイズを確立する。このアプローチにおいて、遅延アークが最終モデルサイズへの寄与を全て等しくさせることが想定される。この想定が与えられると、アンカーポイントの識別は、静的回路の最適化のコンテキストにおいて剪定のセットを見出す問題に類似する。この目的は、可変の数ではなく、遅延アークの数を最小化することである。また、入力スルーバリューの最小数に関する遅延アークを特徴付けることが望まれるので、このアプローチは、それらの入来遅延アークを最初に処理することなくランダムに中間ピンを移動しない。これは順序を制約する。この順序において、アンカーポイントは特定され、かつ維持される。

【0026】

アンカーポイントを特定するために、ゲイン値は、以下のようなピンに対して決定される：

ゲイン = (#入来遅延アークの数 × #出て行く遅延アークの数) - #入来遅延アークの数 - #出て行く遅延アークの数

この値は、ピンが移動される場合、遅延アークの数において増大を表す。ある実施形態において、ポジティブゲインを有し、かつ、観察可能である任意のピンは、アンカーポイントに対する候補である。ピンから初期の出力または持続されたピンへのパスがある場合、ピンは観察可能である。このアプローチにおいて、可観測性により、アンカーポイントは、最終的に移動されるピンの推移的ファンイン（fan-in）錐体に形成されることが防止される。例えば、レジスタ入力ピンは、観測されず、最終的に移動され得る。

【0027】

例えば、図1において、中間ピン150の移動以前に、オリジナルタイミンググラフ100において6つの遅延アークがある（すなわち、アーク102、104、106、108、110、および112）。ピン150が移動される場合、遅延アークの数は、3つのゲインを残して9つになる（すなわち、アーク120～136）。このゲイン値は、上記

10

20

30

40

50

の式を用いて特定され得る。この式において、入来遅延アークの数は 3 になり（アーク 102、104、および 106）、出て行く遅延アークの数も 3 になる（アーク 108、110、112）。従って、ゲイン = ((3 × 3) - 3 - 3) = ピン 150 に対して 3 になる。故に中間ピン 150 に対するゲイン値がゼロを超えるので、ピン 150 は、縮小プロセスから排他されるアンカーポイントが考慮され得る。

#### 【0028】

一旦、アンカーポイントが特定されると、アンカーポイントは特定のパスに対して有効である。1つのパスが、全ての中間ピンの完全な掃引を構成する。アンカーポイントは、次のパスにおいて再び特定される。

#### 【0029】

アンカーポイントの決定に対する限界ゲイン値は、性能期待値を得るように、または変化するように調整され得る。ゲイン閾値に対する十分高い値と共に、全てのアンカーポイントは、設計から除去され得る。アンカーポイントの最大数は、ゲイン閾値を「1」の値にセットすることによって特定される。結果として生じるタイミングモデルがオリジナルタイミンググラフのサイズを超過しないことを保証するために、ゲイン閾値は 1 に設定され得る。

#### 【0030】

ゲイン閾値が高い値に設定されるとき、遅延の数は、最終モデルサイズがより大きくなるがより小さい閾値に対してよりも小さくなることが起こり得る。これが起こるのは、いくつかの遅延アークが遷移マトリックスの点に関して他の遅延アークよりも「濃く」なるからである。これは、全ての遅延アークが最終モデルサイズに等しく寄与させるという想定が局所的なレンジを越えて必然的に変化しないので、起こる。しかし、中間入来 / 出て行く遅延アークの数は全ての遅延アークではなく、このアプローチが観測されるので、これはアンカーポイントに関連付けられた見積もりに影響しない。

#### 【0031】

よりグローバルな観点に対して、遅延アークの異なる密度または重さはまた、アンカーポイントを決定するとき、考慮に取り入れられる。

#### （組み合わせモデルの縮小）

このセクションは、組み合わせモードを処理するために図 4 b のセクション 474 を実施するためのアプローチの実施形態を記載する。タイミンググラフを縮小するためのこのアプローチにおける 2 つの操作は、シリアル - マージ（「s マージ」）およびパラレル - マージ（「p マージ」）操作である。

#### 【0032】

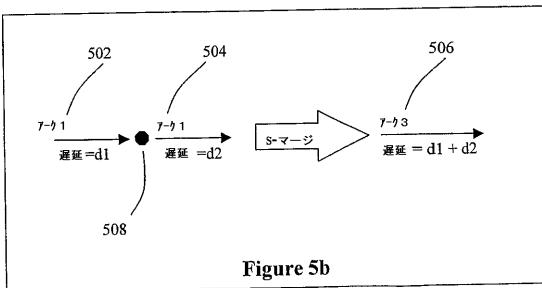

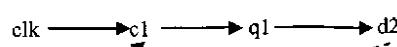

この実施形態において、s マージ操作は、連続して 2 つの遅延アーク（d1 および d2）を得て、第 1 のアーク（d1）のソースから第 2 のアーク（d2）のシンクに、d1 と d2 との「合計」を表すように新しいアーク（d3）を生じる。s マージは、精度を損なうことなくタイミンググラフからの中間ピンの除去を可能にする縮小操作である、基本的な縮小操作である。s マージが実行されると、マージされたアークの新しいアークの遅延が計算される。

#### 【0033】

図 5 b を参照して、中間ピン 508 にわたって連続である 2 つのアーク、アーク 1502 およびアーク 2504 を考慮する。アーク 1502 およびアーク 2504 は、図 5 a に示される遅延値を有する。これら 2 つのアークは、中間ピン 508 を移動することによってシリアルにマージされる。アーク 1502 とアーク 2504 との間の s マージから生じる新しいアーク 3506 は、アーク 1502 およびアーク 2504 の個々の遅延を合計することによって計算される遅延を有する。

#### 【0034】

この実施形態において、「レイジー」スルーチャンネルが用いられ、ゆえに、出力スルーチャンネルおよびアーク遅延は、遅延および出力スルーチャンネルにおける変化につながり得る新しい入力スルーチャンネルに対してのみ計算される。また、ロード - 依存遅延計算は、出力ポートを駆動する最後

のアークに制限され得る。

【0035】

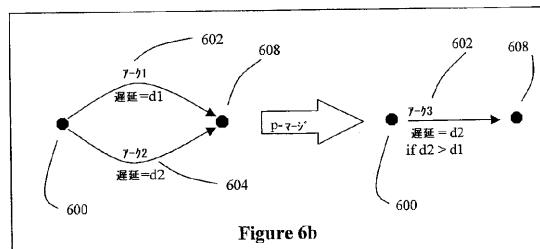

pマージ操作は、2つのパラレルアークを取り、それらを単一のアークにマージする。pマージ操作は、それが次のステージの計算において処理されることを必要とするアークの数を縮小させるように、モデル抽出時間にのける次の縮小に通じ得る。ある実施形態において、2つのパラレル遅延アークが与えられ、pマージは、2つのアークの「最も悪い」ものを選び、他のアークが廃棄されることを可能にする。

【0036】

図6bを参照して、ピン600から始まり、ピン608で終わる2つのパラレルアーク、アーク1 602およびアーク2 604を考慮する。これらのアークに対する遅延値は、図6aの表に示される。単一のアーク3 602を用いて2つのアークからの情報をマージすることが所望される。

10

【0037】

アーク1 602に対するアーク遅延d1がアーク2 604に対するアーク遅延d2よりも少ないということを想定する（すなわち、d1 < d2）。当該のパスが遅い場合、次に、pマージ操作は、出力スルーチンを選定し、最悪の場合のアーク（この例示においては、より大きいアーク遅延値を有するのでアーク2 604である）からアーク遅延を選定する。早いパスおよび遅いパスが共に当該である場合、次に、pマージは、アーク1 602からd1の最悪の早い遅延、およびアーク2 604からd2の最悪の遅い遅延を獲得し得る。次に、アーク602は、pマージの後の2つの遅延：d1の早い遅延およびd2の遅い遅延を有する。

20

【0038】

ある実施形態において、合成アーク3 606は新しいアークではない。それは、pマージプロセスにおいて縮小するようにパラレルアーク602および604のセットから持続するために選択されたアークである。従って、アーク602および604に導入されるpマージについて、遅いパスが当該の場合、かつ、アーク2 604がアーク1 602よりも大きいアークを有することが想定される場合、次に、pマージプロセスの後、アーク1 602は移動され、アーク2 604のみが合成アーク3 606として残る。代替の実施形態において、アーク3 606は、選択されたアーク値に基づいて必要とされるプロパティと共に形成される全体的に新しいアークである。

30

【0039】

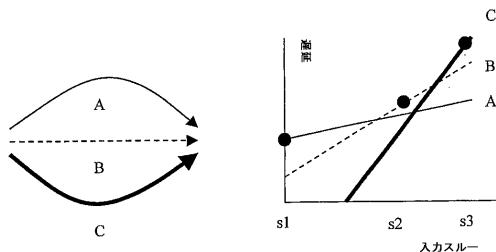

pマージ操作が入力スルーチンにおける変化のために変化する重要なパスを考慮に入れるように構成され得ることに留意されたい。図7におけるタイミンググラフを考慮する。図7では、s1からs2、s3へと変化する入力スルーチンと同様に、重要なパスは、AからB、Cへと変化する。2つのpマージ操作の後に結果として生じるアーク遅延は、重要なパスにおける変化を反映する。従って、本アプローチは、オリジナルに選択される特定の重要なパスにロックされないが、例えば入力スルーチンにおける反かに基づいて、重要なパスを動的に決定し得る。

【0040】

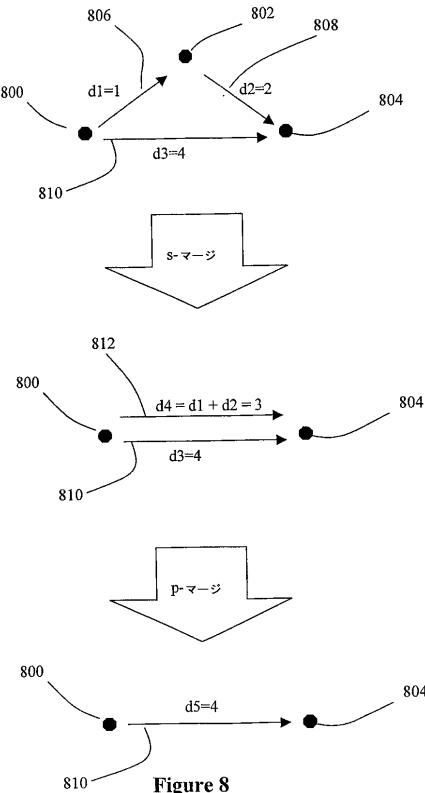

図8は、タイミンググラフの一部を縮小するために実行され得る一連のpマージおよびsマージ動作を説明する。最初に、タイミンググラフ部分は、第2のタイミングピン804に接続される遅延アーク810を有する第1のタイミングピン800を含む。別の遅延アーク806は、タイミングピン800から中間タイミングピン802まで伸びる。遅延アーク808は、中間タイミングピン802からタイミングピン804まで伸びる。

40

【0041】

遅延アーク806および遅延アーク808が中間タイミングピン802を介して連続的に伸びることが見られ得る。従って、sマージ動作は、これら2つのアークをマージされた遅延アーク812の中へ縮小するように実行され得る。遅延アーク806が遅延値d1 = 1を有し、遅延アーク808が遅延値d2 = 2を有する場合、次に、sマージされたアーク812に対する遅延値d4は、2つの遅延値の合計（すなわち、d4 = d1 + d2 =

50

$1 + 2 = 3$  ) に等しくなる。 s マージ操作の後、中間タイミングピン 8 0 2 は除去され、 2 つの遅延アーク 8 0 6 および 8 0 8 は遅延値  $d = 3$  を有する単一の遅延アーク 8 1 2 にマージされた。

#### 【 0 0 4 2 】

この点について、マージされた遅延アーク 8 1 2 は、オリジナル遅延アーク 8 1 0 と平行になる。なぜなら、同様の入力タイミングピン 8 0 0 から同様の出力タイミングピン 8 0 4 まで共に伸びるからである。 p マージ操作は、これら 2 つのアークを単一のマージされたアーク 8 1 0 中にさらに縮小するように実行され得る。当該のパスが遅い場合、次に、マージされたアーク 8 1 0 は、より大きい遅延値を有するどちらのアーク 8 1 0 または 8 1 2 でも遅延値に関連付けられる。ここで、アーク 8 1 0 は、それに平行なアーク 8 1 2 よりも大きい遅延値を有するので、マージされたアーク 8 1 0 は、アーク 8 1 0 の遅延値に関連付けられる ( すなわち、遅延値  $d = ( d_3 \text{ または } d_4 \text{ の大きい方 } )$  ) 。

#### 【 0 0 4 3 】

縮小操作が完成されたとき、オリジナルタイミンググラフ部分において 3 つの遅延アークおよび 3 つのタイミングピンが存在されるので、最終的なタイミングもであるは、単一の遅延アークおよび 2 つのタイミングピンのみを含む。

#### 【 0 0 4 4 】

例えば、 p マージおよび s マージの一方のマージングが実行されると、関連した遷移マトリクスもまた変化し得る。

#### ( シーケンシャルモデル )

このセクションは、シーケンシャルモデルを処理するために、図 4 b のセクション 4 7 6 および 4 7 8 をインプリメントするためのアプローチの実施形態を記載する。チェックアークは、少なくとも 2 つのメイングループに分類化され得る。あるグループは、「セットアップ」グループと呼ばれる、ここではデータ信号が基準またはクロック信号より以前に到達するように予測される。「セットアップ」グループの例は、セットアップ、リカバリ、スキューリ、クロック分離などである。他のグループは、「ホールド」グループと呼ばれ、ここでは、基準信号がデータ信号より以前に到達するように予測される。「ホールド」グループの例は、ホールド、および移動である。

#### 【 0 0 4 5 】

レジスタまたはフリップ - フロップは移動され、上記のように、ラッチ情報の一部は、ラッチ挙動を持続するように維持される。この実施形態において、全てのラッチ入力ピンおよびラッチ出力ピンは、維持される。シーケンシャルエレメントの移動に関連付けられた操作は、組み合わせモデルに対する操作に類似する。遅延アークとチェックアークとの間の相互作用を正確にかたどるために、2 つの異なる s マージ操作が用いられる：前方 s マージ 4 7 8 および後進 s マージ 4 7 6 。シーケンシャル p マージは、組み合わせ p マージと本質的に同様である。この差は、同様のタイプのチェックアークのみがマージされることである。

#### 【 0 0 4 6 】

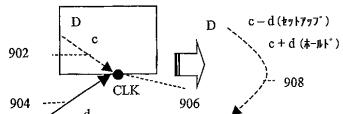

レジスタ / ラッチクロックピンが移動されるとき、前方 s マージ操作が用いられる。遅延アークおよびチェックアークがクロックピンに集まるとき、新しいチェックアークは、古いデータ信号 ( チェックアークの信号端 ) と新しいクロック信号 ( 遅延アークのソース ) との間に新しいチェック値を表すように生成される。仮に、  $d$  は遅延アーク上の遅延アークを示し、  $c$  はチェックアーク上のチェック値を示すとする。一実施形態において、セットアップグループに対して 2 つのアークをマージするとき、新しいチェック値は  $c - d$  になり、ホールドグループに対して、新しいチェック値は  $c + d$  になる。

#### 【 0 0 4 7 】

図 9 は、前方 s マージ操作を示す。この図は、レジスタに対するタイミンググラフを示す。レジスタにおいて、チェックアーク 9 0 2 および遅延アーク 9 0 4 は、クロックピン 9 0 6 に関連付けられる。前方 s マージ操作を用いて、2 つのアークをマージし、クロックピン 9 0 6 を移動することによってこのタイミンググラフを縮小させる。マージされた

10

20

30

40

50

アーク 908 は、セットアップグループに対してチェック値  $c - d$  およびホールドグループに対して  $c + d$  を有するチェックアークである。

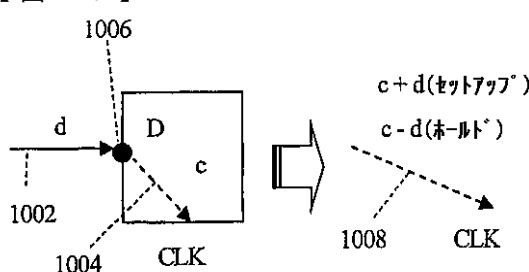

#### 【0048】

レジスタ入力ピンが移動されるとき、後進  $s$  マージ操作が用いられる。遅延アークおよびチェックアークがデータピンに集まるとき、新しいアークは、遅延アークのソースと古いクロック信号との間に新しいチェック値を表すように生成される（チェックアークの基準端）。セットアップグループに対して、新しいチェック値は  $c + d$  になり、ホールドグループに対して、新しいチェック値は  $c - d$  になる。

#### 【0049】

図 10 は後進  $s$  マージ操作を示す。この図は、レジスタに対するタイミンググラフを示し、レジスタにおいて、チェックアーク 1002 および遅延アーク 1004 は、入力ピン 1006 に集まる。後進  $s$  マージ操作を用いて、2 つのアークをマージし、入力ピン 1006 を移動することによってこのタイミンググラフを縮小する。マージされたアーク 1008 は、セットアップグループに対してチェック値  $c + d$  およびホールドグループに対して  $c - d$  を有するチェックアークである。

#### （セルフループチェックアーク）

信号端および基準端が共に同様のピンを差す場合、ある「セルフループ」チェックアークがある。このようなタイミングチェックは、限定されないが、クロック上に最小パルス幅（MPW）および最小周期（MP）チェックを含む。前方および後進  $s$  マージ操作を用いることによって、このようなセルフ・ループチェックアークは、正確なクロックパス遅延（非対称の起伏 / 落ち込みを含む）およびスルー伝播を用いてかたどられ得る。

#### 【0050】

図 11 は、MPW セルフループチェックアーク 1102 を有するクロックパスのタイミンググラフフラグメントの例示を示す。入来遅延アーク 1104 は、セルフループチェックアーク 1102 の信号および基準端共に同じピン 1106 に接続されるように示される。

#### 【0051】

セルフループチェックアークは、入来遅延アークを概念的に複製することによってセルフループを有さないチェックアークとして「膨張」され得る。遅延アーク 1104 は、2 つのアーク  $d1 1104a$  および  $d2 1104b$  を生成するように複製される。アーク 1102 の各端部を複製されたアーク  $1104a$  および  $1104b$  に接続することによって、チェックアーク 1102 は変形され、故に、セルループアークになる。

#### 【0052】

従って、後進  $s$  マージは、遅延アーク  $d1 1104a$  およびチェックアーク 1102 上で実行され、マージされたチェックアーク 1106 を生成し得る。次に、前方  $s$  マージ操作は、遅延アーク  $d2 1104b$  およびチェックアーク 1106 上で実行される。これは、クロックパス遅延およびスルー伝播を正確に反映する、ポート CK における別のセルフループチェックアーク 1108 につながる。遅延アークまたはピンは、ここで実際に複製される必要がないことに留意されたい。図 11 において、説明のためのみの複製である。

#### （遅延計算およびロード特徴付け）

一実施形態において、遅延計算は、 $s$  マージおよび  $p$  マージ操作の間に実行される。この操作中に、スルー、ロード、および / またはデータ値の固定レンジを越えて計算される。例えば、ロードレンジは、出力ポートで終端する遅延アークに利用され得る。レンジは、ある遅延アークまたはチェックアークから他のものへ変化し得る。

#### 【0053】

得られるロードおよびスルー値の精度のよいレンジに対して、所望される。表ベースのライブラリ（例えば、TLF、.lib、または ALF）に対して、ライブラリテンプレートにおいて明確化されるように、レンジが得られ得る。等式ベースのライブラリ（例えば、OLA）に対して、レンジは特徴付けられ得る。次のセクションは、スルー / ロード

10

20

30

40

50

レンジ値を得るためのアプローチの実施形態を記載する。

【0054】

表ベースのライブラリに対して、ロードレンジは、遅延アークに関連付けられた表のテンプレートにおいて観測することによって得られ得る。（例えば、T L F ライブラリから）以下のテンプレートと共に遅延アークを考慮する。

【0055】

```

Timing_Model ("Model"

(Spline

(Input_Slew_Axis

0.0500, 0.3000, 0.5500, 0.8000, 1.0500) 10

(Load_Axis

0.0820, 0.1639, 0.3279, 0.6557, 1.3115, 2.623

0, 5.2459)

data()

)

)

```

このテンプレートの初期のロードレンジは、以下の7つの値、0.0820、0.1639、0.3279、0.6557、1.3115、2.6230、5.2459からなる。

【0056】

スルーロードレンジを決定するためのアプローチは、許容値を確立して、レンジに対する所望の精度値を明確にすることである。このアプローチにおいて、初期レンジにおける全ての値は、それが所望の精度レベルを満たす間に降下され得る場合、チェックするように評価される。一旦、値がそのレンジから降下されると、遅延および出力スルーレンジは、その近傍からの点を用いて補間される必要がある。補間された遅延および出力スルーレンジが、特定の許容限界内にある場合、値はそのレンジから降下される。このアプローチにおいて、許容パーセンテージが高くなれば、より多くの値がそのレンジから外れ得る。このアプローチは、処理するための入力スルーレンジおよび出力ロード値を共に縮小する。

【0057】

等式ベースのライブラリに対して、反復加重二分割法 (iterative\_weighted\_bisectioning\_technique) が用いられ得る。プロセスは、初期レンジ {0, MaxVal} で開始する。MaxVal は、最大出力ロードまたは入力スルーレンジであり得、ユーザによって明確にされ得る。レンジは、中間点において2つのレンジに分割される。その後、全ての既存のサブレンジによって、それ以上の加重を有するレンジが選択される。加重は、レンジの2つの端点間の出力遅延（または出力スルーレンジ）において勾配がある。所望の数のデータポイントが得られるまで、この二分割は継続される。一旦、レンジが決定されると、表ベースのライブラリに対して提案される許容ベースの剪定によってさらに縮小され得る。

【0058】

別のアプローチにおいて、レンジにおけるロード値の数が出力ロードの最大数 (N) を超える場合、その後、そのレンジは、隣接した近傍点への最も長い加重距離を有するN値を選択することによって剪定され得る。レンジが上向きの順序にソートされる場合、レンジにおける (i) 番目の値に対する距離は、(i + 1) 番目の値と (i - 1) 番目の値との間のロード値における差によって見出される。レンジにおける第1の値に対する距離は、無限大になるように仮定され、最後の値に対する距離は無限大の半分になるように仮定される。これは、端点により高い加重を与えるためである（より高い加重は、レンジ置ける第1の値に与えられる）。上記の例示に対して、N = 6 と想定する。距離表は、以下のように示される。

【0059】

【表1】

|      |        |        |        |        |        |        |         |

|------|--------|--------|--------|--------|--------|--------|---------|

| ロード値 | 0.0820 | 0.1639 | 0.3279 | 0.6557 | 1.3115 | 2.6230 | 5.2459  |

| 距離   | Inf    | 0.2459 | 0.4918 | 0.9836 | 1.9673 | 3.9344 | Inf / 2 |

最も長い距離を有する6の値を選定することによって、レンジは、0.0820、0.3279、0.6557、1.3115、2.6230、5.2459に剪定され得る。

(複数のファンインおよびファンアウトの考慮)

10

入力ポートは、再改装バスにつながり得、これは、pマージにおいて問題を生じ得、再改装バスが異なるスルーバリューと共に関連付けられる。同様に、出力ポートは、マルチプレクサを含む設計から生じる複数のファンインバスを有し得る。この理由のため、全ての遅延アーケークおよび入力ポートから発散するチェックアーケークに対して同様のスルーレンジおよび出力ポートを終端する全ての遅延アーケークに対する同様の出力ロードレンジを用いることは適切である。レンジは、入力/出力ポートによって異なり得る。これを適応させるために、スルーバリュー(ロード)範囲は、入力ポートから発散する(出力ポートで終端する)全ての遅延アーケークおよびチェックアーケークに対して特徴付けられる。その後、全てのスルーバリュー/ロード値は、各入力/出力ポートに対するリストにマージされる。

(チェックアーケークの考慮)

20

本発明の実施形態のBFSトランザクションプロセスは、ピンへの遅延アーケークの入力が全て、ピンが移動される前に処理されることを確実にする。しかし、チェックアーケークは、時として、特別な考慮を必要とする。なぜなら、完全にチェックアーケークを特徴付けるために、スルーバリューのレンジが信号端および基準端において共に利用可能にされるからである。いくつかの場合において、BFSトランザクションは、全てのチェックアーケークの信号端および基準端が共に、前方sマージまたは後進sマージ操作以前に処理されることを保証しない。

#### 【0060】

30

例えば、図13のタイミンググラフを考慮する。ピンc1が移動されると、チェックアーケークの信号端(d2)から生じるスルーバリューのレンジは、利用可能に成らない。一実施形態において、チェックアーケークは、全ての可能なスルーバリューについて特徴付けられる(ほとんどの場合、6よりも少ないスルーバリューはチェックアーケークを特徴付けるためには、十分な値である)。ピンd2が処理された後で、チェックアーケークは、適切なスルーバリューに対して再び特徴付けられる。代替の実施形態において、c1の移動後のd2におけるスルーバリューのレンジが推測される。ピンd2が処理されるときのみ、スルーレンジは利用可能になる。その後、チェックアーケーク遅延は、補間を実施することによって再計算され得る。

(挿入遅延)

40

挿入遅延は、クロックソースポートからレジスタおよびラッチに属する内部クロックピンまでの遅延について言う。挿入遅延は、セル内に組み込まれるクロックツリーを介するファースト(早い)バスおよびスロー(遅い)バスの特徴付けをイネーブルにする。挿入遅延を計算するために、さらなる計算が、内部クロックピンにおいて実行され得る。一実施形態において、プロセスがレジスタまたはラッチにおいてクロックピンに遭遇するときに、挿入遅延は計算される。下記は、本発明の一実施形態において挿入遅延を計算するための擬似コードである。

#### 【0061】

```

/* ピンは、レジスタまたはラッチ用の内部クロックピンである */

computeInsertionDelay(pin) {

Paths = tracePathsToClockSourcePin(pin);

for each path in paths {

addInsertionDelay(src pin of path, path);

}

}

```

10

20

30

40

50

}

パスは、遅延アークのリストである。addInsertionDelay()の手続は、パス遅延を計算し、かつ、クロックソースポートであるパス発生ピンにそのパス遅延を格納する。前述したsマージおよびpマージ操作は、このルーチンにおいて用いられ得る。実質的に、ラッチまたはレジスタのクロックピンに遭遇するとき、プロセスは、オリジナルクロックソースまでさかのぼってパスをトレースし、かつ、最悪の挙動を有するあるピンをトラッキングする。

#### (縮小の例示)

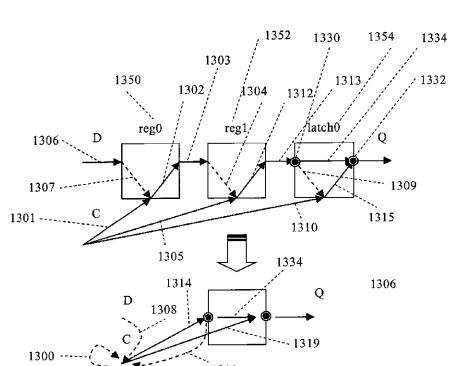

図14は、2つのレジスタ1350、1352、および1つのラッチ1354を有する回路上のグラフ縮小の例示を示す。この例示において、アーク1306および1307は、後進sマージ操作を用いてチェックアーク1308にマージされる。アーク1301、1302、1303、1304、および1305は、sマージ、後進sマージ、および前方sマージ操作の組み合わせを用いてセルフループチェックアーク1300にマージされる。アーク1309および1310は、前方sマージ操作を用いてアーク1311にマージされる。アーク1305、1312、および1313は、sマージ操作を用いてアーク1314にマージされる。アーク1305が、最終タイミングモデルにおいて、結果としてアーク1300および1314を共に生じる、2つの個々の操作のセットにかかわることに留意されたい。アーク1310および1313は、sマージ操作を用いてアーク1319にマージされる。

#### 【0062】

ピン1330および1332は、ラッチ1354の入力および出力ピンであるので、それらはモデルから移動される。最終モデルは、ラッチ挙動を持続するために2つの内部ピン1330および1332を含む。reg1 1352におけるセットアップ/ホールドが、クロックCにおけるセルフループセットアップ/ホールドチェックアークとしてモデリングされることに留意されたい。

#### (モデルライタ)

このセクションは、タイミングモデルを書き込むためのプロセスおよびメカニズムの実施形態を記載する。モデルライタは、所望のフォーマットにおけるピン、遅延アーク、およびチェックアークを外へ放出するために縮小したモデルグラフを越えるか、または渡る。

#### 【0063】

縮小モデルサイズに対して、タイミングモデルは、異なる遅延アークおよびチェックアークの間で共有され得る。あるアプローチにおいて、これは、遅延テーブルをハッシングすることによって達成される。さらに、モデルサイズは、遅延テーブルをソートおよび縮小させることによって縮小され得る。スルーバリューがソートされ、複製がモデルグラフリデューサにおいて移動され得るが、いくつかの最終的なチューニングは、モデルリデューサが全ての遷移の可能性（起伏、降下、早い、遅い）を考慮するので、いくつかの最適化をし損なう場合、いくつかの最終的なチューニングが必要とされ得る。遅延テーブルに値が与えられると、モデルライタメカニズムは、軸に現れ、かつ複製のソーティングおよび移動を実行するスルーバリューを調べ得る。

#### 【0064】

他でより詳細に記載されるように、モデルライタメカニズムは、a)例外に関連付けられた全ての内部ピンを持続し、b)モデルI/Oポートにおける例外をダミーの内部ピンに格納し、かつ、c)モデルの一部として新しい例外を書き出す。これは、アサーションおよび制約の持続を容易にする。なぜなら、例外は、タイミングモデルに挿入されるからである。一実施形態において、オリジナル回路上にあるユーザのアサーションだけが、モデルの一部として書き込まれる。

#### (アサーションハンドラ)

このセクションは、本発明の一実施形態においてどのようにアサーションがモデル抽出に対して処理されるかを記載する。説明のため、アサーションの扱いは、モデル抽出のグ

10

20

30

40

50

ラフ縮小のコンテキストおよび内部ピンのコンテキストに記載される。しかし、アサーションを扱うための本発明のコンセプトは、他のモデル抽出アプローチおよび非内部ピンに対して等しく利用可能であり（例えば、ブラックボックスモデルのパストレーシングに対するアサーションを扱う）、故に、説明のため、かつ、データの異なるソースからの抽出（例えば、ネットリスト、タイミンググラフなどからのタイミングモデルの抽出）のために本明細書中に開示される特定の実施形態に限定されるべきでないことに留意されたい。

#### 【0065】

例えば、バジェッタといったツールに由来するアサーションである「生成されたアサーション」の例は、

- ・クロック到達時刻

- ・クロック必要時間

- ・データ到達時刻

- ・データ必要時間

- ・スルー時間

- ・一定のタイミング

- ・駆動抵抗

- ・駆動セル

- ・入力遅延

- ・出力（外部）遅延

を含む。ユーザによるアサーションのセットである「ユーザアサーション」の例は、誤ったパス、マルチサイクルパス、またはディセーブルタイミングを含む。

#### 【0066】

公知のモデル抽出アプローチにおける問題の1つは、オリジナルアサーション／制約が抽出されたモデルに適用し難いことである。内部ピンの損失または名称変化は、この困難性に起因する。

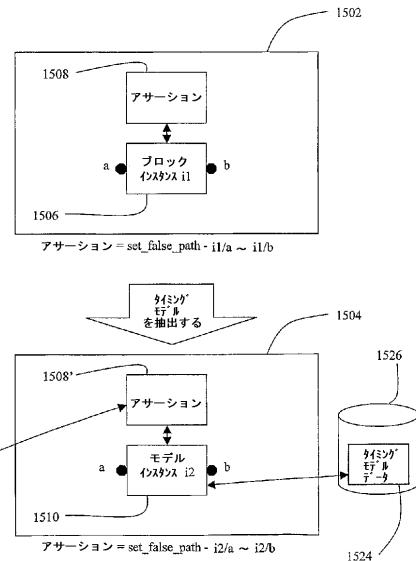

#### 【0067】

図15は、公知のアプローチのこの欠点を説明する。ピンaおよびbを有するインスタンスi1として例示される回路ブロック1506を有するオリジナルネットリスト1502を考慮する。トップレベルにおけるアサーション1508は、以下のように存在する：「set\_false\_path - from i1/a - to i1/b」。異なるインスタンスにおいて、抽出されるタイミングモデルが例示される場合、アサーションは、ピンの名称における変化を反映するために異なる様態で変更されるか、または調達される必要がある。従来のモデル抽出において、マニュアルプロセスを使用して、抽出されるモデル1510に対してアサーション1508の適切な関連性を保証する。この例において、アサーション1508は、set\_false\_path - from i2/a - to i2/bのように修正されたアサーション1508'に変換される。一般的な回路設計は、極めて多くの回路エレメント（可能性的に100万の数）を制約し、これらのエレメントが、アサーションが対応するエレメントに適切に関連付けられることを保証するよう検索され、再検討される必要があるので、手動訂正に依存する任意のプロセスおよびアサーションの関連性がエラーの導入または監視の可能性を伴う単調かつ時間消費の手続になる。さらに、一旦、アサーションが訂正されると、それらは、タイミングモデル1524の格納口ケーション1526とは別の格納口ケーション1522に格納される。これは、少なくとも2つの個々のデータ格納口ケーションは、タイミングモデル部分のモデル情報を取り出すようにアクセスされる必要があることを意味する。

#### 【0068】

本発明の一実施形態においてこれらの問題を解決するために、アサーションに関連付けられた内部ピンが維持される。これにより、オリジナルアサーションは、変更がないか、またはほとんど変更がないモデルに適用されることが可能になり、複数のブロックにかかるアサーションを含む。また、本アプローチは、それを、オリジナルタイミング制約／アサーションに持続させ、かつ適用し易くさせる。タイミング制約／アサーションは、モデ

10

20

30

40

50

ルの一部として観測され、新しい制約のセットは、モデル抽出プロセスの一部として自動的に生成され得る。タイミング制約のサポートは、トップダウンの階層的なフローにとって重要である。

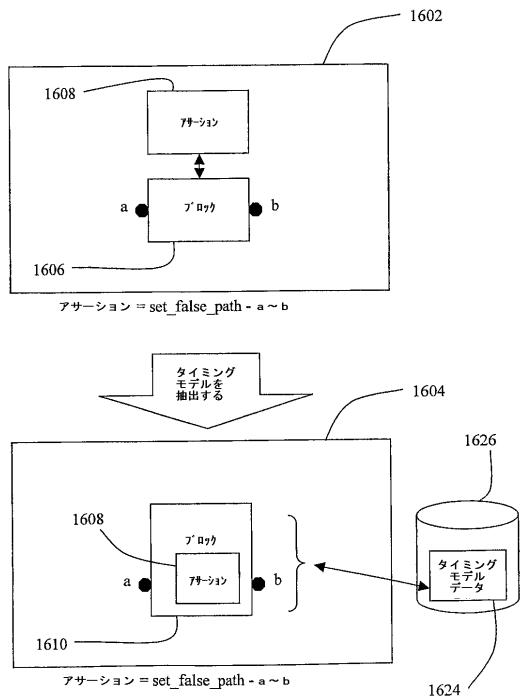

【0069】

図16は、本発明の実施形態を説明する。ここで、タイミンググラフ部分1602は、ピンaとbとの間の回路ブロックを含む。アサーション1608は、前の例、「set\_false\_path - from a - to b」に類似する。しかし、モデル抽出が実施形態されるとき、ピンaおよびbは、わざと移動、リネーム、または他の変更から外される。なぜなら、アサーション1608は、これらのピンに関連付けられるように特定されるからである。従って、ピンaおよびbは、抽出したモデルグラフ1610において維持される。このアプローチは、本質的に、オリジナルアサーション1608の正当性および利用可能性を抽出したモデルにおいて対応するピンaおよびbに持続する。

【0070】

さらに、アサーションは、モデルグラフ1610およびタイミングモデル1624に書き改められるタイミングに自動的に書き込まれ、かつ、取り付けられ得る。この情報は、例えば、タイミングモデルにおけるセルレベル属性として格納され得る。従って、タイミングモデル1624の格納されたバージョンは、タイミングデータおよびタイミングモデルに対応する関連付けられたアサーションデータを共に含む。モデルは、オリジナルアサーションの統合性をより精度良く保証する。アサーションは、モデルの一部になり、モデルが読み込まれるときに、自動的に適用される。

【0071】

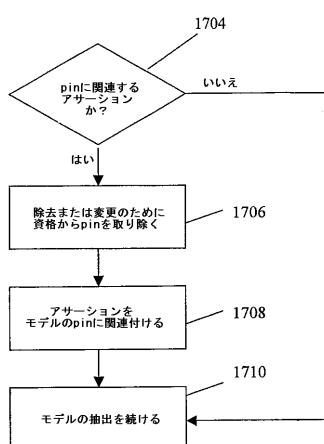

図17は、アサーションを処理するためのプロセスの実施形態のフローチャートを示す。図1704において、特定のピンがアサーションに関連付けられるかどうか、決定される。そうである場合、次に、ピンは維持され、移動の適性から除去される(1706)。1708において、特定されたピンは、アサーションに関連付けられるので、モデルが書き込まれるとき、アサーションは、自動的にモデルに組み込まれる。1710において、通常モデル抽出プロセスが継続する。

【0072】

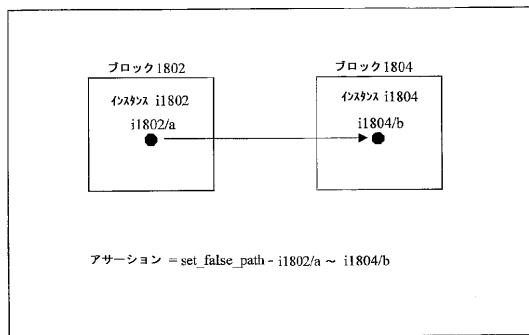

図18を参照し、アサーションが複数のブロックにかかるときの状況を考慮する。ブロック1802において第1のピンi1802/aと共に2つのブロック1802および1804、ならびにブロック1804において第2のピンi1804/bが示される。アサーションは、「set\_false\_path - from i1802/a - to i1804/b」として存在すると仮定する。

【0073】

この実施形態において、複数ブロックにわたって伸長されるアサーションは、それぞれのブロック内の関連付けられたピンの全てがタイミングモデル内で保持されるようにする。従って、ピンi1802/aおよびi1804/bが、ブロック1802および1804のモデル抽出プロセスの間保持され得る。1つのブロックの複数のピンに関わる状況において、複数ブロックのアサーション関連のピンを保持するこのアプローチは、モデル抽出の間、タイミング挙動が適切に保存されることを確実にするために役立つ。アサーション情報は、抽出後、タイミングモデルに自動的に書き込まれる。あるアプローチにおいて、アサーションが1より多いブロックにまたがる場合、モデルが読み込まれた後、このようなアサーションに変更を加えないことがある。

【0074】

(階層ピンアサーション)

回路内に見られるピンには少なくとも2つのタイプがあり得る。インスタンスピップンおよび階層ピンがある。階層ピンは、階層境界を確立する。信号が階層ピンを交差する場合、ある階層から他の階層へと移動する。階層ピンは、境界交差情報のプレースホルダーであり、基礎となる物理的なピン表現を有さない。

【0075】

10

20

30

40

50

アサーションは、インスタンスピンだけでなく、階層ピンにも関連付けられ得る。多くのタイミングツールについて、階層ピンはタイミンググラフが作られるときには現れないことがある。本発明のある実施形態において、アサーションが階層ピンと関連付けられる場合、タイミンググラフは、階層ピンの新たに作製された内部ピンを挿入するために変更され、アサーションはこれらの新たなピンの点から再表現される。このマッピングは、概して、異なるタイプのアサーションをサポートするために用いられる。スルーを保存するゼロ遅延アーク（すなわち、出力スルー = 入力スルー）は、これらの新たな「ダミー」は内部ピンに向かって、またはそこから伸長される。

## 【0076】

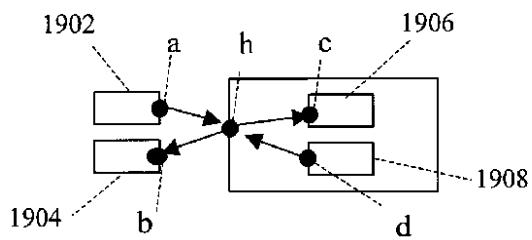

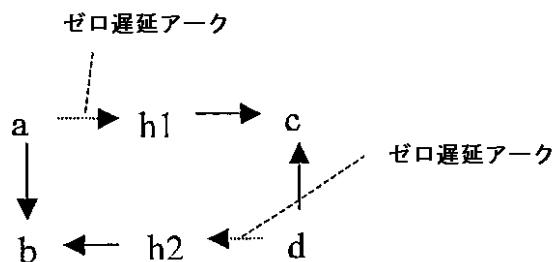

図19aに示す例示的な回路を考える。図の矩形のそれぞれは、インスタンスを表す。インスタンス1902、1904、1906および1908が示されている。ピンは黒い点で表されている。インスタンスピン「a」、「b」、「c」、および「d」が示されている。ピン「h」は、階層ピンである。

10

## 【0077】

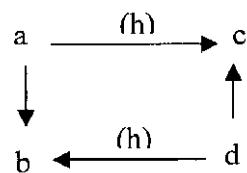

この回路のタイミンググラフを図19bに示す。ここで、階層ピン「h」は、2つの遅延a -> cおよびd -> bを通じてアクセスされ得る。

## 【0078】

ピン「h」についてのスルーピンアサーションがある場合、以下のように考えられる。

## 【0079】

```

set_false_path - from a -> h through h - to c

```

20

抽出されたモデルにおいてこのアサーションを捕捉するため、2つの新たな内部ピンがモデルに導入される。これらの新たなピンは、「ダミー」内部ピンと考えることができる。この例において、a -> bおよびa -> c遅延がd -> bおよびd -> c遅延とは異なるので、2つのピンが用いられる。新たな内部ピン「h1」および「h2」を用いて伸長されたタイミンググラフを、図19cに示す。新たなピンh1およびh2が導入される場合、新たなアークa -> h1およびd -> h2も導入される。この例において、a -> h1およびd -> h2は、ゼロ遅延アークを表すことに留意されたい。h1 -> cおよびh2 -> b遅延は、それぞれ、元のタイミンググラフにおけるa -> cおよびd -> b遅延と同じである。

## 【0080】

ピン「h」が2つのピン「h1」および「h2」に分割されるので、元のアサーションは以下のように変換される。

30

## 【0081】

```

set_false_path - from a -> h1 through h1 - to c

set_false_path - from a -> h2 through h2 - to c

```

階層ピンアサーションのサポートに関わる2つのアクションは、1) タイミンググラフ伸長、および2) モデルアサーションライターである。

## 【0082】

タイミンググラフ伸長は、タイミンググラフに新たな内部ピンを挿入して、階層ピンアサーションを正確に捕捉するプロセスのことを指す。これは、遅延アークの全てを通じて反復し、アサーションを有する階層ピンをサーチすることによって行われ得る。このような階層ピンが遅延アークにおいて見つけられる場合、タイミンググラフを伸長するために、貪欲な「見つけるか、なければ作製する」という戦略が用いられる。図12は、このようなプロセスの擬似コードを示す。コードには、2つのマッピングテーブルがある。

40

## 【0083】

1. 「map\_table」は、階層ピンを1つより多い新たに作製された内部ピンにマッピングする（1対複数マッピング）。これは、モデルアサーションライターにおいて用いられる。

## 【0084】

2. 「visited」は、階層ピンを一番最近作製された内部ピンにマッピングする

50

(1対1マッピング)。

【0085】

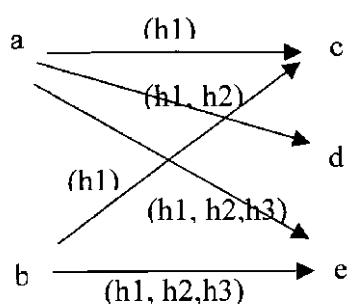

図20aに示すタイミンググラフを考える。階層ピンは、遅延アークにおいて、括弧に入れられている。タイミンググラフ伸長後の新たなタイミンググラフは、図20bに示すようなグラフになる。

【0086】

この例のmap\_tableのコンテンツは、以下のとおりである。

【0087】

```

h1 : h11, h12

h2 : h21, h22

h3 : h31, h32

```

10

モデルアーサーションライターは、モデルデータを変換し、モデル内のピンに関連付けられたアーサーション情報を書き込むメカニズムのことを指す。階層ピンアーサーションがサポートされていない場合、アーサーションライターは、所与の階層の全てを単純に横切り、全てのモジュールポートおよび全てのインスタンスピンにおいてアーサーションを書き出す。ある実施形態において、クロック定義のようなグローバルアーサーションは、例えば、ある特定の状況において、モデルの構築の間このようなアーサーションが有限ループにつながり得るので、書き込まれない。また、ある実施形態において、電気的ポートアーサーションが書き込まれる。

【0088】

階層ピンアーサーションの実現は、さらなるアーサーションの作製だけでなく、ピンの名前の変化につながり得る。これらのアクションの両方は、タイミンググラフを伸張する以前のアクションからのマッピングテーブルを用いて行われ得る。例えば、コールバック機能は、アーサーションを手に入れるために行われ得る方法と同様のこのアクションを行うと規定され得る。

20

【0089】

ピン「a」が2つの内部ピン「a1」および「a2」に分割された階層ピンである以下のアーサーションを考える。

【0090】

```

set_false_path - from a - to b

```

30

アーサーションライターは、このアーサーションを以下のアーサーションにマッピングする。

【0091】

```

set_false_path - from a1 - to b

set_false_path - from a2 - to b

(ポートアーサーション)

```

空間的な考慮がI/Oポートのアーサーションに対して為され得る。しばしば、モデルに関連付けられたアーサーションが、モデルが用いられる場合に自動的に手に入れられ、モデルが取り除かれるか、または、交換される場合に自動的に取り除かれることが所望される。ある特定の状況において、I/Oポートのアーサーションは、取り除くプロセスを困難にする。このため、ある実施形態において、I/Oポートのアーサーションは、以前のセクションの類似のグラフ伸長技術を用いて内部ピンに移動される。これによって、モデルが、入力および出力ポートに直接付けられたアーサーションを有さないことを可能にし、モデルをより自己充足的にする。

40

【0092】

入力ポートまたはbindi入力部分のアーサーションについて、この入力ポート用に新たな「ダミー」内部ピンが作製され、この入力ポートアーサーションがこのピンに転送される。新たな内部ピンは、入力ポートによって駆動される全てのピンを駆動し、ゼロ遅延アークを通じて入力ポートによって駆動される。また、入力ポートに関連付けられたチェックアークの全ては、ここで、新たな内部ピンに関連付けられている。

【0093】

50

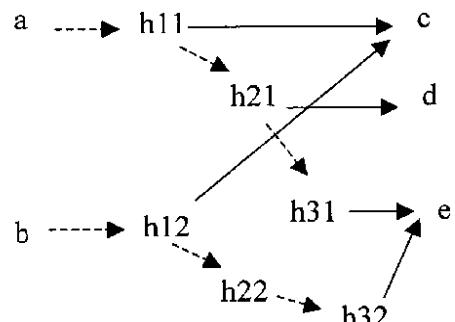

この伸長の一例が図 21 a に示されている。ここで、元のグラフ 2102 は、それぞれ、ピン b および c へのアーク 2104 および 2106 を有する入力ポート a を含む。ポート a に関連付けられたアサーションがあると仮定する。変更されたグラフ 2110 は、アーク 2104 および 2106 に関連付けられた、新たな内部ピン「a\_IN\_ASRT」を含む。ポート a に関連付けられていたアサーションは、ここで、ピン a\_IN\_ASRT に伸長する、新たなアーク 2112 が作製される。この新たなアークは、出力スルーハンドリングが入力スルーハンドリングと同じになるように、ゼロ遅延値を用いて作製される。

#### 【0094】

出力ポートまたは双方向出力部のアサーションは、同様に処理される。内部ピンは、出力ポートに供給する遅延アークがここで全て内部ピンに供給するように作製される。ポートにおける出力ロードへの依存性を保存するため、新たな内部ピンに入る遅延アークの全てについて、三次元テーブルが作製される。

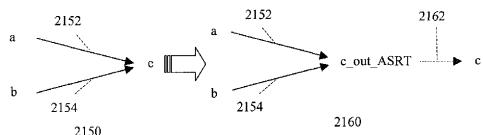

#### 【0095】

図 21 b に示す例を考える。元のタイミンググラフ 2150 は、ピン a からピン c に伸長する遅延アーク 2152 と、ピン b から出力ポート c に伸長する遅延アーク 2154 とを有する。変更されたグラフ 2160 は、新たなピン「c\_OUT\_ASRT」を含む。「c\_OUT\_ASRT」は、ポートアサーションが転送される新たな内部ピンである。新たなゼロ遅延アーク 2162 が、出力スルーハンドリングが入力スルーハンドリングと同じになるように、出力ポート c へのピン c\_OUT\_ASRT から作製される。ピン a からピン c\_OUT\_ASRT へのアーク 2152 と、ピン b からピン c\_OUT\_ASRT へのアーク 2154 とは、ポート c におけるロード依存性を捕捉するため、三次元遅延テーブルに関連付けられ得ることに留意されたい。

#### 【図面の簡単な説明】

#### 【0096】

【図 1】図 1 は、既存のブラックボックスモデリング方法を有する問題を示す。

【図 2 a】図 2 a は、例示のタイミンググラフを示す。

【図 2 b】図 2 b は、図 2 a の回路に対する例示の遷移マトリクスを示す。

【図 3 a】図 3 a は、モデル抽出をインプリメントするためのプロセスの実施形態のフローチャートを示す。

【図 3 b】図 3 b は、グラフ縮小のための処理の実施形態のフローチャートを示す。

【図 3 c】図 3 c は、モデル抽出のためのアーキテクチャの実施形態を示す。

【図 4 a】図 4 a は、本発明の実施形態によるグラフ縮小をインプリメントするための擬似コードの例を示す。

【図 4 b】図 4 b は、本発明の実施形態によるグラフ縮小をインプリメントするための擬似コードの例を示す。

【図 4 c】図 4 c は、本発明の実施形態によるグラフ縮小をインプリメントするための擬似コードの例を示す。

【図 5 a】図 5 a は、本発明の実施形態によるシリアルマージ (s マージ) 操作を示す。

【図 5 b】図 5 b は、本発明の実施形態によるシリアルマージ (s マージ) 操作を示す。

【図 6 a】図 6 a は、本発明の実施形態によるパラレルマージ (p マージ) 操作を示す。

【図 6 b】図 6 b は、本発明の実施形態によるパラレルマージ (p マージ) 操作を示す。

【図 7】図 7 は、p マージ操作が本発明の実施形態による重要なパスにおける変化を正確に反映することを示す。

【図 8】図 8 は、本発明の実施形態による回路部分を縮小するためのプロセスを示す。

【図 9】図 9 は、本発明の実施形態による前方 s マージ操作を示す。

【図 10】図 10 は、本発明の実施形態による後進 s マージ操作を示す。

【図 11】図 11 は、本発明の実施形態によるセルフループチェックの処理を示す。

【図 12】図 12 は、本発明の実施形態による階層的ピンアサーションのハンドリングを示す。

10

20

30

40

50

【図13】図13は、チェックアークの特別な処理を必要とするタイミンググラフ部分を示す。

【図14】図14は、本発明の実施形態による2つのレジスタおよびラッチを有する回路上のグラフ縮小の例を示す。

【図15】図15は、モデル抽出のアサーションハンドリングへの1つのアプローチを示す。

【図16】図16は、本発明の実施形態におけるモデル抽出のためのアサーションハンドリングへの代替のアプローチを示す。

【図17】図17は、アサーションハンドリングのためのプロセスの実施形態のフローチャートを示す。

10

【図18】図18は、本発明の実施形態による複数のブロックを越えるアサーションをハンドリングするためのアプローチを示す。

【図19a】図19aは、モデル抽出のための階層的ピンアサーションを指定するためのプロセスの実施形態を示す。

【図19b】図19bは、モデル抽出のための階層的ピンアサーションを指定するためのプロセスの実施形態を示す。

【図19c】図19cは、モデル抽出のための階層的ピンアサーションを指定するためのプロセスの実施形態を示す。

【図20a】図20aは、モデル抽出のための階層的ピンアサーションを指定するためのプロセスの実施形態を示す。

【図20b】図20bは、モデル抽出のための階層的ピンアサーションを指定するためのプロセスの実施形態を示す。

【図21a】図21aは、入力または出力ポートにおけるアサーションを指定するためのプロセスの実施形態を示す。

【図21b】図21bは、入力または出力ポートにおけるアサーションを指定するためのプロセスの実施形態を示す。

20

【図1】

Figure 1

【図2 a】

Figure 2a

【図2 b】

| CLK | Q  | 遷移 |

|-----|----|----|

| 上昇  | 上昇 | 真  |

| 上昇  | 下降 | 真  |

| 下降  | 上昇 | 偽  |

| 下降  | 下降 | 偽  |

Figure 2b

【図3 a】

Figure 3a

【図3 b】

Figure 3b

【図3c】

Figure 3c

【図4a】

```

reduceGraph(graph) {

changed = 1;

while (changed) {

changed = 0;

for each pin of graph in BFS order {

if (removePin(pin)) {

changed = 1;

}

}

postProcess(graph);

}

}

```

Figure 4a

【図4b】

```

removePin(pin) {

if (!canRemovePin(pin)) {

retainPin(pin);

return 0;

}

for each incoming delay arc d1 to pin {

for each outgoing delay arc d2 from pin {

if (d1 == d2) {

for each delay arc d parallel to d1 {

p-merge(d3, d1);

delete d1;

}

}

}

}

for each arc c1 having pin as sig {

c3 = backward-s-merge(d1, c1);

for each check arc c parallel to c3 {

p-merge(c3, c);

delete c;

}

}

for each arc c2 having pin as ref {

c4 = forward-s-merge(d1, c2);

for each check arc c parallel to c4 {

p-merge(c4, c);

delete c;

}

}

delete pin;

return 1;

}

```

Figure 4b

【図4c】

```

retainPin(pin) {

for each incoming delay arc d of pin {

compute_delay(d);

}

combine all incoming input slew at pin;

for each outgoing delay arc d from pin {

compute_delay(d);

}

}

```

Figure 4c

【図5a】

| 7-1       |           |           |

|-----------|-----------|-----------|

| 入力<br>スロー | 出力<br>スロー | アーケ<br>遅延 |

| is1       | os1       | d1        |

| 7-2       |           |           |

| 入力<br>スロー | 出力<br>スロー | アーケ<br>遅延 |

| os1       | os2       | d2        |

| 7-3       |           |           |

| 入力<br>スロー | 出力<br>スロー | アーケ<br>遅延 |

| is1       | os2       | d1 + d2   |

502

504

506

Figure 5a

【図5b】

Figure 5b

【図6a】

| 7-1   |       |       |

|-------|-------|-------|

| 入力スルー | 出力スルー | アーケ遅延 |

| is1   | os1   | d1    |

| 7-2   |       |       |

| 入力スルー | 出力スルー | アーケ遅延 |

| is1   | os2   | d2    |

| 7-3   |       |       |

| 入力スルー | 出力スルー | アーケ遅延 |

| is1   | os2   | d2    |

602

604

606

Figure 6a

【図6b】

Figure 6b

【図7】

Figure 7

【図8】

Figure 8

【図9】

Figure 9

【図10】

Figure 10

【図12】

```

expandGraphForHierarchicalPin(graph) {

initialize map_table;

for each hierarchical pin in graph {

initialize visited;

for each delay arc emanating from pin {

this_arc = arc;

for each hierarchical pin hpin with assertions on this_arc {

internal_pin =

findOrCreateInternalPin(hpin, visited, map_table);

this_arc = splitDelayArc(internal_pin, this_arc);

}

delete visited;

}

findOrCreateInternalPin(hpin, visited, map_table);

if (hpin already exists in visited) {

return the internal_pin stored in visited for hpin;

}

create a new internal_pin;

add a mapping from hpin to internal_pin in visited;

add an entry that associates hpin to internal_pin in map_table;

return internal_pin;

}

splitDelayArc(internal_pin, arc);

create a zero delay and slew-preserving arc

from source of arc to internal_pin;

create a new arc new_arc with the same delay characteristics as arc

from internal_pin to sink of arc;

return new_arc;

}

```

Figure 12

【図11】

Figure 11

【図13】

Figure 13

【図14】

**Figure 14**

【 図 15 】

**Figure 15**

【図16】

**Figure 16**

【 図 1 7 】

Figure 17

【図18】

Figure 18

【図19a】

Figure 19a

【図19b】

Figure 19b

【図19c】

Figure 19c

【図20a】

Figure 20a

【図20b】

Figure 20b

【図21a】

Figure 21a

## 【図21b】

Figure 21b

## 【手続補正書】

【提出日】平成16年9月3日(2004.9.3)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

## 【請求項1】

タイミングモデルを抽出する方法であって、

タイミンググラフを受け取るステップと、

該タイミンググラフを縮小することによって縮小されたモデルグラフを生成するステップと、

該縮小されたモデルグラフから該タイミングモデルを抽出するステップと

を包含する、方法。

## 【請求項2】

前記タイミンググラフの要素が保持のために識別される、請求項1に記載の方法。

## 【請求項3】

前記タイミンググラフの要素はタイミングピンを含む、請求項2に記載の方法。

## 【請求項4】

前記タイミングモデルのサイズを制限するアンカー点を識別するステップをさらに包含する、請求項1に記載の方法。

## 【請求項5】

前記アンカー点は、利得値に関連する、請求項4に記載の方法。

## 【請求項6】

前記利得値は、

$G_{a i n} = (\# \text{入来遅延アーク} \times \# \text{出て行く遅延アーク}) - \# \text{入来遅延アーク} - \# \text{出て行く遅延アーク}$

として規定される、請求項 5 に記載の方法。

【請求項 7】

ラッチ入力ピン、ラッチ出力ピン、ゲートッドクロック出力ピン、ゲートッドクロック入力ピン、アサーションに関連付けられているピン、ラッティネーブルピン、ラッチクリアピン、ラッチプリセットピン、出力から出力へのパスに関連付けられているピン、および、取り除かれる場合モデルサイズの増大と関連付けられているピンからなる群から選択される基準に基づく前記タイミンググラフの要素を保持するか否かを判定するステップをさらに包含する、請求項 2 に記載の方法。

【請求項 8】

前記縮小されたモデルグラフは、BFS順序の前記タイミンググラフにおけるピンを処理することによって生成される、請求項 1 に記載の方法。

【請求項 9】

前記タイミンググラフにおける組み合わせ回路部分が縮小される、請求項 1 に記載の方法。

【請求項 10】

シリアルマージ動作は、前記組み合わせ回路部分に対して行われる、請求項 9 に記載の方法。

【請求項 11】

パラレルマージ動作は、前記組み合わせ回路部分に対して行われる、請求項 9 に記載の方法。

【請求項 12】

前記パラレルマージ動作は、シリアルマージ動作の直後に続く、請求項 11 に記載の方法。

【請求項 13】

前記タイミンググラフにおける連続的回路部分が縮小される、請求項 1 に記載の方法。

【請求項 14】

前進 s マージ動作は、前記連続的回路部分に対して行われる、請求項 13 に記載の方法。

【請求項 15】

後進 s マージ動作は、前記連続的回路部分に対して行われる、請求項 13 に記載の方法。

【請求項 16】

自己ループチェックアークが前記タイミンググラフにおいて処理される、請求項 1 に記載の方法。

【請求項 17】

前記タイミングモデルを繰り返して抽出するために、ピンが取り除かれる、請求項 1 に記載の方法。

【請求項 18】

前記タイミングモデルを抽出する行動は、前記タイミングモデルを書き込むステップを含む、請求項 1 に記載の方法。

【請求項 19】

前記タイミングモデルを抽出する行動は、モデル構成要素を識別するように、前記縮小されたモデルグラフをウォーキングさせるステップを含む、請求項 1 に記載の方法。

【請求項 20】

アサーションに関連付けられている前記タイミンググラフにおけるピンは、前記縮小されたモデルグラフ内に保持される、請求項 1 に記載の方法。

【請求項 21】

アサーションは、前記タイミングモデル内の対応するピンに自動的に関連付けられている、請求項1に記載の方法。

【請求項22】

前記タイミングモデルは、アサーション情報を含む、請求項1に記載の方法。

【請求項23】

階層アサーションは前記タイミングモデル内に自動的に含まれる、請求項1に記載の方法。

【請求項24】

ポートアサーションが前記タイミングモデルに自動的に含まれる、請求項1に記載の方法。

【請求項25】

請求項1～24のうちのいずれか1つに記載の方法を実行するシステム。

【請求項26】

格納された命令のセットを有するコンピュータプログラム製品であって、該格納された命令のセットを行うことにより、請求項1～24のいずれか1つに記載の方法が実行される、コンピュータプログラム製品。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/US 02/38799

A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 G06F17/50

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 G06F

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                       | Relevant to claim No.                 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| X          | US 6 158 022 A (AVIDAN JACOB)<br>5 December 2000 (2000-12-05)<br><br>column 15, line 34 -column 16, line 3<br>column 18, line 55 -column 19, line 5<br>column 21, line 62 -column 22, line 14<br><br>--- | 1,2,15,<br>19,23,<br>24,37-39         |

| X          | US 5 535 145 A (HATHAWAY DAVID J)<br>9 July 1996 (1996-07-09)<br><br>column 3, line 4 - line 18<br>column 4, line 54 -column 5, line 10<br>column 6, line 5 - line 10<br>figures 9,10<br><br>---         | 1,2,11,<br>12,19,<br>37-39<br><br>-/- |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

|                                                                                                                                                                                           |                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Date of the actual completion of the international search<br><br>4 February 2004                                                                                                          | Date of mailing of the international search report<br><br>18/02/2004 |

| Name and mailing address of the ISA<br><br>European Patent Office, P.B. 5618 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Guingale, A                                |

| INTERNATIONAL SEARCH REPORT                         |                                                                                                                                                                                                                                                                                                                                                                                        | International application No.<br>PCT/US 02/38799 |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| C(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |

| Category *                                          | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                     | Relevant to claim No.                            |

| X                                                   | US 5 796 621 A (PRUESSE GARA ET AL)<br>18 August 1998 (1998-08-18)<br>column 2, line 9 - line 20<br>column 2, line 31 - line 55<br>column 3, line 30 -column 4, line 2<br>column 10, line 13 - line 39                                                                                                                                                                                 | 1,2,11,<br>19,37-39                              |

| A                                                   | US 5 581 473 A (RUSU STEFAN ET AL)<br>3 December 1996 (1996-12-03)<br>column 2, line 36 - line 65<br>column 4, line 23 -column 7, line 45<br>figures 4-7                                                                                                                                                                                                                               | 1-40                                             |

| P,X                                                 | MOON C W ET AL: "Timing model extraction<br>of hierarchical blocks by graph reduction"<br>PROCEEDINGS 2002 DESIGN AUTOMATION<br>CONFERENCE (IEEE CAT. NO.02CH37324),<br>PROCEEDINGS OF 39TH DESIGN AUTOMATION<br>CONFERENCE, NEW ORLEANS, LA, USA, 10-14<br>JUNE 2002,<br>pages 152-157, XP002268610<br>2002, New York, NY, USA, ACM, USA<br>ISBN: 1-58113-461-4<br>the whole document | 1-40                                             |

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US 02/38799

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| US 6158022                             | A 05-12-2000     | US 5740347 A            | 14-04-1998       |

| US 5535145                             | A 09-07-1996     | NONE                    |                  |

| US 5796621                             | A 18-08-1998     | NONE                    |                  |

| US 5581473                             | A 03-12-1996     | NONE                    |                  |

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,OM,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 ムーン, チョ ウー

アメリカ合衆国 カリフォルニア 92130, サン デイエゴ, バリアーレイク ウッズ

ドライブ 10698

(72)発明者 クリプラニ, ハリシュ

アメリカ合衆国 カリフォルニア 95070, セラトガ, ゴレタ アベニュー 12286

(72)発明者 ベルクヘール, クリシュナ プラサド

アメリカ合衆国 カリフォルニア 95070, セラトガ, ピアス ロード 20125

F ターム(参考) 5B046 AA08 BA03 JA01