(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-67393

(P2007-67393A)

(43) 公開日 平成19年3月15日(2007.3.15)

| (51) Int.C1.          | F 1        | テーマコード (参考) |       |

|-----------------------|------------|-------------|-------|

| HO1L 27/146 (2006.01) | HO1L 27/14 | A           | 4M118 |

| HO1L 31/10 (2006.01)  | HO1L 31/10 | A           | 5C024 |

| HO4N 5/335 (2006.01)  | HO4N 5/335 | E           | 5F049 |

|                       | HO4N 5/335 | U           |       |

審査請求 未請求 請求項の数 22 O L 外国語出願 (全 14 頁)

|              |                              |          |                                                                                                                    |

|--------------|------------------------------|----------|--------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-212759 (P2006-212759) | (71) 出願人 | 306023761<br>アバゴ・テクノロジーズ・センサー・アイ<br>ピー(シンガポール)プライベート・リミ<br>テッド<br>シンガポール国シンガポール768923<br>, イーション・アベニュー・7・ナンバー<br>1 |

| (22) 出願日     | 平成18年8月4日 (2006.8.4)         | (74) 代理人 | 100087642<br>弁理士 古谷 聰                                                                                              |

| (31) 優先権主張番号 | 11/197004                    | (74) 代理人 | 100076680<br>弁理士 溝部 孝彦                                                                                             |

| (32) 優先日     | 平成17年8月4日 (2005.8.4)         | (74) 代理人 | 100121061<br>弁理士 西山 清春                                                                                             |

| (33) 優先権主張国  | 米国(US)                       |          |                                                                                                                    |

最終頁に続く

(54) 【発明の名称】クロストークの少ないCMOSイメージセンサ

## (57) 【要約】

【課題】 高感度で、特に赤外波長に対する遠赤外線のクロストークが少ないCMOSイメージセンサを提供する。

【解決手段】 本発明のCMOSイメージセンサは、基板と、基板上のエピタキシャル層と、光を受容するための、エピタキシャル層内に拡がる複数のピクセルと、基板内に発生したキャリアがエピタキシャル層に移動するのを防ぐための、基板とエピタキシャル層の間の水平方向の障壁層と、エピタキシャル層内の電子の横方向への拡散を防ぐための、複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との少なくとも1つとを含むことを特徴とする。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

基板と、

前記基板上のエピタキシャル層と、

光を受容するための、前記エピタキシャル層内に拡がる複数のピクセルと、

前記基板内に発生したキャリアが前記エピタキシャル層に移動するのを防ぐための、前記基板と前記エピタキシャル層の間の水平方向の障壁層と、前記エピタキシャル層内の電子の横方向への拡散を防ぐための、前記複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との少なくとも 1 つとを含むCMOSイメージセンサ。

**【請求項 2】**

前記基板内に発生したキャリアが前記エピタキシャル層に移動するのを防ぐための、前記基板と前記エピタキシャル層の間の水平方向の障壁層と、前記エピタキシャル層内の電子の横方向への拡散を防ぐための、前記複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との少なくとも 1 つが、少なくとも前記水平方向の障壁層からなる請求項 1 に記載のCMOSイメージセンサ。

**【請求項 3】**

前記水平方向の障壁層が非常に高濃度にドープされたシリコンを含む請求項 2 に記載のCMOSイメージセンサ。

**【請求項 4】**

前記水平方向の障壁層が、ホウ素、アルミニウム、ガリウム、インジウム、燐、砒素、アンチモン、ゲルマニウム、炭素の 1 つ又は複数を含む請求項 3 に記載のCMOSイメージセンサ。

**【請求項 5】**

前記水平方向の障壁層が、炭素を含む層によって一方又は両方の側部を封入されている請求項 3 に記載のCMOSイメージセンサ。

**【請求項 6】**

前記水平方向の障壁層が、約 10 nm (100 オングストローム) から約 1 μm の厚みを有する請求項 3 に記載のCMOSイメージセンサ。

**【請求項 7】**

前記エピタキシャル層が、約 2 μm から約 20 μm の厚みを有し、前記複数のピクセルのそれぞれが、約 1 μm から約 15 μm の深さまで前記エピタキシャル層中に拡がる井戸部分を含む請求項 2 に記載のCMOSイメージセンサ。

**【請求項 8】**

前記エピタキシャル層内のドープが、空乏層の深さより下で傾斜し、キャリアを方向付ける電界をもたらす請求項 7 に記載のCMOSイメージセンサ。

**【請求項 9】**

前記基板内に発生したキャリアが前記エピタキシャル層に移動するのを防ぐための、前記基板と前記エピタキシャル層の間の水平方向の障壁層と、前記エピタキシャル層内の電子の横方向への拡散を防ぐための、前記複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との少なくとも 1 つが、少なくとも前記複数の横方向の障壁層からなる請求項 1 に記載のCMOSイメージセンサ。

**【請求項 10】**

前記複数の横方向の障壁層のそれぞれが、前記エピ層内に約 2 μm から約 20 μm の深さまで拡がる隣接するピクセル間の深いP-井戸からなる請求項 9 に記載のCMOSイメージセンサ。

**【請求項 11】**

前記複数の横方向の障壁層のそれぞれが、さらに前記深いP-井戸にトレンチを含む請求項 10 に記載のCMOSイメージセンサ。

**【請求項 12】**

前記複数の横方向の障壁層のトレンチが、ポリシリコン、酸化シリコン、二酸化シリコ

10

20

30

40

50

ンの少なくとも 1 つで充填されている請求項 1 1 に記載の CMOS イメージセンサ。

【請求項 1 3】

前記 CMOS イメージセンサが、前記基板内に発生したキャリアが前記エピタキシャル層に移動するのを防ぐための、前記基板と前記エピタキシャル層の間の水平方向の障壁層と、前記エピタキシャル層内の電子の横方向への拡散を防ぐための、前記複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との両方を含む請求項 1 に記載の CMOS イメージセンサ。

【請求項 1 4】

前記光が、赤外線波長範囲に対する遠赤外線の光を含む請求項 1 に記載の CMOS イメージセンサ。

10

【請求項 1 5】

基板と、

前記基板上のエピタキシャル層と、

それぞれが前記エピタキシャル層内に拡がる光を受容するための複数のピクセルと、

前記基板内に発生したキャリアが前記エピタキシャル層に移動するのを防ぐための、前記基板と前記エピタキシャル層の間の水平方向の障壁層と、

前記エピタキシャル層内の電子の横方向への拡散を防ぐための、前記複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層を含む CMOS イメージセンサ。

【請求項 1 6】

前記水平方向の障壁層が非常に高濃度にドープされたシリコンを含む請求項 1 5 に記載の CMOS イメージセンサ。

20

【請求項 1 7】

前記エピタキシャル層内のドープが、空乏層の深さより下で傾斜し、キャリアを方向付ける電界をもたらす請求項 1 6 記載の CMOS イメージセンサ。

【請求項 1 8】

前記複数の横方向の障壁層のそれぞれが、前記エピ層内に約  $2 \mu m$  から約  $20 \mu m$  の深さまで拡がる隣接するピクセル間の深い P- 井戸及び、当該深い P- 井戸のそれぞれの中の横方向のトレンチとからなる請求項 1 5 に記載の CMOS イメージセンサ。

【請求項 1 9】

前記光が、赤外線波長範囲に対する遠赤外線の光を含む請求項 1 5 に記載の CMOS イメージセンサ。

30

【請求項 2 0】

基板、その基板上のエピタキシャル層、そのエピタキシャル層内に拡がる複数のピクセルを含む CMOS イメージセンサを製造する方法であって、

前記基板内に発生したキャリアが前記エピタキシャル層に移動するのを防ぐための、前記基板と前記エピタキシャル層の間の水平方向の障壁層と、前記エピタキシャル層内の電子の横方向への拡散を防ぐための、前記複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との少なくとも 1 つを形成することを含む方法。

【請求項 2 1】

前記基板内に発生したキャリアが前記エピタキシャル層に移動するのを防ぐための、前記基板と前記エピタキシャル層の間の水平方向の障壁層と、前記エピタキシャル層内の電子の横方向への拡散を防ぐための、前記複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との少なくとも 1 つを形成することが、非常に高濃度にドープされたシリコンを利用して水平方向の障壁層を形成することを含む請求項 2 0 に記載の方法。

40

【請求項 2 2】

前記基板内に発生したキャリアが前記エピタキシャル層に移動するのを防ぐための、前記基板と前記エピタキシャル層の間の水平方向の障壁層と、前記エピタキシャル層内の電子の横方向への拡散を防ぐための、前記複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との少なくとも 1 つを形成することが、深い P- 井戸及び当該 P- 井戸内のトレンチを含む複数の横方向の障壁層を形成することを含む請求項 2 0 に記載の方法。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、クロストークの少ないCMOSイメージセンサに関する。

**【背景技術】****【0002】**

CMOS(相補性金属酸化膜半導体)イメージセンサは、赤外線波長(約700nm～約1mm)に対する遠赤外線の高いクロストークと低い感度との両方を欠点として有するが、これは、それらの波長における吸収の深さがピクセルの深さよりも遙かに大きいことによる。高いクロストークは、イメージセンサに当たる光がセンサのシリコンの表面の遙か下まで貫通し、電子-正孔対が基板の深部で発生することによって起こる。これらの深さは、ピクセルの収集領域の遙か下であり、したがって光生成キャリアが全ての方向に自由に拡散する。通常利用される基板に対する電子の拡散距離は約5μmであり、これにより、電子は比較的容易に隣接するピクセル内に拡散し、クロストークを生じさせる。低ドープエピ(エピタキシャル)層における拡散距離はさらに長くなることがあり、これは、不適切に設計されたイメージセンサで深刻なクロストークを生じさせることがある。赤外領域に対する遠赤外線におけるCMOSイメージセンサの感度は、深部で発生したキャリアが基板内で再結合し、消失することによって低下する。

**【0003】**

CMOSイメージセンサにおいてクロストークを少なくするための構造は、概して、可視光に対してよりよいカメラチップを製造することに基づく。通常、イメージセンサのドーパントの分布は、空乏領域ではない領域の疑似電界がホトダイオード内へキャリアを押し戻すように仕立てられている。イメージセンサ内のクロストークを少なくする公知の構造の例示は、深部アレイインプラントを設け、基板の上部に軽くドープされた薄い層を設け、赤色のピクセルの下方ではなく、青色と緑色のピクセルの下方に深部p+層を埋め込み、多層構造のある種の形態をもたらすことを含む。そのような構造は、クロストークを少なくする点では幾らか効果があるが、またイメージセンサの感度を低下させ、特に赤外波長に対する遠赤外線における感度を低下させる。

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

本発明は、高感度で、特に赤外波長に対する遠赤外線のクロストークが少ないCMOSイメージセンサ及び、そのCMOSイメージセンサを製造する方法を提供する。

**【課題を解決するための手段】****【0005】**

本発明のCMOSイメージセンサは、基板と、基板上のエピタキシャル層と、そのエピタキシャル層に拡がる光を受容するための複数のピクセルとを有する。また、イメージセンサは、基板内で発生したキャリアがエピタキシャル層へ移動することを防ぐための、基板とエピタキシャル層の間の少なくとも1つの水平方向の障壁層と、エピタキシャル層内で電子の横方向の拡散を防ぐための、複数のピクセルの隣接するもの同士間の複数の横方向の障壁層とを含む。

**【発明の効果】****【0006】**

本発明は、特に赤外波長に対する遠赤外線のクロストークが少なく、高い感度を有するCMOSイメージセンサ及び、CMOSイメージセンサの製造方法に関する。CMOSイメージセンサは、基板、その基板上のエピタキシャル層、光を受容するための、エピタキシャル層中に拡がる複数のピクセルを有する。またイメージセンサは、基板内に発生したキャリアがエピタキシャル層に移動するのを防ぐための、基板とエピタキシャル層の間の水平方向の障壁層と、エピタキシャル層内の電子の横方向への拡散を防ぐための、複数のピクセルの隣接するもの同士の間の複数の横方向の障壁層との少なくとも1つとを含む。

10

20

30

40

50

**【発明を実施するための最良の形態】****【0007】**

さらに、上記に加えて、及び上記に代えて、本発明は、実施形態を提供し、及び更なる特徴、利点をもたらす。それらの多くの特徴及び利点は、添付の図面を参照して以下の説明から明らかになる。

**【0008】**

本発明の例示的な実施形態は、特に赤外線波長に対する遠赤外線のクロストークが少なく、高い感度を有するCMOSイメージセンサを提供し、またそのCMOSイメージセンサを製造する方法を提供する。

**【0009】**

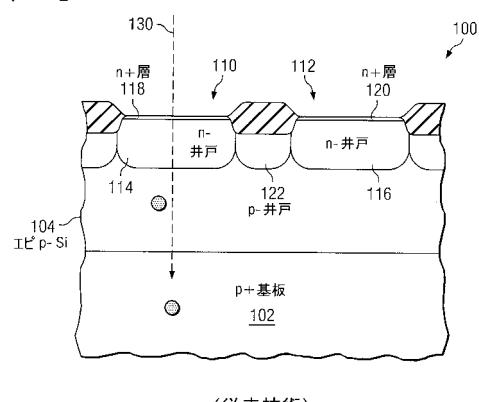

図1は、本発明の説明を補助するための、従来技術で公知のCMOSイメージセンサの部分を示す側面の概略的な断面図である。CMOSイメージセンサは、参照番号100により指示され、概して、基板102、基板102上のエピタキシャル(エピ)層104、アレイに配列されてエピ層104内に拡がる複数のピクセル(ピクセル110及び112の2つのみを図1に図解する)を含む。基板102及びエピ層104はどちらも、シリコン半導体材料からなるが、しかしながら基板102はP+(高濃度ドープP型)半導体材料から製造され、エピ層104はP-(低濃度ドープP型)半導体材料から製造されている。

**【0010】**

ピクセル110及び112は、ホトダイオードn-井戸114及び116をそれぞれ含み、またホトダイオードn-井戸114及び116上に堆積され、ピクセルに対する接触を改善する表面埋め込み領域118及び120をそれぞれ含む。ホトダイオードn-井戸114及び116は、N-(低濃度ドープN型)半導体材料から製造され、表面埋め込み領域118及び120は、N+(高濃度ドープN型)半導体材料から製造されている。P型半導体材料(図1に示すP-井戸122として指示する)は、ピクセル110及び112の間に設けられ、ピクセル間を絶縁する。

**【0011】**

図1に概略的に図解するように、赤外線波長に対する遠赤外線(以降、概して赤外線波長と称する)の光130がピクセル素子110に衝突すると、光はイメージセンサ100のシリコンの表面より遙か下まで貫通し、電子-正孔対が基板102の深部で発生する。これらの深さは、ピクセルの収集領域の遙か下であり、したがって光生成キャリアが全ての方向に自由に拡散する。高濃度ドープシリコン基板102のような一般的な基板に対する電子の拡散距離は約5μmであり、ピクセル112のような隣接するピクセルに多くの電子が比較的容易に拡散し、クロストークを生じる。さらに、CMOSイメージセンサ100内では、図1に概略的に図解するようにそのピクセル自体に進むエピ層内で発生したキャリアとは区別されるよう、深部で発生したキャリアの多くが基板内で再結合し、消失するので感度が低下する。

**【0012】**

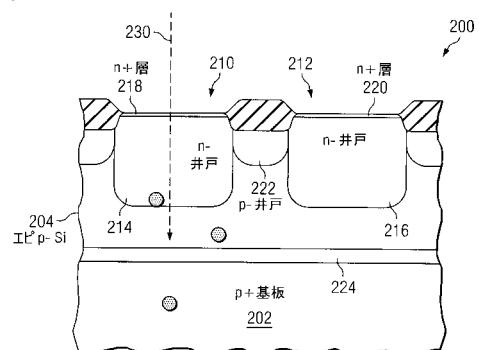

図2Aは、本発明の例示的な実施態様によるCMOSイメージセンサの部分を示す側面の概略的な断面図である。イメージセンサは、概して参照番号200により指示され、図1のCMOSイメージセンサと同様に、基板202と、エピ層204と、ホトダイオードn-井戸214及び216並びに表面埋め込み領域218及び220をそれぞれ含むとともにエピ層204内に拡がるピクセル210及び212とを含む。また図1のCMOSイメージセンサと同様に、基板202はP+シリコン半導体材料を含み、エピ層204はP-シリコン半導体材料を含み、ホトダイオードn-井戸214及び216はN-半導体材料から形成され、表面埋め込み領域218及び220はN+半導体材料から形成されている。P型半導体材料(P-井戸222として指示する)は、ピクセル210と212の間に設けられ、ピクセル間を絶縁する。

**【0013】**

図2AのCMOSイメージセンサ200は、図1のCMOSイメージセンサ100と異なり、エピ層204はエピ層104よりも厚く(例えば、図1のイメージセンサのような典型的なCMOSイメージセンサにおいては厚みが約2μm-6μmであるのに対して、約4μmから約20μmの厚みである)、より深いホトダイオードn-井戸214及び216を含む(図1のイメージセンサのよう

な典型的なCMOSイメージセンサでは、約  $1 \mu\text{m}$  -  $2 \mu\text{m}$  の深さであるのに対して、例えば、エピ層204内に約  $2 \mu\text{m}$  から約  $10 \mu\text{m}$  の深さまで拡がる）。より厚いエピ層及びより深いホトダイオードn-井戸により、空乏層の深さはピクセルの表面の遙か下まで貫通する。

#### 【0014】

エピ層204は、低濃度ドープP型材料であり、空乏層の深さより下にあり、キャリアに導かれる電界をもたらすように段階的にドープされている。加えて、水平方向の障壁層224が、エピ層の傾斜部分の下、基板202とエピ層204の間に設けられている。水平方向の障壁層224は、水平方向の障壁層の下方の基板202内で発生したキャリアが隣接するピクセルに及び隣接するピクセル内に拡散してクロストークが生じることを防ぐように機能する。

#### 【0015】

CMOSイメージセンサ200内のホトダイオードn-井戸214及び216の深さが増大するので、多くのキャリアの収集が可能となり、したがってイメージセンサの感度が増大する。同時に、水平方向の障壁層224の下の基板202内で発生する電子は、基板内にとどまり再結合する。したがって、CMOSイメージセンサ200は、図1のイメージセンサと比較して、赤外線波長におけるクロストークを低減し、またより高い感度を有する。

#### 【0016】

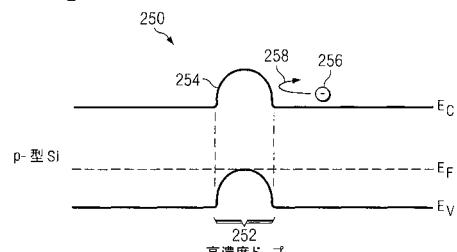

図2Bは、本発明の説明を補助するための、p型半導体における不純物添加障壁の機能を概略的に示す図である。示すように、半導体は、概して参考番号250により指示され、障壁254を形成し、電子256のような電子の移動を実質的に制御する高濃度ドープ領域252を含む。特に、矢印258により図解するように、電子256は障壁254を横切らない。このようにして、254のような障壁は、隣接するピクセル内に電子が拡散することを防ぎ、クロストークが生じることを防ぐのに利用される。

#### 【0017】

本発明の例示的な実施形態によれば、水平方向の障壁層224は、選択的な水平方向のドープによりもたらされる。高効率の障壁をもたらすために、厚みが約  $10 \text{ nm}$  ( $100 \text{ オングストローム}$ ) から約  $1 \mu\text{m}$  であり、約  $10^{19} / \text{cm}^3$  から  $10^{20} / \text{cm}^3$  の範囲でドープされた非常に高濃度にホウ素をドープした層が利用される。また、障壁層224は、通常のCMOS製造プロセスの熱量に耐えることが可能でなければならないが、これは、通常の熱量は相当のホウ素の拡散を生じさせ、それによってホウ素は広がり、イメージセンサのホトダイオード領域内に拡散し、感度を低下させるので、適合させることは困難である。また、この外方への拡散は、障壁層内のホウ素の量を低減させ、その効果を低下させる。本発明の例示的な実施形態によれば、約3パーセント未満の濃度の炭素とともに障壁層を合金化することによって、ホウ素の拡散を低減させる。

#### 【0018】

水平方向の障壁層224を設けることに関連して生じる他の問題は、ホウ素と炭素の双方を付加することが障壁層の厚みを制限するシリコンの格子定数を低下させることである。本発明の例示的な実施形態によれば、ホウ素の外方への拡散を制限する一方で、格子応力を低減させるために、より厚い障壁層を、Geの付加による歪み補正により成長させることができる。一般に、拡散を制限し、格子歪みを緩和するために、水平方向の障壁層224は、本発明の例示的な実施形態によれば、ホウ素、アルミニウム、インジウム、燐、砒素、アンチモン、ゲルマニウム、炭素の1つ又はそれ以上を含む。

#### 【0019】

本発明の例示的な実施形態によれば、また、水平方向の障壁層をもたらす高濃度にホウ素をドープされたSi層を、炭素を含む薄い層によって一方又は両方の側部をキャッピングすること又は封入することの何れかによりホウ素の外方への拡散を制限する一方で、格子歪みを低減することができる。さらに、Cドープ(炭素をドープされた)Si層でキャッピングすることにより、続く固体ソース拡散を実施することができる。

#### 【0020】

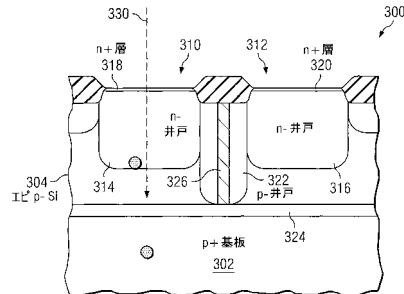

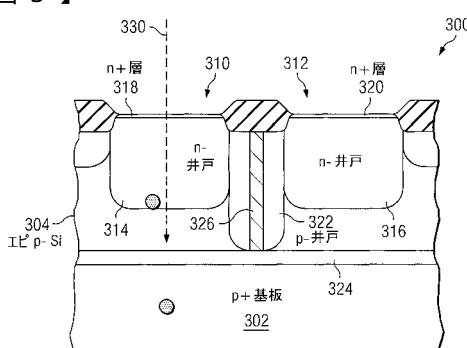

図3は、本発明のさらなる実施形態によるCMOSイメージセンサの部分を示す側面の概略的な断面図である。イメージセンサは、概して参考番号300により指示され、図2AのCMO

10

20

30

40

50

Sイメージセンサ200と同様であり、基板302、エピタキシャル層304、基板とエピタキシャル層の間の水平方向の障壁層324、ホトダイオードn-井戸314と316及び表面埋め込み領域318と320をそれぞれ含むピクセル310と312を含む。また、図2AのCMOSイメージセンサ200と同様に、基板302は、P+シリコン半導体材料を含み、エピ層304はP-シリコン半導体材料を含み、水平方向の障壁層324は非常に高濃度にホウ素をドープされた層を含み、ホトダイオードn-井戸314及び316はN-半導体材料から形成され、表面埋め込み領域318及び320はN+半導体材料から形成されている。P型半導体材料(P-井戸322として指示する)は、ピクセル310と312の間に設けられている。

## 【0021】

CMOSイメージセンサ300は、CMOSイメージセンサ200と異なり、隣接するピクセル310と312の間のP-井戸が図2AのP-井戸222よりも大幅に深く延伸し(図1のイメージセンサ100のような典型的なイメージセンサでは約1μm-2μmの深さであるのに対して、例えば、表面の下方約2μmから約20μmの深さまで)、加えて各P-井戸322内に深いトレンチ326を含む。

## 【0022】

特に、CMOSイメージセンサ200に設けられているようなより深いホトダイオード収集層に対して、エピ層内の横方向の拡散がクロストークを増大させる作用を有する。しかしながら、イメージセンサ300では、トレンチ326とともに深いP-井戸322が、隣接するピクセル間の横方向の障壁層として機能し、ピクセル間の横方向の拡散を防ぐ。トレンチは約0.5μmから約5μmの厚みを有し、P-井戸及びトレンチを含む横方向の障壁は、約1μmから約10μmの厚みを有する。

## 【0023】

本発明の例示的な実施形態によれば、深いトレンチ326は、P-井戸分離体322が設けられる前に、形成されることが好ましい。これにより、ホウ素を素子内の深部に入れることができる。代替的に、トレンチ充填物としてP型ポリシリコンを堆積させ、さらにポリシリコン内でP型ドーパントを形成して拡散させることができる。窒化シリコン及び酸化シリコンを含む他のトレンチ充填物を利用することもできる。また、ドープされたSiO<sub>2</sub>(ホウケイ酸ガラス)を利用してホウ素をもたらすこともできる。

## 【0024】

イメージセンサ300では、n-井戸からの空乏領域又はp-n接合はトレンチに達してはならない。これは、トレンチの表面が表面エネルギー準位を含み、空乏領域がトレンチに達するならば、漏れ電流が生じ流れるためである。実際に、これはホウ素を拡散させるための主たる理由である。ホウ素は、N-井戸からの空乏領域がトレンチに達するのを防ぐ。また、トレンチの存在しない実施形態では同時に、ホウ素はピクセルの絶縁に役立つ。

## 【0025】

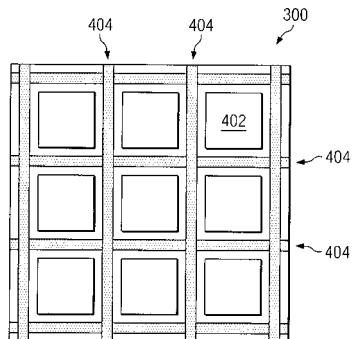

図4は、図3に図解するCMOSイメージセンサの部分を示す概略的な平面図である。特に、図4は、CMOSイメージセンサ300内の複数のピクセル402のそれぞれの間に設けられ、隣接するピクセル間で横方向の拡散を防ぐ横方向の障壁層を形成する図3のトレンチ326を画定するマスク404を図解する。

## 【0026】

したがって、CMOSイメージセンサ300は、より厚いエピ層及びより深いホトダイオード接合と関連して、赤外線波長における少ないクロストーク及び高い感度の双方をもたらす水平方向の障壁層324と、隣接するピクセル間の深いP-井戸324及びトレンチ326によって画定され、より深いホトダイオードの間の横方向の拡散を低減する横方向の障壁層を備えている。

## 【0027】

したがって、本発明の例示的な実施形態によれば、より厚いエピ層及びより深いホトダイオード接合とともに、イメージセンサのエピ層と基板の間の1つ又はそれ以上の水平方向の障壁層と、隣接するピクセル間の横方向の障壁層とを有するCMOSイメージセンサは、特に赤外線波長に対する遠赤外線の光に対して高い感度と少ないクロストークとを備えた

10

20

30

40

50

イメージセンサをもたらす。本発明は、780 nm又は840 nm用のAlGaAs/GaAsのような低価格の赤外線光源と関連してCMOSイメージセンサを使用する、コンピュータの光学式マウスのような動きを検出する用途及び、目の検出装置のような赤外線イメージング用途に対して特に適するが、本発明が、光の何らかの特定の波長、又は何らかの特定の用途で使用されることに限定されないことを理解されたい。赤外線光源は、網膜によるより高い反射率のため、及び被写体の注意をそらせることなく目の測定を行うことができるため、いずれにしても目の検出用途に対して特に望ましい。

【0028】

図5-12は、本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する。特に、図5-12は、図3に図解するイメージセンサに設けられるようなトレンチを含まない、ピクセル間の横方向の障壁層を有するCMOSイメージセンサを製造する方法の工程を図解する。

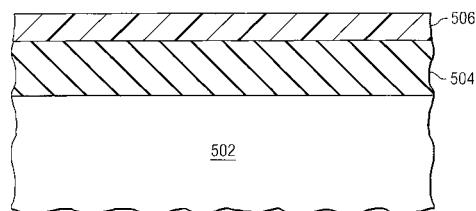

【0029】

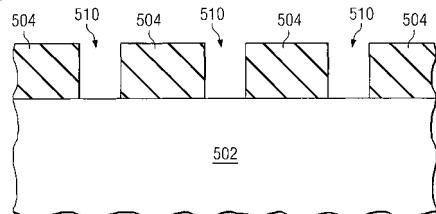

先ず図5を参照すると、約 $5 \times 10^{18}$ にまで高濃度にホウ素をドープしたシリコンの開始プロックが、502で示すように、最初に設けられる。本発明がP型ドーパントとしてホウ素に制限されないことを理解されたい。アルミニウム、ガリウム、インジウムを含む他のP型ドーパントを使用することができる。同様に、燐、砒素、アンチモンを含む他のN型ドーパントを使用することができる。さらに、シリコン上にLTO(低温熱酸化)の1000 nm(10000オングストローム)及び500 nm(5000オングストローム)厚の熱酸化層504が成長され、ホトレジスト層506がさらに酸化層上に適用される。

【0030】

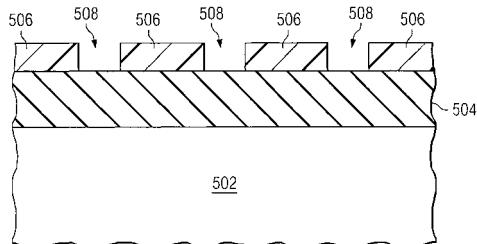

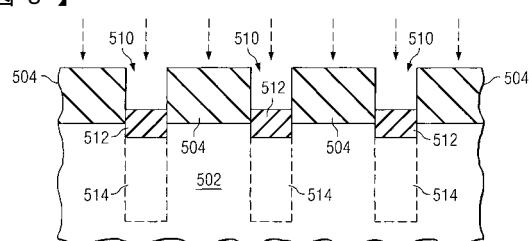

図6を参照すると、さらに、508で示すようにホトレジスト層506内にパターンが現像される。図7に示すように、さらに、510で示すように、酸化層がエッチングされ、さらにホトレジスト層が、図7に示すように、取り除かれる。

【0031】

さらに、図8の512で概略的に示すように、埋め込み酸化物が成長される。これは、シリコン内の工程で生じ、エピ層が適用された後、位置合わせされる。さらに高線量のホウ素が、複数のエネルギーにおいて注入される。514で概略的に示すように、これによりホウ素は異なる深さまで貫通し、したがって横方向の拡散障壁が形成される。本発明の例示的な実施形態による注入線量及びエネルギーは以下の通りである。

1. エネルギー 30keV 線量  $2.9 \times 10^{14}$

2. エネルギー 60keV 線量  $5.8 \times 10^{14}$

3. エネルギー 90keV 線量  $6.4 \times 10^{14}$

4. エネルギー 120keV 線量  $7.7 \times 10^{14}$

5. エネルギー 180keV 線量  $1.15 \times 10^{15}$

6. エネルギー 240keV 線量  $1.34 \times 10^{15}$

より高いエネルギーの注入は、エネルギー準位の半分で、二重イオン化ホウ素を注入することにより実施され得ることが認識されなければならない。

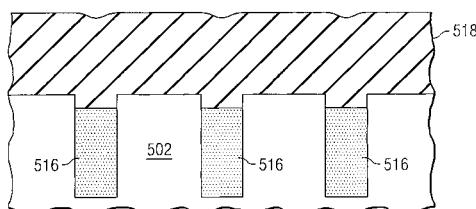

【0032】

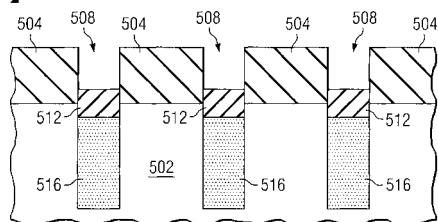

さらに、高温での焼鈍及び注入物の拡散が、図9の516で概略的に図解するように実施される。本発明の例示的な実施形態による障壁層の駆動手法は以下の通りである。

1. 850 でN<sub>2</sub>を供給する

2. N<sub>2</sub>内で1000 まで毎分5 の割合で昇温する

3. N<sub>2</sub>内において1000 、90分間焼鈍する

4. N<sub>2</sub>内で1125 まで毎分3 の割合で昇温する

5. 2.5%の酸素を含むN<sub>2</sub>内で、1125 、220分間保持する

6. N<sub>2</sub>内で1000 まで毎分3 の割合で降温する

7. N<sub>2</sub>内において1000 、240分間焼鈍する

8. N<sub>2</sub>内で850 まで毎分3 の割合で降温する

9. N<sub>2</sub>内にウエハを引き出す。

10

20

30

40

50

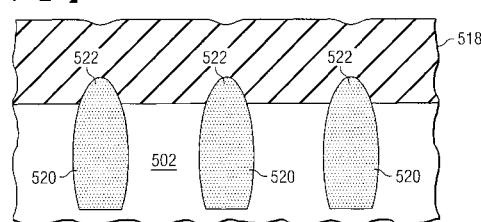

## 【0033】

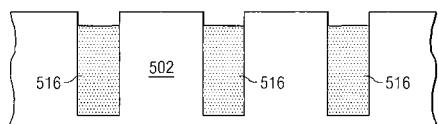

さらに、図10に示すように、酸化物が取り除かれ、p型エピ層518が、図11に示すように成長される。工程の後、横方向の障壁層（横方向のドープ障壁）520は、図12に示すように拡散される。上方に伸びる拡がり522は電子のより良好な閉じ込めを助ける。

## 【0034】

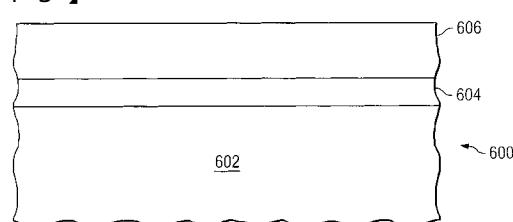

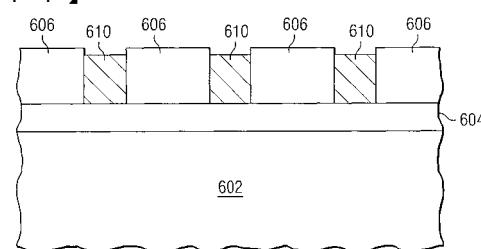

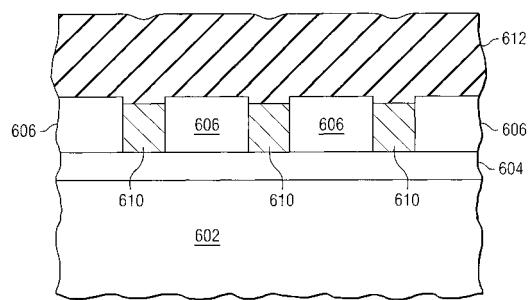

図13-15は、本発明のさらなる例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する。特に、図13-15は、本発明の例示的な実施形態によるイメージセンサにおいて、イメージセンサのエピ層と基板の間の水平方向の障壁と、隣接するピクセル間の横方向の障壁層のどちらも有するCMOSイメージセンサを製造する方法の工程を概略的に図解する。

10

## 【0035】

最初に、図13に示すように、非常に高濃度にドープされた水平方向の障壁層（ $> 1 \times 10^{19}$ のホウ素）614が、高濃度にドープされたシリコン基板（ $5 \times 10^{18}$ のホウ素）602の上部に形成される。さらに、固定された中程度の量ドープされた又は段階的にドープされたエピ層606が、水平方向の障壁層604の上に設けられる。段階的なドーピングプロファイルは、キャリアを上方に方向付け、収集効率を改善する電界をもたらす。

## 【0036】

さらに、図5-12を参照して上述した横方向の障壁層とともにCMOSイメージセンサを製造する工程が実施され、図14に示すように、エピ層606内に横方向の障壁層610がもたらされる。最後に、さらに、低濃度にドープされたホトダイオードエピが、図15の612で示すように成長され、イメージセンサが完成する。

20

## 【0037】

本発明の例示的な実施形態を開示してきたが、本発明の範囲から逸脱することなく、本発明を種々の仕方で改変できることが認識されなければならない。例えば、本発明の例示的な実施形態は、CMOSイメージセンサを製造する方法を開示するが、本発明のイメージセンサは、本発明の範囲から逸脱することなく、多くの異なる方法で製造することができる。加えて、本明細書で開示するCMOSイメージセンサの特定の特性は、本発明の範囲から逸脱することなく、様々に変化させることができる。例えば、本明細書で開示するイメージセンサは、反対のドープ型、すなわちn+基板、n-エピ、n-井戸分離体、p-井戸ピクセル、p+接触を利用して製造することもできる。そのようなイメージセンサでは、障壁層はn+となる。概して、本明細書で使用する「CMOSイメージセンサ」は、CMOS工程で製造し、CMOS電子技術と互換性があり、一体化することができる任意のイメージセンサを含むことを意図している。

30

## 【0038】

本発明の例示的な実施形態が多くの仕方で変更可能であるので、本発明は、添付の特許請求の範囲の記載によって要求される範囲でのみ制限されることに理解されたい。

## 【図面の簡単な説明】

## 【0039】

【図1】本発明の説明を補助するための、従来技術で公知のCMOSイメージセンサの部分を示す側面の概略的な断面図である。

40

【図2A】本発明の例示的な実施形態によるCMOSイメージセンサの部分を示す側面の概略的な断面図である。

【図2B】本発明の説明を補助するための、p型半導体における不純物添加障壁の機能を概略的に示す図である。

【図3】本発明のさらなる実施形態によるCMOSイメージセンサの部分を示す側面の概略的な断面図である。

【図4】図3に図解するCMOSイメージセンサの部分を示す概略的な平面図である。

【図5】本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図6】本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概

50

略的に図解する図である。

【図7】本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図8】本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図9】本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図10】本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図11】本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。 10

【図12】本発明の例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図13】本発明のさらなる例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図14】本発明のさらなる例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図15】本発明のさらなる例示的な実施形態によるCMOSイメージセンサを製造する方法の工程を概略的に図解する図である。

【図1】

【図2 B】

【図2 A】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(72)発明者 サンディープ・アール・バール

アメリカ合衆国カリフォルニア州94306, パロアルト, エドリー・アベニュー・297

(72)発明者 フレデリック・ピー・ラマスター

アメリカ合衆国コロラド州80525, フォートコリンズ, ノース, ヒルズボロ・コート・414

(72)発明者 デイビッド・ダブリュー・ビゲロー

アメリカ合衆国コロラド州80526, フォートコリンズ, クレイグ・ドライブ・4407

F ターム(参考) 4M118 AA05 AB01 BA14 CA03 CA18 FA25 FA26 FA27 FA28 FA33

5C024 AX01 CX03 CY47 GX01 GX03 GY31 HX01

5F049 MA04 MB03 NA01 NA20 NB03 PA01 PA09 PA10 PA11 QA03

QA14 RA03 SS03 WA01

【外國語明細書】

2007067393000001.pdf