(19) 日本国特許庁(JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-311785

(P2007-311785A)

(43) 公開日 平成19年11月29日(2007.11.29)

| (51) Int.Cl.             | F I          | テーマコード (参考)   |

|--------------------------|--------------|---------------|

| HO 1 L 21/822 (2006.01)  | HO 1 L 27/04 | C 5FO33       |

| HO 1 L 27/04 (2006.01)   | HO 1 L 21/88 | Z 5FO38       |

| HO 1 L 21/3205 (2006.01) | HO 1 L 27/06 | 1 O 2 A 5FO48 |

| HO 1 L 23/52 (2006.01)   |              |               |

| HO 1 L 21/8234 (2006.01) |              |               |

審査請求 未請求 請求項の数 41 O L (全 21 頁) 最終頁に続く

|              |                              |          |                                                                                  |

|--------------|------------------------------|----------|----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2007-121808 (P2007-121808) | (71) 出願人 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区梅灘洞416 |

| (22) 出願日     | 平成19年5月2日 (2007.5.2)         |          |                                                                                  |

| (31) 優先権主張番号 | 10-2006-0045712              |          |                                                                                  |

| (32) 優先日     | 平成18年5月22日 (2006.5.22)       |          |                                                                                  |

| (33) 優先権主張国  | 韓国 (KR)                      |          |                                                                                  |

| (31) 優先権主張番号 | 11/588575                    | (74) 代理人 | 100086368<br>弁理士 萩原 誠                                                            |

| (32) 優先日     | 平成18年10月27日 (2006.10.27)     | (72) 発明者 | 元 ▲セキ▼ 俊<br>大韓民国ソウル特別市冠岳区奉天7洞16<br>03-25番地                                       |

| (33) 優先権主張国  | 米国 (US)                      | (72) 発明者 | 朴 廷 ▲ミン▼<br>大韓民国京畿道安山市常緑区本五3洞87<br>2番地 ワールドアパート117棟304<br>号                      |

最終頁に続く

(54) 【発明の名称】 MIMキャパシタを含む半導体集積回路素子およびその製造方法

(57) 【要約】

【課題】キャパシタンス値が所定値以上に高く、VCCが所定値以下に維持されるMIMキャパシタを含む半導体集積回路装置を提供する。

【解決手段】活性領域を含む半導体基板、基板の上面の一部に形成され、絶縁領域を定義する絶縁物、共通のコンダクタ層からパターニングされ基板上に形成され、絶縁物上に形成された第1パターン部と、活性領域上に形成され活性領域内に形成されたトランジスタのゲートを含む第2パターン部を含むコンダクタ層パターン、前記第2パターン部は前記活性領域内に形成されたトランジスタのゲートを含み、コンダクタ層パターンの前記第1パターン部上に形成された下部電極、下部電極上に形成された誘電層パターン、および誘電層パターン上に形成された上部電極を含む絶縁領域内のキャパシタを含む半導体集積回路素子とその製造方法が提供される。

【選択図】 図 1 F

**【特許請求の範囲】****【請求項 1】**

活性領域を含む半導体基板と、

前記基板の上面の一部に形成され、絶縁領域を定義する絶縁物と、

共通コンダクタ層からパターニングされ、前記基板上に形成され、前記絶縁物上に形成

された第1パターン部と、

前記活性領域上に形成され、前記活性領域内に形成されたトランジスタのゲートを含む

第2パターン部を含むコンダクタ層パターン、および

前記コンダクタ層パターンの前記第1パターン部上に形成された下部電極、前記下部電

極上に形成された誘電層パターン、および前記誘電層パターン上に形成された上部電極を

含む絶縁領域内のキャパシタを含む半導体集積回路素子。

10

**【請求項 2】**

前記基板は、バルク半導体基板、SOI構造、またはエピタキシャルが成長した基板の

うち、いずれかの一つである請求項1に記載の半導体集積回路素子。

**【請求項 3】**

前記絶縁物は、STIまたはLOCOS構造である請求項1に記載の半導体集積回路素

子。

**【請求項 4】**

前記コンダクタ層は、ポリシリコンである請求項1に記載の半導体集積回路素子。

**【請求項 5】**

前記活性領域内の前記コンダクタ層パターンの第2パターン部下部の前記基板上に形成

されたゲート絶縁層パターンをさらに含む請求項1に記載の半導体集積回路素子。

20

**【請求項 6】**

前記ゲート絶縁層パターンは、前記絶縁領域内の前記コンダクタ層パターンの第1パタ

ーン部下部の前記絶縁物上に形成された請求項5に記載の半導体集積回路素子。

**【請求項 7】**

前記下部電極は、Ti、Ta、W、Hg、Zr、TiN、TaN、WN、HfN、Zr

Nまたはその合金のうち、いずれかの一つの金属である請求項1に記載の半導体集積回路

素子。

30

**【請求項 8】**

前記誘電層パターンは、高誘電率物質、酸化物、酸化物-窒化物-酸化物構造のうちか

ら選択された誘電物質のうちのいずれか一つである請求項1に記載の半導体集積回路素

子。

30

**【請求項 9】**

前記上部電極は、前記誘電層パターン上に形成された第1上部電極層パターンと前記第

1上部電極層パターン上に形成された第2上部電極層パターンとを含む請求項1に記載の

半導体集積回路素子。

**【請求項 10】**

前記第1上部電極層パターンはTiN、TaN、WN、HfN、ZrNまたは他の金属

窒化物のうちから選択されたいずれか一つである請求項9に記載の半導体集積回路素子。

40

**【請求項 11】**

前記第2上部電極層パターンは、CuまたはWのうちのいずれか一つである請求項10

に記載の半導体集積回路素子。

**【請求項 12】**

前記誘電層パターンは、前記上部電極の側壁に沿って形成される請求項1に記載の半導

体集積回路素子。

**【請求項 13】**

前記基板上に形成された層間絶縁膜をさらに含み、前記キャパシタは前記層間絶縁膜を

を通して(through)形成される請求項1に記載の半導体集積回路素子。

**【請求項 14】**

10

20

30

40

50

前記キャパシタは前記コンダクタパターンの第1パターン部上的一部分に形成され、前記下部電極コンタクトが前記層間絶縁膜を介して延長され前記コンダクタパターンの前記第1パターン部の他の部分の上部表面と電気的に連結される請求項13に記載の半導体集積回路素子。

【請求項15】

前記層間絶縁膜を介して延長され前記上部電極の上部表面と電気的に連結される上部電極コンタクトをさらに含む請求項13に記載の半導体集積回路素子。

【請求項16】

前記上部電極コンタクトは多数個で形成される請求項15に記載の半導体集積回路素子。

10

【請求項17】

前記層間絶縁膜は、第1層間絶縁膜と前記キャパシタおよび第1層間絶縁膜上に形成された第2層間絶縁膜とを含み、前記上部電極コンタクトは前記第2層間絶縁膜を介して延長され前記上部電極の上部表面と電気的に連結される請求項15に記載の半導体集積回路素子。

【請求項18】

前記第2層間絶縁膜上に形成され、前記上部電極と電気的に連結されるインターフェクションをさらに含む請求項17に記載の半導体集積回路素子。

【請求項19】

前記第2層間絶縁膜および前記キャパシタ上に形成され、少なくとも一つ以上が前記上部電極と直接電気的に連結されたインターフェクションを含む請求項13に記載の半導体集積回路素子。

20

【請求項20】

半導体基板の上部に絶縁領域を定義する絶縁物を形成し、

基板上にコンダクタ層を形成しパターンングして、前記絶縁領域の絶縁物上の第1パターン部と前記活性領域上の第2パターン部とを含む伝導性パターンを形成し、

前記伝導性パターンの前記第1パターン部上に下部電極を形成し前記下部電極上に誘電層パターンを形成して、および前記誘電層パターン上に上部電極を形成して、前記絶縁領域の絶縁物上にキャパシタを形成することを含む半導体集積回路素子の製造方法。

30

【請求項21】

前記第2パターン部は、前記活性領域に形成されたトランジスタのゲートを含む請求項20に記載の半導体集積回路素子の製造方法。

【請求項22】

前記絶縁物を形成するのは、STIまたはLOCOSを形成する工程のうち一つを選択して前記絶縁物を形成する請求項20に記載の半導体集積回路素子の製造方法。

【請求項23】

前記伝導性パターンは、ポリシリコンを含む請求項20に記載の半導体集積回路素子の製造方法。

【請求項24】

前記コンダクタ層を形成する前に前記活性領域の基板上にゲート絶縁層パターンを形成することをさらに含む請求項20に記載の半導体集積回路素子の製造方法。

40

【請求項25】

前記コンダクタ層を形成する前に前記絶縁領域の基板上にゲート絶縁層パターンを形成することをさらに含む請求項24に記載の半導体集積回路素子の製造方法。

【請求項26】

前記下部電極は、Ti、Ta、W、Hf、Zr、TiN、TaN、WN、HfN、ZrNまたはその合金のうちから選択されたいずれか一つで形成される請求項20に記載の半導体集積回路素子の製造方法。

【請求項27】

前記誘電層パターンは、高誘電物質、酸化物、酸化物-窒化物-酸化物構造のうちから

50

選択されたいずれか一つの誘電物質を含む請求項 20 に記載の半導体集積回路素子の製造方法。

**【請求項 28】**

前記上部電極は、前記誘電層パターン上に形成された第1上部電極層パターンと前記第1上部電極層パターン上に形成された第2電極層パターンとを含む請求項 20 に記載の半導体集積回路素子の製造方法。

**【請求項 29】**

前記第1上部電極層パターンは、TiN、TaN、WN、HfN、ZrNまたは他の金属窒化物のうちから選択されたいずれかの一つを含む請求項 20 に記載の半導体集積回路素子の製造方法。

**【請求項 30】**

前記第2上部電極層パターンは、CuまたはWのうちから選択されたいずれかの一つを含む請求項 29 に記載の半導体集積回路素子の製造方法。

**【請求項 31】**

前記キャパシタは、

前記伝導性層パターン上の基板上に層間絶縁膜を形成し、

前記層間絶縁膜をパターニングして前記伝導性層パターン上の第1パターン部の一部を露出させるオープニングを形成し、

前記オープニングの底面および内壁に下部電極層を形成し、

前記オープニングの底面上の下部電極層パターンを形成するために前記下部電極層をエッティングし、

前記下部電極上に誘電層を形成し、

前記誘電層上に上部電極層を形成して、

前記上部電極層と前記誘電層下部の前記層間絶縁膜を露出させるために前記層間絶縁膜を平坦化する工程を行うことを含む請求項 20 に記載の半導体集積回路素子の製造方法。

**【請求項 32】**

前記上部電極層のエッティングは、前記オープニングの内壁から電極層を除去する請求項 31 に記載の半導体集積回路素子の製造方法。

**【請求項 33】**

前記層間絶縁膜を平坦化する前に前記層間絶縁膜上に犠牲層をさらに形成してパターニングすることを含み、

前記パターニング工程は前記犠牲層と層間絶縁膜とをパターニングして、第1オープニングを形成することである請求項 31 に記載の半導体集積回路素子の製造方法。

**【請求項 34】**

エッティング方法で第2オープニングを形成するために前記第1オープニングを拡張させることをさらに含む請求項 33 に記載の半導体集積回路素子の製造方法。

**【請求項 35】**

前記拡張の後に、前記犠牲層の下が除去された部分が前記第2オープニング上に形成される請求項 34 に記載の半導体集積回路素子の製造方法。

**【請求項 36】**

前記キャパシタは、前記伝導性パターンの前記第1パターン部上の一部に形成され、前記層間絶縁膜を通して延長され前記伝導性パターンの前記第1パターン部の他の部分の上部表面と電気的に連結される下部電極コンタクトを形成することをさらに含む請求項 31 に記載の半導体集積回路素子の製造方法。

**【請求項 37】**

前記層間絶縁膜を介して延長され前記上部電極の上部表面と電気的に連結される上部電極コンタクトを形成することをさらに含む請求項 31 に記載の半導体集積回路素子の製造方法。

**【請求項 38】**

前記上部電極コンタクトを多数個で形成することをさらに含む請求項 37 に記載の半導

10

20

30

40

50

体集積回路素子の製造方法。

【請求項 39】

前記層間絶縁膜は、第1層間絶縁膜を含み、前記平坦化工程を行った後、前記キャパシタ上に第2層間絶縁膜を形成し、前記上部電極コンタクトは前記第2層間絶縁膜を介して延長され前記上部電極の上部表面と電気的に連結される請求項37に記載の半導体集積回路素子の製造方法。

【請求項 40】

前記第2層間絶縁膜上に前記上部電極と電気的に連結されるインターフェクションを形成することをさらに含む請求項39に記載の半導体集積回路素子の製造方法。

【請求項 41】

前記平坦化工程を行った後、前記キャパシタ上に、少なくとも一つが前記上部電極と電気的に連結されるインターフェクションを形成することをさらに含む請求項31に記載の半導体集積回路素子の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はMIMキャパシタを備える半導体集積回路装置およびその製造方法に関する。

【背景技術】

【0002】

最近になって半導体素子の高集積化(high integration degree)および高性能化(high performance)にともない一つの完全な機能を遂行するためにデジタル回路とアナログ回路とを共に備えるシステムLSI(Large Scale Integrated circuit)に対する必要性が増大している。すなわち、マルチメディア、通信、およびグラフィックプロセッシング用IC、イメージセンサ、LDIなどのような多様なシステムLSI製品ではデジタル回路に付加してアナログ回路が要求される。

【0003】

半導体集積回路素子は共通的に素子内に集積されたキャパシタを含む。このような集積されたキャパシタは互いに離隔された第1電極と第2電極とを含む。集積回路素子内で、キャパシタは多様で多数の形態で存在する。例えば、MOS(Metal-Oxide-Semiconductor)キャパシタ、PN接合キャパシタ、PIP(poly silicon-insulator-poly silicon)キャパシタ、およびMIM(Metal-Insulator-Metal)などである。このような名称は電極または誘電膜を形成する物質の種類によって付けられる。

【0004】

MOSとPIPキャパシタ類は多結晶半導体層または単結晶半導体層を電極とするキャパシタで、PN接合キャパシタ類は下部電極にドーピングされた単結晶シリコンを使用するキャパシタである。このような多結晶半導体または単結晶半導体は金属より抵抗が高い。そのため、キャパシタの多結晶半導体または単結晶半導体で形成された電極にバイアス電圧が印加されるとき、空乏領域が生じてバイアス電圧が不安定となり望まないキャパシタンスの変動を起こす。キャパシタンスの変動はキャパシタに印加される信号(signaling)の周波数に大きく依存する。

【0005】

アナログ回路の主要構成要素はキャパシタと抵抗である。アナログ回路キャパシタの性能を向上させるために、アナログキャパシタでは $3\text{ fF}/\mu\text{m}^2$ 以上の高いキャパシタンスが要求されるだけでなく、抵抗では数百 $/\text{mm}^2$ から数K $/\text{mm}^2$ 程度の高い抵抗が要求される。また、アナログキャパシタが予測可能な範囲内でエラーなく動作するためにはアナログキャパシタのキャパシタンス電圧係数(Voltage Coefficients of Capacitance、以下VCC)が所定値以下で一定に維持されなければならず、ウェハ上の位置によるVCCの分布が可能な限り小さくなければならない

10

20

30

40

50

。この時、VCCは、

【0006】

【数1】

$$VCC = \frac{1}{C_0} \left( \frac{dC}{dV} \right)$$

のように定義される。

10

【0007】

ここで、 $C_0$ は素子内での一般的なキャパシタンスであり、( $dC/dV$ )は印加された電圧に応答するキャパシタンスの変動である。

VCCはアナログキャパシタのキャパシタンスと電圧との間の関係を表す2次方程式の各項の係数を指称する。

【0008】

キャパシタ電極が金属で形成されたMIMキャパシタは電極の抵抗が低く、より安定したキャパシタンスを維持することができる。この場合、周波数依存度が低くなる。金属電極のキャパシタにバイアス電圧が印加される場合、空乏領域が生じなかつたり、とても小さくなる。

20

【0009】

こういう安定したキャパシタンス特性のため、MIMキャパシタはアナログ素子、SOC (System On a Chip) 素子、およびすべての混合信号応用分野などに使用される半導体集積回路素子に広く重要な使用される。例えば、MIMキャパシタは CIS (CMOS Image Sensor)、LDI (LCD Driver ICs)、RF フィルタ素子およびその他多様に使用される。

【0010】

一般的なPIPキャパシタは多結晶シリコンで形成された二つの電極を含む。PIPキャパシタは一枚のフォトマスクだけを使用して製造されるため相対的に簡単である。そのため、PIPキャパシタは普通低い等級の素子に使用され、PIPキャパシタの上に金属インターロケクション層が形成されるためルーティング (routing) 領域が広いのでワイヤリング特性が良い。

30

【0011】

しかし、PIPキャパシタは多結晶シリコン電極が含む空乏領域のためにキャパシタンスの変動が激しい。このような空乏領域は高いキャパシタンスと低いVCC値とを確保するのに障害となるため、PIPキャパシタは高い等級の素子に使用しづらい。相対的に、MIMキャパシタは性能が優れているが金属インターロケクション層と同じ高さに作られるものの、上、下部電極が大きく配線に必要なルーティング面積が狭くてワイヤリング特性が悪い。

【0012】

一方、ますます複雑化する配線に必要なルーティング面積を最大化することができ、さらに単純化された工程で最小限のマスクを使用し、形成することができる金属アナログキャパシタに対する必要性が増大している。金属アナログキャパシタンスを含む半導体集積回路素子に関しては、特許文献1に記載されたものが知られている。

40

【特許文献1】特開2005-268551号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

本発明が解決しようとする課題は、キャパシタンス値が所定値以上に高く、VCCが所定値以下に維持されるMIMキャパシタを含む半導体集積回路装置を提供することにある

50

。

#### 【0014】

本発明が解決しようとする他の課題は、配線ルーティングに有利でありつつも、最小限のマスクを使用するMIMキャパシタの製造方法を提供することにある。

#### 【0015】

本発明が解決しようとする課題は、以上で言及した技術的課題に制限されず、言及されていないまた他の課題は次の記載から当業者に明確に理解できるであろう。

#### 【課題を解決するための手段】

#### 【0016】

前記課題を達成するための本発明の一実施形態による半導体集積回路素子は、活性領域を含む半導体基板、基板の上面の一部に形成され絶縁領域を定義する絶縁物、共通コンダクタ層からパターニングされ基板上に形成されて絶縁物上に形成された第1パターン部と、活性領域上に形成され活性領域内に形成されたトランジスタのゲートを含む第2パターン部を含むコンダクタ層パターン、およびコンダクタ層パターンの第1パターン部上に形成された下部電極、下部電極上に形成された誘電層パターン、および誘電層パターン上に形成された上部電極を含む絶縁領域内のキャパシタを含む。

#### 【0017】

また、前記他の課題を達成するための本発明の一実施形態による半導体集積回路素子の製造方法は、半導体基板の上部に絶縁領域を定義する絶縁物を形成し、基板上にコンダクタ層を形成してパターニングして、絶縁領域の絶縁物上の第1パターン部と活性領域上の第2パターン部とを含む伝導性パターンを形成し、および伝導性パターンの第1パターン部上に下部電極を形成して、下部電極上に誘電層パターンを形成し、および誘電層パターン上に上部電極を形成して、絶縁領域の絶縁物上にキャパシタを形成することを含む。

その他実施形態の具体的な事項は詳細な説明および図に含まれている。

#### 【発明の効果】

#### 【0018】

本発明の実施形態によるMIMキャパシタは、素子の低い位置のルーティング層より下に形成されるため広いルーティング領域と金属配線領域とを確保することができ、空乏領域が殆どなくてキャパシタンスが良く、金属電極を有することにより高性能動作をすることができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

本発明の利点および特徴、そしてそれらを達成する方法は添付される図面と共に詳細に後述されている実施形態を参照すれば明確になるであろう。しかし本発明は以下で開示される実施形態に限定されるものではなく互いに異なる多様な形態で実現され得るものであり、単に本実施形態は本発明の開示が完全なようにし、本発明が属する技術分野で通常の知識を有する者に発明の範疇を完全に知らせるために提供されているもので、本発明は請求項の範囲によってのみ定義される。図面において層および領域の大きさおよび相対的な大きさは説明の明瞭性のために誇張されたものあり得る。明細書全体にかけて、同一参考符号は同一構成要素を指称する。

#### 【0020】

本明細書で記述する実施形態は本発明の理想的な概略図である平面図および断面図を参考にして説明されるであろう。したがって、製造技術および/または許容誤差などによって例示図の形態が変形され得る。したがって、本発明の実施形態は図示された特定形態に制限されるものではなく、製造工程に伴い生成される形態の変化も含むものである。したがって、図に例示された領域は概略的な属性を有し、図に例示された領域の形は素子の領域の特定形態を例示するためのものであり、発明の範疇を制限するものではない。

#### 【0021】

本明細書で、「基板」はシリコンバルク基板、SOI(silicon on insulator)、または単結晶層から成長したエピタキシャルを含む基板のうち、いずれ

10

20

30

40

50

かの一つを意味し得るが、これに限定さるものではない。

【0022】

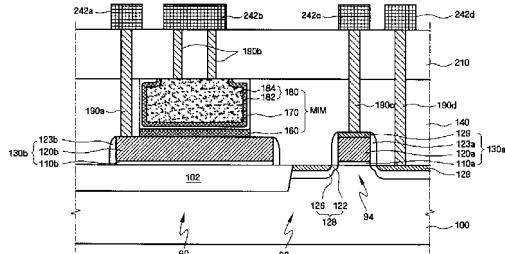

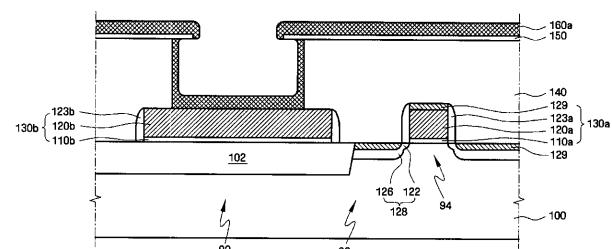

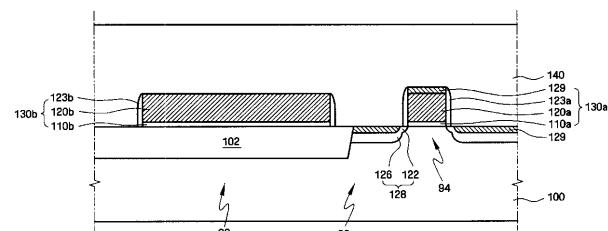

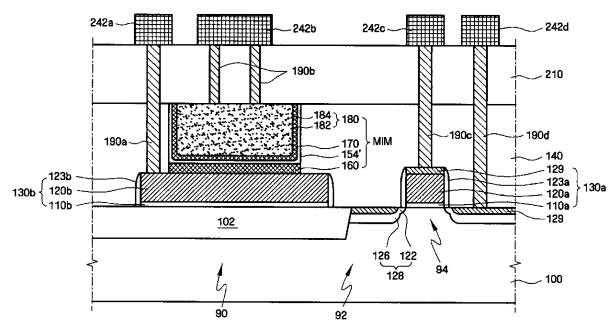

図1Aないし1Fは、本発明の第1実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図であり、図2は本発明の実施形態による半導体集積回路装置のMIMキャパシタを表す断面図である。

【0023】

図1Fは本発明の第1実施形態によるMIMキャパシタである。

【0024】

フィールド酸化膜102が基板100の絶縁領域90と活性領域92とを定義し、基板100内に形成される。活性領域92にはトランジスタ94のような活性素子が形成される。本実施形態で、トランジスタ94は基板100の活性領域92上に形成された第1ゲートスタック(stack、130a)を含む。第1ゲートスタック130aの左右側の基板100内にはソース／ドレイン領域(source/drain region、128)が形成される。

10

【0025】

MIMキャパシタはフィールド酸化膜102上に形成される。フィールド酸化膜102はMIMキャパシタを基板100の活性領域92と隔離させる。MIMキャパシタの構成要素は第2ゲートスタック130b上に形成される。第2ゲートスタック130bは第1ゲートスタック130aと同一の物質で同時に形成することが出来る。第2ゲートスタック130bはトランジスタのゲートとしては動作することはないが、MIMキャパシタの下部電極160と上層インターフェクション(intercconnection、242a)と連結された垂直コンタクト190aとの間で電流経路として動作する。

20

【0026】

MIMキャパシタは、第2ゲートスタック130bの多結晶シリコンパターン120bと連結された下部電極160、下部電極160上のキャパシタ誘電膜170、キャパシタ誘電膜170上の上部電極180を含む。上部電極180は金属充填層である第2上部電極層184と接着層である第1上部電極層182とを含み得る。

30

【0027】

第1層間絶縁膜140および第2層間絶縁膜210がMIMキャパシタとトランジスタの結果物上に形成される。

【0028】

垂直コンタクト190a、190b、190c、190dがMIMキャパシタの第1および第2電極160、180と上層配線242a、242bとの間、および活性領域92のトランジスタのゲート、ソース／ドレイン128と上層配線242c、242dとの間に第1および第2層間絶縁膜140、210を貫通して形成される。

40

【0029】

次に、図1Aないし1Fを参照して、本発明のMIMキャパシタを含む半導体集積回路素子を製造する方法を説明する。

【0030】

図1Aを参照すれば、フィールド酸化膜102が基板100の絶縁領域90と活性領域92とを定義し、基板100内に形成される。本実施形態で、フィールド酸化膜102はよく知られた絶縁技術であるSTI(Shallow Trench Isolation)またはLOCOS(Local Oxidation of Silicon)方法を利用して形成することが出来る。フィールド酸化膜102は基板100の内部と上部にも形成することが出来る。

【0031】

活性領域92には、トランジスタ94のような活性素子が形成される。本実施形態で、第1ゲートスタック130aが基板100の活性領域92上に積層およびパターニングされ、第1ゲートスタック130aと同一の物質で第2ゲートスタック130bがフィールド酸化膜102上に積層およびパターニングされる。また、例示的に、第1および第2ゲ

50

ートスタック 130a、130b は第 1 および第 2 ゲート酸化膜パターン 110a、110b、および第 1 および第 2 ゲートポリシリコン膜パターン 120a、120b を形成するためにはパターニングされるゲート酸化膜 110 とゲートポリシリコン膜 120 とを含む。

#### 【0032】

活性領域 92 で、シリサイド層 129 がゲート抵抗を減らすため第 2 ポリシリコンパターン 120a の上部に形成することが出来、コンタクト抵抗を減らすためソース / ドレイン領域 128 の上部にも形成することが出来る。図 1A に図示された実施形態で、第 2 ゲートポリシリコンパターン 120b 上にシリサイドが形成されるのを防止するために選択的にシリサイドプロッキング層を第 2 ゲートポリシリコンパターン 120b 上に形成することが出来る。しかし他の実施形態でシリサイド層を第 2 ゲートポリシリコンパターン 120b 上に形成してもよい。

#### 【0033】

第 1 および第 2 側壁スペーサ 123a、123b を第 1 および第 2 ゲートスタック 130a、130b の側面に形成してもよい。第 1 および第 2 側壁スペーサ 123a、123b を、よく知られた側壁スペーサ形成技術によって第 1 および第 2 ゲートスタック 130、130b 上に絶縁層を形成して、異方性でエッチングして形成することが出来る。

#### 【0034】

本実施形態で、第 1 ゲートスタック 130a の左右側の基板 100 内にはイオン注入方法を利用してソース / ドレイン領域 128 が形成される。各ソース / ドレイン領域 128 は高濃度ドーピング領域 126 と低濃度ドーピング領域 122 とを含み、このような方法はトランジスタ形成技術分野でよく知られている。

#### 【0035】

その後、第 1 層間絶縁膜 140 が結果物上に形成される。ある実施形態で、第 1 層間絶縁膜 140 はシリコン酸化物で形成される。次に第 1 層間絶縁膜 140 は CMP (Chemical Mechanical Polishing) 技術などを利用して平坦化される。

次に、犠牲層 150 を平坦化された第 1 層間絶縁膜 140 上に形成する。犠牲層 150 は TiN、TaN、SiN、金属窒化物など、第 1 層間絶縁膜 140 がシリコン酸化物である場合に湿式エッチング選択比を有し得る多様な物質で形成される。

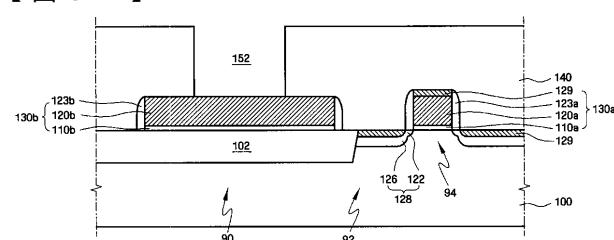

#### 【0036】

図 1B を参照すれば、犠牲層 150 と第 1 層間絶縁膜 140 を、写真エッチング工程でパターニングし、第 1 層間絶縁膜 140 内にキャパシタオープニング 152 を形成する。

#### 【0037】

本実施形態で、キャパシタオープニング 152 を形成するためのフォトリソグラフィ工程が一度だけ必要である。キャパシタオープニング 152 はキャパシタを形成するための究極的な位置であり、これはより効果的な集積化された MIM キャパシタ製造工程である。

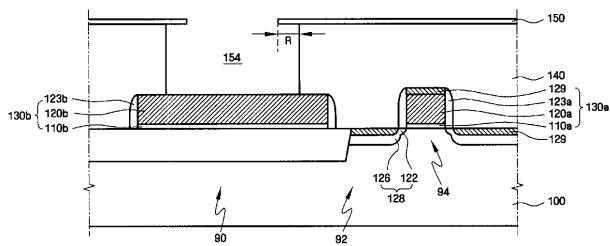

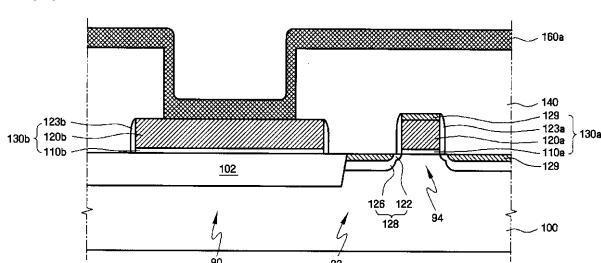

#### 【0038】

図 1C を参照すれば、キャパシタオープニング 152 が拡張されたキャパシタオープニング 154 を形成するために広げられる。この工程で、第 1 層間絶縁膜 140 が選択的にエッチングされ犠牲層 150 はエッチングされず、そのまま残る。この方法で、犠牲層 150 はエッチング工程の間、R 分だけ拡張されたキャパシタオープニング 154 の内部側壁で下が空いた形 (undermined feature) で残る。拡張されたキャパシタオープニング 154 を形成する工程は犠牲層 150 を最小限、またはエッチングされないようにする LAL (Limus Amebocyte Lyse)、または HF を利用して、キャパシタオープニング 152 の内壁をエッチングすることによって行われる。

#### 【0039】

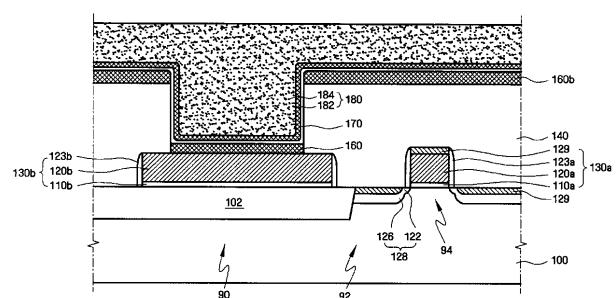

図 1D を参照すれば、犠牲層 150 の表面と拡張されたキャパシタオープニング 154

10

20

30

40

50

の内部側壁と底表面上に金属層 160 a を形成する。金属層 160 a はスパッタリング方法を利用して形成することが出来る。金属層 160 a は Ti、Ta、W、Hf、Zr、TiN、TaN、WN、HfN、ZrN およびその組合せのうちから選択されたいずれか一つ以上で形成することが出来る。拡張されたキャパシタオーブニング 154 の底面上に形成された金属層 160 a の一部は後続工程でキャパシタの下部電極として変化する。金属層 160 a を形成するとき、拡張されたキャパシタオーブニング 154 の底面上に形成される金属層 160 a は内部側壁に形成された金属層 160 a より十分に厚く形成することが要求される。

#### 【0040】

図 1 E を参照すれば、金属層 160 a が湿式エッチング方法などを利用して分離される。湿式エッチング後に、拡張されたキャパシタオーブニング 154 の内部側壁に形成されていた金属層 160 a が除去される。MIM キャパシタの下部電極 160 を形成するために、拡張されたキャパシタオーブニング 154 の底面上に形成された金属層 160 の一部が残る。犠牲層 150 上に形成された金属層 160 b の一部も残る。

#### 【0041】

次に、キャパシタ誘電層 170 が犠牲層 150 上に形成された金属層 160 b、拡張されたキャパシタオーブニング 154 の内部側壁、下が除去された形の犠牲層 150 下部、および下部電極 160 上に形成される。

#### 【0042】

キャパシタ誘電層 170 は例えば、高誘電率の誘電膜、酸化物、酸化物 - 窒化物 - 酸化物構造またはその組合せの物質のうち、いずれかの一つで形成される。

#### 【0043】

キャパシタ上部電極層 180 がキャパシタ誘電層 170 の上面と側面を覆い、拡張されたキャパシタオーブニング 154 を充填し形成される。上部電極層 180 は第 1 上部電極層 182 と第 2 上部電極層 184 とで形成することが出来る。第 1 上部電極層 182 は第 2 上部電極層 184 とキャパシタ誘電層 170 との接着力を向上させ、拡散障壁の特性を有し、相対的に薄く形成される。第 1 上部電極は例えば、TiN、TaN、WN、HfN、ZrN、他の金属窒化物またはその組合せで形成することが出来る。第 2 上部電極層 184 は例えば Cu または W のように優秀な充填特性を有し、抵抗が低い金属で形成することが出来る。

#### 【0044】

図 1 F を参照すれば、CMP 工程等を行い、第 1 層間絶縁膜 140 を露出させる。具体的に、第 1 層間絶縁膜 140 上に形成された第 2 上部電極層 184、第 1 上部電極層 182、キャパシタ誘電層 170、金属層 160 b、および犠牲層 150 が除去される。

#### 【0045】

MIM キャパシタは第 2 ゲートスタック 130 b 上に形成された下部電極 160、キャパシタ誘電層 170、および第 1 および第 2 上部電極層 182、184 を含む上部電極 180 を含む構造で形成される。

#### 【0046】

次に、第 2 層間絶縁膜 210 を形成して平坦化する。第 2 層間絶縁膜 210 の厚さはその上に形成される上層のインターフェクション 242 a、242 b、242 c、242 d が位置しなければならない高さを考慮した厚さで形成することが出来る。

#### 【0047】

インターフェクション 242 a、242 b、242 c、242 d を形成する前に、第 2 および第 1 層間絶縁膜 210、140 を垂直に貫通し、第 2 ゲートポリシリコンパターン 120 b、上部キャパシタ電極層 184、第 1 ゲートスタック 130 a 上のシリサイド層 129 およびソース / ドレイン領域 128 上のシリサイド領域 129 の上部領域を露出するコンタクトホールが形成される。

#### 【0048】

次に、第 1 ないし第 4 垂直コンタクト 190 a、190 b、190 c、190 d を形成

10

20

30

40

50

するためにコンタクトホール内に金属が充填される。この時、上部電極層 184 と電気的に連結される第2垂直コンタクト 190b は抵抗を低くし、電流を増加させるために複数個で形成することが出来る。図示されていないが、第2ゲートポリシリコンパターン 120 および下部電極 160 と電気的に連結された第1垂直コンタクト 190a も同じ理由で複数個で形成することが出来る。一般的なPIP と MIM キャパシタの電極と比較すれば、図示された MIM キャパシタの上部および下部電極 180、160 が低い抵抗を有するため、垂直コンタクトは PIP キャパシタに比べ、相対的に少ない数で形成することが出来る。したがって上層金属高さ (metal level) でワイヤリングのための有効面積が増加する。

## 【0049】

10

第2層間絶縁膜 210 上に第1ないし第4垂直コンタクト 190a、190b、190c、190d と電気的に連結される上位インターフェクション 242a、242b、242c、242d が素子の他の位置に信号を伝達するために形成される。

## 【0050】

本実施形態で、MIM キャパシタの要素を定義するために一枚だけの追加的なフォトマスクが要求されるため工程効率が高くなる。本実施形態で、キャパシタは MIM 構造であるため優秀な VCC 特性を有し、基板 100 上に近づくほど低い高さに MIM 構造でキャパシタが形成されるため上層金属高さ (metal level) によって広いルーティング面積を確保することができる。

## 【0051】

20

キャパシタ下部電極 160 は側壁がないように形成することが出来る。言い換えると、拡張されたキャパシタオープニング 154 の内部側壁に形成されないところがあり得る。側壁が形成される場合、後続 CMP 工程で下部電極 160 の側壁と上部電極 180 の側壁とが短絡 (short) することがある。

## 【0052】

キャパシタオープニング 152 は犠牲層 150 の下が除去された部分を形成するために拡張され、犠牲層 150 の下が除去された領域と隣接する内部側壁とで下部電極 160 を隠すことによってキャパシタオープニング 152 内で相対的に薄い下部電極 160 の側面と相対的に厚い下部電極 160 の底部とを形成する。

## 【0053】

30

この結果物に、後続される湿式エッティング工程を行うと下部電極 160 の側壁は除去され、拡張されたキャパシタオープニング 154 の底の部分に残った金属の相対的に厚い部分は残留する。これは、キャパシタ構造の上部を除去するための後続 CMP 工程が行われる時、下部電極 160 の側壁が存在しないので、短絡問題を避けることができる。

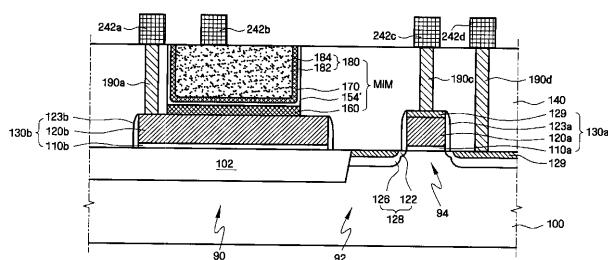

## 【0054】

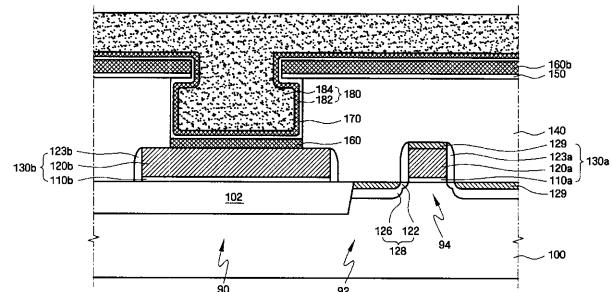

図 2 は本発明の第2実施形態による MIM キャパシタを含む半導体集積回路素子の断面図である。

## 【0055】

40

図 2 の第2実施形態は第1実施形態と比較して、実質的に同じ方法を使用して、製造することが出来、実質的に類似した構造である。第1実施形態とは異なり、第2層間絶縁膜 210 が形成されず、第1層間絶縁膜 140 上に形成された犠牲層 150、金属層 160b、キャパシタ誘電層 170、第1上部電極層 182 および第2上部電極層 184 が CMP 工程で除去される。

## 【0056】

本発明の第2実施形態では、第2ゲートポリシリコンパターン 120b の上部領域、第1ゲートスタック 130a 上のシリサイド層 129、および活性領域 92 に形成されたトランジスタ 94 のソース / ドレイン領域 128 上のシリサイド層 129 を露出するように第1層間絶縁膜 140 内にコンタクトホールが形成される。その後、垂直コンタクト 190a、190c、190d の内部が金属で充填される。

## 【0057】

50

次に、素子の他の領域に信号を伝達するための上層のインターフェクション 242a、242c、242d が垂直コンタクト 190a、190c、190d と電気的に連結され第 1 層間絶縁膜 140 上に形成される。また、上層のインターフェクションのうちの一つ 242b は直接 MIM キャパシタの上部電極 180 と電気的に連結される。この場合、工程が単純になる。

#### 【0058】

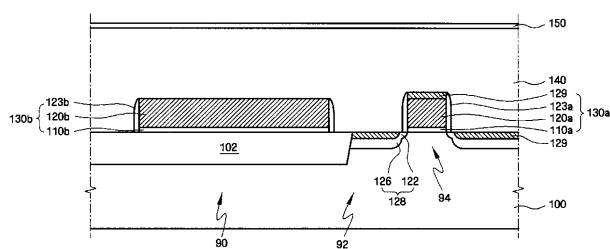

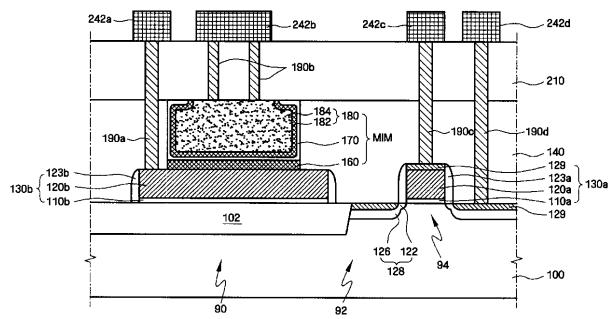

図 3A ないし 3E は本発明の第 3 実施形態による MIM キャパシタを製造する方法を説明するための断面図である。第 3 実施形態は第 1 実施形態の製造方法と比較して、類似した構造と製造方法である。第 3 実施形態ではキャパシタオーブニング 152 を拡張する工程が行われず、犠牲層が形成されない。この結果として、犠牲層によるシャード効果によってキャパシタオーブニング 152 の内部側壁に金属層 160 が形成されない部分がなくなる。

#### 【0059】

次に、金属層 160 が、第 1 実施形態と比較して、キャパシタオーブニングの側壁に相対的に厚く形成される。

#### 【0060】

図 3A を参照すれば、第 1 実施形態でも説明されたように、フィールド酸化膜 102 が基板 100 の絶縁領域 90 と活性領域 92 とを定義する。本実施形態で、フィールド酸化膜 102 はよく知られた STI または LOCOS 工程を使用して形成することが出来る。

#### 【0061】

第 1 実施形態で説明したように、活性領域 92 内で、トランジスタ 94 のような活性素子を形成することが出来る。

#### 【0062】

本実施形態において、第 1 ゲートスタック 130a は基板 100 の活性領域 92 上に積層およびパターニングされて形成され、第 2 ゲートスタック 130b はフィールド酸化膜 102 領域上に積層およびパターニングされて形成することが出来る。

#### 【0063】

本実施形態において、第 1 および第 2 ゲートスタック 130a、130b は、ゲート酸化物層 110 とゲートポリシリコン層 120 を含む。ゲート酸化物層 110 は第 1 および第 2 ゲート酸化膜パターン 110a、110b を形成するためにパターニングされ、ゲートポリシリコン層 120 は第 1 および第 2 ゲートポリシリコン層パターン 120a、120b を形成するためにパターニングされる。

#### 【0064】

活性領域 92 で、ゲートの抵抗を低くするためのシリサイド層 129 が第 1 ゲートポリシリコンパターン 120a の上部に形成され、コンタクト抵抗を低くするためにソース / ドレイン領域 128 の上部に形成される。

#### 【0065】

図 3A に図示された実施形態において、第 2 ゲートポリシリコンパターン 120b 上にシリサイドが形成されることを防止するために選択的にシリサイドブロッキング層が第 2 ゲートポリシリコンパターン 120b 上に形成することが出来る。

#### 【0066】

他の実施形態として、シリサイド層を第 2 ゲートポリシリコンパターン 120b 上に形成することが出来る。

#### 【0067】

第 1 および第 2 側壁スペーサ 123a、123b はよく知られた側壁スペーサ形成技術によって第 1 および第 2 ゲートスタック 130、130b 上に絶縁層を形成し、異方性エッチングにより形成することができる。

#### 【0068】

図 3A に図示された実施形態において、第 1 ゲートスタック 130a の左右側の基板 100 内にはイオン注入方法を利用してソース / ドレイン領域 128 が形成される。各ソ

10

20

30

40

50

スノドレイン領域128は高濃度ドーピング領域126と低濃度ドーピング領域122とを含み、このような方法はトランジスタ形成技術分野でよく知られている。

#### 【0069】

その後、第1層間絶縁膜140が結果物上に形成される。ある実施形態として、第1層間絶縁膜140はシリコン酸化物で形成することが出来る。その後に第1層間絶縁膜140はCMP等を利用して平坦化される。

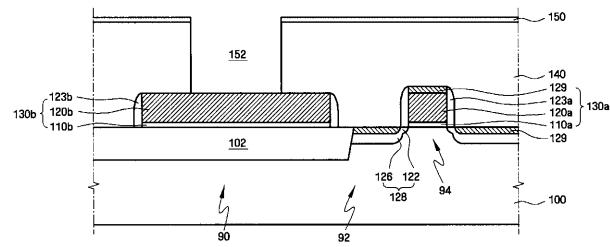

#### 【0070】

図3Bを参照すれば、写真エッチング工程を遂行して、第1層間絶縁膜140内部にキャパシタオープニング152を形成する。

#### 【0071】

本実施形態で、キャパシタオープニング152を形成するために一度のフォトリソグラフィ工程だけが必要である。

#### 【0072】

キャパシタオープニング152はキャパシタを形成するための究極的な位置であり、これはより効果的な集積化されたMIMキャパシタ製造工程である。

#### 【0073】

図3Cを参照すれば、キャパシタオープニング152を拡張する工程を行わず、第1層間絶縁膜140とキャパシタオープニング152の底および内部側壁上に金属層160aが形成される。本実施形態で、金属層160aはスパッタリング方法を行い形成され得る。金属層160aはTi、Ta、W、Hf、Zr、TiN、TaN、WN、HfN、ZrNおよびその組合せのうちから選択されたいずれか一つ以上で形成することが出来る。

#### 【0074】

キャパシタオープニング152の底面上に形成された金属層160aは後続工程でキャパシタの下部電極に変化する。

#### 【0075】

金属層160aを蒸着する間、第3実施形態のようにキャパシタオープニング152の内部側壁が区分されないため、第1層間絶縁膜140およびキャパシタオープニング152の側壁に形成された金属層160aを除去するための湿式エッチング工程で、下部電極に形成されるための十分な量の金属層160aが残れるほどキャパシタオープニング152の底面に形成された金属層160aの底の部分が十分に厚く、キャパシタオープニング152の側壁に形成された金属層が相対的に薄い。

#### 【0076】

図3Dを参照すれば、金属層160aが湿式エッチング等を利用し、第1層間絶縁膜140上に形成された部分と第2ゲートポリシリコン120b上に形成された部分とに分離される。この湿式エッチングの結果として、キャパシタオープニング152の内部側壁に形成されていた金属層160aの側壁の部分が除去され、キャパシタオープニング152の側壁が露出する。

#### 【0077】

したがって、キャパシタオープニング152の底面に形成されていた金属層160aがMIMキャパシタの下部電極160として形成される。この時、第1層間絶縁膜140上に形成されていた金属層160aの一部も残る。

#### 【0078】

キャパシタ誘電層170が第1層間絶縁膜140上に形成された金属層160bの上部と下部電極160上のキャパシタオープニング152の内部側壁と底面とに形成される。

#### 【0079】

本実施形態で、キャパシタ誘電層170は例えば、高誘電率の誘電膜、酸化物、酸化物-窒化物-酸化物構造またはその組合せの物質のうち、いずれかの一つで形成することが出来る。

#### 【0080】

キャパシタ上部電極180がキャパシタ誘電層170の上部および側壁を覆いキャパシ

10

20

30

40

50

タオープニング 152 を充填するよう形成される。

【0081】

本実施形態で、キャパシタ上部電極 180 は第1上部電極層 182 と第2上部電極層 184 として形成される。

【0082】

第1上部電極層 182 は第2上部電極層 184 とキャパシタ誘電層 170 との接着力を向上させ、拡散障壁の特性を有し、相対的に薄く形成される。第1上部電極は例えば、TiN、TaN、WN、HfN、ZrN、他の金属窒化物またはその組合せで形成することが出来る。

【0083】

第2上部電極層 184 は例えばCuまたはWのように優秀な充填特性を有し、抵抗が低い金属で形成される。

【0084】

図3Eを参照すれば、CMP工程等を行い、第1層間絶縁膜 140 を露出させる。第1層間絶縁膜 140 上に形成された第2上部電極層 184、第1上部電極層 182、キャパシタ誘電層 170 および金属層 160b が除去される。

【0085】

MIMキャパシタは第2ゲートスタック 130b 上に形成された下部電極 160、キャパシタ誘電層 170、および第1および第2上部電極層 182、184 を含む上部電極 180 を含む。

【0086】

次に、第2層間絶縁膜 210 が形成されて平坦化される。第2層間絶縁膜 210 の厚さはその上に形成される上層のインターフェクション 242a、242b、242c、242d が位置しなければならない高さを考慮した厚さで形成される。

【0087】

上層のインターフェクション 242a、242b、242c、242d を形成する前に、第2および第1層間絶縁膜 210、140 を垂直に貫通し、第2ゲートポリシリコンパターン 120b、上部キャパシタ電極層 184、第1ゲートスタック 130a 上のシリサイド層 129 およびソース／ドレイン領域 128 上のシリサイド領域 129 の上部領域を露出するコントラクトホールが形成される。

【0088】

次に、第1ないし第4垂直コンタクト 190a、190b、190c、190d を形成するためにコンタクトホール内に金属が充填される。

【0089】

上部キャパシタ電極層 184 と電気的に連結される第2垂直コンタクト 190b および第2ポリシリコンパターン 120b / キャパシタ下部電極 160 と電気的に連結される第1垂直コンタクト 190a は抵抗を低くして電流を増加させるために複数個で形成することが出来る。

【0090】

第2層間絶縁膜 210 上に第1ないし第4垂直コンタクト 190a、190b、190c、190d と電気的に連結される上層のインターフェクション 242a、242b、242c、242d が素子の他の位置に信号を伝達するために形成される。

【0091】

本実施形態で、MIMキャパシタの要素を定義するために一枚だけの追加的なフォトマスクが要求されるので工程効率が増加する。

【0092】

本実施形態で、キャパシタはMIM構造であるため優秀なVCC特性を有し、基板 100 と上に近く低い高さにMIM構造でキャパシタが形成されるので金属層 (metal level) で広いルーティング面積を確保することができる。

【0093】

10

20

30

40

50

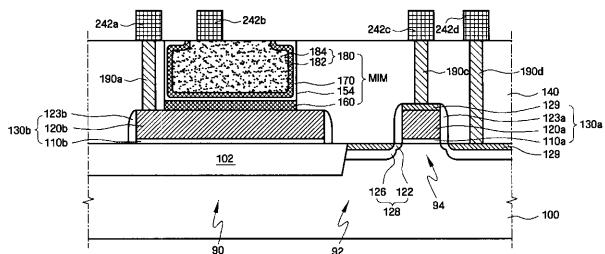

図4は本発明の第4実施形態によるMIMキャパシタを含む半導体集積回路素子の断面図である。

【0094】

図4の第4実施形態は図3Aないし3Eに図示された第3実施形態と比較して、実質的に同じ方法を使用し、製造することが出来、実質的に類似の構造である。

【0095】

第3実施形態とは異なり、第2層間絶縁膜210が形成されず、第1層間絶縁膜140上に形成された金属層160b、キャパシタ誘電層170、第1上部電極層182および第2上部電極層184がCMP工程で除去される。

【0096】

本発明の第2実施形態では、第2ゲートポリシリコンパターン120bの上部領域、第1ゲートスタック130a上のシリサイド層129、および活性領域92に形成されたトランジスタ94のソース／ドレイン領域128上のシリサイド層129を露出するように第1層間絶縁膜140内にコンタクトホールが形成される。その後、垂直コンタクト190a、190c、190dの内部が金属で充填される。

【0097】

次に、素子の他の領域に信号を伝達するための上層のインターフェクション242a、242c、242dが垂直コンタクト190a、190c、190dと電気的に連結され第1層間絶縁膜140上に形成される。また、上層インターフェクションのうちの一つ242bは直接MIMキャパシタの上部電極180と電気的に連結される。

【0098】

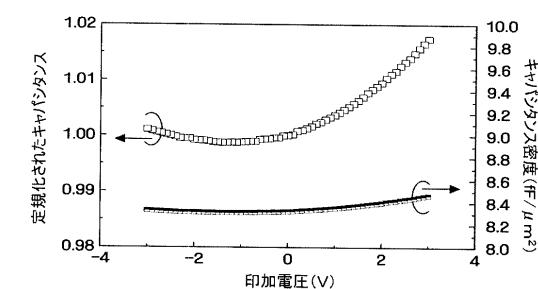

多様な実施形態の効果を立証するための実験が行われた。

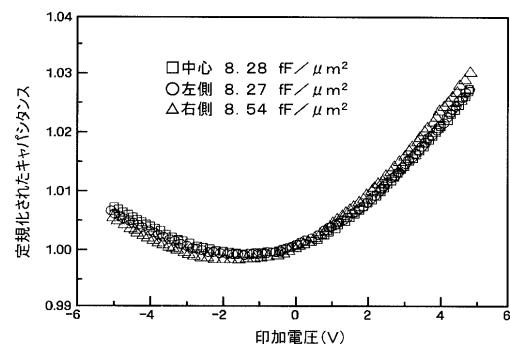

本実験の目的はキャパシタが半導体ウェハ上に第1上部電極180の第1上部電極層182と下部電極160がTINであり、キャパシタ誘電層170が約200nmの厚さのHfO<sub>2</sub>で形成された場合のキャパシタンスである。図9に見られるように、キャパシタンスは8fF/μm<sup>2</sup>以上で比較的高いキャパシタンスであった。上部金属線を通さず、データがポリシリコンパターン／キャパシタの下部および上部電極と直接連結されたプローブを利用して得られた。

【0099】

図5は本発明によって製造されたMIMキャパシタで、印加電圧(X軸)によって相対的に安定した定規化されたキャパシタンス(左側Y軸)とキャパシタンス密度(右側Y軸)を示す実験データのグラフである。

【0100】

図5を参照すれば、本発明によるMIMキャパシタのキャパシタンス密度は約8fF/μm<sup>2</sup>以上で、一般的なPIPキャパシタのキャパシタンス密度の約4fF/μm<sup>2</sup>より1ないし2fF/μm<sup>2</sup>以上さらに高い数値である。

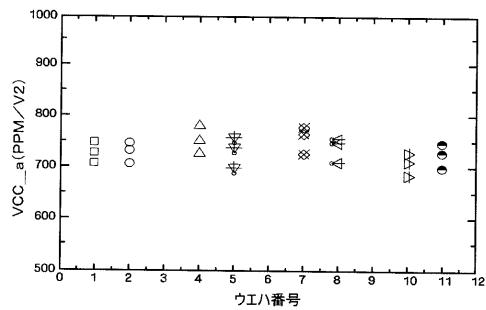

【0101】

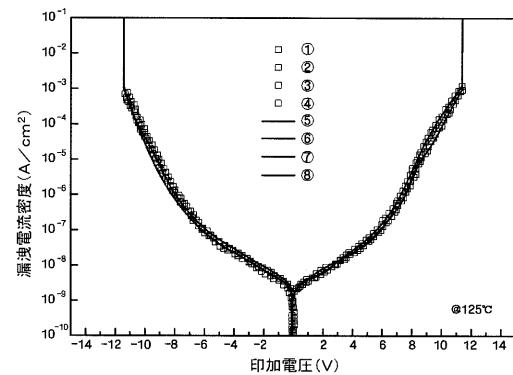

図6は本発明によって、8種の他の工程によって製造されたMIMキャパシタのウェハで、VCC値を反復的に示す実験データのグラフである。8種の他の工程は図11を参照して説明される。

【0102】

図6を参照すれば、ウェハナンバーに関係なく約700ppm/V<sup>2</sup>程度の相対的に低いVCC値を示す。一般的なPIPとのこの比較で、一般的なVCCは約3000ppm/V<sup>2</sup>程度である。このグラフは他の工程条件で形成されたとしても希望のVCC値が得られるということを示している。

【0103】

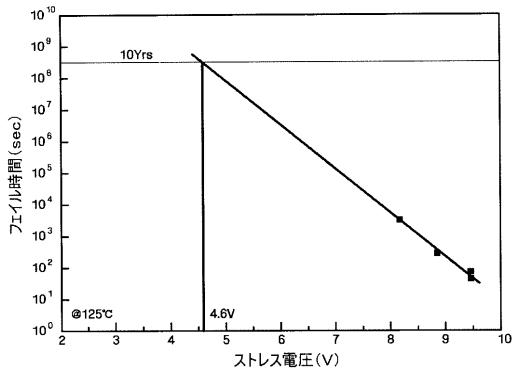

図7は本発明によって製造されたMIMキャパシタで、ストレス電圧によってフェイルが発生する時間を示す実験データのグラフである。

【0104】

図7を参照すれば、本発明によるMIMを使用したCISで、一般的な電圧の3.3V

10

20

30

40

50

でより長い寿命を有すようになることが分かる。さらに詳細に、図7は125で10年寿命を満足する電圧が約4.6Vであることを表す。

#### 【0105】

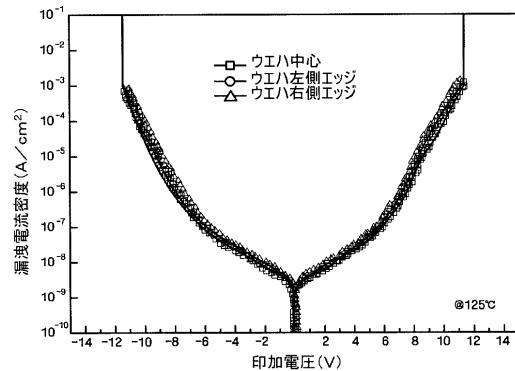

図8は本発明によって、ウェハ上の互いに異なる位置に製造されたMIMキャパシタで、印加された電圧によって相対的に安定した漏洩電流密度を示す実験データのグラフである。

#### 【0106】

図8を参照すれば、ウェハ中心、左側エッジ、右側エッジで測定した漏洩電流特性がすべて良好でほとんど一致することを表している。すなわち、ウェハ位置に格別な影響を受けないことが分かる。

#### 【0107】

図9は本発明によって、ウェハ上の互いに異なる位置に製造されたMIMキャパシタで、印加された電圧によって定規化されたキャパシタンス値を反復的に示す実験データのグラフである。

#### 【0108】

図9を参照すれば、ウェハ位置に大きい影響を受けない定規化されたキャパシタンス値を示しているのが分かる。すなわち、VCC分布がほとんど存在しない。

図10は本発明による8種の他の工程によって製造されたMIMキャパシタで、印加電圧にともなう漏洩電流密度を示した実験データのグラフである。

#### 【0109】

図10を参照すれば、キャパシタオープニング拡張方法、下部金属層蒸着方式および下部金属電極層除去条件間の比較結果、漏洩電流特性がほとんど同一であることが分かる。

#### 【0110】

図11は本発明においての図10の8種の工程の実験データ表である。

図11を参照すれば、キャパシタオープニングを拡張させるための2種の方法(HF/LAL湿式エッチング)と、下部電極層を形成するための2種の方法(物理的気相蒸着方法/イオン化された物理的気相蒸着方法)および多様なPAN方法による8種の工程条件を示している。

#### 【0111】

以上で、MIMキャパシタを含む半導体集積回路素子およびその製造方法を説明した。特に、他の位置に形成されたトランジスタのゲート層を形成するために使用されるパターンングされた伝導体上に形成されたMIMを含む半導体集積回路素子が説明された。

#### 【0112】

以上添付された図面を参照し、本発明の実施形態を説明したが、本発明が属する技術分野で通常の知識を有する者は本発明がその技術的思想や必須的な特徴を変更せずとも他の具体的な形態で実施され得るということを理解できるであろう。そのため以上で記述した実施形態はすべての面で例示的なものであり、限定的ではないものと理解しなければならない。

#### 【産業上の利用可能性】

#### 【0113】

本発明のMIMキャパシタを含む半導体集積回路素子およびその製造方法はロジック、CISおよびメモリ半導体素子、モジュールスマートカード等、電子産業分野に広く使用することが出来る。ただし、以上で言及した素子および産業上利用分野は例示的なものに過ぎない。

#### 【図面の簡単な説明】

#### 【0114】

【図1A】本発明の一番実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である(その1)。

【図1B】本発明の一番実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である(その2)。

10

20

30

40

50

【図 1 C】本発明の一番実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である(その3)。

【図 1 D】本発明の一番実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である(その4)。

【図 1 E】本発明の一番実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である(その5)。

【図 1 F】本発明の一番実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である(その6)。

【図 2】は本発明の第2実施形態によるMIMキャパシタの断面図である。

【図 3 A】は本発明の第3実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である。図1に例示されている本発明の一実施形態による半導体集積回路装置の製造工程を示す工程中間段階構造物の断面図である(その1)。

【図 3 B】は本発明の第3実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である。図1に例示されている本発明の一実施形態による半導体集積回路装置の製造工程を示す工程中間段階構造物の断面図である(その2)。

【図 3 C】は本発明の第3実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である。図1に例示されている本発明の一実施形態による半導体集積回路装置の製造工程を示す工程中間段階構造物の断面図である(その3)。

【図 3 D】は本発明の第3実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である。図1に例示されている本発明の一実施形態による半導体集積回路装置の製造工程を示す工程中間段階構造物の断面図である(その4)。

【図 3 E】は本発明の第3実施形態によるMIMキャパシタを製造する方法を説明するためのMIMキャパシタの断面図である。図1に例示されている本発明の一実施形態による半導体集積回路装置の製造工程を示す工程中間段階構造物の断面図である(その5)。

【図 4】は本発明の第4実施形態によるMIMキャパシタの断面図である。

【図 5】は本発明により製造されたMIMキャパシタで、印加される電圧により相対的に安定したキャパシタンス密度を示す実験データのグラフである。

【図 6】は本発明による8種の他の工程によって製造されたMIMキャパシタのウェハで、VCC値を反復的に示す実験データのグラフである。

【図 7】は本発明により製造されたMIMキャパシタで、ストレス電圧によりフェイルが発生する時間を示す実験データのグラフである。

【図 8】は本発明によるウェハ上の互いに異なる位置に製造されたMIMキャパシタで、印加された電圧により相対的に安定した漏洩電流密度を示す実験データのグラフである。

【図 9】は本発明によるウェハ上の互いに異なる位置に製造されたMIMキャパシタで、印加された電圧により提供されている定規化されたキャパシタンス値を反復的に示す実験データのグラフである。

【図 10】は本発明による8種の他の工程によって、製造されたMIMキャパシタで、印加電圧にともなう漏洩電流密度を示す実験データのグラフである。

【図 11】は本発明で、図6および図10の8種類工程の実験データ表である。

#### 【符号の説明】

##### 【0115】

|     |            |

|-----|------------|

| 100 | 基板         |

| 90  | 絶縁領域       |

| 92  | 活性領域       |

| 94  | トランジスタ     |

| 102 | フィールド酸化膜   |

| 110 | ゲート酸化膜     |

| 120 | ゲートポリシリコン  |

| 128 | ソース／ドレイン領域 |

| 129 | シリサイド領域    |

10

20

30

40

50

|       |            |

|-------|------------|

| 1 3 0 | ゲートスタック    |

| 1 4 0 | 第1層間絶縁膜    |

| 1 5 0 | 犠牲層        |

| 1 6 0 | 下部電極       |

| 1 7 0 | キャパシタ誘電層   |

| 1 8 0 | 上部電極       |

| 1 9 0 | 垂直コンタクト    |

| 2 1 0 | 第2層間絶縁膜    |

| 2 4 2 | インターロネクション |

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

|   | 拡張方法<br>(エッジング液/時間) | 下部電極<br>形成方法 | キャバシタパターンの<br>側壁除去方法<br>(エッジング液/時間) |

|---|---------------------|--------------|-------------------------------------|

| 1 | HF600s              | PVD-TIN 200Å | PAN/120s                            |

| 2 | HF600s              | PVD-TIN 200Å | PAN/180s                            |

| 3 | HF600s              | PVD-TIN 200Å | PAN/120s                            |

| 4 | HF600s              | PVD-TIN 200Å | PAN/180s                            |

| 5 | LAL/20s             | PVD-TIN 200Å | PAN/60s                             |

| 6 | LAL/20s             | PVD-TIN 200Å | PAN/120s                            |

| 7 | LAL/20s             | PVD-TIN 200Å | PAN/60s                             |

| 8 | LAL/20s             | PVD-TIN 200Å | PAN/120s                            |

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

**H 0 1 L 27/06 (2006.01)**

F ターム(参考) 5F033 HH04 HH07 HH11 HH17 HH18 HH19 HH21 HH25 HH32 HH33

HH34 KK04 KK11 KK17 KK19 KK21 KK25 KK32 KK33 KK34

MM05 MM07 PP15 QQ09 QQ16 QQ19 QQ28 QQ37 QQ43 QQ44

QQ48 RR04 TT08 UU01 VV06 VV10

5F038 AC05 AC15 AC16 AC17 EZ06 EZ13 EZ14 EZ15 EZ16 EZ20

5F048 AA07 AC10 BA01 BA02 BA16 BB05 BB08 BB12 BC06 BF01

BF03 BF06 BF07 BF11 BF15 BF16 BG12 BG13 DA25