## (10) **DE 10 2006 018 874 A1** 2007.10.25

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2006 018 874.8

(22) Anmeldetag: 24.04.2006(43) Offenlegungstag: 25.10.2007

(51) Int Cl.8: **H01L 23/48** (2006.01)

**H05K 1/02** (2006.01) **H05K 1/11** (2006.01) **H01L 25/11** (2006.01)

(71) Anmelder:

Infineon Technologies AG, 81669 München, DE

(74) Vertreter:

Epping Hermann Fischer, Patentanwaltsgesellschaft mbH, 80339 München (72) Erfinder:

Djordjevic, Srdjan, 81547 München, DE; Hoppe, Wolfgang, 83646 Bad Tölz, DE

Prüfungsantrag gemäß § 44 PatG ist gestellt.

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

(54) Bezeichnung: Schaltungsanordnung zur Koppelung einer Spannungsversorgung an ein Halbleiterbauelement, Verfahren zur Herstellung der Schaltungsanordnung sowie Datenverarbeitungsgerät umfassend die Schaltungsanordnung

(57) Zusammenfassung: Eine Schaltungsanordnung (1) umfasst eine Anordnung von Schichten (6), wobei die Anordnung von Schichten (6) eine erste Oberfläche (2) und eine zweite Oberfläche (3) aufweist, mindestens eine erste (100) und mindestens eine zweite (200) Durchkontaktierung, mindestens eine dritte Durchkontaktierung (300), mindestens ein erstes Halbleiterbauelement (4) und mindestens ein zweites Halbleiterbauelement (5). Eine erste (10-6) einer Vielzahl von Schichten (10-1 bis 10-10) weist einen ersten leitfähigen Bereich (20) und einen zweiten leitfähigen Bereich (30) auf, die über eine leitfähige Verbindung (150) gekoppelt sind. Eine zweite (10-10) der Vielzahl von Schichten (10-1 bis 10-10) weist mindestens einen ersten leitfähigen Bereich (70) auf, der an die erste Durchkontaktierung (100) gekoppelt ist und einen zweiten leitfähigen Bereich (80), der an die zweite Durchkontaktierung (200) gekoppelt ist. Der erste leitfähige Bereich (20) der ersten (10-6) Schicht ist an die erste Durchkontaktierung (100) gekoppelt und der zweite leitfähige Bereich (30) der ersten Schicht (10-6) ist an die zweite Durchkontaktierung (200) gekoppelt. Das erste Halbleiterbauelement (4) ist auf der ersten Oberfläche (2) angeordnet und an den ersten leitfähigen Bereich (20) der ersten Schicht (10-6) über die dritte Durchkontaktierung (300) gekoppelt. Ein Kontaktanschluss (40) zur Kopplung an eine Spannungsversorgung ist an der zweiten Oberfläche (3) angeordnet und an den ersten leitfähigen Bereich (70) der ...

#### **Beschreibung**

**[0001]** Schaltungsanordnung zur Koppelung einer Spannungsversorgung an ein Halbleiterbauelement, Verfahren zur Herstellung der Schaltungsanordnung sowie Datenverarbeitungsgerät umfassend die Schaltungsanordnung

[0002] Die vorliegende Erfindung betrifft eine Schaltungsanordnung zur Koppelung einer Spannungsversorgung an ein Halbleiterbauelement, ein Verfahren zur Herstellung der Schaltungsanordnung sowie ein Datenverarbeitungsgerät umfassend die Schaltungsanordnung. Die Erfindung betrifft insbesondere Schaltungsanordnungen, die als gepuffertes Dual Inline Memory Module ausgebildet sind.

[0003] Datenverarbeitungseinrichtungen, insbesondere Server-Systeme, umfassen typischerweise eine Vielzahl von Speichermodulen, die über eine Leiterplatte an eine Steuereinheit der Datenverarbeitungseinrichtung gekoppelt sind. Gepufferte Speichermodule weisen dabei eine Mehrlagenleiterplatte, einen auf einer Oberfläche der Mehrlagenleiterplatte angeordneten Hubchip sowie mehrere auf einer Oberfläche der Mehrlagenleiterplatte angeordnete Speicherchips wie etwa Speicherchips mit wahlfreiem Zugriff (DRAMs) zum Speichern von Daten auf. Zugriffe von der Steuereinheit auf die jeweiligen Speichermodule, wie etwa Lese- und Schreibzugriffe, werden dabei von dem jeweiligen Hubchip kontrolliert.

**[0004]** Um die Funktionstüchtigkeit der Datenverarbeitungseinrichtung zu gewährleisten muss eine an den einzelnen Hubchips anliegende Versorgungsspannung innerhalb gewisser Grenzen kontrolliert werden.

[0005] Die Versorgungsspannung kann mittels einem auf der Leiterplatte des Datenverarbeitungsgeräts angeordneten Spannungsregulierer eingestellt und über in der Leiterplatte verlaufende Leiterbahnen zu jeweiligen Kontaktanschlüssen der Speichermodule geführt werden. Typischerweise versorgt der Spannungsregulierer mehrere der Speichermodule, die in einer Reihenanordnung angeordnet sind.

**[0006]** Innerhalb der einzelnen Speichermodule wird die Versorgungsspannung dann über eine leitfähige Verbindung, die beispielsweise Kontaktlöcher, die sich von einer Lage der Mehrlagenleiterplatte bis zu einer anderen Lage der Mehrlagenleiterplatte erstrecken, und eine oder mehrere strukturierte leitfähige Schichten der Mehrlagenleiterplatte umfasst, zu dem Hubchip geführt.

[0007] Bei einem Herstellungsprozesses der Mehrlagenleiterplatte, der das Ausbilden von Kontaktlöchern, die sich von einer Lage der Mehrlagenleiterplatte bis zu einer anderen Lage der Mehrlagenleiter-

platte erstrecken, umfasst, kann gegebenenfalls die Schichtdicke von strukturierten leitfähigen Schichten, die zur leitfähigen Verbindung zwischen dem Kontaktanschluss und dem Hubchip beitragen, variieren.

**[0008]** Ist die Schichtdicke beispielsweise gering, so kann die an dem Hubchip in Folge einer hohen Impedanz der leitfähigen Verbindung anliegende Spannung niedriger sein als vorgegeben.

**[0009]** Ist die Schichtdicke dagegen beispielsweise hoch, so kann die an dem Hubchip in Folge einer geringen Impedanz der leitfähigen Verbindung anliegende Spannung höher sein als vorgegeben.

**[0010]** Es besteht daher die Anforderung, Schaltungsanordnungen, Verfahren zur Herstellung von Schaltungsanordnungen sowie Datenverarbeitungsgeräte, die eine Schaltungsanordnung aufweisen, weiter zu verbessern.

[0011] Gemäß einer Ausführungsform der Erfindung wird eine Schaltungsanordnung vorgesehen. Die Schaltungsanordnung umfasst eine Anordnung von Schichten, wobei die Anordnung von Schichten eine erste Oberfläche und eine zweite Oberfläche, sowie eine Vielzahl von Schichten, die in einer übereinander gestapelten Anordnung zwischen der ersten Oberfläche und der zweiten Oberfläche angeordnet sind, aufweist, mindestens eine erste Durchkontaktierung, mindestens eine zweite Durchkontaktierung, mindestens ein erstes Halbleiterbauelement, und mindestens ein zweites Halbleiterbauelement.

[0012] Eine erste der Vielzahl von Schichten weist einen ersten leitfähigen Bereich und einen zweiten leitfähigen Bereich auf, die über eine einen hohen elektrischen Widerstand aufweisende leitfähige Verbindung gekoppelt sind. Eine zweite der Vielzahl von Schichten weist mindestens einen ersten leitfähigen Bereich, der an die erste Durchkontaktierung gekoppelt ist, und einen zweiten leitfähigen Bereich auf, der an die zweite Durchkontaktierung gekoppelt ist.

**[0013]** Der erste leitfähige Bereich der ersten der Vielzahl von Schichten ist an die erste Durchkontaktierung gekoppelt und der zweite leitfähige Bereich der ersten der Vielzahl von Schichten ist an die zweite Durchkontaktierung gekoppelt.

**[0014]** Das erste Halbleiterbauelement ist auf der ersten Oberfläche angeordnet und an den ersten leitfähigen Bereich der ersten der Vielzahl von Schichten über die dritte Durchkontaktierung gekoppelt.

**[0015]** Die erste Durchkontaktierung und die zweite Durchkontaktierung erstrecken sich jeweils von der zweiten Oberfläche bis zu einer der zweiten Schicht abgewandten Oberfläche der ersten Schicht.

**[0016]** An der zweiten Oberfläche ist ein Kontaktanschluss zur Kopplung an eine Spannungsversorgung angeordnet, wobei der Kontaktanschluss an den ersten leitfähigen Bereich der zweiten Schicht gekoppelt ist

[0017] Gemäß einer weiteren Ausführungsform der Erfindung ist ein Verfahren zum Ausbilden einer Schaltungsanordnung vorgesehen. Das Verfahren umfasst das Strukturieren einer ersten Schicht einer ersten Anordnung von Schichten, wobei die erste Anordnung von Schichten eine erste Oberfläche und eine zweite Oberfläche und eine Vielzahl von Schichten, die in einer übereinander gestapelten Anordnung zwischen der ersten Oberfläche und der zweiten Oberfläche angeordnet sind, aufweist, wobei die erste Schicht benachbart zu der ersten Oberfläche angeordnet ist, und dabei Ausbilden eines ersten leitfähigen Bereichs, eines zweiten leitfähigen Bereichs und einer einen hohen Widerstand aufweisenden leitfähigen Verbindung zwischen dem ersten leitfähigen Bereich und dem zweiten leitfähigen Bereich der ersten Schicht.

[0018] Das Verfahren umfasst ferner das Strukturieren einer der zweiten Oberfläche benachbarten zweiten Schicht der ersten Anordnung von Schichten und dabei Ausbilden eines ersten leitfähigen Bereichs und eines zweiten leitfähigen Bereichs der zweiten Schicht.

[0019] Des Weiteren umfasst das Verfahren das Ausbilden eines ersten Kontaktlochs, das sich von dem ersten leitfähigen Bereich der ersten Schicht bis zu dem ersten leitfähigen Bereich der zweiten Schicht erstreckt, das Ausbilden eines zweiten Kontaktlochs, das sich von dem zweiten leitfähigen Bereich der ersten Schicht bis zu dem zweiten leitfähigen Bereich der zweiten Schicht erstreckt, das Füllen des ersten und des zweiten Kontaktlochs mit einem leitfähigen Material, das Verbinden der ersten Anordnung von Schichten mit einer zweiten Anordnung von Schichten, wobei die zweite Anordnung von Schichten eine erste Oberfläche und eine zweite Oberfläche aufweist und dabei Ausbilden einer isolierenden Schicht auf der ersten Oberfläche der ersten Anordnung von Schichten oder auf der zweiten Oberfläche der zweiten Anordnung von Schichten.

[0020] Das Verfahren umfasst ferner das Ausbilden eines Kontaktlochs, das sich von der ersten Oberfläche der zweiten Anordnung von Schichten bis zur zweiten Oberfläche der ersten Anordnung von Schichten erstreckt und an den ersten leitfähigen Bereich der zweiten Schicht der ersten Anordnung von Schichten angrenzt, das Füllen des Kontaktlochs mit einem leitfähigen Material, das Ausbilden eines Kontaktanschlusses an der zweiten Oberfläche der ersten Anordnung von Schichten und Koppeln des Kontaktanschlusses an den ersten leitfähigen Bereich

der zweiten Schicht der ersten Anordnung von Schichten.

**[0021]** Gemäß einer weiteren Ausführungsform der Erfindung ist ein Datenverarbeitungsgerät vorgesehen, das eine Leiterplatte mit mehreren Buchsen, eine auf der Leiterplatte angeordnete Steuereinheit sowie mindestens eine Schaltungsanordnung gemäß einer Ausführungsform der Erfindung umfasst, wobei die mindestens eine Schaltungsanordnung einen Randstecker aufweist und mittels des Randsteckers an die Steuereinheit gekoppelt ist.

**[0022]** Weitere vorteilhafte Ausführungen der Erfindung sind den Unteransprüchen zu entnehmen.

**[0023]** Die Erfindung soll anhand von Ausführungsbeispielen mit Hilfe von Zeichnungen näher erläutert werden. Darin zeigen:

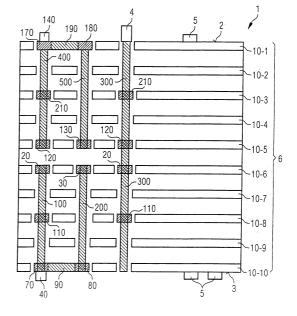

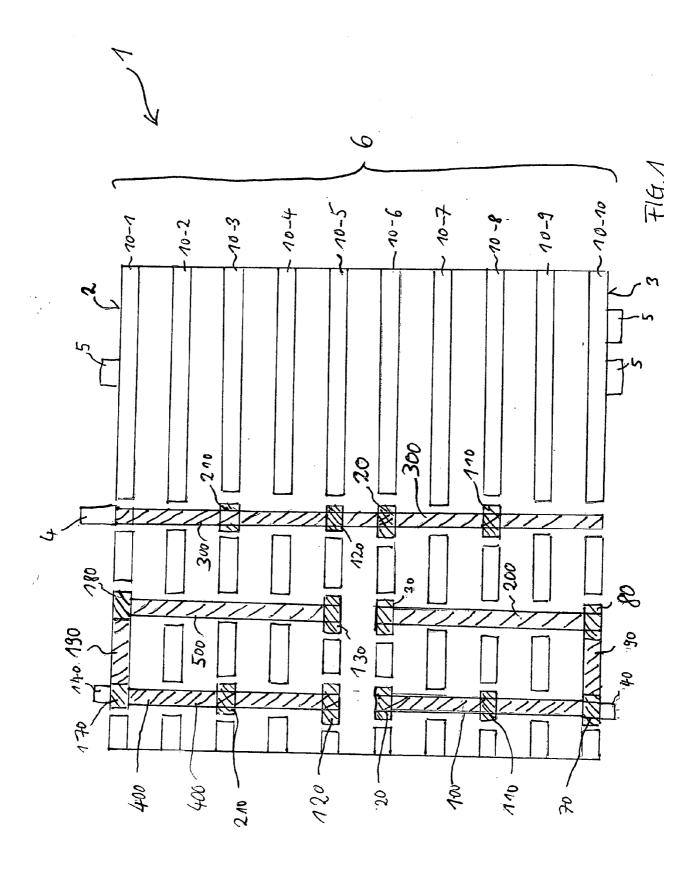

**[0024]** Fig. 1 schematisch eine Querschnittsansicht einer Schaltungsanordnung gemäß einer Ausführungsform der Erfindung,

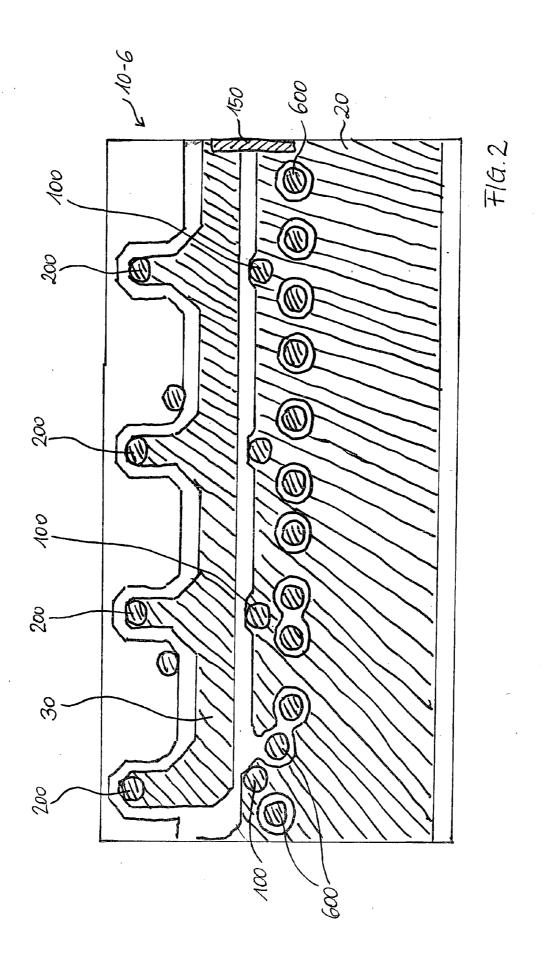

[0025] Fig. 2 eine Draufsicht auf einen Abschnitt der in Fig. 1 dargestellten ersten Schicht 10-6 der Schaltungsanordnung,

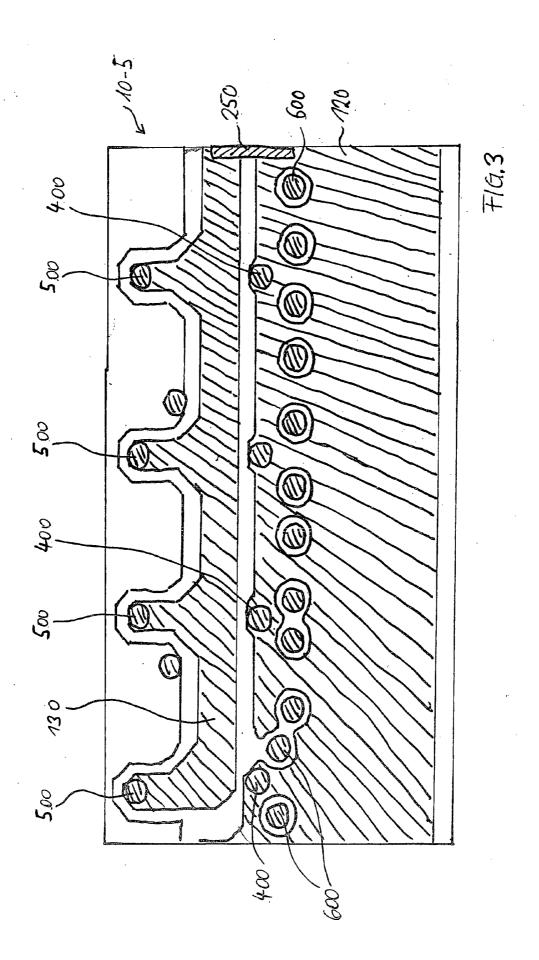

[0026] Fig. 3 eine Draufsicht auf einen Abschnitt der in Fig. 1 dargestellten vierten Schicht 10-5 der Schaltungsanordnung,

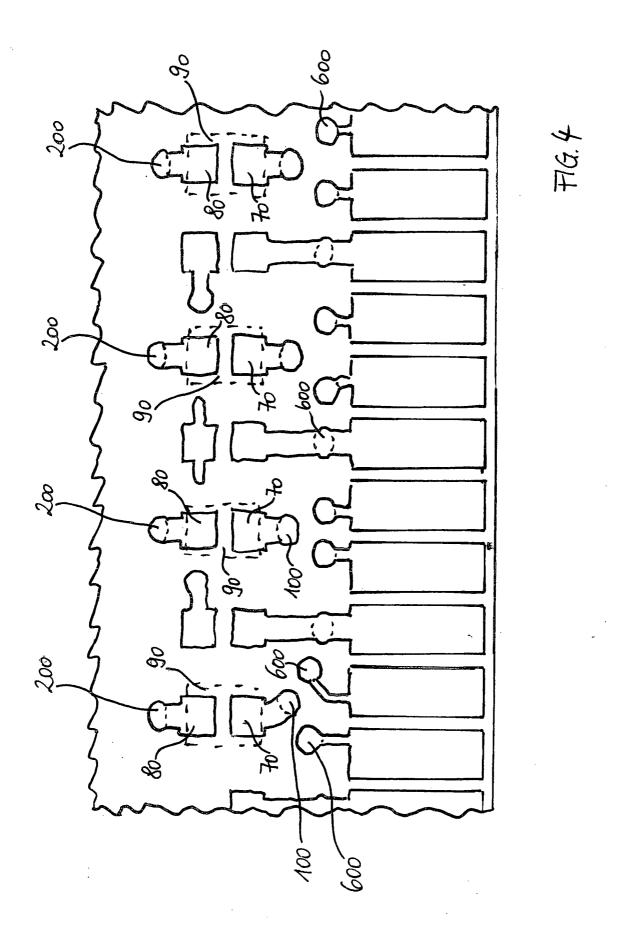

[0027] Fig. 4 eine Draufsicht auf einen Abschnitt der in Fig. 1 dargestellten zweiten Schicht 10-10 der Schaltungsanordnung,

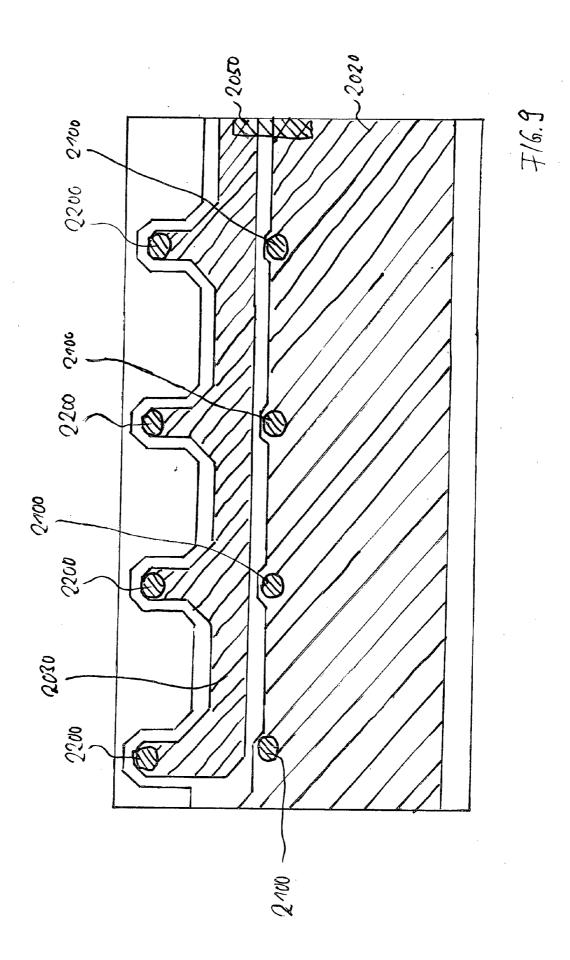

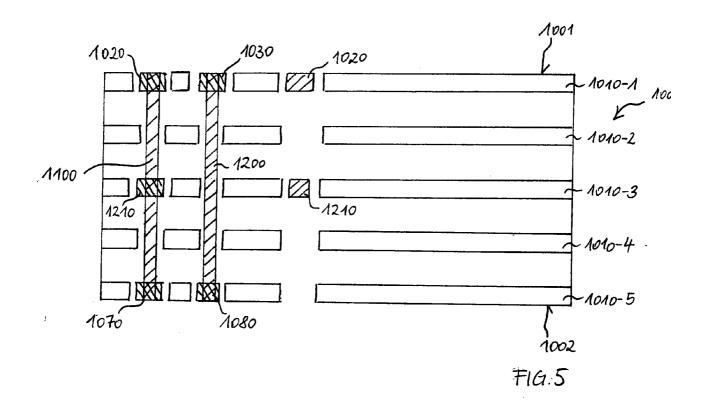

**[0028]** Fig. 5 bis Fig. 9 eine Schaltungsanordnung in unterschiedlichen Stufen des Herstellungsprozesses der Schaltungsanordnung, und

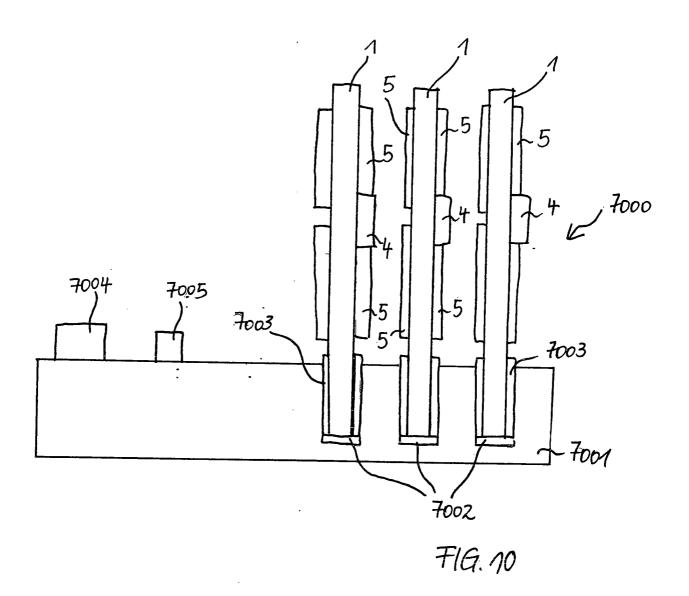

**[0029]** Fig. 10 ein Datenverarbeitungsgerät gemäß einer Ausführungsform der Erfindung.

[0030] Fig. 1 zeigt schematisch eine Querschnittsansicht einer Schaltungsanordnung gemäß einer Ausführungsform der Erfindung. Die Schaltungsanordnung 1 umfasst eine Anordnung von Schichten 6, wobei die Anordnung von Schichten 6 beispielsweise als Mehrlagenleiterplatte ausgebildet ist, und wobei die Anordnung von Schichten 6 eine erste Oberfläche 2, eine von der ersten Oberfläche 2 abgewandte zweite Oberfläche 3 und eine Vielzahl von Schichten 10-1 bis 10-10, die in einer übereinander gestapelten Anordnung zwischen der ersten Oberfläche 2 und der zweiten Oberfläche 3 der Anordnung von Schichten 6 angeordnet sind, aufweist.

[0031] Jede der Vielzahl von Schichten 10-1 bis 10-10 kann eine oder mehrere strukturierte leitfähige Leiterbahnen umfassen. Bevorzugt umfassen die

### DE 10 2006 018 874 A1 2007.10.25

strukturierten Leiterbahnen ein Metall, wie etwa Kupfer. Zwischen benachbarten der Vielzahl von Schichten 10-1 bis 10-10 ist jeweils ein elektrisch isolierendes Material (nicht gezeigt in Fig. 1) vorgesehen. Das elektrisch isolierende Material umfasst bevorzugt mit Epoxidharz getränkte Glasfasermatten. Das elektrisch isolierende Material kann aber auch Teflon, Keramik oder Polyesterfolie umfassen.

[0032] Eine erste 10-6 der Vielzahl von Schichten 10-10 weist einen ersten strukturierten leitfähigen Bereich 20 und einen zweiten strukturierten leitfähigen Bereich 30 auf. Der erste strukturierte leitfähige Bereich 20 und der zweite strukturierte leitfähige Bereich 30 der ersten Schicht 10-6 sind über eine einen hohen elektrischen Widerstand aufweisende leitfähige Verbindung (nicht gezeigt in Fig. 1) gekoppelt.

[0033] Eine zweite 10-10 der Vielzahl von Schichten 10-1 bis 10-10 ist benachbart zu der zweiten Oberfläche 3 der Anordnung von Schichten 6 angeordnet. Die zweite Schicht 10-10 weist einen ersten strukturierten leitfähigen Bereich 70 und einen zweiten strukturierten leitfähigen Bereich 80 auf.

[0034] Eine erste Durchkontaktierung 100 erstreckt sich von der zweiten Oberfläche 3 der Anordnung von Schichten 6 bis zu der ersten 10-6 der Vielzahl von Schichten 10-1 bis 10-10, wobei der erste strukturierte leitfähige Bereich 20 der ersten Schicht 10-6 an die erste Durchkontaktierung 100 gekoppelt ist, und wobei der erste strukturierte leitfähige Bereich 70 der zweiten Schicht 10-10 an die erste Durchkontaktierung 100 gekoppelt ist.

[0035] Des Weiteren ist eine zweite Durchkontaktierung 200 vorgesehen, die sich von der zweiten Oberfläche 3 der Anordnung von Schichten 6 bis zu der ersten Schicht 10-6 erstreckt, wobei der zweite strukturierte leitfähige Bereich 30 der ersten Schicht 10-6 an die zweite Durchkontaktierung 200 gekoppelt ist, und wobei der zweite strukturierte leitfähige Bereich 80 der zweiten Schicht 10-10 an die zweite Durchkontaktierung 200 gekoppelt ist.

[0036] Eine dritte Durchkontaktierung 300 erstreckt sich von der ersten Oberfläche 2 der Anordnung von Schichten 6 bis zu der zweiten Oberfläche 3 der Anordnung von Schichten 6. Der erste strukturierte leitfähige Bereich 20 der ersten Schicht 10-6 ist an die dritte Durchkontaktierung 300 gekoppelt.

[0037] Auf der ersten Oberfläche 2 der Anordnung von Schichten 6 ist ein erstes Halbleiterbauelement 4 angeordnet, das an die dritte Durchkontaktierung 300 gekoppelt ist. Außerdem ist auf der ersten 2 und/oder der zweiten Oberfläche 3 der Anordnung von Schichten 6 mindestens ein zweites Halbleiterbauelement 5 angeordnet.

**[0038]** Bevorzugt umfasst das erste Halbleiterbauelement **4** einen Hubchip. Das zweite Halbleiterbauelement **5** kann beispielsweise einen Speicherchip mit dynamischen Speicherzellen mit wahlfreiem Zugriff (DRAM) oder einen Speicherchip mit synchronen dynamischen Speicherzellen mit wahlfreiem Zugriff (SDRAM) umfassen.

[0039] Die Schaltungsanordnung 1 kann als gepuffertes Dual Inline Memory Module (DIMM) ausgebildet sein, bei dem das erste Halbleiterbauelement 4 ein Durchführen von Lese- und Schreibzugriffen auf das mindestens eine zweite Halbleiterbauelement 5 steuert.

[0040] Auf der zweiten Oberfläche 3 der Anordnung von Schichten 6 ist ein Anschlusskontakt 40 zur Koppelung an eine externe Spannungsversorgung vorgesehen, der an den ersten leitfähigen Bereich 70 der zweiten Schicht 10-10 gekoppelt ist.

[0041] Das auf der ersten Oberfläche 2 der Anordnung von Schichten 6 angeordnete erste Halbleiterbauelement 4 ist über einen leitfähigen Pfad, der die dritte Durchkontaktierung 300, den ersten strukturierten leitfähigen Bereich 20 der ersten Schicht 10-6, die erste Durchkontaktierung 100 und den ersten strukturierten leitfähigen Bereich 70 der zweiten Schicht 10-10 umfasst, an den Kontaktanschluss 40 gekoppelt.

**[0042]** Um eine Funktionalität der Schaltungsanordnung **1** zu gewährleisten muss eine Impedanz des leitfähigen Pfades bestimmten Anforderungen genügen. Beispielsweise kann es erforderlich sein, dass die Impedanz des leitfähigen Pfades innerhalb eines Bereichs von 4,06 mOhm und 5,74 mOhm liegt.

[0043] Die Impedanz des leitfähigen Pfades wird insbesondere durch die Ausgestaltung des ersten strukturierten leitfähigen Bereichs 20 der ersten Schicht 10-6 bestimmt.

[0044] Aufgrund des anhand der Fig. 5 bis Fig. 9 näher erläuterten Herstellungsprozesses der Schaltungsanordnung 1 kann die Schichtdicke der ersten Schicht 10-6, und damit die Schichtdicke des ersten strukturierten leitfähigen Bereichs 20 der ersten Schicht 10-6, in einem Maße variieren, so dass die Impedanz des leitfähigen Pfades höher ist, als gefordert wird.

[0045] In diesem Fall kann der erste leitfähige Bereich 70 der zweiten Schicht 10-10 an den zweiten leitfähigen Bereich 80 der zweiten Schicht 10-10 über eine optionale leitfähige Verbindung 90 gekoppelt werden. Durch die leitfähige Verbindung 90 wird auch der zweite leitfähige Bereich 30 der ersten Schicht 10-6 über die zweite Durchkontaktierung 200 an den Anschlusskontakt 40 gekoppelt.

[0046] Da der zweite strukturierte leitfähige Bereich 30 der ersten Schicht 10-6 ferner an den ersten strukturierten leitfähigen Bereich 20 der ersten Schicht 10-6 über die einen hoher Widerstand aufweisende leitfähige Verbindung (nicht gezeigt in Fig. 1) gekoppelt ist, ist ein weiterer leitfähiger Pfad zwischen dem Anschlusskontakt 40 und der dritten Durchkontaktierung 300 vorgesehen. Der weitere leitfähige Pfad verläuft parallel zu einem Abschnitt des leitfähigen Pfades, der zwischen dem ersten strukturierten leitfähigen Bereich 70 der zweiten Schicht 10-10 und der leitfähigen Verbindung (nicht gezeigt in Fig. 1), die zwischen dem ersten strukturierten leitfähigen Bereich 20 der ersten Schicht 10-6 und dem zweiten strukturierten leitfähigen Bereich 30 der ersten Schicht 10-6 vorgesehenen ist.

[0047] Durch die Ausbildung der optionalen leitfähigen Verbindung 90 zwischen dem ersten strukturierten leitfähigen Bereich 70 der zweiten Schicht 10-10 und dem zweiten strukturierten leitfähigen Bereich 80 der zweiten Schicht 10-10 wird die Impedanz einer leitfähigen Verbindung zwischen dem ersten Halbleiterbauelement 4 und dem Kontaktanschluss 40 abgesenkt.

**[0048]** Die Koppelung zwischen dem ersten Halbleiterbauelement **4** und dem Kontaktanschluss **40** kann ferner über weitere leitfähige Verbindungen erfolgen.

[0049] Beispielsweise kann die Anordnung von Schichten 6 eine dritte 10-8 der Vielzahl von Schichten 10-1 bis 10-10 umfassen, die einen strukturierten leitfähigen Bereich 110 umfasst, der über die erste Durchkontaktierung 100 und den ersten strukturierten leitfähigen Bereich 70 der zweiten Schicht 10-10 an den Kontaktanschluss 40 gekoppelt ist, und über die dritte Durchkontaktierung 300 an das erste Halbleiterbauelement 4 gekoppelt ist.

[0050] Gemäß einer Ausführungsform der Erfindung kann das erste Halbleiterbauelement 4 ferner über einen weiteren Kontaktanschluss 140, der an der ersten Oberfläche 2 der Anordnung von Schichten 6 angeordnet ist, an die externe Spannungsquelle gekoppelt werden.

[0051] In diesem Fall umfasst die Anordnung von Schichten 6 des Weiteren eine vierte Schicht 10-5, die einen ersten strukturierten leitfähigen Bereich 120 und einen zweiten strukturierten leitfähigen Bereich 130 aufweist, wobei der erste strukturierte leitfähige Bereich 120 und der zweite strukturierte leitfähige Bereich 130 der vierten Schicht 10-5 über eine einen hohen elektrischen Widerstand aufweisende leitfähige Verbindung (nicht gezeigt in Fig. 1) gekoppelt sind.

[0052] Ferner weist die Anordnung von Schichten 6 eine benachbart der ersten Oberfläche 2 der Anord-

nung von Schichten 6 angeordnete fünfte Schicht 10-1 auf, die einen ersten strukturierten leitfähigen Bereich 170 und einen zweiten strukturierten leitfähigen Bereich 180 umfasst, wobei der erste strukturierte leitfähige Bereich 170 an den weiteren Kontaktanschluss 140 gekoppelt ist.

[0053] Über eine vierte Durchkontaktierung 400, die sich von der ersten Oberfläche 2 der Anordnung von Schichten 6 bis zu der vierten Schicht 10-5 erstreckt, ist der erste strukturierte leitfähige Bereich 170 der fünften Schicht 10-1 an den ersten leitfähigen Bereich 120 der vierten Schicht 10-5 gekoppelt.

[0054] Über eine fünfte Durchkontaktierung 500, die sich von der ersten Oberfläche 2 der Anordnung von Schichten 6 bis zu der vierten Schicht 10-5 erstreckt, ist der zweite strukturierte leitfähige Bereich 130 der vierten Schicht 10-5 an den zweiten strukturierten leitfähigen Bereich 180 der fünften Schicht 10-1 gekoppelt.

[0055] Der erste strukturierte leitfähige Bereich 120 der vierten 10-5 der Vielzahl von Schichten 10-1 bis 10-10 ist ferner an die dritte Durchkontaktierung 300 gekoppelt.

[0056] Das erste Halbleiterbauelement 4 ist somit über einen leitfähigen Pfad, der die dritte Durchkontaktierung 300, den ersten strukturierten leitfähigen Bereich 120 der vierten Schicht 10-5, die vierte Durchkontaktierung 400 und den ersten strukturierten leitfähigen Bereich 170 der fünften Schicht 10-1 umfasst, an den weiteren Anschlusskontakt 140 gekoppelt.

[0057] Die Impedanz einer Kopplung zwischen dem ersten Halbleiterbauelement 4 und dem weiteren Anschlusskontakt 140 kann durch Ausbildung einer leitfähigen Verbindung 190 zwischen dem ersten strukturierten leitfähigen Bereich 170 der fünften Schicht 10-1 und dem zweiten strukturierten leitfähigen Bereich 180 der fünften Schicht 10-1 verringert werden.

[0058] Durch die Ausbildung der leitfähigen Verbindung 190 wird der zweite strukturierte leitfähige Bereich 130 der vierten Schicht 10-5 an den weiteren Anschlusskontakt 140 gekoppelt. Da der zweite strukturierte leitfähige Bereich 130 der vierten Schicht 10-5 ferner an den ersten strukturierten Bereich 120 der vierten Schicht 10-5 gekoppelt ist, ist ein weiterer leitfähiger Pfad zwischen dem weiteren Anschlusskontakt 140 und der Durchkontaktierung vorgesehen.

**[0059]** Die Koppelung zwischen dem ersten Halbleiterbauelement **4** und dem Kontaktanschluss **140** kann ferner über weitere leitfähige Verbindungen erfolgen.

[0060] Beispielsweise kann die Anordnung von Schichten 6 eine sechste 10-3 der Vielzahl von Schichten 10-1 bis 10-10 umfassen, die einen strukturierten leitfähigen Bereich 210 aufweist, der an die vierte Durchkontaktierung 400 und an die dritte Durchkontaktierung 300 gekoppelt ist.

[0061] Fig. 2 zeigt eine Draufsicht auf einen Abschnitt der in Fig. 1 dargestellten ersten Schicht 10-6. Die erste Schicht 10-6 weist einen ersten strukturierten leitfähigen Bereich 20 und einen zweiten strukturierten leitfähigen Bereich 30 auf. Der erste strukturierte leitfähige Bereich 20 ist an mehrere erste Durchkontaktierungen 100 gekoppelt. Ferner sind weitere Durchkontaktierungen 600 vorgesehen, die jedoch nicht an den ersten strukturierten leitfähigen Bereich 20 gekoppelt sind. Die weiteren Durchkontaktierungen 600 können an strukturierte leitfähige Bereiche von anderen der Vielzahl von Schichten 10-1 bis 10-5, 10-7 bis 10-10 (nicht gezeigt in Fig. 2) gekoppelt sein.

[0062] Der zweite strukturierte Bereich 30 ist an mehrere zweite Durchkontaktierungen 200 gekoppelt. Der erste strukturierte Bereich 20 und der zweite strukturierte Bereich 30 sind über eine leitfähige Verbindung 150 gekoppelt, die bevorzugt einen hohen Widerstand aufweist.

[0063] Fig. 3 zeigt eine Draufsicht auf einen Abschnitt der in Fig. 1 dargestellten vierten Schicht 10-5. Die vierte Schicht 10-5 weist einen ersten strukturierten leitfähigen Bereich 120 und einen zweiten strukturierten leitfähigen Bereich 130 auf. Der erste strukturierte leitfähige Bereich 120 ist an mehrere vierte Durchkontaktierungen 400 gekoppelt. Ferner sind weitere Durchkontaktierungen 600 vorgesehen, die jedoch nicht an den ersten strukturierten leitfähigen Bereich 120 gekoppelt sind. Die weiteren Durchkontaktierungen 600 können an strukturierte leitfähige Bereiche von anderen der Vielzahl von Schichten 10-1 bis 10-4, 10-7 bis 10-10 (nicht gezeigt in Fig. 3) gekoppelt sein.

[0064] Der zweite strukturierte Bereich 130 ist an mehrere fünfte Durchkontaktierungen 500 gekoppelt. Der erste strukturierte Bereich 120 und der zweite strukturierte Bereich 130 sind über eine leitfähige Verbindung 250 gekoppelt, die bevorzugt einen hohen Widerstand aufweist.

[0065] Fig. 4 zeigt eine Draufsicht auf einen Abschnitt der zweiten Schicht 10-10 der in Fig. 1 gezeigten Schaltungsanordnung 1.

[0066] Jeweilige erste Durchkontaktierungen 100 sind an jeweilige erste strukturierte leitfähige Bereiche 70 der zweiten Schicht 10-10 gekoppelt. Ferner sind jeweilige zweite strukturierte leitfähige Bereiche 80 an jeweilige zweite Durchkontaktierungen 200 ge-

koppelt.

**[0067]** Aus Gründen der Übersichtlichkeit ist die Kopplung des Anschlusskontakts **40** (nicht gezeigt in Fig. 4) an jeweilige erste strukturierte leitfähige Bereich **70** in Fig. 4 nicht gezeigt.

[0068] Außerdem sind weitere Durchkontaktierungen 600 vorgesehen, die jedoch nicht an die ersten strukturierten leitfähigen Bereiche 70 oder die zweiten strukturierten leitfähigen Bereiche 80 gekoppelt sind

[0069] Wie in Fig. 4 gezeigt, können jeweilige erste strukturierte Bereiche 70 und zweite strukturierte Bereiche 80 über eine optionale leitfähige Verbindung 90 gekoppelt sein. Die leitfähige Verbindung 90 kann beispielsweise mittels eines Lötverfahrens an den ersten strukturierten leitfähigen Bereich 70 und den zweiten strukturierten leitfähigen Bereich 80 gekoppelt werden.

**[0070]** Anhand der <u>Fig. 5</u> bis <u>Fig. 9</u> wird im Folgenden ein Verfahren zur Herstellung einer Schaltungsanordnung gemäß einer Ausführungsform der Erfindung illustriert.

[0071] Mit Bezug auf Fig. 5 wird zunächst eine erste leitfähige Schicht 1010-1 einer ersten Anordnung von Schichten 1000 strukturiert. Das Strukturieren der ersten Schicht 1010-1 kann ebenso wie die im folgenden angegebenen Strukturierungsschritte beispielsweise das Ausbilden eines Photolacks auf der leitfähigen Schicht, Strukturieren des Photolacks mittels Photolithographie und anschließendem Entwickeln des Photolacks, und Ätzen von von dem Photolack unbedeckten Stellen der leitfähigen Schicht beinhalten

[0072] Die erste Anordnung von Schichten 1000 weist eine erste Oberfläche 1001 und eine von der ersten Oberfläche 1001 abgewandte zweite Oberfläche 1002 auf. Zwischen der ersten Oberfläche 1001 und der zweiten Oberfläche 1002 ist eine Vielzahl von Schichten 1010-1 bis 1010-5 in einer übereinander gestapelten Anordnung angeordnet.

[0073] Jede der Vielzahl von Schichten 1010-1 bis 1010-5 kann eine oder mehrere strukturierte leitfähige Leiterbahnen umfassen. Bevorzugt umfassen die strukturierten Leiterbahnen ein Metall, wie etwa Kupfer. Zwischen benachbarten der Vielzahl von Schichten 1010-1 bis 1010-5 ist jeweils ein elektrisch isolierendes Material (nicht gezeigt in Fig. 5) vorgesehen. Das elektrisch isolierende Material umfasst bevorzugt mit Epoxidharz getränkte Glasfasermatten. Das elektrisch isolierende Material kann aber auch Teflon, Keramik oder Polyesterfolie umfassen.

[0074] Die erste Schicht 1010-1 ist benachbart zu

der ersten Oberfläche 1001 der ersten Anordnung von Schichten 1000 angeordnet. Durch die Strukturierung erfolgt ein Ausbilden eines ersten leitfähigen Bereichs 1020, eines zweiten leitfähigen Bereichs 1030 und einer einen hohen Widerstand aufweisenden leitfähigen Verbindung (nicht gezeigt in Fig. 5) zwischen dem ersten leitfähigen Bereich 1020 und dem zweiten leitfähigen Bereich 1030 der ersten Schicht 1010-1.

[0075] Dann wird eine zweite Schicht 1010-5, die benachbart zu der zweiten Oberfläche 1002 der ersten Anordnung von Schichten 1000 angeordnet ist, strukturiert. Dabei wird ein erster strukturierter leitfähiger Bereich 1070 und ein zweiter strukturierter leitfähiger Bereich 1080 der zweiten Schicht 1010-5 ausgebildet.

[0076] Ein erstes Kontaktloch 1100 wird ausgebildet, das sich von der ersten Oberfläche 1001 bis zur zweiten Oberfläche 1002 der ersten Anordnung von Schichten 1000 erstreckt. Beispielsweise kann die Ausbildung des ersten Kontaktlochs 1100 wie auch die Ausbildung weiterer Kontaktlöcher mittels Bohrens erfolgen.

[0077] Das erste Kontaktloch 1100 grenzt an den ersten strukturierten leitfähigen Bereich 1020 der ersten Schicht 1010-1 und an den ersten strukturierten leitfähigen Bereich 1070 der zweiten Schicht 1010-5 an

[0078] Ferner wird ein zweites Kontaktloch 1200 ausgebildet, das sich von der ersten Oberfläche 1001 bis zur zweiten Oberfläche 1002 der ersten Anordnung von Schichten 1000 erstreckt.

[0079] Das zweite Kontaktloch 1200 grenzt an den zweiten strukturierten leitfähigen Bereich 1030 der ersten Schicht 1010-1 und an den zweiten strukturierten leitfähigen Bereich 1080 der zweiten Schicht 1010-5 an.

[0080] Das erste 1100 und das zweite 1200 Kontaktloch werden dann mit einem leitfähigen Material gefüllt.

[0081] Über das mit dem leitfähigen Material gefüllte erste Kontaktloch 1100 wird eine leitfähige Verbindung zwischen dem ersten strukturierten Bereich 1020 der ersten Schicht 1010-1 und dem ersten strukturierten leitfähigen Bereich 1070 der zweiten Schicht 1010-5 hergestellt.

[0082] Über das mit einem leitfähigen Material gefüllte zweite Kontaktloch 1200 wird eine leitfähige Verbindung zwischen dem zweiten strukturierten Bereich 1030 der ersten Schicht 1010-1 und dem zweiten strukturierten Bereich 1080 der zweiten Schicht 1010-5 hergestellt.

[0083] Gemäß einer Ausführungsform der Erfindung kann eine dritte Schicht 1010-3, die sich zwischen der ersten Schicht 1010-1 und der zweiten Schicht 1010-5 befindet, so strukturiert sein, dass sie einen strukturierten leitfähigen Bereich 1210 aufweist. Ein Abschnitt des strukturierten leitfähigen Bereichs 1210 kann an das mit einem elektrisch leitfähigen Material gefüllte erste Kontaktloch 1100 gekoppelt sein.

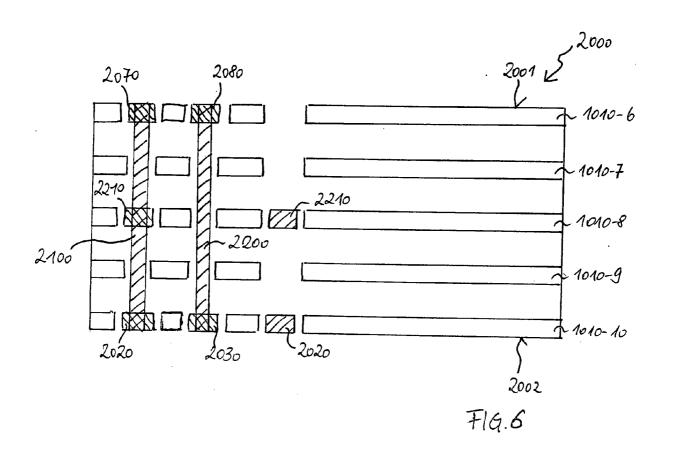

[0084] Unter Bezugnahme auf Fig. 6 wird eine zweite Anordnung von Schichten 2000 vorgesehen. Die zweite Anordnung von Schichten 2000 ist beispielsweise als Mehrlagenleiterplatte ausgebildet und weist eine erste Oberfläche 2001 und eine von der ersten Oberfläche 2001 abgewandte zweite Oberfläche 2002 auf. Zwischen der ersten Oberfläche 2001 und der zweiten Oberfläche 2002 der zweiten Anordnung von Schichten 2000 ist eine Vielzahl von Schichten 1010-6 bis 1010-10 in einer übereinander gestapelten Anordnung zwischen der ersten Oberfläche 2001 und der zweiten Oberfläche 2002 angeordnet. Zwischen benachbarten der Vielzahl von Schichten 1010-6 bis 1010-10 der zweiten Anordnung von Schichten 2000 sind jeweils isolierende Schichten (nicht gezeigt in Fig. 6) vorgesehen.

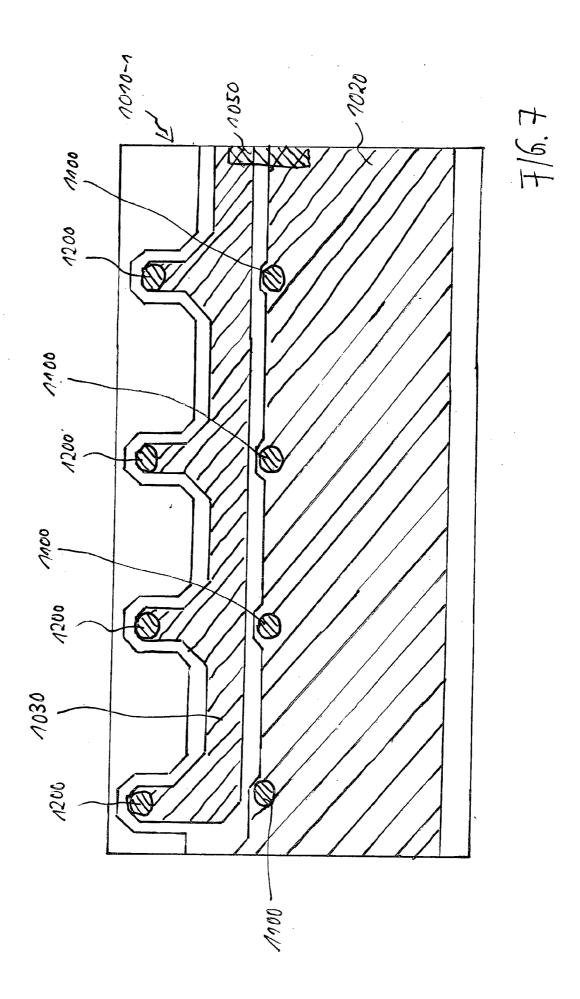

[0085] Fig. 7 zeigt eine Draufsicht auf einen Abschnitt der in Fig. 5 dargestellten ersten Schicht 1010-1 der ersten Anordnung von Schichten 1000. Die erste Schicht 1010-1 weist einen ersten strukturierten leitfähigen Bereich 1020 und einen zweiten strukturierten leitfähigen Bereich 1030 auf. Der erste strukturierte leitfähige Bereich 1020 ist an mehrere mit einem leitfähigen Material gefüllte erste Kontaktlöcher 1100 gekoppelt.

[0086] Der zweite strukturierte Bereich 1030 ist an mehrere mit einem leitfähigen Material gefüllte zweite Kontaktlöcher 1200 gekoppelt. Der erste strukturierte Bereich 1020 und der zweite strukturierte Bereich 1030 sind über eine leitfähige Verbindung 1050 gekoppelt, die bevorzugt einen hohen Widerstand aufweist.

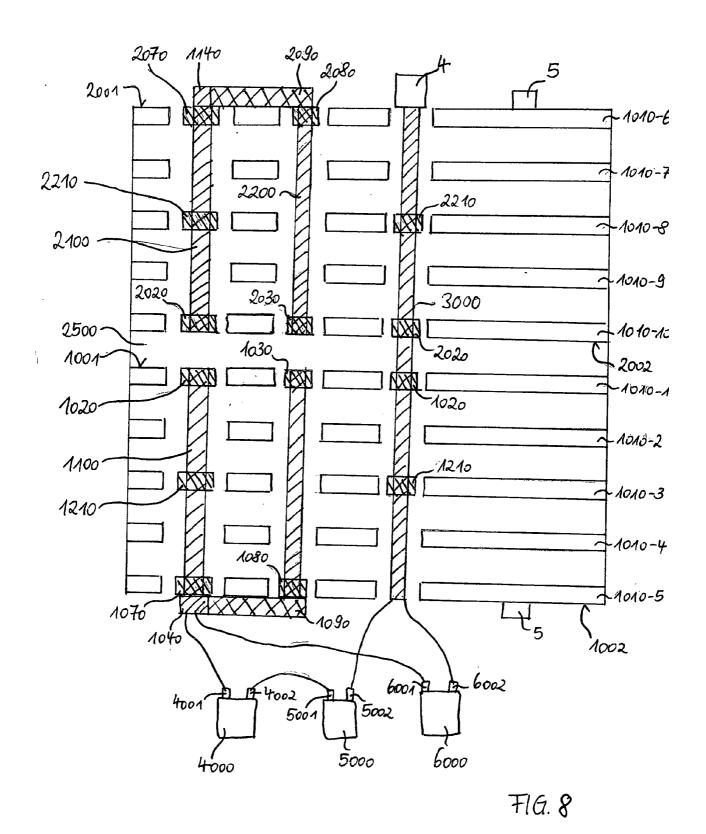

[0087] Mit Bezugnahme auf Fig. 8 werden dann gemäß einer Ausführungsform der Erfindung die zweite Anordnung von Schichten 2000 und die erste Anordnung von Schichten 1000 mittels einer isolierenden Schicht 2500 so verbunden, dass die erste Oberfläche 1001 der ersten Anordnung von Schichten 1000 der zweiten Oberfläche 2002 der zweiten Anordnung von Schichten 2000 zugewandt ist. Die isolierende Schicht 2500 kann auf der zweiten Oberfläche 2002 der zweiten Anordnung von Schichten 2000 oder auf der ersten Oberfläche 1001 der ersten Anordnung von Schichten 1000 ausgebildet werden.

[0088] Dann wird ein Kontaktloch 3000 ausgebildet, das sich von der ersten Oberfläche 2001 der zweiten

Anordnung von Schichten **2000** bis zu der zweiten Oberfläche **1002** der ersten Anordnung von Schichten **1000** erstreckt. Das Kontaktloch **3000** grenzt dabei an den strukturierten ersten leitfähigen Bereich **1020** der ersten Schicht **1010-1** der ersten Anordnung von Schichten **1000** an.

[0089] Im Falle, dass eine dritte Schicht 1010-3 der ersten Anordnung von Schichten 1000 mit einem strukturierten leitfähigen Bereich 1210 vorgesehen ist, wird das Kontaktloch 3000 so ausgebildet, dass es an den strukturierten Bereich 1210 angrenzt.

[0090] Das Kontaktloch 3000 wird dann mit einem elektrisch leitfähigen Material gefüllt.

[0091] Auf der zweiten Oberfläche 1002 der ersten Anordnung von Schichten 1000 wird dann ein Kontaktanschluss 1040 ausgebildet, der an den ersten strukturierten leitfähigen Bereich 1070 der zweiten Schicht 1010-5 gekoppelt wird.

[0092] Das leitfähige Material des Kontaktlochs 3000 ist über einen leitfähigen Pfad, der den ersten strukturierten leitfähigen Bereich 1020 der ersten Schicht 1010-1 der ersten Anordnung von Schichten 1000, das leitfähige Material des ersten Kontaktlochs 1100 der ersten Anordnung von Schichten 1000 und den ersten strukturierten leitfähigen Bereich 1070 der zweiten Schicht 1010-5 der ersten Anordnung von Schichten 1000 umfasst, an den Kontaktanschluss 1040 gekoppelt.

[0093] Im Falle, dass eine dritte Schicht 1010-3 der ersten Anordnung von Schichten 1000 mit einem strukturierten leitfähigen Bereich 1210 vorgesehen ist, ist das leitfähige Material des Kontaktlochs 3000 ferner über einen weiteren leitfähigen Pfad, der den strukturierten leitfähigen Bereich 1210, das leitfähige Material des ersten Kontaktlochs 1100 und den ersten strukturierten leitfähigen Bereich 1070 der zweiten Schicht 1010-5 der ersten Anordnung von Schichten umfasst, an den Kontaktanschluss 1040 gekoppelt.

[0094] Dann wird eine Impedanz zwischen dem leitfähigen Material des Kontaktlochs 3000 und dem Kontaktanschluss 1040 gemessen, die durch eine Impedanz des leitfähigen Pfads und gegebenenfalls des weiteren leitfähigen Pfads bestimmt ist.

[0095] Zur Messung der Impedanz wird ein Ausgang 4001 einer Spannungsquelle 4000 an den Kontaktanschluss 1040 gekoppelt, das leitfähige Material des Kontaktlochs 3000 an einen Eingang 5002 eines Strommessgeräts 5000 gekoppelt und ein Ausgang 5001 des Strommessgeräts 5000 an einen Eingang 4002 der Spannungsquelle 4000 gekoppelt.

[0096] Ferner wird ein Ausgang 6001 eines Span-

nungsmessgeräts **6000** an den Kontaktanschluss **1040** gekoppelt und ein Eingang **6002** des Spannungsmessgeräts **6000** wird an das leitfähige Material des Kontaktlochs **3000** gekoppelt.

[0097] Dann wird mittels der Spannungsquelle 4000 eine Spannung zwischen dem Kontaktanschluss 1040 und dem leitfähigen Material des Kontaktlochs 3000 angelegt. Ein durch das Strommessgerät 5000 fließender Strom und eine zwischen dem Eingang 6001 und dem Ausgang 6002 des Spannungsmessgeräts 6000 anliegende Spannung wird gemessen.

**[0098]** Aus der gemessenen Spannung und dem gemessenen Strom wird dann durch eine Division des Werts der Spannung durch den Wert des Stroms die Impedanz bestimmt.

[0099] Der bestimmte Wert der Impedanz wird nun mit einem vorgegebenen Wert verglichen. Ist der bestimmte Wert der Impedanz höher als der vorgegebene Wert, so wird eine leitfähige Verbindung 1090 zwischen dem ersten strukturierten leitfähigen Bereich 1070 und dem zweiten strukturierten leitfähigen Bereich 1080 der zweiten Schicht 1010-5 der ersten Anordnung von Schichten 1000 ausgebildet. Da nun auch der zweite strukturierte leitfähige Bereich 1030 der ersten Schicht 1010-1 der ersten Anordnung von Schichten 1000 zwischen das leitfähige Material des Kontaktlochs 3000 und den Kontaktanschluss 1040 gekoppelt ist, wird die Impedanz zwischen dem leitfähigen Material des Kontaktlochs 3000 und dem Kontaktanschluss 1040 verringert.

[0100] Schließlich wird ein erstes Halbleiterbauelement 4 auf der ersten Oberfläche 2001 der zweiten Anordnung von Schichten 2000 angeordnet und an das leitfähige Material des Kontaktlochs 3000 gekoppelt.

[0101] Des Weiteren wird mindestens ein zweites Halbleiterbauelement 5 auf der ersten Oberfläche 2001 der zweiten Anordnung von Schichten 2000 und/oder der zweiten Oberfläche 1002 der ersten Anordnung von Schichten 1000 angeordnet.

**[0102]** Bevorzugt umfasst das erste Halbleiterbauelement **4** einen Hubchip. Das zweite Halbleiterbauelement **5** kann beispielsweise einen Speicherchip mit dynamischen Speicherzellen mit wahlfreiem Zugriff (DRAM) oder einen Speicherchip mit synchronen dynamischen Speicherzellen mit wahlfreiem Zugriff (SDRAM) umfassen.

[0103] Gemäß einer weiteren Ausführungsform der Erfindung kann vor der Verbindung der ersten Anordnung von Schichten 1000 mit der zweiten Anordnung von Schichten 2000 mit Bezug auf Fig. 6 eine erste Schicht 1010-6 der zweiten Anordnung von Schichten 2000 strukturiert werden, wobei die erste Schicht

**1010-6** benachbart zu der ersten Oberfläche **2001** der zweiten Anordnung von Schichten **2000** angeordnet ist.

[0104] In Folge des Strukturierens der ersten leitenden Schicht 1010-6 wird ein erster strukturierter leitfähiger Bereich 2070 und ein zweiter strukturierter leitfähiger Bereich 2080 der ersten Schicht 1010-6 der zweiten Anordnung von Schichten 2000 ausgebildet.

[0105] Dann wird eine zweite Schicht 1010-10, die benachbart zu der zweiten Oberfläche 2002 der zweiten Anordnung von Schichten 2000 angeordnet ist, strukturiert. Durch das Strukturieren der zweiten leitfähigen Schicht 1010-10 wird ein erster strukturierter leitfähiger Bereich 2020, ein zweiter strukturierter leitfähiger Bereich 2030 und eine einen hohen Widerstand aufweisende leitfähige Verbindung (nicht gezeigt in Fig. 6) zwischen dem ersten strukturierten leitfähigen Bereich 2020 und dem zweiten strukturierten leitfähigen Bereich 2030 der zweiten Schicht 1010-10 der zweiten Anordnung von Schichten 2000 ausgebildet.

[0106] Dann werden ein erstes Kontaktloch 2100, das sich von der ersten Oberfläche 2001 bis zur zweiten Oberfläche 2002 der zweiten Anordnung von Schichten 2000 erstreckt, und ein zweites Kontaktloch 2200 das sich von der ersten Oberfläche 2001 bis zur zweiten Oberfläche 2002 der zweiten Anordnung von Schichten 2000 erstreckt, ausgebildet. Das erste Kontaktloch 2100 grenzt an den ersten strukturierten leitfähigen Bereich 2070 der ersten Schicht 1010-6 und an den ersten strukturierten leitfähigen Bereich 2020 grenzt an den zweiten strukturierten leitfähigen Bereich 2080 der ersten Schicht 1010-6 und an den zweiten strukturierten leitfähigen Bereich 2030 der zweiten strukturierten leitfähigen Bereich 2030 der zweiten Schicht 1010-10 an.

**[0107]** Dann werden das erste Kontaktloch **2100** und das zweite Kontaktloch **2200** der zweiten Anordnung von Schichten **2000** mit einem leitfähigen Material gefüllt.

[0108] Über das mit einem leitfähigen Material gefüllte erste Kontaktloch 2100 wird eine leitfähige Verbindung zwischen dem ersten strukturierten leitfähigen Bereich 2070 der ersten Schicht 1010-5 und dem ersten strukturierten leitfähigen Bereich 2020 der zweiten Schicht 1010-10 bereitgestellt.

[0109] Über das mit einem leitfähigen Material gefüllte zweite Kontaktloch 2200 wird eine leitfähige Verbindung zwischen dem zweiten strukturierten leitfähigen Bereich 2080 der ersten Schicht 1010-6 und dem zweiten strukturierten leitfähigen Bereich 2030 der zweiten Schicht 1010-10 bereitgestellt.

[0110] Gemäß einer Ausführungsform der Erfindung kann eine dritte Schicht 1010-8 der zweiten Anordnung von Schichten 2000, die sich zwischen der ersten Schicht 1010-6 und der zweiten Schicht 1010-10 befindet, so strukturiert sein, dass sie einen strukturierten leitfähigen Bereich 2210 aufweist. Ein Abschnitt des strukturierten leitfähigen Bereichs 2210 kann an das mit einem elektrisch leitfähigen Material gefüllte erste Kontaktloch 2100 gekoppelt sein.

[0111] Die mit Bezug auf Fig. 8 beschriebene Ausbildung des Kontaktlochs 3000 erfolgt dann so, dass das Kontaktloch 3000 an den ersten strukturierten leitfähigen Bereich 2020 der zweiten Schicht 1010-10 der zweiten Anordnung von Schichten 2000 und gegebenenfalls an den strukturierten leitfähigen Bereich 2210 der dritten Schicht 1010-8 der zweiten Anordnung von Schichten 2000 angrenzt.

[0112] Auf der ersten Oberfläche 2001 der zweiten Anordnung von Schichten 2000 wird dann ein weiterer Kontaktanschluss 1140 ausgebildet, der an den ersten strukturierten leitfähigen Bereich 2070 der ersten Schicht 1010-6 der zweiten Anordnung von Schichten 2000 gekoppelt ist.

[0113] Durch die Füllung des Kontaktlochs 3000 mit einem leitfähigen Material wird ein leitfähiger Pfad ausgebildet, der das leitfähige Material des Kontaktlochs 3000 an den weiteren Kontaktanschluss 1140 koppelt. Der leitfähige Pfad umfasst den ersten strukturierten leitfähigen Bereich 2020 der zweiten Schicht 1010-10 der zweiten Anordnung von Schichten 2000, das leitfähige Material des ersten Kontaktlochs 2100 der zweiten Anordnung von Schichten 2000 und den ersten strukturierten leitfähigen Bereich 2070 der ersten Schicht 1010-6 der zweiten Anordnung von Schichten 2000.

[0114] Im Falle, dass eine dritte Schicht 1010-8 der zweiten Anordnung von Schichten 2000 mit einem strukturierten leitfähigen Bereich 2210 vorgesehen ist, ist das leitfähige Material des Kontaktlochs 3000 ferner über einen weiteren leitfähigen Pfad, der den strukturierten leitfähigen Bereich 2210, das leitfähige Material des ersten Kontaktlochs 2100 und den ersten strukturierten leitfähigen Bereich 2070 der ersten Schicht 1010-6 der zweiten Anordnung von Schichten 2000 umfasst, an den weiteren Kontaktanschluss 140 gekoppelt.

**[0115]** Dann wird entsprechend obiger Ausführungen eine Impedanz zwischen dem leitfähigen Material des Kontaktlochs **3000** und dem weiteren Kontaktanschluss **1140** bestimmt.

**[0116]** Wenn der bestimmte Wert der Impedanz höher als ein vorgegebener Wert ist, so wird eine leitfähige Verbindung **2090** zwischen dem ersten struktu-

rierten leitfähigen Bereich 2070 und dem zweiten strukturierten leitfähigen Bereich 2080 der ersten Schicht 1010-6 der zweiten Anordnung von Schichten 2000 ausgebildet. Da nun auch der zweite strukturierte leitfähige Bereich 2030 der zweiten Schicht 1010-10 zwischen dem leitfähigen Material des Kontaktlochs 3000 und dem weiteren Kontaktanschluss 1140 gekoppelt ist, wird die Impedanz zwischen dem leitfähigen Material des Kontaktlochs 3000 und dem weiteren Kontaktanschluss 1140 verringert.

[0117] Fig. 9 zeigt eine Draufsicht auf einen Abschnitt der in Fig. 6 dargestellten zweiten Schicht 1010-10 der zweiten Anordnung von Schichten 2000. Die zweite Schicht 1010-10 weist einen ersten strukturierten leitfähigen Bereich 2020 und einen zweiten strukturierten leitfähigen Bereich 2030 auf. Der erste strukturierte leitfähige Bereich 2020 ist an mehrere mit einem leitfähigen Material gefüllte erste Kontaktlöcher 2100 gekoppelt.

[0118] Der zweite strukturierte Bereich 2030 ist an mehrere mit einem leitfähigen Material gefüllte zweite Kontaktlöcher 2200 gekoppelt. Der erste strukturierte Bereich 2020 und der zweite strukturierte Bereich 2030 sind über eine leitfähige Verbindung 2050 gekoppelt, die bevorzugt einen hohen Widerstand aufweist.

[0119] Fig. 10 zeigt ein Datenverarbeitungsgerät 7000 gemäß einer Ausführungsform der Erfindung. Das Datenverarbeitungsgerät 7000 umfasst eine Leiterplatte 7001, beispielsweise ein Motherboard, das mehrere Buchsen 7002 zur Aufnahme jeweils einer erfindungsgemäßen Schaltungsanordnung 1 aufweist. In den Buchsen 7002 befinden sich erfindungsgemäße Schaltungsanordnungen 1 mit jeweils einem ersten Halbleiterbauelement 4 und jeweils mindestens einem zweiten Halbleiterbauelement 5. Jede der Schaltungsanordnungen 1 weist ferner einen Randstecker 7003 auf, der den Kontaktanschluss 40 und den weiteren Kontaktanschluss 140 umfasst.

[0120] Auf der Leiterplatte 7001 ist ferner eine Steuereinheit 7004 angeordnet, die über in der Leiterplatte 7001 angeordnete Leiterbahnen (nicht gezeigt in Fig. 10) und die jeweiligen Randstecker 7003 an die jeweiligen Schaltungsanordnungen 1 gekoppelt ist.

[0121] Über einen auf der Leiterplatte 7001 angeordneten Spannungsregulierer 7005, in der Leiterplatte angeordnete Leiterbahnen (nicht gezeigt in Fig. 10) und jeweiligen Kontaktanschlüssen 40 und jeweiligen weiteren Kontaktanschlüssen 140 (nicht gezeigt in Fig. 10) wird den ersten Halbleiterbauelemente 4 jeder der Schaltungsanordnungen 1 eine Versorgungsspannung zugeführt.

#### Patentansprüche

- 1. Schaltungsanordnung (1), umfassend eine Anordnung von Schichten (6), wobei die Anordnung von Schichten (6) eine erste Oberfläche (2) und eine zweite Oberfläche (3) sowie eine Vielzahl von Schichten (10-1 bis 10-10), die in einer übereinander gestapelten Anordnung zwischen der ersten Oberfläche (2) und der zweiten Oberfläche (3) angeordnet sind, aufweist, mindestens eine erste Durchkontaktierung (100), mindestens eine zweite Durchkontaktierung (200), mindestens ein erstes Halbleiterbauelement (4) und mindestens ein zweites Halbleiterbauelement (5); wobei

- eine erste (10-6) der Vielzahl von Schichten (10-1 bis 10-10) einen ersten leitfähigen Bereich (20) und einen zweiten leitfähigen Bereich (30) aufweist, die über eine einen hohen elektrischen Widerstand aufweisende leitfähige Verbindung (150) gekoppelt sind;

eine zweite (10-10) der Vielzahl von Schichten (10-1 bis 10-10) mindestens einen ersten leitfähigen Bereich (70), der an die erste Durchkontaktierung (100) gekoppelt ist und einen zweiten leitfähigen Bereich (80), der an die zweite Durchkontaktierung (200) gekoppelt ist, aufweist;

- der erste leitfähige Bereich (20) der ersten (10-6) der Vielzahl von Schichten (10-1 bis 10-10) an die erste Durchkontaktierung (100) gekoppelt ist und der zweite leitfähige Bereich (30) der ersten (10-6) der Vielzahl von Schichten (10-1 bis 10-10) an die zweite Durchkontaktierung (200) gekoppelt ist;

- das erste Halbleiterbauelement (4) auf der ersten Oberfläche (2) angeordnet ist und an den ersten leitfähigen Bereich (20) der ersten (10-6) der Vielzahl von Schichten (10-1 bis 10-10) über die dritte Durchkontaktierung (300) gekoppelt ist;

- die erste Durchkontaktierung (100) und die zweite

Durchkontaktierung (200) sich jeweils von der zweiten Oberfläche (3) bis zu einer der zweiten Schicht (10-10) abgewandten Oberfläche der ersten Schicht (10-6) erstrecken;

- ein Kontaktanschluss (40) zur Kopplung an eine Spannungsversorgung an der zweiten Oberfläche (3) angeordnet ist und der Kontaktanschluss (40) an den ersten leitfähigen Bereich (70) der zweiten Schicht (10-10) gekoppelt ist.

- 2. Schaltungsanordnung (1) nach Anspruch 1, bei der der erste leitfähige Bereich (70) und der zweite leitfähige Bereich (80) der zweiten (10-10) der Vielzahl von Schichten über (10-1 bis 10-10) eine leitfähige Verbindung (90) gekoppelt sind.

- 3. Schaltungsanordnung (1) nach Anspruch 2, bei der eine dritte (10-8) der Vielzahl von Schichten (10-1 bis 10-10) einen leitfähigen Bereich (110) aufweist, der an die erste Durchkontaktierung (100) und an die dritte Durchkontaktierung (300) gekoppelt ist.

- 4. Schaltungsanordnung (1) nach einem der Ansprüche 1 bis 3, des Weiteren umfassend eine vierte Durchkontaktierung (400) und eine fünfte Durchkontaktierung (500), wobei

- eine vierte (10-5) der Vielzahl von Schichten (10-1 bis 10-10) einen ersten leitfähigen Bereich (120) und einen zweiten leitfähigen Bereich (130) aufweist, die über eine einen hohen elektrischen Widerstand aufweisende leitfähige Verbindung (250) gekoppelt sind;

eine fünfte (10-1) der Vielzahl von Schichten (10-1 bis 10-10) mindestens einen ersten leitfähigen Bereich (170), der an die vierte Durchkontaktierung (400) gekoppelt ist und mindestens einen zweiten leitfähigen Bereich (180), der an die fünfte Durchkontaktierung (500) gekoppelt ist, aufweist;

- der erste leitfähige Bereich (120) der vierten (10-5) der Vielzahl von Schichten (10-1 bis 10-10) an die vierte Durchkontaktierung (400) gekoppelt ist und der zweite leitfähige Bereich (130) der vierten (10-5) der Vielzahl von Schichten (10-1 bis 10-10) an die fünfte Durchkontaktierung (500) gekoppelt ist;

- der erste leitfähigen Bereich (120) der vierten (10-5)

der Vielzahl von Schichten (10-1 bis 10-10) an die dritte Durchkontaktierung (300) gekoppelt ist;

- die vierte Durchkontaktierung (400) und die fünfte Durchkontaktierung (500) sich jeweils von der ersten Oberfläche (2) bis zu einer der vierten Schicht (10-5) abgewandten Oberfläche der fünften Schicht (10-5) erstrecken;

- ein weiterer Kontaktanschluss (140) zur Kopplung an eine Spannungsversorgung an der ersten Oberfläche (2) angeordnet ist und der weitere Kontaktanschluss (140) an den ersten leitfähigen Bereich (170) der vierten Schicht (10-1) gekoppelt ist.

- 5. Schaltungsanordnung (1) nach Anspruch 4, bei der der erste leitfähige Bereich (170) und der zweite leitfähige Bereich (180) der vierten (10-1) der Vielzahl von Schichten (10-1 bis 10-10) über eine leitfähige Verbindung (190) gekoppelt sind.

- 6. Schaltungsanordnung (1) nach Anspruch 4 oder 5, bei der eine sechste (10-3) der Vielzahl von Schichten (10-1 bis 10-10) einen leitfähigen Bereich (210) aufweist, der an die vierte Durchkontaktierung (400) und an die dritte Durchkontaktierung (300) gekoppelt ist.

- 7. Schaltungsanordnung (1) nach einem der Ansprüche 1 bis 6, bei der das mindestens eine zweite Halbleiterbauelement (5) einen Speicherchip mit dynamischen Speicherzellen mit wahlfreiem Zugriff umfasst.

- 8. Schaltungsanordnung (1) nach Anspruch 7, bei der das erste Halbleiterbauelement (4) ein Durchführen von Lese- und Schreibzugriffen auf das mindestens eine zweite Halbleiterbauelement (5) steuert.

- 9. Schaltungsanordnung nach Anspruch 8, bei der das erste Halbleiterbauelement (4) einen Hubchip umfasst.

- 10. Verfahren zum Ausbilden einer Schaltungsanordnung (1), umfassend:

- Strukturieren einer ersten Schicht (1010-1) einer ersten Anordnung von Schichten (1000), wobei die erste Anordnung von Schichten (1000) eine erste Oberfläche (1001) und eine zweite Oberfläche (1002) und eine Vielzahl von Schichten (1010-1 bis 1010-5), die in einer übereinander gestapelten Anordnung zwischen der ersten Oberfläche (1001) und der zweiten Oberfläche (1002) angeordnet sind, aufweist, wobei die erste Schicht (1010-1) benachbart zu der ersten Oberfläche (1001) angeordnet ist, und dabei Ausbilden eines ersten leitfähigen Bereichs (1020), eines zweiten leitfähigen Bereichs (1030) und einer einen hohen Widerstand aufweisenden leitfähigen Verbindung (1050) zwischen dem ersten leitfähigen Bereich (1020) und dem zweiten leitfähigen Bereich (1030) der ersten Schicht (1010-1);

- Strukturieren einer der zweiten Oberfläche (1002) benachbarten zweiten Schicht (1010-5) der ersten Anordnung von Schichten (1000) und dadurch Ausbilden eines ersten leitfähigen Bereichs (1070) und eines zweiten leitfähigen Bereichs (1080) der zweiten Schicht (1010-5);

- Ausbilden eines ersten Kontaktlochs (1100), das sich von dem ersten leitfähigen Bereich (1020) der ersten Schicht (1010-1) bis zu dem ersten leitfähigen Bereich (1070) der zweiten Schicht (1010-5) erstreckt;

- Ausbilden eines zweiten Kontaktlochs (1200), das sich von dem zweiten leitfähigen Bereich (1030) der ersten Schicht (1010-1) bis zu dem zweiten leitfähigen Bereich (1080) der zweiten Schicht (1010-5) erstreckt;

- Füllen des ersten (1100) und des zweiten (1200)

Kontaktlochs mit einem leitfähigen Material;

- Verbinden der ersten Anordnung von Schichten (1000) mit einer zweiten Anordnung von Schichten (2000), wobei die zweite Anordnung von Schichten (2000) eine erste Oberfläche (2001) und eine zweite Oberfläche (2002) aufweist und dabei Ausbilden einer isolierenden Schicht (2500) auf der ersten Oberfläche (1001) der ersten Anordnung von Schichten (1000) oder auf der zweiten Oberfläche (2002) der zweiten Anordnung von Schichten (2000);

- Ausbilden eines Kontaktlochs (3000) das sich von der ersten Oberfläche (2001) der zweiten Anordnung von Schichten (2000) bis zur zweiten Oberfläche (1002) der ersten Anordnung von Schichten (1000) erstreckt und an den ersten leitfähigen Bereich (1070) der zweiten Schicht (1010-5) der ersten Anordnung von Schichten (1000) angrenzt;

- Füllen des Kontaktlochs (3000) mit einem leitfähigen Material;

- Ausbilden eines Kontaktanschlusses (1040) an der zweiten Oberfläche (1002) der ersten Anordnung von

Schichten (1000) und Koppeln des Kontaktanschlusses (1040) an den ersten leitfähigen Bereich (1070) der zweiten Schicht (1010-5) der ersten Anordnung von Schichten (1000).

- 11. Verfahren nach Anspruch 10, bei dem eine dritte Schicht (1010-3) der ersten Anordnung von Schichten (1000) einen leitfähigen Bereich (1210) umfasst, der an das Kontaktloch (3000) angrenzt.

- 12. Verfahren nach Anspruch 10 oder 11, des Weiteren umfassend ein Koppeln eines Ausgangs (4001) einer Spannungsquelle (4000) an den Kontaktanschluss (1040), ein Koppeln des leitfähigen Materials des Kontaktlochs (3000) an einen Eingang (5002) eines Strommessgeräts (5000), ein Koppeln eines Ausgangs (5001) des Strommessgeräts (5000) an einen Eingang (4002) der Spannungsquelle (4000), ein Koppeln eines Ausgangs (6001) eines Spannungsmessgeräts (6000) an den Kontaktanschluss (1040), ein Koppeln eines Eingangs (6002) des Spannungsmessgeräts (6000) an das leitfähige Material des Kontaktlochs (3000), Anlegen eine Spannung mittels der Spannungsquelle (4000), ein Messen eines durch das Strommessgerät (5000) fließenden Stroms und Messen einer zwischen dem Eingang (6001) und dem Ausgang (6002) des Spannungsmessgeräts anliegenden Spannung.

- 13. Verfahren nach Anspruch 11 oder 12, des Weiteren umfassend:

- Bestimmen eines Werts einer Impedanz mittels Division eines Werts der gemessenen Spannung durch einen Wert des gemessenen Stroms;

- Vergleichen des bestimmten Werts der Impedanz mit einem vorgegebenen Wert;

- Ausbilden einer leitfähigen Verbindung (1090) zwischen dem ersten leitfähigen Bereich (1070) und dem zweiten leitfähigen Bereich (1080) der zweiten Schicht 1010-5 der ersten Anordnung von Schichten (1000), falls der bestimmte Wert der Impedanz höher ist als der vorgegebene Wert.

- 14. Verfahren nach einem der Ansprüche 10 bis 13, bei dem die zweite Anordnung von Schichten (2000) eine Vielzahl von Schichten (1010-6 bis 1010-10), die in einer übereinander gestapelten Anordnung zwischen der ersten Oberfläche (2001) und der zweiten Oberfläche (2002) der zweiten Anordnung von Schichten (2000) angeordnet sind, aufweist, des Weiteren umfassend:

- Strukturieren einer ersten Schicht (1010-6) der zweiten Anordnung von Schichten (2000), wobei die erste Schicht (1010-6) benachbart zu der ersten Oberfläche (2001) der zweiten Anordnung von Schichten (2000) angeordnet ist und dabei Ausbilden eines ersten leitfähigen Bereichs (2070) und eines zweiten leitfähigen Bereichs (2080) der ersten Schicht (1010-6);

- Strukturieren einer zweiten Schicht (1010-10) der

- zweiten Anordnung von Schichten (2000), wobei die zweite Schicht (1010-10) benachbart zu der zweiten Oberfläche (2002) der zweiten Anordnung von Schichten (2000) angeordnet ist, und dabei Ausbilden eines ersten leitfähigen Bereichs (2020), eines zweiten leitfähigen Bereichs (2030) und einer einen hohen Widerstand aufweisenden leitfähigen Verbindung (2050) zwischen dem ersten leitfähigen Bereich (2020) und dem zweiten leitfähigen Bereich (2030) der zweiten Schicht (1010-10) der zweiten Anordnung von Schichten (2000);

- Ausbilden eines ersten Kontaktlochs (2100), das sich von dem ersten leitfähigen Bereich (2070) der ersten Schicht (2010-1) der zweiten Anordnung von Schichten (2000) bis zu dem ersten leitfähigen Bereich (2020) der zweiten Schicht (1010-10) der zweiten Anordnung von Schichten (2000) erstreckt;

- Ausbilden eines zweiten Kontaktlochs (2200), das sich von dem zweiten leitfähigen Bereich (2080) der ersten Schicht (1010-6) der zweiten Anordnung von Schichten (2000) bis zu dem zweiten leitfähigen Bereich (2030) der zweiten Schicht (1010-10) der zweiten Anordnung von Schichten (2000) erstreckt;

- Füllen des ersten (2100) und des zweiten (2200)

Kontaktlochs der zweiten Anordnung von Schichten (2000) mit einem leitfähigen Material;

- Ausbilden eines weiteren Kontaktanschlusses (1140) an der ersten Oberfläche (2001) der zweiten Anordnung von Schichten (2000) und Koppeln des weiteren Kontaktanschlusses (1140) an den ersten leitfähigen Bereich (2070) der ersten Schicht (1010-6) der zweiten Anordnung von Schichten (2000).

- 15. Verfahren nach Anspruch 14, bei dem das Kontaktloch (3000) an den ersten leitfähigen Bereich (2020) der zweiten Schicht (1010-10) der zweiten Anordnung von Schichten (2000) angrenzt.

- 16. Verfahren nach Anspruch 15, bei dem eine dritte Schicht (1010-8) der zweiten Anordnung von Schichten (2000) einen leitfähigen Bereich (2210) umfasst, der an das Kontaktloch (3000) angrenzt.

- 17. Verfahren nach Anspruch 14 oder 15, des Weiteren umfassend ein Koppeln eines Ausgangs (4001) einer Spannungsquelle (4000) an den weiteren Kontaktanschluss (1140), ein Koppeln des leitfähigen Materials des Kontaktlochs (3000) an einen Eingang (5002) eines Strommessgeräts (5000), ein Koppeln eines Ausgangs (5001) des Strommessgeräts (5000) an einen Eingang (4002) der Spannungsquelle (4000), ein Koppeln eines Ausgangs (6001) eines Spannungsmessgeräts (6000) an den weiteren Kontaktanschluss (1140), ein Koppeln eines Eingangs (6002) des Spannungsmessgeräts (6000) an das leitfähige Material des Kontaktlochs (3000), Anlegen eine Spannung mittels der Spannungsquelle (4000), ein Messen eines durch das Strommessgerät (5000) fließenden Stroms und Messen einer zwi-

### DE 10 2006 018 874 A1 2007.10.25

schen dem Eingang (6001) und dem Ausgang (6002) des Spannungsmessgeräts anliegenden Spannung.

schluss (40) an den Spannungsregulierer gekoppelt ist.

- 18. Verfahren nach Anspruch 17, des Weiteren umfassend:

- Bestimmen eines Werts einer Impedanz mittels Division eines Werts der gemessenen Spannung durch einen Wert des gemessenen Stroms;

- Vergleichen des bestimmten Werts der Impedanz mit einem vorgegebenen Wert;

- Ausbilden einer leitfähigen Verbindung (2090) zwischen dem ersten leitfähigen Bereich (2070) und dem zweiten leitfähigen Bereich (2080) der ersten Schicht 1010-6 der zweiten Anordnung von Schichten (2000), falls der bestimmte Wert der Impedanz höher ist als der vorgegebene Wert.

- 19. Verfahren nach einem der Ansprüche 10 bis 18, des Weiteren umfassend:

- Anordnen eines ersten Halbleiterbauelements (4) an der ersten Oberfläche (2001) der zweiten Anordnung von Schichten (2000) und Koppeln des ersten Halbleiterbauelements (4) an das leitfähige Material des Kontaktlochs (3000).

- 20. Verfahren nach einem der Ansprüche 10 bis 19, des Weiteren umfassend:

- Anordnen mindestens eines zweiten Halbleiterbauelements (5) an der ersten Oberfläche (2001) der zweiten Anordnung von Schichten (2000) oder an der zweiten Oberfläche (1002) der ersten Anordnung von Schichten (1000).

- 21. Verfahren nach Anspruch 19 oder 20, bei dem das erste Halbleiterbauelement (4) einen Speicherchip mit dynamischen Speicherzellen mit wahlfreiem Zugriff umfasst.

- 22. Verfahren nach einem der Ansprüche 19 bis 21, bei dem das erste Halbleiterbauelement (4) einen HUB-Chip umfasst.

- 23. Datenverarbeitungsgerät (**7000**) umfassend:

- eine Leiterplatte (7001) mit mehreren Buchsen (7002);

- eine auf der Leiterplatte angeordnete Steuereinheit (7004);

- mindestens eine Schaltungsanordnung (1) gemäß einem der Ansprüche 1 bis 10; wobei die mindestens eine Schaltungsanordnung (1) einen Randstecker (7003) aufweist und mittels des Randsteckers (7003) an die Steuereinheit (7004) gekoppelt ist.

- 24. Datenverarbeitungsgerät (**7000**) nach Anspruch 23, des Weiteren umfassend:

- einen auf der Leiterplatte (7001) angeordneten Spannungsregulierer (7005), wobei der Randstecker (7003) den Kontaktanschluss (40) umfasst und das erste Halbleiterbauelement (4) der mindestens einen Schaltungsanordnung (1) über den Kontaktan-

Es folgen 9 Blatt Zeichnungen

## Anhängende Zeichnungen

20/22