(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6533757号

(P6533757)

(45) 発行日 令和1年6月19日(2019.6.19)

(24) 登録日 令和1年5月31日(2019.5.31)

(51) Int.Cl.

F 1

H01L 23/15 (2006.01)

H01L 23/14

C

H01L 23/32 (2006.01)

H01L 23/32

D

G06F 21/75 (2013.01)

G06F 21/75

請求項の数 5 (全 17 頁)

(21) 出願番号 特願2016-76215 (P2016-76215)

(22) 出願日 平成28年4月5日 (2016.4.5)

(65) 公開番号 特開2016-208017 (P2016-208017A)

(43) 公開日 平成28年12月8日 (2016.12.8)

審査請求日 平成31年4月3日 (2019.4.3)

(31) 優先権主張番号 14/694,132

(32) 優先日 平成27年4月23日 (2015.4.23)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 504407000

パロ アルト リサーチ センター イン

コーポレイテッド

アメリカ合衆国 カリフォルニア州 94

304 パロ アルト カイオーテ ヒル

ロード 3333

(74) 代理人 100086771

弁理士 西島 孝喜

(74) 代理人 100088694

弁理士 弟子丸 健

(74) 代理人 100094569

弁理士 田中 伸一郎

(74) 代理人 100067013

弁理士 大塚 文昭

最終頁に続く

(54) 【発明の名称】イオン交換ガラス処理されたインターポーラを伴う過渡的な電子デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

電子回路が形成されている半導体基板、および、第1のパターンで前記半導体基板の表面上に配置されるIC接触パッド、を含む集積回路(IC)ダイであって、前記IC接触パッドは前記電子回路と動作可能に結合される、集積回路ダイと、

パッケージ基板、第2のパターンで第1の表面上に配置される複数の第1のパッケージ接触構造、第2の表面上に配置される複数の第2のパッケージ接触構造、および、前記第1および第2の表面の間にパッケージ構造を介して延びる複数のパッケージ導体であって、それにより、前記パッケージ導体の各々は関連する第1のパッケージ接触構造および関連する第2のパッケージ接触構造の間に電気経路を形成する、複数のパッケージ導体、を含むパッケージ構造と、

前記第1のパターンで第1の表面上に配置される複数の第1の接触点、第2の表面上に配置される複数の第2の接触点、および、複数のインターポーラ導体、を含むガラス基板を備えるインターポーラをあって、前記インターポーラ導体の各々は関連する第1の接触点および関連する第2の接触点の間に電気経路を形成するよう構成される、インターポーラと、

前記インターポーラと付着され、トリガ信号に応答して前記ガラス基板上に初期の破碎強度を生成および印加するよう構成される、トリガデバイスと、

を備える過渡的な電子デバイスであって、

前記インターポーラは前記パッケージ基板に固定され、それにより、前記第2の表面上

10

20

に配置される前記第2の接触点の各々は、対応する第1のパッケージ接触構造と電気的に接続され、

前記ガラス基板は相当量のイオンを含有し、それにより、第2の破碎が前記初期の破碎強度に応答して前記ガラス基板に生成されて前記ガラス基板全体に伝搬し、したがって、前記ガラス基板が粉末化され、および、

前記ICダイは前記ガラス基板に固定的に付着され、それにより、前記第2の破碎が前記ICダイ内に、前記ICダイを粉末化するのに十分なエネルギーで伝搬する、

過渡的な電子デバイス。

#### 【請求項2】

前記ガラス基板は100μm～300μmの範囲の厚さを備える、請求項1に記載の過渡的な電子デバイス。 10

#### 【請求項3】

前記ガラス基板はケイ酸塩ガラスを備える、請求項2に記載の過渡的な電子デバイス。

#### 【請求項4】

前記ガラス基板は、前記第1の表面および前記第2の表面の間に延びる複数のガラス貫通ビアを規定する、請求項2に記載の過渡的な電子デバイス。

#### 【請求項5】

前記トリガデバイスは、前記初期の破碎強度の放出を外部から供給されるトリガ信号に応答して制御するよう構成される作動メカニズムを備える、請求項1に記載の過渡的な電子デバイス。 20

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は過渡的な電子機器に関し、より具体的には、過渡的な電子組立において利用されるインターポーヴに関する。

#### 【背景技術】

#### 【0002】

広域の感知は、様々な軍事的、生態学的、および、商業的な利益にとって重要であり、歴史的に、中央長距離センサの使用を介して機能してきた。しかしながら、電子システムの小型化が急速に進んだことにより、小型センサデバイスの性能が大幅に向上している。これらのマイクロセンサは、運用の適応性、近接近でのみ可能な従来と異なる検知手順、向上した感度およびネットワーク化された知能を介する知識抽出において利点を有する、「大N」分散ネットワークを作成する可能性を有する。 30

#### 【0003】

分散ネットワークシステムは非常に有望な見込みを有する一方で、実際の使用は、環境内への蓄積、検出および無効化、および、積極的な制御を維持できることによる搾取と関連付けられるリスクにより、限定される（中央長距離センサと異なる）。

#### 【0004】

「過渡的な電子機器」という語句は、設定された期間内に消滅する（分解および消失する）電子デバイスの比較的に新しい群を指し、理想的には、分散ネットワークシステムに適用させる。従来の過渡的な電子システムは、典型的に、可溶性基板および電子材料（シリクなど）の使用に依存する。溶媒（典型的には、水）内に置かれると、これらの従来の基板および電子機器は、ゆっくり溶液内に溶解する。したがって、従来の過渡的な電子デバイスで構成される分散ネットワークシステムは、比較的に短い時間で（例えば、周期的な降雨の後）「消滅」することが予期され得る。 40

#### 【0005】

従来の過渡的な電子手法は、電子機器を使用後に「消滅」させるという目的を達成するが、完全に分解および消失するのに長い溶解期間が必要なため、従来の手法は命令下で急速かつ完全に分解することが必要な個別の（例えば、軍事的な）用途には不向きである。さらに、従来の手法は、既存の集積回路製造および組立技術に適合しない材料を利用して 50

いるため、新しいIC製造プロセスを膨大なコストで開発する必要がある。

【0006】

インターポーザは、半導体デバイスパッケージとの関連において既知の電気的インターフェースであり、典型的には、ICダイ(チップ)と、ボールグリッドアレイ(BGA)パッケージまたはピングリッドアレイ(PGA)パッケージなどの標準化された半導体パッケージ構造と、の間に配置される。インターポーザは、典型的に、2つの異なるパターンで対向する基板表面上に配置される対応する接触構造(点)の間に、複数の金属導体が延びる、平坦な絶縁体基板(例えば、FR4などの硬質絶縁体、または、ポリイミドなどの軟質絶縁体のいずれか)を含む。すなわち、インターポーザ基板の1つの側部上に配置される接触点の第1のセットが、対応する接触パッドと合致するパターンでICダイ上に形成され、(例えば、表面搭載技術による)ICとインターポーザとの接続が容易になる。さらに、インターポーザの対向する側部上における接触点の第2のセットが、ホストパッケージの内部表面上に配置される対応する接触構造と合致する第2の(異なる)パターンで並べられ、インターポーザのホストパッケージへの表面搭載が容易になる。金属導体はインターポーザ基板を通過して、第1および第2のセットの対応する接触構造の間に信号経路を提供する。この配列を伴って、ホストパッケージ構造が、例えば、電気システムの印刷回路基板(PCB)と実質的に接続されると、インターポーザにより、ICダイ(複数可)と電気システムとの間の信号の通過が、ホストパッケージのI/Oピン/ボールにより容易になる。

【0007】

インターポーザは、典型的に本来は、標準的なパッケージ構造における対応する接触点とのICダイ接続を別の経路に切り替えるために利用されていたが、近年は他の目的にも役立てられている。例えば、半導体製造の進歩により、相応に微細なピッチのICダイ接触パッドを有する小型のICダイが容易になるので、インターポーザは、さらに、微細に離れたICダイ接触点を、従来のパッケージ構造との適合性が高い幅広いピッチまで広げるために、利用される。この事例において、インターポーザは、微細なピッチの(第1の)パターンで1つの表面上に並べられる第1の接触点、および、幅広いピッチの(第2の)パターンで対向する表面上に並べられる第2の接触点を含み、導電性金属ビアおよびトレースが基板を介して対向する表面に沿って延び、関連する第1および第2の接触点の間に電気信号経路を提供する。微細に離れたICダイ接触点を幅広いピッチに広げることに加えて、インターポーザは、2つ以上のダイを単一のパッケージ構造内に固定するために使用されている。

【0008】

既存のIC製造技術と適合する過渡的な電子パッケージ組立が必要とされており、配置されるICダイが命令により十分に完全に分解され、ICダイ上に実装される無欠損の集積回路へのアクセスを防ぐことで、セキュリティおよび改ざん対策保護の両方を提供することを、達成する。

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、少なくとも1つの集積回路(IC)ダイが、介在するガラスベースのインターポーザを利用してパッケージ構造に搭載される、過渡的な電子デバイスに向けられている。インターポーザは、十分な量のイオンを包含するよう処理されるガラス基板を有し、それにより、過渡的なイベントトリガ信号に応答して破碎(粉末化)され、その際に接合されたICダイ(複数可)も破碎(粉末化)される。従来の配列と類似して、新規のインターポーザは、第1の基板表面上に配置され、ICダイの対応する接触パッドと合致する(第1の)パターンで並べられる、接触点(すなわち、金属パッドまたは他の接触構造)の第1のセットと、対向する基板表面上に配置され、パッケージ構造の対応する接触構造と合致する(第2の)パターンで並べられる、接触点の第2のセットと、関連する第1および第2の接触点の間に電気信号経路を生成する基板上および/または基板を介して延び

10

20

30

40

50

る導体とを含む。本発明の態様にしたがって、I Cダイはインターポーザに固定的に付着される。インターポーザは、イオン交換処理により壊れやすくなるガラス基板を含み、それにより、トリガデバイスによりトリガ信号に応答して生成される初期の破碎強度がインターポーザを介して伝搬し、I Cダイを粉末化する。具体的には、イオン交換処理されたガラス基板は、既知のイオン交換プロセスを使用して処理され、それにより、ガラスは十分なエネルギーを保持して、初期の破碎強度に応じて第2の破碎を生成し、第2の破碎がガラス基板全体に伝搬する。ガラス基板は、プリンスラパートの滴におけるものと類似のメカニズムを使用して、ミクロンサイズの微粒子（すなわち、100 μm以下）に完全に分解（「粉末化」）される。適切な従来の接合技術（例えば、陽極接合または封着ガラスを用いる）を利用して、I Cダイをガラス基板に固定的に付着させることにより、第2の破碎は、さらに、I Cダイを粉末化するのに十分なエネルギーでI Cダイ内へ伝搬する（すなわち、インターポーザ表面の粉末化と実質的に同時）。したがって、本発明により、I Cダイ（複数可）上に形成される機能回路が、従来の（例えば、可溶性基板の）手法を使用して可能な時間よりも、大幅に短い時間で効率的に消滅（粉末化）する、過渡的な電子デバイスおよびシステムの生産が容易になる。さらに、不正な改ざん（例えば、過渡的なデバイスが搭載されるパッケージ構造または印刷回路基板での改ざん）の検出下で粉末化を始動するようトリガデバイスを構成することにより、本発明は、無欠損である一方でI Cダイ上に実装される集積回路への不正なアクセスを防ぐことにより、セキュリティおよび改ざん対策保護の両方を提供する。さらに、インターポーザは低価格の既存のI C製造技術と互換性があるので、本発明により、コアのI C製造プロセスに対する最小の修正を伴う（または、潜在的に全く修正されない）電子デバイスを含む過渡的な電子システムの生産が容易になる。1020

#### 【課題を解決するための手段】

##### 【0010】

本発明の1つの実施形態によると、インターポーザのガラス基板は、（例えば、レーザ、機械的または化学的エッティング技術を使用して）エッティングされて複数のガラス貫通ビア（TGV）開口部を含む、イオン交換特有ガラス（例えば、適切なアルカリ組成物を有する全てのケイ酸塩ガラス）の（例えば、100 μm～300 μmの範囲の厚さを有する）薄いガラスウェハー／シートを備える。その後、TGV開口部は導電性材料（例えば、銅などの金属）で満たされる。ここで、導電性材料は、好ましくは、イオン交換特有ガラスのCTEと合致する（すなわち、+/-10%の）熱膨張係数（CTE）を有し、それにより、導電性材料は、対向する基板表面上に露出される開口部端部を有する金属ビア構造を形成する。その後、接触点（例えば、金属パッド）および選択的な金属トレース構造は、対向する基板表面のうちの1つまたは両方でパターン化され、接触点は上述された所望のパターンで並べられ、および、選択的な金属トレースはパターン化され、上部／下部（第1／第2）の接触点および関連する金属ビア構造の対向する端部の対応するペアの間に電気接続を提供し、それにより、上部／下部（第1／第2）の接触点の対応するペアの間にインターポーザ導体（導電性経路）を形成する。30

##### 【0011】

現段階で好ましい実施形態によると、インターポーザ接触構造および金属トレース構造がガラス基板上に形成される際に、過渡的なイベントトリガデバイスが製造され、あるいは、各インターポーザ上に配置される。トリガデバイスは、トリガデバイスへ供給されるトリガ信号（例えば、外部に伝達される電流パルス）に応答して、初期の破碎強度の放出を制御（すなわち、生成および適用）する作動メカニズムを含む。代替の実施形態において、作動メカニズムは、抵抗過熱をガラス基板へ印加するよう構成されるデバイス、および、機械的圧力をガラス基板へ印加するよう構成されるデバイス、のうちの1つを備える。トリガデバイスをこの手法で構成することにより、トリガ信号を受信すると、作動メカニズムは、十分に強い初期の破碎強度を生成してガラス基板へ印加し、それにより、インターポーザは十分な強度で突発的かつ破滅的に粉末化して、搭載されたI Cダイ（複数可）を完全に確実に破壊（粉末化）する。4050

## 【0012】

本発明の別の態様によると、インターポーザと同時にICダイを確実に粉末化する製造およびダイ接合技術を使用して、ICダイが製造されガラス基板に固定的に付着される。現段階で好ましい実施形態において、ICダイは、標準的なシリコンオンインシュレータ(SOI)製造技術を使用して製造されるICデバイスを含む(すなわち、機能回路がSOI集積回路構造として実装される)。1つの実施形態において、ICダイは、陽極接合を使用してガラス基板に付着され、ガラス基板からの亀裂伝搬が接着チップを確実に破壊するよう良好なインターフェース接着を提供する。代替的な実施形態において、封着ガラスを使用する方法など、別の接合方法が利用されてよい。機能回路をSOI集積回路として形成しICダイをガラス基板に陽極接合することにより、ICダイを微粒子へ過渡的なイベント中に確実に粉末化できる。別の実施形態において、ICダイは、接合プロセスの前または後のいずれかに(例えば、化学的機械的研磨を施すことにより)「薄く」され、ICダイの厚さを削減して、さらに、ICダイを過渡的なイベント中に確実に粉末化する。

## 【0013】

本発明の別の実施形態によると、過渡的な電子デバイスを生産するための方法は、上述のインターポーザ構造を少なくとも部分的に形成すること、および、ガラス基板にイオン交換処理を施してガラス基板の壊れやすさを増大させること、を含む。選択的な浅いイオン交換プロセスがピアエッチングの後に行われ、ピア測壁に沿って壊れやすさを増大させる。(上述された)トリガデバイス、インターポーザ接触構造、および、金属トレース構造は、イオン交換処理の前または後のいずれかに、ガラス基板上に形成/配置される。その後、1つ以上のICダイは、処理されたガラス基板の上部(第1)表面に固定的に(例えば、陽極接合により)付着され、それにより、IC接触点が対応する(第1の)インターポーザ接触構造と電気的に接続される。その後、インターポーザがパッケージ構造上に搭載されて、それにより、第2のパターンでパッケージ構造上に配置される接触構造は、ガラス基板の下部(第2)表面上に配置される対応する(第2の)インターポーザ接触構造と電気的に接続される。上述されるように、インターポーザのガラス基板にイオン交換処理が施され、それにより、そのイオン含有量は、十分に壊れやすく処理されたガラス基板がトリガデバイスにより供給される初期の破碎強度に応答して第2の破碎を生成するまで増大する。ICダイは処理されたガラス基板に接合され、それにより、第2の破碎がICダイ内へ、ICダイを粉末化するのに十分なエネルギーで伝搬する。トリガ後の最終的な微粒子サイズは、ガラス基板の厚さ、イオン交換処理のレベル、ダイ接合プロセス、および、初期の破碎強度などの要因に基づく。1つの実施形態において、ICダイはパターン化され、最終的な破碎された微粒子サイズを制御するのに役立つ破碎点(特性)を提供する(すなわち、破碎特性は、ガラス基板が粉末化されるとICチップがパターン化された破碎特性に沿って破碎するよう形成される)。

## 【0014】

代替的な特有の実施形態によると、過渡的な電子デバイス製造方法は、シートレベルのインターポーザパターンニングまたはダイレベルのインターポーザパターンニングの、いずれかに関与する。各事例において、複数のインターポーザコアは、単一のガラスシート上に一体化して配置される(すなわち、各インターポーザコアのガラス基板は、ガラスシートの対応する部分により形成される)。シートレベルのパターンニング手法において、インターポーザ接触構造およびトリガデバイスが各インターポーザコア上に形成され、その後、ガラスシートが、さいの目状に切られて個々のインターポーザが切り離される。その後、(例えば、個別または一括で)イオン処理が施され、ICダイはインターポーザの各々の上へ接合される。ダイレベルのパターンニング手法によると、ガラスシートは、さいの目状に切られて個々のインターポーザが切り離され、インターポーザ接触構造およびトリガデバイスが各インターポーザコア上に形成される前にイオン交換処理が施され、その後、ICダイがインターポーザの各々の上へ接合される。これらの2つの手法の主な差は、コストおよび性能である。さいの目状に切る前にインターポーザ層をパターンングすることにより、処理能力が向上してコストが削減されるが、パターンングされた金属層でガラスを

10

20

30

40

50

イオン交換することにより、さらに、壊れやすさが減少する可能性がある不均一な表面応力プロファイルを作成する。一方で、パターニング前に個々のダイをイオン交換することにより、より信頼性の高い壊れやすい基板が提供されるが、個々の部分をパターニングするための追加コストは好ましくない。これらの例示的な手法に対する他の変形が、当業者にとって明らかである。

【0015】

本発明のこれらの、および、他の特性、態様、および利点は、以下の記載、付属の請求項、および添付の図と関連して、より良好に理解されるであろう。

【図面の簡単な説明】

【0016】

10

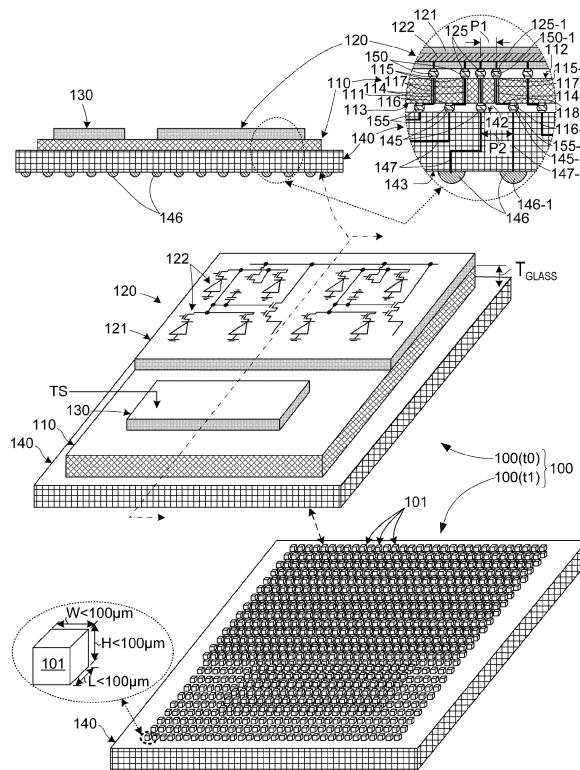

【図1】図1は、本発明の例示的な実施形態にしたがって生産される過渡的な電子デバイスを示す上面斜視図である。

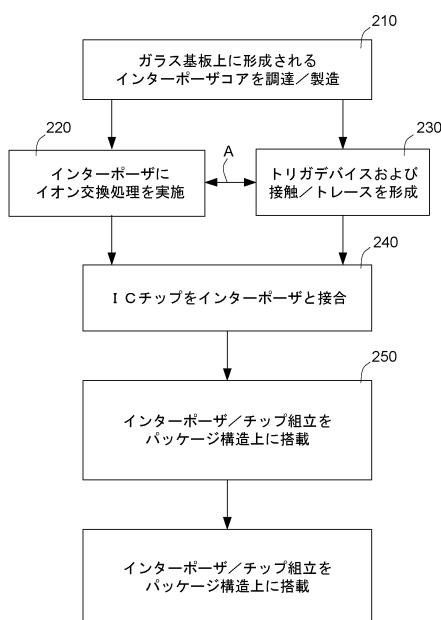

【図2】図2は、図1の過渡的な電子デバイスを生産するための一般化された製造プロセスを示すフロー図である。

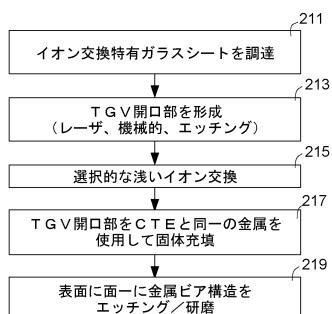

【図3】図3は、本発明の実施形態による、ガラス貫通金属ビア構造を含むインターポーラーコアを生産するための製造プロセスを示すフロー図である。

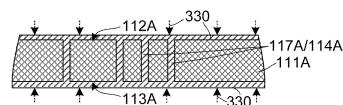

【図3A】図3Aは、図3のプロセスフローによる、インターポーラーコアの生産を示す簡略化された断面側面図である。

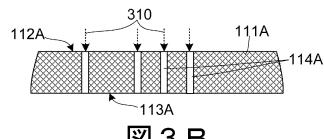

【図3B】図3Bは、図3のプロセスフローによる、インターポーラーコアの生産を示す簡略化された断面側面図である。

20

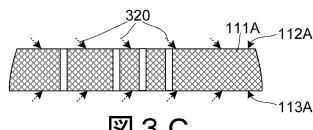

【図3C】図3Cは、図3のプロセスフローによる、インターポーラーコアの生産を示す簡略化された断面側面図である。

【図3D】図3Dは、図3のプロセスフローによる、インターポーラーコアの生産を示す簡略化された断面側面図である。

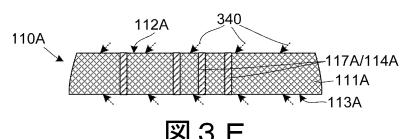

【図3E】図3Eは、図3のプロセスフローによる、インターポーラーコアの生産を示す簡略化された断面側面図である。

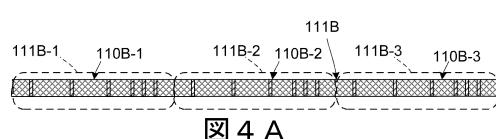

【図4A】図4Aは、本発明のシートレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

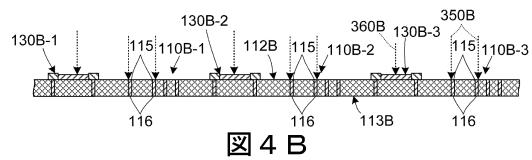

【図4B】図4Bは、本発明のシートレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

30

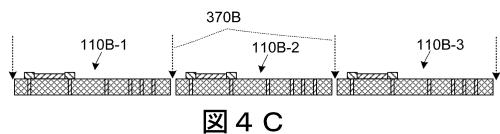

【図4C】図4Cは、本発明のシートレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

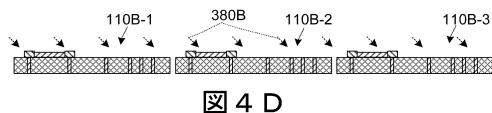

【図4D】図4Dは、本発明のシートレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

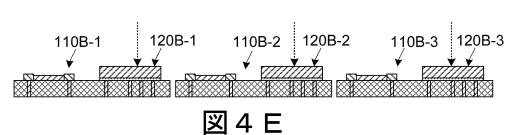

【図4E】図4Eは、本発明のシートレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

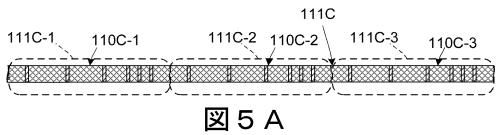

【図5A】図5Aは、本発明のダイレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

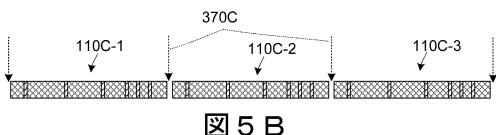

【図5B】図5Bは、本発明のダイレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

40

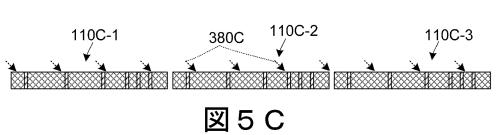

【図5C】図5Cは、本発明のダイレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

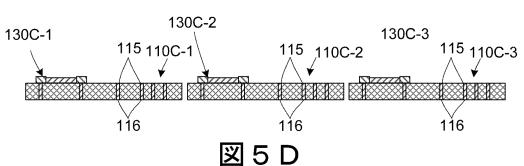

【図5D】図5Dは、本発明のダイレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

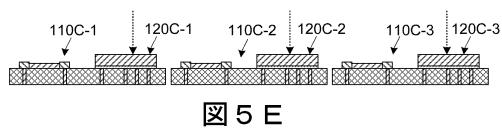

【図5E】図5Eは、本発明のダイレベルのパターニング実施形態による、複数の過渡的な電子デバイスの生産を示す簡略化された断面側面図である。

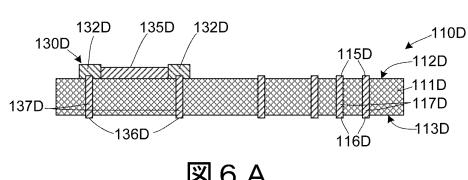

【図6A】図6Aは、本発明の別の実施形態にしたがって生産される過渡的な電子デバイスを示す断面側面図である。

【図6B】図6Bは、本発明の別の実施形態にしたがって生産される過渡的な電子デバイスを示す断面側面図である。

50

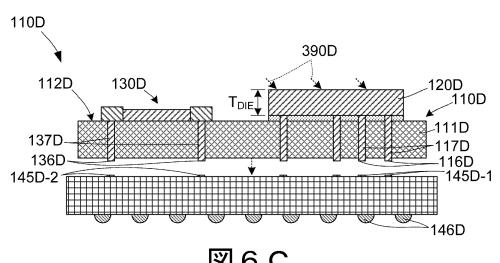

【図6C】図6Cは、本発明の別の実施形態にしたがって生産される過渡的な電子デバイスを示す断面側面図である。

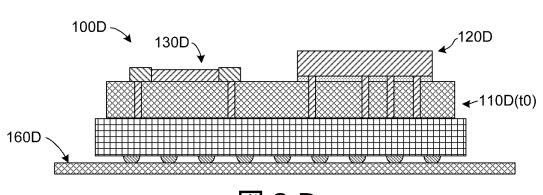

【図6D】図6Dは、本発明の別の実施形態にしたがって生産される過渡的な電子デバイスを示す断面側面図である。

【図6E】図6Eは、本発明の別の実施形態にしたがって生産される過渡的な電子デバイスを示す断面側面図である。

【図6F】図6Fは、本発明の別の実施形態にしたがって生産される過渡的な電子デバイスを示す断面側面図である。

【発明を実施するための形態】

【0017】

10

本発明は、過渡的な電子デバイスの改良に関する。以下の説明は、当業者が、特定の用途および要件の文脈において提供されるように本発明を作成および使用できるよう提示される。本明細書において使用される際、「上部」「上方」「下部」「下方」などの方向を示す用語は、説明の目的で相対的な位置を提供する意図があり、参照の絶対的なフレームを規定する意図はない。好適な実施形態に対する様々な修正が当業者に明らかになり、本明細書に規定される一般的な原理が、他の実施形態に適用されてよい。したがって、本発明は、図示および記載される特定の実施形態に限定されることを意図しないが、本明細書に開示される原理および新規の特性と一致する最も広い範囲に合致する。

【0018】

20

図1は、過渡前の「全体の」状態（すなわち、図1の中央および上部部分に示されるデバイス100（t0））、および、過渡後の「粉末化の」状態（すなわち、図1の下部部分に示されるデバイス100（t1））にある、過渡的な電子デバイス100を示す斜視図および断面図を含む簡略化された図である。

【0019】

図1の中央および上部部分を参照すると、過渡前の状態（例えば、生産の直後）において、過渡的な電子デバイス100（t0）は、一般的に、インターポーラ110上に配置される集積回路（IC）ダイ120およびトリガデバイス130を含み、インターポーラ110は例示的なパッケージ構造140上に搭載される。

【0020】

30

図1の右上部部分に位置づけられるバブルを参照すると、ICダイ120は、任意の既知の半導体製造技術を使用して、基板121（すなわち、例えば、半導体「チップ」）上に形成される電子回路122を含む集積回路デバイスであるが、現段階で好適な実施形態において、ICダイ120は、シリコンオンインシュレータ（SOI）集積回路デバイスである。電子回路122は、以下に記載するように、過渡的なイベントまで所定の有益な機能（例えば、センサ動作）を行うよう構成される、1つ以上の電子的要素を含む。IC接触パッド125は、第1のパターンP1で半導体基板121の表面上に配置され、例えば、従来の金属化パターン（図示せず）を利用して、電子回路122と動作可能に結合される。

【0021】

40

図1の左上部部分に描寫されるように、パッケージ構造140は、例示的な実施形態において、システム回路基板（図示せず）上への表面搭載組立を容易にするよう構成される、複数のボールまたは突起146を含むボールグリッドアレイ（BGA）パッケージ構造として描寫される。具体的には、図1の右上部部分に位置づけられるバブルで示されるように、パッケージ140は、第2のパターンP2でパッケージ基板141の上部表面142上に配置される複数の（第1の）パッケージ接触構造145を含み、ボール／突起（第2のパッケージ接触構造）146が基板141の下部表面143上に配置され、そこから伸びている。パッケージ導体147は、既知の技術を使用して形成され、パッケージ構造141を介して伸び、関連する接触構造間に信号経路を提供する（例えば、導体147-1は、パッケージ接触構造145-1と関連するボール／突起146-1との間に電気経路を形成する）。もちろん、パッケージ構造140は、ピングリッドアレイパッケージ構

50

造など、他のパッケージ種類を使用して実装されてもよい。

【0022】

図1の左上部部分を再び参照すると、従来の配列と同様に、インターポーザ110は、ICダイ120とパッケージ構造140との間に配置され、パッケージ基板140に固定されて、ICダイ120の各接触パッド125をパッケージ構造140上の対応するボール／突起146と結合するアダプタとして機能する。具体的には、インターポーザ110は、現段階で好適な実施形態において、100μm～300μmの範囲である基板の厚さT<sub>G L A S S</sub>だけ離された、上部表面112および対向する下部表面113を有する、薄いガラス基板111を含む。接触点（すなわち、金属パッドまたは他の接触構造）115の第1のセットは、パターンP1で上部表面112上に配置され、それにより、各接触点115の位置がICダイ120の対応する接触パッド125の位置と合致し、ICダイがインターポーザ110上に搭載および固定的に付着（例えば、接合）される表面である場合、動作可能な電気接続が（例えば、はんだ付け構造150を用いて）容易になる。例えば、図1のバブルに示されるように、接触点115-1は、対応する接触パッド125-1と一致し、はんだ付け構造150-1を用いて電気的に接続される。インターポーザ110は、下部表面113上に配置される第2の接触点116を用いてパッケージ構造140に固定され、パターンP2で並べられて、各々がパッケージ構造140上の対応するパッケージ接触構造145と（例えば、はんだ付け構造155を用いて）電気的に接続され、インターポーザ110がパッケージ構造140上に動作可能に搭載される場合、動作可能な電気接続が容易になる。例えば、図1のバブルに示されるように、接触点116-1は、対応する接触構造145-1と一致し、はんだ付け構造155-1を用いて電気的に接続される。さらに、インターポーザ110は、関連する接触点115および116の間に電気信号経路を形成する複数の導体を含み、ここで各導体は、ガラス基板111を介して延びる関連するガラス貫通ビア（TGV）開口部114に配置される金属ビア構造117、および、上部表面112および下部表面113の1つ以上に形成される1つ以上の選択的な金属トレース118を含む。例えば、接触点115-1および116-1は、金属ビア構造117-1および金属トレース118-1により形成される導体により接続され、金属トレースは下部表面113上に形成される。したがって、インターポーザ110は、ICダイ120の接触パッド125-1およびパッケージ構造140のボール／突起146-1の間に、接触点116-1を用いて電気信号経路を提供する。接触点116-1は接触構造145-1および導体147-1によりボール／突起146-1と接続され、導体は金属ビア構造117-1および金属トレース118-1、および、接触点115-1により形成される。

【0023】

以下の追加的な詳細に記載されるように、トリガデバイス130は、ICダイ120の粉末化（断片化）を過渡的なイベント中に、外部から生成されたトリガ信号TSに応答してガラス基板111上へ初期の破碎強度を生成および印加することにより始動するよう機能する。具体的には、トリガデバイス130は、外部から生成されるトリガ信号TSに応答して初期の破碎強度を生成するよう構成され、ガラス基板111の上部表面112に動作可能に付着されて、それにより、生成された初期の破碎強度がガラス基板111上へ印加される。以下に説明されるように、初期の破碎強度は、インターポーザ110およびICダイ120の粉末化を生じさせるのに十分なエネルギーで生成される。

【0024】

本発明の態様によると、ガラス基板111は、イオン交換特有ガラス材料（すなわち、イオン交換処理が施されるガラス）を備え、インターポーザ110は、十分に壊れやすいガラス基板111を提供するプロセスを使用して製造され、それにより、トリガデバイス130により生成される初期の破碎強度に応答して、第2の破碎が生成されガラス基板111を介して十分なエネルギーで伝搬し、ガラス基板111を粉末化する。具体的には、インターポーザコアが以下に記載される手法で生成された後、ガラス基板111に既知のイオン交換プロセスを使用して処理（焼き戻し）を施し、それにより、ガラス基板111

のイオン含有量（すなわち、ガラス基板 111 に含有されるイオンの量）は、十分に壊れやすいガラスを提供する程度まで増大し、それにより、後続の過渡的なイベント中、第 2 の破碎がガラス基板 111 に、トリガデバイス 130 により印加される初期の破碎強度に応答して生成される。さらに、図 1 の下部部分でデバイス 100 (t1) により示されるように、ガラス基板 111 はイオン交換処理により十分に壊れやすくなり、それにより、第 2 の破碎がガラス基板 111 全体に過渡的なイベント中に伝搬する。したがって、ガラス基板 111 は、プリンスラパートの滴におけるものと類似のメカニズムを使用して、ミクロンサイズの微粒子（すなわち、 $100 \mu\text{m}$  以下）に完全に分解（「粉末化」）される。すなわち、図 1 の左下部部分に位置づけられるバブルに示されるように、第 2 の破碎は、処理されたガラス基板 111 全体に急速に伝わる。したがって、ガラス基板 111 は、ミクロンサイズの微粒子 101（すなわち、概して  $100 \mu\text{m}$  より小さい寸法の長さ L、幅 W、および、高さ H を有する）へ、突発的かつ破滅的に分解（粉末化）される。上述された壊れやすさの状態（すなわち、インターポーザコアに施されるイオン交換処理のパラメータ）を達成するために必要なガラス基板 111 の最適なイオン含有量は、ガラス基板 111 の種類および厚さを含み、当業者の能力内での最適な量を判定する、いくつかの要因に依存する。

#### 【0025】

本発明の別の態様によると、ICダイ 120 はインターポーザ 110 に固定的に付着され、それにより、ガラス基板 111 において過渡的なイベント中に生成される第 2 の破碎は、ICダイ 120 をさらに粉末化するのに十分な応力で伝わる。ICダイ 110 をガラス基板 111 に、適切な従来の接合技術（例えば、陽極接合または封着ガラスを用いる）を利用して固定的に付着させることにより、さらに、ガラス基板 111 に生成される第 2 の破碎は、ICダイ 120 内へ、ICダイ 120 を粉末化するのに十分なエネルギーで（すなわち、図 1 の底部に表示されるように、実質的にインターポーザ 110 の粉末化と同時に）伝搬する。したがって、本発明により、ICダイ 120 上に形成される機能回路が従来の（例えば、可溶性基板）手法で可能な時間よりも大幅に短い時間で効率的に消失（粉末化）する、過渡的な電子デバイス 100 の生産が容易になる。さらに、不正な改ざん（例えば、過渡的なデバイス 100 が搭載されるパッケージ構造 140 またはシステム回路基板（図示せず）での改ざん）を検出すると粉末化を始動するようトリガデバイス 130 を構成することにより、本発明は、ICダイ 120 が無欠損な間に電子回路 122 への不正なアクセスを防ぐことで、セキュリティおよび改ざん対策保護を提供する。さらに、インターポーザ 110 は低コストの既存の IC 製造技術に適合するので、本発明により、コア IC 製造プロセスに対する最小の修正で（または、潜在的に修正なしで）過渡的な電子デバイス 100 の生産が容易になる。

#### 【0026】

図 2 は、例示的な実施形態による、過渡的な電子デバイス 100（図 1 参照）を生産するための製造プロセスを示すフロー図である。ここで、本方法は、一般的に、インターポーザ 110 にイオン交換処理を施すこと、その後、ICダイ 120 を処理されたガラス基板 111 に固定的に付着させること、その後、インターポーザ 110 をパッケージ 140 に固定すること、を含む。図 2 の上部部分のブロック 210 を参照すると、本方法は、インターポーザコア（例えば、金属ビア構造を含むが、接触構造、金属トレースまたはトリガデバイスを含まない、適切なガラス基板）を生産または製造することで開始される。例示的なインターポーザコアの製造は、図 3 および図 3 (A) ~ 図 3 (E) を参照して、以下に記載される。次に、イオン交換処理が行われてガラス基板のイオン含有量が増大し（ブロック 220）、インターポーザの製造が完了する（すなわち、接触構造は、図 1 を参照して上述されるパターン P1 および P2 などの所定の配列にしたがって形成され、金属トレースは基板表面の一方または両方に形成され、トリガデバイスはガラス基板上に形成または搭載される）。図 2 の矢印 A に示されるように、および、以下に記載される特定の例示的な実施形態に明記されるように、ブロック 220 において不完全なインターポーザコアにイオン交換処理が施されるか、または、ブロック 230 においてインターポーザが

終了した後にブロック 220 でイオン交換処理が施される。ブロック 240 に示されるように、イオン交換処理が行われた後、1つ以上の IC ダイは、過渡的なイベント中に IC ダイ（複数可）を粉末化するのに十分なエネルギーで、インターポーラから IC ダイ（複数可）内への第 2 の破碎の伝搬を促すダイ接合技術を使用して上述される手法で、各インターポーラと接合される。ブロック 250 を参照すると、その後、インターポーラは、パッケージ構造（例えば、図 1 に示される BGA パッケージ構造 140）上へ動作可能に固定され、したがって、過渡的な電子デバイスはホストシステム内への組み立てが可能な状態となる。

#### 【0027】

図 3 は、本発明の実施形態による、インターポーラコアを生産するための製造プロセスを示すフロー図であり、図 3 (A) ~ 図 3 (E) は、図 3 のプロセスフローの様々な段階中の例示的なインターポーラコアを描写する。

#### 【0028】

図 3 のブロック 211 および図 3 (A) を参照すると、プロセスは、適切な厚さ  $T_{GL_{ASS}}$  を有するイオン交換特有ガラスシート 111A を得ることにより開始される。適切なイオン交換特有ガラスは、強化されていない Corning Gorilla Glass、SCHOTT Xensation および AGC Dragontrail glass を含み、これらは、カリフォルニア州 Santa Paula の Abrisa Technologies など、様々なガラス販売業者から入手可能である。

#### 【0029】

図 3 のブロック 213 および図 3 (B) を参照すると、ガラス貫通ビア (TGV) 開口部 114A は、ガラス基板 111A を介して（すなわち、上部表面 112A および下部表面 113A の間に）全体に延びるよう形成される。代替的な特定の実施形態において、TGV 開口部 114A は、レーザエッチングプロセス、機械的なエッチングプロセス、および、化学的なエッチングプロセスのうちの 1 つを使用して、ガラス基板 111A の一部分をエッチングすることによるものであり、あるいは、切除することによるものである（図 3 (B) の矢印 310 により集合的に示される）。

#### 【0030】

図 3 のブロック 215 および図 3 (C) を参照すると、その後、選択的な浅いイオン交換プロセス（矢印 320 により示される）が行われる（すなわち、金属ビア構造を TGV 開口部 114 に形成する前）。

#### 【0031】

その後、金属ビア構造 117A は、各 TGV 開口部 114A に適切な方法を使用して形成される。図 3 のブロック 217 および図 3 (D) を参照すると、1 つの特定の実施形態において、金属材料 330 が上部表面 112A および下部表面 113A 全体に置かれ、それにより、金属材料の一部分が各 TGV 開口部 114A に入り、対応する金属ビア構造 117A を形成する。図 3 のブロック 219 および図 3 (E) を参照すると、その後、金属材料の残留部分は、上部表面 112A および下部表面 113A から、例えば、適切なエッチング液 340 を使用して除去される。図 3 (E) に描写されるように、エッチングプロセスが行われ、それにより、結果的に生じるインターポーラコア 110A は、ガラス基板 111A を介して延びる、上部表面 112A および下部表面 113A 上にそれぞれ露出される対向する端部を有する、各金属ビア構造 117A を含み、続いて形成される構造（例えば、インターポーラ接触構造および金属トレース構造）への接続が容易になる。

#### 【0032】

その後、上述のインターポーラコアが処理され、IC ダイが搭載される完成したインターポーラを提供する。代替の例示的な実施形態によると、インターポーラコアは、シートレベルのパターニングまたはダイレベルのパターニングのいずれかを使用して、処理される。例示的なシートレベルのパターニングプロセスは、図 4 (A) ~ 図 4 (E) を参照して以下に記載され、例示的なダイレベルのパターニングプロセスは、図 5 (A) ~ 図 5 (E) を参照して以下に記載される。シートレベルおよびダイレベルの処理はいずれも、單

10

20

30

40

50

一のガラスシート上に形成されて一体的に接続される複数のインターポーザコアで開始される。例えば、図4(A)に示されるように、単一の(継続的な/壊れていない)ガラスシート111Bは、3つの一体的に接続されたインターポーザコア110B-1、110B-2、および110B-3を含み、各々が、ガラスシート111Bの対応する部分により形成される各々のガラス基板111B-1、111B-2、および111B-3を有する。同様に、図5(A)に示されるように、一体的なインターポーザコア110C-1、110C-2、および、110C-3は、単一のガラスシート111Cの対応する部分により形成される各々のガラス基板111C-1、111C-2、および、111C-3を有する。

## 【0033】

図4(A)に示される一体的なインターポーザコアで開始され、シートレベルのパターニングは、図4(B)に示されるように、パターニング接触構造、選択的な金属トレース構造、およびトリガデバイスを、各インターポーザコア上へ既知の技術を使用してパターニングすることにより開始される。例えば、接触構造115(および、選択的な金属トレース構造(図示せず))は、適切な金属350Bを上部シート表面112B上に印刷することにより、ガラスシート111Bで形成される。接触構造116および選択的な金属トレース構造(図示せず)は、下部シート表面113B上に形成され、その後、例えば、シート111Bを反転させて金属印刷プロセスを繰り返すことにより形成される。その後、トリガデバイス130B-1～130B-3は、印刷プロセスを使用して適切な材料360Bを置くことにより、または、形成前の構造を各インターポーザ110B-1～110B-3上へ表面搭載することにより、形成される。図4(C)を参照すると、その後、ガラスシート111Bは、さいの目状に切られて(例えば、レーザ370Bを使用して切断されて)、インターポーザ110B-1～110B-3が互いに分離され、その後、図4(D)に示されるように(矢印380Bにより示される)、個々のインターポーザ110B-1～110B-3にイオン交換処理が施される。図4(E)に示されるように、イオン交換処理後、ICダイ120B-1、120B-2、および120B-3は、それぞれインターポーザ110B-1、110B-2、および110B-3上に接合される。

## 【0034】

図5(A)～図5(E)に描写されるダイレベルのパターニングは、各インターポーザコアを独立的に処理することに関与する。すなわち、図5(A)に示される一体的なインターポーザコアで開始され、ダイレベルのパターニングは、さいの目状に切って(例えば、レーザ370Cを使用して切断して)インターポーザコア110C-1～110C-3を互いに分離することにより開始され、その後、図5(C)に示されるように、個々のインターポーザコア110C-1～110C-3にイオン交換処理が施される(矢印380Cにより示される)。イオン交換処理後、図5(D)に示されるように、接触構造115および116、選択的な金属トレース構造、およびトリガデバイス130C-1～130C-3は、上述の技術を使用して各インターポーザコア110C-1～110C-3上に形成され、その後、図5(E)に示されるように、ICダイ120C-1、120C-2、および120C-3が、それぞれインターポーザ110C-1、110C-2、および110C-3上に接合される。

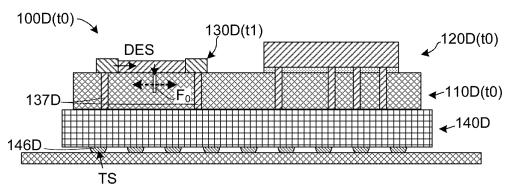

## 【0035】

図6(A)～図6(F)は、本発明の別の実施形態による、過渡的な電子デバイス100Dの製造および後続の作動を描写する。

## 【0036】

図6Aは、上述の技法と一致する手法で生産されたインターポーザ110Dを描写する。描写の目的で、関連する接触構造115Dおよび116Dは、それぞれ上部表面112Dおよび下部表面113D上に配置され、関連する金属ビア構造117Dを備える単一の接触構造を用いて接続される。現段階の実施形態において、トリガデバイス130Dは電気的に制御され、より具体的には、加熱素子を利用して、金属ビア構造137Dを介して送信される印加された電気パルスに応答して局所的な熱を生成する。ここで金属ビア構造

10

20

30

40

50

137Dは、下部表面113D上に配置される関連する接触構造136Dと接続される。1つの実施形態において、トリガデバイス130Dは、広域な／厚い下部抵抗電極132Dを金属ビア構造137Dの関連する上端部部分上へ形成した後、抵抗性の薄く狭い抵抗器（アクチュエータ）構造135Dを電極132Dの間に形成することにより、構築され、ここで抵抗器構造135Dは高温を持続可能な材料（例えば、タンゲステンなどの金属）を使用して形成される。トリガデバイス130Dは、標準的な微細加工技術（蒸着および光パターニング）を使用して、または、単にシャドウマスク蒸発を介して、ガラス基板110D上に直接的に製造される。

【0037】

図6Bは、封着ガラス127Dまたは陽極接合のいずれかを用いる、ICダイ120Dのガラス基板111Dへの後続の固定付着を描写する。図1を参照して上述したように、ICダイ120Dが搭載され、これにより、接触パッド125Dは、ガラス基板111Dの上部表面112D上に配置される接触構造115Dと電気接続される。

10

【0038】

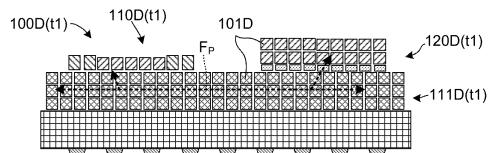

図6(C)は、過渡的な電子デバイス110Dの組み立てを完了するために、インターポーザ110Dをパッケージ構造140Dに固定することを描写する。上記で明記されたように、インターポーザ110Dが搭載され、それにより、パッケージ接触構造145D-1は、ガラス基板110Dの下部表面113D上に配置される対応するインターポーザ接触構造116Dと電気的に接続される。この実施形態において、さらに、トリガデバイス130Dの作動は、パッケージ接触構造145D-2と対応する接触構造136Dとの間の電気接続を用いて可能となり、パッケージ構造140Dのボール／突起146Dとトリガデバイス130Dとの間に、パッケージ構造140に形成される導体（図示せず）およびインターポーザ110Dに配置される金属ビア構造137Dを用いて、信号経路を形成する。

20

【0039】

さらに図6(C)に描写されるように、1つの実施形態において、ICダイ120Dは、化学的機械的研磨(CMP)390Dを介して実際の厚さ $T_{DIE}$ まで、さらに粉末化を促進するために薄くされる。ICダイ120Dの壊れやすさを達成するために重要なのは、ガラス基板111DからICダイ120D内へ伝搬する破碎の亀裂を結合することであり、ICダイ120Dを薄くすることにより（すなわち、描写されるように、インターポーザ110Dへの付着後、または、付着前のいずれかに）可能となる。破碎プロセスは、2つの可能な結果間の競合と見なされ得る：亀裂がダイ基板／シリコン内へ上方に伝搬し得るか、または、鋭く旋回され、代わりに接合領域を介して伝搬し剥離を生じさせ得る。ガラス／シリコン接合に必要な割合を超えるために、陽極接合または低溶解点のいずれかの封着ガラス127Dが、ICダイ120Dをガラス基板111Dに固定するために利用される。代替的に、共晶または粘着接合が、ICダイ120Dをガラス基板110Dに固定するために使用されてよい。

30

【0040】

図6(D)は、過渡的な電子デバイス100Dのシステムレベルの印刷回路基板160Dへの後続的な付着を描写し、パッケージ構造140Dおよびインターポーザ110Dを用いて電力を供給しIC120Dと通信する。例示的な実施形態において、回路基板160Dは、不正な改ざんを筐体で検出可能なセキュリティシステム（例えば、センサ）、および、ICダイ120Dおよびトリガデバイス130Dと通信するよう構成される制御システムを含む、固定された筐体（図示せず）の内部に搭載される。すなわち、正常な動作状態下で、システムコントローラにより、ICダイの機能的な動作が容易になる。しかしながら、図6(E)および図6(F)を参照して以下に記載されるように、システムコントローラが不正な改ざんをシステム筐体（ICダイ120Dの機能回路でアクセスまたは改ざんしようすることに関連してよい）で検出する場合、システムコントローラは、トリガ信号をトリガデバイス130Dへ、過渡的なイベントを始動するために送信する。

40

【0041】

50

図 6 ( E ) および図 6 ( F ) は、過渡的なイベント中の（すなわち、過渡的な電子デバイス 100D へパッケージ構造 140D のボール / 突起 146D を用いて印加されるトリガ信号 TS に応答する）、過渡的な電子デバイス 100D の制御された破壊（分解）を図示する。例示的な実施形態において、トリガデバイス 130D により生成される破碎の仕組みは、抵抗器構造 135D により加熱されるガラス基板 110D の一部分が膨張する際に生成される円周応力である。そのようなトリガデバイスのシミュレーションは、電流パルスが印加されてから 0.5 ms 後、100 ~ 150 MPa の範囲の引張円周応力が抵抗器構造の下位に存在することを示す。これは、ほぼ全ての従来の強化ガラスに破碎を生じさせるのに十分であろう。これらのシミュレーションの結果は、大きな表面張力が適度な量の電流およびエネルギーで取得され得ることを示す。この例において、タンゲステンの特性を使用する抵抗の予測に基づいて、電流は約 70 mA であり、抵抗器全体の電圧は約 80 mV である。これらの量は、現段階で入手可能なスマートフォームファクタ電池の性能内で良好である。図 6 ( E ) に示されるように、時間 t0 (すなわち、トリガ信号 TS の送信直後) の結果的に生じる初期破碎  $F_0$  は、局所的な加熱を用いてガラス基板 110D に生成されるが、IC ダイ 120D は全体的に無欠損のままである。図 6 ( F ) に示されるように、第 2 の破碎  $F_p$  は、ガラス基板 111D (t1) 全体に伝搬する初期の破碎強度に応答して、ガラス基板 111D (t1) に生成される。これにより、ガラス基板 111D (t1) は、微粒子 101D に粉末化される。加えて、IC ダイ 120D (t1) はガラス基板 111D (t1) と十分に接合されるので、第 2 の破碎  $F_p$  は IC ダイ 120D (t1) 内へ、ダイ材料を微粒子 101D に粉末化するのに十分なエネルギーで伝搬する。

#### 【0042】

先の実施形態に描写される局所的な加熱手法に加えて、他のトリガデバイスが、デバイスの粉末化を生成するのに必要な初期破碎を生成するために利用されてよい。例えば、適切なトリガデバイスが生産されてよく、ガラス基板の表面上で化学反応を始動することにより、または、局所的な機械的圧力を（例えば、圧電素子を使用して）ガラス基板上に印加することにより、局所的な破碎を生成する。

#### 【0043】

本発明は特定の実施形態に対して記載されているが、本発明の発明的な特性が他の実施形態にも適用可能であり、その全てが本発明の範囲内にあることを意図することが、当業者に明らかになるであろう。

【図1】

圖 1

【図2】

2

( 3 )

义 3

(図3C)

図 3 C

(図3D)

図 3 D

### 【図3A】

3 A

【図3B】

115A

( 図 3 E )

図3E

### 【図 4 A】

## 図 4 A

【図 4 B】

【図 4 C】

【図 4 D】

【図 4 E】

【図 5 A】

【図 5 B】

【図 5 C】

【図 5 D】

【図 5 E】

【図 6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

図 6 E

【図 6 F】

図 6 F

---

フロントページの続き

(74)代理人 100109070

弁理士 須田 洋之

(74)代理人 100109335

弁理士 上杉 浩

(74)代理人 100120525

弁理士 近藤 直樹

(74)代理人 100167911

弁理士 豊島 匠二

(72)発明者 スコット・ジェイ・エイチ・リム

アメリカ合衆国 カリフォルニア州 94306 パロ・アルト グラント・アベニュー 455

ナンバー1

(72)発明者 グレゴリー・エル・ホワイティング

アメリカ合衆国 カリフォルニア州 94025 メンロー・パーク ミドル・アベニュー 61

7

審査官 河合 俊英

(56)参考文献 特開2015-23197 (JP, A)

特開2014-82447 (JP, A)

国際公開第2015/116749 (WO, A1)

特開2008-153325 (JP, A)

特開平1-273137 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/15

G06F 21/75

H01L 23/32