(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6503264号

(P6503264)

(45) 発行日 平成31年4月17日(2019.4.17)

(24) 登録日 平成31年3月29日(2019.3.29)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 21/60  | (2006.01)    |

| HO 1 L 21/822 | (2006.01)    |

| HO 1 L 27/04  | (2006.01)    |

| HO 1 L 25/00  | (2006.01)    |

|               | HO 1 L 21/60 |

|               | HO 1 L 27/04 |

|               | HO 1 L 21/60 |

|               | HO 1 L 25/00 |

請求項の数 14 (全 18 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2015-167789 (P2015-167789) |

| (22) 出願日  | 平成27年8月27日 (2015.8.27)       |

| (65) 公開番号 | 特開2017-45878 (P2017-45878A)  |

| (43) 公開日  | 平成29年3月2日 (2017.3.2)         |

| 審査請求日     | 平成30年5月17日 (2018.5.17)       |

|           |                                                                |

|-----------|----------------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>東京都江東区豊洲三丁目2番24号              |

| (74) 代理人  | 110002066<br>特許業務法人筒井国際特許事務所                                   |

| (72) 発明者  | 桑島 照弘<br>茨城県ひたちなか市堀口751番地 ルネ<br>サスセミコンダクタマニュファクチュアリ<br>ング株式会社内 |

| (72) 発明者  | 松本 明<br>茨城県ひたちなか市堀口751番地 ルネ<br>サスセミコンダクタマニュファクチュアリ<br>ング株式会社内  |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、前記基板上に層間絶縁膜を挟み、かつ積層された下層コイルおよび上層コイルと、前記上層コイルと電気的に接続された回路部と、複数の電極パッドと、を備えた半導体チップと、

前記上層コイルと、前記回路部と、を電気的に接続し、かつ前記半導体チップ上に配置された第1ワイヤと、

前記半導体チップの周囲に配置された複数のリード部と、

前記半導体チップの前記複数の電極パッドのそれぞれと、前記複数のリード部のそれぞれと、を電気的に接続する複数の第2ワイヤと、

を有し、

前記第1ワイヤは、前記複数の第2ワイヤの延在方向に沿った方向に延在されている、半導体装置。

## 【請求項 2】

請求項1に記載の半導体装置において、

前記第1ワイヤの長さは、前記複数の第2ワイヤのそれぞれの長さより短い、半導体装置。

## 【請求項 3】

請求項1に記載の半導体装置において、

前記回路部は、平面視で、前記第1ワイヤの一端が接続される前記上層コイルの端子と

10

20

、前記第1ワイヤの他端が接続される前記回路部の端子と、の間に配置されている、半導体装置。

【請求項4】

請求項3に記載の半導体装置において、

前記回路部は、平面視で、前記第1ワイヤと重なる位置に配置されている、半導体装置。

【請求項5】

請求項1に記載の半導体装置において、

前記半導体チップ、前記第1ワイヤおよび前記複数の第2ワイヤを覆う樹脂製の封止体が形成されている、半導体装置。

10

【請求項6】

請求項1に記載の半導体装置において、

前記第1ワイヤは、コイル機能を有する、半導体装置。

【請求項7】

請求項1に記載の半導体装置において、

前記第1ワイヤおよび前記複数の第2ワイヤは、同一の材料からなる、半導体装置。

【請求項8】

基板と、前記基板上に層間絶縁膜を挟み、かつ積層された下層コイルおよび上層コイルと、前記上層コイルと電気的に接続された回路部と、複数の電極パッドと、を備えた半導体チップと、

20

前記上層コイルと、前記回路部と、を電気的に接続し、かつ前記半導体チップ上に配置された第1ワイヤと、

前記半導体チップの正面の4辺のそれぞれの周囲に配置された複数のリード部と、

前記半導体チップの前記複数の電極パッドのそれぞれと、前記複数のリード部のそれぞれと、を電気的に接続する複数の第2ワイヤと、

を有し、

前記第1ワイヤは、前記半導体チップの前記正面の4つの辺に沿って設けられた前記複数の電極パッドのうち、平面視における前記上層コイルの中心と最も近い位置の前記電極パッドに接続された前記第2ワイヤの延在方向に沿った方向に延在されている、半導体装置。

30

【請求項9】

請求項8に記載の半導体装置において、

前記第1ワイヤの長さは、前記複数の第2ワイヤのそれぞれの長さより短い、半導体装置。

【請求項10】

請求項8に記載の半導体装置において、

前記回路部は、平面視で、前記第1ワイヤの一端が接続される前記上層コイルの端子と、前記第1ワイヤの他端が接続される前記回路部の端子と、の間に配置されている、半導体装置。

40

【請求項11】

請求項10に記載の半導体装置において、

前記回路部は、平面視で、前記第1ワイヤと重なる位置に配置されている、半導体装置。

【請求項12】

請求項8に記載の半導体装置において、

前記半導体チップ、前記第1ワイヤおよび前記複数の第2ワイヤを覆う樹脂製の封止体が形成されている、半導体装置。

【請求項13】

請求項8に記載の半導体装置において、

前記第1ワイヤは、コイル機能を有する、半導体装置。

50

**【請求項 14】**

請求項 8 に記載の半導体装置において、

前記第 1 ワイヤおよび前記複数の第 2 ワイヤは、同一の材料からなる、半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、例えば、層間絶縁膜を介して積層される 2 つのコイルが設けられた半導体チップを有する半導体装置に関する。

**【背景技術】****【0002】**

基板上に層間絶縁膜を挟んで 2 つのコイルが積層された構造のマイクロトランジスタ素子が知られている。このマイクロトランジスタ素子では、送信回路が接続される送信側コイルと、受信回路が接続される受信側コイルと、を備えている。

**【0003】**

上記マイクロトランジスタ素子については、例えば特開 2011-82212 号公報（特許文献 1）に記載があり、この特許文献 1 には、マイクロトランジスタ素子および送信回路が形成された半導体チップと、受信回路が形成された半導体チップと、が外部配線（ワイヤ）によって接続された構造が開示されている。

**【先行技術文献】****【特許文献】****【0004】****【特許文献 1】特開 2011-82212 号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

上記特許文献 1 に記載された一対のインダクタ素子（マイクロトランジスタ素子）では、一対のインダクタ素子が形成された一方の半導体チップと、インダクタ素子が形成されていない他方の半導体チップと、がワイヤによって接続されている。

**【0006】**

この場合、2 つのチップ間でのチップ厚の差、層間絶縁膜の膜構造の違い、パッド構造の違い等から半導体装置の組立ての難易度が高くなる。さらに、チップ間を接続するワイヤのワイヤ長が長いと、樹脂モールド時にワイヤ流れが発生し、その結果、半導体装置の組立ての難易度がさらに高まる。

**【0007】**

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

**【課題を解決するための手段】****【0008】**

一実施の形態による半導体装置は、基板上に層間絶縁膜を挟みかつ積層された下層コイルおよび上層コイルと、前記上層コイルと電気的に接続された回路部と、複数の電極パッドと、を備えた半導体チップを有する。さらに、上記上層コイルと上記回路部とを電気的に接続し、かつ上記半導体チップ上に配置された第 1 ワイヤと、上記半導体チップの周囲に配置された複数のリード部と、上記半導体チップの上記複数の電極パッドと上記複数のリード部とを電気的に接続する複数の第 2 ワイヤと、を有し、上記第 1 ワイヤは、上記複数の第 2 ワイヤの延在方向に沿った方向に延在されている。

**【0009】**

また、一実施の形態による他の半導体装置は、基板上に層間絶縁膜を挟みかつ積層された下層コイルおよび上層コイルと、上記上層コイルと電気的に接続された回路部と、複数の電極パッドと、を備えた半導体チップを有する。さらに、上記上層コイルと上記回路部とを電気的に接続し、かつ上記半導体チップ上に配置された第 1 ワイヤと、上記半導体チ

10

20

30

40

50

ツップの正面の4辺の周囲に配置された複数のリード部と、上記半導体チップの上記複数の電極パッドと上記複数のリード部とを電気的に接続する複数の第2ワイヤと、を有する。さらに、上記第1ワイヤは、上記半導体チップの上記正面の4つの辺に沿って設けられた上記複数の電極パッドのうち、平面視における上記上層コイルの中心と最も近い位置の上記電極パッドに接続された上記第2ワイヤの延在方向に沿った方向に延在されている。

**【発明の効果】**

**【0010】**

上記一実施の形態によれば、半導体装置の組立ての容易化を図ることができる。

**【図面の簡単な説明】**

**【0011】**

10

【図1】実施の形態の半導体装置の要部の基本構造の一例を示す平面図である。

【図2】図1に示すA-A線に沿って切断した構造を示す断面図である。

【図3】実施の形態の半導体装置の構造の一例を内部を透過して示す平面図である。

【図4】図3に示す半導体装置に搭載される半導体チップの構造の一例を示す断面図である。

【図5】図3に示すA-A線に沿って切断した構造を示す断面図である。

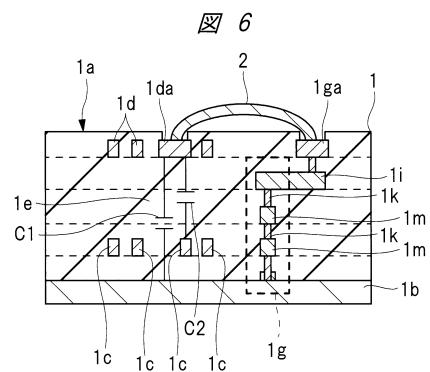

【図6】実施の形態の半導体装置に搭載される半導体チップの基本構造を示す断面図である。

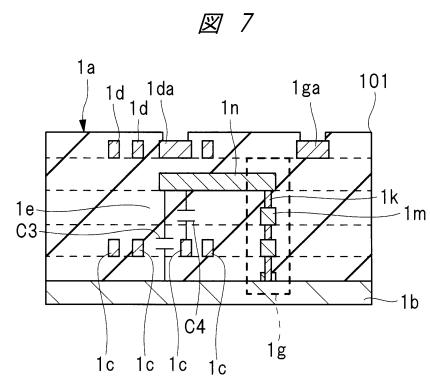

【図7】比較例の半導体チップの構造を示す断面図である。

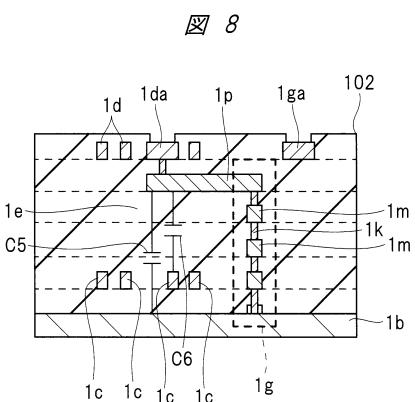

【図8】他の比較例の半導体チップの構造を示す断面図である。

20

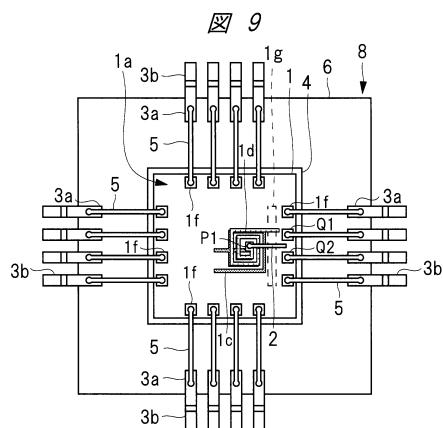

【図9】第1変形例の半導体装置の構造を内部を透過して示す平面図である。

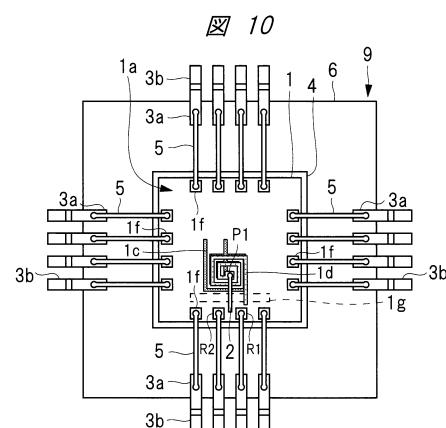

【図10】第2変形例の半導体装置の構造を内部を透過して示す平面図である。

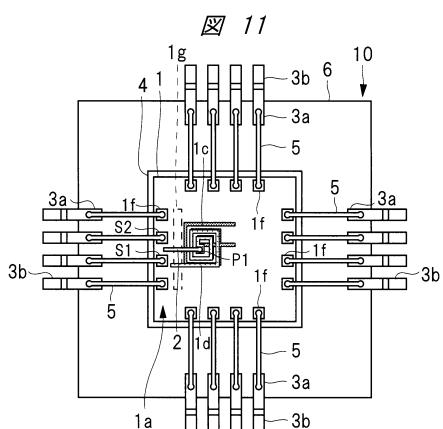

【図11】第3変形例の半導体装置の構造を内部を透過して示す平面図である。

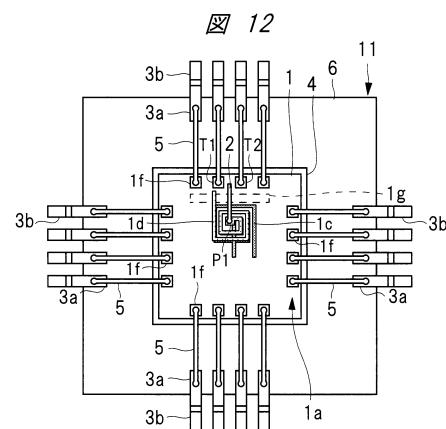

【図12】第4変形例の半導体装置の構造を内部を透過して示す平面図である。

**【発明を実施するための形態】**

**【0012】**

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

**【0013】**

30

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

**【0014】**

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

**【0015】**

40

また、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

**【0016】**

また、以下の実施の形態において、構成要素等について、「Aから成る」、「Aより成る」、「Aを有する」、「Aを含む」と言うときは、特にその要素のみである旨明示した場合等を除き、それ以外の要素を排除するものでないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

50

## 【0017】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、図面をわかりやすくするために平面図であってもハッチングを付す場合がある。

## 【0018】

## &lt;半導体装置の構造&gt;

図1は実施の形態の半導体装置の要部の基本構造の一例を示す平面図、図2は図1に示すA-A線に沿って切断した構造を示す断面図、図3は実施の形態の半導体装置の構造の一例を内部を透過して示す平面図、図4は図3に示す半導体装置に搭載される半導体チップの構造の一例を示す断面図、図5は図3に示すA-A線に沿って切断した構造を示す断面図である。

10

## 【0019】

本実施の形態の半導体装置は、図1および図2の基本構造に示すように、内部に搭載される半導体チップ1に一対の2つのインダクタ(コイル)が配置されたものであり、チップ内において、2つのインダクタ(一対のインダクタ素子であり、この素子のことをマイクロトランジスタともいう)を誘導結合させることにより、インダクタ間を非接触で電気信号を伝達するものである。ここで、誘導結合させるインダクタ間での電源電圧は、例えば、低電圧側が数V程度で、一方、高電圧側が数百V~数千V程度と大きく異なっており、したがって、上記インダクタ間で絶縁膜(絶縁層)を介して非接触で電気信号を伝達する。

20

## 【0020】

また、半導体チップ1には、外部に信号を送信する回路部や、外部からの信号を受信する回路部が設けられている。すなわち、本実施の形態の半導体装置は、インダクタ結合を行う2つのコイルやコイルへの信号の送受信を行う回路部が1つの半導体チップ1に組み込まれ、1チップ化された半導体パッケージである。

## 【0021】

ここで、本実施の形態の半導体装置の用途について説明すると、本実施の形態の半導体装置は、例えば、自動車(EV:電気自動車、HV:ハイブリッド自動車)、スイッチング電源、照明コントローラ、太陽光発電コントローラ、または携帯電話器やモバイル通信機器等に適用することができる。

30

## 【0022】

その中で、例えば、自動車用途としては、半導体チップ1の低電圧側の供給電源電圧が、例えば5V程度であるのに対し、一方、高電圧側の供給電源電圧は、例えば600V~1000Vもしくはそれ以上の電圧である。

## 【0023】

次に、図3~図5を用いて本実施の形態の半導体装置の詳細構造について説明する。なお、本実施の形態では、上記半導体装置の一例として、SOP(Small Outline Package)7を取り上げて説明する。

## 【0024】

40

SOP7には、図4に示すように、シリコンのベース板である基板1b、基板1b上に設けられた回路部、および正面1aに露出する複数の電極パッド1fを備えた半導体チップ1が組み込まれている。さらに、半導体チップ1には、基板1b上において、層間絶縁膜1eを挟み、かつ積層された下層コイル(下層インダクタ)1cおよび上層コイル(上層インダクタ)1dと、上層コイル1dに電気的に接続された第1回路部(回路部)1gと、下層コイル1cに電気的に接続された第2回路部1hと、が設けられている。

## 【0025】

すなわち、下層コイル1cと上層コイル1dは、層間絶縁膜1eを挟んだ状態で対向して配置されている。言い換えると下層コイル1cと上層コイル1dは、電気的に絶縁(分離)されている。これにより、チップ内部において、下層コイル1cと上層コイル1dと

50

が誘導結合され、その結果、下層コイル 1 c と上層コイル 1 d との間で非接触で電気信号を伝達することができる。

**【 0 0 2 6 】**

なお、下層コイル 1 c および上層コイル 1 d は、例えば、銅 ( C u ) 配線からなり、下層コイル 1 c と上層コイル 1 d の間に介在される層間絶縁膜 1 e は、例えば、ポリイミドからなる。

**【 0 0 2 7 】**

また、下層コイル 1 c と上層コイル 1 d のそれぞれ平面形状は、四角形の渦巻き状からなる。

**【 0 0 2 8 】**

ここで、半導体チップ 1 は、図 5 に示すように、接着材であるダイボンド材を介してダイパッド 4 上に搭載されている。

**【 0 0 2 9 】**

さらに、半導体チップ 1 の正面 1 a 上には、上層コイル 1 d と、第 1 回路部 1 g とを電気的に接続する外部配線であるワイヤ ( 第 1 ワイヤ ) 2 が配置されている。すなわち、ワイヤ 2 は、上層コイル 1 d の端子 1 d a と第 1 回路部 1 g の端子 1 g a とを電気的に接続するものであるが、半導体チップ 1 の外部に配置された外部配線である。

**【 0 0 3 0 】**

これは、チップ内において、内部配線で上層コイル 1 d と第 1 回路部 1 g とを電気的に接続しようとすると、上層コイル 1 d の端子 1 d a は、コイルの中心付近に配置されているため、上層コイル 1 d と同一層では引き出すことができない。その結果、上層コイル 1 d と第 1 回路部 1 g とを電気的に接続するための、半導体チップ 1 の外部配線としてワイヤ 2 が用いられている。なお、上層コイル 1 d と層を変えて内部配線を用いて引き出すことも考えられるが、その場合、半導体チップ 1 の層数が増えるため、コスト高となる。

**【 0 0 3 1 】**

したがって、本実施の形態の S O P 7 では、半導体チップ 1 における上層コイル 1 d と第 1 回路部 1 g とを外部配線 ( ワイヤ 2 ) によって電気的に接続している。

**【 0 0 3 2 】**

また、図 3 に示すように、S O P 7 は、半導体チップ 1 の周囲に配置された複数のインナリード ( リード部 ) 3 a と、複数のインナリード 3 a のそれぞれに繋がる外部端子であるアウタリード 3 b と、半導体チップ 1 の複数の電極パッド 1 f のそれぞれと複数のインナリード 3 a のそれぞれとを電気的に接続する複数のワイヤ ( 第 2 ワイヤ ) 5 と、を有している。

**【 0 0 3 3 】**

すなわち、S O P 7 では、半導体チップ 1 の正面 1 a の対向する 2 つの辺の周縁部のそれぞれに複数の電極パッド 1 f が配置されており、半導体チップ 1 の正面 1 a の対向する 2 辺それぞれに対向して複数のインナリード 3 a が設けられている。

**【 0 0 3 4 】**

したがって、S O P 7 における複数のインナリード 3 a は、図 3 に示すように、半導体チップ 1 の正面 1 a の対向する 2 辺それぞれに対向する状態で配置されているため、これらのインナリード 3 a に接続される複数のワイヤ 5 は、それぞれ同じ方向に沿って延在している。

**【 0 0 3 5 】**

そして、本実施の形態の S O P 7 では、ワイヤ 2 は、複数のワイヤ 5 の延在方向に沿った方向に延在するように形成されている。すなわち、半導体チップ 1 上に配置されるワイヤ 2 と、複数のインナリード 3 a のそれぞれに接続する組立て用の複数のワイヤ 5 は、同一方向に形成されている。

**【 0 0 3 6 】**

さらに、半導体チップ 1 上に配置されるワイヤ 2 の長さは、複数のワイヤ 5 のそれぞれの長さより短い。つまり、複数のワイヤ 5 のそれぞれの延在方向に沿った方向におけるワ

イヤ2の長さが、複数のワイヤ5それぞれの長さより短くなっている。

**【0037】**

また、SOP7では、上層コイル1dの一部としてワイヤ2を用いている。言い換えると、ワイヤ2はコイル機能を有している。すなわち、ワイヤ2は、図3に示すように、一端が上層コイル1dの端子1daに接続し、他端が第1回路部1gの端子1gaに接続されているが、上層コイル1dを設計する際に、ワイヤ2も上層コイル1dの一部と見做して抵抗値等を考慮して設計されている。つまり、ワイヤ2の端子1gaとの境界部までを上層コイル1dと見做して設計している。

**【0038】**

これにより、コイルの設計を容易にすることができます。

10

**【0039】**

なお、ワイヤ2は、必ずしも上層コイル1dの一部と見做さずにコイル（インダクタ）を設計してもよい。つまり、ワイヤ2はコイル機能を有していないなくてもよい。この場合には、上層コイル1dの端子1daまでをコイル（インダクタ）として設計する。

**【0040】**

また、SOP7では、複数のアウタリード3bのそれぞれは、図5に示すように、ガルウィング状に曲げ成形されている。

**【0041】**

また、半導体チップ1に形成される第1回路部1gおよび第2回路部1hは、第1回路部1gおよび第2回路部1hのうち、何れか一方が送信回路であり、何れか他方が受信回路である。例えば、上層コイル1dとワイヤ2を介して電気的に接続される第1回路部1gが送信回路である場合、下層コイル1cと電気的に接続される第2回路部1hは、受信回路である。この時、送信回路は、外部に信号を送信するものであり、受信回路は、外部からの信号を受信するものである。

20

**【0042】**

一方、例えば、上層コイル1dとワイヤ2を介して電気的に接続される第1回路部1gが受信回路である場合、下層コイル1cと電気的に接続される第2回路部1hが、送信回路である。

**【0043】**

なお、図4に示すように、半導体チップ1の内部において、第1回路部1gおよび第2回路部1hは、相互に絶縁された2枚のSOI(Silicon On Insulator)1j上に形成されている。また、第1回路部1gおよび第2回路部1hは、それぞれ内部配線1mとビア配線1kとによって形成されている。そして、第2回路部1hは、下層コイル1cの端子1caと電気的に接続されているが、一方、第1回路部1gは、引き出し配線1iによって引き出されて、この引き出し配線1iが第1回路部1gの端子1gaに接続されている。

30

**【0044】**

このように引き出し配線1iを配置することで、ワイヤ2の最小の距離を確保している。すなわち、ワイヤ2をワイヤボンディングするためには、少なくともパッド間に1mm程度の長さ（パッド間距離）が必要である。したがって、この距離を確保するために第1回路部1gは引き出し配線1iを介して端子1gaに接続されている。

40

**【0045】**

そして、本実施の形態のSOP7では、このワイヤ2の1mm程度の長さを利用して、半導体チップ1のこのワイヤ2の直下のスペースに第1回路部1gを形成している。

**【0046】**

すなわち、図3に示すように、第1回路部1gは、平面視で、ワイヤ2の一端が接続される上層コイル1dの端子1daと、ワイヤ2の他端が接続される第1回路部1gの端子1gaと、の間に配置されている。

**【0047】**

別の言い方をすると、第1回路部1gは、平面視で、ワイヤ2と重なる位置に配置され

50

ている。

**【0048】**

なお、第1回路部1gおよび第2回路部1hは、送受信回路以外の他の回路、例えば、ロジック回路等であってもよい。

**【0049】**

また、SOP7では、図5に示すように、半導体チップ1、複数のインナリード3a、ワイヤ2および複数のワイヤ5を覆う樹脂製の封止体6が形成されている。封止体6は、例えば、樹脂モールディングによって形成されるものであり、例えば、熱硬化性のエポキシ樹脂等が用いられる。

**【0050】**

また、SOP7では、ワイヤ2および複数のワイヤ5は、同一の材料からなることが好みしい。例えば、金(Au)ワイヤ、もしくは銅(Cu)ワイヤ等である。

**【0051】**

本実施の形態のSOP(半導体装置)7によれば、下層コイル1cおよび上層コイル1d、上層コイル1dと接続された第1回路部1gが1チップに設けられ、かつ上層コイル1dと第1回路部1gとを接続する外部配線のワイヤ2が、組立て用の複数のワイヤ5と同一方向に延在されていることで、樹脂モールド時のワイヤ2のワイヤ流れの発生を抑制することができる。つまり、樹脂モールド時に、樹脂が複数のワイヤ5の延在方向に沿って流れるように設定されてモールドが行われるため、ワイヤ2も複数のワイヤ5と同一方向に形成することで、ワイヤ2のワイヤ流れを抑制することができる。

10

**【0052】**

これにより、封止体6を形成する樹脂モールド時のワイヤ2のワイヤ倒れおよびワイヤ歪みを抑制することができる。その結果、半導体装置の組立ての容易化を図ることができる。

**【0053】**

また、下層コイル1cおよび上層コイル1d、上層コイル1dと接続された第1回路部1gが1チップに設けられたことで、2つのチップ間でのチップ厚の差、層間絶縁膜の膜構造の違い、パッド構造の違い等の発生を阻止することができる。これにより、2つのチップを用いて組立てる場合に比べて、チップ厚の差、層間絶縁膜の膜構造の違い、パッド構造の違い等から発生する半導体装置の組立ての難易度が高くなることを抑制できる。

20

**【0054】**

したがって、半導体装置の組立ての容易化をさらに図ることができる。

**【0055】**

また、半導体チップ1上に配置されるワイヤ2の長さが、複数のワイヤ5のそれぞれの長さより短いことにより、封止体6を形成する樹脂モールドにおけるワイヤ2のワイヤ流れの発生を抑制することができる。さらに、ワイヤ2の長さが短いため、ワイヤ2の電気的抵抗を低く(小さく)することができ、ワイヤ2の電気的特性を向上させることができる。また、ワイヤ2の長さが短いことにより、ワイヤ2を上層コイル1dの一部として見做した場合に、ワイヤ2の電気的抵抗が小さくなることで、上層コイル1dの容量Cを低減したり、ノイズを小さくしたりすることができ、コイル特性を高めることができる。

30

**【0056】**

また、第1回路部1gは、平面視で、ワイヤ2のパッド間、すなわち上層コイル1dの端子1daと第1回路部1gの端子1gaとの間の位置に配置されている。もしくは、第1回路部1gは、平面視で、ワイヤ2と重なる位置に配置されている。これにより、回路部のレイアウトを効率良くすることができる。また、チップ内における回路部のレイアウトを効率良くすることができるため、半導体チップ1の小型化を図ることができる。その結果、SOP(半導体装置)7の小型化を図ることができる。

40

**【0057】**

また、ワイヤ2とワイヤ5とが同一の材料からなることにより、ワイヤボンディング工程において、ワイヤを換えることなく同一のボンディング処理でワイヤ2とワイヤ5の両

50

方をボンディングすることができ、半導体装置の組立ての効率を向上させることができる。なお、ワイヤボンディング工程において、ワイヤ2とワイヤ5とでは、両者のうち、より内側に配置されるワイヤ2のボンディングを先に行い、ワイヤ2をボンディングした後に、ワイヤ2より外側の位置に配置される複数のワイヤ5のボンディングを行う。

#### 【0058】

ここで、本実施の形態の半導体装置と、本願発明者が比較検討を行った構造とで、比較を行う。図6は実施の形態の半導体装置に搭載される半導体チップの基本構造を示す断面図、図7は比較例の半導体チップの構造を示す断面図、図8は他の比較例の半導体チップの構造を示す断面図である。

#### 【0059】

本実施の形態の半導体装置(SOP7)の半導体チップ1では、図6に示すように、上層コイル1dと第1回路部1gとが、外部配線(ワイヤ2)によって接続されており、かつワイヤ2が接続されるパッド間(上層コイル1dの端子1daと第1回路部1gの端子1gaとの間)に第1回路部1gが配置されている。

#### 【0060】

これに対して図7に示す比較例の構造では、図6に示すような外部配線(ワイヤ2)を用いない代わりに、内層の引き出し配線1nによって上層コイル1dと第1回路部1gとが電気的に接続されている。

#### 【0061】

図7に示す構造の場合、半導体チップ101内において、引き出し配線1nと基板1bとの距離が、図6の上層コイル1dと基板1bとの距離より短くなるため、図6の上層コイル1d - 基板1b間の容量C1に対して、図7の引き出し配線1n - 基板1b間の容量C3が大きくなる。さらに、図6の上層コイル1d - 下層コイル1c間の容量C2に対して、図7の引き出し配線1n - 下層コイル1c間の容量C4も大きくなる。

#### 【0062】

つまり、図7に示す比較例の構造では、容量を低減することができない。

#### 【0063】

また、図7に示す構造の場合、引き出し配線1nと基板1bとの距離が、図6の上層コイル1dと基板1bとの距離より短くなるため、図6の本実施の形態の構造に比べて耐圧を向上させることができない。結果として、図7に示す比較例の構造は、図6の本実施の形態の構造に対して、容量低減を図ることができず、かつ耐圧向上も図ることができない。

#### 【0064】

次に、図8に示す他の比較例の構造は、図6に示すような外部配線(ワイヤ2)を用いない代わりに、配線層を1層増やしてその配線層に引き出し配線1pを形成し、この引き出し配線1pによって上層コイル1dと第1回路部1gとを電気的に接続したものである。

#### 【0065】

図8に示す構造の場合、半導体チップ102内において、引き出し配線1pと基板1bとの距離は、図6の上層コイル1dと基板1bとの距離と同じである。したがって、図6の上層コイル1d - 基板1b間の容量C1と、図8の引き出し配線1p - 基板1b間の容量C5は、同じ大きさである。さらに、図6の上層コイル1d - 下層コイル1c間の容量C2と、図8の引き出し配線1p - 下層コイル1c間の容量C6も同じ大きさである。

#### 【0066】

その結果、図8に示す他の比較例の構造は、図6の本実施の形態の構造と比べて、容量および耐圧について同等である。しかしながら、図8の他の比較例の構造では、図6の構造に比べて引き出し配線1pを形成するための配線層を一層増やしているため、半導体チップ1のコストが増えてしまう。

#### 【0067】

つまり、図6に示す本実施の形態の、外部配線(ワイヤ2)を用いたチップ構造によれ

10

20

30

40

50

ば、配線層の数を増やさないことでコストを増加させることなく、上層コイル 1 d と下層コイル 1 c 間、および上層コイル 1 d と基板 1 b 間それぞれの容量低減と耐圧向上を図ることができる。

#### 【0068】

また、チップ上の外部配線であるワイヤ 2 を、組立て用の複数のワイヤ 5 と同一方向に延在させたことにより、樹脂モールド時のワイヤ 2 のワイヤ流れ等によるワイヤ倒れやワイヤ歪みを抑制することができ、半導体装置の組立ての容易化を図ることができる。

#### 【0069】

また、ワイヤ 2 を接続する両パッド間に送受信等の回路部である第 1 回路部 1 g を配置することにより、チップ内の空きスペースを有効活用することができ、チップ内における回路部のレイアウトを効率良くすることができる。これにより、半導体チップ 1 の小型化を図ることができる。10

#### 【0070】

<第 1 变形例>

図 9 は第 1 变形例の半導体装置の構造を内部を透過して示す平面図である。

#### 【0071】

図 9 に示す半導体装置は、半導体チップ 1 の主面 1 a の 4 辺のそれぞれの周囲に複数のリード部が配置された QFP (Quad Flat Package) 8 であり、本第 1 变形例では、QFP 8 について説明する。

#### 【0072】

なお、上記実施の形態では、1 チップに 2 つのコイルと、これらのコイルと電気的に接続される送受信回路とが組み込まれた SOP 7 の場合を説明したが、本第 1 变形例では、さらにチップの機能向上等によりピン数が増えた場合を考慮し、その一例として QFP 8 を取り上げて説明する。20

#### 【0073】

図 9 に示す QFP 8 の構造について説明すると、QFP 8 には、図 4 に示す基板 1 b と、基板 1 b 上に層間絶縁膜 1 e を挟み、かつ積層された一対の下層コイル 1 c および上層コイル 1 d と、上層コイル 1 d と電気的に接続された回路部である第 1 回路部 1 g と、複数の電極パッド 1 f と、を備えた半導体チップ 1 が組み込まれている。また、半導体チップ 1 には、下層コイル 1 c に電気的に接続された第 2 回路部 1 h も形成されている。第 1 回路部 1 g および第 2 回路部 1 h は、例えば、送信回路または受信回路であるが、送受信回路以外の他の回路、例えば、ロジック回路等であってもよい。30

#### 【0074】

また、半導体チップ 1 上には、上層コイル 1 d と第 1 回路部 1 g とを電気的に接続する外部配線であるワイヤ（第 1 ワイヤ）2 が設けられている。

#### 【0075】

さらに、半導体チップの主面 1 a の 4 辺のそれぞれの周囲に配置された複数のリード部であるインナリード 3 a と、複数のインナリード 3 a に繋がる複数の外部端子であるアウターリード 3 b とを有している。また、半導体チップ 1 の複数の電極パッド 1 f のそれぞれと、複数のインナリード 3 a のそれぞれとを電気的に接続する複数のワイヤ（第 2 ワイヤ）5 と、を有している。40

#### 【0076】

また、半導体チップ 1、複数のインナリード 3 a、ワイヤ 2 および複数のワイヤ 5 を覆う樹脂製の封止体 6 が形成されている。

#### 【0077】

ここで、QFP 8 におけるワイヤ 2 は、半導体チップ 1 の主面 1 a の 4 つの辺に沿って設けられた複数の電極パッド 1 f のうち、平面視における上層コイル 1 d の中心 P 1 と最も近い位置の電極パッド 1 f に接続されたワイヤ 5 の延在方向に沿った方向に延在されている。言い換えると、外部配線であるワイヤ 2 は、半導体チップ 1 の主面 1 a の 4 辺に沿って設けられた複数の電極パッド 1 f のうち、上層コイル 1 d の中心 P 1 と最も近い位置50

の電極パッド 1 f に接続されたワイヤ 5 と同一の方向に延在されている。

**【 0 0 7 8 】**

図 9 に示す構造では、ワイヤ 2 は、上層コイル 1 d の中心 P 1 と最も近い位置の電極パッド 1 f ( Q 1 もしくは Q 2 ) に接続されたワイヤ 5 の延在方向と同一の方向に延在されている。なお、上層コイル 1 d の中心 P 1 に近い電極パッド 1 f が同程度の距離に複数個設けられている場合には、それらの電極パッド 1 f のうちの何れの電極パッド 1 f を採用してもよく、その選択した電極パッド 1 f に接続されたワイヤ 5 の延在方向と同一方向に延在されればよい。

**【 0 0 7 9 】**

また、上記実施の形態の S O P 7 と同様に、ワイヤ 2 の長さは、複数のワイヤ 5 のそれぞれの長さより短い。10

**【 0 0 8 0 】**

さらに、図 4 に示す半導体チップ 1 と同様に、第 1 回路部 1 g は、平面視で、ワイヤ 2 の一端が接続される上層コイル 1 d の端子 1 d a と、ワイヤ 2 の他端が接続される第 1 回路部 1 g の端子 1 g a と、の間に配置されている。別の言い方をすると、第 1 回路部 1 g は、平面視で、ワイヤ 2 と重なる位置に配置されている。

**【 0 0 8 1 】**

本第 1 変形例の Q F P 8 のその他の構造については、上記実施の形態の S O P 7 と同様であるため、その重複説明は省略する。

**【 0 0 8 2 】**

本第 1 変形例の Q F P 8 によれば、ワイヤ 2 を、最も近い位置の組立て用のワイヤ 5 と同一方向に延在させたことにより、上記実施の形態の S O P 7 と同様に、樹脂モールド時のワイヤ 2 のワイヤ流れ等によるワイヤ倒れやワイヤ歪みを抑制することができ、半導体装置の組立ての容易化を図ることができる。20

**【 0 0 8 3 】**

また、半導体チップ 1 上に配置されるワイヤ 2 の長さが、複数のワイヤ 5 のそれぞれの長さより短いことにより、封止体 6 を形成する樹脂モールドにおけるワイヤ 2 のワイヤ流れの発生を抑制することができる。さらに、ワイヤ 2 の長さが短いため、ワイヤ 2 の電気的抵抗を低く（小さく）することができ、ワイヤ 2 の電気的特性を向上させることができる。30

**【 0 0 8 4 】**

また、ワイヤ 2 を接続する両パッド間に送受信等の回路部である第 1 回路部 1 g を配置することにより、チップ内の空きスペースを有効活用することができ、チップ内における回路部のレイアウトを効率良くすることができる。これにより、半導体チップ 1 の小型化を図ることができる。

**【 0 0 8 5 】**

本第 1 変形例の Q F P 8 によって得られるその他の効果については、上記実施の形態の S O P 7 と同様であるため、その重複説明は省略する。

**【 0 0 8 6 】**

< 第 2 変形例 >

40

図 10 は第 2 変形例の半導体装置の構造を内部を透過して示す平面図である。

**【 0 0 8 7 】**

本第 2 変形例は第 1 変形例と同様の構造の Q F P 9 について説明するものである。Q F P 9 は、上記第 1 変形例の Q F P 8 と同様の構造のものであるが、Q F P 8 との相違点は、半導体チップ 1 に対する上層コイル 1 d と下層コイル 1 c が設けられた位置とこれらコイルの向きである。

**【 0 0 8 8 】**

そして、Q F P 9 の場合にも、そのワイヤ 2 は、半導体チップ 1 の正面 1 a の 4 つの辺に沿って設けられた複数の電極パッド 1 f のうち、平面視における上層コイル 1 d の中心 P 1 と最も近い位置の電極パッド 1 f に接続されたワイヤ 5 の延在方向に沿った方向に延

50

在されている。言い換えると、外部配線であるワイヤ2は、半導体チップ1の正面1aの4辺に沿って設けられた複数の電極パッド1fのうち、上層コイル1dの中心P1と最も近い位置の電極パッド1fに接続されたワイヤ5と同一の方向に延在されている。

#### 【0089】

図10に示す構造では、ワイヤ2は、上層コイル1dの中心P1と最も近い位置の電極パッド1f(R1もしくはR2)に接続されたワイヤ5の延在方向と同一の方向に延在されている。

#### 【0090】

また、上記第1変形例のQFP8と同様に、ワイヤ2の長さは、複数のワイヤ5のそれぞれの長さより短い。

10

#### 【0091】

さらに、図4に示す半導体チップ1と同様に、第1回路部1gは、平面視で、ワイヤ2の一端が接続される上層コイル1dの端子1daと、ワイヤ2の他端が接続される第1回路部1gの端子1gaと、の間に配置されている。

#### 【0092】

本第2変形例のQFP9のその他の構造については、第1変形例のQFP8と同様であるため、その重複説明は省略する。

#### 【0093】

本第2変形例のQFP9によれば、ワイヤ2を、最も近い位置の組立て用のワイヤ5と同一方向に延在させることにより、上記第1変形例のQFP8と同様に、樹脂モールド時のワイヤ2のワイヤ流れ等によるワイヤ倒れやワイヤ歪みを抑制することができ、半導体装置の組立ての容易化を図ることができる。

20

#### 【0094】

また、半導体チップ1上に配置されるワイヤ2の長さが、複数のワイヤ5のそれぞれの長さより短いことにより、封止体6を形成する樹脂モールドにおけるワイヤ2のワイヤ流れの発生をさらに抑制することができる。また、ワイヤ2の長さが短いため、ワイヤ2の電気的抵抗を低く(小さく)することができ、ワイヤ2の電気的特性を向上させることができる。

#### 【0095】

また、ワイヤ2を接続する両パッド間に送受信等の回路部である第1回路部1gを配置することにより、チップ内の空きスペースを有効活用することができ、チップ内における回路部のレイアウトを効率良くすることができる。これにより、半導体チップ1の小型化を図ることができる。

30

#### 【0096】

本第2変形例のQFP9によって得られるその他の効果については、上記第1変形例のQFP8と同様であるため、その重複説明は省略する。

#### 【0097】

<第3変形例>

図11は第3変形例の半導体装置の構造を内部を透過して示す平面図である。

#### 【0098】

本第3変形例は第1変形例と同様の構造のQFP10について説明するものである。QFP10は、上記第1変形例のQFP8と同様の構造のものであるが、QFP8との相違点は、半導体チップ1に対する上層コイル1dと下層コイル1cが設けられた位置とこれらのコイルの向きである。

40

#### 【0099】

そして、QFP10の場合にも、そのワイヤ2は、半導体チップ1の正面1aの4つの辺に沿って設けられた複数の電極パッド1fのうち、平面視における上層コイル1dの中心P1と最も近い位置の電極パッド1fに接続されたワイヤ5の延在方向に沿った方向に延在されている。言い換えると、外部配線であるワイヤ2は、半導体チップ1の正面1aの4辺に沿って設けられた複数の電極パッド1fのうち、上層コイル1dの中心P1と最

50

も近い位置の電極パッド 1 f に接続されたワイヤ 5 と同一の方向に延在されている。

**【 0 1 0 0 】**

図 1 1 に示す構造では、ワイヤ 2 は、上層コイル 1 d の中心 P 1 と最も近い位置の電極パッド 1 f ( S 1 もしくは S 2 ) に接続されたワイヤ 5 の延在方向と同一の方向に延在されている。

**【 0 1 0 1 】**

また、上記第 1 変形例の Q F P 8 と同様に、ワイヤ 2 の長さは、複数のワイヤ 5 のそれぞれの長さより短い。

**【 0 1 0 2 】**

さらに、図 4 に示す半導体チップ 1 と同様に、第 1 回路部 1 g は、平面視で、ワイヤ 2 の一端が接続される上層コイル 1 d の端子 1 d a と、ワイヤ 2 の他端が接続される第 1 回路部 1 g の端子 1 g a と、の間に配置されている。10

**【 0 1 0 3 】**

本第 3 変形例の Q F P 1 0 のその他の構造については、第 1 変形例の Q F P 8 と同様であるため、その重複説明は省略する。

**【 0 1 0 4 】**

本第 3 変形例の Q F P 1 0 によれば、ワイヤ 2 を、最も近い位置の組立て用のワイヤ 5 と同一方向に延在させたことにより、上記第 1 変形例の Q F P 8 と同様に、樹脂モールド時のワイヤ 2 のワイヤ流れ等によるワイヤ倒れやワイヤ歪みを抑制することができ、半導体装置の組立ての容易化を図ることができる。20

**【 0 1 0 5 】**

また、半導体チップ 1 上に配置されるワイヤ 2 の長さが、複数のワイヤ 5 のそれぞれの長さより短いことにより、封止体 6 を形成する樹脂モールドにおけるワイヤ 2 のワイヤ流れの発生をさらに抑制することができる。また、ワイヤ 2 の長さが短いため、ワイヤ 2 の電気的抵抗を低く（小さく）することができ、ワイヤ 2 の電気的特性を向上させることができる。

**【 0 1 0 6 】**

また、ワイヤ 2 を接続する両パッド間に送受信等の回路部である第 1 回路部 1 g を配置することにより、チップ内の空きスペースを有効活用することができ、チップ内における回路部のレイアウトを効率良くすることができる。これにより、半導体チップ 1 の小型化を図ることができる。30

**【 0 1 0 7 】**

本第 3 変形例の Q F P 1 0 によって得られるその他の効果については、上記第 1 変形例の Q F P 8 と同様であるため、その重複説明は省略する。

**【 0 1 0 8 】**

< 第 4 変形例 >

図 1 2 は第 4 変形例の半導体装置の構造を内部を透過して示す平面図である。

**【 0 1 0 9 】**

本第 4 変形例は第 1 変形例と同様の構造の Q F P 1 1 について説明するものである。Q F P 1 1 は、上記第 1 変形例の Q F P 8 と同様の構造のものであるが、Q F P 8 との相違点は、半導体チップ 1 に対する上層コイル 1 d と下層コイル 1 c が設けられた位置とこれらのコイルの向きである。40

**【 0 1 1 0 】**

そして、Q F P 1 1 の場合にも、そのワイヤ 2 は、半導体チップ 1 の正面 1 a の 4 つの辺に沿って設けられた複数の電極パッド 1 f のうち、平面視における上層コイル 1 d の中心 P 1 と最も近い位置の電極パッド 1 f に接続されたワイヤ 5 の延在方向に沿った方向に延在されている。言い換えると、外部配線であるワイヤ 2 は、半導体チップ 1 の正面 1 a の 4 辺に沿って設けられた複数の電極パッド 1 f のうち、上層コイル 1 d の中心 P 1 と最も近い位置の電極パッド 1 f に接続されたワイヤ 5 と同一の方向に延在している。

**【 0 1 1 1 】**

図12に示す構造では、ワイヤ2は、上層コイル1dの中心P1と最も近い位置の電極パッド1f(T1もしくはT2)に接続されたワイヤ5の延在方向と同一の方向に延在されている。

#### 【0112】

また、上記第1変形例のQFP8と同様に、ワイヤ2の長さは、複数のワイヤ5のそれぞれの長さより短い。

#### 【0113】

さらに、図4に示す半導体チップ1と同様に、第1回路部1gは、平面視で、ワイヤ2の一端が接続される上層コイル1dの端子1daと、ワイヤ2の他端が接続される第1回路部1gの端子1gaと、の間に配置されている。

10

#### 【0114】

本第4変形例のQFP11のその他の構造については、第1変形例のQFP8と同様であるため、その重複説明は省略する。

#### 【0115】

本第4変形例のQFP11によれば、ワイヤ2を、最も近い位置の組立て用のワイヤ5と同一方向に延在させたことにより、上記第1変形例のQFP8と同様に、樹脂モールド時のワイヤ2のワイヤ流れ等によるワイヤ倒れやワイヤ歪みを抑制することができ、半導体装置の組立ての容易化を図ることができる。

#### 【0116】

また、半導体チップ1上に配置されるワイヤ2の長さが、複数のワイヤ5のそれぞれの長さより短いことにより、封止体6を形成する樹脂モールドにおけるワイヤ2のワイヤ流れの発生をさらに抑制することができる。また、ワイヤ2の長さが短いため、ワイヤ2の電気的抵抗を低く(小さく)することができ、ワイヤ2の電気的特性を向上させることができ。

20

#### 【0117】

また、ワイヤ2を接続する両パッド間に送受信等の回路部である第1回路部1gを配置することにより、チップ内の空きスペースを有効活用することができ、チップ内における回路部のレイアウトを効率良くすることができる。これにより、半導体チップ1の小型化を図ることができる。

#### 【0118】

本第4変形例のQFP11によって得られるその他の効果については、上記第1変形例のQFP8と同様であるため、その重複説明は省略する。

30

#### 【0119】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明はこれまで記載した実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【0120】

上記実施の形態および各変形例では、下層コイル1cと上層コイル1dのそれぞれ平面形状が、四角形の渦巻き状からなる場合を説明したが、下層コイル1cと上層コイル1dのそれぞれ平面形状は、四角形以外の多角形等の渦巻き状であってもよい。

40

#### 【0121】

上記実施の形態および各変形例では、半導体装置が、SOPもしくはQFPの場合について説明したが、上記半導体装置は、チップ上の第1ワイヤ(ワイヤ2)と、各リード部と接続される複数の第2ワイヤ(ワイヤ5)を有するものであれば、他の半導体装置であってもよい。例えば、SON(Small Outline Nonleaded package)、QFN(Quad Flat Non-leaded Package)等の半導体装置であってもよい。さらに、BGA(Ball Grid Array)等の基板タイプの他の半導体装置であってもよい。

#### 【0122】

さらに、上記実施の形態で説明した技術思想の要旨を逸脱しない範囲内において、変形例同士を組み合わせて適用することができる。

50

## 【符号の説明】

## 【0 1 2 3】

- 1 半導体チップ

1 c 下層コイル

1 d 上層コイル

1 e 層間絶縁膜

1 f 電極パッド

1 g 第1回路部(回路部)

1 h 第2回路部

2 ワイヤ(第1ワイヤ)

3 a インナリード(リード部)

5 ワイヤ(第2ワイヤ)

6 封止体

7 S O P(半導体装置)

10

【図1】

【図3】

【図2】

【 四 4 】

【 図 5 】

【図6】

【 四 8 】

【 7 】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 中柴 康 隆

茨城県ひたちなか市堀口751番地 ルネサスセミコンダクタマニュファクチャリング株式会社

内

(72)発明者 岩垂 史

茨城県ひたちなか市堀口751番地 ルネサスセミコンダクタマニュファクチャリング株式会社

内

審査官 加藤 芳健

(56)参考文献 特開2009-295804(JP,A)

特開2015-8229(JP,A)

特開2002-164214(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60

H01L 21/822

H01L 25/00

H01L 27/04