(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3903960号

(P3903960)

(45) 発行日 平成19年4月11日(2007.4.11)

(24) 登録日 平成19年1月19日(2007.1.19)

(51) Int.C1.

F 1

|             |              |                  |      |      |      |

|-------------|--------------|------------------|------|------|------|

| <b>G09G</b> | <b>5/00</b>  | <b>(2006.01)</b> | G09G | 5/00 | 550M |

| <b>G09G</b> | <b>5/397</b> | <b>(2006.01)</b> | G09G | 5/00 | 510S |

| <b>G09G</b> | <b>5/399</b> | <b>(2006.01)</b> | G09G | 5/00 | 555W |

| <b>HO4N</b> | <b>5/66</b>  | <b>(2006.01)</b> | HO4N | 5/66 | B    |

請求項の数 16 (全 16 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2003-158189 (P2003-158189) |

| (22) 出願日     | 平成15年6月3日 (2003.6.3)         |

| (65) 公開番号    | 特開2004-29783 (P2004-29783A)  |

| (43) 公開日     | 平成16年1月29日 (2004.1.29)       |

| 審査請求日        | 平成15年11月12日 (2003.11.12)     |

| (31) 優先権主張番号 | 10/161965                    |

| (32) 優先日     | 平成14年6月3日 (2002.6.3)         |

| (33) 優先権主張国  | 米国(US)                       |

|           |                                                                  |

|-----------|------------------------------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号                    |

| (74) 代理人  | 100095728<br>弁理士 上柳 雅善                                           |

| (74) 代理人  | 100107076<br>弁理士 藤綱 英吉                                           |

| (74) 代理人  | 100107261<br>弁理士 須澤 修                                            |

| (72) 発明者  | エリック ジェフリー<br>カナダ ブリティッシュ コロンビア リ<br>ッチモンド アルダーストリート 34-<br>6388 |

最終頁に続く

(54) 【発明の名称】画素データをメモリから取出すグラフィックスコントローラ及び装置

## (57) 【特許請求の範囲】

## 【請求項1】

インタリース走査で表示装置に表示するデータを用意するグラフィックスコントローラで、

メモリと、

ビデオデータを受信するラインバッファと、

前記ラインバッファと通信すると共に、受信されたビデオデータを偶数セグメントは偶数フィールドの線のデータに関連付け、奇数セグメントは奇数フィールドの線のデータに関連付け、偶数セグメント及びそれに対応する奇数セグメントで少なくとも1画素分のデータを定義した上で、前記偶数セグメント及びそれに対応する奇数セグメントとして受信データをメモリに格納可能に処理するデータ配列回路と、

前記偶数セグメント及びそれに対応する奇数セグメントを前記メモリへの1回のメモリアクセスで検索する1つのパイプバッファと、

前記1つのパイプバッファからの出力を受信するフリッカーフィルタと、

を含むことを特徴とするグラフィックスコントローラ。

## 【請求項2】

前記データ配列回路はラインバッファカウンタ及びラインカウンタを備え、前記ラインバッファカウンタは前記ラインバッファが線1つの全体のデータを受信することをモニタし、前記ラインカウンタはフレームの線数を数えることを特徴とする請求項1に記載のグラフィックスコントローラ。

**【請求項 3】**

前記データ配列回路はラインカウンタコンパレータを備え、前記メモリへの書き込みが許可されるかを判断するために、前記ラインカウンタが前記ラインカウンタコンパレータに信号を出力することを特徴とする請求項 2 に記載のグラフィックスコントローラ。

**【請求項 4】**

前記データ配列回路はラインバッファカウンタコンパレータを備え、前記ラインバッファカウンタが前記ラインバッファカウンタコンパレータに信号を出力し、前記ラインバッファカウンタコンパレータは 1 本の線全体のデータを受信すると前記ラインバッファカウンタをリセットと共に、前記ラインカウンタを増分させる信号を出力することを特徴とする請求項 2 に記載のグラフィックスコントローラ。 10

**【請求項 5】**

前記ラインバッファがフレームの最初の線のデータで埋められている間、前記データ配列回路がメモリへの書き込みを防止することを特徴とする請求項 1 に記載のグラフィックスコントローラ。

**【請求項 6】**

前記ラインバッファが複数の記憶回路を有するシフトレジスタであることを特徴とする請求項 1 に記載のグラフィックスコントローラ。

**【請求項 7】**

前記複数の記憶回路がクロックドラッチであることを特徴とする請求項 6 に記載のグラフィックスコントローラ。 20

**【請求項 8】**

前記ラインバッファに含まれるクロックドラッチの数は、インタースビデオデータの線 1 本分を格納するのに充分な数であることを特徴とする請求項 7 に記載のグラフィックスコントローラ。

**【請求項 9】**

表示画面にインタース画像の表示を可能にする装置で、

中央演算装置 (CPU) と、

バスと、

前記バスを介して前記 CPU と通信し、画像データを受信するグラフィックスコントローラとを有し、 30

前記グラフィックスコントローラは、

メモリと、

前記画像データを受信するラインバッファと、

前記画像データの偶数セグメント及びそれに対応する奇数セグメントで少なくともデータの 1 画素を定義した上で、前記偶数セグメント及びそれに対応する奇数セグメントとしてメモリに格納可能に前記画像データを処理するデータ配列回路と、

前記メモリへの 1 回のメモリアクセスで前記偶数セグメント及びそれに対応する奇数セグメントを検索する 1 つのパイプバッファと、

前記 1 つのパイプバッファからの出力を受信するフリッカーフィルタと、

を含むことを特徴とする装置。 40

**【請求項 10】**

前記ラインバッファがフレームの最初の線のデータで埋められている間は、前記データ配列回路が前記メモリへの書き込みを防止することを特徴とする請求項 9 に記載の装置。

**【請求項 11】**

前記データ配列回路がさらに、第 1 コンパレータと、前記第 1 コンパレータと通信するラインバッファカウンタと、第 2 コンパレータと、前記第 2 コンパレータと通信するラインカウンタとを備えることを特徴とする請求項 9 に記載の装置。

**【請求項 12】**

前記第 1 コンパレータが、前記ラインバッファカウンタへのリセット信号と共に前記ラインカウンタへの増分信号を送信することを特徴とする請求項 11 に記載の装置。 50

**【請求項 1 3】**

前記データ配列回路がさらに、ANDゲートを備え、前記第2コンパレータが前記ANDゲートに信号を送ると共に当該ANDゲートへの信号がメモリへの書き込みを許可するかどうかを決めることを特徴とする請求項11に記載の装置。

**【請求項 1 4】**

前記ラインバッファがシフトレジスタであることを特徴とする請求項9に記載の装置。

**【請求項 1 5】**

前記ラインバッファが複数のフリップフロップ回路を備え、この複数のフリップフロップ回路がインタースピデオのデータの線1本を格納するのに充分であることを特徴とする請求項9に記載の装置。 10

**【請求項 1 6】**

前記フリッカーフィルタが偶数セグメント及びそれに対応する奇数セグメントを平均してフリッカーを軽減することを特徴とする請求項9に記載の装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は一般的に画像表示システムに関し、より具体的にはインタース走査によって表示画面に表示する画像データを格納し取出すグラフィックスコントローラ及び装置に関する。 20

**【0002】****【従来の技術】**

テレビは家庭における娯楽の中心になっている。またテレビの機能も常に増え続けている。最近、コンピュータとテレビとの境界がはっきりしなくなるにつれ、テレビはコンピュータの特性をより備えるようになり、逆にコンピュータもテレビの特性をより備えるようになってきている。加えてテレビはアナログ処理からデジタル処理に移行しつつある。両デバイスが互いに近似するにつれ、そのシステムに対する要求は増加してきている。このようにより多くのデータがシステムによって処理され、システムメモリへの要求も増加していくと、画像が損なわれるのを防ぐためにより高い帯域が必要となる。さらにテレビ装置における表示品質及び解像度は常に向上しており、これがさらなる処理要求をシステムに課している。 30

**【0003】**

テレビの表示画面上に提示される画像は、明るい帯域と暗い帯域に分離されることなく、全体に均一な明るさを確保するためにインタース走査が用いられる。すなわち、各静止画は、交互に配置された2つの走査によって構成される。例えば偶数番目の線が走査され、その後に奇数番目の線が走査されることで1フレーム分のデータを定義する偶数番・奇数番のすべての線が完全に走査される。

**【0004】**

隣接する走査線で色が急変すると、テレビ画面で表示した際にフリッカーが発生する。すなわち全国テレビジョン方式委員会(NTSC)のモニタ画面の場合、より輝度の高い画素又は水平方向の画素群が、その上下でより輝度の低い画素と隣接するとフリッカーを発生する。フリッカーは人の目に良くないと同時に表示品質を悪くする。テレビの場合は、帯域幅の問題から、フレーム繰返し率を2分の1に減らして、一垂直走査毎に半分の線を走査するインタース走査が採用されている。従って、各フレームは、2回の垂直走査により、偶数番目と奇数番目の線が交互のフィールドに分けて走査される。 40

**【0005】**

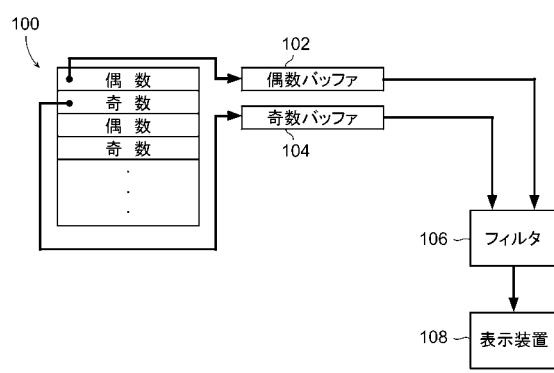

図1は画像データをテレビのメモリに格納するシステムの概略図である。画像データは、データと相互に作用するソフトウェアが使い易いように偶数線と奇数線が交互にメモリ100に格納される。奇数線のデータと偶数線のデータには、それぞれ別々のメモリアクセスが必要となる。つまり偶数線のデータを取出して偶数バッファ102に入れるために1回のメモリアクセスを行ない、奇数線のデータを取出して奇数バッファ104に入れるた 50

めにもう一回メモリアクセスが行なわれる。その後、偶数線及び奇数線はフリッカーフィルタ106により平均化され、最終的に1つの線として表示装置108に出力される。このように、表示データの1画素を出力するためには、偶数線と奇数線のデータを2つのバッファ各々から取得し平均するという、2回のメモリアクセスが必要となる。

#### 【0006】

他のデバイスもメモリを使用する場合、バッファからの複数回の取出しは、メモリの負担を大きくする。そうなるとデータ要求についていくためには、メモリは高帯域幅が必要となる。メモリがデータの要求に対応できなくなると、その結果、表示装置上に損なわれた画面である不可解な表示、つまり破損画像が生成される。さらにテレビ装置において視聴者が利用できる機能がさらに強化され、同時にテレビメーカーが高品位テレビを採用するようになるとメモリへの要求はさらに大きなものになる。従って、このような要求に対応するためには、画像破損を避けるためのメモリ容量の増加や電力消費の増加というように対応コストが発生することになる。10

#### 【0007】

##### 【特許文献1】

米国特許第6,067,120号明細書

##### 【特許文献2】

米国特許第6,081,303号明細書

#### 【0008】

##### 【発明が解決しようとする課題】

従って画像の品質を維持しながらメモリの負担を軽減し、インターレース走査によって表示を出力するシステム用のグラフィックスコントローラ及び装置を提供するためには、従来技術の問題を解決する必要がある。20

#### 【0009】

##### 【課題を解決するための手段】

概して本発明は、メモリにデータを格納しそこから取出すグラフィックスコントローラを提供することによって上記の用件を満たすものである。本発明はシステムとして、あるいはデバイスとして、といったように様々な方法で実施することができる。以下に本発明の創意に富んだ実施例をいくつか説明する。

#### 【0010】

本発明のグラフィックスコントローラは、インターレース走査で表示装置に表示するデータを用意するグラフィックスコントローラで、30

メモリと、

ビデオデータを受信するラインバッファと、

前記ラインバッファと通信すると共に、受信されたビデオデータを偶数セグメントは偶数フィールドの線のデータに関連付け、奇数セグメントは奇数フィールドの線のデータに関連付け、偶数セグメント及びそれに対応する奇数セグメントで少なくとも1画素分のデータを定義した上で、前記偶数セグメント及びそれに対応する奇数セグメントとして受信データをメモリに格納可能に処理するデータ配列回路と、

前記偶数セグメント及びそれに対応する奇数セグメントを前記メモリへの1回のメモリアクセスで検索する1つのパイプバッファと、40

前記1つのパイプバッファからの出力を受信するフリッカーフィルタと、

を含むことを特徴とする。

#### 【0011】

また、本発明の装置は、表示画面にインターレース画像の表示を可能にする装置で、

中央演算装置(CPU)と、

バスと、

前記バスを介して前記CPUと通信し、画像データを受信するグラフィックスコントローラとを有し、

前記グラフィックスコントローラは、50

メモリと、

前記画像データを受信するラインバッファと、

前記画像データの偶数セグメント及びそれに対応する奇数セグメントで少なくともデータの1画素を定義した上で、前記偶数セグメント及びそれに対応する奇数セグメントとしてメモリに格納可能に前記画像データを処理するデータ配列回路と、

前記メモリへの1回のメモリアクセスで前記偶数セグメント及びそれに対応する奇数セグメントを検索する1つのパイプバッファと、

前記1つのパイプバッファからの出力を受信するフリッカーフィルタと、

を含むことを特徴とする。

#### 【0014】

10

本発明の他の特徴及び利点は以下の詳細な説明及びそれに伴い本発明の原理を例示する添付図面で明らかにされる。

#### 【0015】

##### 【発明の実施の形態】

インタレス走査で提示される画像データにおいて、画像データを効率的に格納し、メモリの負担を増やすことなく画像データを迅速に取出すことを可能にする装置及び方法に関する発明が説明される。以下の説明から本発明は以下の具体的な内容の一部あるいはすべてがなくても実施することができることは当業者であれば明らかであろう。また本発明を必要に不明確にしないよう、公知の処理操作は詳しく説明していない。

#### 【0016】

20

本発明の実施例はインタレス走査によって画像を表示するように構成されたシステムに、画素データをメモリから取出す装置及び方法を提供するものである。受信されたビデオデータは、インタレス走査用1フレーム分のデータとして交互する偶数線及び奇数線のセグメントとして格納される。1実施例においては、ある偶数線の16ビットのセグメントと対応する奇数線の16ビットのセグメントがペアとしてメモリに格納される。この偶数線及び奇数線は、1フレームのデータにおいて隣接する線である。受信されたビデオデータを交互に偶数セグメント及び奇数セグメントとして格納することによって、表示パイプによる1回のメモリアクセスで1画素分のデータを取出すことができる。すなわち本発明の1実施例においては、32ビットのバスを経由して1回のメモリアクセスをすることにより、16ビットの偶数セグメント及び16ビットの奇数セグメントを取得する。その結果表示パイプのメモリに対する負担は相当軽減される。

30

#### 【0017】

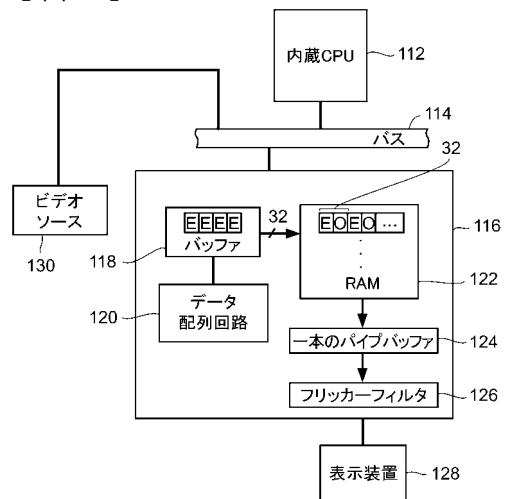

図2はインタレス走査により表示装置に提示されるデータを用意するように構成された本発明の1実施例におけるグラフィックスコントローラの概略図である。中央演算装置(CPU)112は、バス114経由でグラフィックスコントローラ116と通信する。ビデオソース130は、グラフィックスコントローラ116が処理し表示装置128に表示されるビデオ画像データを供給する。1実施例では、CPU112の指示に従い、ビデオ画像が外部ソースからグラフィックスコントローラ116に供給される。別の実施例では、ビデオ画像が有線テレビあるいは衛星のソースなどからライブで直接グラフィックスコントローラ116に供給される。グラフィックスコントローラ116は、32ビットバス経由でランダムアクセスメモリ(RAM)122と通信する1つのラインバッファ118を備えている。RAM122をバッファ118に接続するバスは、32ビットのバスサイズに限定されるものではなく、適切であればどのようなバスサイズでも良い。データ配列回路120はバッファ118と通信する。データ配列回路は以下により詳しく説明される通りビデオデータを処理し、データを交互に偶数セグメントそして奇数セグメントとしてRAM122に格納できるよう構成されている。1実施例では、偶数セグメント及び奇数セグメントが各々16ビットのセグメントで、組み合わせたセグメントサイズが32ビットとなる。偶数セグメントは偶数線に対応し、奇数セグメントは奇数線に対応する。ここで偶数セグメントと奇数セグメントの各ペアは、各々隣接する偶数線及び奇数線に対応する。従って偶数セグメント及び奇数セグメントの各ペアは1画素分のデータを定義する。

40

50

ビデオ画像データを16ビットの偶数と奇数の交互するデータ量として格納することによって、1つのパイプバッファ124が1回のメモリアクセスで1画素分のデータを取出すことが可能になる。つまり32ビットの取出し1回で偶数及び奇数の画素データが取得される。1つのパイプバッファ124が取出した偶数及び奇数の画素データはフリッカーフィルタ126に転送される。公知のように、フリッカーフィルタ126は、表示線間のコントラストを滑らかにするために、隣接する線のデータを平均することによってインターレース走査によるフリッカーを軽減する。引き続いてフリッカーフィルタのデータはテレビ(TV)の表示画面などのインターレース走査により画像を表示する表示画面に表示するために表示装置128に出力される。

## 【0018】

図2において、CPU112は、ビデオソース130からビデオデータをバス114経由でグラフィックスコントローラ116に送信する命令するコードを備えたデジタルシグナルプロセッサ(DSP)であっても良いことは当業者であれば理解しよう。さらにCPU112は、内蔵システムの1つの要素であっても良い。1実施例では、バッファ118は、線1本分の偶数データ又は奇数データを保持するサイズになっている。バッファ118は、受信するビデオ画像データを格納し、そのデータをRAM122に転送するためにラッチ、フリップフロップなどの適当な記憶回路を備えている。データ配列回路は、受信したビデオデータをバッファ118に移し、適切な偶数セグメント及び奇数セグメントをRAM122に転送するために論理ゲート、カウンタ、コンパレータ、レジスタなどの回路を備えている。1実施例では、バッファ118は、ビデオソース130から受信するビデオデータの線を1つ格納するのに適した複数のクロックドラッヂあるいはフリップフロップからなるシフトレジスタである。ビデオソース130から受信されるビデオデータはインターレースの形で入る。すなわち受信ビデオデータは、隣接する偶数線及び奇数線で送信される。

## 【0019】

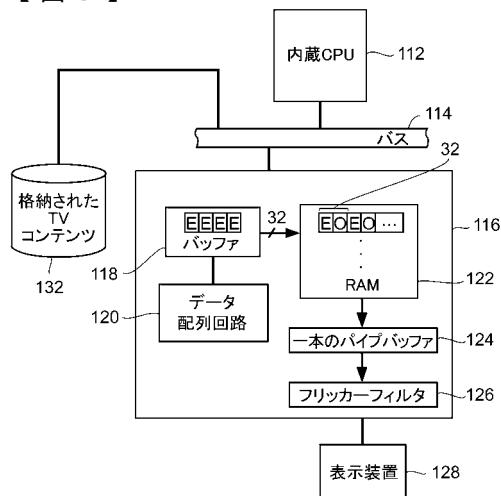

図3は図2におけるグラフィックスコントローラで、ビデオ画像データが、格納されたテレビ(TV)コンテンツから供給される場合の概略図である。格納されたTVコンテンツ132は、デジタルテレビあるいは高品位テレビに関連した適当なTVコンテンツであれば何でも良い。例えば格納されたTVコンテンツは、デジタルビデオレコーダに関連するようなハードドライブに格納されたデータでも良い。図2と同様に、CPU112は、格納されたTVコンテンツ132をグラフィックスコントローラ116に送り込む。グラフィックスコントローラ116は、格納されたTVデータを図2で説明したように処理する。すなわち、TVデータを交互する偶数セグメント及び奇数セグメントのペアとしてRAM122に格納することによって、1つのパイプバッファ124が1回の取出しで1画素分のデータを取得することができる。従来は32ビット画素のデータを出力するためには2回の取出しが必要であったのに対し、このように32ビットの画素データを出力するためにRAM122へのメモリアクセスは1回しか必要としないので、1つのパイプバッファ124のRAM122への負担は約50%軽減される。

## 【0020】

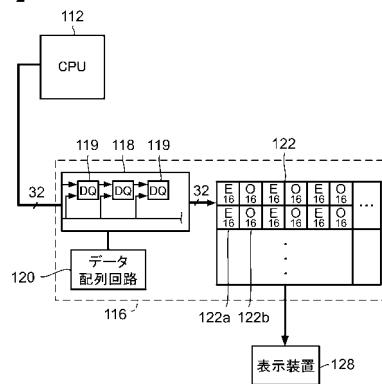

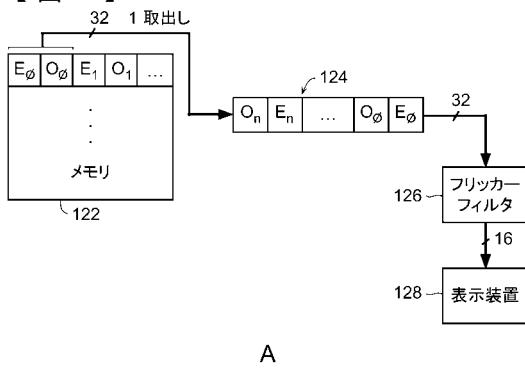

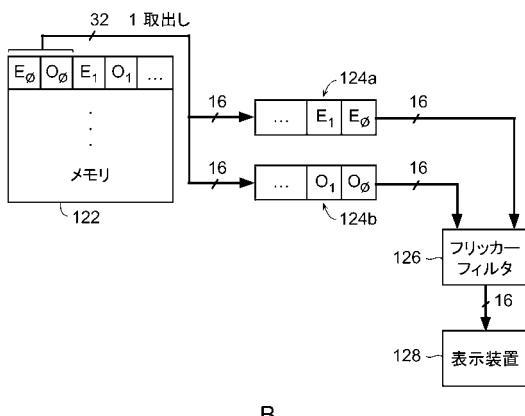

図4Aは、受信したビデオ画像を本発明の1実施例におけるグラフィックスコントローラのメモリに交互に偶数セグメント及び奇数セグメントとして格納した場合の概略図である。CPU112は、32ビットのバス経由でビデオ画像データをグラフィックスコントローラ116に送り込む。インターレースのビデオ画像データはラインバッファ118に入力される。図中示されるように、ラインバッファ118は、フリップフロップ119などの1列の記憶回路を備えるシフトレジスタで、デジタルデータが順に右へシフトすることを可能にする。1実施例では、ラインバッファ118におけるフリップフロップ119の数は、表示装置128用の線1本分のデータを保持するに適した数である。ラインバッファ118の適切なサイズは色々である。例えば表示装置128が表示する各水平走査線1本に480の画素を有するテレビ画面の場合は、ラインバッファ118は480の画素(線1本分)を保持できるだけのフリップフロップ119を備えることになる。上述の通り

10

20

30

40

50

、データ配列回路 120 は、バッファ 118 で受信するビデオデータを、交互に偶数セグメント及び奇数セグメントとして RAM 122 に格納するためのハード的にコード化された命令を備えている。データ配列回路 120 については図 4B でさらに詳しく説明する。1 実施例では、一旦受信ビデオデータの線 1 本分が完全にラインバッファ 118 に入ると、最初の偶数セグメントは最初の奇数セグメントとともにラインバッファ 118 から RAM 122 にシフトされる。この偶数セグメント及び奇数セグメントは、インターレースデータの隣接する線に対応している。この作業は受信ビデオデータの各線に対し繰り返される。

#### 【0021】

さらに図 4Aにおいて、RAM 122 は交互する偶数セグメント及び奇数セグメントの 16 ビットデータとしてそのデータを格納していることを示している。1 実施例として、交互する 16 ビットの偶数セグメントと奇数セグメントの各ペアが 1 画素を定義している。すなわち偶数の 16 ビットデータ 122A とこれに対応する奇数の 16 ビットデータ 122B で 1 つの画素を定義している。図中 RAM 122 に格納されるデータは、偶数データの後に奇数データが続くように示されているが、各画素を定義するパターンが知られている限り RAM 122 におけるデータの順は重要でないことは当業者であれば理解できよう。図 4A では偶数データが偶数線を表し、対応する奇数データは隣接する奇数線を表しているが、1 画素のデータを定義するものであれば別のパターンで格納してもよい。例えば、2 本の線ではなく 3 本の隣接する線のセグメントの平均が使用される場合は、交互する偶数及び奇数のセグメントは 10 ビットのセグメントとなる。すなわち RAM 122 には、交互する偶数セグメント及び奇数セグメントからなる 3 つのデータが格納される。この場合、32 ビットの取出しを 1 回行なうと、1 画素のデータ取出しに 2 ビットの無効データが含まれることになる。偶数データ及び奇数データの交互するセグメントを格納するパターンは、バッファ 118 が少なくともある一定のサイズであることを必要とすることは当業者には明らかであろう。例示的な目的から、図 4A は交互の偶数及び奇数セグメントを論理的な配列で表示している。RAM 122 におけるデータの物理的配列は論理的配列と異なり得ることは当業者に明らかであろう。

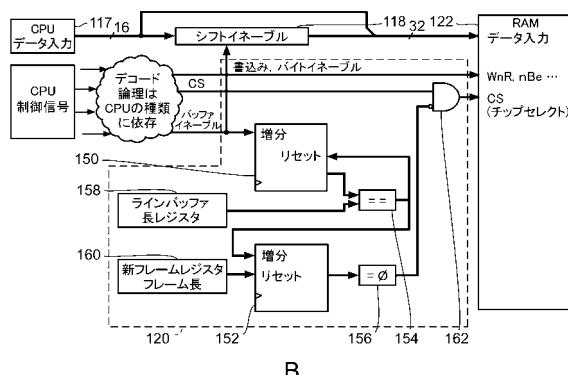

#### 【0022】

図 4B は、交互の偶数セグメント及び奇数セグメントをメモリに格納するように構成された本発明の 1 実施例におけるグラフィックスコントローラのデータ配列回路の要素を示す概略図である。CPU データ 117 は、ラインバッファ 118 で受信される。データ配列回路 120 は、CPU データが偶数セグメント及び奇数セグメントとしてメモリに格納できるように CPU データ 117 を処理する。CPU データ 117 がグラフィックスコントローラに受信されながらデータはラインバッファ 118 に配列される。1 実施例では、ラインバッファ 118 はシフトレジスタである。シフトレジスタにシフトイネーブル信号が通信されると、さらにデータが入るとデータをシフトするようにシフトレジスタが指示を受ける。1 実施例では、シフトイネーブル信号がラインバッファ 118 の各ラッチあるいはフリップフロップに送信される。従って、シフトイネーブル信号がハイでアクティブの場合、シフトイネーブルがクロックサイクルにおいてハイの場合は、すべてのラッチあるいはフリップフロップがシフトされる。しかしシフトイネーブル信号がローの場合はクロックサイクル中には何も起こらない。

#### 【0023】

CPU の制御信号はデコード論理で翻訳される。デコード論理は当然 CPU の種類に依存する。デコード論理とは、例えば RAM 122 のようなメモリにデータを書き込んだり読み出したしたりするためのアドレスを提供するものである。例えばワード線及びビット線のアドレスをデコード論理により提供することができる。1 実施例では、制御信号に書き込み信号、バイトイネーブル信号、チップセレクト (CS) 信号及びバッファイネーブル信号が含まれる。1 実施例において、デコード論理はグラフィックスコントローラの RAM 122 インタフェースに所在していることは当業者には明らかであろう。

#### 【0024】

10

20

30

40

50

図4Bにおけるラインバッファカウンタ150は、ラインバッファ118の受信したデータを数える。すなわち新しいデータがラインバッファ118にシフトする毎にラインバッファカウンタ150が増分する。上述の通り、インタレース走査の場合、1フレームのデータは複数の偶数線及び奇数線からなる。線長は例えばラインバッファ長レジスタ(RegLineBufferLength)158などのレジスタに記憶される。ラインバッファカウンタ150は、データをコンパレータ154に出力する。コンパレータ154は、ラインバッファカウンタ150からのデータをRegLineBufferLength158からの線長と比較して、ラインバッファ118が1本の線で一杯になったかどうかを判断する。一旦ラインバッファ118が1本分の線データで一杯になると、コンパレータ154はラインバッファカウンタ150にリセット信号を出力し、ラインバッファカウンタは、ラインバッファから次のデータを受信すると、次の線データとしてそのデータのカウントを始める。

#### 【0025】

さらに図4Bにおいて、ラインバッファカウンタ150に加えコンパレータ154からラインカウンタ152にも信号が出力される。ラインカウンタ152はフレームの線数を数え、ラインバッファ118がフレームの最初の線で埋められている最中にメモリ122への書き込みを防ぐ。コンパレータ156は、ラインカウンタ152からの出力を比較してラインカウンタがゼロであるか、すなわちラインバッファ118が最初の線を受信しているかを判断する。このようにラインカウンタ152がゼロの場合、ラインバッファ118にフレームの最初の線が埋められている最中はメモリへの書き込みは許可されない。1実施例では、ANDゲート162がチップセレクト(CS)信号をローで出力しメモリへの書き込みを防止している。ラインカウンタ152が増分すると、つまりラインバッファ118に1線分のデータが埋まり終わると、メモリへの書き込みが許可される。すなわち一旦ラインカウンタ152がゼロから増分するとコンパレータ156からの出力はハイになり、ANDゲート162への入力がハイとなることでANDゲート162の出力もハイとなる。その後CPUの各書き込みでは、CPUからのデータ及びラインバッファ118からのデータがメモリに書き込まれる。言うまでもなく、交互の偶数セグメント及び奇数セグメントといったCPUからのデータ及びラインバッファ118からの書き込みデータの機構は、データのフリッカーをフィルタリングする方法に依存する。データのフリッckerをフィルタリングする代表的な方法については図8A-8Cで検討する。上記説明では信号がハイでアクティブであるが、信号がローでアクティブとなるように回路を設計することもできることは当業者には明らかであろう。ここで1実施例において、データの奇数セグメント及び偶数セグメントがメモリ122に書き込まれ交互するペアとして格納されているのは、図8A及び8Bに示すフリッckerをフィルタする機構に対応するためである。

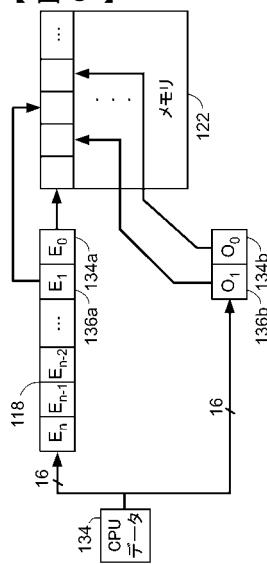

#### 【0026】

図5は、本発明の1実施例において、データを交互の偶数セグメント及び奇数セグメントとしてメモリに書き込む処理を示す概略図である。CPUデータ134はラインバッファ118に書き込まれる。上述のように、ラインバッファ118はシフトレジスタの役割を果たす。すなわちE<sub>0</sub>ないしE<sub>n</sub>で表される最初の線データの各偶数セグメントがラインバッファ118に受信されると、ラインバッファ内の各セグメントは位置を1つ分だけ右にシフトする。1実施例では、ラインバッファ118が画像データのインタレース走査線の1本分に対応するセグメント数を保持できるサイズになっている。1実施例では、E<sub>0</sub>134aの中身がメモリ122に書き込まれるようになっている。対応する奇数セグメントのデータO<sub>0</sub>は、メモリ122内でE<sub>0</sub>134aとペアになる。E<sub>0</sub>134aがラインバッファ118の外にシフトされると、E<sub>1</sub>136aが位置を1つ分右にシフトするということを当業者は理解するであろう。次にE<sub>1</sub>136aがメモリ122に書き込まれる。同様に偶数セグメントE<sub>1</sub>136aに対応する奇数セグメントO<sub>1</sub>136bがメモリ122に書き込まれる。この処理はインタレース画像の偶数線及び奇数線で表される各画素が、偶数データ及び奇数データの交互するセグメントとしてメモリ122に配列されるまで続けられる。ここでデータ配列回路は偶数セグメント及び奇数セグメントを交互にペアとしてメモリに配列することを可能にしており、各ペアはインタレース走査の隣接する線からのデータを

表している。図 6 B でさらに詳しく説明するが、2 本以上の隣接する線のデータを交互のセグメントとして、各セグメントの組み合わせが画像画面に表示される 1 画素分のデータとなるようにメモリに配列することができる。

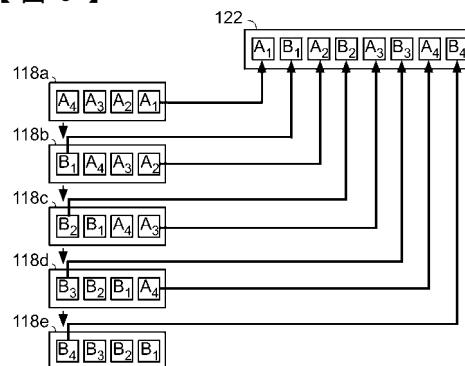

#### 【 0 0 2 7 】

図 6 A は本発明の 1 実施例により、データを偶数及び奇数データの交互するセグメントとしてメモリに書き込む処理を示した図である。例示的に、A<sub>1</sub> ~ A<sub>4</sub> は偶数線のセグメントを表し、B<sub>1</sub> ~ B<sub>4</sub> は奇数線のセグメントを表すとする。放映データや格納されたテレビコンテンツなどのビデオソースから、偶数線の各セグメントがバッファ 118 a に配列される。セグメント A<sub>1</sub> がメモリ 122 に書き込まれ、奇数セグメント B<sub>1</sub> がラインバッファ 118 b のように配列されるように、残りのセグメント (A<sub>2</sub> ~ A<sub>4</sub>) は右にシフトする。そして奇数セグメント B<sub>1</sub> もメモリに書き込まれる。ここでセグメント A<sub>1</sub> 及びセグメント B<sub>1</sub> は 1 回の 32 ビットの書き込み、すなわち 1 回のメモリアクセスでメモリ 122 に書き込まれる。さらに奇数セグメント B<sub>1</sub> は対応する偶数セグメント A<sub>1</sub> と対になる。ここでセグメント A<sub>1</sub> 及び B<sub>1</sub> はインターレース走査の隣接する線からのセグメントである。次に偶数セグメント A<sub>2</sub> がメモリ 122 に書き込まれ、奇数セグメント B<sub>2</sub> がラインバッファ 118 c のように配列されるように、残りのセグメント (A<sub>3</sub> ~ A<sub>4</sub>, B<sub>1</sub>) は右にシフトする。そして奇数セグメント B<sub>2</sub> もメモリに書き込まれる。この処理は、偶数線の各セグメント A<sub>1</sub> ~ A<sub>4</sub> と対応する奇数線のセグメント B<sub>1</sub> ~ B<sub>4</sub> がメモリ 122 内で関連付けられるまで上述の如く継続される。この処理はインターレース走査のフレームを構成する偶数線及び奇数線に対し繰り返される。ここでラインバッファ 118 a, 118 b 及び 118 c は、図 5 のラインバッファ 118 がそれぞれ異なる時間帯で異なるセグメントをラインバッファ 118 に格納している状態を示している。10 20

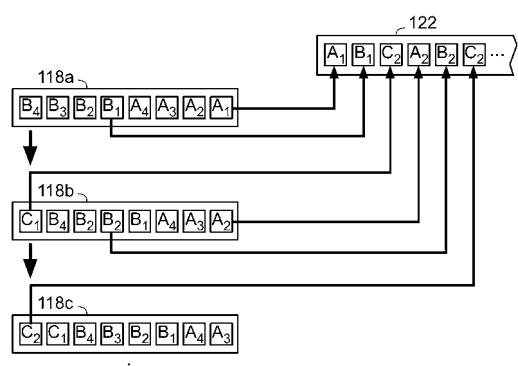

#### 【 0 0 2 8 】

図 6 B は、本発明の 1 実施例である、3 本の連続する線からのセグメントがメモリに格納された状態を示した図である。この場合、セグメント A<sub>1</sub> ~ A<sub>4</sub> 及び B<sub>1</sub> ~ B<sub>4</sub> がラインバッファ 118 a に受信される。セグメント A<sub>1</sub> はメモリ 122 内でセグメント B<sub>1</sub> 及び C<sub>1</sub> と組合わされ、セグメント A<sub>1</sub>, B<sub>1</sub> 及び C<sub>1</sub> で定義される 3 つが 1 画素分のデータを定義する。より具体的には、ラインバッファ 118 a は、セグメント C<sub>1</sub> を受信すると、ラインバッファ 118 b に示すようにシフトする。そしてセグメント A<sub>2</sub> 及び B<sub>2</sub> がメモリ 122 に書き込まれる。次にセグメント C<sub>2</sub> を受信すると、ラインバッファ 118 c に示すように、セグメント C<sub>2</sub> は、A<sub>2</sub> 及び B<sub>2</sub> といっしょに配置される。ここでセグメント A<sub>1</sub>、セグメント B<sub>1</sub> 及びセグメント C<sub>1</sub> は 1 回の 32 ビットの書き込み、すなわち 1 回のメモリアクセスでメモリ 122 に書き込まれる。3 本の連続走査線から対応するデータセグメントの交互の 3 つのデータセットを作成する処理は、インターレース走査のフレームを構成する線に対し繰り返される。1 実施例では、セグメント A<sub>1</sub>, B<sub>1</sub> 及び C<sub>1</sub> が各々 10 ビットのサイズで、合計 30 ビットのビットサイズとなっている。従ってメモリ 122 から 32 ビットの取出しを 1 回行なうと、その内 2 ビットは有効なデータではないので、この無効データは無視される。上述の通りラインバッファ 118 a, 118 b 及び 118 c は図 5 のラインバッファ 118 がそれぞれ異なる時間帯において異なるセグメントをラインバッファ 118 に格納した状態を示している。すなわちラインバッファ 118 a, 118 b 及び 118 c は、ラインバッファ 118 がデータを受信する間の異なった構成のスナップショットである。さらに、図 6 A 及び図 6 B で説明した実施例は、2 本あるいは 3 本より多い連続する線からセグメントを処理するために適応できる。ラインバッファ 118 のサイズはセグメントがメモリに格納されるパターン、すなわち 2 つか、3 つか、等々によって異なるということを当業者は理解するであろう。30 40

#### 【 0 0 2 9 】

図 7 A は本発明の 1 実施例により、1 画素分のデータを取得するための 1 回のメモリアクセスの実行を示した概略図である。ここで偶数セグメント及び対応する奇数セグメントは図 4、図 5、図 6 A で説明した通り、メモリ 122 に格納され、それにより表示パイプ 124 が 1 回のメモリアクセスで 1 画素分のデータを取出すことができる。つまり表示50

パイプ 124 とメモリ 122との間の 32 ビットバスを介して、1回のメモリアクセスで 1 画素分のデータを取出す。すなわち、偶数セグメント及び奇数セグメントのデータを交互にメモリに格納することによって、複数回のメモリアクセスではなく 1 回のメモリアクセスで 1 画素分のデータの取出しが可能になる。表示パイプ 124 は、フリッカーフィルタ 126 と通信している。フリッカーフィルタ 126 は、インタレース走査画像に係わるフリッカーを最小限にするために、対応する偶数セグメント及び奇数セグメントを平均するものであることは当業者であれば理解するであろう。フィルタを通過した画素データはその後表示画面 128 に表示される。1 実施例では、表示画面 128 は、例えばテレビ画面など、インタレース走査を表示するよう構成されている。

## 【0030】

10

図 7B は、図 7A の 1 本の表示パイプに対し、フリッカーフィルタに 2 本の表示パイプが供給された場合の構成である。ここでも 1 回のメモリアクセスで 1 画素分のデータを取出している。しかし、1 回のメモリアクセスによって偶数セグメントは表示パイプ 124a に誘導され、奇数セグメントは表示パイプ 124b に誘導される。対応する偶数セグメント及び奇数セグメントは、16 ビットのバスを経由してフリッカーフィルタ 126 に入力される。フリッカーフィルタ 126 は、図 7A で説明した通り、データを平均化する。平均化されたデータは続いて表示画面 128 で表示される。ここで 1 回の取出しで 1 画素分のデータが取得できるので、メモリ 122 に対する表示パイプ 124 の負担が軽減される。

## 【0031】

20

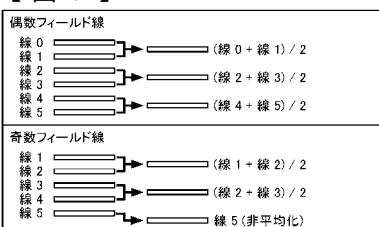

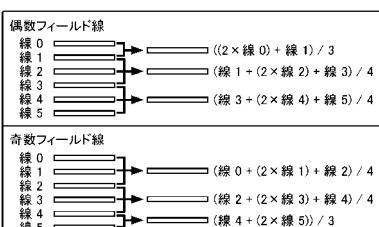

図 8A は、本発明の 1 実施例において、インタレース走査によって表示される画像データに対してフリッカーをフィルタリングする方法を示した概略図である。フリッカーをフィルタリングするとは、インタレース走査の隣接線間のコントラストが原因となるフリッcker を軽減するものであることは当業者であれば理解するであろう。偶数フィールドの線（フィールド 0）は線 0 から始まり、線の各ペアを平均化する。例えば、線 0 と線 1 が平均されて偶数フィールドの最初の線が生成され、次に線 2 と線 3 が平均されて偶数フィールドの 2 番目の線が生成され、・・・以下同様である。奇数フィールドの線（フィールド 1）は線 1 から始まり、線の各対を平均化する。例えば、線 1 と線 2 が平均され奇数フィールドの最初の線が生成され、次に線 3 と 4 が平均され奇数フィールドの 2 番目の線が生成され、・・・以下同様である。このようにフィールド 0 における最初の表示線は線 0 の情報を持んでいるが、フィールド 1 における最初の表示線は線 0 の情報を含んでいない。本発明の 1 実施例では、図 4B におけるデータ配列回路が上記説明のフリッcker をフィルタする方法に対応するよう構成されている。

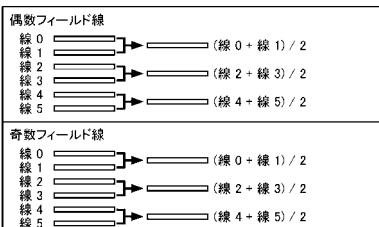

## 【0032】

30

図 8B は、本発明の 1 実施例における、インタレース走査によって表示される画像に対するフリッcker をフィルタリングする別のアルゴリズムを示した概略図である。この場合、フリッcker をフィルタリングする方法は同量の情報を含む偶数フィールドと奇数フィールドから線を生成する。具体的には偶数フィールドは奇数フィールドとともにフレームの線 0 から始まり、各ペアとなる線を平均化する。例えば線ゼロと線 1 が平均され偶数フィールド及び奇数フィールドの最初の線を定義する。同様に線 2 と線 3 が平均され偶数フィールド及び奇数フィールドの 2 番目の線を定義する。以下同様である。従って偶数フィールド及び奇数フィールド双方における最初の表示線は同量の情報を含むことになる。フィルタリングされた偶数線とフィルタリングされた奇数線を同一にすることにより、インタレース方式で表示されるフリッcker の無い画像が表示画面に向かって生成される。

## 【0033】

40

図 8C は、本発明の 1 実施例において、インタレース方式で表示するコンピュータ生成画像の偶数フィールド線及び奇数フィールド線のフリッcker をフィルタリングするさらに別の方法を示す概略図である。この場合、偶数線及び奇数線を生成するために複数線の重み付け平均が使用される。例えば、最初の偶数フィールド線は線 0 と線 1 の重み付き平均である。すなわち線ゼロのデータを 2 倍にして線 1 のデータに加え、合計を 3 で割って最初

50

の偶数フィールド線を得る。図で示される通り 2 番目の偶数フィールド線は線 2 を 2 回数えて線 1、2 及び 3 の重み付き平均を計算している。奇数フィールド線も同様に計算されるが、最初の奇数フィールド線は最初の線 3 本の重み付き平均を取る。以下同様である。結果として得られるフィルタされた偶数フィールド線及び奇数フィールド線の組み合わせで表示されたインターレース画像は、複数線の重み付き平均により際立った変化及びコントラストが和らげられる。フリッカーフィルタリングのアルゴリズムは多種あり、本発明は図 8 A - 8 C について説明したフリッカーフィルタリングのアルゴリズムに限定されるものではない。各々異なるフリッカーフィルタリングのアルゴリズムは異なる方法で画素データを平均化するが、偶数セグメントと奇数セグメントを交互にメモリに格納することによって、フリッカーフィルタへのデータの供給が 1 回のメモリアクセスで可能になる。

10

#### 【0034】

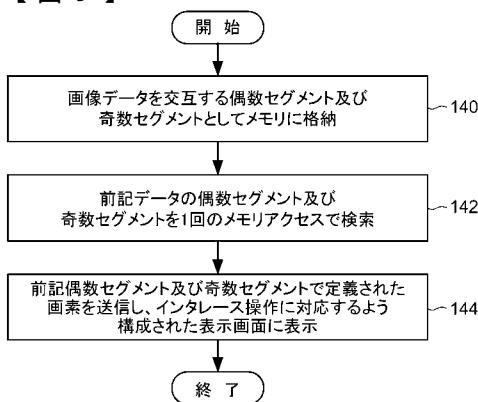

図 9 は、本発明の 1 実施例において、インターレース走査に対応する表示画面に画像データを表示するための操作方法を示すフローチャートである。この方法は操作 140 から始まり、メモリ内の画像データが、交互する偶数セグメント及び奇数セグメントとして格納される。ここでは各偶数セグメントと奇数セグメントのペアが画素を定義している。例えば、偶数セグメントと奇数セグメントがともに 16 ビットセグメントであれば、図 4 及び図 5 で説明した通り、偶数セグメントと奇数セグメントのペアは 32 ビットの画素を定義することになる。1 実施例では、データ配列回路によって交互する偶数セグメント及び奇数セグメントのペアをグラフィックスコントローラのメモリに格納することが可能になっている。図 9 における方法の操作を実行するのに適したグラフィックスコントローラは図 2 及び図 3 で説明した。次に操作 142 に進み、データの偶数セグメント及び奇数セグメントがともに 1 回のメモリアクセスで検索される。すなわち図 7 A 及び図 7 B について言えば、1 つあるいは複数の表示パイプから、1 回の取出しで偶数セグメント及び奇数セグメントのデータが取得される。ここで偶数セグメントのデータ及び奇数セグメントのデータは各々互いに隣接する偶数線及び奇数線に対応するものである。より具体的には、データをフィルタリングしてフリッカーを最小限にする又は実質的に除去するために、偶数セグメント及び奇数セグメントは同様に互いに隣接する画像データに対応している。

20

#### 【0035】

図 9 の方法は次に操作 144 に進み、1 回のメモリアクセスで検索した偶数セグメント及び奇数セグメントのペアで定義される画素が送信されインターレース走査に対応する表示画面で表示される。1 実施例では、偶数セグメント及び奇数セグメントのペアが、表示のために送信される前にフリッカーのフィルタリングがされる。加えて、フリッカーフィルタリングの機構は、図 8 A - 8 C で説明した通り、フレームの複数線の対応セグメントの平均を含むこともできる。同様に画素は 2 本より多い隣接線からのデータで定義することもできる。例えば前述のように、3 本の連続する線からのセグメントを使用して画素を定義することもできる。図 2 - 図 4 A 及び図 5 は、メモリに格納された画像データの交互する一対あるいは 3 つを論理的に表したものである。

30

#### 【0036】

#### 【発明の効果】

要約すると、上記の実施例は 1 画素のデータを定義する偶数セグメント及び奇数セグメントを 1 回のメモリアクセスで取出し、インターレース走査として表示することを可能にする。セグメントを交互に格納することにより偶数セグメント及び奇数セグメントがともにフリッカーフィルタに供給され平均化されるようにデータを取り込むことができる。

40

#### 【0037】

上述の発明は表示画面に画像を表示するためにインターレース走査を使用する表示システムであればどのようなものにおいても実施できる。上記実施例に留意しつつ、本発明はコンピュータシステムに格納されたデータにかかる各種のコンピュータに実行される操作を使用できることを理解することが必要である。これらの操作は物理的な量を物理的に処理する必要のあるものである。必須ではないが通常これらの量は格納、転送、組み合わせ、比較、及びその他処理可能な電気あるいは磁気信号の形を取る。さらに実施さ

50

れる処理はしばしば作成、識別、判断、あるいは比較といった用語で引き合いにされる。

**【0038】**

本発明はコンピュータの読み取り可能な媒体上におけるコンピュータの読み取り可能なコードとして実施することもできる。コンピュータの読み取り可能媒体とは後でコンピュータシステムが読み取りできるデータを記憶する事のできるデータ記憶媒体であれば何でも良い。コンピュータが読み取りできる媒体の例としてはハードドライブ、ネットワーク上の記憶装置 (N A S = network attached storage)、読み出し専用メモリ、ランダムアクセスメモリ、C D - R O M , C D - R , C D - R W , 磁気テープ、及びその他光学的、非光学的データ記憶装置が含まれる。コンピュータが読み取りできる媒体はネットワークで連結されたコンピュータシステムに分散されることも可能で、この場合はコンピュータが読み取りできるコードは分散された形で格納され実施される。10

**【0039】**

上述の発明は明快に理解できるようかなり詳細に説明されているが、添付クレームの範囲内でいくらかの変更及び修正を実施できることは上述の説明からも明らかであろう。従って本実施例は例示的とみなされ、限定するものではない。本発明は本明細書内に述べられた内容に限定されるものではなく、添付クレームの範囲内及び同等のものにおいて修正することができる。

**【図面の簡単な説明】**

**【図1】** 画像データをメモリに格納する従来のシステム。

**【図2】** 本発明の1つの実施例によるグラフィックスコントローラの概略図。20

**【図3】** 図2のグラフィックスコントローラに、ビデオ画像データが供給された場合の概略図。

**【図4】** A 受信したビデオ画像をグラフィックスコントローラのメモリに交互に偶数セグメント、奇数セグメントとして格納した場合の概略図。

B グラフィックスコントローラのデータ配列回路の要素を示す概略図。

**【図5】** データを偶数セグメント、奇数セグメントとしてメモリに書き込む処理を示す概略図。

**【図6】** A データを偶数・奇数データの交互するセグメントとしてメモリに書き込む処理を示す図。

B 3本の連続する線のセグメントがメモリに格納された状態を示す図。30

**【図7】** A 1画素分のデータ1回のメモリアクセスで実行する場合の概略図。

B フリッカーフィルタに2本の表示パイプが供給された場合の概略図。

**【図8】** A 画像データがインタ雷斯走査によって提示されるようにフリッカーをフィルタする方法を示す概略図。

B 別のフリッカーフィルタ用アルゴリズムを示す概略図。

C インタ雷斯の形で提示するコンピュータ生成画像の偶数、奇数フィールド線のフリッカーをフィルタする別の方法を示す概略図。

**【図9】** インタ雷斯走査に対応する構成の表示画面に画像データを提示するための操作方法を示すフローチャート。

**【符号の説明】**

100 メモリ

102 偶数バッファ

104 奇数バッファ

106、126 フリッカーフィルタ

108、128 表示装置

112 C P U

114 バス

116 グラフィックスコントローラ

117 C P Uデータ

118 ラインバッファ

40

50

1 1 9 フリップフロップ

1 2 0 データ配列回路

1 2 2 R A M

1 2 4 パイプバッファ

1 3 0 ビデオソース

1 3 2 T V コンテンツ

1 5 0 ラインバッファカウンタ

1 5 2 ラインカウンタ

1 5 4、1 5 6 コンパレータ

1 5 8 ラインバッファ長レジスタ

1 6 2 A N D ゲート

10

【図1】

(従来技術)

【図2】

【図3】

【図4】

A

B

【図5】

【図6】

A

B

【図7】

A

B

【図8】

A

B

C

【図9】

---

フロントページの続き

(72)発明者 バリンダー シング ライ

カナダ ブリティッシュ コロンビア サレー 60A アベニュー 12566

審査官 樋口 信宏

(56)参考文献 特開平11-187360(JP,A)

特開2002-140064(JP,A)

特開平09-292969(JP,A)

特開平06-118925(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G5/00-5/42

H04N5/66-5/74

H04N7/00-7/088