## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5580190号 (P5580190)

(45) 発行日 平成26年8月27日 (2014.8.27)

(24) 登録日 平成26年7月18日 (2014.7.18)

| (51) Int.Cl. |         |            | FΙ   |       |      |

|--------------|---------|------------|------|-------|------|

| HO1L         | 21/8242 | (2006.01)  | HO1L | 27/10 | 321  |

| HO1L         | 27/108  | (2006.01)  | HO1L | 27/10 | 441  |

| HO1L         | 27/105  | (2006.01)  | G11C | 17/00 | 623A |

| G11C         | 16/04   | (2006.01)  | G11C | 11/34 | 352B |

| G11C         | 11/405  | (2006, 01) |      |       |      |

請求項の数 2 (全 52 頁)

(21) 出願番号 特願2010-289073 (P2010-289073)

(22) 出願日 平成22年12月27日 (2010.12.27)

(65) 公開番号 特開2011-155255 (P2011-155255A)

(43) 公開日 平成23年8月11日 (2011.8.11)

審查請求日 平成25年9月19日 (2013.9.19)

(31) 優先権主張番号 特願2009-297140 (P2009-297140)

(32) 優先日 平成21年12月28日 (2009.12.28)

(33) 優先権主張国 日本国 (JP)

||(73)特許権者 000153878

株式会社半導体エネルギー研究所 神奈川県厚木市長谷398番地

∥(72)発明者 塩野入 豊

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

|(72)発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 加藤 清

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 小山 満

最終頁に続く

# (54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

## 【請求項1】

第1のトランジスタと、第2のトランジスタと、容量素子と、を有し、

前記第1のトランジスタは、第1の導電層と、第2の導電層と、第3の導電層と、第4の導電層と、第1の半導体膜と、を有し、

前記第1の導電層は、絶縁表面の上方に設けられ、

前記第1の半導体膜は、前記第1の導電層の上方に設けられ、

前記第2の導電層は、前記第1の半導体膜の上方に設けられ、

前記第1の半導体膜は、前記第1のトランジスタのチャネル形成領域を含み、

前記第1の導電層は、第1の絶縁膜を介して前記第1のトランジスタのチャネル形成領域と重なる領域を有し、

前記第2の導電層は、第2の絶縁膜を介して前記第1のトランジスタのチャネル形成領域と重なる領域を有し、

前記第1の導電層は、前記第1のトランジスタの第1のゲートとなることができる機能 を有し、

前記第2の導電層は、前記第1のトランジスタの第2のゲートとなることができる機能を有し、

前記第3の導電層は、前記第1のトランジスタの<u>ソース電極又はドレイン電極</u>の一方となることができる機能を有し、

前記第3の導電層は、前記第1の半導体膜と電気的に接続され、

前記第4の導電層は、前記第1のトランジスタのソース電極又はドレイン電極の他方と なることができる機能を有し、

前記第4の導電層は、前記第1の半導体膜と電気的に接続され、

前記第2のトランジスタは、第5の導電層と、第6の導電層と、第7の導電層と、第2 の半導体膜と、を有し、

前記第5の導電層は、前記絶縁表面の上方に設けられ、

前記第2の半導体膜は、前記第5の導電層の上方に設けられ、

前記第2の半導体膜は、前記第2のトランジスタのチャネル形成領域を含み、

前記第5の導電層は、第3の絶縁膜を介して前記第2のトランジスタのチャネル形成領 域と重なる領域を有し、

前記第5の導電層は、前記第2のトランジスタのゲートとなることができる機能を有し

前記第6の導電層は、前記第2のトランジスタのソース電極又はドレイン電極の一方と なることができる機能を有し、

前記第6の導電層は、前記第2の半導体膜と電気的に接続され、

前記第7の導電層は、前記第2のトランジスタのソース電極又はドレイン電極の他方と なることができる機能を有し、

前記第7の導電層は、前記第2の半導体膜と電気的に接続され、

前記第7の導電層は、前記第2の導電層と電気的に接続され、

前記第1の半導体膜は、シリコンを有し、

前記第2の半導体膜は、酸化物半導体を有し、

前記第1のトランジスタのソース電極又はドレイン電極の一方は、第1の配線と電気的 に接続され、

前記第1のトランジスタのソース電極又はドレイン電極の他方は、前記容量素子の一対 の電極のうちの一方と電気的に接続され、

前記第1のトランジスタの前記第2のゲートは、前記容量素子の一対の電極のうちの他 方と電気的に接続され、

前記第4の導電層は、前記容量素子の一対の電極のうちの一方となる第1の領域を有し

前記第2の導電層は、前記容量素子の一対の電極のうちの他方となる第2の領域を有し

前記第1の領域と前記第2の領域とは、前記第2の絶縁膜を介して重なり、

前記第2のトランジスタのソース電極又はドレイン電極の一方は、第2の配線と電気的 に接続され、

前記第1のトランジスタの前記第1のゲートは、前記第1のトランジスタを導通状態と する電位と、前記第1のトランジスタを非導通状態とする電位と、が供給されることがで きる機能を有し、

前記第2のトランジスタの前記ゲートは、前記第2のトランジスタを導通状態とする電 位と、前記第2のトランジスタを非導通状態とする電位と、が供給されることができる機 能を有することを特徴とする半導体装置。

【請求項2】

第1のトランジスタと、第2のトランジスタと、容量素子と、を有し、

前記第1のトランジスタは、第1の導電層と、第2の導電層と、第3の導電層と、第4 の導電層と、第1の半導体膜と、を有し、

前記第1の導電層は、絶縁表面の上方に設けられ、

前記第1の半導体膜は、前記第1の導電層の上方に設けられ、

前記第2の導電層は、前記第1の半導体膜の上方に設けられ、

前記第1の半導体膜は、前記第1のトランジスタのチャネル形成領域を含み、

前記第1の導電層は、第1の絶縁膜を介して前記第1のトランジスタのチャネル形成領 域と重なる領域を有し、

10

20

30

40

前記第2の導電層は、第2の絶縁膜を介して前記第1のトランジスタのチャネル形成領域と重なる領域を有し、

前記第1の導電層は、前記第1のトランジスタの第1のゲートとなることができる機能 を有し、

前記第2の導電層は、前記第1のトランジスタの第2のゲートとなることができる機能 を有し、

<u>前記第3の導電層は、前記第1のトランジスタのソース電極又はドレイン電極の一方と</u>なることができる機能を有し、

前記第3の導電層は、前記第1の半導体膜と電気的に接続され、

<u>前記第4の</u>導電層は、前記第1のトランジスタのソース電極又はドレイン電極の他方と なることができる機能を有し、

前記第4の導電層は、前記第1の半導体膜と電気的に接続され、

前記第2のトランジスタは、第5の導電層と、第6の導電層と、第7の導電層と、第2 の半導体膜と、を有し、

前記第5の導電層は、前記絶縁表面の上方に設けられ、

前記第2の半導体膜は、前記第5の導電層の上方に設けられ、

前記第2の半導体膜は、前記第2のトランジスタのチャネル形成領域を含み、

<u>前記第5の</u>導電層は、第3の絶縁膜を介して前記第2のトランジスタのチャネル形成領域と重なる領域を有し、

前記第5の導電層は、前記第2のトランジスタのゲートとなることができる機能を有し

<u>前記第6の</u>導電層は、前記第2のトランジスタのソース電極又はドレイン電極の一方となることができる機能を有し、

前記第6の導電層は、前記第2の半導体膜と電気的に接続され、

<u>前記第7の</u>導電層は、前記第2のトランジスタのソース電極又はドレイン電極の他方となることができる機能を有し、

前記第7の導電層は、前記第2の半導体膜と電気的に接続され、

前記第7の導電層は、前記第2の導電層と電気的に接続され、

前記第1の半導体膜は、酸化物半導体を有し、

前記第2の半導体膜は、酸化物半導体を有し、

前記第1のトランジスタのソース電極又はドレイン電極の一方は、第1の配線と電気的 に接続され、

前記第1のトランジスタのソース電極又はドレイン電極の他方は、前記容量素子の一対の電極のうちの一方と電気的に接続され、

前記第1のトランジスタの前記第2のゲートは、前記容量素子の一対の電極のうちの他 方と電気的に接続され、

前記第4の導電層は、前記容量素子の一対の電極のうちの一方となる第1の領域を有し

\_\_\_\_

前記第2の導電層は、前記容量素子の一対の電極のうちの他方となる第2の領域を有し

`\_\_

前記第1の領域と前記第2の領域とは、前記第2の絶縁膜を介して重なり、

<u>前記第2のトランジスタのソース電極又はドレイン電極の一方は、第2の配線と電気的</u>に接続され、

前記第1のトランジスタの前記第1のゲートは、前記第1のトランジスタを導通状態とする電位と、前記第1のトランジスタを非導通状態とする電位と、が供給されることができる機能を有し、

前記第2のトランジスタの前記ゲートは、前記第2のトランジスタを導通状態とする電位と、前記第2のトランジスタを非導通状態とする電位と、が供給されることができる機能を有することを特徴とする半導体装置。

【発明の詳細な説明】

50

10

20

30

## 【技術分野】

[0001]

不揮発性半導体記憶装置に係り、データを保持するメモリセルの構成及び駆動方法に関する。

# 【背景技術】

[0002]

半導体記憶装置(以下、単に記憶装置とする)には、揮発性メモリに分類されるDRAM、SRAM、不揮発性メモリに分類されるマスクROM、EPROM、EEPROM、フラッシュメモリ、強誘電体メモリなどがあり、単結晶の半導体基板を用いて形成されたこれらのメモリの多くは既に実用化されている。上記の半導体メモリの中でも、フラッシュメモリは、データの書き込みと消去を繰り返し行うことができ、電源の供給がなくてもデータの保持が可能な不揮発性メモリであるために、利便性が高く、また、物理的な衝撃に強いため、主にUSBメモリ、メモリーカードなどの携帯型の記憶媒体に用いられ、市場に広く出回っている。

## [0003]

フラッシュメモリには、複数のメモリセルが直列に接続された構造を有するNAND型と、複数のメモリセルがマトリクス状に接続された構造を有するNOR型とがあるが、いずれのフラッシュメモリも、記憶素子として機能するトランジスタを各メモリセルに有する。そして、この記憶素子として機能するトランジスタは、フローティングゲートと呼ばれる電荷を蓄積するための電極を、ゲート電極と、活性層である半導体膜との間に有しており、フローティングゲートにおける電荷の蓄積によりデータの記憶を行うことができる。

[0004]

下記の特許文献 1 と特許文献 2 には、ガラス基板上に形成された、フローティングゲートを有する薄膜トランジスタについて記載されている。

【先行技術文献】

## 【特許文献】

[0005]

【特許文献1】特開平6-021478号公報

【特許文献2】特開2005-322899号公報

【発明の概要】

【発明が解決しようとする課題】

[0006]

ところで、不揮発性メモリは、データの書き込み時に記憶素子に印加される電圧の絶対値が、20V前後と、揮発性メモリに比べて一般的に大きい傾向にある。データの書き換えを繰り返し行うことができるフラッシュメモリの場合は、データの書き込み時のみならず、データの消去時にも、記憶素子として用いるトランジスタに大きい電圧を印加する必要がある。よって、データの書き込み、消去などの、フラッシュメモリの動作時において消費される電力は高く、そのことが、フラッシュメモリを記憶装置として用いる電子機器の、低消費電力化を阻む一因となっている。特に、カメラや携帯電話などの携帯型の電子機器にフラッシュメモリを用いる場合、消費電力の高さは、連続使用時間の短縮化というデメリットに繋がる。

[0007]

また、フラッシュメモリは不揮発性メモリではあるが、微少な電荷のリークによりデータが消失してしまう。そのため、データの保持期間は現状 5 年から 1 0 年程度であると言われており、より長い保持期間の確保が可能なフラッシュメモリの実現が望まれている。

# [0008]

さらに、フラッシュメモリは、データの書き込みと消去を繰り返し行うことが可能ではあるが、フローティングゲートに電荷を蓄積する際に、トンネル電流によりゲート絶縁膜が劣化しやすい。そのため、1つの記憶素子におけるデータの書き換え回数は数万から数十万回程度が限度であり、より多くの書き換え回数に耐えうるようなフラッシュメモリの実

10

20

30

40

現が望まれている。

## [0009]

上述の課題に鑑み、本発明は、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。また、本発明は、さらに長い期間においてデータの保持が可能な記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。また、本発明は、データの書き換え回数を増やすことができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

## 【課題を解決するための手段】

## [0010]

本発明の一態様では、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられたトランジスタを記憶素子として用い、不揮発性の記憶装置を構成する。そして、上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、記憶素子として用いるトランジスタの閾値電圧を制御するための第2のゲート電極の電位を、オフ電流が極めて小さいトランジスタによって制御することで、データの書き込みを行う。すなわち、本発明の一態様に係る記憶装置は、少なくとも、第2のゲート電極によって閾値電圧が制御されるトランジスタと、該第2のゲート電極の電位を保持するための容量素子と、当該容量素子の充放電を制御するためのスイッチング素子として用いるトランジスタとで、構成されることを特徴としている。

#### [0011]

記憶素子として用いるトランジスタの閾値電圧のシフト量は、第2のゲート電極の電位の高さ、より具体的には、ソース電極と第2のゲート電極の電位差により制御される。そして、閾値電圧の高さの違い、或いは、閾値電圧の高さの違いによるソース電極とドレイン電極間の抵抗値の違いが、記憶素子が記憶しているデータの違いとなる。

## [0012]

記憶素子として用いるトランジスタは、絶縁ゲート型電界効果トランジスタであれば良く、具体的には、第1のゲート電極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極と、を有する。

## [0013]

そして、スイッチング素子として用いるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含むことを特徴とするものである。上述したような特性を有する半導体材料をチャネル形成領域に含むことで、オフ電流が極めて低いトランジスタを実現することができる。このような半導体材料としては、例えば、シリコンの約3倍程度の大きなバンドギャップを有する、酸化物半導体、炭化シリコン、窒化ガリウムなどが挙げられる。

# [0014]

なお、酸化物半導体は、微結晶シリコンまたは多結晶シリコンによって得られる高い移動度と、非晶質シリコンによって得られる均一な素子特性とを兼ね備えた、半導体特性を示す金属酸化物である。そして、電子供与体(ドナー)となる水分または水素などの不純物が低減されて高純度化された酸化物半導体(purified OS)は、i型(真性半導体)又はi型に限りなく近く、上記酸化物半導体を用いたトランジスタは、オフ電流なの不純物を除去し、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)による、酸化物半導体に含まれる水素濃度の測定値が、 $5\times10^{19}$ /cm³以下、好ましくは $5\times10^{19}$ /cm³以下、より好ましくは $5\times10^{19}$ /cm³以下、より好ましくは $5\times10^{19}$ /cm³以下、より好ましくは $1\times10^{19}$ /cm³以下とする。また、ホール効果測定により測定できる酸化物半導体膜のキャリア密度は、 $1\times10^{14}$ cm³未満、好ましくは $1\times10^{12}$ cm³未満、さらに好ましくは測定限界以下の $1\times10^{11}$ cm³未満とする。即ち、酸化物半導体膜のキャリア密度は、限りなくゼロに近

30

20

10

40

20

30

40

50

い。また、バンドギャップは2eV以上、好ましくは2.5eV以上、より好ましくは3 eV以上である。水分または水素などの不純物濃度が十分に低減されて高純度化された酸 化物半導体膜を用いることにより、トランジスタのオフ電流を下げることができる。

# [0015]

ここで、酸化物半導体膜中及び導電膜中の、水素濃度の分析について触れておく。酸化物半導体膜中及び導電膜中の水素濃度測定は、SIMSで行う。SIMSは、その原理上、試料表面近傍や、材質が異なる膜との積層界面近傍のデータを正確に得ることが困難であることが知られている。そこで、膜中における水素濃度の厚さ方向の分布をSIMSで分析する場合、対象となる膜が存在する範囲において、値に極端な変動が無く、ほぼ一定の値が得られる領域における平均値を、水素濃度として採用する。また、測定の対象となる膜の厚さが小さい場合、隣接する膜内の水素濃度の影響を受けて、ほぼ一定の値が得られる領域を見いだせない場合がある。この場合、当該膜が存在する領域における、水素濃度の極大値または極小値を、当該膜中の水素濃度として採用する。さらに、当該膜の存在する領域において、極大値を有する山型のピーク、極小値を有する谷型のピークが存在しない場合、変曲点の値を水素濃度として採用する。

## [0016]

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分または水素が多量に含まれていることが判明している。水分または水素はドナー準位を形成しやすいため、酸化物半導体自体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物半導体膜に対して、窒素、酸素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウムなど)の雰囲気下で加熱処理を行う。上記加熱処理は、500 以上850 以下(若しくはガラス基板の歪点以下)、好ましくは550 以上750 以下の温度範囲で行うのが望ましい。なお、この加熱処理は、用いる基板の耐熱温度を超えないものとする。水分または水素の加熱処理による脱離の効果については、TDS(Thermal Desorption Spectroscopv;昇温脱離ガス分析)により確認済みである。

#### [0017]

加熱処理は、炉での熱処理またはラピッドサーマルアニール法(RTA法)を用いる。RTA法は、ランプ光源を用いる方法と、加熱されたガス中に基板を移動させて短時間の熱処理を行う方法がある。RTA法を用いると熱処理に要する時間を0.1時間よりも短くすることもできる。

### [0018]

具体的に、上述した加熱処理により高純度化された酸化物半導体膜を活性層として用いた トランジスタは、例えば、チャネル幅Wが $1 \times 10^6 \mu m$ でチャネル長Lが $10 \mu m$ の素 子であっても、ソース電極とドレイン電極間の電圧(ドレイン電圧)が1Vから10Vの 範囲において、オフ電流(ゲート電極とソース電極間の電圧を0Vとしたときのドレイン 電流)が、半導体パラメータアナライザの測定限界以下、すなわち1×10 <sup>- 1 3</sup> A以下 という特性を得ることができる。よって、オフ電流をトランジスタのチャネル幅で除した 数値に相当するオフ電流密度は、100zA/μm以下であることが分かる。また、保持 容量の電荷を保持するためのスイッチング素子として、高純度化された酸化物半導体膜を 有するゲート絶縁膜の厚さが100nmのトランジスタを用いて、保持容量の単位時間あ たりの電荷量の推移から当該トランジスタのオフ電流を測定したところ、トランジスタの ソース電極とドレイン電極間の電圧が 3 Vの場合に、10 ΖΑ/μm乃至100 ΖΑ/μ mという、さらに低いオフ電流が得られることが分かった。したがって、本発明の一態様 に係る記憶装置では、高純度化された酸化物半導体膜を活性層として用いたトランジスタ のオフ電流密度を、100zA/μm以下、好ましくは10zA/μm以下、更に好まし くは1zA/μm以下にすることができる。従って、高純度化された酸化物半導体膜を活 性層として用いたトランジスタは、ゲート電極とソース電極間の電圧が0以下におけるオ フ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。

#### [0019]

また、高純度化された酸化物半導体を用いたトランジスタは、オフ電流の温度依存性がほ とんど現れない。これは、酸化物半導体中で電子供与体(ドナー)となる不純物を除去し て、酸化物半導体が高純度化することによって、導電型が限りなく真性型に近づき、フェ ルミ準位が禁制帯の中央に位置するためと言える。また、これは、酸化物半導体のエネル ギーギャップが 3 e V 以上であり、熱励起キャリアが極めて少ないことにも起因する。ま た、ソース電極及びドレイン電極が縮退した状態にあることも、温度依存性が現れない要 因となっている。トランジスタの動作は、縮退したソース電極から酸化物半導体に注入さ れたキャリアによるものがほとんどであり、キャリア密度には温度依存性がないことから 、オフ電流の温度依存性がみられないことを説明することができる。

[0020]

なお、酸化物半導体は、四元系金属酸化物であるIn-Sn-Ga-Zn-O系酸化物半 導体や、三元系金属酸化物であるIn-Ga-Zn-O系酸化物半導体、In-Sn-Z n - O系酸化物半導体、In - Al - Zn - O系酸化物半導体、Sn - Ga - Zn - O系 酸化物半導体、A1-Ga-Zn-O系酸化物半導体、Sn-A1-Zn-O系酸化物半 導体や、二元系金属酸化物であるIn-Zn-O系酸化物半導体、Sn-Zn-O系酸化 物半導体、A1-Zn-O系酸化物半導体、Zn-Mg-O系酸化物半導体、Sn-Mg - O系酸化物半導体、In-Mg-O系酸化物半導体、In-Ga-O系酸化物半導体や In-O系酸化物半導体、Sn-O系酸化物半導体、Zn-O系酸化物半導体などを用 いることができる。なお、本明細書においては、例えば、In-Sn-Ga-Zn-O系 酸化物半導体とは、インジウム(In)、錫(Sn)、ガリウム(Ga)、亜鉛(Zn) を有する金属酸化物、という意味であり、その化学量論的組成比は特に問わない。また、 上記酸化物半導体は、珪素を含んでいてもよい。

[0021]

或いは、酸化物半導体は、化学式InMO╕(ZnO)g(m>0)で表記することがで きる。ここで、Mは、Ga、Al、Mn及びCoから選ばれた一又は複数の金属元素を示 す。

## 【発明の効果】

[0022]

上記オフ電流の低いトランジスタを、記憶素子に蓄積された電荷を保持するためのスイッ チング素子として用いることで、記憶素子からの電荷のリークを防ぐことができる。よっ て、長期間に渡るデータの保持が可能な記憶装置、当該記憶装置を用いた半導体装置を提 供することができる。

[0023]

また、記憶素子へのデータの書き込み及び読み出しに必要な電圧は、スイッチング素子と して機能するトランジスタの動作電圧によりほぼ決まる。よって、従来のフラッシュに比 べて動作電圧を格段に低くすることができ、消費電力を抑えられる記憶装置、当該記憶装 置を用いた半導体装置を提供することができる。

また、トンネル電流によるゲート絶縁膜の劣化を、従来のフラッシュに比べて抑えること ができるので、データの書き換え回数を増やすことができる記憶装置、当該記憶装置を用 いた半導体装置を提供することができる。

【図面の簡単な説明】

[0025]

- 【図1】メモリセルの構成を示す図。

- 【図2】(A)記憶素子の構成と、(B)その動作について説明する図。

- 【図3】メモリセルの構成を示す図。

- 【図4】メモリセルの構成を示す図。

- 【図5】セルアレイの構成を示す図。

- 【図6】セルアレイの構成を示す図。

10

20

40

- 【図7】記憶装置の駆動方法を示すタイミングチャート。

- 【図8】記憶装置の構成を示す図。

- 【図9】読み出し回路の構成を示す図。

- 【図10】記憶装置の作製方法を示す、メモリセルの断面図。

- 【図11】メモリセルの上面図。

- 【図12】酸化物半導体を用いた逆スタガ型のトランジスタの縦断面図。

- 【図13】図12に示すA-A′上におけるエネルギーバンド図(模式図)。

- 【図14】(A)ゲート電極(GE)に正の電圧(VG>0)が印加された状態を示し、

- (B)ゲート電極(GE)に負の電圧(VG<0)が印加された状態を示す図。

- 【図15】真空準位と金属の仕事関数( <sub>M</sub>)、酸化物半導体の電子親和力( )の関係を示す図。

- 【図16】記憶媒体の構成を示す図。

- 【図17】電子機器の構成を示す図。

- 【図18】測定用回路の構成を示す図。

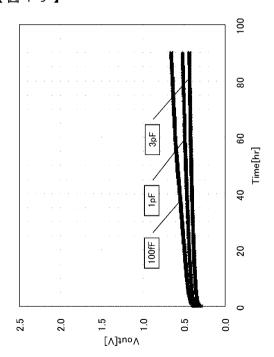

- 【図19】測定結果を示す図(経過時間Timeと、出力電位Voutとの関係を示す図)。

- 【図20】測定結果を示す図(ソース・ドレイン電圧 V と、オフ電流 I との関係を示す図)。

- 【図21】記憶装置の駆動方法を示すタイミングチャート。

# 【発明を実施するための形態】

[0026]

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

[0027]

なお、マイクロプロセッサ、画像処理回路などの集積回路や、RFタグ、記憶媒体、半導体表示装置など、記憶装置を用いることができるありとあらゆる半導体装置が、本発明の範疇に含まれる。また、半導体表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)など、半導体膜を用いた回路素子を画素部または駆動回路に有している半導体表示装置が、その範疇に含まれる。

[0028]

(実施の形態1)

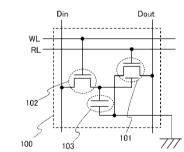

図1(A)に、本発明の記憶装置の最小単位に当たるメモリセルの、回路図の一例を示す。図1(A)に示すメモリセル100は、記憶素子として機能するトランジスタ101と、トランジスタ101の第2のゲート電極への電位の供給を制御することができる、スイッチング素子として機能するトランジスタ102とを有する。また、メモリセル100は、トランジスタ101の第2のゲート電極の電位を保持するための容量素子103が設けられていても良い。

[0029]

なお、メモリセル 1 0 0 は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の回路素子を、さらに有していても良い。

[0030]

記憶素子として機能するトランジスタ101は、第1のゲート電極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極と、を有する。トランジ

20

10

30

40

スタ101の第1のゲート電極、第2のゲート電極、ソース電極、ドレイン電極に与える 電位により、記憶装置の各種動作を制御することができる。

## [0031]

スイッチング素子として機能するトランジスタ102は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含むものである。このような半導体材料をトランジスタ102のチャネル形成領域に用いることで、オフ電流を十分低減することができるからである。

## [0032]

シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料の一例として、炭化珪素(SiC)、窒化ガリウム(GaN)などの化合物半導体、酸化亜鉛(ZnO)などの金属酸化物でなる酸化物半導体などを適用することができる。この中でも酸化物半導体は、スパッタリング法や湿式法(印刷法など)により作製可能であり、量産性に優れるといった利点がある。また、炭化シリコンのプロセス温度は約1100 であるが、酸化物半導体の成膜温度は、300~500 (ガラス転移温度以下、最大でも700 程度)と低く、安心の安心で入手しやすいガラス基板上への成膜が可能であり、また、1500~2000 もの高温での熱処理に対する耐性を有さない半導体材料を用いた集積回路上に、酸化物半導体による半導体素子を積層させることも可能である。また、基板の大型化にも対応が可能である。よって、上述したワイドギャップ半導体の中でも、特に酸化物半導体に高いというメリットを有する。また、トランジスタの性能(例えば電界効果移動度)を向いというメリットを有する。また、トランジスタの性能(例えば電界効果移動度)を向いというメリットを有する。また、トランジスタの性能(例えば電界効果移動度)を向いというメリットを有する。また、トランジスタの性能(例えば電界効果移動度)を向いたは記性の酸化物半導体を得ることができる。

## [0033]

以下の説明では第2のトランジスタ102の半導体膜として、上記のような利点を有する酸化物半導体を用いる場合を例に挙げている。

## [0034]

なお、図1(A)では、メモリセル100がスイッチング素子として機能するトランジスタ102を一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、スイッチング素子として機能するトランジスタが各メモリセルに最低限1つ設けられていれば良く、上記トランジスタの数は複数であっても良い。メモリセル100がスイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていても良いし、直列に接続されていても良いし、直列に接続されていても良い。

## [0035]

なお、トランジスタが直列に接続されている状態とは、第1のトランジスタのソース電極とドレイン電極のいずれか一方のみが、第2のトランジスタのソース電極とドレイン電極のいずれか一方のみに接続されている状態を意味する。また、トランジスタが並列に接続されている状態とは、第1のトランジスタのソース電極が第2のトランジスタのソース電極に接続され、第1のトランジスタのドレイン電極が第2のトランジスタのドレイン電極に接続されている状態を意味する。

# [0036]

また、スイッチング素子として機能するトランジスタ102は、記憶素子として機能するトランジスタ101とは異なり、活性層の片側にだけ存在するゲート電極を有していれば良い。ただし、本発明はこの構成に限定されず、スイッチング素子として機能するトランジスタも、記憶素子として機能するトランジスタと同様に、活性層を間に挟んで存在する一対のゲート電極を有していても良い。

## [0037]

また、本発明の一態様では、少なくとも、スイッチング素子として機能するトランジスタ 102が、上述したワイドギャップ半導体材料を活性層に有していれば良い。よって、記 憶素子として機能するトランジスタ101の活性層に、酸化物半導体膜が用いられていて 10

20

30

40

も良い。或いは、記憶素子として機能するトランジスタ101の活性層に、酸化物半導体以外の、非晶質、微結晶、多結晶、または単結晶の、シリコン、またはゲルマニウムなどの半導体が用いられていても良い。ただし、メモリセル100内の全てのトランジスタの活性層に、酸化物半導体膜を用いることで、プロセスを簡略化することができる。

## [0038]

次いで、図1(A)に示したメモリセル100における、トランジスタ101、トランジスタ102、容量素子103の接続関係について説明する。

## [0039]

トランジスタ102のゲート電極は、書き込み用ワード線WLに接続されている。そして、トランジスタ102は、ソース電極とドレイン電極のうち、いずれか一方が入力用データ線Dinに接続され、他方が、トランジスタ101の第2のゲート電極に接続されている。また、トランジスタ101の第1のゲート電極は、読み出し用ワード線RLに接続されている。そして、トランジスタ101は、ソース電極とドレイン電極のうち、いずれか一方が出力用データ線Doutに接続され、他方がグラウンドなどの固定電位が与えられている電源線に接続されている。

#### [0040]

また、容量素子103が有する一対の電極は、一方がトランジスタ101の第2のゲート 電極に接続されており、他方がグラウンドなどの固定電位が与えられている電源線に接続 されている。

# [0041]

なお、本明細書において接続とは電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、配線、抵抗、ダイオード、トランジスタなどの回路素子を介して間接的に接続している状態も、その範疇に含む。

## [0042]

また、回路図上は独立している構成要素どうしが接続されている場合であっても、実際には、例えば配線の一部が電極としても機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っているだけの場合もある。本明細書において接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

### [0043]

また、トランジスタが有するソース電極とドレイン電極は、トランジスタの極性及び各電極に与えられる電位の高低差によって、その呼び方が入れ替わる。一般的に、nチャネル型トランジスタでは、低い電位が与えられる電極がソース電極と呼ばれ、高い電位が与えられる電極がドレイン電極と呼ばれる。また、pチャネル型トランジスタでは、低い電位が与えられる電極がドレイン電極と呼ばれ、高い電位が与えられる電極がソース電極と呼ばれ、高い電位が与えられる電極がソース電極と呼ばれる。本明細書では、便宜上、ソース電極とドレイン電極とが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソース電極とドレイン電極の呼び方が入れ替わる。

# [0044]

なお、図1(A)では、トランジスタ102がゲート電極を活性層の片側にのみ有している場合を示している。トランジスタ102が、活性層を間に挟んで存在する一対のゲート電極を有している場合は、一方のゲート電極が書き込み用ワード線WLに接続され、他方のゲート電極は、電気的に絶縁しているフローティングの状態であっても良いし、電位が他から与えられている状態であっても良い。後者の場合、一対の電極に、同じ高さの電位が与えられていても良いし、他方のゲート電極にのみグラウンドなどの固定電位が与えられていても良い。他方のゲート電極に与える電位の高さを制御することで、トランジスタ102の閾値電圧を制御することができる。

#### [0045]

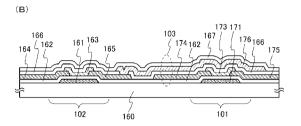

次いで、図1(B)に、図1(A)に示した回路構成を有するメモリセル100の、断面

20

10

30

40

図の一例を示す。図1(B)に示すメモリセルは、記憶素子として機能するトランジスタ 101と、スイッチング素子として機能するトランジスタ102とが、絶縁表面を有する 基板110上に形成されている。

#### [0046]

具体的に、トランジスタ101は、絶縁表面を有する基板110上に、第1のゲート電極121と、第1のゲート電極121上の絶縁膜112と、絶縁膜112を間に挟んで第1のゲート電極121と重なる、活性層として機能する酸化物半導体膜123と、酸化物半導体膜123上のソース電極124、ドレイン電極125と、酸化物半導体膜123、ソース電極124及びドレイン電極125上の絶縁膜116と、絶縁膜116上において酸化物半導体膜123と重なっている第2のゲート電極126とを有している。また、第2のゲート電極126上には絶縁膜117が形成されており、トランジスタ101は絶縁膜117を構成要素に含んでいても良い。

## [0047]

また、トランジスタ102は、絶縁表面を有する基板110上に、ゲート電極111と、ゲート電極111上の絶縁膜112と、絶縁膜112を間に挟んでゲート電極111と重なる、活性層として機能する酸化物半導体膜113と、酸化物半導体膜113上のソース電極114、ドレイン電極115とを有している。酸化物半導体膜113、ソース電極114及びドレイン電極115上には絶縁膜116が形成されており、トランジスタ102は絶縁膜116を構成要素に含んでいても良い。

# [0048]

また、容量素子103は、トランジスタ101のソース電極124と、第2のゲート電極126とが、絶縁膜116を間に挟んで重なり合っている領域に形成されている。

## [0049]

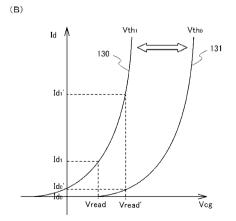

次いで、図2を用いて、記憶素子として機能するトランジスタの動作について、トランジスタ101がnチャネル型であり、なおかつ2値のデータを扱う場合を例に挙げて説明する。なお、図2(A)には、トランジスタ101の回路図を示しており、第1のゲート電極の電位をVcg、第2のゲート電極の電位をVbg、ソース電極の電位をVs、ドレイン電極の電位をVdとして、トランジスタ101が有する各電極の電位を表記している。

## [0050]

まず、データの書き込み時におけるトランジスタ101の動作について説明する。書き込み時において、トランジスタ101は、第1のゲート電極とソース電極間に、閾値電圧Vth $_0$ と同じか、それよりも低い電圧が印加される。なお、閾値電圧Vth $_0$ は、第2のゲート電極の電位Vbgがグラウンドの電位Vgndに等しいときの、トランジスタ101の閾値電圧に相当する。具体的に、書き込み時における第1のゲート電極とソース電極の電位の関係は、Vcg・Vs Vth $_0$ となる。よって、トランジスタ101は書き込み時においてオフであり、ドレイン電極はハイインピーダンスの状態にある。

# [0051]

そして、データの書き込み時において、第 2 のゲート電極の電位 V b g は、書き込むデータの値に従ってその高さが制御される。 2 値のデータを扱う場合、第 2 のゲート電極には、高電位 V d d v s s v g n d で表される。例えば、第 v 2 のゲート電極の電位 v b g が低電位 v s s v g n d で表される。例えば、第 v 2 のゲート電極の電位 v b g が低電位 v s s v g n d に設定された場合、トランジスタ v 1 0 1 の閾値電圧は v t h v 0 のままである。一方、第 v 2 のゲート電極の電位 v b g が高電位 v d d に設定された場合、トランジスタ 1 0 1 の閾値電圧はマイナス側にシフトし、v t h v 2 なる。

#### [0052]

なお、本実施の形態では、書き込み時において低電位 V s s = V g n d である場合を例に挙げて説明したが、低電位 V s s は必ずしもグラウンドの電位 V g n d と等しくある必要はない。例えば、V d d > V s s > V g n d としてもよい。ただし、この場合、閾値電圧のシフト量は、第2のゲート電極の電位 V b g が高電位 V d d に設定された場合における閾値電圧のシフト量よりも、小さいものとする。

10

20

30

40

20

30

40

50

## [0053]

次いで、データの保持時におけるトランジスタ101の動作について説明する。保持時において、スイッチング素子として機能するトランジスタ102はオフである。上述したようにトランジスタ102はオフ電流が著しく低いので、第2のゲート電極の電位Vbgは、書き込み時において設定された高さを保持する。

# [0054]

次いで、データの読み出し時におけるトランジスタ101の動作について説明する。読み出し時において、トランジスタ101は、第1のゲート電極とソース電極間に、閾値電圧 Vth<sub>1</sub>よりも高くVth<sub>0</sub>よりも低い電圧が印加される。

# [0055]

そして、直前に行われたデータの書き込み時において、トランジスタ101の閾値電圧が V th  $_1$  に設定されている場合は、第1のゲート電極とソース電極間の電圧が閾値電圧 V th  $_1$  よりも高くなることで、トランジスタ101がオンになり、ソース電極とドレイン電極間の抵抗値が下がる。よって、ソース電極の電位 V s は、ドレイン電極に与えられる。一方、直前に行われたデータの書き込み時において、トランジスタ101の閾値電圧が V th  $_0$  に設定されている場合、第1のゲート電極とソース電極間の電圧が、閾値電圧 V th  $_1$  よりも高くなっても、閾値電圧 V th  $_0$  よりも低いと、トランジスタ101はオフのままである。よって、ソース電極とドレイン電極間の抵抗値が高く、ドレイン電極の電位 V d はハイインピーダンスの状態のままである。

# [0056]

従って、ドレイン電極の電位 V d は、直前に行われたデータの書き込み時において、第 2 のゲート電極に与えられた電位の高さに連動している。図 2 ( B )に、読み出し時における、第 1 のゲート電極の電位 V c g と、トランジスタ 1 0 1 のドレイン電流 I d の関係を示す。線 1 3 0 は、閾値電圧が V t h  $_1$  に設定されている場合の、電位 V c g とドレイン電流 I d の関係を示しており、線 1 3 1 は、閾値電圧が V t h  $_0$  に設定されている場合の、電位 V c g とドレイン電流 I d の関係を示している。図 2 ( B )に示すように、第 1 のゲート電極とソース電極間の電圧が、閾値電圧 V t h  $_1$  よりも高く、閾値電圧 V t h  $_0$  の場合に得られるドレイン電流 I d  $_1$  が、閾値電圧が V t h  $_0$  の場合に得られるドレイン電流 I d  $_1$  が、閾値電圧が V t h  $_0$  の場合に得られるドレイン電流 I d  $_0$  よりも高くなる。よって、ドレイン電流 I d もしくはドレイン電極の電位 V d の値を読み取ることで、書き込まれたデータの値を把握することができる。

# [0057]

なお、本実施の形態では、読み出し時において第1のゲート電極とソース電極間の電圧が 、閾値電圧Vth<sub>1</sub>よりも高く、閾値電圧Vth<sub>0</sub>よりも低い場合について説明したが、 本発明はこの構成に限定されない。読み出し時における第1のゲート電極とソース電極間 の電圧は、必ずしも閾値電圧Vth。以下である必要はない。例えば、直前に行われたデ ータの書き込み時において、トランジスタ101の閾値電圧がVth,に設定されている 場合、読み出し時において、第1のゲート電極とソース電極間の電圧が閾値電圧Vt $h_0$ より高いと、トランジスタ101がオンになり、ソース電極とドレイン電極間の抵抗値が 下がる。このときの、ソース電極とドレイン電極間の抵抗値をRds 。 とする。一方、直 前に行われたデータの書き込み時において、トランジスタ101の閾値電圧がVth。に 設定されている場合、読み出し時において、第1のゲート電極とソース電極間の電圧が閾 値電圧Vth。より高いと、トランジスタ101はオンになり、ソース電極とドレイン電 極間の抵抗値が下がる。このときの、ソース電極とドレイン電極間の抵抗値を Rds 1 と する。そして、少なくとも、閾値電圧がVthィに設定されている場合に、トランジスタ 101を飽和領域で動作させることで、読み出し時におけるトランジスタ101が、Vt h<sub>1</sub>及びVth<sub>0</sub>のいずれの閾値電圧設定時においてオンの状態であっても、ソース電極 とドレイン電極間の抵抗値をRds 。<Rds 」として差を持たせることができる。具体 的には、第1のゲート電極とソース電極間の電圧をVgs、ソース電極とドレイン電極間

20

30

40

50

(13)

ンジスタ101を動作させればよい。ソース電極とドレイン電極間の抵抗値をRds $_0$ <Rds $_1$ として差を持たせることで、読み出し時における第1のゲート電極とソース電極間の電圧が、閾値電圧Vth $_0$ より高くあっても、ドレイン電極の電位Vdを、直前に行われたデータの書き込み時において第2のゲート電極に与えられた電位の高さに連動させることが可能である。例えば、図2(B)に示すように、第1のゲート電極とソース電極間の電圧が、閾値電圧Vth $_0$ よりも高い電位Vread'に設定されると、線130と線131から、閾値電圧がVth $_1$ の場合に得られるドレイン電流 Id $_1$ 'が、閾値電圧がVth $_1$ の場合に得られるドレイン電流 Id $_1$ 'が、閾値電圧がVth $_0$ の場合に得られるドレイン電流 Id $_0$ 'よりも高くなる。よって、ドレイン電流 Idもしくはドレイン電極の電位Vdの値を読み取ることで、書き込まれたデータの値を把握することができる。

[0058]

次いで、データの消去時におけるトランジスタ101の動作について説明する。消去時において、トランジスタ101は、データの書き込み時と同様に、第1のゲート電極とソース電極間に、閾値電圧Vth<sub>1</sub>と同じか、それよりも低い電圧が印加される。具体的に、消去時における第1のゲート電極とソース電極の電位の関係は、Vcg・Vs Vth<sub>1</sub>となる。よって、トランジスタ101は消去時においてオフであり、ドレイン電極はハイインピーダンスの状態にある。そして、データの消去時において、第2のゲート電極の電位Vbgは、グラウンドなどの固定電位に設定され、トランジスタ101の閾値電圧はVth<sub>0</sub>に設定される。

[0059]

なお、本実施の形態では、書き込んだデータを消去する記憶装置の駆動方法について説明したが、本発明はこの構成に限定されない。本発明の一態様に係る記憶装置は、従来のフラッシュメモリとは異なり、消去動作を必要としない点が、利点の一つでもある。よって、例えば、先に書き込んだデータに上書きするように、別のデータを書き込むことも可能である。

[0060]

なお、一般的なフラッシュメモリの場合、データの書き込み時において、電荷を蓄積する フローティングゲートが、絶縁膜で覆われた絶縁状態にある。よって、フローティングゲ ートに、トンネル効果を利用して電荷を蓄積させるためには、 2 0 V 程度の高い電圧を記 憶素子に印加する必要がある。しかし、本発明の一態様では、高純度化された酸化物半導 体膜をトランジスタの活性層として用いたトランジスタにより、データの書き込み及び読 み出しを行うことができる。よって、記憶装置の動作時に必要な電圧は数 V 程度であり、 消費電力を格段に小さく抑えることができる。なお、フラッシュメモリの記憶素子として 用いられているトランジスタと、本発明の一態様に係る記憶装置の記憶素子として用いら れているトランジスタとは、構造や駆動方法が異なるため、記憶素子の各電極に与えられ る電位から、動作時の消費電力の違いを正確に把握することは難しい。しかし、例えば、 データの書き込み時についてのみに着目して消費電力を比較してみると、本発明の一態様 に係る記憶装置では、第2のゲート電極とソース電極間に印加される電圧が5Vあれば十 分データの書き込みが可能である。一方、通常のフラッシュメモリでは、フローティング ゲートに電荷を蓄積させてデータの書き込みを行うために、ゲート電極とソース電極間に 、少なくとも16V程度の電圧が必要となる。トランジスタにおいて消費される電力は、 トランジスタのゲート電圧の二乗を、トランジスタの負荷抵抗で割ったものに相当するこ とから、本発明の一態様に係る記憶装置の消費電力は、通常のフラッシュメモリの消費電 力の約10%程度であることがわかる。したがって、書き込み時における消費電力の比較 から、動作時の消費電力が大幅に削減できることがわかる。

[0061]

なお、一般的なフラッシュメモリを用いた半導体装置では、フラッシュメモリの動作時に必要な電圧(動作電圧)が大きいので、通常、昇圧回路などを用いてフラッシュメモリに与える電圧を昇圧している。しかし、本発明の一態様に係る記憶装置では、記憶装置の動作電圧を小さく抑えられるので、消費電力を小さくすることができる。よって、半導体装

置内の、記憶装置の動作に係わる昇圧回路などの外部回路の負担を軽減することができ、その分、外部回路の機能拡張などを行い、半導体装置の高機能化を実現することができる。また、記憶装置の動作電圧を小さく抑えられることで、動作電圧の大きさをカバーするための冗長な回路設計が不要となるため、半導体装置に用いられている集積回路の集積度を高めることができ、半導体装置を高機能化させることが出来る。

### [0062]

また、本実施の形態では、2値のデジタルデータを扱う場合の駆動方法について説明したが、本発明の記憶装置では、3値以上の多値のデータを扱うことも可能である。3値以上の多値のデータを扱うことも可能である。3値以上の多値のデータを扱うことも可能である。3値以上の多値のデータを扱うは、データの書き込み時において、第2のゲート電極の電位とりまり、はなり、はできるようにする。関値電圧の値は、第2のゲート電極のでは、りりの高さに従って、関値電圧の高さを3段階以上に設定できる。そして、関値電圧の高さの違いによりドレイン電流に生じる差を明いて、多値のデータの読み出しを行なよりによりドレイン電極間の抵抗値に生じる差を用いて、多値のデータの読み出しを行びよりできる。さらに別の方法として、関値電圧の高さの段階に応じて、最値電圧を第1のゲート電極に印加し、4段階であるの段階分だけ読み出しを行う。例えば、4値のデータを読み出す場合、4段階で電圧の高さの段階分だけ読み出しを行う。例えば、4値のデータを読み出す場合の4つの電圧(V t h 0、 V t h 2、 V t h 3)の各段階よりやや高めの4つの電圧(V r e a d 0、 V r e a d 2、 V r e a d 3)を予め準備しておきる。上記構成によって、面積を抑えつつ、記憶装置の記憶容量を増やすことができる。

#### [0063]

なお、3値以上の多値のデータの場合、値が4値、5値と増えていくにつれて各値どうしの閾値電圧の差が小さくなるため、微少なオフ電流が存在すると、第2のゲート電極の電位が変化し、データの正確さを維持するのが難しく、保持期間がさらに短くなる傾向にある。しかし、本発明の一態様では、高純度化された酸化物半導体膜を用いることでオフ電流が著しく低減されたトランジスタをスイッチング素子として用いるので、シリコンを用いたトランジスタよりも、オフ電流を防ぐ効果がより高い。従って、多値化に伴う保持期間の短縮化を抑えることができる。

## [0064]

また、図1(B)では、スイッチング素子として機能するトランジスタ102が、ゲート電極111上に酸化物半導体膜113を有するボトムゲート型である場合を例示していいたが、トランジスタ102はボトムゲート型に限定されない。トランジスタ102は、酸化物半導体膜を活性層として用いていれば良く、例えば、酸化物半導体膜上にゲート型であっても良い。また、トランジスタ102は、ソース電極1115が酸化物半導体膜113上に形成されているトップコンタクト型に限定されず、ソース電極114とドレイン電極115上に酸化物半導体膜113が形成れているボトムコンタクト型であっても良い。また、トランジスタ102は、ソースでは、カースでは、カースでは、カースであっても良い。また、トランジスタ102は、ソースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カースでは、カース

#### [0065]

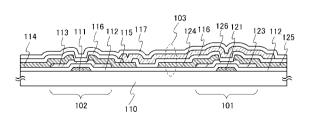

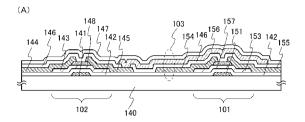

図3(A)に、図1(A)に示した回路構成を有するメモリセル100の、断面図の一例を示す。図3(A)に示すメモリセルは、記憶素子として機能するチャネル保護型のトランジスタ101と、スイッチング素子として機能するチャネル保護型のトランジスタ102とが、絶縁表面を有する基板140上に形成されている。

# [0066]

10

20

30

具体的に、トランジスタ101は、絶縁表面を有する基板140上に、第1のゲート電極151と、第1のゲート電極151上の絶縁膜142と、絶縁膜142を間に挟んで第1のゲート電極151と重なる、活性層として機能する酸化物半導体膜153と、酸化物半導体膜153上においてゲート電極151と重なるチャネル保護膜157と、酸化物半導体膜153上のソース電極154、ドレイン電極155と、酸化物半導体膜153、チャネル保護膜157、ソース電極154及びドレイン電極155上の絶縁膜146と、絶縁膜146上において酸化物半導体膜153と重なっている第2のゲート電極156とを有している。また、第2のゲート電極156上には絶縁膜147が形成されており、トランジスタ101は絶縁膜147を構成要素に含んでいても良い。

#### [0067]

また、トランジスタ102は、絶縁表面を有する基板140上に、ゲート電極141と、ゲート電極141上の絶縁膜142と、絶縁膜142を間に挟んでゲート電極141と重なる、活性層として機能する酸化物半導体膜143と、酸化物半導体膜143上のチャネル保護膜148と、酸化物半導体膜143上のソース電極144及びドレイン電極145とを有している。酸化物半導体膜143、チャネル保護膜148、ソース電極144及びドレイン電極145上には絶縁膜146が形成されており、トランジスタ102は絶縁膜146を構成要素に含んでいても良い。

## [0068]

また、容量素子103は、トランジスタ101のソース電極154と、第2のゲート電極156とが、絶縁膜146を間に挟んで重なりあっている領域に形成されている。

## [0069]

チャネル保護膜157、チャネル保護膜148は、プラズマCVD法や熱CVD法などの化学気相成長法やスパッタリング法を用いて形成することができる。また、チャネル保護膜148には、酸素を含む無機材料(酸化珪素、酸化窒化珪素、窒化酸化珪素など)を用いることが望ましい。酸素を含む無機材料をチャネル保護膜157、チャネル保護膜148に用いることで、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜155、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜153、酸化物半導体膜153、最大地保護膜157、チャネル保護膜148とそれぞれ接する領域に酸素を供給し、ドナーとなる酸素欠損を低減して化学量論的組成比を満たす構成とすることが可能である。よって、チャネル形成領域を、1型化または実質的に1型化させることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。

#### [0070]

なお、チャネル形成領域とは、半導体膜のうち、ゲート絶縁膜を間に挟んでゲート電極と 重なる領域に相当する。記憶素子として用いるトランジスタの場合は、半導体膜のうち、 ソース電極とドレイン電極の間において、ゲート絶縁膜を間に挟んで、第1のゲート電極 または第2のゲート電極と重なる領域に相当する。

## [0071]

次いで、図3(B)に、図1(A)に示した回路構成を有するメモリセル100の、断面図の一例を示す。図3(B)に示すメモリセルは、記憶素子として機能するボトムコンタクト型のトランジスタ101と、スイッチング素子として機能するボトムコンタクト型のトランジスタ102とが、絶縁表面を有する基板160上に形成されている。

## [0072]

具体的に、トランジスタ101は、絶縁表面を有する基板160上に、第1のゲート電極 171と、第1のゲート電極171上の絶縁膜162と、絶縁膜162上のソース電極1 74及びドレイン電極175と、絶縁膜162を間に挟んで第1のゲート電極171と重 なっており、ソース電極174及びドレイン電極175と接している、活性層として機能 する酸化物半導体膜173と、酸化物半導体膜173、ソース電極174及びドレイン電 極175上の絶縁膜166と、絶縁膜166上において酸化物半導体膜173と重なって いる第2のゲート電極176とを有している。また、第2のゲート電極176上には絶縁 10

20

30

40

膜167が形成されており、トランジスタ101は絶縁膜167を構成要素に含んでいても良い。

# [0073]

また、トランジスタ102は、絶縁表面を有する基板160上に、ゲート電極161と、ゲート電極161上の絶縁膜162と、絶縁膜162上のソース電極164及びドレイン電極165と、絶縁膜162を間に挟んでゲート電極161と重なっており、ソース電極164及びドレイン電極165と接している、活性層として機能する酸化物半導体膜163と、を有している。酸化物半導体膜163、ソース電極164及びドレイン電極165上には絶縁膜166が形成されており、トランジスタ102は絶縁膜166を構成要素に含んでいても良い。

[0074]

また、容量素子103は、トランジスタ101のソース電極174と、第2のゲート電極 176とが、絶縁膜166を間に挟んで重なりあっている領域に形成されている。

[0075]

また、図1(A)、図3(A)、図3(B)では、記憶素子として機能するトランジスタ 101の活性層に、酸化物半導体膜が用いられている場合を例示しているが、上述したように、トランジスタ101の活性層に、酸化物半導体以外の、非晶質、微結晶、多結晶、または単結晶の、シリコン、またはゲルマニウムなどの半導体が用いられていても良い。 【0076】

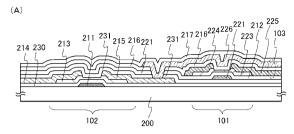

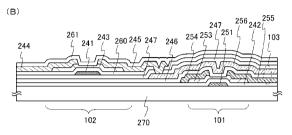

図4(A)に、記憶素子として機能するトランジスタ101の活性層に、シリコンを含む 半導体膜を用いた場合の、メモリセル100の断面図を、一例として示す。図4(A)に 示すメモリセルは、記憶素子として機能するトランジスタ101と、スイッチング素子と して機能するトランジスタ102とが、絶縁表面を有する基板200上に形成されている

[0077]

具体的に、トランジスタ102は、絶縁表面を有する基板200上に、ゲート電極211と、ゲート電極211上の絶縁膜230と、絶縁膜230を間に挟んでゲート電極211と重なる、活性層として機能する酸化物半導体膜213と、酸化物半導体膜213上のソース電極214及びドレイン電極215上には絶縁膜231が形成されており、トランジスタ102は絶縁膜231を構成要素に含んでいても良い。

[0078]

また、トランジスタ101は、絶縁表面を有する基板200上に形成された絶縁膜231上に、第1のゲート電極221と、第1のゲート電極221上の絶縁膜212と、絶縁膜212を間に挟んで第1のゲート電極221と重なる、シリコンを用いた活性層として機能する半導体膜223と、半導体膜223上のソース電極224、ドレイン電極225と、半導体膜223、ソース電極224及びドレイン電極225上の絶縁膜216と、絶縁膜216上において半導体膜223と重なっている第2のゲート電極226とを有している。また、第2のゲート電極226上には絶縁膜217が形成されており、トランジスタ101は絶縁膜217を構成要素に含んでいても良い。

[0079]

また、容量素子103は、トランジスタ101のドレイン電極225と、第2のゲート電極226とが、絶縁膜216を間に挟んで重なりあっている領域に形成されている。

[0800]

次いで、図4(B)に、記憶素子として機能するトランジスタ101の活性層に、シリコンを含む半導体膜を用いた場合の、メモリセル100の断面図を、一例として示す。図4(B)に示すメモリセルは、記憶素子として機能するトランジスタ101と、スイッチング素子として機能するトランジスタ102とが、絶縁表面を有する基板270上に形成されている。

[0081]

10

20

30

20

30

40

50

具体的に、トランジスタ102は、基板270上に形成された絶縁膜247上に、ゲート電極241と、ゲート電極241上の絶縁膜260と、絶縁膜260を間に挟んでゲート電極241と重なる、活性層として機能する酸化物半導体膜243と、酸化物半導体膜243上のソース電極244またはドレイン電極245とを有している。酸化物半導体膜243、ソース電極244及びドレイン電極245上には絶縁膜261が形成されており、トランジスタ102は絶縁膜261を構成要素に含んでいても良い。

#### [0082]

また、トランジスタ101は、基板270上に、第1のゲート電極251と、第1のゲート電極251上の絶縁膜242と、絶縁膜242を間に挟んで第1のゲート電極251と重なる、シリコンを用いた活性層として機能する半導体膜253と、半導体膜253上のソース電極254、ドレイン電極255と、半導体膜253、ソース電極254及びドレイン電極255上の絶縁膜246と、絶縁膜246上において半導体膜253と重なっている第2のゲート電極256とを有している。また、第2のゲート電極256上には絶縁膜247が形成されており、トランジスタ101は絶縁膜247を構成要素に含んでいても良い。

#### [0083]

また、容量素子103は、トランジスタ101のドレイン電極255と、第2のゲート電極256とが、絶縁膜246を間に挟んで重なりあっている領域に形成されている。

#### [0084]

なお、図4(A)と図4(B)に示したトランジスタ101は、ともにボトムゲート型である場合を例示しているが、トップゲート型であっても良いし、ボトムコンタクト型であっても良い。そして、トランジスタ101は、チャネルエッチ型であるが、チャネル保護型であっても良い。また、図4(A)と図4(B)に示したトランジスタ102は、ともにボトムゲート型である場合を例示しているが、トップゲート型であっても良いし、ボトムコンタクト型であっても良い。そして、トランジスタ102は、チャネルエッチ型であるが、チャネル保護型であっても良い。

# [0085]

## (実施の形態2)

本実施の形態では、複数のメモリセルを有する記憶装置の構成と、その駆動方法の一例について説明する。

## [0086]

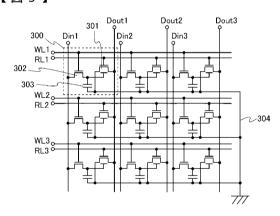

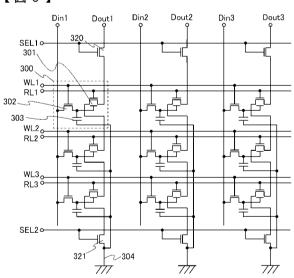

図 5 に、複数のメモリセル 3 0 0 がマトリクス状に接続された、NOR型の記憶装置のセルアレイの回路図を、一例として示す。図 5 に示す記憶装置が有する各メモリセル 3 0 0 の構成については、実施の形態 1 において、メモリセル 1 0 0 の構成について説明した内容を参酌することができる。

#### [0087]

具体的に、メモリセル300は、記憶素子として機能するトランジスタ301と、トランジスタ301の第2のゲート電極への電位の供給を制御することができる、スイッチング素子として機能するトランジスタ302とを有する。また、メモリセル300は、トランジスタ301の第2のゲート電極の電位を保持するための容量素子303が設けられていても良い。メモリセル300は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の回路素子を、さらに有していても良い。

## [0088]

図5に示すセルアレイでは、複数の入力用データ線 Din、複数の出力用データ線 Dout、複数の書き込み用ワード線 WL、複数の読み出し用ワード線 RLなどの各種配線が設けられており、セルアレイの駆動回路からの信号または電源電位が、これら配線を介して各メモリセル300に供給される。よって、上記配線の数は、メモリセル300の数及び配置によって決めることができる。

#### [0089]

具体的に、図5に示すセルアレイの場合、3行×3列のメモリセルがマトリクス状に接続

20

30

40

50

されており、少なくとも、入力用データ線Din1~Din3、出力用データ線Dout1~Dout3、書き込み用ワード線WL1~WL3、読み出し用ワード線RL1~RL3が、セルアレイ内に配置されている場合を例示している。

#### [0090]

そして、上記配線と、メモリセル300内の回路素子との接続構造について、入力用データ線Din1、出力用データ線Dout1、書き込み用ワード線WL1、読み出し用ワード線RL1に接続されているメモリセル300のひとつを例に挙げ、説明する。トランジスタ302のゲート電極は、書き込み用ワード線WL1に接続されている。そして、トランジスタ302は、ソース電極とドレイン電極のうち、いずれか一方が入力用データ線Din1に接続され、他方が、トランジスタ301の第2のゲート電極に接続されている。また、トランジスタ301の第1のゲート電極は、読み出し用ワード線RL1に接続されている。そして、トランジスタ301は、ソース電極とドレイン電極のうち、いずれか一方が出力用データ線Dout1に接続され、他方がグラウンドなどの固定電位が与えられている電源線304に接続されている。

### [0091]

また、容量素子303が有する一対の電極は、一方がトランジスタ301の第2のゲート電極に接続されており、他方がグラウンドなどの固定電位が与えられている電源線304に接続されている。

#### [0092]

また、図6に、複数のメモリセル300が直列に接続された、NAND型の記憶装置のセルアレイの回路図を、一例として示す。図6に示す記憶装置が有する各メモリセルの構成は、図5と同じであり、実施の形態1において、メモリセル100の構成について説明した内容を参酌することができる。

#### [0093]

図6に示すセルアレイの場合、3つのメモリセルが直列に接続されたセルアレイを3列分配置した場合を例示している。具体的には、3×3のメモリセルを備えるセルアレイで、入力用データ線Din1~Din3、出力用データ線Dout1~Dout3、書き込み用ワード線WL1~WL3、読み出し用ワード線RL1~RL3、選択信号線SEL1~SEL2、電源線304が、セルアレイ内に配置されている場合を例示している。セルアレイの駆動回路からの信号または電源電位が、これら配線を介して各メモリセルに供給される。よって、上記配線の数は、メモリセル300の数によって決めることができる。

# [0094]

次いで、上記配線と、メモリセル300内の回路素子との接続構造について説明する。例えば、入力用データ線Din1、出力用データ線Dout1、書き込み用ワード線WL1、読み出し用ワード線RL1に接続されているメモリセル300に着目すると、トランジスタ302のゲート電極は、書き込み用ワード線WL1に接続されている。そして、トランジスタ302は、ソース電極とドレイン電極のうち、いずれか一方が入力用データ線Din1に接続され、他方が、トランジスタ301の第2のゲート電極に接続されている。また、トランジスタ301のゲート電極は、読み出し用ワード線RL1に接続されている。そして、トランジスタ301は、出力用データ線Dout1とグラウンドなどの固定電位が与えられている電源線304の間において、隣接するメモリセルどうしで直列に接続されている。

## [0095]

また、容量素子303が有する一対の電極は、一方がトランジスタ301の第2のゲート 電極に接続されており、他方がグラウンドなどの固定電位が与えられている電源線304 に接続されている。

#### [0096]

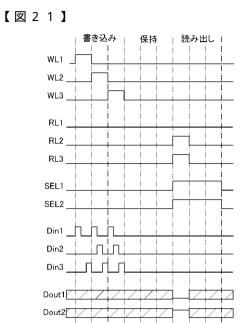

次いで、図6に示すセルアレイを例に挙げ、本発明の一態様に係る記憶装置の動作について、図21を用いて説明する。図21は、各配線に入力される信号の電位の時間変化を示すタイミングチャートであり、トランジスタ301及びトランジスタ302がnチャネル

型であり、なおかつ2値のデータを扱う場合を例示している。

### [0097]

まず、データの書き込み時における記憶装置の動作について説明する。書き込み時において、書き込み用ワード線WL1にパルスを有する信号が入力されると、当該パルスの電位、具体的にはハイレベルの電位が、トランジスタ302のゲート電極に与えられる。そして、書き込み用ワード線WL1にゲート電極が接続されているトランジスタ302は、全てオンになる。一方、読み出し用ワード線RL1にはローレベルの電位が入力されることで、トランジスタ301の第1のゲート電極にはローレベルの電位が与えられる。そして、読み出し用ワード線RL1に第1のゲート電極が接続されているトランジスタ301は、全てオフになる。

[0098]

そして、入力用データ線 Din1~Din3に、順に、データを情報として含む信号が入力される。図21では、入力用データ線 Din1と入力用データ線 Din3にはハイレベルの電位を有する信号を入力し、入力用データ線 Din2にはローレベルの電位を有する信号が入力されている場合を例示している。入力用データ線 Din1~Din3に入力される信号の電位のレベルは、データの内容によって当然異なる。

[0099]

入力用データ線 D i n 1 ~ D i n 3 に入力されている電位は、オンのトランジスタ 3 0 2 を介して、トランジスタ 3 0 1 が有する第 2 のゲート電極に与えられる。そして、第 2 のゲート電極の電位に従って、トランジスタ 3 0 1 の閾値電圧のシフト量が決まる。具体的には、入力用データ線 D i n 1 に接続されているメモリセル 3 0 0 にはハイレベルの電位を有する信号が入力されているので、入力用データ線 D i n 1 に接続されているメモリセル 3 0 0 において、トランジスタ 3 0 1 の第 2 のゲート電極の電位は、ハイレベルとなっている。つまり、当該メモリセル 3 0 0 において、記憶素子として機能するトランジスタ 3 0 1 は、図 2 における線 1 3 0 に従って動作する。一方、入力用データ線 D i n 2 にはローレベルの電位を有する信号が入力されているので、入力用データ線 D i n 2 に接続されているメモリセル 3 0 0 において、トランジスタ 3 0 1 の第 2 のゲート電極の電位は、ローレベルとなっている。つまり、当該メモリセル 3 0 0 において、記憶素子として機能するトランジスタ 3 0 1 は、図 2 における線 1 3 1 に従って動作する。

[0100]

書き込み用ワード線WL1への、パルスを有する信号の入力が終了すると、書き込み用ワード線WL1にゲート電極が接続されているトランジスタ302が、全てオフになる。そして、書き込み用ワード線WL2、書き込み用ワード線WL3に、パルスを有する信号が順に入力され、書き込み用ワード線WL2を有するメモリセル、書き込み用ワード線WL3を有するメモリセルにおいて、上述した動作が同様に繰り返される。

[0101]

次いで、データの保持時における記憶装置の動作について説明する。保持時において、全ての書き込み用ワード線WL1~WL3には、トランジスタ302がオフとなるレベルの電位、具体的にはローレベルの電位が与えられる。トランジスタ302は、上述したようにオフ電流が著しく低いので、第2のゲート電極の電位は、書き込み時において設定されたレベルを保持する。また、全ての読み出し用ワード線RL1~RL3には、ローレベルの電位が与えられている。

[0102]

図 2 1 のタイミングチャートではデータを保持する動作を説明するために保持期間を設けている。しかし、実際のメモリの動作においては保持期間を設けなくとも良い。

[0103]

次いで、データの読み出し時における記憶装置の動作について説明する。読み出し時において、全ての書き込み用ワード線WL1~WL3には、保持時と同様に、トランジスタ302がオフとなるレベルの電位、具体的にはローレベルの電位が与えられる。

10

20

30

40

20

30

40

50

#### [0104]

NAND型の記憶装置は、出力用データ線とグラウンドなどの固定電位が与えられている電源線の間において、隣接するメモリセルどうしが直列に接続されている。とあるメモリセルのデータを読み出したい場合、当該メモリセルと同一の出力用データ線に接続されているメモリセルを制御することで、当該メモリセルが接続された出力用データ線が、グラウンドなどの固定電位が与えられている電源線と導通するか否かで、記憶されている 2 値を区別することができる。

## [0105]

具体的には、入力用データ線Din1、出力用データ線Dout1、書き込み用ワード線WL1、読み出し用ワード線RL1に接続されているメモリセル300に着目し、当該該メモリセル300に結信されたハイレベルのデータを読み出す場合について考える。当上1をリセル300が接続されている出力用データ線Dout1を選択するために、SEL1およびSEL2をハイレベルの電位にし、SEL1に接続されたトランジスタ321をオンする。そして、当該メモリセル300内のトランジスタ301の第1のゲート電極に接続された読み出し用ワード線RL1に持続された見つレベルの電位をする。では読み出し用ワード線RL2~RL3にバイレベルの電位をオンジスタ301をオンジスタ301をオンジスタ301をオンジスタ301に表別でより、第2のゲート電極にハイレベルのデジスのが書き込まれている。つまり、図2において示した、記憶素子として機能するトラスのが書き込まれている。つまり、図2において示した、記憶素子として機能するトラスのより、別値電圧はマイナス側にシフトし、Vth1となっている。したがって、出力用データ線Dout1に接続されたトランジスタは全てオンとなり、出力用データ線Dout1に接続されている電源線と導通し、グラウンドとおおよそ同じ電位になる。

#### [0106]

続いて、入力用データ線 Din2、出力用データ線 Dout2、書き込み用ワード線 WL1、読み出し用ワード線 RL1に接続されているメモリセル300に着目し、当該メモリセル300に記憶されたローレベルのデータを読み出す場合を考える。出力用データ線 Dout2を選択するために、SEL1およびSEL2をハイレベルの電位にし、SEL1に接続されたトランジスタ321をオンする。そして、当該メモリセル300内のトランジスタ301の第1のゲート電極に接にされた読み出し用ワード線 RL1はローレベルにする。さらに、読み出し用ワード線 RL2~RL3に接続されたランジスタ301は月ワード線 RL2~RL3に接続されたランジスタ301をオンする。当該メモリセル300のトランジスタ301はた、第2のゲート電極にローレベルのデータが書き込まれている。つまり、図2において示い、第2のゲート電極にローレベルのデータが書き込まれている。のまり、図2において示した、記憶素子として機能するトランジスタ301の動作に従い、閾値電圧はシフトせず、、出力用データ線 Dout2はグラウンドが与えられている電源線とは導通せずに、ハイインピーダンス状態となる。

## [0107]

なお、各出力用データ線 Doutの先には読み出し回路が接続されており、読み出し回路の出力信号がメモリの実際の出力となる。

#### [0108]

なお、本実施の形態においては、データの読み出し時において出力用データ線を選択するに当たり、SEL1およびSEL2の二つの選択信号線とそれぞれの信号線にゲート電極が接続されたトランジスタを用いた場合を例示している。データの読み出し時における出力用データ線の選択は、出力用データ線とそれにつながる読み出し回路との導通、非導通を選択出来ればよいので、少なくとも一つの選択信号線とその選択信号線に接続されたトランジスタがあればよい。

#### [0109]

本実施の形態では、書き込み、保持、読み出し、の各動作を、複数のメモリセルにおいて

順に行う駆動方法について説明したが、本発明はこの構成に限定されない。指定されたア ドレスのメモリセルにおいてのみ、上記動作を行うようにしても良い。

#### [0110]

また、図6に示したセルアレイの場合、各メモリセルに、入力用データ線 Din、出力用データ線 Dout、書き込み用ワード線 WL、読み出し用ワード線 RLの4つの配線が接続されている場合を例示しているが、本発明の記憶装置において、各メモリセルに接続されている配線の数はこれに限定されない。トランジスタ301のスイッチングを制御するための信号、トランジスタ301が有する第2のゲート電極に電位を供給するための信号を、メモリセル300に供給することができ、なおかつ、トランジスタ301のドレイン電流、またはソース電極とドレイン電極間の抵抗値が、情報として含まれる電位を、駆動回路に送ることができるように、配線の数及び接続構造を、適宜決めれば良い。

#### [0111]

なお、図21に示したタイミングチャートにおいて、出力用データ線Dout1、Dout2およびDout3の斜線部はデータが不確定な状態を表している。また、各信号の立ち上がりは垂直に立ち上げ、各信号の立ち下がりは垂直に立ち下げているが、実際の各信号は信号線の負荷やノイズ等の影響を受けるため各信号の波形が鈍ることは当業者であれば容易に理解される。

#### [0112]

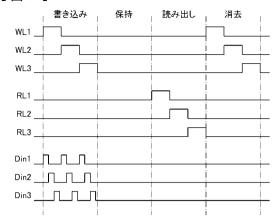

次いで、図5に示すセルアレイを例に挙げ、本発明の一態様に係る記憶装置の動作について、図7を用いて説明する。図7は、各配線に入力される信号の電位の時間変化を示すタイミングチャートであり、トランジスタ301及びトランジスタ302がnチャネル型であり、なおかつ2値のデータを扱う場合を例示している。

# [0113]

まず、データの書き込み時における記憶装置の動作について説明する。書き込み時において、書き込み用ワード線WL1に、パルスを有する信号が入力されると、当該パルスの電位、具体的にはハイレベルの電位が、ゲート電極に与えられることで、書き込み用ワード線WL1にゲート電極が接続されているトランジスタ302が、全てオンになる。一方、読み出し用ワード線RL1には、記憶素子として機能するトランジスタの動作について示した図2のVthヵよりも低い電位を有する信号が入力されており、読み出し用ワード線RL1に第1のゲート電極が接続されているトランジスタ301は、全てオフを維持する

### [0114]

そして、入力用データ線 Din1~Din3に、順に、データを情報として含む信号が入力される。図7では、入力用データ線 Din1~Din3の全てに、ハイレベルの電位を有する信号が入力されている場合を例示しているが、入力用データ線 Din1~Din3に入力される信号の電位のレベルは、データの内容によって当然異なる。また、2値のデータを扱う場合は、入力用データ線 Din1~Din3に入力される信号の電位が電源電圧に相当する電位(例えば Vddと Vss)の2値であれば良いが、3値以上の多値のデータを扱う場合は、その扱うデータに用いられている基数に合わせて、電位のレベルの数を決めればよい。

## [0115]

入力用データ線 D i n 1 ~ D i n 3 に入力されている電位は、オンのトランジスタ 3 0 2 を介して、トランジスタ 3 0 1 が有する第 2 のゲート電極に与えられる。そして、第 2 のゲート電極の電位に従って、トランジスタ 3 0 1 の閾値電圧のシフト量が決まる。

# [0116]

書き込み用ワード線WL1への、パルスを有する信号の入力が終了すると、書き込み用ワード線WL1にゲート電極が接続されているトランジスタ302が、全てオフになる。そして、書き込み用ワード線WL2、書き込み用ワード線WL3に、パルスを有する信号が順に入力され、書き込み用ワード線WL2を有するメモリセル、書き込み用ワード線WL

10

20

30

40

3を有するメモリセルにおいて、上述した動作が同様に繰り返される。

#### [0117]

次いで、データの保持時における記憶装置の動作について説明する。保持時において、全ての書き込み用ワード線WL1~WL3には、トランジスタ302がオフとなるレベルの電位、具体的にはローレベルの電位が与えられる。トランジスタ302は、上述したようにオフ電流が著しく低いので、第2のゲート電極の電位は、書き込み時において設定されたレベルを保持する。また、全ての読み出し用ワード線RL1~RL3には、トランジスタ301がオフとなるレベルの電位、具体的には記憶素子として機能するトランジスタの動作について示した図2のVth1よりも低い電位が与えられる。

#### [0118]

図 7 のタイミングチャートではデータを保持する動作を説明するために保持期間を設けている。しかし、実際のメモリの動作においては保持期間を設けなくとも良い。

#### [0119]

次いで、データの読み出し時における記憶装置の動作について説明する。読み出し時において、全ての書き込み用ワード線WL1~WL3には、保持時と同様に、トランジスタ302がオフとなるレベルの電位、具体的にはローレベルの電位が与えられる。

## [0120]

一方、読み出し時において、読み出し用ワード線RL1~RL3には、パルスを有する信号が順に入力される。具体的には、まず、読み出し用ワード線RL1に、パルスを有する信号が入力されると、当該パルスの電位、具体的には、記憶素子として機能するトランジスタの動作について示した図2のVth1よりも高くVth0よりも低い電位、あるいは、Vth0よりも高い電位が、トランジスタ301の第1のゲート電極に与えられる。トランジスタ301では、第1のゲート電極に記憶素子として機能するトランジスタの動作について示した図2のVth1よりも高くVth0よりも低い電位、あるいは、Vth0よりも高い電位が与えられると、直前の書き込み時において設定された閾値電圧に従って、そのドレイン電流、またはソース電極とドレイン電極間の抵抗値が定まる。

### [0121]

そして、トランジスタ301のドレイン電流、またはソース電極とドレイン電極間の抵抗値が、情報として含まれる電位、すなわちトランジスタ301が有するソース電極とドレイン電極のうち、出力用データ線Dout1~Dout3に接続されている方の電極の電位が、出力用データ線Dout1~Dout3を介して駆動回路に供給される。

# [0122]

なお、出力用データ線 Dout1~Dout3に供給される電位は、メモリセルに書き込まれているデータに従って、そのレベルが決まる。よって、理想的には、複数のメモリセルに同じ値のデータが記憶されているならば、当該メモリセルに接続された全ての出力用データ線には、同じレベルの電位が供給されているはずである。しかし、実際には、トランジスタ301またはトランジスタ302の特性が、メモリセル間においてばらついている場合があるため、読み出されるはずのデータが全て同じ値であっても、出力用データ線に供給される電位にばらつきが生じ、その分布に幅を有することがある。よって、出力用データ線 Dout1~Dout3に供給される電位に多少のばらつきが生じていても、上記電位から、読み出されたデータを情報として含み、なおかつ、所望の仕様に合わせて振幅、波形が処理された信号を形成することができる読み出し回路を、駆動回路として記憶装置に設ける。

# [0123]

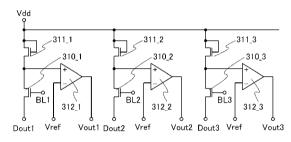

図9に、読み出し回路の一例を回路図で示す。図9に示す読み出し回路は、出力用データ線Dout1~Dout3の電位の、読み出し回路への入力を制御するためのスイッチング素子として機能するトランジスタ310\_1~310\_3と、抵抗として機能するトランジスタ311\_1~311\_3とを有する。また、図9に示す読み出し回路は、オペアンプ312\_1~312\_3を有している。

# [0124]

50

40

10

20

20

30

40

50

具体的に、トランジスタ311\_1~311\_3は、それぞれ、そのゲート電極とドレイン電極が接続されており、なおかつ、ゲート電極及びドレイン電極にハイレベルの電源電位 V d d が与えられている。また、トランジスタ311\_1~311\_3は、ソース電極が、オペアンプ312\_1~312\_3の非反転入力端子(+)に接続されている。よって、トランジスタ311\_1~311\_3は、電源電位 V d d が与えられているノードと、オペアンプ312\_1~312\_3の非反転入力端子(+)との間に接続された、抵抗として機能する。なお、図9では、ゲート電極とドレイン電極が接続されたトランジスタを抵抗として用いたが、本発明はこれに限定されず、抵抗として機能する素子であれば代替が可能である。

## [0125]

また、スイッチング素子として機能するトランジスタ310\_1~310\_3は、ゲート電極がビット線BL1~BL3にそれぞれ接続されている。そして、ビット線BL1~BL3の電位に従って、出力用データ線Dout1~Dout3と、トランジスタ311\_1~311\_3のソース電極との間の接続が制御される。

## [0126]

例えば、トランジスタ310\_1がオンになると、メモリセル300内のトランジスタ301と、読み出し回路内のトランジスタ311\_1とが、直列に接続されるので、当該接続のノードにおける電位Vdataが、オペアンプ312\_1~312\_3の非反転入力端子(+)に与えられることになる。そして、電位Vdataの高さは、トランジスタ301のソース電極とドレイン電極間の抵抗値と、トランジスタ311\_1のソース電極とドレイン電極間の抵抗値の比に従って決まるので、電位Vdataのレベルには、読み出されたデータの値が反映されている。

# [0127]

一方、オペアンプ312\_1~312\_3の反転入力端子(・)には、基準電位Vrefが与えられている。そして、非反転入力端子(+)に与えられる電位Vdataが、基準電位Vrefに対して高いか低いかにより、出力端子の電位Voutのレベルを異ならせることができ、それにより、間接的にデータを情報として含む信号を得ることができる。

#### [0128]

なお、同じ値のデータが記憶されているメモリセルであっても、メモリセル間の特性のばらつきにより、読み出された電位 V d a t a のレベルにもばらつきが生じ、その分布に幅を有する場合がある。よって、基準電位 V r e f のレベルは、データの値を正確に読み取るために、ノードの電位 V d a t a のばらつきを考慮して定める。

#### [0129]

また、図9では、データの読み出しに用いるオペアンプは、各出力用データ線に1つ用いているが、オペアンプの数はこれに限定されない。n値(nは2以上の自然数)のデータを扱う場合は、各出力用データ線に用いるオペアンプの数を、(n - 1)とする。

# [0130]

次いで、データの消去時における記憶装置の動作について説明する。消去時では、データの書き込み時と同様に、書き込み用ワード線WL1に、パルスを有する信号が入力されると、当該パルスの電位、具体的にはハイレベルの電位が、ゲート電極に与えられることで、書き込み用ワード線WL1にゲート電極が接続されているトランジスタ302は、全てオンになる。一方、読み出し用ワード線RL1には、記憶素子として機能するトランジスタの動作について示した図2のVth1よりも低い電位を有する信号が入力されており、読み出し用ワード線RL1に第1のゲート電極が接続されているトランジスタ301は、全てオフを維持する。

# [0131]

そして、入力用データ線Din1~Din3に、グラウンドなどの固定電位が与えられる。図7では、入力用データ線Din1~Din3の全てに、ローレベルの電位を有する信号が入力されている場合を例示している。入力用データ線Din1~Din3に入力されているローレベルの固定電位は、オンのトランジスタ302を介して、トランジスタ30

20

30

40

50

1が有する第2のゲート電極に与えられる。そして、第2のゲート電極の電位に従って、 トランジスタ301の閾値電圧の値はリセットされる。

#### [0132]

書き込み用ワード線WL1への、パルスを有する信号の入力が終了すると、書き込み用ワード線WL1にゲート電極が接続されているトランジスタ302が、全てオフになる。そして、書き込み用ワード線WL2、書き込み用ワード線WL3に、パルスを有する信号が順に入力され、書き込み用ワード線WL2を有するメモリセル、書き込み用ワード線WL3を有するメモリセルにおいて、上述した動作が同様に繰り返される。

## [0133]

図 7 のタイミングチャートではデータを消去する動作を説明するために消去期間を設けている。しかし、実際のメモリの動作においては消去期間を設けなくとも良く、この場合、先に書き込んだデータに上書きするように、別のデータを書き込むようにすれば良い。消去期間を設けなくても良いことが、本発明の一態様に係る記憶装置の利点の一つである。 【 0 1 3 4 】

また、本実施の形態では、書き込み、保持、読み出し、消去の動作を、複数のメモリセルにおいて順に行う駆動方法について説明したが、本発明はこの構成に限定されない。指定されたアドレスのメモリセルにおいてのみ、上記動作を行うようにしても良い。

### [ 0 1 3 5 ]

また、図5に示したセルアレイの場合、各メモリセルに、入力用データ線 Din、出力用データ線 Dout、書き込み用ワード線 WL、読み出し用ワード線 RLの4つの配線が接続されている場合を例示しているが、本発明の記憶装置において、各メモリセルに接続されている配線の数はこれに限定されない。トランジスタ301のスイッチングを制御するための信号、トランジスタ301が有する第2のゲート電極に電位を供給するための信号を、メモリセル300に供給することができ、なおかつ、トランジスタ301のドレイン電流、またはソース電極とドレイン電極間の抵抗値が、情報として含まれる電位を、駆動回路に送ることができるように、配線の数及び接続構造を、適宜決めれば良い。

#### [0136]

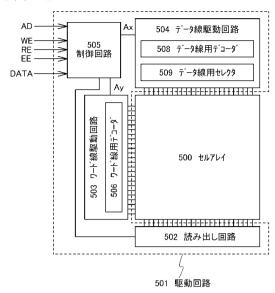

次いで、図5に示すセルアレイを用いた記憶装置を例に挙げ、本発明の一態様に係る記憶装置の、駆動回路の構成について説明する。

## [0137]

図 8 に、本発明の一態様に係る記憶装置の構成を、一例としてブロック図で示す。なお、図 8 に示すブロック図では、記憶装置内の回路を機能ごとに分類し、互いに独立したブロックとして示しているが、実際の回路は機能ごとに完全に切り分けることが難しく、一つの回路が複数の機能に係わることもあり得る。

#### [0138]

図8に示す記憶装置は、複数のメモリセルがマトリクス状に接続されたセルアレイ500と、セルアレイ500の駆動を制御する駆動回路501とを有している。そして、駆動回路501は、セルアレイ500から読み出されたデータを情報として含む信号を生成する読み出し回路502と、セルアレイ500が有するメモリセルを、行ごとに選択するワード線駆動回路503と、選択されたメモリセルにおけるデータの書き込みまたは消去を制御するデータ線駆動回路504と、読み出し回路502、ワード線駆動回路503は、データ線駆動回路503は、ワード線用デコーダ506を有する。また、データ線駆動回路504は、データ線用デコーダ508と、データ線用セレクタ509とを有する。

# [0139]

なお、本発明の一態様に係る記憶装置は、少なくともセルアレイ 5 0 0 をその構成に含んでいればよい。本発明の一態様に係る記憶装置は、セルアレイと、セルアレイに駆動回路の一部または全てが接続された状態にあるメモリモジュールとを、その範疇に含む。メモリモジュールは、プリント配線基板等に実装することが可能な接続端子が設けられ、なお

かつ樹脂等で保護された、所謂パッケージングされた状態であっても良い。

## [0140]

また、上記駆動回路501の全てまたは一部は、セルアレイ500と共に、一の基板上に形成されていても良いし、セルアレイ500とは異なる基板に形成されていても良い。駆動回路501の全てまたは一部と、セルアレイ500とが異なる基板に形成されている場合、FPC(Flexible Printed Circuit)などを介してセルアレイ500と駆動回路501の全てまたは一部とを接続することができる。この場合、駆動回路501の一部がFPCにCOF(Chip On Film)法を用いて接続されていても良い。また、COG(Chip On Glass)法を用いて、駆動回路501の全てまたは一部がセルアレイ500に接続されていても良い。

# [0141]

セルアレイ500と、駆動回路501とを、共に一つの基板上に形成することで、記憶装置に接続する外部回路の部品点数が減るので、組立工程や検査工程の削減によるコストダウンを図ることができる。また、記憶装置と外部回路の接続部における、接点の数を減らすことができるので、接続不良に起因する歩留まり低下を防ぎ、接続箇所における機械的強度の低さによる信頼性の低下を防ぐことができる。また、ワード線駆動回路503、データ線用セレクタ509などの、駆動周波数が他の回路よりも比較的低い回路だけを、セルアレイ500と共に一つの基板上に形成することも可能である。このように、部分的に駆動回路501をセルアレイ500と共に一つの基板上に形成することで、上述した接続不良に起因する歩留まりの低下や、接続箇所における機械的強度の低さなどの回避、組立工程や検査工程の削減によるコストダウン、といったメリットをある程度享受できる。さらに、セルアレイ500、駆動回路501を全て一基板上に形成する場合に比べて、駆動周波数が高い回路の性能をより高めることができる。

#### [0142]

記憶装置にアドレス(Ax、Ay)を情報として含む信号ADが入力されると、制御回路505は、アドレスの列方向に関する情報であるアドレスAxをデータ線駆動回路504に送り、アドレスの行方向に関する情報であるアドレスAyをワード線駆動回路503に送る。また、制御回路505は、記憶装置に入力されたデータを情報として含む信号DATAを、データ線駆動回路504に送る。

# [0143]

データの書き込みを行なうか、読み出しを行なうか、消去を行うかの、動作の選択は、制御回路 5 0 5 に供給されるRE(Read enable)、WE(Write enable)、EE(Erase enable)などの信号によって選択される。なお、記憶装置に複数のセルアレイ 5 0 0 が設けられている場合、制御回路 5 0 5 に、セルアレイを選択するための信号 CE(Chip enable)が入力されていても良い。

#### [0144]

信号WEによって書き込みの動作が選択されると、制御回路505からの指示に従って、ワード線駆動回路503が有するワード線用デコーダ506により、アドレスAyに対応する書き込み用ワード線WLに、パルスを有する信号が入力される。一方、信号WEによって書き込みの動作が選択されると、制御回路505からの指示に従って、データ線駆動回路504では、データ線用デコーダ508からデータ線用セレクタ509の動作を制御する信号が、データ線用セレクタ509に与えられる。データ線用セレクタ509では、データ線用デコーダ508からの信号に従って、データを情報として含む信号DATAをサンプリングし、アドレスAxに対応する入力用データ線Dinにサンプリングした信号を入力する。

# [0145]

信号REによって読み出しの動作が選択されると、制御回路505からの指示に従って、ワード線駆動回路503が有するワード線用デコーダ506により、アドレスAyに対応する読み出し用ワード線RLに、パルスを有する信号が入力される。一方、信号REによって読み出しの動作が選択されると、制御回路505からの指示に従って、読み出し回路

10

20

30

40

## [0146]

信号 E E によって消去の動作が選択されると、制御回路 5 0 5 からの指示に従って、ワード線駆動回路 5 0 3 が有するワード線用デコーダ 5 0 6 により、該当するアドレス A y の書き込み用ワード線W L に、パルスを有する信号が入力される。一方、信号 E E によって消去の動作が選択されると、制御回路 5 0 5 からの指示に従って、データ線駆動回路 5 0 4 では、データ線用デコーダ 5 0 8 からデータ線用セレクタ 5 0 9 の動作を制御する信号が、データ線用セレクタ 5 0 9 では、データ線用デコーダ 5 0 8 からの信号に従って、データを消去するための信号を、該当するアドレス A x の入力用データ線 D i n に入力する。

## [0147]

なお、図 8 に示す記憶装置では、ワード線駆動回路 5 0 3 により、書き込み用ワード線W L への信号の入力と、読み出し用ワード線 R L への信号の入力とを、両方制御しているが、本発明はこの構成に限定されない。書き込み用ワード線 W L への信号の入力を制御する駆動回路と、読み出し用ワード線 R L への信号の入力を制御する駆動回路とを、それぞれ記憶装置に設けるようにしても良い。

#### [0148]

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

## [0149]

#### (実施の形態3)

チャネルエッチ構造のボトムゲート型のトランジスタを例に挙げ、本発明の一態様に係る記憶装置の作製方法について説明する。なお、本実施の形態では、記憶素子として機能するトランジスタとが、共に酸化物半導体膜を活性層として用いる場合を例に挙げて、説明する。

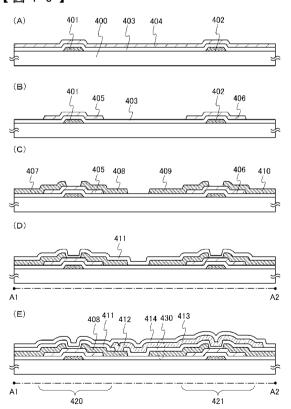

## [0150]

図 1 0 ( A ) に示すように、基板 4 0 0 上にゲート電極 4 0 1、ゲート電極 4 0 2 を形成する。

# [0151]

絶縁表面を有する基板 4 0 0 として使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、フュージョン法やフロート法で作製されるガラス基板を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 7 3 0 以上のものを用いると良い。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、一般に、酸化ホウ素と比較して酸化バリウム(BaO)を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、B2O3よりBaOを多く含むガラス基板を用いることが好ましい。

#### [0152]

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いても良い。他にも、結晶化ガラスなどを用いることができる。ステンレス合金などの金属基板の表面に絶縁膜を設けた基板を用いても良い。

# [0153]

また、プラスチック等の可撓性を有する合成樹脂からなる基板は、耐熱温度が一般的に低い傾向にあるが、後の作製工程における処理温度に耐え得るのであれば、基板400として用いることが可能である。プラスチック基板として、ポリエチレンテレフタレート(PET)に代表されるポリエステル、ポリエーテルスルホン(PES)、ポリエチレンナフ

10

20

30

40

20

30

40

50

タレート(PEN)、ポリカーボネート(PC)、ポリエーテルエーテルケトン(PEEK)、ポリスルホン(PSF)、ポリエーテルイミド(PEI)、ポリアリレート(PAR)、ポリブチレンテレフタレート(PBT)、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。

# [ 0 1 5 4 ]

基板 4 0 0 と、ゲート電極 4 0 1 及びゲート電極 4 0 2 との間に、下地膜となる絶縁膜を形成しておいても良い。下地膜として、例えば、酸化珪素膜、酸化窒化珪素膜、窒化珪素膜、窒化酸化珪素膜、窒化皮ルミニウム膜、または窒化酸化アルミニウム膜のいずれか 1 つを単層で、或いは複数を積層させて用いることができる。特に、下地膜に、バリア性の高い絶縁膜、例えば窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などを用いることで、水分または水素などの雰囲気中の不純物、或いは基板 4 0 0 内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体膜内、ゲート絶縁膜内、或いは、酸化物半導体膜と他の絶縁膜の界面とその近傍に入り込むのを防ぐことができる。

#### [0155]

なお、本明細書において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い物質をいう。

# [0156]

ゲート電極401、ゲート電極402の材料は、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等の金属材料、これら金属材料を主成分とする合金材料を用いた導電膜、或いはこれら金属の窒化物を、単層で又は積層で用いることができる。なお、後の工程において行われる加熱処理の温度に耐えうるのであれば、上記金属材料としてアルミニウム、銅を用いることも出来る。アルミニウムまたは銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等を用いることができる。

## [0157]

例えば、二層の積層構造を有するゲート電極 4 0 1、ゲート電極 4 0 2 として、アルミニウム膜上にモリブデン膜が積層された二層の積層構造、銅膜上にモリブデン膜を積層した二層構造、銅膜上に窒化チタン膜若しくは窒化タンタル膜を積層した二層構造、または、窒化チタン膜とモリブデン膜とを積層した二層構造とすることが好ましい。 3 層の積層構造を有するゲート電極 4 0 1、ゲート電極 4 0 2 としては、アルミニウム膜、アルミニウムとシリコンの合金膜、アルミニウムとチタンの合金膜またはアルミニウムとネオジムの合金膜を中間層とし、タングステン膜、窒化タングステン膜、窒化チタン膜またはチタン膜を上下層として積層した構造とすることが好ましい。

## [0158]

また、ゲート電極 4 0 1、ゲート電極 4 0 2 に酸化インジウム膜、酸化インジウム酸化スズ合金膜、酸化インジウム酸化亜鉛合金膜、酸化亜鉛膜、酸化亜鉛アルミニウム膜、酸窒化亜鉛アルミニウム膜、または酸化亜鉛ガリウム膜等の透光性を有する酸化物導電膜を用いることで、画素部の開口率を向上させることができる。

# [0159]

ゲート電極401、ゲート電極402の膜厚は、10nm~400nm、好ましくは10 0nm~200nmとする。本実施の形態では、タングステンターゲットを用いたスパッ タ法により150nmのゲート電極用の導電膜を形成した後、該導電膜をエッチングによ り所望の形状に加工(パターニング)することで、ゲート電極401、ゲート電極402 を形成する。なお、形成されたゲート電極の端部がテーパ形状であると、上に積層するゲート絶縁膜の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法 で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用 しないため、製造コストを低減できる。

## [0160]

次いで、ゲート電極 4 0 1、ゲート電極 4 0 2 上に、ゲート絶縁膜 4 0 3 を形成する。ゲート絶縁膜 4 0 3 は、プラズマ C V D 法又はスパッタリング法等を用いて、酸化珪素膜、窒化珪素膜、酸化室化理素膜、窒化酸化理素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化ハフニウム膜または酸化タンタル膜を単層で又は積層させて形成することができる。ゲート絶縁膜 4 0 3 は、水分や、水素などの不純物を極力含まないことが望ましい。スパッタリング法により酸化珪素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

[0161]

不純物を除去することによりi型化又は実質的にi型化された酸化物半導体(高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、高純度化された酸化物半導体とゲート絶縁膜403との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁膜(GI)は、高品質化が要求される。

[0162]

例えば、 $\mu$ 波(2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁膜とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

[ 0 1 6 3 ]

もちろん、ゲート絶縁膜として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁膜の膜質、ゲート絶縁膜と酸化物半導体との界面特性が改善される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、ゲート絶縁膜と酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

[0164]

バリア性の高い材料を用いた絶縁膜と、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜とを積層させた構造を有するゲート絶縁膜403を形成しても良い。この場合、酸化珪素膜、酸化窒化珪素膜などの絶縁膜は、バリア性の高い絶縁膜と酸化物半導体膜の間に形成する。バリア性の高い絶縁膜として、例えば窒化珪素膜、窒化酸化珪素膜、窒化酸化する。バリア性の高い絶縁膜を用いることで、水分または水素などの雰囲気中の不純物、或いは基板内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体膜内、ゲート絶縁膜403内、或いは、酸化物半導体膜と他の絶縁膜の界面とその近傍に入り込むのを防ぐことができる。また、酸化物半導体膜に接するように窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い絶縁膜が直接酸化物半導体膜に接するのを防ぐことができる。

[0165]

例えば、第1のゲート絶縁膜としてスパッタリング法により膜厚 5 0 n m 以上 2 0 0 n m 以下の窒化珪素膜(SiN<sub>y</sub>(y > 0))を形成し、第1のゲート絶縁膜上に第2のゲート絶縁膜として膜厚 5 n m 以上 3 0 0 n m 以下の酸化珪素膜(SiO<sub>x</sub>(x > 0))を積層して、膜厚 1 0 0 n m のゲート絶縁膜 4 0 3 としても良い。ゲート絶縁膜 4 0 3 の膜厚は、トランジスタに要求される特性によって適宜設定すればよく、 3 5 0 n m 乃至 4 0 0 n m 程度でもよい。

[0166]

本実施の形態では、スパッタ法で形成された膜厚50nmの窒化珪素膜上に、スパッタ法で形成された膜厚100nmの酸化珪素膜を積層させた構造を有する、ゲート絶縁膜403を形成する。

10

20

30

40

## [0167]

なお、ゲート絶縁膜403に水素、水酸基及び水分がなるべく含まれないようにするためには、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極401、ゲート電極402が形成された基板400を予備加熱し、基板400に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度としては、100以上400以下、好ましくは150以上300以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

# [0168]

次いで、ゲート絶縁膜403上に膜厚2nm以上200nm以下、好ましくは膜厚3nm以上50nm以下、さらに好ましくは膜厚3nm以上20nm以下の酸化物半導体膜404を形成する。酸化物半導体膜404は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜404は、希ガス(例えばアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(例えばアルゴン)及び酸素混合雰囲気下においてスパッタ法により形成することができる。

#### [0169]

なお、酸化物半導体膜 4 0 4 をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁膜 4 0 3 の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に R F 電源を用いて電圧を印加して基板にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、水素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

#### [0170]

酸化物半導体膜404には、上述したような酸化物半導体を用いることができる。

## [0171]

# [0172]

減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲットとして基板400上で酸化物半導体膜404を成膜する。成膜時に、基板温度を100以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンプリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H20)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

# [0173]

50

10

20

30

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生するパーティクルと呼ばれる塵埃が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

#### [0174]

なお、酸化物半導体膜404に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート絶縁膜403までが形成された基板400を予備加熱し、基板400に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度としては、100 以上400 以下、好ましくは150 以上300 以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、絶縁膜411の成膜前に、ソース電極407及びドレイン電極408、ソース電極409及びドレイン電極410まで形成した基板400にも同様に行ってもよい。

## [0175]

スパッタリング法にはスパッタ用電源に高周波電源を用いるRFスパッタリング法と、DCスパッタリング法があり、さらにパルス的にバイアスを与えるパルスDCスパッタリング法もある。RFスパッタリング法は主に絶縁膜を成膜する場合に用いられ、DCスパッタリング法は主に金属膜を成膜する場合に用いられる。

#### [ 0 1 7 6 ]

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ 装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種 類の材料を同時に放電させて成膜することもできる。

## [0177]

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタリング法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタリング法を用いるスパッタ装置がある。

## [0178]

また、スパッタリング法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法もある。

## [0179]

ゲート絶縁膜403及び酸化物半導体膜404を大気に触れさせることなく連続的に形成してもよい。大気に触れさせることなく連続成膜することで、界面が、水やハイドロカーボンなどの、大気成分や大気中に浮遊する不純物元素に汚染されることなく各積層界面を形成することができるので、トランジスタ特性のばらつきを低減することができる。

## [0180]

次いで、図10(B)に示すように、酸化物半導体膜404をエッチングなどにより所望の形状に加工(パターニング)し、ゲート電極401、ゲート電極402と重なる位置において、ゲート絶縁膜403上に島状の酸化物半導体膜405、酸化物半導体膜406を、それぞれ形成する。

# [0181]

島状の酸化物半導体膜405、酸化物半導体膜406を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

### [0182]

また、ゲート絶縁膜403にコンタクトホールを形成する場合、その工程は島状の酸化物半導体膜405、酸化物半導体膜406の形成時に行うことができる。

10

20

30

40

## [0183]

なお、島状の酸化物半導体膜 4 0 5 、酸化物半導体膜 4 0 6 を形成するためのエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、塩化硼素(BCl3)、塩化珪素(SiCl4)、四塩化炭素(CCl4)など)が好ましい。また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF4)、六弗化硫黄(SF6)、三弗化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(HBr)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、などを用いることができる。

## [0184]

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

#### [0185]

ウェットエッチングに用いるエッチング液としては、燐酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO-07N(関東化学社製)を用いてもよい。また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体膜に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化を図ることができる。

## [0186]

なお、次工程の導電膜を形成する前に逆スパッタを行い、島状の酸化物半導体膜405、酸化物半導体膜406及びゲート絶縁膜403の表面に付着しているレジスト残渣などを除去することが好ましい。

## [0187]

次いで、窒素、酸素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、酸化物半導体膜405、酸化物半導体膜406に加熱処理を施すことで、酸化物半導体膜405、酸化物半導体膜405、酸化物半導体膜405、酸化物半導体膜405、酸化物半導体膜405、酸化物半導体膜405に加熱処理を施すことができる。具体的には、300 以上850 以下(若しくはガラス基板の歪点以下の温度)、好ましくは550以上750 以下で加熱処理を行えば良い。例えば、600 、3分間以上6分間以下程度で行えばよい。RTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。或いは、基板温度が450に達した状態で、1時間程度、加熱処理を行うようにしても良い。

## [0188]

本実施の形態では、加熱処理装置の一つである電気炉を用い、酸化物半導体膜405、酸化物半導体膜406に対して、窒素雰囲気下において、基板温度が600 に達した状態で6分間、加熱処理を行う。上記加熱処理の後は、水分または水素の再混入を防ぐために、酸化物半導体膜405、酸化物半導体膜406を大気に触れさせないようにする。

## [0189]

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置

10

20

30

40

である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

## [0190]

例えば、加熱処理として、650~700 の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

## [0191]

なお、加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水分または水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

# [0192]

水分または水素などの不純物が酸化物半導体に添加されていると、85、 $2 \times 10^6 \text{ V}$ /cm、12時間のゲートバイアス・熱ストレス試験(BT試験)において、不純物と酸化物半導体の主成分との結合手が、強電界(B:バイアス)と高温(T:温度)により切断され、生成された不対結合手が閾値電圧(Vth)のドリフトを誘発することとなる。しかし、上述したように、ゲート絶縁膜と酸化物半導体膜との界面特性を良好にし、なおかつ、酸化物半導体膜中の不純物、特に水分または水素等を極力除去することにより、BT試験に対しても安定なトランジスタが得られる。

#### [0193]

以上の工程により酸化物半導体膜中の水素の濃度を低減し、高純度化することができる。 それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体膜を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧性が高く、ショートチャネル効果が低く、オンオフ比の高いトランジスタを作製することができる。

## [0194]

なお、酸化物半導体膜を加熱する場合、酸化物半導体膜の材料や加熱条件にもよるが、その上表面に板状結晶が形成されることがある。板状結晶は、酸化物半導体膜の表面に対して略垂直に c 軸配向した単結晶体であることが好ましい。また、単結晶体でなくともチャネル形成領域で各結晶の a b 面が一致するか、 a 軸、或いは、 b 軸が全てにおいて一致し、かつ、酸化物半導体膜の表面に対して略垂直に c 軸配向した多結晶体であることが好ましい。なお、酸化物半導体膜の下地表面に凹凸がある場合、板状結晶は多結晶体となる。

## [0195]

次いで、図10(C)に示すように、ゲート絶縁膜403、酸化物半導体膜405、酸化物半導体膜406上に、ソース電極及びドレイン電極(これと同じ層で形成される配線を含む)となる導電膜を形成した後、該導電膜をパターニングすることで、酸化物半導体膜405上にソース電極407及びドレイン電極408、酸化物半導体膜406上にソース電極409及びドレイン電極410を、それぞれ形成する。導電膜をスパッタ法や真空蒸着法で形成すればよい。ソース電極及びドレイン電極(これと同じ層で形成される配線を含む)となる導電膜の材料としては、A1、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、A1、Cuなどの金属膜の下側もしくは上側にCr、Ta、Ti、Mo、Wなどの高融点金属膜を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどA1膜に生ずるヒロックやウィスカーの発生を防止する元素が添加されているA1材料を用いることで耐熱性を向上させることが可能となる。

10

20

30

### [0196]

また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。

## [0197]

また、ソース電極及びドレイン電極(これと同じ層で形成される配線を含む)となる導電膜としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金( $In_2O_3$   $SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金( $In_2O_3$  ZnO)または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

#### [0198]

導電膜後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

#### [0199]

そして、導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極407及びドレイン電極408と、ソース電極409及びドレイン電極410とを形成した後、レジストマスクを除去する。

# [0200]

フォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体膜405、酸化物半導体膜406上で隣り合うソース電極の下端部とドレイン電極の下端部との間隔幅によって後に形成されるトランジスタのチャネル長しが決定される。なお、チャネル長し=25nm未満の露光を行う場合には、フォトリソグラフィ工程でのレジストマスク形成時に、数nm~数10nmと極めて波長が短い超紫外線(Extreme Ultraviolet)を用いて露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長しを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も図ることができる。

## [0201]

なお、導電膜のエッチングの際に、酸化物半導体膜405、酸化物半導体膜406がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。

### [0202]

本実施の形態では、導電膜にチタン膜を用い、アンモニアと過酸化水素水を含む溶液(アンモニア過水)を用いて、導電膜をウェットエッチングすることで、ソース電極 407 及びドレイン電極 408 と、ソース電極 409 及びドレイン電極 410 とを形成する。アンモニア過水を含む溶液は、具体的には、31 重量%の過酸化水素水と、28 重量%のアンモニア水と水とを、体積比 5:2:2 で混合した水溶液を用いる。或いは、塩素( $C1_2$ )、塩化硼素( $BC1_3$ )などを含むガスを用いて、導電膜をドライエッチングしても良い。

# [0203]

上記パターニングによりソース電極 4 0 7 及びドレイン電極 4 0 8 と、ソース電極 4 0 9 及びドレイン電極 4 1 0 とを形成する際に、島状の酸化物半導体膜 4 0 5 、酸化物半導体膜 4 0 6 の露出した部分が一部エッチングされることで、溝部(凹部)が形成されることもある。また、ソース電極 4 0 7 及びドレイン電極 4 0 8 と、ソース電極 4 0 9 及びドレイン電極 4 1 0 とを形成するためのレジストマスクを、インクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## [0204]

10

20

30

20

30

40

50

また、フォトリソグラフィエ程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィエ程も削減できるため、工程の簡略化が可能となる。

## [0205]

次いで、 $N_2$ O、 $N_2$ 、またはArなどのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体膜の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

#### [0206]

なお、プラズマ処理を行った後、図10(D)に示すように、ソース電極407及びドレ イン電極408と、ソース電極409及びドレイン電極410と、酸化物半導体膜405 と、酸化物半導体膜406とを覆うように、絶縁膜411を形成する。絶縁膜411は、 水分や、水素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良い し、積層された複数の絶縁膜で構成されていても良い。絶縁膜411に水素が含まれると その水素が酸化物半導体膜へ侵入し、又は水素が酸化物半導体膜中の酸素を引き抜き、 酸化物半導体膜のバックチャネル部が低抵抗化(n型化)してしまい、寄生チャネルが形 成されるおそれがある。よって、絶縁膜411はできるだけ水素を含まない膜になるよう に、成膜方法に水素を用いないことが重要である。上記絶縁膜411には、バリア性の高 い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化 酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などを用いることがで きる。複数の積層された絶縁膜を用いる場合、上記バリア性の高い絶縁膜よりも、窒素の 含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を、酸化物半導体膜405、酸 化物半導体膜406に近い側に形成する。そして、窒素の含有比率が低い絶縁膜を間に挟 んで、ソース電極 4 0 7 及びドレイン電極 4 0 8 、ソース電極 4 0 9 及びドレイン電極 4 10、及び酸化物半導体膜405、酸化物半導体膜406と重なるように、バリア性の高 い絶縁膜を形成する。バリア性の高い絶縁膜を用いることで、酸化物半導体膜405及び 酸化物半導体膜406内、ゲート絶縁膜403内、或いは、酸化物半導体膜405及び酸 化物半導体膜406と他の絶縁膜の界面とその近傍に、水分または水素などの不純物が入 り込むのを防ぐことができる。また、酸化物半導体膜405、酸化物半導体膜406に接 するように窒素の比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで 、バリア性の高い材料を用いた絶縁膜が直接酸化物半導体膜405、酸化物半導体膜40 6に接するのを防ぐことができる。

# [0207]

本実施の形態では、スパッタ法で形成された膜厚200nmの酸化珪素膜上に、スパッタ法で形成された膜厚100nmの窒化珪素膜を積層させた構造を有する、絶縁膜411を形成する。成膜時の基板温度は、室温以上300 以下とすればよく、本実施の形態では100 とする。

#### [0208]

なお、絶縁膜411を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、酸素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、好ましくは200 以上400 以下、例えば250 以上350 以下で行う。本実施の形態では、例えば、窒素雰囲気下で250 、1時間の加熱処理を行う。或いは、ソース電極407及びドレイン電極408と、ソース電極409及びドレイン電極410とを形成する前に、酸化物半導体膜に対して行った先の加熱処理と同様に、高温短時間のRTA処理を行っても良い。酸化物半導体膜に対して行った先の加熱処理により、酸化物半導体

膜405及び酸化物半導体膜406に酸素欠損が発生していたとしても、ソース電極407とドレイン電極408の間に設けられた酸化物半導体膜405の露出領域と、酸素を含む絶縁膜411とが接して設けられた後、または、ソース電極409とドレイン電極410の間に設けられた酸化物半導体膜406の露出領域と、酸素を含む絶縁膜411とが接して設けられた後に、加熱処理が施されることによって、酸化物半導体膜405、酸化物半導体膜406に酸素が供与される。そのため、酸化物半導体膜405、酸化物半導体膜406の絶縁膜411と接する領域に酸素が供与されることで、ドナーとなる酸素欠損を低減し、化学量論的組成比を満たす構成とすることが可能である。その結果、酸化物半導体膜405及び酸化物半導体膜406を主型化または実質的に主型化にすることができる。の加熱処理を行うタイミングは、絶縁膜411の形成後であれば特に限定されない。他の工程における加熱処理、例えば樹脂膜形成時の加熱処理や、透明導電膜を低抵抗化さるための加熱処理が、上記加熱処理を兼ねるようにすることで、工程数を増やすことなく、酸化物半導体膜405及び酸化物半導体膜406を主型化または実質的に主型化にすることができる。

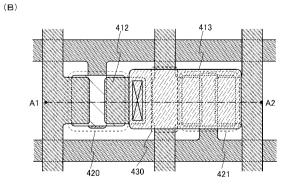

## [0209]

図11(A)に、図10(D)に示す工程まで終了した後の、記憶装置の上面図を示す。 なお、図11(A)の破線A1-A2における断面図が、図10(D)に相当する。

#### [0210]

次いで、絶縁膜411に、エッチング等によりコンタクトホール412を形成し、ドレイン電極408の一部を露出させる。そして、図10(E)に示すように、絶縁膜411上に導電膜を形成した後、該導電膜をパターニングすることで、酸化物半導体膜406と重なる位置にバックゲート電極413を形成した後、バックゲート電極413を覆うように絶縁膜414を形成する。バックゲート電極413は、コンタクトホール412においてドレイン電極408に接続されている。バックゲート電極413は、ゲート電極401、ゲート電極402、或いはソース電極407及びドレイン電極408、ソース電極409及びドレイン電極410と同様の材料、構造を用いて形成することが可能である。

#### [0211]

バックゲート電極 4 1 3 の膜厚は、1 0 n m ~ 4 0 0 n m、好ましくは1 0 0 n m ~ 2 0 0 n mとする。本実施の形態では、チタン膜、アルミニウム膜、チタン膜が積層された構造を有する導電膜を形成した後、フォトリソグラフィ法などによりレジストマスクを形成し、エッチングにより不要な部分を除去して、該導電膜を所望の形状に加工(パターニング)することで、バックゲート電極 4 1 3 を形成する。

## [0212]

絶縁膜414は、雰囲気中の水分、水素などがトランジスタの特性に影響を与えるのを防ぐことができる、バリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などを、プラズマCVD法又はスパッタリング法等により単層で又は積層させて形成することができる。バリア性の効果を得るには、絶縁膜414は、例えば厚さ15mm~400mmの膜厚で形成することが好ましい。

# [0213]

本実施の形態では、プラズマ C V D 法により 3 0 0 n m の絶縁膜を形成する。成膜条件は、シランガスの流量を 4 s c c m とし、一酸化二窒素 ( N  $_2$  O ) の流量を 8 0 0 s c c m とし、基板温度を 4 0 0 とする。

#### [0214]

以上の工程により、スイッチング素子として機能するトランジスタ420と、記憶素子として機能するトランジスタ421と、容量素子430が形成される。図11(B)に、図10(E)に示すメモリセルの上面図を示す。図10(E)は、図11(B)の破線A1-A2における断面図に相当する。

# [0215]

10

20

30

トランジスタ420は、絶縁表面を有する基板400上に形成されたゲート電極401と、ゲート電極401上のゲート絶縁膜403と、ゲート絶縁膜403上においてゲート電極401と重なっている酸化物半導体膜405と、酸化物半導体膜405上に形成された一対のソース電極407またはドレイン電極408とを有する。さらに、トランジスタ420は、酸化物半導体膜405上に形成された絶縁膜411を、その構成要素に含めても良い。図10(E)に示すトランジスタ420は、ソース電極407とドレイン電極408の間において、酸化物半導体膜405の一部がエッチングされたチャネルエッチ構造である。

## [0216]

なお、トランジスタ420はシングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極401を有することで、チャネル形成領域を複数有する、マルチゲート構造のトランジスタも形成することができる。

#### [0217]

また、トランジスタ421は、絶縁表面を有する基板400上に形成されたゲート電極402と、ゲート電極402上のゲート絶縁膜403と、ゲート絶縁膜403上においてゲート電極402と重なっている酸化物半導体膜406と、酸化物半導体膜406上に形成された一対のソース電極409またはドレイン電極410と、酸化物半導体膜406、ソース電極409、ドレイン電極410上に形成された絶縁膜411と、絶縁膜411上において、酸化物半導体膜406及びゲート電極402と重なっているバックゲート電極413上に形成された絶縁膜414を、その構成要素に含めても良い。図10(E)に示すトランジスタ421は、ソース電極409とドレイン電極410の間において、酸化物半導体膜406の一部がエッチングされたチャネルエッチ構造である。

#### [ 0 2 1 8 ]

なお、トランジスタ421はシングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極402を有することで、チャネル形成領域を複数有する、マルチゲート構造のトランジスタも形成することができる。

#### [0219]

また、容量素子430は、トランジスタ421のソース電極409と、バックゲート電極413とが、絶縁膜411を間に挟んで重なりあっている領域に形成されている。

### [0220]

トランジスタ421が有するゲート電極402は、その電位を制御することで、データの書き込み、読み出し、保持、消去などの、記憶素子としての動作を選択することができる、第1の電極として機能する。また、バックゲート電極413は、その電位を制御することができる、記憶素子として用いるトランジスタ421の閾値電圧の値を制御することができる、第2のゲート電極として機能する。なお、本実施の形態では、記憶素子として用いるトランジスタ421において、酸化物半導体膜406の前に形成されるゲート電極402を第1の電極、酸化物半導体膜406の後に形成されるバックゲート電極413を第2の電極として用いるメモリセルについて例示しているが、本発明はこの構成に限定されない。例えば、記憶素子として用いるトランジスタ421において、酸化物半導体膜406の前に形成されるゲート電極402を第2の電極、酸化物半導体膜406の後に形成されるバックゲート電極402を第2の電極、酸化物半導体膜406の後に形成されるバックゲート電極402を第2の電極、酸化物半導体膜406の後に形成されるバックゲート電極403を第1の電極として、動作させることも可能である。ただし、この場合、バックゲート電極413の代わりに、ゲート電極402を、トランジスタ420のドレイン電極408に接続させるようにする。

#### [0221]

また、図11(B)では、バックゲート電極413が、酸化物半導体膜406全体を覆っている場合を例示しているが、本発明はこの構成に限定されない。バックゲート電極41 3は、酸化物半導体膜406が有するチャネル形成領域の一部と少なくとも重なっていれば良い。

# [0222]

50

40

10

20

なお、酸化物半導体のバンドギャップは3.0~3.5 e V である。一方、炭化シリコンのバンドギャップは3.2 6 e V、窒化ガリウムのバンドギャップは3.3 9 e V と、ともにシリコンの約3倍程度の大きなバンドギャップを有している。よって、これら炭化シリコンや窒化ガリウムなどの化合物半導体は、ワイドギャップ半導体という点において、酸化物半導体と共通であり、バンドギャップが大きいという特性が、トランジスタの耐圧向上、電力損失の低減などに有利である。

#### [0223]

次いで、本実施の形態のように酸化物半導体膜中に含まれる水分または水素などの不純物を極力除去し、酸化物半導体膜を高純度化することが、トランジスタの特性にどのように影響を与えるかを以下に説明する。

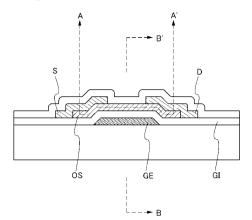

# [0224]

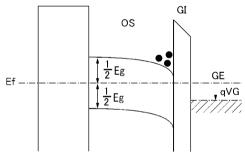

図12は、酸化物半導体を用いた逆スタガ型のトランジスタの縦断面図を示す。ゲート電極(GE)上にゲート絶縁膜(GI)を介して酸化物半導体膜(OS)が設けられ、その上にソース電極(S)及びドレイン電極(D)が設けられ、ソース電極(S)およびドレイン電極(D)を覆うように絶縁膜が設けられている。

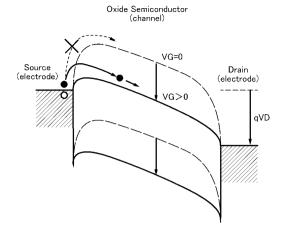

#### [0225]

図13は、図12に示すA-A<sup>・</sup>上におけるエネルギーバンド図(模式図)を示す。また、図13において、黒丸( )は電子を示し、白丸( )は正孔を示し、それぞれは電荷・qと+qを有している。ドレイン電極(D)に正の電圧(VD>0)を印加した上で、破線はゲート電極(GE)に電圧を印加しない場合(VG=0)、実線はゲート電極(GE)に正の電圧(VG>0)を印加する場合を示す。ゲート電極(GE)に電圧を印加しない場合は高いポテンシャル障壁のためにソース電極(S)から酸化物半導体膜(OS)側へキャリア(電子)が注入されず、電流を流さないオフ状態を示す。一方、ゲート電極(GE)に正の電圧を印加するとポテンシャル障壁が低下し、電流を流すオン状態を示す

#### [0226]

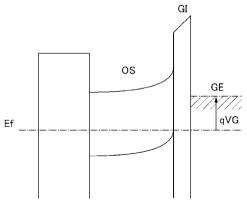

図 1 4 は、図 1 2 における B - B '上におけるエネルギーバンド図(模式図)である。図 1 4 (A) はゲート電極(GE)に正の電位(VG>0)が印加された状態であり、ソース電極(S)とドレイン電極(D)間にキャリア(電子)が流れるオン状態を示している。また、図 1 4 (B) は、ゲート電極(GE)に負の電位(VG<0)が印加された状態であり、オフ状態(少数キャリアは流れない)である場合を示す。

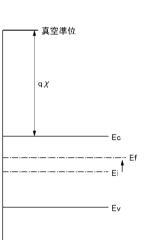

# [0227]

図 1 5 は、真空準位と金属の仕事関数 ( M)、酸化物半導体の電子親和力 ( )の関係を示す。

#### [0228]

常温において金属中の電子は縮退しており、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体は一般にn型であり、その場合のフェルミ準位(Ef)は、バンドギャップ中央に位置する真性フェルミ準位(Ei)から離れて、伝導帯(Ec)寄りに位置している。なお、酸化物半導体において水素の一部はドナーとなり、酸化物半導体がn型化する一つの要因であることが知られている。また、酸素欠損もn型化する一つの要因であることが知られている。

# [0229]

これに対して、本発明の一態様は、n型不純物である水素を酸化物半導体から除去して酸化物半導体の主成分以外の不純物が極力含まれないように高純度化し、かつ、酸素欠損を除去することにより、酸化物半導体を限りなく真性に近づけたものである。すなわち、不純物を添加して酸化物半導体を主型化するのでなく、水分または水素等の不純物や酸素欠損を極力除去して高純度化することにより、主型(真性半導体)又は主型(真性半導体)に限りなく近い酸化物半導体を得ることを特徴としている。上記構成により、矢印で示すように、フェルミ準位(Ef)は真性フェルミ準位(Ei)と同じレベルに限りなく近づけることができる。

10

20

30

酸化物半導体のバンドギャップ(Eg)は3.15eVで、電子親和力()は4.3Vと言われている。ソース電極及びドレイン電極を構成するチタン(Ti)の仕事関数は、酸化物半導体の電子親和力()とほぼ等しい。この場合、金属・酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。

(38)

[0231]

このとき電子は、図14(A)で示すようにゲート絶縁膜と高純度化された酸化物半導体との界面における、酸化物半導体側のエネルギー的に安定な最低部を移動する。

[0232]

また、図14(B)において、ゲート電極(GE)に負の電位が印加されると、少数キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

[0233]

次いで、酸化物半導体中の真性キャリア密度を計算した。In-Ga-Zn-O系酸化物 半導体のバンドギャップは、3.05eVであり、この値を元に真性キャリア密度を計算 する。固体中の電子のエネルギー分布f(E)は次の式で示されるフェルミ・ディラック 統計に従うことが知られている。

[0234]

【数1】

$$f(E) = \frac{1}{1 + \exp\left(\frac{E - E_F}{kT}\right)} \tag{1}$$

[0235]

キャリア密度が著しく高くない(縮退していない)普通の半導体では、次の関係式が成立 する。

[0236]

【数2】

$$|E - E_F| > kT \tag{2}$$

30

40

50

10

[0237]

従って、(1)式のフェルミ・ディラック分布は次の式で示されるボルツマン分布の式に 近似される。

[0238]

【数3】

$$f(E) = \exp\left[-\frac{E - E_F}{kT}\right]$$

(3)

[0239]

(3)式を使って半導体の真性キャリア密度(n<sub>i</sub>)を計算すると以下の式が得られる。

[0240]

【数4】

$$n_i = \sqrt{N_C N_V} \exp\left(-\frac{E_g}{2kT}\right) \tag{4}$$

[0241]

そして、(4)式に、SiとIn-Ga-Zn-O系酸化物半導体の実効状態密度(Nc、Nv)、バンドギャップ(Eg)の値を代入し、真性キャリア密度を計算した。その結

果を表1に示す。

#### [0242]

#### 【表1】

|                  |                     | Si                    | IGZO                 |

|------------------|---------------------|-----------------------|----------------------|

| <i>Nc</i> (300K) | [cm <sup>-3</sup> ] | 2.8×10 <sup>19</sup>  | 5.0×10 <sup>18</sup> |

| <i>Nv</i> (300K) | $[cm^{-3}]$         | $1.04 \times 10^{19}$ | $5.0 \times 10^{18}$ |

| Eg (300K)        | [eV]                | 1.08                  | 3.05                 |

| $n_i$ (300K)     | [cm <sup>-3</sup> ] | 1.45×10 <sup>10</sup> | 1.2×10 <sup>-7</sup> |

10

#### [0243]

In-Ga-Zn-O系酸化物半導体は、Siに比べて極端に真性キャリア密度が少ないことがわかる。In-Ga-Zn-O系酸化物半導体のバンドギャップとして3.05eVを選んだ場合、SiとIn-Ga-Zn-O系酸化物半導体とでは、真性キャリア密度におよそフェルミ・ディラックの分布則が正しいと仮定して、前者は後者よりキャリア密度が約10<sup>17</sup>倍大きいと言える。

#### [0244]

次いで、高純度化された酸化物半導体膜を有するトランジスタの、オフ電流の測定方法と その結果について説明する。

20

#### [0245]

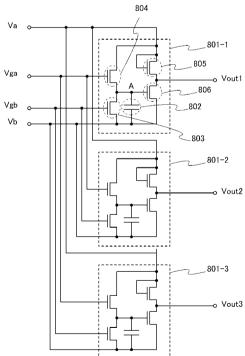

図18に、実際の測定に用いた、測定用回路の構成を示す。図18に示す測定用回路は、保持容量の電荷を保持するためのスイッチング素子として、高純度化された酸化物半導体膜を有するトランジスタを用い、上記保持容量の単位時間あたりの電荷量の推移から、上記トランジスタのオフ電流を測定するものである。

#### [0246]

具体的に、図18に示す測定用回路は、オフ電流を測定するための3つの測定系801-1~測定系801-3が、並列に接続された構成を有している。そして、測定系801-1~測定系801-3は、容量素子802と、測定の対象となるトランジスタ803とを、それぞれ有している。さらに、測定系801-1~測定系801-3は、トランジスタ804~トランジスタ806を、それぞれ有している。

30

#### [0247]

各測定系において、トランジスタ803のゲート電極は、電位Vgbが与えられるノードに接続されている。また、トランジスタ803は、ソース電極が電位Vbの与えられるノードに接続されており、ドレイン電極がノードAに接続されている。また、トランジスタ804のゲート電極は、電位Vgaが与えられるノードに接続されている。また、トランジスタ804は、ソース電極がノードAに接続されており、ドレイン電極が電位Vaの与えられるノードに接続されている。また、トランジスタ806のゲート電極とドレイン電極は、電位Vaが与えられるノードに接続されている。また、トランジスタ806のゲート電極は、ノードAに接続されており、トランジスタ805のソース電極が電位Vbの与えられるノードに接続されており、これら2つの電極の電位が、電位Vout1~電位Vout3として、各測定系からそれぞれ出力される。容量素子802が有する一対の電極は、一方がノードAに接続され、他方が電位Vbの与えられるノードに接続されている。

40

#### [0248]

また、本実施の形態では、測定の対象となるトランジスタ 8 0 3 は、高純度化された膜厚 3 0 n mの酸化物半導体膜と、膜厚が 1 0 0 n mのゲート絶縁膜を用いた。そして、トランジスタ 8 0 3 のチャネル形成領域は、チャネル長 L = 1 0  $\mu$  m、チャネル幅W = 5 0  $\mu$  mとした。また、各測定系が有する容量素子 8 0 2 の容量値は、それぞれ、 1 0 0 f F、

1 p F 、 3 p F とした。

#### [0249]

測定前に、初期化を行う。まず、電位Vgbを、トランジスタ803がオンとなるような高さに設定する。これによって、トランジスタ803がオンとなり、ノードAには電位Vb、すなわちローレベルの電位VSSが与えられる。その後、電位Vgbを、トランジスタ803がオフとなるような高さに設定することで、トランジスタ803をオフとする。次に、電位Vgaを、トランジスタ804がオンとなるような高さに設定する。これによって、ノードAには電位Va、すなわちハイレベルの電位VDDが与えられ、容量素子802の一対の電極間には、ローレベルの電位VSSとハイレベルの電位VDDの電位差が印加された状態となる。その後、電位Vgaの高さを、トランジスタ804がオフとなるような高さに設定することで、トランジスタ804がオフとなり、ノードAがフローティング状態となる。

#### [0250]

次いで、測定の動作に移る。測定を行う際には、電位Vaおよび電位Vbを、ノードAに電荷が流れ込む、またはノードAから電荷が流れ出すような高さに設定する。本実施の形態では、電位Vaおよび電位Vbをローレベルの電位VSSとした。なお、電位Voutを測定するタイミングにおいて、一時的に電位Vaをハイレベルの電位VDDに設定したが、それ以外は電位Vaおよび電位Vbをローレベルの電位VSSに維持した。

#### [ 0 2 5 1 ]

トランジスタ803には微少なオフ電流が流れるため、時間の経過と共にノードAに保持される電荷量は変動する。そして、ノードAに保持される電荷量の変動に伴って、ノードAの電位が変動するため、電位Vout1~Vout3は、トランジスタ803のオフ電流の値に従って、その高さが変化する。

#### [0252]

具体的に、本測定では、電位 V D D を 5 V 、電位 V S S を 0 V とした。そして、測定の際には、電位 V a を原則として電位 V S S とし、 1 0 ~ 3 0 0 s e c ごとに、 1 0 0 m s e c の期間だけ電位 V a を電位 V D D にして、電位 V o u t 1 ~ 電位 V o u t 3 を測定した

#### [0253]

図19に、上記電流測定に係る経過時間Timeと、電位Voutとの関係を示す。90時間程度から、電位変化の様子が確認できる。

# [0254]

あらかじめ、ノードAの電位  $V_A$  と、電位  $V_B$  の  $U_B$  は  $U_B$  の電位  $U_A$  を求めることが可能である。一般に、ノード A の電位  $U_A$  は 、電位  $V_B$  の  $U_B$  は  $U_B$  として次式のように表すことができる。

[0255]

# 【数5】

$$V_A = F(Vout)$$

#### [0256]

また、ノードAの電荷Q<sub>A</sub>は、ノードAの電位V<sub>A</sub>、ノードAに接続される容量C<sub>A</sub>、定数(const)を用いて、次式のように表される。ここで、ノードAに接続される容量C<sub>A</sub>は、容量素子802の容量値と他の容量(トランジスタ805及びトランジスタ806で構成される回路の入力容量など)の和である。

#### [0257]

10

20

30

【数6】

$$Q_A = C_A V_A + const$$

[0258]

ノードAの電流Iは、ノードAに流れ込む電荷(またはノードAから流れ出る電荷)の時間微分であるから、ノードAの電流Iは次式のように表現される。

[0259]

【数7】

$$I \equiv \frac{\Delta Q_A}{\Delta t} = \frac{C_A \cdot \Delta F(Vout)}{\Delta t}$$

[0260]

このように、ノードAに接続される容量  $C_A$  と、電位 V o u t 1 ~ V o u t 3 から、ノードA の電流 I を求めることができる。

[0261]

図20には、上記測定によって算出されたオフ電流を示す。トランジスタ803に流れる 20電流Iの算出に用いられる tは、約30000secとした。なお、図20は、ソース電極ドレイン電極間電圧Vと、オフ電流Iとの関係を表すものである。図20から、ソース電極ドレイン電極間電圧が4Vの条件において、オフ電流は約40zA/μmであることが分かる。

[0262]

このように、酸化物半導体の主成分以外の水分または水素などの不純物が極力含まれないように、酸化物半導体膜を高純度化することにより、トランジスタの動作を良好なものとすることができる。

[0263]

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

[0264]

(実施の形態4)

本実施の形態では、本発明の一態様に係る記憶装置を用いた半導体装置の一つである、携帯型の記憶媒体の一例について説明する。

[0265]

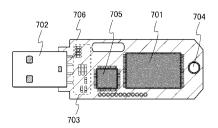

図16(A)に、本発明の一態様にかかる記憶媒体の構成を、一例として示す。図16(A)に示す記憶媒体は、本発明の一態様に係る記憶装置701と、駆動装置と記憶媒体の電気的な接続を行うコネクタ702と、コネクタ702を介して入出力される各種信号に、仕様に合わせて信号処理を施すインターフェース703と、記憶媒体の動作状態などに従って点灯する発光ダイオード704と、記憶装置701、インターフェース703、発光ダイオード704などの、記憶媒体内の各種回路や半導体素子の動作を制御するコントローラ705とが、プリント配線基板706に実装されている。その他に、コントローラ705の動作を制御するためのクロック信号を生成するのに用いられる水晶振動子、記憶媒体内における電源電圧の高さを制御するためのレギュレータなどが設けられていても良い。

[0266]

図 1 6 ( A ) に示すプリント配線基板 7 0 6 は、図 1 6 ( B ) に示すように、コネクタ 7 0 2 と発光ダイオード 7 0 4 が一部露出するように、樹脂等を用いたカバー材 7 0 7 で覆って、保護するようにしても良い。

[0267]

50

30

本発明の一態様にかかる記憶装置701は、その動作時における消費電力を低く抑えることができるので、記憶装置701を用いる記憶媒体の低消費電力化、延いては記憶媒体に接続される駆動装置の低消費電力化を実現することができる。また、本発明の一態様にかかる記憶装置701は、長期間に渡るデータの保持が可能であり、なおかつデータの書き換え回数を増やすことができるので、記憶媒体の信頼性を高めることができる。また、長期間に渡るデータの保持が可能であり、なおかつデータの書き換え回数を増やすことができるので、記憶媒体の動作条件の制約が緩くなり、記憶媒体の汎用性を高めることができる。

#### [0268]

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

10

20

#### 【実施例1】

【0269】

本発明の一態様に係る半導体装置を用いることで、信頼性が高い電子機器、消費電力の低い電子機器、高速駆動の電子機器を提供することが可能である。特に電力の供給を常時受けることが困難な携帯用の電子機器の場合、本発明の一態様に係る消費電力の低い半導体装置をその構成要素に追加することにより、連続使用時間が長くなるといったメリットが得られる。

#### [0270]

また、本発明の半導体装置では、作製工程における加熱処理の温度を抑えることができるので、ガラスよりも耐熱性の劣る、プラスチック等の可撓性を有する合成樹脂からなる基板上においても、特性が優れており、信頼性が高いトランジスタを作製することが可能である。従って、本発明の一態様に係る作製方法を用いることで、信頼性が高く、軽量かつフレキシブルな半導体装置を提供することが可能である。プラスチック基板として、ポリエチレンテレフタレート(PET)に代表されるポリエステル、ポリエーテルスルホン(PES)、ポリエチレンナフタレート(PEN)、ポリカーボネート(PC)、ポリエーテルエーテルケトン(PEEK)、ポリスルホン(PSF)、ポリエーテルイミド(PEI)、ポリアリレート(PAR)、ポリブチレンテレフタレート(PBT)、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。

[0271]

30

本発明の一態様に係る半導体装置は、表示装置、ノート型パーソナルコンピュータ、記録媒体を備えた画像再生装置(代表的にはDVD:Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型ゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機(ATM)、自動販売機などが挙げられる。これら電子機器の具体例を図17に示す。

[0272]

40

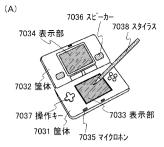

図17(A)は携帯型ゲーム機であり、筐体7031、筐体7032、表示部7033、表示部7034、マイクロホン7035、スピーカー7036、操作キー7037、スタイラス7038等を有する。本発明の一態様に係る半導体装置は、携帯型ゲーム機の駆動を制御するための集積回路に用いることができる。携帯型ゲーム機の駆動を制御するための集積回路に本発明の一態様に係る半導体装置を用いることで、信頼性が高い携帯型ゲーム機、消費電力の低い携帯型ゲーム機、高速駆動の携帯型ゲーム機、高機能の携帯型ゲーム機を提供することができる。なお、図17(A)に示した携帯型ゲーム機は、2つの表示部7033と表示部7034とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

# [0273]

図17(B)は携帯電話であり、筐体7041、表示部7042、音声入力部7043、 音声出力部7044、操作キー7045、受光部7046等を有する。受光部7046に おいて受信した光を電気信号に変換することで、外部の画像を取り込むことができる。本 発明の一態様に係る半導体装置は、携帯電話の駆動を制御するための集積回路に用いるこ とができる。携帯電話の駆動を制御するための集積回路に本発明の一態様に係る半導体装 置を用いることで、信頼性が高い携帯電話、消費電力の低い携帯電話、高速駆動の携帯電 話、高機能の携帯電話を提供することができる。

#### [0274]

図17(C)は携帯情報端末であり、筐体7051、表示部7052、操作キー7053 等を有する。図17(C)に示す携帯情報端末は、モデムが筐体7051に内蔵されてい ても良い。本発明の一態様に係る半導体装置は、携帯情報端末の駆動を制御するための集 精回路に用いることができる。携帯情報端末の駆動を制御するための集積回路に本発明の 一態様に係る半導体装置を用いることで、信頼性が高い携帯情報端末、消費電力の低い携 帯情報端末、高速駆動の携帯情報端末、高機能の携帯情報端末を提供することができる。

#### [0275]

本実施例は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【符号の説明】

# [0276]

| 1 0 0 | メモリセル  |  |

|-------|--------|--|

| 1 0 1 | トランジスタ |  |

| 1 0 2 | トランジスタ |  |

1 0 3 容量素子

1 1 0 基板

1 1 1 ゲート電極

1 1 2 絶縁膜

1 1 3 酸化物半導体膜

1 1 4 ソース電極

1 1 5 ドレイン電極

1 1 6 絶縁膜

1 1 7 絶縁膜

1 2 1 ゲート電極

1 2 3 酸化物半導体膜

ソース電極 1 2 4

1 2 5 ドレイン電極

線

1 2 6 ゲート電極

1 3 0 線

1 3 1

1 4 0 基板

1 4 1 ゲート雷極

1 4 2 絶縁膜

1 4 3 酸化物半導体膜

1 4 4 ソース電極

1 4 5 ドレイン電極

1 4 6 絶縁膜

1 4 7 絶縁膜

1 4 8 チャネル保護膜

1 5 1 ゲート電極

1 5 3 酸化物半導体膜

1 5 4 ソース電極

1 5 5 ドレイン電極 10

20

30

40

|       | :-                        |

|-------|---------------------------|

| 1 5 6 | ゲート電極                     |

| 1 5 7 | チャネル保護膜                   |

| 1 6 0 | 基板                        |

| 1 6 1 | ゲート電極                     |

| 1 6 2 | 絶縁膜                       |

| 1 6 3 | 酸化物半導体膜                   |

| 1 6 4 | ソース電極                     |

| 1 6 5 | ドレイン電極                    |

| 1 6 6 | 絶 縁 膜                     |

| 1 6 7 | 絶 縁 膜                     |

| 1 7 1 | ゲート電極                     |

| 1 7 3 | 酸化物半導体膜                   |

| 1 7 4 | ソース電極                     |

| 1 7 5 | ドレイン電極                    |

| 176   | ゲート電極                     |

| 2 0 0 | 基板                        |

| 2 0 8 | 酸化物半導体膜                   |

| 2 1 1 | 版 10 初 千 辱 体 族<br>ゲート 電 極 |

| 2 1 2 | グート電極<br>絶縁膜              |

|       |                           |

| 2 1 3 | 酸化物半導体膜                   |

| 2 1 4 | ソース電極                     |

| 2 1 5 | ドレイン電極                    |

| 2 1 6 | 絶縁膜                       |

| 2 1 7 | 絶縁膜                       |

| 2 2 1 | ゲート電極                     |

| 2 2 3 | 半導体膜                      |

| 2 2 4 | ソース電極                     |

| 2 2 5 | ドレイン電極                    |

| 2 2 6 | ゲート電極                     |

| 2 3 0 | 絶縁膜                       |

| 2 3 1 | 絶縁膜                       |

| 2 4 1 | ゲート電極                     |

| 2 4 2 | 絶縁膜                       |

| 2 4 3 | 酸化物半導体膜                   |

| 2 4 4 | ソース電極                     |

| 2 4 5 | ドレイン電極                    |

| 2 4 6 | 絶縁膜                       |

| 2 4 7 | 絶縁膜                       |

| 2 5 1 | ゲート電極                     |

| 2 5 3 | 半導体膜                      |

| 2 5 4 | 十等体膜ソース電極                 |

| 2 5 5 | ソース电極<br>ドレイン電極           |

| 255   | トレイプ電極<br>ゲート電極           |

| 2 5 6 |                           |

|       | 絶縁膜                       |

| 2 6 1 | 絶縁膜                       |

| 2 7 0 | 基板                        |

| 3 0 0 | メモリセル                     |

| 3 0 1 | トランジスタ                    |

| 3 0 2 | トランジスタ                    |

| 3 0 3 | 容量素子                      |

10

20

30

40

```

3 0 4 電源線

3 1 0 _ 1

トランジスタ

3 1 0 __ 2

トランジスタ

3 1 0 _ 3

トランジスタ

3 1 1 __ 1

トランジスタ

3 1 1 2

トランジスタ

3 1 1 3

トランジスタ

3 1 2 __ 1

オペアンプ

3 1 2 2

オペアンプ

3 1 2 __ 3

オペアンプ

320 トランジスタ

3 2 1

トランジスタ

4 0 0

基板

4 0 1

ゲート電極

4 0 2

ゲート電極

4 0 3

ゲート絶縁膜

4 0 4

酸化物半導体膜