(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년12월23일

(11) 등록번호 10-1474152

(24) 등록일자 2014년12월11일

(51) 국제특허분류(Int. Cl.)

H01G 4/12 (2006.01) H01G 4/30 (2006.01)

(21) 출원번호 10-2013-0084171

(22) 출원일자 2013년07월17일

심사청구일자 2013년07월17일

(56) 선행기술조사문헌

JP10022161 A

JP06215978 A

KR1020120133697 A

KR1020000003052 A

(73) 특허권자

삼성전기주식회사

경기도 수원시 영통구 매영로 150 (매탄동)

(72) 발명자

채은혁

경기 수원시 영통구 매영로 150, (매탄동, 삼성

전기)

이병화

경기 수원시 영통구 매영로 150, (매탄동, 삼성

전기)

(74) 대리인

특허법인씨엔에스

전체 청구항 수 : 총 10 항

심사관 : 전한철

(54) 발명의 명칭 적층 세라믹 커패시터 및 그 제조 방법

**(57) 요약**

본 발명은, 복수의 유전체층이 적층된 세라믹 본체; 상기 유전체층을 사이에 두고 상기 세라믹 본체의 양 단면을 통해 번갈아 노출되도록 형성된 복수의 제1 및 제2 내부 전극을 포함하는 액티브층; 상기 액티브층의 상부 및 하부에 각각 형성된 상부 및 하부 커버층; 및 상기 세라믹 본체의 양 단면에 형성된 제1 및 제2 외부 전극; 을 포함하며, 상기 세라믹 본체의 두께를 T로, 상기 액티브층의 두께를 S로, 상기 하부 커버층의 두께를 C로, 최하부의 내부 전극의 길이 방향의 단부에서 가까운 외부 전극의 밴드의 단부까지의 거리를 A로 규정할 때,  $0.25 \leq S/T \leq 0.75$  및  $3 \leq A/C \leq 10$ 의 범위를 만족하는 적층 세라믹 커패시터를 제공한다.

**대 표 도 - 도2**

## 특허청구의 범위

### 청구항 1

복수의 유전체층이 적층된 세라믹 본체;

상기 유전체층을 사이에 두고 상기 세라믹 본체의 양 단면을 통해 번갈아 노출되도록 형성된 복수의 제1 및 제2 내부 전극을 포함하는 액티브층;

상기 액티브층의 상부 및 하부에 각각 형성된 상부 및 하부 커버층; 및

상기 세라믹 본체의 양 단면에 형성된 제1 및 제2 외부 전극; 을 포함하며,

상기 세라믹 본체의 두께를 T로, 상기 액티브층의 두께를 S로, 상기 하부 커버층의 두께를 C로, 최하부의 내부 전극의 길이 방향의 단부에서 가까운 외부 전극의 밴드의 단부까지의 거리를 A로 규정할 때,  $0.25 \leq S/T \leq 0.75$  및  $3 \leq A/C \leq 10$ 의 범위를 만족하는 적층 세라믹 커패시터.

### 청구항 2

제1항에 있어서,

상기 세라믹 본체의 두께가  $80 \mu\text{m}$  이하인 것을 특징으로 하는 적층 세라믹 커패시터.

### 청구항 3

제1항에 있어서,

상기 하부 커버층의 두께가 상기 상부 커버층의 두께에 비해 두껍게 형성된 것을 특징으로 하는 적층 세라믹 커패시터.

### 청구항 4

제1항에 있어서,

상기 세라믹 본체의 양 단면에 상기 제1 및 제2 외부 전극을 덮도록 제1 및 제2 도금층이 형성된 것을 특징으로 하는 적층 세라믹 커패시터.

### 청구항 5

제4항에 있어서,

상기 제1 및 제2 도금층의 두께가  $5 \mu\text{m}$  이하인 것을 특징으로 하는 적층 세라믹 커패시터.

### 청구항 6

복수의 세라믹 그린 시트를 마련하는 단계;

상기 각각의 세라믹 그린 시트 상에 서로 대향하는 방향으로 번갈아 노출되도록 복수의 제1 및 제2 내부 전극을 형성하는 단계;

상기 제1 및 제2 내부 전극이 형성된 복수의 세라믹 그린 시트를 적층하여 예비 적층체를 형성하는 단계;

상기 예비 적층체의 상부 및 하부에 세라믹 그린 시트를 적층하여 상부 및 하부 커버층을 형성하여 세라믹 적층

체를 형성하는 단계;

상기 세라믹 적층체를 소성하여 세라믹 본체를 형성하는 단계; 및

상기 세라믹 본체의 양 단면에 상기 제1 및 제2 내부 전극의 노출된 부분과 접촉되어 전기적으로 연결되도록 제1 및 제2 외부 전극을 형성하는 단계; 를 포함하며,

상기 세라믹 본체의 두께를 T로, 상기 예비 적층체의 두께를 S로, 상기 하부 커버층의 두께를 C로, 최하부의 내부 전극의 길이 방향의 단부에서 가까운 외부 전극의 벤드의 단부까지의 거리를 A로 규정할 때,  $0.25 \leq S/T \leq 0.75$  및  $3 \leq A/C \leq 10$ 의 범위를 만족하도록 상기 상부 및 하부 커버층과, 상기 제1 및 제2 내부 전극과, 상기 제1 및 제2 외부 전극을 형성하는 적층 세라믹 커패시터의 제조 방법.

### 청구항 7

제6항에 있어서,

상기 세라믹 본체의 두께가  $80 \mu\text{m}$  이하가 되도록 상기 세라믹 그린 시트들을 적층하는 것을 특징으로 하는 적층 세라믹 커패시터의 제조 방법.

### 청구항 8

제6항에 있어서,

상기 상부 및 하부 커버층을 형성하는 단계는, 상기 하부 커버층의 두께를 상기 상부 커버층의 두께에 비해 두껍게 형성하는 것을 특징으로 하는 적층 세라믹 커패시터의 제조 방법.

### 청구항 9

제6항에 있어서,

상기 제1 및 제2 외부 전극을 형성하는 단계 이후에, 상기 세라믹 본체의 양 단면에 상기 제1 및 제2 외부 전극을 덮도록 제1 및 제2 도금층을 형성하는 단계를 더 수행하는 것을 특징으로 하는 적층 세라믹 커패시터의 제조 방법.

### 청구항 10

제9항에 있어서,

상기 제1 및 제2 도금층의 두께가  $5 \mu\text{m}$  이하가 되도록 상기 제1 및 제2 도금층을 형성하는 것을 특징으로 하는 적층 세라믹 커패시터의 제조 방법.

## 명세서

### 기술 분야

본 발명은 적층 세라믹 커패시터 및 그 제조 방법에 관한 것이다.

### 배경 기술

적층 칩 전자 부품의 하나인 적층 세라믹 커패시터는 액정 표시 장치(LCD: Liquid Crystal Display) 및 플라즈마 표시 장치 패널(PDP: Plasma Display Panel) 등의 영상 기기, 컴퓨터, 개인 휴대용 단말기(PDA: Personal Digital Assistants) 및 휴대폰 등 여러 전자 제품의 인쇄회로기판에 장착되어 전기를 충전시키거나 또는 방전시키는 역할을 하는 칩 형태의 콘텐서이다.

[0003] 이러한 적층 세라믹 커패시터(Multi-Layered Ceramic Capacitor)는 소형이면서 고용량이 보장되고 실장이 용이하다는 장점을 인하여 다양한 전자 장치의 부품으로 사용될 수 있다.

[0004] 상기 적층 세라믹 커패시터는 세라믹 시트 위에 시트의 면적 보다 작은 일정 두께의 내부 전극을 인쇄한 후 적층하기 때문에 내부 전극이 미형성된 마진부와 내부 전극이 형성된 유전체층 간의 단차가 필연적으로 발생하게 된다.

[0005] 특히 이러한 단차는 최외곽의 내부 전극이 형성된 부분에서 심화될 수 있다.

[0006] 이렇게 단차가 발생하게 되면 열 충격이 가해지거나 실장 후 인쇄회로기판의 힘에 의한 응력이 가해지는 경우 유전체층 중에서 일부가 서로 박리되는 디라미네이션(delamination)이나 크랙이 발생할 수 있다.

[0007] 따라서, 상기 디라미네이션이나 크랙을 통해 습기 및 기타 이물질 등이 내부 전극의 노출되는 면으로 침투하여 적층 세라믹 커패시터의 절연 저항 열화 및 신뢰성 저하 등의 문제를 야기할 수 있다.

[0008] 하기 특허문헌 1은 적층 세라믹 커패시터를 기재하고 있으나, 세라믹 본체와 액티브층의 비율 및 하부 커버층의 두께와 최하부의 내부 전극의 길이 방향의 단부에서 가까운 외부 전극의 밴드의 단부까지의 거리의 비율에 대한 수치 한정은 개시하지 않는다.

### 선행기술문헌

#### 특허문헌

[0009] (특허문헌 0001) 한국특허공개공보 10-2001-0089761호

#### 발명의 내용

#### 해결하려는 과제

[0010] 당 기술 분야에서는, 내부 전극이 미형성된 마진부와 내부 전극이 형성된 유전체층 간의 단차를 최대한 보상하여 열 충격 또는 실장 후의 인쇄회로기판에서의 힘에 의한 응력과 같은 기계적 충격에 의한 디라미네이션이나 크랙의 발생을 억제할 수 있는 적층 세라믹 커패시터에 대한 새로운 방안이 요구되어 왔다.

#### 과제의 해결 수단

[0011] 본 발명의 일 측면은, 복수의 유전체층이 적층된 세라믹 본체; 상기 유전체층을 사이에 두고 상기 세라믹 본체의 양 단면을 통해 번갈아 노출되도록 형성된 복수의 제1 및 제2 내부 전극을 포함하는 액티브층; 상기 액티브층의 상부 및 하부에 각각 형성된 상부 및 하부 커버층; 및 상기 세라믹 본체의 양 단면에 형성된 제1 및 제2 외부 전극; 을 포함하며, 상기 세라믹 본체의 두께를 T로, 상기 액티브층의 두께를 S로, 상기 하부 커버층의 두께를 C로, 최하부의 내부 전극의 길이 방향의 단부에서 가까운 외부 전극의 밴드의 단부까지의 거리를 A로 규정할 때,  $0.25 \leq S/T \leq 0.75$  및  $3 \leq A/C \leq 10$ 의 범위를 만족하는 적층 세라믹 커패시터를 제공한다.

[0012] 본 발명의 일 실시 예에서, 상기 세라믹 본체의 두께는  $80 \mu\text{m}$  이하일 수 있다.

[0013] 본 발명의 일 실시 예에서, 상기 하부 커버층의 두께는 상기 상부 커버층의 두께에 비해 두껍게 형성될 수 있다.

[0014] 본 발명의 일 실시 예에서, 상기 세라믹 본체의 양 단면에 상기 제1 및 제2 외부 전극을 덮도록 제1 및 제2 도금층이 형성될 수 있다.

[0015] 본 발명의 일 실시 예에서, 상기 제1 및 제2 도금층의 두께는  $5 \mu\text{m}$  이하일 수 있다.

[0016] 본 발명의 다른 측면은, 복수의 세라믹 그린 시트를 마련하는 단계; 상기 각각의 세라믹 그린 시트 상에 서로 대향하는 방향으로 번갈아 노출되도록 복수의 제1 및 제2 내부 전극을 형성하는 단계; 상기 제1 및 제2 내부 전극이 형성된 복수의 세라믹 그린 시트를 적층하여 예비 적층체를 형성하는 단계; 상기 예비 적층체의 상부 및 하부에 세라믹 그린 시트를 적층하여 상부 및 하부 커버층을 형성하여 세라믹 적층체를 형성하는 단계; 상기 세라믹 적층체를 소성하여 세라믹 본체를 형성하는 단계; 및 상기 세라믹 본체의 양 단면에 상기 제1 및 제2 내부 전극의 노출된 부분과 접촉되어 전기적으로 연결되도록 제1 및 제2 외부 전극을 형성하는 단계; 를 포함하며, 상기 세라믹 본체의 두께를 T로, 상기 예비 적층체의 두께를 S로, 상기 하부 커버층의 두께를 C로, 최하부의 내부 전극의 길이 방향의 단부에서 가까운 외부 전극의 밴드의 단부까지의 거리를 A로 규정할 때,  $0.25 \leq S/T \leq 0.75$  및  $3 \leq A/C \leq 10$ 의 범위를 만족하도록 상기 상부 및 하부 커버층과, 상기 제1 및 제2 내부 전극과, 상기 제1 및 제2 외부 전극을 형성하는 적층 세라믹 커패시터의 제조 방법을 제공한다.

### 발명의 효과

[0017] 본 발명의 일 실시 형태에 따르면, 세라믹 본체의 단차를 보상하여 열 충격 또는 실장 후의 인쇄회로기판에서의 힘에 의한 응력과 같은 기계적 충격에 의한 디라미네이션이나 크랙의 발생을 억제하여 내부 전극의 노출되는 면으로 습기 또는 기타 이물질이 침투하는 것을 방지하여 적층 세라믹 커패시터의 절연 저항 열화를 방지하고 신뢰성을 향상시킬 수 있는 효과가 있다.

### 도면의 간단한 설명

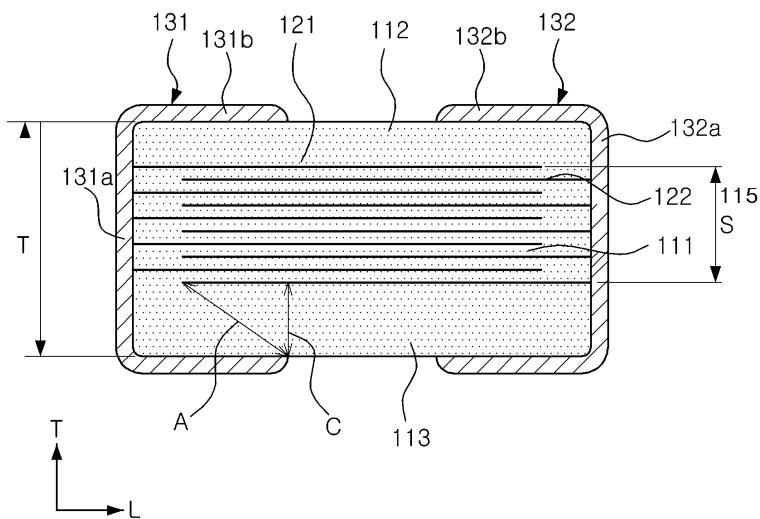

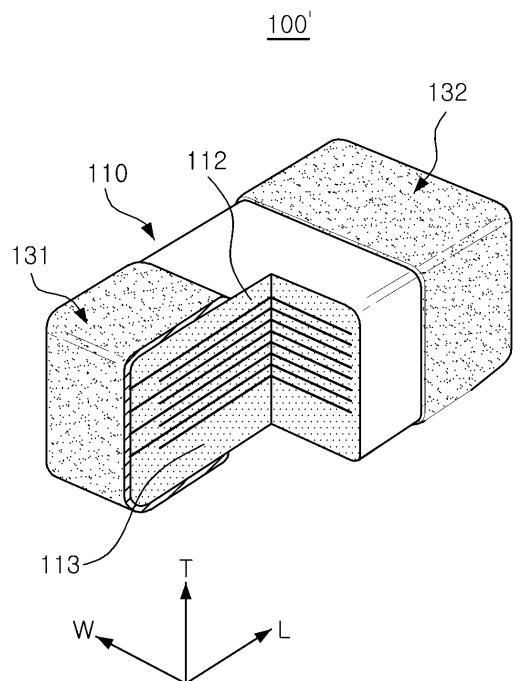

[0018] 도 1은 본 발명의 일 실시 형태에 따른 적층 세라믹 커패시터의 일부를 절개하여 개략적으로 도시한 사시도이다.

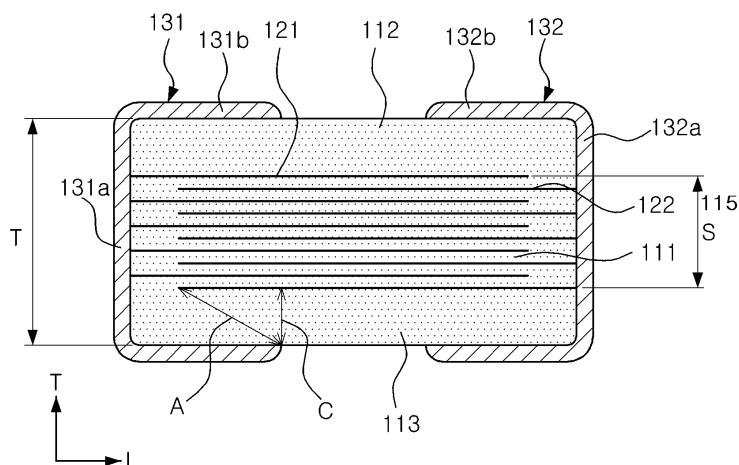

도 2는 도 1의 적층 세라믹 커패시터를 길이 방향으로 절단하여 도시한 단면도이다.

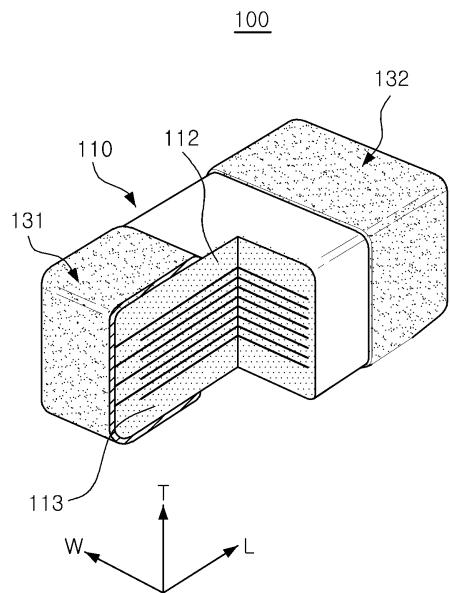

도 3은 본 발명의 다른 실시 형태에 따른 적층 세라믹 커패시터의 일부를 절개하여 개략적으로 도시한 사시도이다.

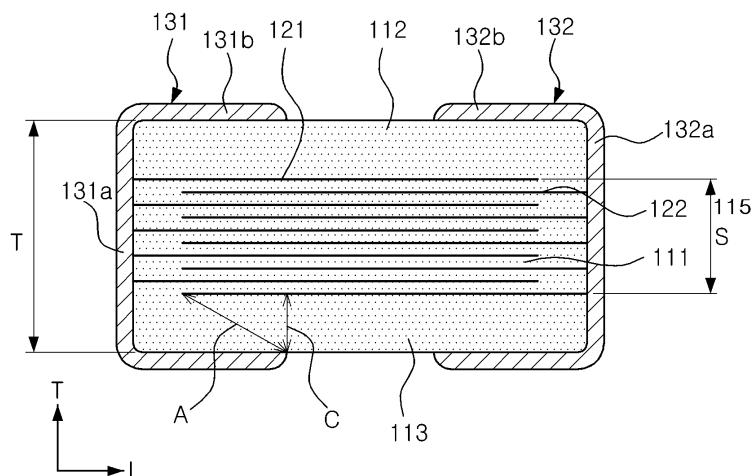

도 4는 도 2의 적층 세라믹 커패시터를 길이 방향으로 절단하여 도시한 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0019] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시 형태들을 설명한다.

[0020] 그러나, 본 발명의 실시 형태는 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 이하 설명하는 실시 형태로 한정되는 것은 아니다.

[0021] 또한, 본 발명의 실시 형태는 당해 기술 분야에서 평균적인 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위해서 제공되는 것이다.

[0022] 도면에서 요소들의 형상 및 크기 등은 보다 명확한 설명을 위해 과장될 수 있다.

[0023] 또한, 각 실시 예의 도면에 나타난 동일한 사상의 범위 내의 기능이 동일한 구성 요소는 동일한 참조 부호를 사용하여 설명한다.

[0024] 본 발명의 실시 예들을 명확하게 설명하기 위해 육면체의 방향을 정의하면, 도면 상에 표시된 L, W 및 T는 각각 길이 방향, 폭 방향 및 두께 방향을 나타낸다. 여기서, 두께 방향은 유전체층이 적층된 적층 방향과 동일한 개념으로 사용될 수 있다.

- [0025] 또한, 본 실시 형태에서는 설명의 편의를 위해 세라믹 본체의 길이 방향으로 제1 및 제2 외부 전극이 형성되는 면을 좌우 양 단면으로 설정하고, 이와 수직으로 교차되는 면을 좌우 측면으로 설정하여 함께 설명하기로 한다.

- [0026] 도 1 및 도 2를 참조하면, 본 발명의 일 실시 형태에 따른 적층 세라믹 커패시터(100)는, 세라믹 본체(110), 제1 및 제2 내부 전극(121, 122)을 갖는 액티브층(115), 상부 및 하부 커버층(112, 113) 및 세라믹 본체(110)의 양 단면을 덮도록 형성된 제1 및 제2 외부 전극(131, 132)을 포함한다.

- [0027] 세라믹 본체(110)는 복수의 유전체층(111)을 적층한 다음 소성하여 형성되며, 이러한 세라믹 본체(110)의 형상, 치수 및 유전체층(111)의 적층 수가 본 실시 형태에 도시된 것으로 한정되는 것은 아니다.

- [0028] 또한, 세라믹 본체(110)를 형성하는 복수의 유전체층(111)은 소결된 상태로서, 인접하는 유전체층(111) 사이의 경계는 주사전자현미경(SEM: Scanning Electron Microscope)를 이용하지 않고 확인하기 곤란할 정도로 일체화될 수 있다.

- [0029] 이러한 세라믹 본체(110)는 커패시터의 용량 형성에 기여하는 부분으로서의 액티브층(115)과, 상하 마진부로서 액티브층(115)의 상하부에 각각 형성된 상부 및 하부 커버층(112, 113)으로 구성될 수 있다.

- [0030] 액티브층(115)은 유전체층(111)을 사이에 두고 복수의 제1 및 제2 내부 전극(121, 122)을 반복적으로 적층하여 형성될 수 있다.

- [0031] 이때, 유전체층(111)의 두께는 적층 세라믹 커패시터(100)의 용량 설계에 맞추어 임의로 변경할 수 있으며, 바람직하게 1 층의 두께는 소성 후 0.01 내지 1.00  $\mu\text{m}$ 이 되도록 구성할 수 있으나, 본 발명이 이에 한정되는 것은 아니다.

- [0032] 또한, 유전체층(111)은 고유전률을 갖는 세라믹 분말, 예를 들어 티탄산바륨( $\text{BaTiO}_3$ )계 또는 티탄산스트론튬( $\text{SrTiO}_3$ )계 분말을 포함할 수 있으며, 본 발명이 이에 한정되는 것은 아니다.

- [0033] 상부 및 하부 커버층(112, 113)은 내부 전극을 포함하지 않는 것을 제외하고는 유전체층(111)과 동일한 재질 및 구성을 가질 수 있다.

- [0034] 상부 및 하부 커버층(112, 113)은 단일 유전체층 또는 2 개 이상의 유전체층을 액티브층(115)의 상하 면에 각각 상하 방향으로 적층하여 형성할 수 있으며, 기본적으로 물리적 또는 화학적 스트레스에 의한 제1 및 제2 내부 전극(121, 122)의 손상을 방지하는 역할을 수행할 수 있다.

- [0035] 제1 및 제2 내부 전극(121, 122)은 서로 다른 극성을 갖는 한 쌍의 전극으로서, 유전체층(111) 상에 소정의 두께로 도전성 금속을 포함하는 도전성 페이스트를 인쇄하여 유전체층(111)의 적층 방향을 따라 양 단면을 통해 번갈아 노출되도록 형성될 수 있으며, 중간에 배치된 유전체층(111)에 의해 서로 전기적으로 절연될 수 있다.

- [0036] 즉, 제1 및 제2 내부 전극(121, 122)은 세라믹 본체(110)의 양 단면을 통해 번갈아 노출되는 부분을 통해 제1 및 제2 외부 전극(131, 132)과 각각 전기적으로 연결될 수 있다.

- [0037] 따라서, 제1 및 제2 외부 전극(131, 132)에 전압을 인가하면 서로 대향하는 제1 및 제2 내부 전극(121, 122) 사이에 전하가 축적되고, 이때 적층 세라믹 커패시터(100)의 정전 용량은 제1 및 제2 내부 전극(121, 122)의 서로 중첩되는 영역의 면적과 비례하게 된다.

- [0038] 이러한 제1 및 제2 내부 전극(121, 122)의 두께는 용도에 따라 결정될 수 있는데, 예를 들어 세라믹 본체(110)의 크기를 고려하여 0.2 내지 1.0  $\mu\text{m}$ 의 범위 내에 있도록 결정될 수 있으며, 본 발명이 이에 한정되는 것은 아

니다.

[0039] 또한, 제1 및 제2 내부 전극(121, 122)을 형성하는 도전성 페이스트에 포함되는 도전성 금속은 니켈(Ni), 구리(Cu), 팔라듐(Pd), 또는 이들의 합금일 수 있으며, 본 발명이 이에 한정되는 것은 아니다.

[0040] 또한, 상기 도전성 페이스트의 인쇄 방법은 스크린 인쇄법 또는 그라비아 인쇄법 등을 사용할 수 있으며, 본 발명이 이에 한정되는 것은 아니다.

[0041] 제1 및 제2 외부 전극(131, 132)은 도전성 금속을 포함하는 도전성 페이스트에 의해 세라믹 본체(110)의 길이 방향의 양 단면을 덮는 머리부(131a, 132a)와 머리부(131a, 132a)에서 연장되어 세라믹 본체(110)의 상하면 및 측면 중 일부를 덮는 밴드(131b, 132b)로 구성될 수 있다.

[0042] 이때, 상기 도전성 금속은 니켈(Ni), 구리(Cu), 팔라듐(Pd), 금(Au) 또는 이들의 합금일 수 있으며, 본 발명이 이에 한정되는 것은 아니다.

[0043] 한편, 세라믹 본체(110)의 양 단면에는 제1 및 제2 외부 전극(131, 132)를 덮도록 제1 및 제2 도금층(미도시)이 더 형성될 수 있다.

[0044] 이러한 제1 및 제2 도금층은 외부 전극 위에 도금되는 과정에서 수축 또는 인장 응력이 발생하여 세라믹 본체(110)에 크랙이 발생하는 것을 방지하는 효과를 더 증대시킬 수 있다.

[0045] 상기 제1 및 제2 도금층의 두께는 세라믹 본체(110)로 수분이 침투하는 신뢰성 불량을 방지하기 위해 바람직하게  $5 \mu\text{m}$  이하로 조절될 수 있으며, 본 발명이 이에 한정되는 것은 아니다.

[0046] 제1 및 제2 외부 전극(131, 132)은 인쇄회로기판에 실장시 단차가 주로 발생되는 제1 및 제2 내부 전극(121, 122)의 단부와의 거리를 조절하고, 세라믹 본체(110)의 두께와 액티브층(115)의 두께를 조절하여 휙크랙이나 디라미네이션의 발생을 저감하여 신뢰성을 높일 필요가 있다.

[0047] 본 실시 형태에서는, 세라믹 본체(110)의 전체 두께를 T로, 액티브층(115)의 전체 두께를 S로, 하부 커버층(113)의 두께를 C로, 최하부의 제2 내부 전극(122)의 길이 방향의 단부에서 가까운 제1 외부 전극(131)의 밴드부(131b)의 단부까지의 거리를 A로 규정한다.

[0048] 여기서, 세라믹 본체(110)의 전체 두께는 세라믹 본체(110)의 상면에서 하면까지의 거리를 의미하고, 액티브층(115)의 전체 두께는 액티브층(115)의 최상부에 형성된 제1 내부 전극(121)의 상면에서 액티브층(115)의 최하부에 형성된 제2 내부 전극(122)의 하면까지의 거리를 의미하고, 하부 커버층(113)의 두께(B)는 액티브층(115)의 두께 방향의 최하부에 형성된 제2 내부 전극(122)의 하면에서 세라믹 본체(110)의 하면까지의 거리를 의미한다.

[0049] 이때, 디라미네이션이나 휙크랙의 발생을 저감하여 신뢰성을 높일 수 있는 범위는  $0.25 \leq S/T \leq 0.75$  및  $3 \leq A/C \leq 10$  이 될 수 있다.

[0050] 즉, 수축률 차이로 인해 응력이 집중되는 내부 전극의 단부와 도금에 의해 도금 응력이 집중되는 외부 전극의 단부까지의 거리를 일정 거리 이상으로 구현함으로써 휙크랙을 방지할 수 있다.

[0051] 이때, S/T가 0.25 미만인 경우 휙크랙이 발생하는 문제점이 발생할 수 있으며, S/T가 0.75를 초과하게 되면 디라미네이션이 발생할 수 있다.

[0052] 또한, A/C가 3 미만인 경우 수축율 차이로 인해 인쇄회로기판의 휙에 의한 응력과 같은 기계적 충격이 집중되는 부분이 세라믹 본체(110)의 단차가 생기는 부분과 일치하거나 가깝게 설정되어 휙크랙 발생률이 증가될 수 있다.

[0053] 또한, A/C가 10을 초과하는 경우 BDV가 저하될 수 있다.

- [0054] 도 3 및 도 4는 본 발명의 다른 실시 형태에 따른 적층 세라믹 커패시터(100')를 나타낸 것이다.

- [0055] 도 3 및 도 4를 참조하면, 본 발명의 다른 실시 형태에 따른 적층 세라믹 커패시터(100')는 하부 커버층(113)이 상부 커버층(112) 보다 유전체층의 적층 수를 더 늘림으로써 상부 커버층(112)에 비해 더 두꺼운 두께를 가질 수 있다.

- [0056] 이러한 구조는 일 실시 형태의 휙크랙 및 디라미네이션을 방지하는 효과와 더불어 어쿠스틱 노이즈를 줄일 수 있는 효과를 더 기대할 수 있다. 그 외 다른 사항은 상기 일 실시 형태와 동일하므로 이에 상세한 설명은 생략한다.

- [0057] 이하, 적층 세라믹 커패시터에 포함되는 구성 요소들의 치수와 휙크랙, 디라미네이션 및 BDV 저하의 발생 빈도에 대한 관계를 설명한다.

- [0058] 본 발명의 실시 예와 비교 예에 따른 적층 세라믹 커패시터는 하기와 같이 제작되었다.

- [0059] 먼저, 티탄산바륨( $BaTiO_3$ ) 등의 파우더를 포함하여 형성된 슬러리를 캐리어 필름(carrier film) 상에 도포 및 건조하여 소정 두께로 제조된 복수의 세라믹 그린 시트를 마련한다.

- [0060] 다음으로, 상기 각각의 세라믹 그린 시트 상에 상기 세라믹 그린 시트의 L 방향의 서로 대향하는 양 단면을 통해 노출되도록 내부 전극용 도전성 페이스트를 도포하여, T 방향을 따라 상기 적층 세라믹 커패시터의 양 단면을 통해 번갈아 노출되는 복수의 제1 및 제2 내부 전극(121, 122)을 형성한다.

- [0061] 이때, 상기 도전성 페이스트의 도포는 스크린 방식 등을 이용할 수 있으며, 본 발명이 이에 한정되는 것은 아니다.

- [0062] 다음으로, 제1 및 제2 내부 전극(121, 122)이 형성된 복수의 세라믹 그린 시트를 T 방향으로 적층하여 예비 적층체를 형성한다.

- [0063] 그리고, 상기 예비 적층체의 상부 및 하부에 내부 전극이 미형성된 세라믹 그린 시트를 각각 적층하여 세라믹 적층체를 형성한다.

- [0064] 이때, 상기 내부 전극이 미형성된 세라믹 그린 시트는 상기 예비 적층체의 상부 및 하부에 각각 적어도 하나 이상 적층할 수 있으며, 본 발명은 상기 내부 전극이 미형성된 세라믹 그린 시트의 적층되는 개수가 한정되는 것은 아니다.

- [0065] 또한, 필요시 내부 전극이 미형성된 세라믹 그린 시트는 제1 및 제2 내부 전극(121, 122)이 형성된 상기 예비 적층체의 하부에서 상부보다 더 많이 적층할 수 있다.

- [0066] 이후, 상기 세라믹 적층체를 85 °C에서 약  $1000 \text{ kgf/cm}^2$  압력 조건으로 등압암축성형(isostatic pressing) 한다.

- [0067] 이때, 상기 압축성형된 세라믹 적층체의 두께를 T로, 복수의 제1 및 제2 내부 전극(121, 122)을 포함하는 액티브층(115)의 두께를 S로 규정할 때, 제1 및 제2 내부 전극(121, 122)이 형성된 세라믹 그린 시트들과 내부 전극이 미형성된 세라믹 그린 시트들은  $0.25 \leq S/T \leq 0.75$ 의 범위를 만족하도록 적층한다.

- [0068] 다음으로, 상기 압축성형이 완료된 세라믹 적층체를 개별 칩의 형태로 절단하고, 절단된 칩을 대기 분위기에서 약 230 °C 및 약 60 시간 유지하여 탈바인더를 진행한다.

- [0069] 다음으로, 약 1200 °C에서 제1 및 제2 내부 전극(121, 122)이 산화되지 않도록 Ni/NiO 평형산소분압 보다 낮은

$10^{-11}$  내지  $10^{-10}$  atm의 산소분압하의 환원분위기에서 소성하여 세라믹 본체(110)를 형성한다.

[0070] 이때, 소성 후의 세라믹 본체(110)의 두께는 각각 150 mm, 100 mm, 80 mm 및 50 mm가 되도록 제작하며, 여기서 제작 공차는  $\pm 0.1$  mm 내의 범위로 정한다.

[0071] 다음으로, 세라믹 본체(110)의 양 단면에 제1 및 제2 외부 전극(131, 132)을 형성한다.

[0072] 제1 및 제2 외부 전극(131, 132)은 세라믹 본체(110)의 양 단면을 덮어 제1 및 제2 내부 전극(121, 122)과 전기적으로 연결되는 머리부(131a, 132a)와 세라믹 본체(110)의 상하면 및 측면 중 일부를 덮는 밴드부(131b, 132b)를 포함할 수 있다.

[0073] 이때, 하부 커버층(113)의 두께를 C로, 최하부의 제2 내부 전극(122)의 L 방향의 단부에서 제1 외부 전극(131)의 밴드(131b)의 단부까지의 거리를 A로 규정할 때, 하부 커버층(113), 제2 내부 전극(122) 및 제1 외부 전극(131)의 밴드(131b)는  $3 \leq A/C \leq 10$ 의 범위를 만족하도록 형성할 수 있다.

[0074] 제1 내부 전극(121)의 L 방향의 마진부의 길이 및 제2 외부 전극(132)의 밴드(132b)의 길이는 각각 제2 내부 전극(122)의 L 방향의 마진부의 길이 및 제1 외부 전극(131)의 밴드(131b)의 길이와 유사하게 설정하는 것이 바람직하며, 본 발명이 이에 한정되는 것은 아니다.

[0075] 다음으로, 필요시 도금 공정을 수행하여 세라믹 본체(110)의 양 단면에 제1 및 제2 외부 전극(131, 132)을 덮도록 제1 및 제2 도금층을 형성할 수 있다.

[0076] 이때, 상기 제1 및 제2 도금층의 한쪽 두께는 제1 및 제2 외부 전극(131, 132)의 밴드(131b, 132b)의 한쪽 두께를 더한 값이 바람직하게 5  $\mu\text{m}$  이하가 되도록 할 수 있으며, 본 발명이 이에 한정되는 것은 아니다.

[0077] 이와 같이 적층 세라믹 커패시터를 제작한 후 실험하여 휨크랙, 디라미네이션 및 BDV 저하의 발생 빈도수를 측정하였다.

[0078] 도 2와 같이 적층 세라믹 커패시터(100)의 세라믹 본체(110)의 W 방향의 중심부에서 L 방향 및 T 방향으로 절개한 단면을 주사전자현미경(SEM, Scanning Electron Microscope)으로 찍은 사진을 기준으로 각각의 치수를 측정하였다.

[0079] 여기서 A, C, S 및 T는 상기에서 설명한 바와 같이, 세라믹 본체(110)의 전체 두께를 T로, 액티브층(115)의 전체 두께를 S로, 하부 커버층(113)의 두께를 C로, 제2 내부 전극(122)의 L 방향의 단부에서 제1 외부 전극(131)의 밴드(131b)의 L 방향의 단부까지의 거리를 A로 규정하였다.

[0080] 하기 표 1의 데이터는 세라믹 소체(110)의 두께가 50 mm일 때이고, 하기 표 2의 데이터는 세라믹 소체(110)의 두께가 80 mm일 때이고, 하기 표 3의 데이터는 세라믹 소체(110)의 두께가 100 mm일 때이고, 하기 표 4의 데이터는 세라믹 소체(110)의 두께가 150 mm일 때의 적층 세라믹 커패시터의 S/T 및 A/C에 따른 휨크랙, 디라미네이션 및 BDV 저하의 발생 빈도수를 나타낸 것이다.

[0081] 하기의 휨크랙, 디라미네이션 및 BDV 저하의 수치는 각 샘플별로 200 개를 실험하여 그 중 불량이 발생하는 수를 표시한 것이다.

표 1

| No. | 세라믹 본체의 두께(mm) | S/T  | A/C | 휩크랙 발생빈도 | Delamination | BDV 저하 |

|-----|----------------|------|-----|----------|--------------|--------|

| 1   | 50             | 0.15 | 2   | 0/200    | 0/200        | 0/200  |

| 2   |                | 0.15 | 3   | 0/200    | 0/200        | 0/200  |

| 3   | 50             |      | 5   | 0/200    | 0/200        | 0/200  |

| 4   |                |      | 7   | 0/200    | 0/200        | 0/200  |

| 5   |                |      | 10  | 0/200    | 0/200        | 13/200 |

| 6   |                |      | 12  | 0/200    | 0/200        | 27/200 |

| 7   |                | 0.20 | 2   | 0/200    | 0/200        | 0/200  |

| 8   |                |      | 3   | 0/200    | 0/200        | 0/200  |

| 9   |                |      | 5   | 0/200    | 0/200        | 0/200  |

| 10  |                |      | 7   | 0/200    | 0/200        | 0/200  |

| 11  |                |      | 10  | 0/200    | 0/200        | 8/200  |

| 12  |                |      | 12  | 0/200    | 0/200        | 21/200 |

| 13  |                | 0.25 | 2   | 6/200    | 0/200        | 0/200  |

| 14  |                |      | 3   | 0/200    | 0/200        | 0/200  |

| 15  |                |      | 5   | 0/200    | 0/200        | 0/200  |

| 16  |                |      | 7   | 0/200    | 0/200        | 0/200  |

| 17  |                |      | 10  | 0/200    | 0/200        | 0/200  |

| 18  |                |      | 12  | 0/200    | 0/200        | 12/200 |

| 19  |                | 0.30 | 2   | 12/200   | 0/200        | 0/200  |

| 20  |                |      | 3   | 0/200    | 0/200        | 0/200  |

| 21  |                |      | 5   | 0/200    | 0/200        | 0/200  |

| 22  |                |      | 7   | 0/200    | 0/200        | 0/200  |

| 23  |                |      | 10  | 0/200    | 0/200        | 0/200  |

| 24  |                |      | 12  | 0/200    | 0/200        | 7/200  |

| 25  |                | 0.50 | 2   | 17/200   | 0/200        | 0/200  |

| 26  |                |      | 3   | 0/200    | 0/200        | 0/200  |

| 27  |                |      | 5   | 0/200    | 0/200        | 0/200  |

| 28  |                |      | 7   | 0/200    | 0/200        | 0/200  |

| 29  |                |      | 10  | 0/200    | 0/200        | 0/200  |

| 30  |                |      | 12  | 0/200    | 0/200        | 5/200  |

| 31  |                | 0.75 | 2   | 23/200   | 0/200        | 0/200  |

| 32  |                |      | 3   | 0/200    | 0/200        | 0/200  |

| 33  |                |      | 5   | 0/200    | 0/200        | 0/200  |

| 34  |                |      | 7   | 0/200    | 0/200        | 0/200  |

| 35  |                |      | 10  | 0/200    | 0/200        | 0/200  |

| 36  |                |      | 12  | 0/200    | 0/200        | 3/200  |

| 37  |                | 0.85 | 2   | 27/200   | 4/200        | 0/200  |

| 38  |                |      | 3   | 18/200   | 10/200       | 0/200  |

| 39  |                |      | 5   | 15/200   | 31/200       | 0/200  |

| 40  |                |      | 7   | 7/200    | 54/200       | 0/200  |

| 41  |                |      | 10  | 1/200    | 64/200       | 0/200  |

| 42  |                |      | 12  | 0/200    | 89/200       | 3/200  |

&lt;세라믹 소체의 두께가 50 mm인 적층 세라믹 커匮시터&gt;

표 2

| No. | 세라믹 본체의 두께(mm) | S/T | A/C | 휩크랙 발생빈도 | Delamination | BDV 저하 |

|-----|----------------|-----|-----|----------|--------------|--------|

|-----|----------------|-----|-----|----------|--------------|--------|

|    |      |      |        |        |        |        |

|----|------|------|--------|--------|--------|--------|

| 1  | 80   | 0.15 | 2      | 0/200  | 0/200  | 0/200  |

| 2  |      |      | 3      | 0/200  | 0/200  | 0/200  |

| 3  |      |      | 5      | 0/200  | 0/200  | 0/200  |

| 4  |      |      | 7      | 0/200  | 0/200  | 2/200  |

| 5  |      |      | 10     | 0/200  | 0/200  | 16/200 |

| 6  |      |      | 12     | 0/200  | 0/200  | 31/200 |

| 7  |      | 0.20 | 2      | 0/200  | 0/200  | 0/200  |

| 8  |      |      | 3      | 0/200  | 0/200  | 0/200  |

| 9  |      |      | 5      | 0/200  | 0/200  | 0/200  |

| 10 |      |      | 7      | 0/200  | 0/200  | 0/200  |

| 11 |      |      | 10     | 0/200  | 0/200  | 10/200 |

| 12 |      |      | 12     | 0/200  | 0/200  | 27/200 |

| 13 | 0.25 | 2    | 4/200  | 0/200  | 0/200  |        |

| 14 |      | 3    | 0/200  | 0/200  | 0/200  |        |

| 15 |      | 5    | 0/200  | 0/200  | 0/200  |        |

| 16 |      | 7    | 0/200  | 0/200  | 0/200  |        |

| 17 |      | 10   | 0/200  | 0/200  | 0/200  |        |

| 18 |      | 12   | 0/200  | 0/200  | 13/200 |        |

| 19 | 0.30 | 2    | 9/200  | 0/200  | 0/200  |        |

| 20 |      | 3    | 0/200  | 0/200  | 0/200  |        |

| 21 |      | 5    | 0/200  | 0/200  | 0/200  |        |

| 22 |      | 7    | 0/200  | 0/200  | 0/200  |        |

| 23 |      | 10   | 0/200  | 0/200  | 0/200  |        |

| 24 |      | 12   | 0/200  | 0/200  | 11/200 |        |

| 25 | 0.50 | 2    | 15/200 | 0/200  | 0/200  |        |

| 26 |      | 3    | 0/200  | 0/200  | 0/200  |        |

| 27 |      | 5    | 0/200  | 0/200  | 0/200  |        |

| 28 |      | 7    | 0/200  | 0/200  | 0/200  |        |

| 29 |      | 10   | 0/200  | 0/200  | 0/200  |        |

| 30 |      | 12   | 0/200  | 0/200  | 10/200 |        |

| 31 | 0.75 | 2    | 21/200 | 0/200  | 0/200  |        |

| 32 |      | 3    | 0/200  | 0/200  | 0/200  |        |

| 33 |      | 5    | 0/200  | 0/200  | 0/200  |        |

| 34 |      | 7    | 0/200  | 0/200  | 0/200  |        |

| 35 |      | 10   | 0/200  | 0/200  | 0/200  |        |

| 36 |      | 12   | 0/200  | 0/200  | 9/200  |        |

| 37 | 0.85 | 2    | 24/200 | 2/200  | 0/200  |        |

| 38 |      | 3    | 19/200 | 5/200  | 0/200  |        |

| 39 |      | 5    | 14/200 | 21/200 | 0/200  |        |

| 40 |      | 7    | 4/200  | 34/200 | 0/200  |        |

| 41 |      | 10   | 0/200  | 58/200 | 0/200  |        |

| 42 |      | 12   | 0/200  | 84/200 | 6/200  |        |

&lt;세라믹 소체의 두께가 80 mm인 적층 세라믹 커패시터&gt;

**표 3**

| No. | 세라믹 본체의<br>두께(mm) | S/T | A/C | 휩크랙 발생빈도 | Delamination | BDV 저하 |

|-----|-------------------|-----|-----|----------|--------------|--------|

|-----|-------------------|-----|-----|----------|--------------|--------|

|    |      |      |       |       |        |        |

|----|------|------|-------|-------|--------|--------|

| 1  | 100  | 0.15 | 2     | 0/200 | 0/200  | 0/200  |

| 2  |      |      | 3     | 0/200 | 0/200  | 0/200  |

| 3  |      |      | 5     | 0/200 | 0/200  | 0/200  |

| 4  |      |      | 7     | 0/200 | 0/200  | 8/200  |

| 5  |      |      | 10    | 0/200 | 0/200  | 27/200 |

| 6  |      |      | 12    | 0/200 | 0/200  | 46/200 |

| 7  |      | 0.20 | 2     | 0/200 | 0/200  | 0/200  |

| 8  |      |      | 3     | 0/200 | 0/200  | 0/200  |

| 9  |      |      | 5     | 0/200 | 0/200  | 0/200  |

| 10 |      |      | 7     | 0/200 | 0/200  | 3/200  |

| 11 |      |      | 10    | 0/200 | 0/200  | 15/200 |

| 12 |      |      | 12    | 0/200 | 0/200  | 31/200 |

| 13 | 0.25 | 2    | 0/200 | 0/200 | 0/200  |        |

| 14 |      | 3    | 0/200 | 0/200 | 0/200  |        |

| 15 |      | 5    | 0/200 | 0/200 | 0/200  |        |

| 16 |      | 7    | 0/200 | 0/200 | 0/200  |        |

| 17 |      | 10   | 0/200 | 0/200 | 9/200  |        |

| 18 |      | 12   | 0/200 | 0/200 | 19/200 |        |

| 19 |      | 0.30 | 2     | 0/200 | 0/200  | 0/200  |

| 20 |      |      | 3     | 0/200 | 0/200  | 0/200  |

| 21 |      |      | 5     | 0/200 | 0/200  | 0/200  |

| 22 |      |      | 7     | 0/200 | 0/200  | 0/200  |

| 23 |      |      | 10    | 0/200 | 0/200  | 1/200  |

| 24 |      |      | 12    | 0/200 | 0/200  | 11/200 |

| 25 | 0.50 | 2    | 0/200 | 0/200 | 0/200  |        |

| 26 |      | 3    | 0/200 | 0/200 | 0/200  |        |

| 27 |      | 5    | 0/200 | 0/200 | 0/200  |        |

| 28 |      | 7    | 0/200 | 0/200 | 0/200  |        |

| 29 |      | 10   | 0/200 | 0/200 | 0/200  |        |

| 30 |      | 12   | 0/200 | 0/200 | 9/200  |        |

| 31 | 0.75 | 2    | 0/200 | 0/200 | 0/200  |        |

| 32 |      | 3    | 0/200 | 0/200 | 0/200  |        |

| 33 |      | 5    | 0/200 | 0/200 | 0/200  |        |

| 34 |      | 7    | 0/200 | 0/200 | 0/200  |        |

| 35 |      | 10   | 0/200 | 0/200 | 0/200  |        |

| 36 |      | 12   | 0/200 | 0/200 | 9/200  |        |

| 37 | 0.85 | 2    | 0/200 | 0/200 | 0/200  |        |

| 38 |      | 3    | 0/200 | 0/200 | 0/200  |        |

| 39 |      | 5    | 0/200 | 0/200 | 0/200  |        |

| 40 |      | 7    | 0/200 | 0/200 | 0/200  |        |

| 41 |      | 10   | 0/200 | 0/200 | 0/200  |        |

| 42 |      | 12   | 0/200 | 0/200 | 5/200  |        |

&lt;세라믹 소체의 두께가 100 mm인 적층 세라믹 커패시터&gt;

**표 4**

| No. | 세라믹 본체의<br>두께(mm) | S/T | A/C | 휩크랙 발생빈도 | Delamination | BDV 저하 |

|-----|-------------------|-----|-----|----------|--------------|--------|

|-----|-------------------|-----|-----|----------|--------------|--------|

|    |      |      |       |       |        |        |

|----|------|------|-------|-------|--------|--------|

| 1  | 150  | 0.15 | 2     | 0/200 | 0/200  | 0/200  |

| 2  |      |      | 3     | 0/200 | 0/200  | 0/200  |

| 3  |      |      | 5     | 0/200 | 0/200  | 0/200  |

| 4  |      |      | 7     | 0/200 | 0/200  | 18/200 |

| 5  |      |      | 10    | 0/200 | 0/200  | 35/200 |

| 6  |      |      | 12    | 0/200 | 0/200  | 64/200 |

| 7  |      | 0.20 | 2     | 0/200 | 0/200  | 0/200  |

| 8  |      |      | 3     | 0/200 | 0/200  | 0/200  |

| 9  |      |      | 5     | 0/200 | 0/200  | 0/200  |

| 10 |      |      | 7     | 0/200 | 0/200  | 16/200 |

| 11 |      |      | 10    | 0/200 | 0/200  | 31/200 |

| 12 |      |      | 12    | 0/200 | 0/200  | 57/200 |

| 13 | 0.25 | 2    | 0/200 | 0/200 | 0/200  |        |

| 14 |      | 3    | 0/200 | 0/200 | 0/200  |        |

| 15 |      | 5    | 0/200 | 0/200 | 0/200  |        |

| 16 |      | 7    | 0/200 | 0/200 | 9/200  |        |

| 17 |      | 10   | 0/200 | 0/200 | 22/200 |        |

| 18 |      | 12   | 0/200 | 0/200 | 45/200 |        |

| 19 |      | 0.30 | 2     | 0/200 | 0/200  | 0/200  |

| 20 |      |      | 3     | 0/200 | 0/200  | 0/200  |

| 21 |      |      | 5     | 0/200 | 0/200  | 0/200  |

| 22 |      |      | 7     | 0/200 | 0/200  | 6/200  |

| 23 |      |      | 10    | 0/200 | 0/200  | 17/200 |

| 24 |      |      | 12    | 0/200 | 0/200  | 32/200 |

| 25 | 0.50 | 2    | 0/200 | 0/200 | 0/200  |        |

| 26 |      | 3    | 0/200 | 0/200 | 0/200  |        |

| 27 |      | 5    | 0/200 | 0/200 | 0/200  |        |

| 28 |      | 7    | 0/200 | 0/200 | 2/200  |        |

| 29 |      | 10   | 0/200 | 0/200 | 11/200 |        |

| 30 |      | 12   | 0/200 | 0/200 | 25/200 |        |

| 31 | 0.75 | 2    | 0/200 | 0/200 | 0/200  |        |

| 32 |      | 3    | 0/200 | 0/200 | 0/200  |        |

| 33 |      | 5    | 0/200 | 0/200 | 0/200  |        |

| 34 |      | 7    | 0/200 | 0/200 | 0/200  |        |

| 35 |      | 10   | 0/200 | 0/200 | 7/200  |        |

| 36 |      | 12   | 0/200 | 0/200 | 18/200 |        |

| 37 | 0.85 | 2    | 0/200 | 0/200 | 0/200  |        |

| 38 |      | 3    | 0/200 | 0/200 | 0/200  |        |

| 39 |      | 5    | 0/200 | 0/200 | 0/200  |        |

| 40 |      | 7    | 0/200 | 0/200 | 0/200  |        |

| 41 |      | 10   | 0/200 | 0/200 | 0/200  |        |

| 42 |      | 12   | 0/200 | 0/200 | 8/200  |        |

[0089] <세라믹 소체의 두께가 150 mm인 적층 세라믹 커패시터>

[0090] 상기 표 1에서, S/T가 0.25 이상 0.75 이하인 샘플 13 내지 36에 있어서, A/C가 3 이상 10 이하인 경우 휨크랙 및 디라미네이션이 발생하지 않았으며, BDV 저하도 없음을 알 수 있다.

[0091] 그러나, S/T가 0.25 이상 0.75 이하인 경우에도, A/C가 3 미만인 샘플 13, 19, 25 및 31의 경우 휨크랙이 발생하였으며, A/C가 10을 초과하는 샘플 18, 24, 30 및 36의 경우 BDV가 저하되는 문제점이 있음을 알 수 있다.

[0092] 또한, S/T가 0.25 미만인 샘플들 중 샘플 5 및 11은 A/C가 10 이하일 때도 BDV가 저하되는 문제점이 있음을 알 수 있다.

[0093] 또한, S/T가 0.75를 초과하는 샘플 38 내지 41의 경우 A/C가 3 내지 10의 범위를 만족하더라도 휨크랙이 발생할 뿐만 아니라, 디라미네이션이 심하게 발생함을 알 수 있다.

- [0094] 상기 표 2에서, S/T가 0.25 이상 0.75 이하인 샘플 13 내지 36에 있어서, A/C가 3 이상 10 이하인 경우 휙크랙 및 디라미네이션이 발생하지 않았으며, BDV 저하도 없음을 알 수 있다.

[0095] 그러나, S/T가 0.25 이상 0.75 이하인 경우에도, A/C가 3 미만인 샘플 13, 19, 25 및 31의 경우 휙크랙이 발생하였으며, A/C가 10을 초과하는 샘플 18, 24, 30 및 36의 경우 BDV가 저하되는 문제점이 있음을 알 수 있다.

[0096] 또한, S/T가 0.25 미만인 샘플들 중 샘플 4, 5 및 11은 A/C가 10 이하일 때도 BDV가 저하되는 문제점이 있음을 알 수 있다.

[0097] 또한, S/T가 0.75를 초과하는 샘플 38 내지 41의 경우 A/C가 3 내지 10의 범위를 만족하더라도 휙크랙이 발생할 뿐만 아니라, 디라미네이션이 심하게 발생함을 알 수 있다.

[0098] 따라서, 휙크랙 및 디라미네이션의 발생이 억제되면서 BDV의 저하 또한 방지할 수 있는 바람직한 수치 범위는  $0.25 \leq S/T \leq 0.75$  및  $3 \leq E/B \leq 10$ 인 것을 알 수 있다.

[0099] 상기 표 3를 참조하면, S/T가 0.25 이상 0.75 이하이고, A/C가 3 이상 10 이하인 경우, 샘플 10, 17 및 23에서 휙크랙이나 디라미네이션의 발생은 없었으나 BDV 저하가 발생하였다.

[0100] 또한, 상기 표 4를 참조하면, S/T가 0.25 이상 0.75 이하이고, A/C가 3 이상 10 이하인 경우, 샘플 10, 11, 16, 17, 22, 23, 28, 29 및 35에서 휙크랙이나 디라미네이션의 발생은 없었으나 BDV 저하가 발생하였다.

[0101] 따라서, 휙크랙 및 디라미네이션의 발생이 억제되면서 BDV의 저하 또한 방지할 수 있는 세라믹 소체(110)의 두께는 바람직하게  $80 \mu\text{m}$  이하인 것을 알 수 있다.

[0102] 이상에서 본 발명의 실시 형태에 대하여 상세하게 설명하였지만 본 발명의 권리범위는 이에 한정되는 것은 아니고, 청구범위에 기재된 본 발명의 기술적 사항을 벗어나지 않는 범위 내에서 다양한 수정 및 변형이 가능하다는 것은 당 기술분야의 통상의 지식을 가진 자에게는 자명할 것이다.

부호의 설명

- [0103] 100, 100'; 적층 세라믹 커패시터

110 ; 세라믹 본체 111 ; 유전체층

112 ; 상부 커버층 113 ; 하부 커버층

115 ; 액티브층 121, 122 ; 제1 및 제2 내부 전극

131, 132 ; 제1 및 제2 외부 전극 131a, 132a ; 머리부

131b, 132b ; 밴드

도면

도면1

도면2

도면3

도면4