(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6747371号

(P6747371)

(45) 発行日 令和2年8月26日(2020.8.26)

(24) 登録日 令和2年8月11日(2020.8.11)

(51) Int.CI.

HO3K 19/0185 (2006.01)

F 1

HO3K 19/0185 210

請求項の数 6 (全 11 頁)

(21) 出願番号 特願2017-87490 (P2017-87490)

(22) 出願日 平成29年4月26日 (2017.4.26)

(65) 公開番号 特開2018-186408 (P2018-186408A)

(43) 公開日 平成30年11月22日 (2018.11.22)

審査請求日 令和1年5月15日 (2019.5.15)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100082175

弁理士 高田 守

(74) 代理人 100106150

弁理士 高橋 英樹

(74) 代理人 100148057

弁理士 久野 淑己

(72) 発明者 吉田 寛

福岡県福岡市西区今宿東一丁目1番1号

メルコセミコンダクタエンジニアリング株

式会社内

審査官 渡井 高広

最終頁に続く

(54) 【発明の名称】高圧レベルシフト回路及び駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

オン指令によって駆動する第1の高耐圧N MOSトランジスタと、

オフ指令によって駆動する第2の高耐圧N MOSトランジスタと、

前記第1の高耐圧N MOSトランジスタのドレイン電流を基準側に入力する第1のPMOSカレントミラー回路と、

前記第2の高耐圧N MOSトランジスタのドレイン電流を基準側に入力する第2のPMOSカレントミラー回路と、

前記第2のPMOSカレントミラー回路の出力電流を基準側に入力する第1のN MOSカレントミラー回路と、

前記第1のPMOSカレントミラー回路の出力と前記第1のN MOSカレントミラー回路の出力を入力して出力制御電圧信号を得るI/V信号変換回路とを備え、

前記第1のPMOSカレントミラー回路の基準側PMOSトランジスタのソース及びド

レインに並列に接続された第1のPMOSトランジスタと、

前記第2のPMOSカレントミラー回路の基準側PMOSトランジスタのソース及びド

レインに並列に接続された第2のPMOSトランジスタとを更に備え、

前記第1のPMOSトランジスタのゲートは前記第2のPMOSカレントミラー回路の

ゲート電位によって駆動され、

前記第2のPMOSトランジスタのゲートは前記第1のPMOSカレントミラー回路の

ゲート電位によって駆動されることを特徴とする高圧レベルシフト回路。

10

20

## 【請求項 2】

前記第1のPMOSカレントミラー回路の出力電流を基準側に入力する第2のNMOSカレントミラー回路と、

前記第2のNMOSカレントミラー回路の出力電流を基準側に入力する第3のPMOSカレントミラー回路とを更に備え、

前記I/V信号変換回路は、前記第1のNMOSカレントミラー回路の出力と前記第3のPMOSカレントミラー回路の出力を入力して出力制御電圧信号を得ることを特徴とする請求項1に記載の高圧レベルシフト回路。

## 【請求項 3】

前記第1のNMOSカレントミラー回路は、出力電流が基準側電流にフィードバックされるウィルソン型カレントミラー回路であることを特徴とする請求項1又は2に記載の高圧レベルシフト回路。 10

## 【請求項 4】

前記第1及び第2のPMOSカレントミラー回路は、出力電流が基準側電流にフィードバックされるウィルソン型カレントミラー回路であることを特徴とする請求項1~3の何れか1項に記載の高圧レベルシフト回路。

## 【請求項 5】

前記I/V信号変換回路はラッチ回路であることを特徴とする請求項1~4の何れか1項に記載の高圧レベルシフト回路。 20

## 【請求項 6】

請求項1~5の何れか1項に記載の高圧レベルシフト回路を備え、SiC材料からなるパワーデバイスを駆動することを特徴とする駆動装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、IGBT又はMOSFET等のパワーデバイスを駆動する駆動装置及びそれに用いられる高圧レベルシフト回路に関する。 30

## 【背景技術】

## 【0002】

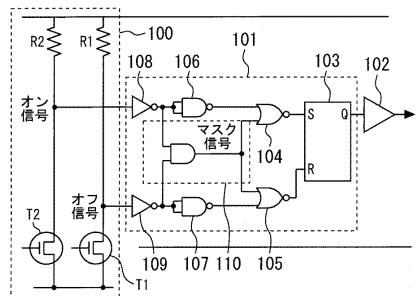

図9は、従来の駆動回路を示す図である。駆動回路は、高圧レベルシフト回路100、伝達回路101、及びドライバ回路102を備える。高圧レベルシフト回路100は、抵抗R1, R2、及び高耐圧電界効果トランジスタ(以下「HNMOSトランジスタ」という。)T1, T2を有する。伝達回路101は、RS型フリップフロップ103、NORゲート104, 105、NANDゲート106, 107、I/V信号変換回路ゲート108, 109、及びANDゲートからなるマスク信号回路110を有する。ドライバ回路102はパワーデバイスに接続され、その出力信号によりパワーデバイスを駆動する。 30

## 【0003】

パワーデバイスのオン・オフ動作を制御するための高電位側信号が高圧レベルシフト回路100に入力される。高電位側信号はパルス状の信号であり、高圧レベルシフト回路100のT1, T2に入力され、高電位にレベルシフトされる。レベルシフトされたオン信号、オフ信号は伝達回路101を介してドライバ回路102からパワーデバイスに伝達される。 40

## 【0004】

一般に、駆動回路により駆動されるパワーデバイスの負荷はモータ等のインダクタンス負荷である場合が多い。インダクタンス負荷、又はプリント基板上の配線等による寄生インダクタンス成分等の影響により、スイッチング時に駆動回路の高電位側基準電位VSが低電位側グランドGNDに対して負側へ変動する。この負側に変動した高電位側基準が低電位側基準まで復帰する際に高電位側信号が誤信号となる。また、この誤信号は、高電位側基準電位が低電位から高電位に遷移する時のdV/dtによって発生する場合もある。 50

## 【0005】

誤信号により、T1, T2の寄生容量又は寄生ダイオード等を介して高電位側電源に接続されたレベルシフト抵抗R1, R2に電流が流れる。これにより、電圧降下が生じ、後段の伝達回路101に誤信号が伝達され、パワーデバイスの誤動作を招く。

## 【0006】

この誤動作対策として従来の駆動回路ではロジックフィルタ方式を使用している。即ち、誤信号をキャンセルする信号を生成するマスク信号回路110を設けている。マスク信号回路110は具体的にはオン信号、オフ信号が共にアクティブになった時にそれらの信号がRS型フリップフロップ103に伝達されないようにマスクするためのマスク信号を生成する。このマスク信号を用いて、NANDゲート106, 107から出力された主信号をマスクする。この時、主信号とマスク信号の動作領域は同じに設定されているが、各々の動作領域にバラツキが生じた場合は、誤信号が後段の伝達回路101へ伝達される場合がある。

10

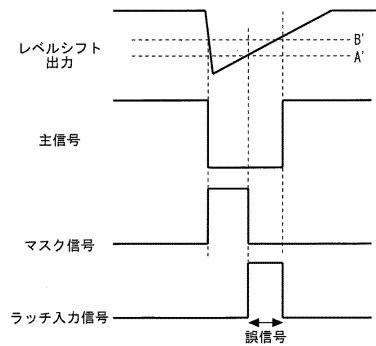

## 【0007】

図10は、従来の駆動回路の動作を示すタイミングチャートである。ここでは、高圧レベルシフト回路100の出力であるオン信号、オフ信号がdV/dt等の影響により急激に低下し、NANDゲート106, 107の閾値とマスク信号回路110の閾値とがバラツキ等により異なる場合を考える。NANDゲート106, 107の閾値が破線B'で示され、マスク信号回路110のANDゲートの閾値が破線A'で示される。この場合、マスク信号がアクティブ(ハイ)になる範囲が、主信号が障害により非アクティブ(ロー)になる範囲よりも狭くなる。このため、誤って非アクティブになった主信号である誤信号が十分にマスクされないことになる。このため、RS型フリップフロップ103のセット入力信号であるラッチ入力信号において誤信号が発生する。

20

## 【0008】

これに対して、安定した動作を供給するレベルシフト回路が開示されている(例えば、特許文献1参照)。しかし、レベルシフト電流を発生させるHVN MOSに加えて、安定動作のためにさらに別の定電流源により定常的にレベルシフト回路に電流を流している。

## 【先行技術文献】

## 【特許文献】

## 【0009】

30

## 【特許文献1】特開2010-161753号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0010】

600V又は1200Vといった高圧系においてレベルシフトを行う場合は、発熱量低減のため、高圧レベルシフトにかかる電流は極力排除する必要がある。従って、従来技術で必須であった別の定電流源を用いずに電流を低減した高圧レベルシフト回路が所望される。

## 【0011】

本発明は、上述のような課題を解決するためになされたもので、その目的は誤信号の伝達を防ぎつつ、電流を低減することができる高圧レベルシフト回路及び駆動装置を得るものである。

40

## 【課題を解決するための手段】

## 【0012】

本発明に係る高圧レベルシフト回路は、オン指令によって駆動する第1の高耐圧N MOSトランジスタと、オフ指令によって駆動する第2の高耐圧N MOSトランジスタと、前記第1の高耐圧N MOSトランジスタのドレイン電流を基準側に入力する第1のPMOSカレントミラー回路と、前記第2の高耐圧N MOSトランジスタのドレイン電流を基準側に入力する第2のPMOSカレントミラー回路と、前記第2のPMOSカレントミラー回路の出力電流を基準側に入力する第1のN MOSカレントミラー回路と、前記第1のPM

50

OS カレントミラー回路の出力と前記第 1 の N MOS カレントミラー回路の出力を入力して出力制御電圧信号を得る I / V 信号変換回路とを備え、前記第 1 の PMOS カレントミラー回路の基準側 PMOS トランジスタのソース及びドレインに並列に接続された第 1 の PMOS トランジスタと、前記第 2 の PMOS カレントミラー回路の基準側 PMOS トランジスタのソース及びドレインに並列に接続された第 2 の PMOS トランジスタとを更に備え、前記第 1 の PMOS トランジスタのゲートは前記第 2 の PMOS カレントミラー回路のゲート電位によって駆動され、前記第 2 の PMOS トランジスタのゲートは前記第 1 の PMOS カレントミラー回路のゲート電位によって駆動されることを特徴とする。

【発明の効果】

【0013】

10

本発明では、第 1 及び第 2 の PMOS カレントミラー回路がそれぞれ第 1 及び第 2 の高耐圧 N MOS トランジスタのドレイン電流を基準側に入力し、第 1 の N MOS カレントミラー回路が第 2 の PMOS カレントミラー回路の出力電流を基準側に入力し、I / V 信号変換回路が第 1 の PMOS カレントミラー回路の出力と第 1 の N MOS カレントミラー回路の出力を入力して出力制御電圧信号を得る。これにより、誤信号の伝達を防ぎつつ、電流を低減することができる。

【図面の簡単な説明】

【0014】

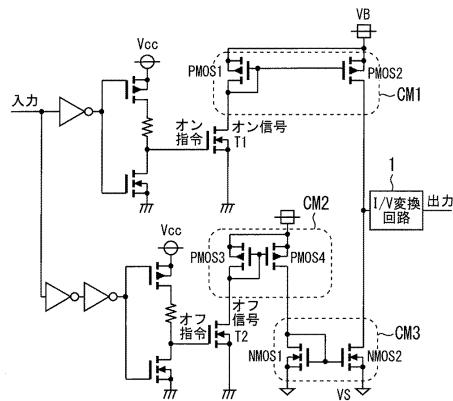

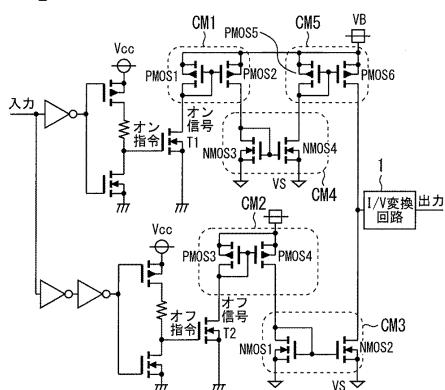

【図 1】本発明の実施の形態 1 に係る高圧レベルシフト回路を示す図である。

20

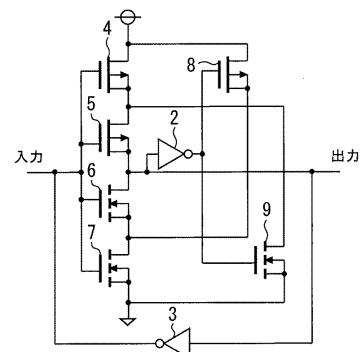

【図 2】本発明の実施の形態 1 に係る I / V 信号変換回路を示す図である。

【図 3】本発明の実施の形態 1 に係る I / V 信号変換回路の変形例を示す図である。

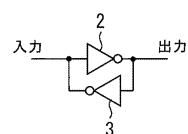

【図 4】本発明の実施の形態 1 に係る高圧レベルシフト回路の変形例を示す図である。

【図 5】本発明の実施の形態 2 に係る高圧レベルシフト回路を示す図である。

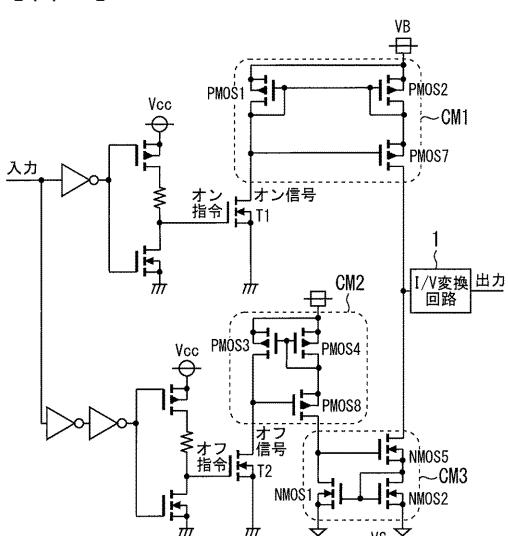

【図 6】本発明の実施の形態 3 に係る高圧レベルシフト回路を示す図である。

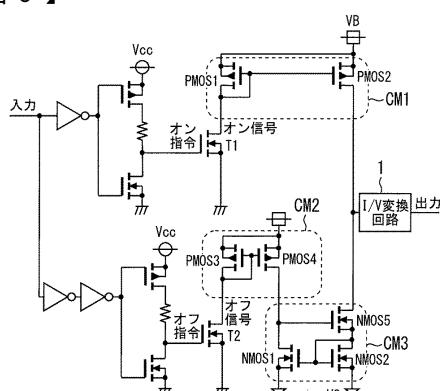

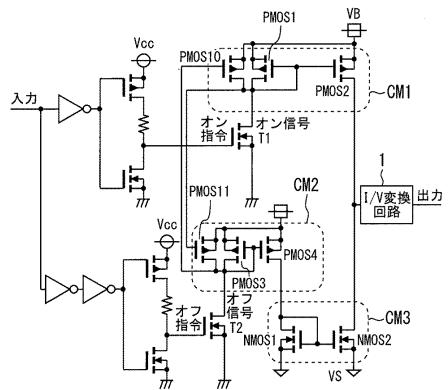

【図 7】本発明の実施の形態 4 に係る高圧レベルシフト回路を示す図である。

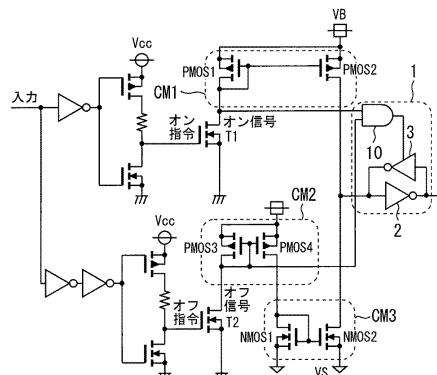

【図 8】本発明の実施の形態 5 に係る高圧レベルシフト回路を示す図である。

【図 9】従来の駆動回路を示す図である。

【図 10】従来の駆動回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0015】

30

本発明の実施の形態に係る高圧レベルシフト回路及び駆動装置について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

【0016】

実施の形態 1 。

図 1 は、本発明の実施の形態 1 に係る高圧レベルシフト回路を示す図である。高圧レベルシフト回路に対して、パワーデバイスのオン・オフ動作を指令するための高電位側信号が入力される。この高電位側信号は直流信号であり、高耐圧電界効果 ( HN MOS ) トランジスタである T 1 , T 2 にそれぞれ入力され、電流信号となって高電位にレベルシフトされる。即ち、T 1 は、オン指令によって駆動し、パワーデバイスをオンに制御するためのオン信号を出力する。T 2 は、オフ指令によって駆動し、パワーデバイスをオフに制御するためのオフ信号を出力する。オン信号、オフ信号を総称して主信号という。

40

【0017】

カレントミラー回路 CM 1 は、PMOS トランジスタである PMOS 1 , PMOS 2 を有し、T 1 のドレイン電流を基準側に入力する。PMOS 1 のゲートとドレインは互いに接続され、かつ PMOS 2 のゲートに接続されている。PMOS 2 は PMOS 1 のドレイン電流に対して所定の比率のドレイン電流を流す。

【0018】

カレントミラー回路 CM 2 は、PMOS トランジスタである PMOS 3 , PMOS 4 を有し、T 2 のドレイン電流を基準側に入力する。PMOS 3 のゲートとドレインは互いに

50

接続され、かつPMOS4のゲートに接続されている。PMOS4はPMOS3のドレイン電流に対して所定の比率のドレイン電流を流す。

【0019】

カレントミラー回路CM3は、NMOSトランジスタであるNMOS1, NMOS2を有し、カレントミラー回路CM2の出力電流を基準側に入力する。NMOS1のゲートとドレインは互いに接続され、かつPMOS4のドレインに接続されている。

【0020】

PMOS2のドレインとNMOS2のドレインの接続点がI/V信号変換回路1の入力に接続されている。I/V信号変換回路1は、カレントミラー回路CM1の出力とカレントミラー回路CM3の出力を入力して出力制御電圧信号を得る。

10

【0021】

続いて、本実施の形態に係る高圧レベルシフト回路の動作を説明する。T1がオン状態になって発生したオン信号は、カレントミラー回路CM1の動作により所定の比率でPMOS2はドレイン電流を流す。この際にT2はオフ状態であり、PMOS3, PMOS4, NMOS1には電流が流れないと、NMOS2は電流を流すことが出来ないハイインピーダンス状態である。従ってPMOS2のドレインとNMOS2のドレインの接続部には定常的な電流は流れることなく、その電圧レベルは電源とほぼ同等となる。これをI/V信号変換回路1がオン信号の出力制御電圧信号として出力する。一方、T2がオン状態の場合、NMOS2が所定の電流を流そうとするが、PMOS2がハイインピーダンスであるため、PMOS2のドレインとNMOS2のドレインの接続部にはやはり定常電流は流れず、I/V信号変換回路1がオフ信号の出力制御電圧信号を出力する。

20

【0022】

高圧電位遷移などによりT1, T2が主信号を受け付けていないにも関わらずPMOS1とPMOS3に同時に電流が流れた場合の挙動について説明する。PMOS1, PMOS3双方に電流が流れた場合、カレントミラー回路CM1, CM2, CM3の動作によりPMOS2とNMOS2はそれぞれ電流を流す。

【0023】

定常状態にはT1, T2の一方がオン状態で他方はオフ状態である。例えばT1がオン状態である場合は、PMOS2がNMOS2に比較してローラインピーダンスでありI/V信号変換回路1の入力はHレベルである。その状態で高圧電位遷移などによりPMOS1, PMOS3双方に電流が流れても、PMOS1に流れる電流はPMOS3に流れる電流より主信号の電流分多い。即ち、PMOS2の電流がNMOS2の電流よりも多いためI/V信号変換回路1への入力はHレベルを保持し、出力論理が誤反転することはない。一方、T2がオン状態である場合は、上記とは逆にNMOS2の電流がPMOS2の電流よりも多くなるため、I/V信号変換回路1の入力はLレベルを保持し、やはり出力論理は誤反転しない。

30

【0024】

主信号をパルス駆動する場合でも同様の効果を得ることができる。パルス駆動の場合、定常状態にはPMOS2もNMOS2もハイインピーダンスであって、I/V信号変換回路1の入力電圧は高圧レベルシフト回路にオン信号、オフ信号の何れが入力された後かによって決まっている。この状態でPMOS1とPMOS3に同時に電流が流れた場合、I/V信号変換回路1の入力電圧はPMOS2とNMOS2のインピーダンスの差分によって電位遷移を起こす。従って、従来技術のように差分に依らない方式に比べて誤信号自体が弱まり、出力誤反転が発生しにくい。これは従来技術で問題となっていた、オン信号とオフ信号から生成するマスク信号発生に要求されるペアリングが緩和される、とも換言できる。

40

【0025】

また、パワーデバイスのスイッチングなどで、高圧側電源の電位が低圧側基準電位より低電位となった際は、PMOS1, PMOS2, PMOS3, PMOS4, NMOS1, NMOS2の全てがハイインピーダンスとなる。I/V信号変換回路1への入力電圧は直

50

前の状態が保持されるためやはり出力の誤反転を防止できる。また、本実施の形態では、高圧側基準電位が低圧側基準電位を超えて低下した際の信号伝達可能領域を従来技術よりも容易に広くできる。

【0026】

高圧側電源電圧を一定として高圧側基準電位が低圧側基準電位よりも低下すると、高圧レベルシフト回路の両端の電位差、即ち高圧側電源と低圧側基準電位の電位差が狭まってT1, T2に十分な電流が流せなくなる。従来技術のように高圧レベルシフトされた主信号を電圧信号として受けるI/V信号変換回路のしきい値よりも本実施の形態のようにMOSトランジスタが電流を流すのに必要なゲート-ドレイン電圧の方が一般的に低いからである。従って、高電圧遷移が生じた際などの変位電流に基づいて発生する誤信号を除去でき、意図しない出力論理反転を防止できる。

10

【0027】

以上説明したように、本実施の形態では、カレントミラー回路CM1, CM2がそれぞれT1, T2のドレイン電流を基準側に入力し、カレントミラー回路CM3がカレントミラー回路CM2の出力電流を基準側に入力し、I/V信号変換回路1がカレントミラー回路CM1の出力とカレントミラー回路CM3の出力を入力して出力制御電圧信号を得る。これにより、誤信号の伝達を防ぎつつ、電流を低減することができる。

【0028】

図2は、本発明の実施の形態1に係るI/V信号変換回路を示す図である。I/V信号変換回路1は、2つのインバータ2, 3が逆並列に接続されたラッチ回路である。このラッチ効果により、上記ハイインピーダンス状態が継続した場合でもI/V信号変換回路1への入力が不安定にならない。

20

【0029】

図3は、本発明の実施の形態1に係るI/V信号変換回路の変形例を示す図である。I/V信号変換回路1は、インバータ2, 3とトランジスタ4~9を有するシュミットトリガ回路である。シュミットトリガ回路は入力しきい値電圧にヒステリシスを持つため、更に安定度が増す。

【0030】

図4は、本発明の実施の形態1に係る高圧レベルシフト回路の変形例を示す図である。I/V信号変換回路1のフィードバック側のインバータ3をスリーステートバッファにて構成する。T1, T2のドレイン電圧を入力するAND回路10によりインバータ3を制御して、ハイインピーダンスとなる無信号入力時のI/V信号変換回路1をラッチ動作させる。これにより、高圧レベルシフト回路をパルス駆動させる場合において、ラッチ回路による出力オン信号とオフ信号の伝達は阻害せず、無信号入力時にはラッチで出力を安定化できる。また、消費電流を低減することができる。また、直流駆動において電流が流れなくなった際にも出力を安定化できる。

30

【0031】

実施の形態2.

図5は、本発明の実施の形態2に係る高圧レベルシフト回路を示す図である。実施の形態1の構成にカレントミラー回路CM4, CM5が追加されている。カレントミラー回路CM4は、NMOSトランジスタであるNMOS3, NMOS4を有し、カレントミラー回路CM1の出力電流を基準側に入力する。カレントミラー回路CM5は、PMOSトランジスタであるPMOS5, PMOS6を有し、カレントミラー回路CM4の出力電流を基準側に入力する。I/V信号変換回路1は、カレントミラー回路CM3の出力とカレントミラー回路CM5の出力を入力して出力制御電圧信号を得る。

40

【0032】

誤信号電流がPMOS1, PMOS3及びT1, T2などに流れる際、電流強度に応じてPMOS1, PMOS3のゲート電位及びドレイン電位が深く掛かる。このとき、例えばNMOS1, NMOS2のトランジスタサイズを増し、さらにPMOS3とPMOS4の電流比を抑えることでNMOS1, NMOS2の電流密度を抑えると、電流密度が高い

50

場合よりもN MOS 1, N MOS 2のゲート電位及びドレイン電位を低くできる。さらに、PMOS 3, 4のゲート電位及びドレイン電圧はカレントミラー回路としてPMOS 3のドレイン電流とPMOS 4のドレイン電流の比率を保ちながらより多くの電流を流すことができるようになる。

【0033】

実施の形態1の構成では、PMOS 2のドレインがN MOS 2のドレインに直接接続されている。このため、発生した誤信号電流に基づいた電流がPMOS 2からN MOS 2に流れる際に、PMOS 2にかかるドレイン電圧が誤信号の電流値に応じて過剰に増加し、I/V信号変換回路1の入力電圧が下がってしまい出力が誤反転する恐れがある。

【0034】

これに対して、本実施の形態ではカレントミラー回路CM 4, CM 5が追加されている。このため、PMOS 1, PMOS 2もPMOS 3, PMOS 4と同様により多くの電流に対してI/V信号変換回路1の入力信号を保持できるようになる。従って、高圧電位遷移時等に発生する偽の電流信号を実施の形態1より多く流すことができるため、誤動作防止機能を高めることができる。

【0035】

実施の形態3。

図6は、本発明の実施の形態3に係る高圧レベルシフト回路を示す図である。実施の形態1との相違点として、カレントミラー回路CM 3は、N MOS 1, N MOS 2に、NMOSトランジスタであるN MOS 5を追加したウィルソン型カレントミラー回路である。ウィルソン型カレントミラー回路では、出力電流が基準側電流にフィードバックされる。N MOS 1, 2のゲートバイアスを出力側で行うため、出力側の電流が流れなければ、基準側の電流も流れない。

【0036】

実施の形態1, 2で直流信号をレベルシフトする場合、PMOS 4とN MOS 1の部分に定常電流が流れる状態がある。一方、本実施の形態では、ウィルソン型カレントミラー回路を用いるため、その部分の定常電流を無くすことができる。高圧内部への電流供給は、高圧内部が低圧状態にある間に低圧側電源から高圧側電源に並列されたコンデンサに充電された電荷を用いることが多い。本実施の形態により高圧内部での電流消費を低減することができる。

【0037】

実施の形態4。

図7は、本発明の実施の形態4に係る高圧レベルシフト回路を示す図である。実施の形態3の構成に加えて、カレントミラー回路CM 1は、PMOS 1, PMOS 2に、PMOSトランジスタであるPMOS 7を追加したウィルソン型カレントミラー回路である。そして、カレントミラー回路CM 2も、PMOS 3, PMOS 4に、PMOSトランジスタであるPMOS 8を追加したウィルソン型カレントミラー回路である。高圧側電源からT1, T2に電流を供給するが、本実施の形態ではこの定常電流も下げることができる。例えば、高圧側電源にアノード、T1, T2のドレインにカソードを接続したダイオードを追加すると、高圧側素子に過大な電圧が印加されることを防止しつつ、高圧側電源の電流消費を抑えることができる。

【0038】

実施の形態5。

図8は、本発明の実施の形態5に係る高圧レベルシフト回路を示す図である。実施の形態1の構成に加えてPMOSトランジスタであるPMOS 10, PMOS 11が追加されている。PMOS 10は、カレントミラー回路CM 1の基準側PMOSトランジスタであるPMOS 1のソース及びドレインに並列に接続されている。PMOS 11は、カレントミラー回路CM 2の基準側PMOSトランジスタであるPMOS 3のソース及びドレインに並列に接続されている。PMOS 10のゲートは、PMOS 3のドレイン及びゲートに接続され、カレントミラー回路CM 2のゲート電位によって駆動される。PMOS 11の

10

20

30

40

50

ゲートは、PMOS1のドレイン及びゲートに接続され、カレントミラー回路CM1のゲート電位によって駆動される。

【0039】

例えば高圧レベルシフト回路にオン信号が入力される場合、PMOS1のゲート・ドレインはバイアスされ、PMOS11も同様にバイアスされる。ただし、T2にはオフ信号が入力されていないため、PMOS11を経由した電流は流れない。

【0040】

高圧電位遷移等により誤信号電流が発生すると、実施の形態1ではPMOS3に誤信号電流として電流が流れ、この誤信号電流はI/V信号変換回路1に接続された部分でPMOS2及びNMOS2により打ち消される。一方、本実施の形態では、誤信号電流の一部はゲートバイアスされているPMOS11を経由してT2などに流れ込む。このため、PMOS3を経由しNMOS2に伝達される誤信号電流がPMOS3の部分で既に低減される。一方、PMOS10は、PMOS11又はPMOS3に誤信号電流が流れるまでは、ゲートバイアスされず、誤信号電流は全てPMOS1を経由してT1などに流れ込む。T1及びPMOS1にはオン信号が入力されているため、さらにオン信号を強めるように電流が流れる。つまり、PMOS11によって誤信号電流のみが弱められるため、出力の誤反転防止を強化することができる。なお、高圧レベルシフト回路にオフ信号が入力されている場合も同様に出力誤反転防止が強化される。

【0041】

また、本実施の形態では、パワーデバイスの通常の駆動時の論理伝達は実施の形態1等と同じであるが、主信号の伝達速度を速めることができる。即ち、T1, T2がオン状態からオフ状態になる際にはT1, T2のドレイン-ソース間のバックゲート容量などの寄生容量を充電する必要があるが、この充電をバイアスされたPMOS10, PMOS11で行うことができるため応答速度が向上する。

【0042】

なお、本実施の形態ではPMOS1, PMOS3に並列にPMOS10, PMOS11を接続したが、NMOS1, NMOS2などの他のカレントミラー回路に同様の構成を適用しても同様の効果を得ることができる。

【0043】

また、駆動回路が駆動するパワーデバイスとして、SiC材料からなるMOSFETは、Si材料からなるIGBT又はMOSFETに比べて動作スピードが早く、dV/dtがより強くなる。従って、SiMOSFETなどのSiC材料からなるパワーデバイスを駆動する駆動装置に実施の形態1～5に係る高圧レベルシフト回路を適用して誤動作を防止することが望ましい。

【符号の説明】

【0044】

1 I/V信号変換回路、CM1 カレントミラー回路（第1のPMOSカレントミラー回路）、CM2 カレントミラー回路（第2のPMOSカレントミラー回路）、CM3 カレントミラー回路（第1のNMOSカレントミラー回路）、CM4 カレントミラー回路（第2のNMOSカレントミラー回路）、CM5 カレントミラー回路（第3のPMOSカレントミラー回路）、PMOS10 PMOSトランジスタ（第1のPMOSトランジスタ）、PMOS11 PMOSトランジスタ（第2のPMOSトランジスタ）、T1 高耐圧電界効果トランジスタ（第1の高耐圧NMOSトランジスタ）、T2 高耐圧電界効果トランジスタ（第2の高耐圧NMOSトランジスタ）

10

20

30

40

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図10】

【図9】

---

フロントページの続き

(56)参考文献 特開2003-179482(JP,A)

特開2001-356829(JP,A)

特開2005-204268(JP,A)

特開平07-226669(JP,A)

特開平06-077804(JP,A)

特開2003-133942(JP,A)

特開2005-257804(JP,A)

特開2010-226835(JP,A)

特開2010-161753(JP,A)

特開2001-085988(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/0185