(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-43955

(P2012-43955A)

(43) 公開日 平成24年3月1日(2012.3.1)

|                         |                    |             |

|-------------------------|--------------------|-------------|

| (51) Int.Cl.            | F 1                | テーマコード (参考) |

| HO 1 L 29/78 (2006.01)  | HO 1 L 29/78 652 C | 5 F 1 4 O   |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 301 V |             |

|                         | HO 1 L 29/78 653 A |             |

|                         | HO 1 L 29/78 652 E |             |

|                         | HO 1 L 29/78 652 H |             |

審査請求 未請求 請求項の数 8 O L (全 14 頁) 最終頁に続く

|           |                              |          |                                       |

|-----------|------------------------------|----------|---------------------------------------|

| (21) 出願番号 | 特願2010-183398 (P2010-183398) | (71) 出願人 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (22) 出願日  | 平成22年8月18日 (2010.8.18)       | (74) 代理人 | 100108062<br>弁理士 日向寺 雅彦               |

|           |                              | (72) 発明者 | 佐藤 慎吾<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内   |

|           |                              | (72) 発明者 | 篠原 仁<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内    |

|           |                              | (72) 発明者 | 河村 圭子<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内   |

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】耐圧を向上した半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。第1導電形の第1半導体領域は、第1部分と第1方向に延出した第2部分とを有する。第1導電形の第2半導体領域は、第1部分上の第3部分と第2部分と隣接する第4部分とを有する。第2導電形の第3半導体領域は、第3部分上の第5部分と第4部分と隣接する第6部分とを有する。第1導電形の第4半導体領域は、第5部分上で第6部分と隣接する。ゲート領域は、第2半導体領域、第3半導体領域及び第4半導体領域を第2方向に貫通するトレンチ内に設けられる。ゲート絶縁膜は、トレンチ内壁とゲート領域との間に設けられる。第2導電形の電界緩和領域は、第3部分と第5部分との間に設けられ、第3半導体領域よりも不純物濃度が低い。

【選択図】図 1

## 【特許請求の範囲】

## 【請求項 1】

第1主面を含む第1部分と、前記第1主面に対して直交する第1方向に延出した第2部分と、を有する第1導電形の第1半導体領域と、

前記第1部分の側において前記第2部分の前記第1方向に沿った長さよりも短く設けられた第3部分と、前記第2部分と隣接し前記第3部分の上面の一部から前記第1方向に延出した第4部分と、を有する第1導電形の第2半導体領域と、

前記第3部分の側において前記第4部分の前記第1方向に沿った長さよりも短く設けられた第5部分と、前記第4部分と隣接し前記第5部分の上面の一部から前記第1方向に延出した第6部分と、を有する第2導電形の第3半導体領域と、

前記第5部分の上において前記第6部分と隣接して設けられた第1導電形の第4半導体領域と、

前記第1方向と直交する第2方向であって、前記第2半導体領域、前記第3半導体領域及び前記第4半導体領域に形成されたトレンチ内に設けられたゲート領域と、

前記トレンチの内壁と、前記ゲート領域と、の間に設けられたゲート絶縁膜と、

前記第3部分と、前記第5部分と、の間に設けられ、前記第3半導体領域の不純物濃度よりも低い不純物濃度を有する第2導電形の電界緩和領域と、

を備えたことを特徴とする半導体装置。

## 【請求項 2】

前記第2部分は、前記第1方向及び前記第2方向と直交する第3方向に延びるよう設けられたことを特徴とする請求項1記載の半導体装置。

## 【請求項 3】

前記第3方向に沿って、複数の前記ゲート領域及び複数の前記ゲート絶縁膜が設けられたことを特徴とする請求項2記載の半導体装置。

## 【請求項 4】

前記第2半導体領域、前記第3半導体領域及び前記第4半導体領域は、前記第3方向に沿って延在することを特徴とする請求項2または3に記載の半導体装置。

## 【請求項 5】

前記ゲート領域の前記第1方向に沿った第1の長さは、前記第4半導体領域の前記第1方向に沿った第2の長さよりも低いことを特徴とする請求項1～4のいずれか1つに記載の半導体装置。

## 【請求項 6】

第1主面を含む第1部分と、前記第1主面に対して直交する第1方向に延出した第2部分と、を有する第1導電形の第1半導体領域を形成する工程と、

前記第1半導体領域を第1導電形の第2半導体領域で覆い、前記第1部分の側において前記第2部分の前記第1方向に沿った長さよりも短く設けられた第3部分と、前記第2部分と隣接し前記第3部分の上面の一部から前記第1方向に延出した第4部分と、を形成する工程と、

前記3部分における、前記第1主面と対向した第2主面に、第2導電形の電界緩和領域を形成する工程と、

前記第2半導体領域を第2導電形の第3半導体領域で覆い、前記第3部分の側において前記第4部分の前記第1方向に沿った長さよりも短く設けられた第5部分と、前記第4部分と隣接し前記第5部分の上面の一部から前記第1方向に延出した第6部分と、を形成する工程と、

前記第3半導体領域を第1導電形の第4半導体領域で覆う工程と、

前記第4半導体領域、前記第3半導体領域及び前記第2半導体領域を、前記第2部分が露出するまで除去する工程と、

前記第1方向と直交する第2方向であって、前記第2半導体領域、前記第3半導体領域及び前記第4半導体領域にトレンチを形成し、前記トレンチ内にゲート絶縁膜を介してゲート領域を形成する工程と、

10

20

30

40

50

を備えたことを特徴とする半導体装置の製造方法。

【請求項 7】

前記電界緩和領域を形成する工程では、前記第2主面に第2導電形となる不純物のイオンを注入することを特徴とする請求項6記載の半導体装置の製造方法。

【請求項 8】

前記イオンの入射角度は、前記第2主面には前記イオンが注入され、前記第4部分における前記第2部分の側面と対向した第3主面には前記イオンが注入されない角度であることを特徴とする請求項7記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来より、例えば電力用MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) の構造として、プレーナ型MOSFETやトレンチ型MOSFETが採用されている。また、MOSFETのチャネル幅を基板の深さ方向に設けた、いわゆる3D (three-dimensional) 型も考えられている。しかしながら、いわゆる3D型のMOSFETにおいては、更なる耐圧の向上が求められている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001-274398号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、耐圧を向上した半導体装置及びその製造方法を提供する。

【課題を解決するための手段】

【0005】

本実施形態に係る半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。

第1半導体領域は、第1主面を含む第1部分と、第1主面に対して直交する第1方向に延出した第2部分と、を有する第1導電形の領域である。

第2半導体領域は、第1部分の側において第2部分の第1方向に沿った長さよりも短く設けられた第3部分と、第2部分と隣接し第3部分の上面の一部から第1方向に延出した第4部分と、を有する第1導電形の領域である。

第3半導体領域は、第3部分の側において第4部分の第1方向に沿った長さよりも短く設けられた第5部分と、第4部分と隣接し第5部分の上面の一部から第1方向に延出した第6部分と、を有する第2導電形の領域である。

第4半導体領域は、第5部分の上において第6部分と隣接して設けられた第1導電形の領域である。

ゲート領域は、第1方向と直交する第2方向であって、第2半導体領域、第3半導体領域及び第4半導体領域に形成されたトレンチ内に設けられている。

ゲート絶縁膜は、トレンチの内壁と、ゲート領域と、の間に設けられている。

電界緩和領域は、第3部分と、第5部分と、の間に設けられ、第3半導体領域の不純物濃度よりも低い不純物濃度を有する第2導電形の領域である。

【0006】

また、他の実施形態に係る半導体装置の製造方法は、先ず、第1主面を含む第1部分と、第1主面に対して直交する第1方向に延出した第2部分と、を有する第1導電形の第1半導体領域を形成する。

10

20

30

40

50

次に、第1半導体領域を第1導電形の第2半導体領域で覆う。これにより、第1部分の側において第2部分の第1方向に沿った長さよりも短く設けられた第3部分と、第2部分と隣接し第3部分の上面の一部から第1方向に延出した第4部分と、を形成する。

次に、第3部分における、第1主面と対向した第2主面に、第2導電形の電界緩和領域を形成する。

次に、第2半導体領域を第2導電形の第3半導体領域で覆う。これにより、第3部分の側において第4部分の第1方向に沿った長さよりも短く設けられた第5部分と、第4部分と隣接し第5部分の上面の一部から第1方向に延出した第6部分と、を形成する。

次に、第3半導体領域を第1導電形の第4半導体領域で覆う。

次に、第4半導体領域、第3半導体領域及び第2半導体領域を、第2部分が露出するまで除去する。 10

次に、第1方向と直交する第2方向であって、第2半導体領域、第3半導体領域及び第4半導体領域にトレンチを形成し、このトレンチ内にゲート絶縁膜を介してゲート領域を形成する。

#### 【図面の簡単な説明】

##### 【0007】

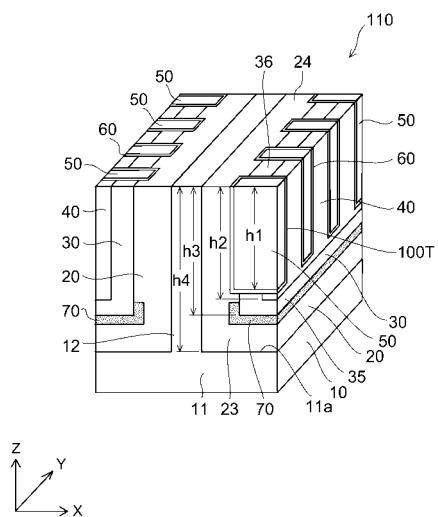

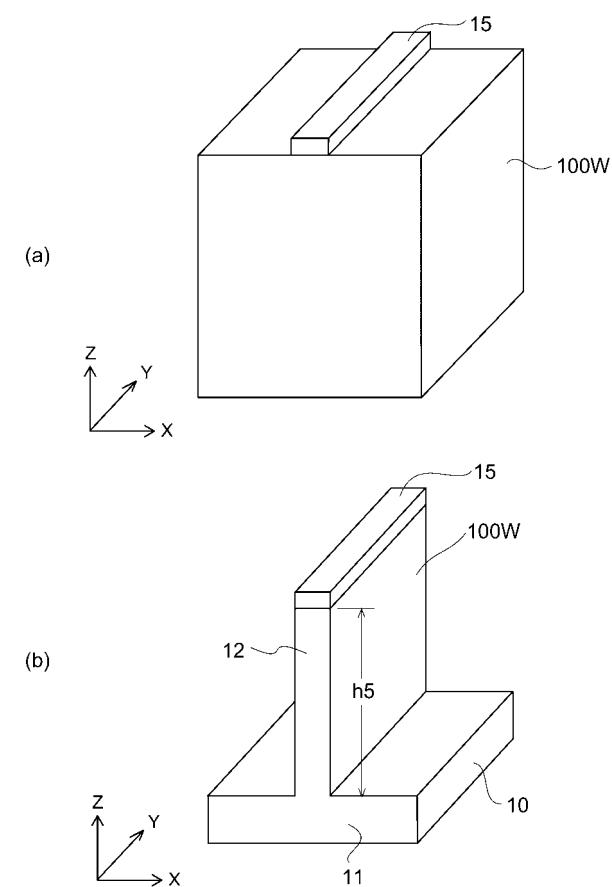

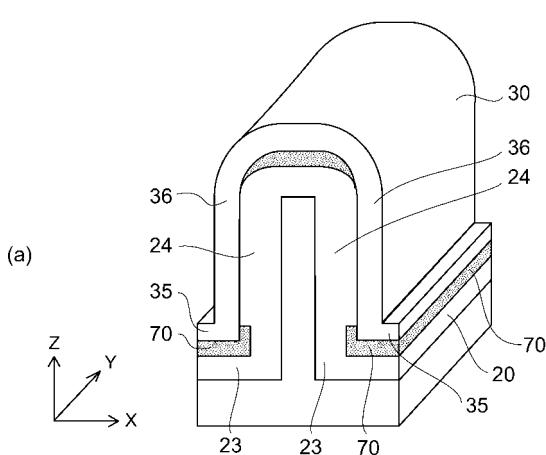

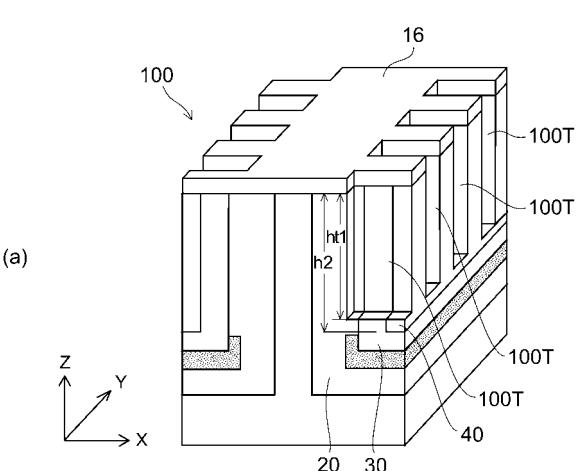

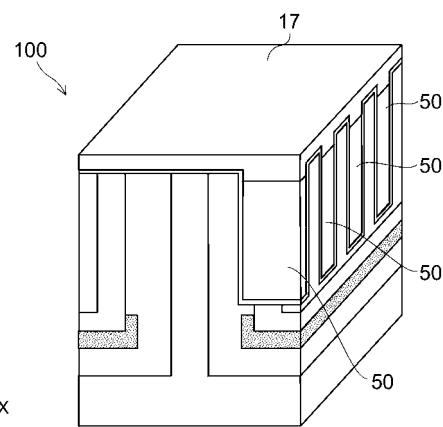

【図1】第1の実施形態に係る半導体装置の構成を例示する模式的斜視図である。

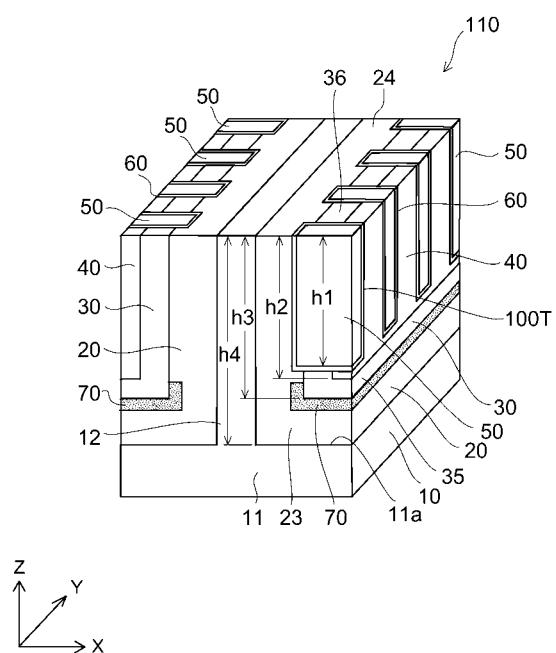

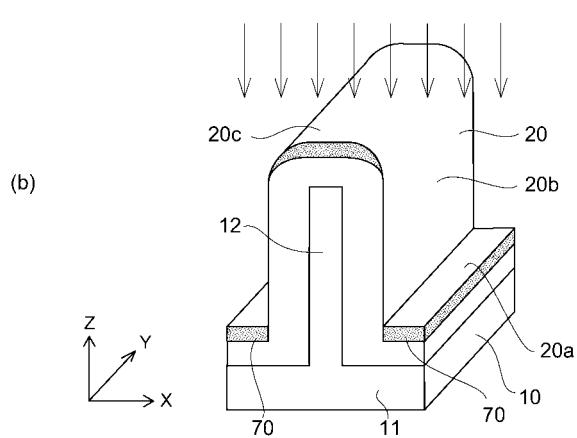

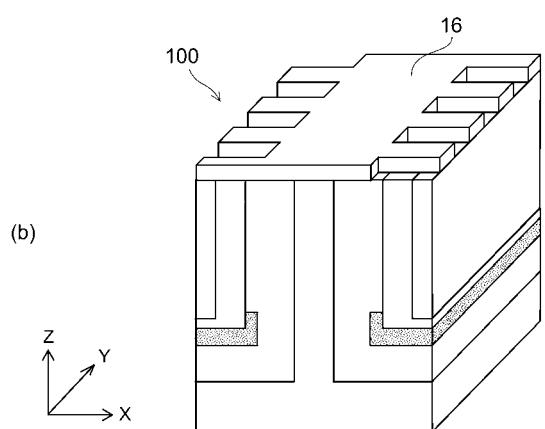

【図2】比較例に係る半導体装置を例示する模式的斜視図である。

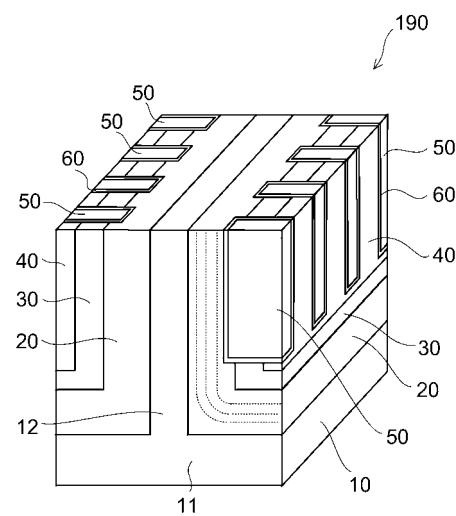

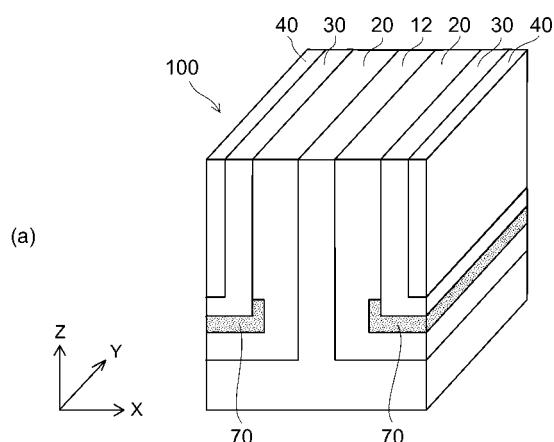

【図3】第1の実施形態に係る半導体装置の電界の状態を例示する模式的斜視図である。

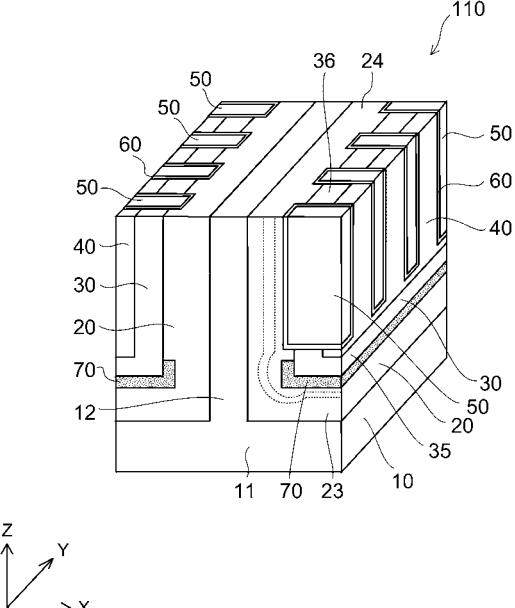

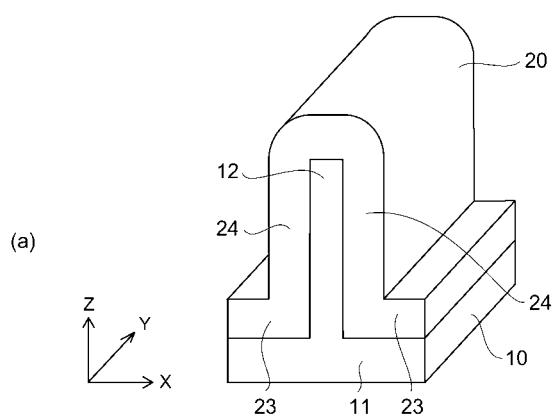

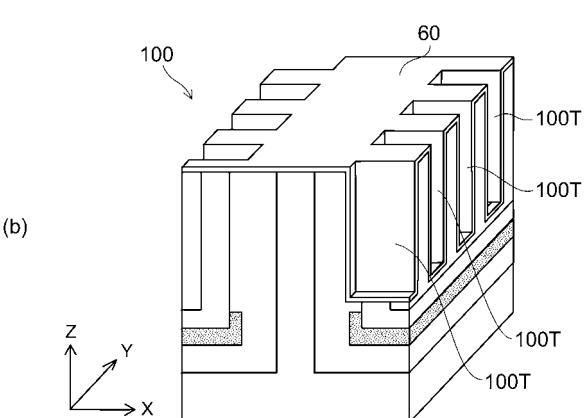

【図4】第1の実施形態に係る半導体装置の製造方法を説明する模式的斜視図である。 20

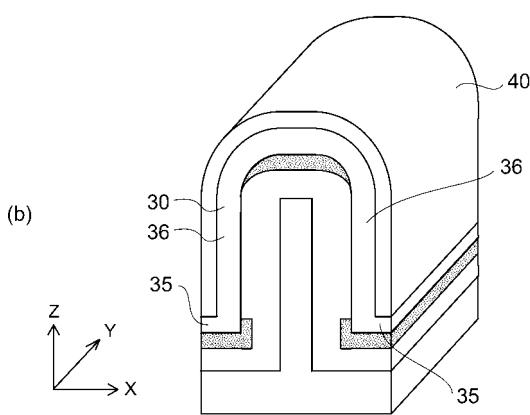

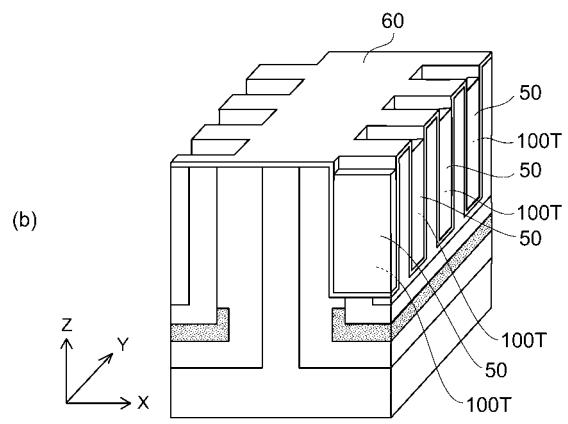

【図5】第1の実施形態に係る半導体装置の製造方法を説明する模式的斜視図である。

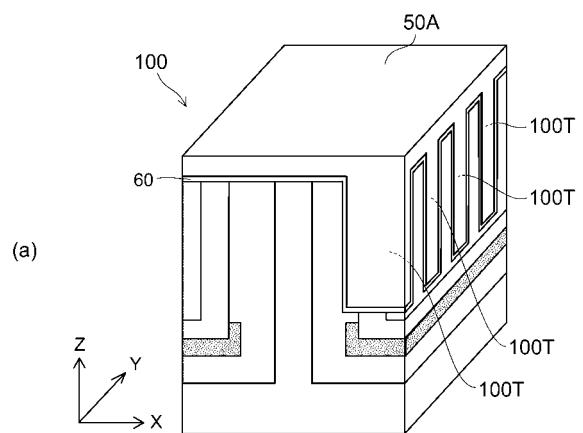

【図6】第1の実施形態に係る半導体装置の製造方法を説明する模式的斜視図である。

【図7】第1の実施形態に係る半導体装置の製造方法を説明する模式的斜視図である。

【図8】第1の実施形態に係る半導体装置の製造方法を説明する模式的斜視図である。

【図9】第1の実施形態に係る半導体装置の製造方法を説明する模式的斜視図である。

【図10】第1の実施形態に係る半導体装置の製造方法を説明する模式的斜視図である。

#### 【発明を実施するための形態】

##### 【0008】

以下、本発明の実施形態を図に基づき説明する。

なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比係数などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比係数が異なって表される場合もある。 30

また、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

##### 【0009】

また、以下の説明では、半導体の一例として、シリコン(Si)を用い、第1導電形をn形、第2導電形をp形とした具体例を挙げる。また、以下の説明において、n<sup>+</sup>、n、n<sup>-</sup>及びp<sup>+</sup>、p、p<sup>-</sup>の表記は、各導電形における不純物濃度の相対的な高低を表す。すなわち、n<sup>+</sup>はnよりもn形の不純物濃度が相対的に高く、n<sup>-</sup>はnよりもn形の不純物濃度が相対的に低いことを示す。また、p<sup>+</sup>はpよりもp形の不純物濃度が相対的に高く、p<sup>-</sup>はpよりもp形の不純物濃度が相対的に低いことを示す。 40

##### 【0010】

#### (第1の実施形態)

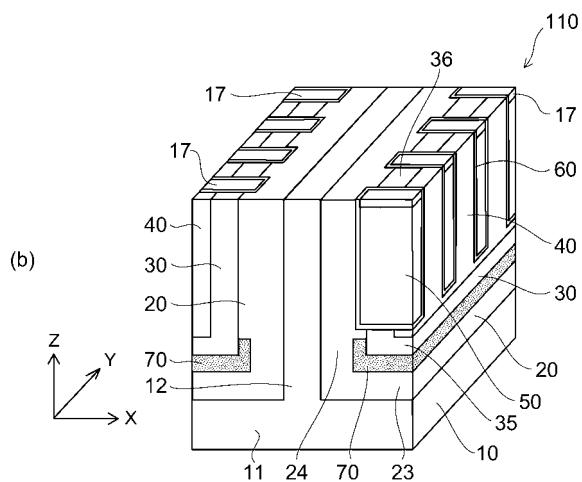

図1は、第1の実施形態に係る半導体装置の構成を例示する模式的斜視図である。

図1に表したように、本実施形態に係る半導体装置110においては、MOSFETのチャネル幅が基板の深さ方向に沿って設けられた、いわゆる3D(three-dimensional)型である。

半導体装置110は、第1半導体領域10、第2半導体領域20、第3半導体領域30、第4半導体領域40、ゲート領域50、ゲート絶縁膜60及び電界緩和領域70を備える。 50

## 【0011】

第1半導体領域10は、第1主面11aを含む第1部分11と、第1主面11aに対して直交する第1方向に延出した第2部分12と、を有する第1導電形の領域である。

なお、本実施形態では、第2部分12が延出する第1方向をZ方向、第1方向と直交する方向のうち一つ（第2方向）をX方向、第1方向及び第2方向と直交する第3方向をY方向とする。また、本実施形態では、説明の便宜上、Z方向に沿って第2部分12が延びる方向を「上」、これと反対方向を「下」とする。

本実施形態において、第1半導体領域10は、例えばシリコンのウェーハに燐（P）がドープされたn<sup>+</sup>ドレイン領域である。

## 【0012】

第2半導体領域20は、第3部分23と、第4部分24と、を有する第1導電形の領域である。

第3部分23は、第1部分11の上において第2部分12のZ方向に沿った長さよりも短く設けられる。第4部分24は、第2部分12と隣接し第3部分23の上面の一部からZ方向に延出して設けられる。

すなわち、第2半導体領域20は、互いに直交する方向に設けられた第3部分23及び第4部分24により、XZ平面における断面視において、第1部分11及び第2部分12に沿った略L字型に設けられる。

## 【0013】

本実施形態において、第2半導体領域20は、例えば第1半導体領域10の表面にエピタキシャル成長によって形成された膜である。第2半導体領域20は、例えばエピタキシャル成長膜に燐（P）がドープされたn<sup>-</sup>ドレイン領域である。第2半導体領域20は、MOSFETにおけるドリフト領域となる。

20

## 【0014】

第3半導体領域30は、第5部分35と、第6部分36と、を有する第2導電形の領域である。

第5部分35は、第3部分23の上において第4部分24のZ方向に沿った長さよりも短く設けられる。第6部分36は、第4部分24と隣接し第5部分35の上面の一部からZ方向に延出して設けられる。

すなわち、第3半導体領域30は、互いに直交する方向に設けられた第5部分35及び第6部分36により、XZ平面における断面視において、第3部分23及び第4部分24に沿った略L字型に設けられる。

30

## 【0015】

第3半導体領域30におけるZ方向に沿った長さh3は、第2半導体領域20におけるZ方向に沿った長さh4よりも短い。

本実施形態において、第3半導体領域30は、例えば第2半導体領域20の表面にエピタキシャル成長によって形成された膜である。第3半導体領域30は、例えばエピタキシャル成長膜にボロン（B）がドープされたp<sup>-</sup>ベース領域である。

## 【0016】

第4半導体領域40は、第5部分35の上において第6部分36と隣接して設けられた第1導電形の領域である。

すなわち、第4半導体領域40は、第3半導体領域30上でZ方向に延在して設けられる。これにより、第4半導体領域40は、XZ平面における断面視において、第3半導体領域30の略L字型の内側に埋め込まれる。

40

## 【0017】

第4半導体領域40におけるZ方向に沿った長さh2は、第3半導体領域30におけるZ方向に沿った長さh3よりも短い。

本実施形態において、第4半導体領域40は、例えば第3半導体領域30上にエピタキシャル成長によって形成された膜である。第4半導体領域40は、例えばエピタキシャル成長膜に燐（P）がドープされたn<sup>+</sup>ソース領域である。

50

## 【0018】

ゲート領域50は、第2半導体領域20、第3半導体領域30及び第4半導体領域40をX方向に貫通するトレンチ100T内に設けられている。

すなわち、第2半導体領域20の第4部分24、第3半導体領域30の第6部分36及び第4半導体領域40は、X方向に沿って隣接している。トレンチ100Tは、この隣接する第4部分24、第6部分36及び第4半導体領域40をX方向に沿って貫通するよう設けられる。ゲート領域50は、トレンチ100T内に、後述のゲート絶縁膜60を介して埋め込まれる。

## 【0019】

また、ゲート領域50は、トレンチ100T内においてZ方向に沿って延びるよう設けられている。ゲート領域50は、Z方向に沿って長さh1で設けられている。長さh1は、例えば第4半導体領域の長さh2よりも短い。ゲート領域50としては、例えば多結晶シリコンが用いられる。

10

## 【0020】

ゲート絶縁膜60は、トレンチ100Tの内壁と、ゲート領域50と、の間に設けられている。ゲート絶縁膜60としては、例えば酸化シリコン膜が用いられる。

## 【0021】

電界緩和領域70は、第2半導体領域20の第3部分23と、第3半導体領域30の第5部分35と、の間に設けられている。電界緩和領域70は、第3半導体領域30の不純物濃度よりも低い不純物濃度を有する第2導電形の領域である。電界緩和領域70は、例えば第3部分23にボロン(B)がドープされたp<sup>-</sup>領域である。

20

## 【0022】

電界緩和領域70は、第3部分23と、第5部分35と、の間から、第4部分24の一部に至るまで設けられている。すなわち、電界緩和領域70は、XZ平面の断面視において、第3半導体領域30の略L字型の隅部の外側の周辺に設けられている。このような電界緩和領域70が設けられると、p<sup>-</sup>形の第3半導体領域30とn<sup>-</sup>形の第2半導体領域20との間の急峻な不純物濃度変化が緩和される。すなわち、本実施形態に係る半導体装置110では、電界緩和領域70がリサーフ領域として機能し、第3半導体領域30の略L字型の隅部の周辺における電界集中を緩和する。

30

## 【0023】

本実施形態に係る半導体装置110では、ゲート領域50にオン電圧を印加することで、ゲート絶縁膜60に隣接する第3半導体領域30であるp<sup>-</sup>ベース領域にチャネルが形成される。半導体装置110では、X方向に沿った第3半導体領域30の長さがチャネル長に対応する。また、半導体装置110では、第3半導体領域30におけるZ方向に沿った長さのうちゲート領域50と対応した深さh1がチャネル幅に対応する。第3半導体領域30におけるチャネル長方向の全体にチャネルが形成されると、ソース領域である第4半導体領域40からドリフト領域である第2半導体領域20を介してドレイン領域である第1半導体領域10へと電流が流れる。

## 【0024】

一方、ゲート領域50にオン電圧が印加されない状態では、第3半導体領域30であるp<sup>-</sup>ベース領域にチャネルが形成されず、電流は流れない。本実施形態に係る半導体装置110では、第3半導体領域30と第2半導体領域20との間に電界緩和領域70が設けられているため、空乏層はチャネル領域から電界緩和領域70にまで達する。これにより、第3半導体領域30の隅部の周辺における電界集中を緩和して、耐圧を高めることができる。

40

## 【0025】

図2は、比較例に係る半導体装置を例示する模式的斜視図である。

図2に表したように、比較例に係る半導体装置190は、図1に表した半導体装置110のような電界緩和領域70が設けられていない。

図2に表した破線は、MOSFETがオフの状態での第3半導体領域30と第2半導体

50

領域 2 0 との間に印加される電界を例示している。この半導体装置 1 9 0 では、第 3 半導体領域 3 0 の隅部周辺に電界が集中している。

【 0 0 2 6 】

半導体装置 1 9 0 においては、第 1 半導体領域 1 0 の第 1 部分 1 1 と第 2 部分 1 2 とで第 2 半導体領域 2 0 の 2 面 ( X Y 平面及び Y Z 平面) が囲まれている。そして、この第 2 半導体領域 2 0 の内側に第 3 半導体領域 3 0 が設けられている。このため、第 3 半導体領域 3 0 は、直交する 2 面 ( X Y 平面及び Y Z 平面) で第 2 半導体領域 2 0 と接する。よって、第 3 半導体領域 3 0 の上記 2 面で挟まれる隅部には、電界が集中しやすくなる。

【 0 0 2 7 】

第 3 半導体領域 3 0 の第 5 部分 3 5 から第 1 半導体領域 1 0 の第 1 部分 1 1 に向かう領域は、いわゆる 3 D - M O S F E T の終端領域と等価であると考えられる。このため、第 3 半導体領域 3 0 の上記 2 面で挟まれる隅部の周辺に電界が集中すると、終端領域での耐圧の低下と同等であり、半導体装置 1 9 0 の全体の耐圧の低下につながる。

10

【 0 0 2 8 】

図 3 は、本実施形態に係る半導体装置の電界の状態を例示する模式的斜視図である。

図 3 に表した破線は、本実施形態に係る半導体装置 1 1 0 の M O S F E T がオフの状態での第 3 半導体領域 3 0 と第 2 半導体領域 2 0 との間に印加される電界を例示している。

本実施形態に係る半導体装置 1 1 0 では、先に説明したように電界緩和領域 7 0 を備えることから、第 3 半導体領域 3 0 と第 2 半導体領域 2 0 との間のうち、特に第 3 半導体領域 3 0 の隅部の周辺での電界の集中が緩和される。これにより、図 2 に例示した比較例に係る半導体装置 1 9 0 に比べ、終端領域での耐圧を向上でき、半導体装置 1 1 0 の全体での耐圧を向上できるようになる。

20

【 0 0 2 9 】

図 1 に例示した半導体装置 1 1 0 では、第 1 半導体領域 1 0 の第 2 部分 1 2 が Y 方向に沿って延びるよう設けられている。また、半導体装置 1 1 0 では、第 3 半導体領域 3 0 及び第 4 半導体領域 4 0 が、 Y 方向に沿って延在している。さらに、半導体装置 1 1 0 では、複数のゲート領域 5 0 及びゲート絶縁膜 6 0 が、 Y 方向に沿って配置されている。

これにより、 Y 方向に延びる第 2 部分 1 2 に対応して複数の M O S F E T 構造を備えることになる。複数の M O S F E T 構造における各ゲート領域は、例えば並列に接続される。また、複数の M O S F E T 構造における各ソース領域は、例えば並列に接続される。

30

【 0 0 3 0 】

また、図 1 に例示した半導体装置 1 1 0 では、第 2 部分 1 2 を中心として、 X 方向に沿った両側に、第 2 半導体領域 2 0 、第 3 半導体領域 3 0 、第 4 半導体領域、複数のゲート領域 5 0 及び複数のゲート絶縁膜 6 0 が設けられている。

半導体装置 1 1 0 では、複数の第 2 部分 1 2 が X 方向に沿って配置され、各第 2 部分 1 2 を中心として X 方向に沿った両側に、複数の M O S F E T 構造を備えるようにしてもよい。

【 0 0 3 1 】

このような本実施形態に係る半導体装置 1 1 0 では、第 3 半導体領域 3 0 の隅部の周辺での電界の集中を緩和することによって、耐圧の向上を図ることができるようになる。

40

【 0 0 3 2 】

( 第 2 の実施形態 )

次に、第 2 の実施形態を説明する。第 2 の実施形態は、第 1 の実施形態に係る半導体装置の製造方法である。

図 4 ~ 図 1 0 は、第 1 の実施形態に係る半導体装置の製造方法を説明する模式的斜視図である。

【 0 0 3 3 】

先ず、図 4 ( a ) に表したように、例えばシリコンのウェーハ 1 0 W を用意する。ウェーハ 1 0 W には、第 1 半導体領域 1 0 であるドレイン領域となるように、例えば磷 ( P ) がドープされ、  $n^+$  になっている。ウェーハ 1 0 W の不純物濃度は、例えば  $4.5 \times 10$

50

$10^9 \text{ cm}^{-3}$  である。

【0034】

次に、ウェーハ 10W の上に、例えばシリコン酸化膜 15 を形成し、フォトリソグラフィ及びエッティングによってパターン形成する。シリコン酸化膜 15 は、パターン形成によって、後述する第 2 部分 12 を形成する部分のみが残されている。

【0035】

次に、図 4 (b) に表したように、パターンング形成されたシリコン酸化膜 15 をマスクとして、ウェーハ 10W をエッティングする。エッティングは、例えば RIE (Reactive Ion Etching) を用いる。ウェーハ 10W のエッティングによって残った部分が第 1 部分 11 となる。また、シリコン酸化膜 15 によってマスクされエッティングされなかった部分は第 2 部分 12 となる。これにより、第 1 部分 11 及び第 2 部分 12 を有する第 1 半導体領域 10 が形成される。

ここで、ウェーハ 10W のエッティング深さは、例えば 15 マイクロメートル ( $\mu\text{m}$ ) ~ 20  $\mu\text{m}$  である。これにより、第 2 部分 12 の Z 方向に沿った長さ  $h_5$  は、15  $\mu\text{m}$  ~ 20  $\mu\text{m}$  となる。

ウェーハ 10W をエッティングした後は、シリコン酸化膜 15 を除去する。

【0036】

次に、図 5 (a) に表したように、第 1 半導体領域 10 の表面に、第 2 半導体領域 20 を成膜する。第 2 半導体領域 20 は、第 1 半導体領域 10 の表面に例えばエピタキシャル成長によって形成される。第 2 半導体領域 20 は、エピタキシャル成長によって約 2  $\mu\text{m}$  の厚さで形成される。第 2 半導体領域 20 は、第 1 半導体領域 10 の第 1 部分 11 及び第 2 部分 12 の表面を覆うように形成される。これにより、第 1 部分 11 の上に第 3 部分 23 が形成され、第 2 部分 12 に隣接した第 4 部分 24 が形成される。

エピタキシャル成長後、第 2 半導体領域 20 には例えば磷 (P) がドーピングされる。これにより、第 2 半導体領域 20 は、n<sup>-</sup> のドレイン領域となる。第 2 半導体領域 20 の不純物濃度は、例えば  $2 \times 10^{16} \text{ cm}^{-3}$  である。

【0037】

次に、図 5 (b) に表したように、第 2 半導体領域 20 の上からイオン注入を行う。イオン注入は、不純物として例えばボロン (B) のイオンを注入し、p<sup>-</sup> とする。ここで、ボロン (B) のイオンは、第 2 半導体領域 20 の上面 20c 及び第 1 半導体領域 10 の第 1 主面 10a と対向する第 2 主面 20a に注入される。このうち、第 2 主面 20a に注入されたボロン (B) による p<sup>-</sup> 領域が、電界緩和領域 70 となる。

【0038】

p<sup>-</sup> 領域 (電界緩和領域 70) の不純物濃度は、後に形成する第 3 半導体領域 30 の不純物濃度よりも低い。ここで行うイオン注入は、例えば、ボロンをドーズ量  $1 \times 10^{14} \text{ cm}^{-2}$  で注入する。これにより、p<sup>-</sup> 領域 (電界緩和領域 70) の不純物濃度は、 $1 \times 10^{18} \text{ cm}^{-3}$  未満となる。

【0039】

また、イオン注入におけるイオンの入射角度は、第 2 半導体領域 20 における第 2 主面 20a にはイオンが注入され、第 2 半導体領域における、第 2 部分 12 の側面と対向する第 3 主面 20b にはイオンが注入されない角度である。イオンの入射角度は、例えば、第 2 主面 20a と垂直な方向に対して約 3 度である。これにより、第 2 半導体領域 20 の第 3 主面 20b にイオンが衝突しても弾かれて注入されず、第 2 主面 20a には注入される。なお、上面 20c にも不純物が注入されるが、後の工程で研削によって除去される。

第 2 半導体領域 20 に不純物を注入した後は、熱処理によって不純物を拡散させる。

【0040】

次に、図 6 (a) に表したように、第 2 半導体領域 20 の表面に、第 3 半導体領域 30 を成膜する。第 3 半導体領域 30 は、第 2 半導体領域 20 の表面に例えばエピタキシャル成長によって形成される。第 3 半導体領域 30 は、エピタキシャル成長によって約 0.35  $\mu\text{m}$  の厚さで形成される。これにより、第 3 部分 23 の上に第 5 部分 35 が形成され、

10

20

30

40

50

第4部分24に隣接した第6部分36が形成される。

エピタキシャル成長後、第3半導体領域30には例えばボロン(B)がドープされ、p-のベース領域となる。第3半導体領域30の不純物濃度は、例えば $1 \times 10^{18} \text{ cm}^{-3}$ である。すなわち、先に形成した電界緩和領域70の不純物濃度よりも高い。

#### 【0041】

次に、図6(b)に表したように、第3半導体領域30の表面に、第4半導体領域40を成膜する。第4半導体領域40は、第3半導体領域30の表面に例えばエピタキシャル成長によって形成される。第4半導体領域40は、エピタキシャル成長によって約0.5 $\mu\text{m}$ の厚さで形成される。これにより、第4半導体領域40は、第5部分35の上において第6部分36と隣接して設けられる。

エピタキシャル成長後、第4半導体領域40には例えば燐(P)がドープされ、n<sup>+</sup>のソース領域となる。第4半導体領域40の不純物濃度は、例えば $3 \times 10^{19} \text{ cm}^{-3}$ である。

#### 【0042】

次に、図7(a)に表したように、第4半導体領域40、第3半導体領域30及び第2半導体領域20を、第1半導体領域10の第2部分12が露出するまで除去する。この除去方法には、例えばCMP(Chemical Mechanical Polishing)が用いられる。CMPによって、第2部分12の露出面が平坦化された構造体100が構成される。

#### 【0043】

次に、図7(b)に表したように、構造体100の上にマスク材16を形成する。マスク材16には、例えば酸化シリコンが用いられる。マスク材16は、例えばCVD(Chemical Vapor Deposition)によって形成される。マスク材16を形成した後は、フォトリソグラフィ及びエッチングによってマスク材16のパターニング形成を行う。例えば、マスク材16の上にレジスト(図示せず)を塗布し、フォトリソグラフィ及びエッチングによってパターニング形成する。その後、レジストをマスクとして、例えばRIEによりマスク材16をエッチングし、パターニング形成する。このパターニング形成では、ゲート領域50及びゲート絶縁膜60を形成する部分のみ、マスク材16に開口が形成される。マスク材16のパターニング形成後は、レジストを除去する。

#### 【0044】

次に、図8(a)に表したように、パターニング形成したマスク材16をマスクとして構造体100をエッチングする。このエッチングによって、マスク材16の開口部分の構造体100が彫り込まれ、トレンチ100Tとなる。トレンチ100Tは、X方向に沿って、第2半導体領域20、第3半導体領域30及び第4半導体領域40を貫通するよう設けられる。また、トレンチ100Tは、Y方向に沿って約1 $\mu\text{m}$ の幅、Z方向に沿って、約15 $\mu\text{m}$ ~20 $\mu\text{m}$ の長さh<sub>t1</sub>、で形成される。本実施形態では、トレンチ100TのZ方向に沿った長さh<sub>t1</sub>は、第4半導体領域40のZ方向に沿った長さh<sub>2</sub>よりも短い。また、必要に応じて、複数のトレンチ100Tが、Y方向及びX方向に沿って設けられる。

トレンチ100Tを形成した後は、マスク材16を除去する。

#### 【0045】

次に、図8(b)に表したように、トレンチ100Tが形成された構造体100の上にゲート絶縁膜60を成膜する。ゲート絶縁膜60は、例えばシリコン酸化膜である。シリコン酸化膜は、例えば熱酸化によって形成される。ゲート絶縁膜60は、例えば100ナノメートル(nm)の厚さで形成される。

#### 【0046】

次に、図9(a)に表したように、ゲート絶縁膜60の上に、ゲート材料50Aを形成する。ゲート材料50Aは、例えば多結晶シリコンである。ゲート材料50Aは、構造体100の上面及びトレンチ100T内に埋め込まれる。

#### 【0047】

次に、ゲート材料50Aをエッチバックする。これにより、図9(b)に表したように

10

20

30

40

50

、トレンチ 100T の中にゲート絶縁膜 60 を介して設けられたゲート領域 50 が形成される。ゲート材料 50A のエッチバックによって形成されたゲート領域 50 の上面は、トレンチ 100T の開口よりも Z 方向に沿ってわずかに低くなっている。

【0048】

次に、図 10 (a) に表したように、構造体 100 の上に層間絶縁膜 17 を形成する。層間絶縁膜 17 は、構造体 100 の上面の全面に形成される。その後、層間絶縁膜 17 を例えば RIE によってエッチングする。このエッチングは、図 10 (b) に表したように、第 2 部分 12、第 2 半導体領域 20、第 3 半導体領域 30 及び第 4 半導体領域 40 が露出するまで行う。これにより、ゲート領域 50 の上に層間絶縁膜 17 が残る状態になる。

【0049】

このあとは、ゲート領域 50、第 1 半導体領域 10 であるドレイン領域及び第 4 半導体領域 40 であるソース領域に導通する図示しない電極（ゲート電極、ドレイン電極及びソース電極）を形成する。電極には、例えばアルミニウム (Al) が用いられる。電極は、フォトリソグラフィ及びエッチングによって所定のパターニング形状にされる。その後、例えばポリイミド等の保護膜（図示せず）を形成する。これにより半導体装置 110 が完成する。

【0050】

このような第 2 の実施形態によれば、第 3 半導体領域 30 と第 2 半導体領域 20 との間に電界緩和領域 70 を備え、電界集中を緩和して耐圧を向上した半導体装置 110 を製造することが可能となる。

10

20

20

【0051】

なお、前述の各実施形態においては、第 1 導電形を n 形、第 2 導電形を p 形として説明したが、本発明は第 1 導電形を p 形、第 2 導電形を n 形としても実施可能である。さらにもう、前述の各実施形態においては、半導体としてシリコン (Si) を用いた MOSFET を説明したが、半導体としては、例えばシリコンカーバイト (SiC) 若しくは窒化ガリウム (GaN) 等の化合物半導体、またはダイアモンド等のワイドバンドギャップ半導体を用いることもできる。

【0052】

さらにまた、前述の各実施の形態および各変形例においては、MOSFET である例を示したが、本発明はこれに限定されず、半導体装置は、例えば、MOSFET と SBD (Schottky Barrier Diode : ショットキーバリアダイオード) との混載素子、または IGBT (Insulated Gate Bipolar Transistor) などの素子でもよい。

30

【0053】

以上説明したように、本実施形態によれば、半導体装置の耐圧を向上することができるようになる。

【0054】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

40

【符号の説明】

【0055】

10 ... 第 1 半導体領域、11 ... 第 1 部分、11a ... 第 1 主面、12 ... 第 2 部分、20 ... 第 2 半導体領域、30 ... 第 3 半導体領域、40 ... 第 4 半導体領域、50 ... ゲート領域、60 ... ゲート絶縁膜、70 ... 電界緩和領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

## フロントページの続き

| (51) Int.Cl. | F I          | テーマコード(参考) |

|--------------|--------------|------------|

|              | H 01 L 29/78 | 652G       |

|              | H 01 L 29/78 | 652F       |

|              | H 01 L 29/78 | 658E       |

|              | H 01 L 29/78 | 658B       |

|              | H 01 L 29/78 | 301W       |

F ターム(参考) 5F140 AA25 AA30 AB04 AB06 AC21 AC23 AC24 BA01 BA02 BA04

BA06 BB05 BB13 BC06 BC12 BC15 BE07 BF01 BF04 BF43

BF47 BF56 BG37 BH12 BH13 BH17 BH30 BH49 BK09 BK17

CC10 CE07