**【特許請求の範囲】****【請求項 1】**

NチャネルトランジスタとPチャネルトランジスタとを直列に接続した回路が並列接続された出力バッファと、前記出力バッファから出力される信号波形の調整を行う波形調整手段と、を有する半導体回路において、

前記波形調整手段で調整された出力波形値に対して所定のオフセット値を付加するオフセット付加手段が設けられていることを特徴とする半導体回路。

**【請求項 2】**

前記波形調整手段には、前記出力バッファにおけるトランジスタの並列数を変化させることによって出力インピーダンスを調整するインピーダンス調整部が設けられ、

前記オフセット調整手段には、前記オフセット値が予め設定されるオフセット設定部、および、前記オフセット設定部に設定された前記オフセット値と前記インピーダンス調整部が調整した前記出力バッファにおけるトランジスタの並列数とを加算する加算部が設けられ、そして、

前記オフセット調整手段では、前記加算部の算出結果に基づいて前記出力バッファの並列数が変更される

ことを特徴とする請求項 1 に記載の半導体回路。

**【請求項 3】**

前記波形調整手段および前記オフセット付加手段が、前記出力バッファのNチャネルトランジスタおよびPチャネルトランジスタにそれぞれ対応して設けられていることを特徴とする請求項 1 または 2 のうちいずれか一項に記載の半導体回路。

**【請求項 4】**

前記オフセット設定部が、レジスタで構成されていることを特徴とする請求項 1 乃至 3 のうちいずれか一項に記載の半導体回路。

**【請求項 5】**

前記オフセット設定部が、外部入力端子で構成されていることを特徴とする請求項 1 乃至 3 のうちいずれか一項に記載の半導体回路。

**【請求項 6】**

前記オフセット設定部が、書き換え可能な不揮発性メモリで構成されていることを特徴とする請求項 1 乃至 3 のうちいずれか一項に記載の半導体回路。

**【請求項 7】**

前記出力バッファに接続される負荷の数が入力される負荷数入力手段と、前記出力バッファから前記負荷までの配線長が入力される配線長入力手段と、前記負荷数入力手段から入力された前記出力バッファに接続される負荷の数および前記配線長入力手段から入力された前記出力バッファから前記負荷までの配線長に基づいて前記オフセット値を算出するオフセット算出部と、が設けられていることを特徴とする請求項 1 乃至 6 のうちいずれか一項に記載の半導体回路。

**【請求項 8】**

NチャネルトランジスタとPチャネルトランジスタとを直列に接続した回路が並列接続された出力バッファから出力される信号波形の調整を行う半導体回路の出力バッファ波形調整方法において、

前記出力バッファに接続される負荷の数および前記出力バッファから前記負荷までの配線長に基づいてオフセット値を算出し、そのオフセット値を調整した波形値に加算することを特徴とする半導体回路の出力バッファ波形調整方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、出力バッファの出力波形を調整する半導体回路と、半導体回路の出力バッファ波形調整方法に関する。

**【背景技術】**

10

20

30

40

50

## 【0002】

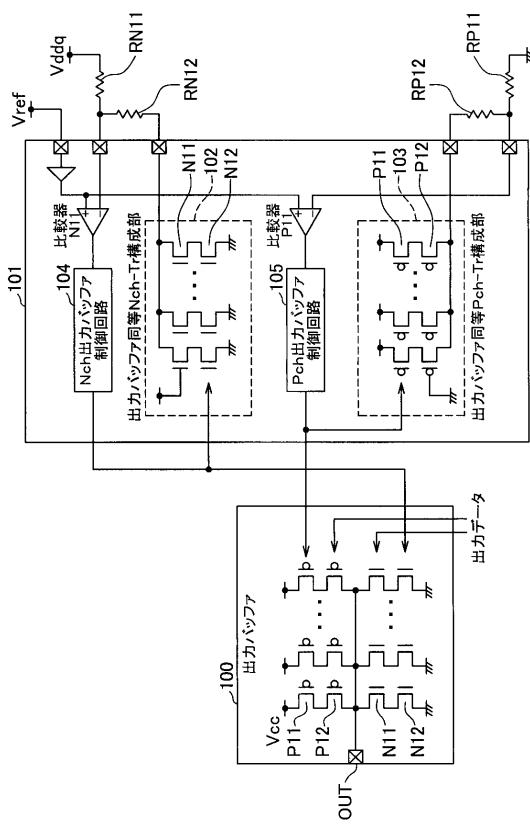

半導体回路において高速インターフェースの出力バッファの出力波形の調整としてインピーダンス調整を自律的に行うことができる回路が組み込まれていることがある。図7のような回路が従来のもので、インピーダンス調整回路からの結果により、バッファの駆動能力を変更する（例えば特許文献1参照）。

## 【0003】

図7の回路は、出力バッファ100と出力インピーダンス調整回路101と、から構成されている。

## 【0004】

出力バッファ100は、Vcc、第1PチャネルトランジスタP11、第2PチャネルトランジスタP12、第1NチャネルトランジスタN11、第2NチャネルトランジスタN12、グランドの順に直列接続されたバッファ回路が複数組設けられ、各バッファ回路の第2PチャネルトランジスタP12と第1NチャネルトランジスタN11の間を互いに並列接続するとともに出力端子OUTとしている。10

## 【0005】

また、出力バッファ100の各第2PチャネルトランジスタP12と各第1NチャネルトランジスタN11のゲートには出力データが、第1PチャネルトランジスタP11のゲートには後述する出力インピーダンス調整回路101のPch出力バッファ制御回路105が出力するコントロール信号が、第2NチャネルトランジスタN12のゲートには後述する出力インピーダンス調整回路101のNch出力バッファ制御回路104が出力するコントロール信号が、それぞれ接続されている。20

## 【0006】

CMOS半導体のドライブ能力はトランジスタのチャネル幅Wによって決まる。Wのサイズが倍になるとドライブ能力も倍となる。バッファ回路1組を1とすると4組のバッファ回路ではWのサイズは4倍となり、4倍のドライブ能力となる。

## 【0007】

出力インピーダンス調整回路101は、出力バッファ同等Nch-Tr構成部102と、出力バッファ同等Pch-Tr構成部103と、Nch出力バッファ制御回路104と、Pch出力バッファ制御回路105と、比較器N10と、比較器P10と、を備えている。30

## 【0008】

出力バッファ同等Nch-Tr構成部102は、出力バッファ100のうちNチャネルトランジスタ部分の複製であって、抵抗RN12、第1NチャネルトランジスタN11、第2NチャネルトランジスタN12、グランドの順に直列に接続された回路が出力バッファ100と同数並列に接続されている。また、各第1NチャネルトランジスタN11のゲートにはVccが入力され、第2NチャネルトランジスタN12のゲートには後述するNch出力バッファ制御回路104のコントロール信号が入力されている。出力バッファ同等Nch-Tr構成部102は、出力バッファ100と同じ構成をとることで、外部出力に影響無く、出力バッファ100のインピーダンス状態をフィードバックすることが出来る。40

## 【0009】

出力バッファ同等Pch-Tr構成部103は、出力バッファ100のうちPチャネルトランジスタ部分の複製であって、Vcc、第1PチャネルトランジスタP11、第2PチャネルトランジスタP12、抵抗RP12の順に直列に接続された回路が出力バッファ100と同数並列に接続されている。また、第1PチャネルトランジスタP11のゲートには後述するPch出力バッファ制御回路105のコントロール信号が入力され、各第2PチャネルトランジスタP12のゲートにはグランドが接続されている。出力バッファ同等Nch-Tr構成部102は、出力バッファ100と同じ構成をとることで、外部出力に影響無く、出力バッファ100のインピーダンス状態をフィードバックすることが出来る。50

## 【0010】

Nch出力バッファ制御回路104は、電圧レベルを比較する比較器N10からの電圧差値を受け取る。電圧差に合わせてONする出力バッファ100および出力バッファ同等Nch-Tr構成部102内のNチャネルトランジスタの並列数を調整するために各第2Nチャネルトランジスタそれぞれに対してコントロール信号が出力されている。つまり、コントロール信号はバッファ回路の並列数分出力される。

## 【0011】

Pch出力バッファ制御回路105は、電圧レベルを比較する比較器P10からの電圧差値を受け取る。電圧差に合わせてONする出力バッファ100および出力バッファ同等Pch-Tr構成部103内のPチャネルトランジスタの並列数を調整するために各第1Pチャネルトランジスタそれぞれに対してコントロール信号が出力されている。つまり、コントロール信号はバッファ回路の並列数分出力される。10

## 【0012】

比較器N10は、リファレンス電圧Vrefと、Vddqに対して抵抗RN11を挟んだ電圧が入力され、比較した結果がNch出力バッファ制御回路104に出力される。

## 【0013】

比較器P10は、リファレンス電圧Vrefと、グランドに対して抵抗RP11を挟んだ電圧が入力され、比較した結果がPch出力バッファ制御回路105に出力される。

## 【0014】

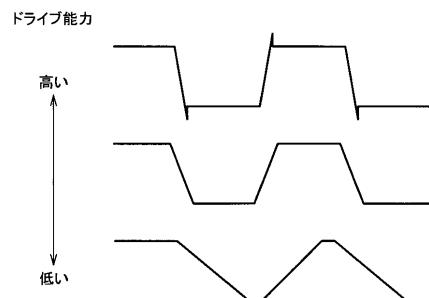

上述した構成の出力インピーダンス調整回路101は、出力バッファ100の駆動能力をチップのプロセス変動、電圧、温度などの周辺環境の変化に合わせて変更する。出力インピーダンスがマッチしていない場合、例えば図8のように、駆動能力が高すぎると波形の傾きは急になるがオーバーシュートやアンダーシュートが発生しやすくなり波形品質が悪くなる。反対に駆動能力が低すぎると波形の傾きは緩やかになり波形振幅が下がるなどに影響することになる。20

## 【0015】

出力インピーダンス調整回路101の動作を詳細に説明すると、Nch出力バッファ制御回路104は、電圧レベルを比較する比較器からの電圧差値を受け取り、電圧差に合わせてONするバッファ回路の数を調整する。比較器Nへの入力はVddq/2がリファレンス電圧Vrefして入力される。比較器Nへのもう片側の入力はVddqに対して抵抗RN11を挟んだ入力となり、これは抵抗RN12を経由し出力バッファ同等Nch-Tr構成部102に送られ、出力バッファ100のインピーダンスが抵抗RN11-RN12と同等となるまで、つまり比較した電位差が無くなるまで段数調整が繰り返される。Pチャネル側も同様に調整される。30

## 【0016】

このような構成であれば出力バッファ100のトランジスタに対して、プロセスによるスレッショルド電圧や飽和電流などの変動によるインピーダンスの違い、外部の温度による電圧の変動、レギュレータやAC電源の電圧の変動をカバーすることが可能となる。

## 【特許文献1】特許第3885773号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0017】

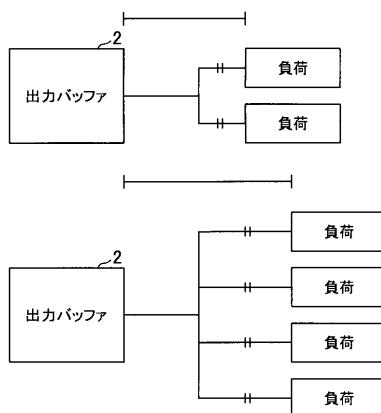

例えば図9に示すように一度に出力バッファ100がドライブする負荷数の違いによってプリント配線基板上での配線抵抗は異なり、負荷数が増えるに従い配線長は長くなる。半導体回路の設計段階では配線長に関する制限を設けた上で許容配線長を決めているが、プリント配線基板の設計段階では規定を守ることが困難になることがある。また、配線容量も分岐配線により大幅に増え、図7に示した出力インピーダンス調整回路101では、実際の配線に合った出力インピーダンスを調整することが困難にならざるを得ない。

## 【0018】

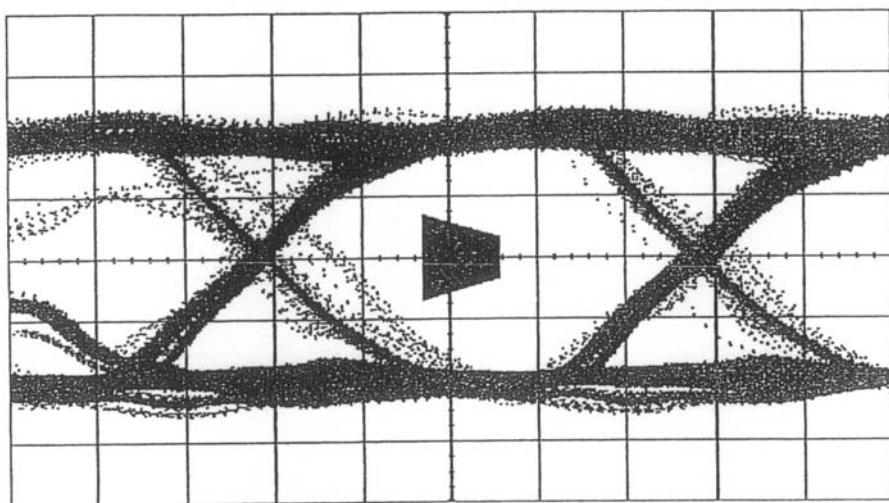

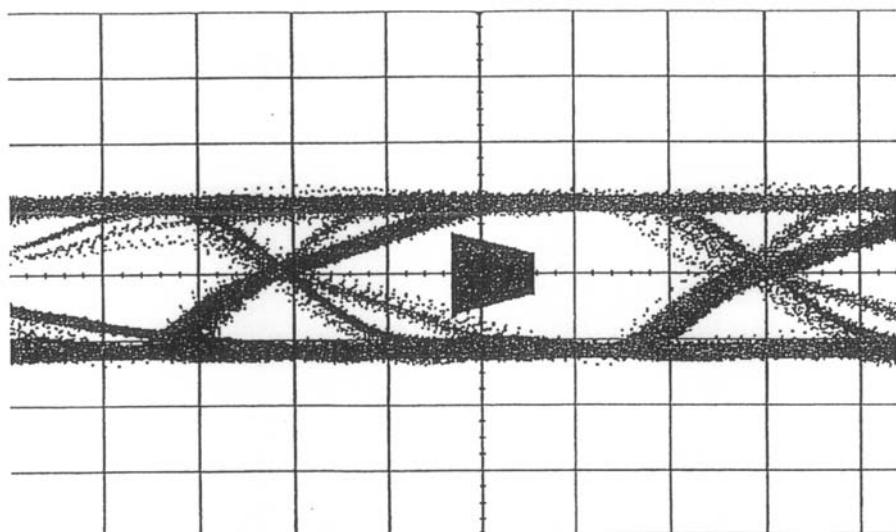

図10は配線長が守れているときのアイダイアグラムで、図11は配線長が守れていな40

いとき、また最短配線長は守れているが負荷数の増大により大幅に容量がついてしまったときのアイダイアグラムである。図11の場合も出力インピーダンス調整回路101は動作しているが波形の品質が低下しドライブ能力が不足していることが分かる。

#### 【0019】

これは、出力インピーダンス調整回路101に接続される抵抗RN1, RN2, RP1, RP2の抵抗値は固定のため、プリント配線基板での配線状態による違いを、出力インピーダンス調整回路101ではカバーしきれないとある。

#### 【0020】

また、このような出力バッファの波形の品質に関する問題は、出力バッファ100のスルーレートを調整する際にも発生し、接続される負荷数や配線長によってスルーレートが調整回路の調整幅ではカバーしきれなくなってしまうことがあった。

10

#### 【0021】

このように、半導体回路設計時の想定と実際のプリント配線基板の配線状態との差が大きくなると、半導体回路内の調整回路ではカバーできないという問題が発生してしまい、そのためにプリント配線基板の設計を再度行うといった対処が必要になり開発期間が長期化し開発コストが上昇してしまう。

#### 【0022】

本発明はかかる問題を解決することを目的としている。

#### 【0023】

すなわち、本発明は、調整回路を変更することなく出力バッファの波形の調整幅を拡大することができる半導体回路および、調整回路を変更することなく出力バッファの波形の調整幅を拡大することができる半導体回路の出力バッファ波形調整方法を提供することを目的としている。

20

#### 【課題を解決するための手段】

#### 【0024】

請求項1に記載された発明は、NチャネルトランジスタとPチャネルトランジスタとを直列に接続した回路が並列接続された出力バッファと、前記出力バッファから出力される信号波形の調整を行う波形調整手段と、を有する半導体回路において、前記波形調整手段で調整された出力波形値に対して所定のオフセット値を付加するオフセット付加手段が設けられていることを特徴とする半導体回路である。

30

#### 【0025】

請求項2に記載された発明は、請求項1に記載された発明において、前記波形調整手段には、前記出力バッファにおけるトランジスタの並列数を変化させることによって出力インピーダンスを調整するインピーダンス調整部が設けられ、前記オフセット調整手段には、前記オフセット値が予め設定されるオフセット設定部、および、前記オフセット設定部に設定された前記オフセット値と前記インピーダンス調整部が調整した前記出力バッファにおけるトランジスタの並列数とを加算する加算部が設けられ、そして、前記オフセット調整手段では、前記加算部の算出結果に基づいて前記出力バッファの並列数が変更されることを特徴とする。

30

#### 【0026】

請求項3に記載された発明は、請求項1または2のうち一項に記載された発明において、前記波形調整手段および前記オフセット付加手段が、前記出力バッファのNチャネルトランジスタおよびPチャネルトランジスタにそれぞれ対応して設けられていることを特徴とする。

40

#### 【0027】

請求項4に記載された発明は、請求項1乃至3のうち一項に記載された発明において、オフセット設定部が、レジスタで構成されていることを特徴とする。

#### 【0028】

請求項5に記載された発明は、請求項1乃至3のうち一項に記載された発明において、オフセット設定部が、外部入力端子で構成されていることを特徴とする。

50

**【 0 0 2 9 】**

請求項 6 に記載された発明は、請求項 1 乃至 3 のうち一項に記載された発明において、オフセット設定部が、書き換え可能な不揮発性メモリで構成されていることを特徴とする。

**【 0 0 3 0 】**

請求項 7 に記載された発明は、請求項 1 乃至 6 のうち一項に記載された発明において、前記出力バッファに接続される負荷の数が入力される負荷数入力手段と、前記出力バッファから前記負荷までの配線長が入力される配線長入力手段と、前記負荷数入力手段から入力された前記出力バッファに接続される負荷の数および前記配線長入力手段から入力された前記出力バッファから前記負荷までの配線長に基づいて前記オフセット値を算出するオフセット算出部と、が設けられていることを特徴とする。

10

**【 0 0 3 1 】**

請求項 8 に記載された発明は、N チャネルトランジスタと P チャネルトランジスタとを直列に接続した回路が並列接続された出力バッファから出力される信号波形の調整を行う半導体回路の出力バッファ波形調整方法において、前記出力バッファに接続される負荷の数および前記出力バッファから前記負荷までの配線長に基づいてオフセット値を算出し、そのオフセット値を調整した波形値に加算することを特徴とする半導体回路の出力バッファ波形調整方法。

20

**【 発明の効果 】****【 0 0 3 2 】**

請求項 1 に記載の発明によれば、波形調整手段が調整した出力波形値に対してオフセット付加手段が所定のオフセット値を付加しているので、オフセットを変更するのみで波形調整手段の調整幅以上の調整を行うことができ、調整回路を変更することなく出力バッファの波形の調整幅に余力を持たせて広くすることができる。

**【 0 0 3 3 】**

請求項 2 に記載の発明によれば、波形調整手段に出力バッファにおけるトランジスタの並列数を変化させることで出力インピーダンスを調整するインピーダンス調整部が設けられて、インピーダンス調整部が調整した出力バッファにおけるトランジスタの並列数に対してオフセット設定部に設定されたオフセット値を加算部で加算して、その加算結果に基づいて出力バッファの並列数を変化させているので、例えばプリント配線基板上の配線長が設計値よりも増大した場合でもプリント配線基板の再設計を行わずに出力バッファの駆動能力を変更することができる。

30

**【 0 0 3 4 】**

請求項 3 に記載の発明によれば、波形調整手段およびオフセット付加手段が、出力バッファの N チャネルトランジスタおよび P チャネルトランジスタそれぞれに対応して設けられているので、N チャネルトランジスタと P チャネルトランジスタそれぞれを独立して調整することができ、オフセット値も個別に設定することができる。そのためにきめ細かい調整を行うことができる。

**【 0 0 3 5 】**

請求項 4 に記載の発明によれば、オフセット設定部がレジスタで構成されているので、レジスタに予めオフセット値を設定することで、波形調整の幅を広げることができる。

40

**【 0 0 3 6 】**

請求項 5 に記載の発明によれば、オフセット設定部が外部入力端子で構成されているので、外部端子を “ H i ” レベルまたは “ L o w ” レベルに設定した組み合わせでオフセット値を設定することができ、波形調整の幅を広げることができる。また、内部にオフセット記憶用の回路が不要となり回路規模を小さくすることができる。

**【 0 0 3 7 】**

請求項 6 に記載の発明によれば、オフセット設定部が書き換え可能な不揮発性メモリで構成されているので、E P R O M ( Erasable Programmable Read Only Memory ) や E E P R O M ( Electrically Erasable and Programmable Read Only Memory ) などの不揮発性

50

メモリに予めオフセット値を設定することで、波形調整の幅を広げることができる。また、不揮発性メモリとすることでオフセット設定部を外付けにしたり、他のパラメータなどが記憶されているメモリと共に用することができる。部にオフセット記憶用の回路を設けることと比較して回路規模を小さくすることができる。

#### 【0038】

請求項7に記載の発明によれば、負荷数入力手段から入力された出力バッファに接続される負荷の数および配線長入力手段から入力された出力バッファから負荷までの配線長に基づいてオフセット算出部でオフセット値を算出しているので、出力バッファに接続される負荷の数と出力バッファから負荷までの配線長を与えるのみでオフセット値を自動的に算出して設定することができる。

10

#### 【0039】

請求項8に記載の発明によれば、出力バッファに接続される負荷の数および配線長入力手段から入力された出力バッファから負荷までの配線長に基づいてオフセット算出部でオフセット値を算出し、そのオフセット値を調整した波形値に加算しているので、出力バッファに接続される負荷の数と出力バッファから負荷までの配線長を与えるのみでオフセット値を自動的に算出して設定することができ、例えばプリント配線基板上の配線長が設計値よりも増大した場合でもプリント配線基板の再設計を行わずに出力バッファの駆動能力を変更することができる。

#### 【発明を実施するための最良の形態】

#### 【0040】

20

#### [第1実施形態]

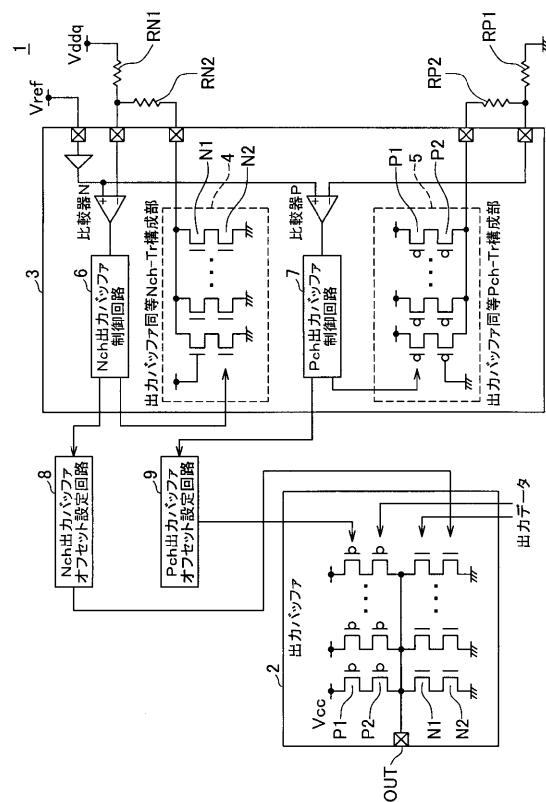

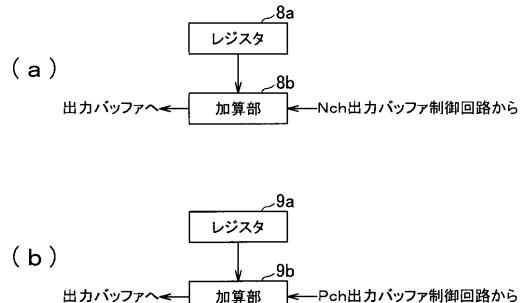

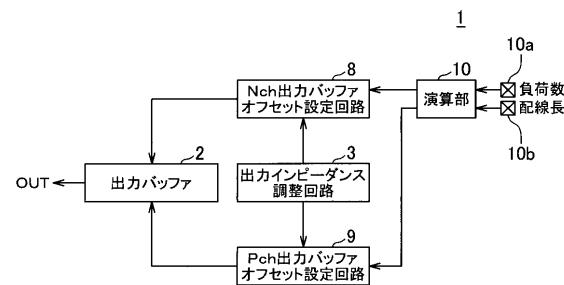

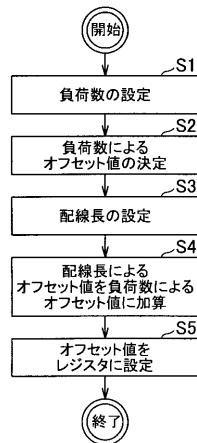

以下、本発明の一実施形態を、図1乃至図6を参照して説明する。図1は、本発明の一実施形態にかかる半導体回路1の回路図である。図2は、図1に示したNch出力バッファオフセット設定回路8の構成を示したブロック図である。図3は、図1に示した出力インピーダンス調整装置1に対してオフセット値を演算する演算部を加えた半導体回路を示すブロック図である。図4は、出力バッファに接続される負荷の数とオフセット値との対応表である。図5は、出力バッファと負荷との間の配線長とオフセット値との対応表である。図6は、図2に示した演算回路でオフセット値が演算される手順を示したフローチャートである。

#### 【0041】

30

図1に示した半導体回路1は、出力バッファ2と出力インピーダンス調整回路3と、Nch出力バッファオフセット設定回路8と、Pch出力バッファオフセット設定回路9と、から構成されている。

#### 【0042】

出力バッファ2は、Vcc、第1PチャネルトランジスタP1、第2PチャネルトランジスタP2、第1NチャネルトランジスタN1、第2NチャネルトランジスタN2、グランドの順に直列接続されたバッファ回路が複数組設けられ、各バッファ回路の第2PチャネルトランジスタP2と第1NチャネルトランジスタN1の間に互いに並列接続するとともに出力端子OUTとしている。

#### 【0043】

40

また、出力バッファ2の各第2PチャネルトランジスタP2と各第1NチャネルトランジスタN1のゲートには出力データが、第1PチャネルトランジスタP1のゲートには後述するPch出力バッファオフセット設定回路9が出力するコントロール信号が、第2NチャネルトランジスタN2のゲートには後述する出力バッファオフセット設定回路8が出力するコントロール信号が、それぞれ接続されている。

#### 【0044】

本実施形態では出力バッファ2の並列数は便宜上15組とする。勿論この数は8組でも12組でも、20組でもよい。出力バッファ2内のバッファ回路は本来何組かはデフォルトでONとなることが一般的であるが、本実施形態においては便宜上出力インピーダンス調整回路3によって設定される7組と、Nch出力バッファオフセット設定回路8および

50

Pch出力バッファオフセット設定回路9によって設定される7組と、デフォルトの1組とに分け、デフォルトの1組は常にONとしている。なお、この場合のONとは、第1Pチャネルトランジスタと第2PチャネルトランジスタとがONになってVccレベルが出力される(Hiレベルが出力される)か、第1Nチャネルトランジスタと第2NチャネルトランジスタとがONになってグランドレベルが出力される(Lowレベルが出力される)か、のいずれかの出力が可能な状態を示している。

#### 【0045】

波形調整手段、インピーダンス調整部としての出力インピーダンス調整回路3は、出力バッファ同等Nch-Tr構成部4と、出力バッファ同等Pch-Tr構成部5と、Nch出力バッファ制御回路6と、Pch出力バッファ制御回路7と、比較器N1と、比較器P1と、を備えている。10

#### 【0046】

出力バッファ同等Nch-Tr構成部4は、出力バッファ2のうちNチャネルトランジスタ部分の複製であって、抵抗RN2、第1NチャネルトランジスタN1、第2NチャネルトランジスタN2、グランドの順に直列に接続された回路が出力バッファ2と同数並列に接続されている。また、各第1NチャネルトランジスタN1のゲートにはVccが入力され、第2NチャネルトランジスタN2のゲートには後述するNch出力バッファ制御回路6のコントロール信号が入力されている。出力バッファ同等Nch-Tr構成部4は、出力バッファ2と同じ構成をとることで外部出力に影響なく、出力バッファ2のインピーダンス状態をフィードバックすることが出来る。20

#### 【0047】

出力バッファ同等Pch-Tr構成部5は、出力バッファ2のうちPチャネルトランジスタ部分の複製であって、Vcc、第1PチャネルトランジスタP1、第2PチャネルトランジスタP2、抵抗RP2の順に直列に接続された回路が出力バッファ2と同数並列に接続されている。また、第1PチャネルトランジスタP1のゲートには後述するPch出力バッファ制御回路7のコントロール信号が入力され、各第2PチャネルトランジスタP2のゲートにはグランドが接続されている。出力バッファ同等Nch-Tr構成部5は、出力バッファ2と同じ構成をとることで外部出力に影響なく、出力バッファ2のインピーダンス状態をフィードバックすることが出来る。30

#### 【0048】

Nch出力バッファ制御回路6は、電圧レベルを比較する比較器Nからの電圧差値を受け取る。電圧差に合わせてONする出力バッファ同等Nch-Tr構成部4内のNチャネルトランジスタの並列数を調整するために各Nチャネルトランジスタそれぞれに対してコントロール信号が出力されている。つまり、コントロール信号はバッファ回路の並列数分出力され、例えば並列数が8だった場合は8本出力されている。また、Nch出力バッファ制御回路6は、前記電圧差に合わせてONするNチャネルトランジスタの並列数を後述するNch出力バッファオフセット設定回路8に出力している。40

#### 【0049】

Pch出力バッファ制御回路7は、電圧レベルを比較する比較器Pからの電圧差値を受け取る。電圧差に合わせてONする出力バッファ同等Pch-Tr構成部5内のPチャネルトランジスタの並列数を調整するために各Pチャネルトランジスタそれぞれに対してコントロール信号が出力されている。つまり、コントロール信号はバッファ回路の並列数分出力され、例えば並列数が8だった場合は8本出力されている。また、Pch出力バッファ制御回路7は、前記電圧差に合わせてONするPチャネルトランジスタの並列数を後述するPch出力バッファオフセット設定回路9に出力している。40

#### 【0050】

比較器Nは、リファレンス電圧Vrefと、Vddqに対して抵抗RN1を挟んだ電圧が入力され、比較した結果がNch出力バッファ制御回路6に出力される。

#### 【0051】

比較器Pは、リファレンス電圧Vrefと、グランドに対して抵抗RP1を挟んだ電圧50

が入力され、比較した結果が P c h 出力バッファ制御回路 7 に出力される。

【0052】

オフセット付加手段としての N c h 出力バッファオフセット設定回路 8 は、図 2 ( a ) に示すようにレジスタ 8 a と加算部 8 b とを備え、 N c h 出力バッファ制御回路 6 から入力されたトランジスタの並列数に対して予めレジスタ 8 a に設定されたオフセット値を加算して算出された最終的な並列数に応じて出力バッファ 2 にコントロール信号を出力する。このコントロール信号は出力バッファ 2 の各バッファ回路の第 2 N チャネルトランジスタ N 2 それぞれのゲートに対して 1 本ずつ出力され、それぞれのコントロール信号が並列数に応じて各第 2 N チャネルトランジスタ N 2 を ON / OFF する。

【0053】

オフセット付加手段としての P c h 出力バッファオフセット設定回路 9 は、図 2 ( b ) に示すようにレジスタ 9 a と加算部 9 b とを備え、 P c h 出力バッファ制御回路 7 から入力されたトランジスタの並列数に対して予めレジスタ 9 a に設定されたオフセット値を加算して算出された最終的な並列数に応じて出力バッファ 2 にコントロール信号を出力する。このコントロール信号は出力バッファ 2 の各バッファ回路の第 1 P チャネルトランジスタ P 1 それぞれのゲートに対して 1 本ずつ出力され、それぞれのコントロール信号が並列数に応じて各第 1 P チャネルトランジスタ N 1 を ON / OFF する。

【0054】

次に、上述した構成の半導体回路 1 における出力バッファのドライブ能力の選択動作について説明する。半導体回路 1 における出力バッファのドライブ能力の選択はキャリブレーションによって行われる。キャリブレーションは以下の手順で行われる。

20

【0055】

まず、 N チャネル側から説明すると、初期状態は出力バッファ同等 N c h - T r 構成部 4 内のバッファ回路は 1 つしか選択されていない状態とする。比較器 N には V d d q からの電位が抵抗 R N 1 を経由しマイナス側の比較電圧として入力される。 V d d q からの電位の一部は R N 2 を経由して出力バッファ同等 N c h - T r 構成部 4 の選択されているバッファ回路から電流を落とされる。一方比較器 N のプラス側には V d d q / 2 のリファレンス電圧 V r e f が入力される。比較器 N はリファレンス電圧 V r e f の方が電圧が大きければ、比較器 N からは “ H ” ( H i レベル ) が output されるが、初期状態においては比較電圧側 ( マイナス側 ) が高いため、当然ながら “ L ” ( L o w レベル ) となる。

30

【0056】

N c h 出力バッファ制御回路 6 には ON にするバッファ回路の数をカウントできるカウンタが設けられており、このカウンタは初期値が 0 となっている。カウンタは 3 ビットで構成され、 0 から 7 の数値を表すことが出来る。カウンタの後段にはカウンタの出力値にしたがって、選択されるコントロール信号が 8 本ある。カウンタ出力が 0 の場合は 8 本のうちの 1 本が “ H ” となり、残りはすべて “ L ” となる。つまり 0 であれば 1 組のバッファ回路の第 2 N チャネルトランジスタ N 2 が ON することになる。カウンタ出力が 4 の場合は 5 本のコントロール信号が “ H ” となり、つまり 5 組のバッファ回路の第 2 N チャネルトランジスタ N 2 が ON することになる。

40

【0057】

そして、カウンタをインクリメントさせながら、そのときに引き抜く電流により電圧の変動を、比較器 N によりリファレンス電圧 V r e f と比較する。比較の結果が “ H ” になったときカウンタのインクリメントをストップし、キャリブレーションの終了となる。このとき、キャリブレーションの結果を比較の結果が “ H ” になったときの数値にするか、その直前の数値にするかはどちらでもかまわない。

【0058】

次に、 P c h 側では、初期状態は出力バッファ同等 P c h - T r 構成部 5 内のバッファ回路は 1 つしか選択されていない状態とする。比較器 P には抵抗 R P 1 を経由しグランドに接続されて比較器 P のマイナス側の比較電圧として入力される。グランドからの電位の一部は抵抗 R P 2 を経由して出力バッファ同等 P c h - T r 構成部 5 の選択されているバ

50

ツファ回路から電流を供給する。一方比較器 P の + 側には  $V_{ddq}/2$  のリファレンス電圧  $V_{ref}$  が入力される。比較器 P はリファレンス電圧  $V_{ref}$  の方が電圧が大きければ、比較器 P からは “H” が出力されるため、初期状態においては比較電圧側（マイナス側）が低いため、当然ながら “H” となる。

#### 【0059】

Pch 出力バッファ制御回路 7 には ON にするバッファ回路の数をカウントできるカウンタが入っており、このカウンタは初期値が 0 となっている。カウンタは 3 ビットで構成され、0 から 7 の数値を表すことが出来る。カウンタの後段にはカウンタの出力値にしたがって、選択されるコントロール信号が 8 本ある。カウンタ出力が 0 の場合は 8 本のうちの 1 本が “L” となり、残りはすべて “H” となる。つまり 0 であれば 1 組のバッファ回路の第 1 P チャネルトランジスタ P1 が ON することになる。カウンタ出力が 4 の場合は 5 本のコントロール信号が “L” となり、つまり 5 組のバッファ回路の第 1 P チャネルトランジスタ P1 が ON することになる。

10

#### 【0060】

Nch 出力バッファ制御回路 6 と Pch 出力バッファ制御回路 7 の結果で ON するバッファ回路のコントロール信号の本数が決まり、加えてデフォルトで ON する本数で全部の本数が決定する。すなわち、出力バッファ 2 におけるトランジスタの並列数を変化させることで、出力波形値としての出力インピーダンスを調整している。

20

#### 【0061】

Nch 出力バッファオフセット設定回路 8 や Pch バッファオフセット設定回路 9 では、キャリブレーション後のカウンタの値 3 ビットが入力される。このとき、Nch 出力バッファオフセット設定回路 8 や Pch バッファオフセット設定回路 9 には外部からプログラムなどで設定可能な 3 ビットのレジスタ 8a、9a が設けられている。そして、このレジスタ 8a、9a と、3 ビットのカウンタの値が加算器により加算され、そのトータル数の値がコントロール信号の本数となる。

20

#### 【0062】

例えば Nch 出力バッファ制御回路 6 から入力されたカウント値が 2、Pch 出力バッファ制御回路 7 から入力されたカウント値が 3、レジスタ 8a の設定値が 4、レジスタ 9a の設定値が 5 であった場合、出力バッファ 2 内で ON される第 2 N チャネルトランジスタ数、つまりコントロール信号数は  $2 + 4 = 6$  本で、さらにデフォルトの 1 本を加えて 7 本が同時に ON することになる。出力バッファ 2 内で ON される第 1 P チャネルトランジスタ数、つまりコントロール信号数は  $3 + 5 = 8$  本でデフォルトの 1 本を加えて 9 本が同時に ON することになる。すなわち、出力インピーダンス調整回路 3 が調整した出力バッファにおけるトランジスタの並列数に対してレジスタ 8a および 9a に設定されたオフセット値を加算し、その加算結果に基づいて出力バッファ 2 の並列数が変更されている。

30

#### 【0063】

なお、Nch 出力バッファオフセット設定回路 8 や Pch バッファオフセット設定回路 9 のレジスタ 8a、9a 設定値が 0 の場合は、Nch 出力バッファ制御回路 6 や Pch 出力バッファ制御回路 7 からのカウント値とデフォルトによる本数の和で設定が決まり、このようにすれば従来技術と同様に出力インピーダンス調整回路 3 のみの調整とができる。

40

#### 【0064】

次に、Nch 出力バッファオフセット設定回路 8 や Pch バッファオフセット設定回路 9 のレジスタ 8a、9a に設定するオフセット値の算出方法について説明する。

#### 【0065】

図 3 に示したように、半導体装置 1 に演算部 10 を設け、演算部 10 で算出した結果を Nch 出力バッファオフセット設定回路 8 や Pch バッファオフセット設定回路 9 に出力してレジスタに書き込む。

#### 【0066】

オフセット算出部としての演算部 10 では、半導体回路 1 の出力バッファ 2 に接続され

50

る負荷の数によって図4に示すようなテーブルが予め記憶されており、負荷数入力手段としての入力端子10aから入力された負荷の数に対応した値をテーブルから読み取る。このテーブルの数値は実機評価もしくはシミュレーション等で決定しておけばよい。

#### 【0067】

また、同様に出力バッファ2と負荷との間の配線長によって図5に示すようなテーブルが予め記憶されており、配線長入力手段としての入力端子10bから入力された配線長に対応した値をテーブルから読み取る。このテーブルの数値は実機評価もしくはシミュレーション等で決定しておけばよい。

#### 【0068】

以上の2つのテーブルから演算部10は負荷の数、配線長からトータルのオフセット値を算出する。算出されたトータルのオフセット値はNch出力バッファオフセット設定回路8やPchバッファオフセット設定回路9に出力されレジスタ8aまたは9aに書き込まれる。すなわち、入力端子10aから入力された出力バッファ2に接続される負荷の数および入力端子10bから入力された出力バッファ2から負荷までの配線長に基づいてオフセット値を算出している。

#### 【0069】

図6に上述したオフセット値の算出動作のフローチャートを示す。

#### 【0070】

まず、ステップS1において、負荷数を設定してステップS2に進む。次に、ステップS2において、負荷数によるオフセット値を決定してステップS3に進む。次に、ステップS3において、配線長を設定してステップS4に進む。次に、ステップS4において、配線長によるオフセット値をステップS2で決定した負荷数によるオフセット値に加算してステップS5に進む。次に、ステップS5において、オフセット値をレジスタ8aや9aに設定する。

#### 【0071】

なお、本実施形態では半導体回路1内部で負荷数と配線長から自動的に算出する方法を示したが、演算部10を外部に設けてもよいし、算出自体は他のコンピュータ等で行って、その結果をプログラムなどでレジスタに設定するようにしてもよい。

#### 【0072】

本実施形態によれば、出力バッファ2のバッファ回路の並列数を調整する出力インピーダンス調整回路3の後段にNchバッファオフセット設定回路8とPchバッファオフセット設定回路9とを設けて、出力インピーダンス調整回路3が調整した並列数にNchバッファオフセット設定回路8とPch出力バッファオフセット設定回路9でオフセット値を加算しているので、出力インピーダンス調整回路3や抵抗RN1, RN2, RP1, RP2を変更することなく出力バッファ2におけるトランジスタの並列数の調整幅を余力を持たすことができ、例えばプリント配線基板上での配線長が設計値よりも増大した場合でもプリント配線基板の再設計を行わずに出力バッファ2の駆動能力を変更することができる。

#### 【0073】

また、Nch出力バッファ制御回路6、Pch出力バッファ制御回路7と、Nch出力バッファオフセット設定回路8とPchバッファオフセット設定回路9とが、出力バッファ2のNチャネルトランジスタおよびPチャネルトランジスタそれぞれに対応して設かれているので、NチャネルトランジスタとPチャネルトランジスタそれぞれを独立してトランジスタの並列数を変更でき、オフセット値も個別に設定することができる。そのためにきめ細かい調整を行うことができる。

#### 【0074】

また、オフセット値がレジスタ8a、9aに設定されているので、レジスタ8a、9aに予めオフセット値を設定することで調整の幅を広げることができる。

#### 【0075】

また、出力バッファ2に接続される負荷の数および出力バッファ2から負荷までの配線

10

20

30

40

50

長に基づいて演算部 10 でオフセット値を算出しているので、出力バッファ 2 に接続される負荷の数と出力バッファ 2 から負荷までの配線長を与えるのみでオフセット値を自動的に算出して設定することができる。

#### 【0076】

なお、本発明はスルーレートの調整においても上述した出力インピーダンスと同様に Nch 出力バッファオフセット設定回路 8 と Pch 出力バッファオフセット設定回路 9 に相当する回路を設けることで調整幅を余力を持たすことができ、例えばプリント配線基板上での配線長が設計値よりも増大した場合でもプリント配線基板の再設計を行わずに出力バッファ 2 の駆動能力を変更することができる。

#### 【0077】

また、上述した実施形態では Nch 出力バッファオフセット設定回路 8 と Pch 出力バッファオフセット設定回路 9 は、レジスタ 8a および 9a にオフセット値を設定していたが、レジスタ 8a および 9a に限らず、外部端子により設定しても良い。例えばオフセット値に 3 ビット必要である場合は、外部端子を N チャネル、P チャネルそれぞれに 3 本ずつ、計 6 本用意し、外部端子での入力を “H” あるいは “L” に設定し、その値を利用すればよい。

#### 【0078】

また、オフセット値は書き換え可能な EEPROM (Erasable Programmable Read Only Memory) や EEPROM (Electrically Erasable and Programmable Read Only Memory) 等の不揮発性メモリ素子を使用してもよい。

10

20

30

40

50

#### 【0079】

また、上述した実施形態のオフセット値は符号無しでの値であったが、符号ありとしてもよい。符号なしでは 3 ビットのカウンタの場合、0 ~ 7 までの数値と扱うことができるが、符号ありでは例えば最上位ビットを符号ビットとすると、-4 ~ 3 までの数値を扱うことができるようになる。そのためオフセット値による減算を行うことも出来るようになる。

#### 【0080】

また、本発明は半導体回路の DDR - SDRAM (Double Data Rate - Synchronous Dynamic Random Access Memory) などのメモリインターフェースといった高速な通信を行う必要があるインターフェースの出力バッファに適用すると好適である。

#### 【0081】

なお、本発明は上記実施形態に限定されるものではない。即ち、本発明の骨子を逸脱しない範囲で種々変形して実施することができる。

#### 【図面の簡単な説明】

#### 【0082】

【図 1】本発明の第 1 の実施形態にかかる半導体回路の回路図である。

【図 2】図 1 に示した Nch 出力バッファオフセット設定回路の構成を示したブロック図である。

【図 3】図 1 に示した出力インピーダンス調整装置 1 に対してオフセット値を演算する演算部を加えた半導体回路を示すブロック図である。

【図 4】出力バッファに接続される負荷の数とオフセット値との対応表である。

【図 5】出力バッファと負荷との間の配線長とオフセット値との対応表である。

【図 6】図 2 に示した演算回路でオフセット値が演算される手順を示したフローチャートである。

【図 7】従来技術にかかる半導体回路の回路図である。

【図 8】出力バッファのドライブ能力による波形の変化の説明図である。

【図 9】出力バッファに接続される負荷の数と配線長の違いについての説明図である。

【図 10】出力バッファのドライブ能力が適当な場合のアイダイヤグラムである。

【図 11】出力バッファのドライブ能力が不足している場合のアイダイヤグラムである。

#### 【符号の説明】

## 【 0 0 8 3 】

- 1 半導体回路

2 出力バッファ

3 出力インピーダンス調整回路（波形調整手段、インピーダンス調整部）

8 Nch出力バッファオフセット設定回路（オフセット付加手段）

8 a レジスタ

8 b 加算部

9 Pch出力バッファオフセット設定回路（オフセット付加手段）

9 a レジスタ

9 b 加算部

10 演算部（オフセット算出部）

10 a 入力端子（負荷数入力手段）

10 b 入力端子（配線長入力手段）

- 10

【図1】

【図2】

【図3】

【図4】

| 負荷の数 | オフセット値 |

|------|--------|

| 1個接続 | 0      |

| 2個接続 | 1      |

| 4個接続 | 2      |

| 8個接続 | 3      |

【図6】

【図5】

| 負荷の数           | オフセット値 |

|----------------|--------|

| 80mm未満         | 0      |

| 80mm以上100mm未満  | 1      |

| 100mm以上120mm未満 | 2      |

| 120mm以上140mm未満 | 3      |

| 140mm以上        | 4      |

【図7】

【図8】

【図9】

【図 10】

【図 11】

---

フロントページの続き

|              |                |      |   |            |

|--------------|----------------|------|---|------------|

| (51) Int.Cl. | F I<br>H 0 3 F | 3/68 | B | テーマコード(参考) |

|--------------|----------------|------|---|------------|

F ターム(参考) 5J056 AA05 AA40 BB00 BB12 CC00 CC09 DD12 DD29 DD59 EE06

EE15 FF09 GG13 KK00

5J500 AA01 AA21 AC73 AF15 AH10 AH17 AK03 AM18 AM21 AT01

5K029 AA03 DD04 DD22 GG07 JJ08