(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3580484号

(P3580484)

(45) 発行日 平成16年10月20日(2004.10.20)

(24) 登録日 平成16年7月30日(2004.7.30)

(51) Int.C1.<sup>7</sup>

F 1

H03K 3/03

G09G 3/20H03K 3/03

G09G 3/20

請求項の数 21 (全 17 頁)

(21) 出願番号 特願平11-304370

(22) 出願日 平成11年10月26日(1999.10.26)

(65) 公開番号 特開2000-232338(P2000-232338A)

(43) 公開日 平成12年8月22日(2000.8.22)

審査請求日 平成14年1月11日(2002.1.11)

(31) 優先権主張番号 9823369.5

(32) 優先日 平成10年10月27日(1998.10.27)

(33) 優先権主張国 英国(GB)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100078282

弁理士 山本 秀策

(72) 発明者 グラハム アンドリュー カーンズ

イギリス国 オーエックス2 8エヌエイ

チ オックスフォード, カッテスロウ,

ボーン クローズ 22

(72) 発明者 マイケル ジェームズ ブラウンロー

イギリス国 オーエックス4 4ワイピー

オックスフォード, サンドフォード

オン テムズ, チャーチ ロード 12

4

最終頁に続く

(54) 【発明の名称】クロックパルス発生器、空間光変調器およびディスプレイ

## (57) 【特許請求の範囲】

## 【請求項1】

クロック入力と、Nは3よりも大きいN個のステージとを備えるクロックパルス発生器であって、

該ステージの各第iステージは、

トランスマッショングートであって、第(i-1)ステージからの制御信号に応じて該クロック入力からのクロックパルスを該トランスマッショングートの出力へパスするように構成されたトランスマッショングートと、

該第(i-1)ステージおよび第(i+1)ステージに動作可能に結合され、該制御信号を生成する、制御信号生成回路であって、該第(i-1)ステージからの該制御信号および該トランスマッショングートからの該クロックパルスが終了した場合に、該第(i+1)ステージに制御信号を供給し、該第(i+1)ステージが制御信号を生成する場合に、該第(i+1)ステージへの該制御信号を終了する、制御信号発生回路とを含み、ここで1 < i < Nである、クロックパルス発生器。

## 【請求項2】

前記各第iステージは、前記第(i+1)ステージからの制御信号により前記トランスマッショングートが選択的に制御されるようにし、該第(i+1)ステージからの該制御信号および前記トランスマッショングートからの前記クロックパルスが終了した場合に、前記制御信号発生回路が、該制御信号を前記第(i-1)ステージへ供給するようにし、該第(i-1)ステージが制御信号を生成する場合に、前記制御信号発生回路が、該制御信

号を終了するようにするスイッチング配置を備える、請求項 1 に記載のクロックパルス発生器。

【請求項 3】

前記スイッチング配置が、前記制御信号発生回路の前記出力に接続され、方向制御信号を受信する制御入力を有する、複数のさらなるトランスマッシュゲートを備える、請求項 2 に記載のクロックパルス発生器。

【請求項 4】

前記トランスマッシュゲート出力の少なくとも 1 つが、前記クロックパルス発生器の出力を構成する、請求項 1 に記載のクロックパルス発生器。

【請求項 5】

前記制御信号またはその相補体の少なくとも 1 つが、前記クロックパルス発生器の出力信号を構成する、請求項 1 に記載のクロックパルス発生器。

【請求項 6】

前記トランスマッシュゲートが前記クロック入力に接続された入力を有する、請求項 1 に記載のクロックパルス発生器。

【請求項 7】

前記各トランスマッシュゲートが、反対の導電性タイプである第 1 および第 2 の金属酸化シリコンフィールド効果トランジスタを備え、該トランジスタのソース - ドレイン路は反平行に接続される、請求項 1 に記載のクロックパルス発生器。

【請求項 8】

前記第 2 のトランジスタのゲートが、インバータの出力に接続され、該インバータの入力が、前記制御信号を受信する前記第 1 のトランジスタのゲートに接続される、請求項 7 に記載のクロックパルス発生器。

【請求項 9】

前記各第 i ステージの前記制御信号発生回路が、第 3、第 4 および第 5 金属酸化シリコンフィールド効果トランジスタと、金属酸化シリコンフィールド効果トランジスタ配置とを備え、該第 3 および該第 4 トランジスタが反対の導電性タイプであり、該第 3 および該第 4 トランジスタは第 1 の供給入力と第 2 の供給入力との間で直列に接続され、該第 3 のトランジスタのゲートは、前記第 ( i - 1 ) ステージの該制御信号発生回路に接続され、該第 4 のトランジスタのゲートが、前記トランスマッシュゲートの前記出力に接続され、該第 5 のトランジスタおよび該トランジスタ配置が、反対の導電性タイプであり、該第 5 のトランジスタおよび該トランジスタ配置は、該第 1 の供給入力と該第 2 の供給入力との間で直列に接続され、該第 5 のトランジスタのゲートは、前記第 ( i + 1 ) ステージの該制御信号発生回路に接続され、該トランジスタ配置の第 1 の制御電極が、該第 3 のトランジスタと第 4 のトランジスタとの間の接続部に接続され、該トランジスタ配置の第 2 の制御電極が、該トランスマッシュゲートの該出力に接続される、請求項 1 に記載のクロックパルス発生器。

【請求項 10】

前記第 4 のトランジスタのゲートおよび前記トランジスタ配置の前記第 2 の制御電極が、インバータを介して前記トランスマッシュゲートの前記出力に接続される、請求項 9 に記載のクロックパルス発生器。

【請求項 11】

前記トランスマッシュゲート出力が、プルアップまたはプルダウントランジスタと共に提供される、請求項 1 に記載のクロックパルス発生器。

【請求項 12】

前記各トランスマッシュゲートが、反対の導電性タイプである第 1 および第 2 の金属酸化シリコンフィールド効果トランジスタを備え、該トランジスタのソース - ドレイン路が反平行に接続され、該第 2 のトランジスタのゲートが、インバータの出力に接続され、該インバータの入力は、前記制御信号を受信する該第 1 のトランジスタのゲートに接続され、

10

20

30

40

50

前記各プルアップまたはプルダウントランジスタが、該インバータの該入力または出力に接続された制御電極を有する、請求項 1 1 に記載のクロックパルス発生器。

【請求項 1 3】

前記各ステージが、先行ステージから前記制御信号を受信する制御信号入力を有し、該制御信号入力がプルアップまたはプルダウン配置と共に提供される、請求項 1 に記載のクロックパルス発生器。

【請求項 1 4】

前記各トランスマッシュゲートが、反対の導電性タイプである第 1 および第 2 の金属酸化シリコンフィールド効果トランジスタを備え、該トランジスタのソース - ドレイン路が反平行に接続され、10

前記第 2 のトランジスタのゲートがインバータの出力に接続され、該インバータの入力は、前記制御信号を受信する該第 1 のトランジスタのゲートに接続され、

前記各プルアップまたはプルダウン配置が、該インバータの該出力に接続された第 1 の制御電極、および先行ステージの該インバータの該出力に接続された第 2 の制御電極を有するトランジスタ配置を備える、請求項 1 3 に記載のクロックパルス発生器。

【請求項 1 5】

前記各ステージが、リセット信号に応じて該ステージをリセットするリセット回路を有する、請求項 1 に記載のクロックパルス発生器。

【請求項 1 6】

前記各ステージが、リセット信号に応じて該ステージをリセットするリセット回路を有し20

該各ステージが、前記制御信号を先行ステージから受信する制御信号入力を有し、該リセット回路が、論理状態をそこでリセットする該制御信号入力に接続されたプルアップまたはプルダウントランジスタを備える、請求項 1 4 に記載のクロックパルス発生器。

【請求項 1 7】

C M O S 集積回路をさらに備える、請求項 1 に記載のクロックパルス発生器。

【請求項 1 8】

請求項 1 に記載のクロックパルス発生器を備える、空間光変調器。

【請求項 1 9】

液晶デバイスをさらに備える、請求項 1 8 に記載の空間光変調器。30

【請求項 2 0】

請求項 1 8 に記載の空間光変調器を備える、ディスプレイ。

【請求項 2 1】

請求項 1 9 に記載の空間光変調器を備える、ディスプレイ。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明はクロックパルス発生器に関する。このような発生器は、高速度低電力制御器回路（例えば、デジタル信号処理（D S P）を含む複合超大規模集積（V L S I）設計）において用いられ得る。クロックパルス発生器は、空間光変調器およびディスプレイのドライバ回路（例えば、明確なパルスのシーケンスが、高速度ビデオデータをサンプル化する回路に供給されなければならないような画素化（p i x e l a t e d）マトリクスタイプのドライバ回路）用にアドレスする際に、利点を生かして用いられ得る。40

【0 0 0 2】

【従来の技術】

公知であるタイプのクロックパルス発生器は、シフトレジスタに基づく。シフトレジスタは、D型フリップフロップの縦列チェーンを備え、このD型フリップフロップは、クロックパルスに応答し、単一記憶論理状態をチェーン内の1つのフリップフロップから次のフリップフロップへバスする。典型的なクロックパルス発生アプリケーションにおいては、フリップフロップの1つの状態を除く全ての状態が論理ロー（0）状態に初期化されるが50

ゆえに、残ったフリップフロップは論理ハイ(1)状態に初期化される。シフトレジスタは公知の周波数においてクロック化され、シフトレジスタ内にある循環する1つの状態が、フリップフロップの出力において順次パルスを発生するために用いられる。この周知の技術は、例えば米国特許第4,542,301号および米国特許第4,612,659号において開示されている。この技術を改良したものが、米国特許第4,785,297号において開示されている。この場合、各フリップフロップの「マスター」および「スレーブ」出力は、組合せ論理ゲート(例えばANDまたはNANDゲート)と組み合わせて用いられる。それにより、所定数の出力パルス用のシフトレジスタのクロッキング速度を落とす。

#### 【0003】

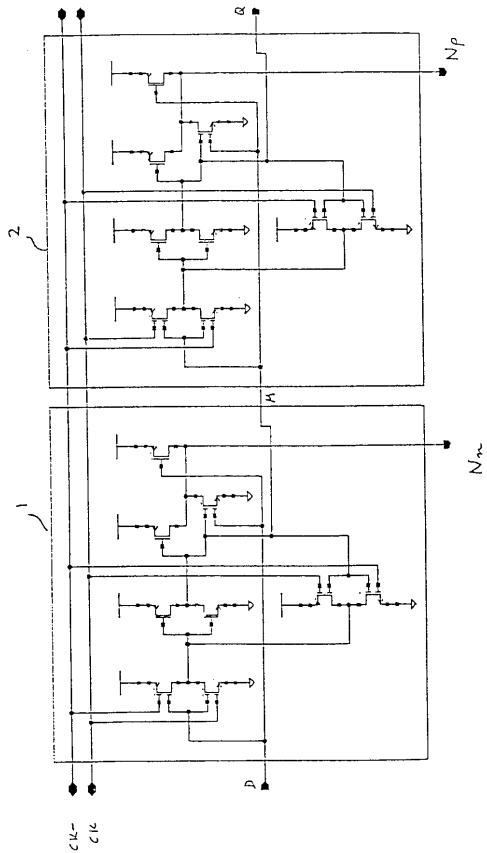

クロックパルス発生回路を連鎖D型ラッチ回路から形成することもまたよく知られている。添付図面の図1は、ラッチ1および2を備える典型的なCMOS回路の一部を図示する。このような配置( arrangement )の構成および動作は周知であるため、詳細には記載しない。ラッチ1および2のように、連続したラッチは、二相クロックの対向したクロック相(CKおよびCK-で表される)上では認識されない。各ラッチの入力および出力は、添付図面の図2に示すクロックパルスN<sub>n</sub>およびN<sub>p</sub>を生成するために、共に「NAND化」される。図2はまた、二相クロック波形、第1ラッチ1へのD入力、第1ラッチ1の出力M(これは第2ラッチ2の入力でもある)、および第2ラッチの出力Qを図示する。

#### 【0004】

この配置にはいくつかの欠点がある。特に、シフトレジスタを駆動するため二相クロックが必要である。また、各クロックラインは、各ラッチ1、2において2つのトランジスタゲートをも駆動する。このことは、比較的高い容量性負荷(capacitive loading)を各クロック相へ与え、最大動作周波数を制限する。さらに、出力パルスN<sub>n</sub>およびN<sub>p</sub>が非オーバーラップになることが保証され得ない。これはあるアプリケーションにおいて(例えば、出力パルスは画素マトリクスディスプレイドライバにおいてビデオデータをサンプル化するために用いられる場合)問題を引き起こし得る。

#### 【0005】

1本のクロックラインまたは複数のクロックラインの容量性負荷を削減し、そして最大動作周波数を増加し、クロック電力消費量を削減するために、様々な技術が開示されてきた。例えば、状態制御クロッククロッキング技術は、クロックパルス発生回路における使用として提案されている。この例としては、米国特許第4,746,915号の中で開示されており、ここでシフトレジスタはいくつかのフリップフロップもしくはラッチのサブレジスタに分割され、より低い周波数において作動する別のシフトレジスタは、クロック信号を各サブルジスタへ選択的に付与するのに使用される。

#### 【0006】

【発明が解決しようとする課題】

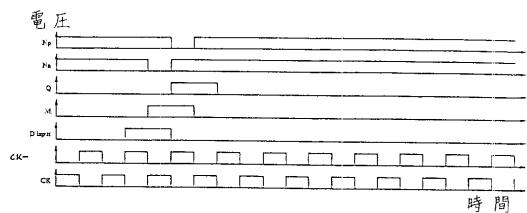

要件が单一循環の1状態であるアプリケーションにおいて、1状態を含む、あるいはそれらの入力時に1状態を有するフリップフロップまたはラッチのみがクロッキングを必要とする。図3に示すように、そのようなアプリケーションにおいて、各フリップフロップの入力および出力を「ORing」することにより発生する信号は、フリップフロップのクロック入力に供給されるクロック信号をゲートするために用いられ得る。このような配置は、T.Mae kawaらによる「A 1.35-in.-diagonal wide-aspect-ratio poly-Si TFT LCD with 513k pixels」(Journal of the Society of Information Display, 415頁~417頁, 1994年)の中で開示されている。しかし、このような配置は、ステージ毎にフルフリップフロップ、およびいくつかのさらなるトランジスタを必要とする。また、フリップフロップ出力は、比較的大きな負荷をも駆動しなければならず、これは最大動作速度を制限する。

#### 【0007】

10

20

30

40

50

**【課題を解決するための手段】**

本発明の第1の局面によると、クロック入力およびNステージを備えるクロックパルス発生器が提供される。ここでNは3よりも大きいN個のステージを備えるクロックパルス発生器であり、ステージの各第iステージは、トランスマッショングートであって、第(i-1)ステージからの制御信号に応じてクロック入力からのクロックパルスをトランスマッショングートの出力へパスするように構成されたトランスマッショングートと、第(i-1)ステージおよび第(i+1)ステージに動作可能に結合され、制御信号を生成する、制御信号生成回路であって、第(i-1)ステージからの制御信号およびトランスマッショングートからのクロックパルスが終了した場合に、第(i+1)ステージに制御信号を供給し、第(i+1)ステージが制御信号を生成する場合に、第(i+1)ステージへの制御信号を終了する、制御信号発生回路とを含み、ここで1 < i < Nである。

10

**【0008】**

各第iステージは、第(i+1)ステージからの制御信号によりトランスマッショングートが選択的に制御されるようにし、第(i+1)ステージからの制御信号およびトランスマッショングートからのクロックパルスが終了した場合に、制御信号発生回路が、制御信号を第(i-1)ステージへ供給するようにし、第(i-1)ステージが制御信号を生成する場合に、制御信号発生回路が、制御信号を終了するようにするスイッチング配置を備えてよい。スイッチング配置は、制御信号発生回路の出力に接続され、方向制御信号を受信する制御入力を有する、複数のさらなるトランスマッショングートを備えてよい。

20

**【0009】**

トランスマッショングート出力は、発生器の出力を構成してもよい。

**【0010】**

制御信号またはその相補体の少なくとも1つは、発生器の出力信号を構成してもよい。

**【0011】**

トランスマッショングートは、前記クロック入力に接続された入力を有してもよい。

**【0012】**

各トランスマッショングートは、反対の導電性タイプである第1および第2の金属酸化シリコンフィールド効果トランジスタを備えてもよく、該トランジスタのソース-ドレイン路は反平行に接続される。第2のトランジスタの前記ゲートは、インバータの出力に接続され、インバータの入力は、制御パルスを受信する第1のトランジスタのゲートに接続されてもよい。

30

**【0013】**

各第iステージの制御信号発生回路が、第3、第4および第5金属酸化シリコンフィールド効果トランジスタと、金属酸化シリコンフィールド効果トランジスタ配置とを備えてよく、第3および第4トランジスタが反対の導電性タイプであり、第3および第4トランジスタは第1の供給入力と第2の供給入力との間で直列に接続され、第3のトランジスタのゲートは、第(i-1)ステージの制御信号発生回路に接続され、第4のトランジスタのゲートが、トランスマッショングートの出力に接続され、第5のトランジスタおよびトランジスタ配置が、反対の導電性タイプであり、第5のトランジスタおよびトランジスタ配置は、第1の供給入力と第2の供給入力との間で直列に接続され、第5のトランジスタのゲートは、第(i+1)ステージの制御信号発生回路に接続され、トランジスタ配置の第1の制御電極が、第3のトランジスタと第4のトランジスタとの間の接続部に接続され、トランジスタ配置の第2の制御電極が、トランスマッショングートの出力に接続される。

40

**【0014】**

第4のトランジスタのゲートおよびトランジスタ配置の第2の制御電極は、インバータを介してトランスマッショングートの出力に接続されてもよい。

**【0015】**

トランスマッショングート出力は、プルアップまたはプルダウントランジスタと共に提供されてもよい。各プルアップまたはプルダウントランジスタは、インバータの入力または

50

出力に接続される制御電極を有してもよい。

【0016】

各ステージは、先行ステージから制御信号を受信する制御信号入力を有してもよく、制御信号入力はプルアップまたはプルダウン配置と共に提供される。各プルアップまたはプルダウン配置は、インバータの出力に接続された第1の制御電極、および先行ステージのインバータの出力に接続された第2の制御電極を有するトランジスタ配置を備えてよい。

【0017】

各ステージは、リセット信号に応じてステージをリセットするリセット回路を有してもよい。各ステージは、制御信号を先行ステージから受信する制御信号入力を有してもよく、リセット回路は、論理状態をそこでリセットする制御信号入力に接続されたプルアップまたはプルダウントランジスタを備えてよい。10

【0018】

発生器は、CMOS集積回路を備えてよい。

【0019】

本発明の第2の局面によると、本発明の第1の局面による発生器を備えた空間光変調器が提供される。

【0020】

空間光変調器は、液晶デバイスを備えてよい。

【0021】

本発明の第3の局面によると、本発明の第2の局面による空間光変調器を備えるディスプレイが提供される。20

【0022】

従って、非常に高い最大動作周波数を有するクロックパルス発生器を提供することが可能である。特に、クロックパルスが1つのトランジスタのみを（トランスマッショングート出力が発生器の出力を構成する場合に、任意の外部負荷に加えて）一度に充電することが要求される発生器を提供することが可能である。また、クロック信号は完全にゲートされ得る。これは2つの理由から重要である。第1に、クロック信号のトランジスタ負荷は、その立ち上がりおよび全体の時間、そしてひいては最大周波数を制限する。本発明の配置では、クロックの負荷は主に寄生素子のためであり、そして比較的大きなクロックパルス発生器において高速度が維持され得る。30

【0023】

第2に、トランジスタゲートによるクロック信号の容量性負荷が最小限化され得る。特に、ステージ毎に1つのゲートのみが充電されることとは別に、スイッチング状態にあるステージ内のトランジスタのゲートのみが充電される。これは結果的に電力消費量を削減し、特にクロック信号を伝える回路トラックのトラック抵抗において、より低い電力を損失することとなる。

【0024】

単相クロックのみが必要とされ、出力パルスはクロック信号の正確なコピー（トランスマッショングートの通過によってのみ劣化する）であり得る。トランスマッショングートは、駆動能力が高くなるように、比較的大きく製造され得る。出力パルスは、トランスマッショングートからきた場合、非オーバーラッピングであることが保証される。クロックパルス発生器は、動的動作、部分静的動作、または疑似静的動作として配置され得る。最高動作速度は動的動作と共に得られるが、部分静的動作、もしくは疑似静的動作はより大きな回路においてより実用的である。40

【0025】

以下の有益な信号がステージから発生し得る。

【0026】

(i) クロックパルスハイ（またはロー）周期に実質的に相当し、クロック立ち上がり（または立ち下がり）エッジと同期する期間の独立した非オーバーラッピング正（または負）パルスと、50

( i i ) クロック周期に実質的に相当し、クロック立ち下がり（または立ち上がり）エッジと同期する期間の独立したオーバーラッピングした正および負パルス。

**【 0 0 2 7 】**

クロックパルス発生器を駆動するために用いられるクロック信号のマーク - スペース比 (mark - to - space ratio) を変化させるだけで、関連パルス幅は変化し得る。

**【 0 0 2 8 】**

**【発明の実施の形態】**

本発明は、添付の図面を参照しながら、実施例を通してさらに説明される。図面を全体に渡り、同じ参照符号が同じ部分を示す。

10

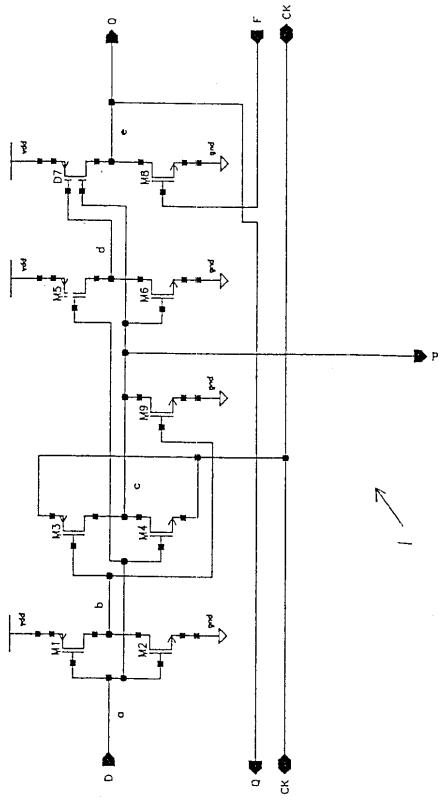

**【 0 0 2 9 】**

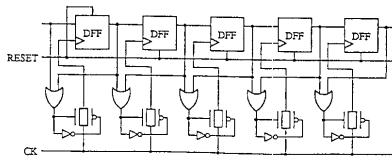

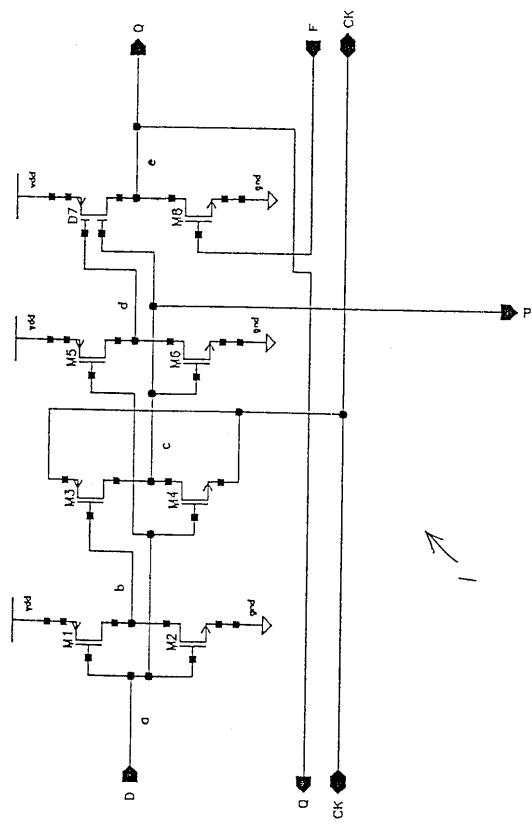

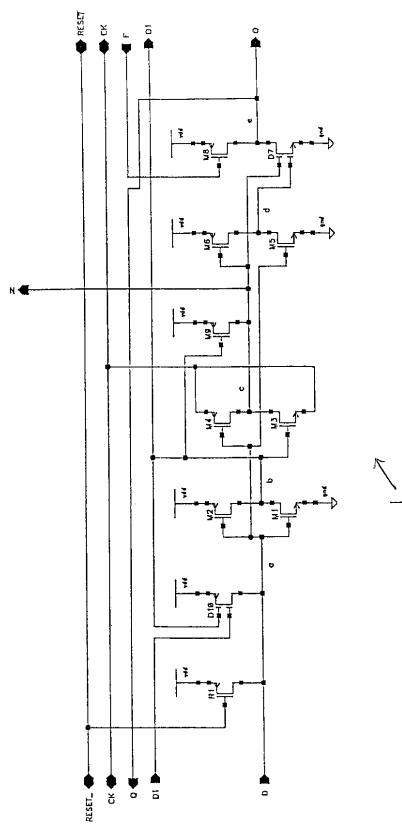

図4に示すクロックパルス発生器ステージ1は、P型金属酸化シリコントランジスタM1、M3、M5およびD7、ならびにN型金属酸化シリコントランジスタM2、M4、M6およびM8を備える。発生器は、CMOS大規模集積回路として、またはその一部として実施される。多様な回路ノード（およびそれらのノードにおいて現れる波形）は、aからeにより表される。

**【 0 0 3 0 】**

ステージ1は制御信号入力Dを有し、これは先行するステージからの制御信号aを受信する。入力DはトランジスタM1およびM2のゲートに接続されており、これら2つのトランジスタは供給ラインvddとgndとの間で直列に接続され、インバータを形成する。トランジスタM3およびM4は、反平行に接続されたこれらのソース - ドレイン路を有し、トランスマッシュゲートを形成する。トランジスタM4のゲートは制御信号aを受信し、トランジスタM3のゲートはインバータからの出力信号bを受信する。トランスマッシュゲートの入力は、外部の信号相クロック（図示せず）からのクロック信号CKを受信するために、クロックラインに接続される。

20

**【 0 0 3 1 】**

トランスマッシュゲートの出力は、トランジスタM5、M6、D7およびM8を備える制御信号発生回路へ信号cを供給する。信号cはまた、ステージ1の出力信号Pをも供給する。トランジスタM5およびM6のゲートは、供給ラインvddとgndとの間で直列に接続される。トランジスタM5のゲートは、先行ステージからの制御信号を受信し、一方トランジスタM6は、トランスマッシュゲートからの信号cを受信する。トランジスタD7（これはデュアルゲートトランジスタとして示されているが、直列に接続されたソース - ドレイン路を備える单一ゲートトランジスタとしても実施され得る）は、供給ラインvddとgndとの間でトランジスタM8と直列に接続される。トランジスタD7の第1のゲートは、回路ノードdにおいてトランジスタM5およびM6のドレインに接続される。トランジスタD7の第2のゲートは、トランスマッシュゲートの出力に接続され、信号cを受信する。トランジスタD7およびM8のドレインは、回路ノードeにおいて共に、制御信号eを後続ステージへ供給するステージの出力Qに接続される。トランジスタM8のゲートは、回路ノードFを介して後続ステージの制御信号発生回路により生成される制御信号を受信するように接続される。信号eは、同様に先行ステージへフィードバックされる。

30

**【 0 0 3 2 】**

トランジスタD7はデュアルゲートトランジスタとして示されるが、直列に接続された2つの单一ゲートトランジスタにより置き換えられ得る。

**【 0 0 3 3 】**

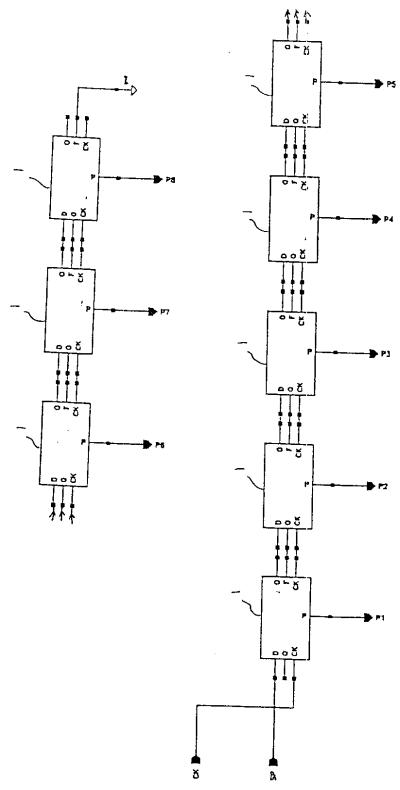

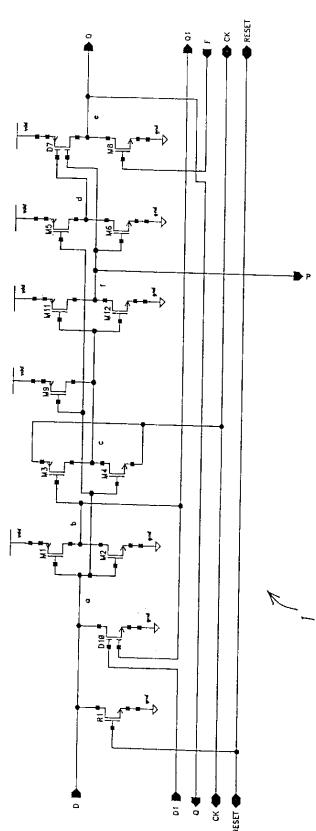

図5は、ステージ1がどのように共に接続され、完全なクロックパルス発生器を形成するかを示す。発生器は、このようなステージを8個備え、連続したステージ間における相互接続は、図4に示すものと同じ参照符号を用いて示される。出力Pは、クロックパルス発生器におけるステージの位置を表す数値が与えられている。スタートパルスSPは、最初のステージの入力Dに供給されるのに対し、最後のステージの出力Qは接続されない。最

40

50

後のステージの入力 F は、供給ライン g n d に接続される。

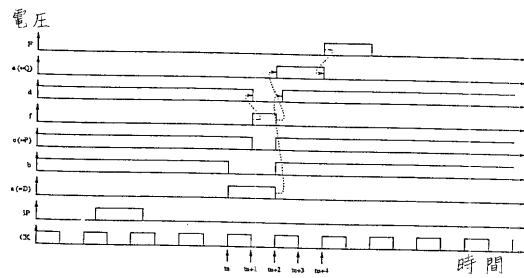

**【 0 0 3 4 】**

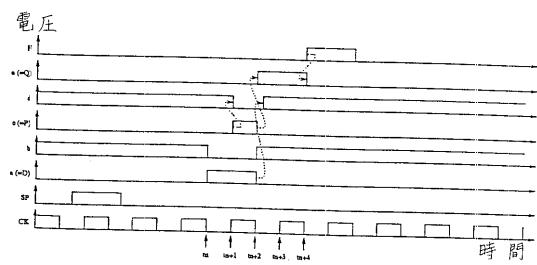

図 6 はスタートパルス S P およびクロックパルス C K を、第 4 のステージ 1 において生じる多様な波形と共に示す。第 4 のステージの初期条件は、信号 b および d がハイであり、信号 a、c、e および F がローであることである。

**【 0 0 3 5 】**

時間 t n において、先行ステージにより供給される信号 a はハイとなり、そしてトランジスタ M 1 および M 2 により形成されるインバータの出力がローとなる。トランジスタ M 3 および M 4 により形成されるトランスミッショングートはオンになり、そして信号 c はクロック信号になる。クロック信号は時間 t n と t n + 1 との間でローであり、そして信号 c は t n + 1 までローのままになる。10

**【 0 0 3 6 】**

時間 t n + 1 において、クロック信号 C K はハイとなり、そして信号 c が続き、トランジスタ M 6 はノード d を放電し、そして信号 d はローとなる。トランジスタ D 7 のゲートの 1 つはローに引き下げられるが、もう一方は回路ノード c に接続され、クロック信号がトランスミッショングートの立ち下がりを通過するまでハイのままになる。従って、信号 e は時間 t n + 2 までローのままになる。

**【 0 0 3 7 】**

時間 t n + 2 において、クロック信号はローとなり、信号 c が後に続く。トランジスタ D 7 のゲートの両方は、ここでローであり、そしてノード e はハイに引き上げられる。信号 e は、次のステージへの制御信号であり、信号 a の正確な位相遅延レプリカである。信号 e は、先行ステージのトランジスタ M 8 に相当するものにフィードバックされ、制御信号 a がローになるようにする。この結果として、回路ノード b および d はそれらのハイ状態へ戻る。20

**【 0 0 3 8 】**

時間 t n + 4 において、後に続くステージにおいて発生する信号 F は、トランジスタ M 8 をオンにする。制御信号 e はローとなり、後続のステージにおけるトランスミッショングートをオフに切り換える。

**【 0 0 3 9 】**

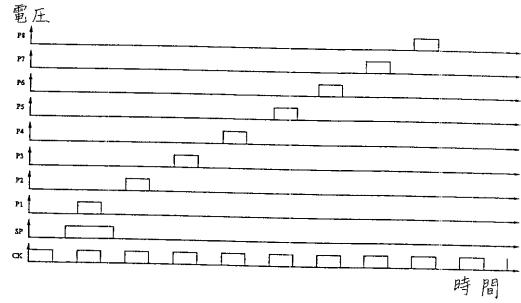

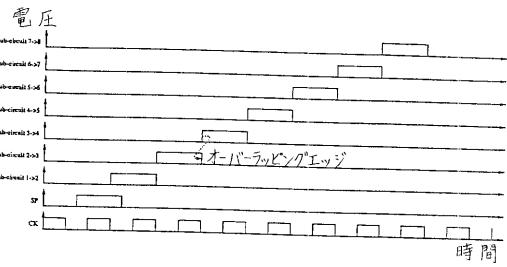

図 7 は、スタートパルス S P およびクロック信号 C K と共に、図 5 におけるクロックパルス発生器の出力 P 1 から P 8 の完全なセットを示す。出力信号は、クロック信号「ハイ位相」からコピーされ、単一のトランスミッショングートにより遅延した、逐次非オーバーラッピング正進行パルスである。ゲートクロックパルス P 1 から P 8 に加えて、制御信号 a および e はクロックパルス発生器からの出力として供給され得る。これらの信号は、図 8 に図示されており、その相補体はまた、ステージ 1 におけるインバータの出力として利用可能となり得る。これらの信号は互いにオーバーラップし（波形の図面に破線矢印で示されるように）、そしてより長い、またはより短い期間パルスが組合せ論理を用いて発生し得る。30

**【 0 0 4 0 】**

図 4 に示すステージにおけるいくつかのノードの初期条件は、回路が正常に働くように強制されなければならない。これは N 型および P 型ドレイン接続の静止平衡点を強制するように、トランジスタの関連サイズをスケールすることにより達成され得る。あるいは、リセットデバイスが後に述べるように提供され得る。しかし、この実施形態の動的回路動作であるために、ノードはトランジスタ電流漏れ (transistor current leakage) および容量注入 (capacitive injection) の結果、ドリフティングに影響されやすい。これはノイズマージンが減少したきれいでない信号を生じ得る。このことが起こることを防ぐために、後に述べるような部分的に静的な、または疑似静的な動作が適用され得る。40

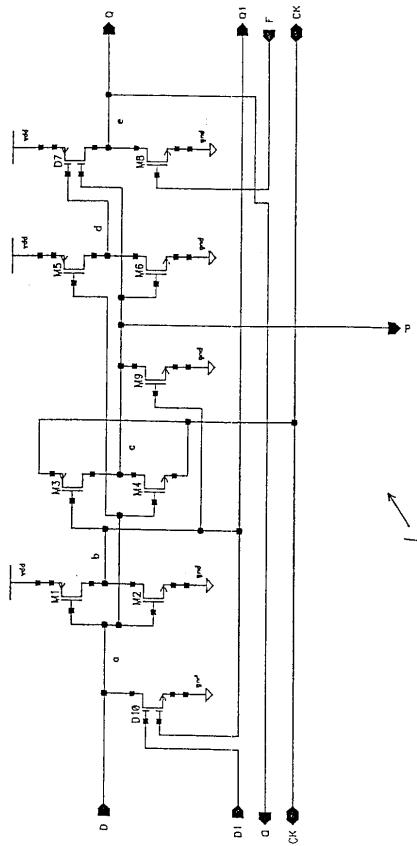

**【 0 0 4 1 】**

図 9 に示すクロックパルス発生器ステージ 1 は、部分的に静的である点で図 4 に示すもの50

とは異なる。特に、N型プルダウントランジスタM9は、トランスミッショングートの出力と、インバータの出力に接続されたゲートを備えた供給ラインgndとの間で接続される。トランジスタM9は、制御信号がローレベルの場合に、出力信号Pがローに引き下げるることを確実にする。従って、出力信号Pは、それらの正確なデフォルト値に固定されるか、あるいはクロック信号に従うかのどちらかである。ステージ1において生じる波形は、図6、7および8に示されるとおりである。

#### 【0042】

図10に示すクロックパルス発生器ステージ1は疑似静的であり、デュアルゲートトランジスタD10が入力Dと供給ラインgndとの間で接続される点で、図9に示すものとは異なる。あるいは、デュアルゲートトランジスタD10、2つの別々の单一ゲートトランジスタにより置き換えられ得る。トランジスタD10の第1のゲートは、回路ノードD1において先行するステージのインバータの出力に接続されるのに対し、第2ゲートは、回路ノードbにおいて図10に示すステージのインバータの出力を受信するように接続される。

10

#### 【0043】

トランジスタM1およびM2を備えるインバータのデフォルト状態は、入力信号aローおよび出力信号bハイを伴う。信号bは、トランジスタD10の第2のゲートにフィードバックされ、第2のゲートはオンになる。先行するステージにおけるインバータの出力のデフォルト状態はハイであり、そしてトランジスタD10の両方がオンになる。トランジスタM1およびM2を備えるインバータは、よってロー入力／ハイ出力状態でロックされる。先行ステージが作動すると、回路ノードD1に供給されるインバータからの信号はローとなり、そしてトランジスタD10の第1のゲートはオフに切り換えられる。信号aが状態を変える場合、1クロック相後に、トランジスタM1およびM2を備えるインバータはロックを解除され、出力信号bがそのデフォルトまたはハイ状態に戻るまで、解除されたままになる。従ってロックは、2つのクロック周期の間、開いている。

20

#### 【0044】

上記で述べたように、ステージがそのデフォルト状態にある場合、全ての回路ノードはアクティブに切り換えられる（すなわち静的である）。しかし、ステージが起動されると、ノードaおよびeは瞬間に浮動的であり、ひいては瞬間に動的である。従って、用語「疑似静的」がこれらのステージを説明するために適用されている。

30

#### 【0045】

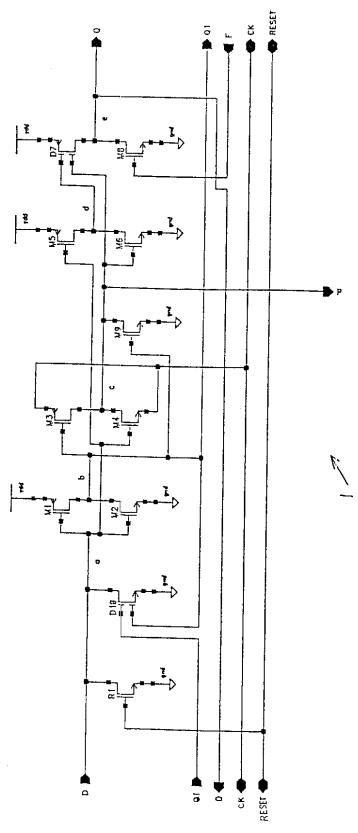

先に述べたように、スケーリング、または電力オンリセット技術を用いて、適切なトランジスタによる慎重な初期化が要求される。しかし、いくつかの回路ノードを、独立したリセット信号を用いて、それらの正確な初期論理状態に強制する必要があり得る。このタイプの配置が図11に図示されており、ここで初期ハイリセット信号RESETがステージ1に供給される。リセット信号は、プルダウンデバイスをトランジスタR1の形で、ステージ1の制御信号入力においてオンにする。従ってノードaは、初期リセットする間にロー状態になるよう強制され、そしてノードbからeはそれらの正確なデフォルト論理状態に置き換えられる。

40

#### 【0046】

図12は、ステージ1がどのように共に接続され、完全なクロックパルス発生器を形成するかを図示する。正確な動作のために、第1のステージ1の入力D1は、インバータ3を介してスタートパルスSPのインバースを受信する。再び、図11および12に示すクロックパルス発生器の動作中に存在する信号は、図6、7および8に示されるとおりである。

#### 【0047】

図13は、図11に示す相補的な回路実施例を表す。この回路は図11と比べると、トランジスタR1、M9およびD10がプルアップデバイスとして配置される点、全てのトランジスタが対応する図11のトランジスタとは反対の導電性タイプである点、ならびに供給ラインvddとgndとの間に供給されるトランジスタが反対の極性供給ラインに接続

50

されている点を除いて、実質的に同じである。動作は、図11のステージのものと類似しているが、しかし各ステージは、負の出力パルスNおよびRESET信号を生成し、スタートパルスSPは「アクティブロー」である。

#### 【0048】

高速度動作における制限要因の1つは、ノードeがデュアルゲートトランジスタD7により切り換えられ得る速度である。図13に示された相補的な実施例は、N型デュアルゲートトランジスタD7（これは通常、相当するP型デバイスよりも高い移動性を有し、従つてより速い可能性をもつ）を用いる。

#### 【0049】

図14は、クロックパルス発生器ステージ1を図示し、これはトランジスタM9が、インバータM1、M2の入力に接続されるプルアップデバイスを備え、トランジスタM3、M4により形成されるトランスマッシュゲートの出力が、トランジスタM11およびM12により形成されるインバータを介してトランジスタM6のゲート、そしてトランジスタD7の第2のゲートに接続される点で、図11に示すものとは異なる。インバータの存在は、（正確に測られるならば）ステージのロバストを改良し、最大動作周波数を増加し得る。これはなぜなら、先行するステージからの制御信号が、1つよりも多いクロックパルスがトランスマッシュゲートを通過すると、ステージの高速度障害モード（high-speed failure modes）の1つが起こるためである。トランジスタM11およびM12により形成されたインバータは、このパルスが小さければ、第2のグリッヂパルスをフィルタリングする。

10

20

#### 【0050】

図15は、スタートパルスSPおよびクロックパルスCKを、図14に示すタイプの縦続ステージ1を備えた、クロックパルス発生器の第4ステージにおいて起こる、多様な波形と共に示す。これらは図6に示す波形とほぼ類似しているが、いくつかの差異がある。例えば、信号cは反対の極性であり、インバータM11、M12の出力における信号fが追加されている。クロックパルスCKに関する全ての信号の位相調整は異なり、異なるよう位相されたスタートパルスSPが要求される。

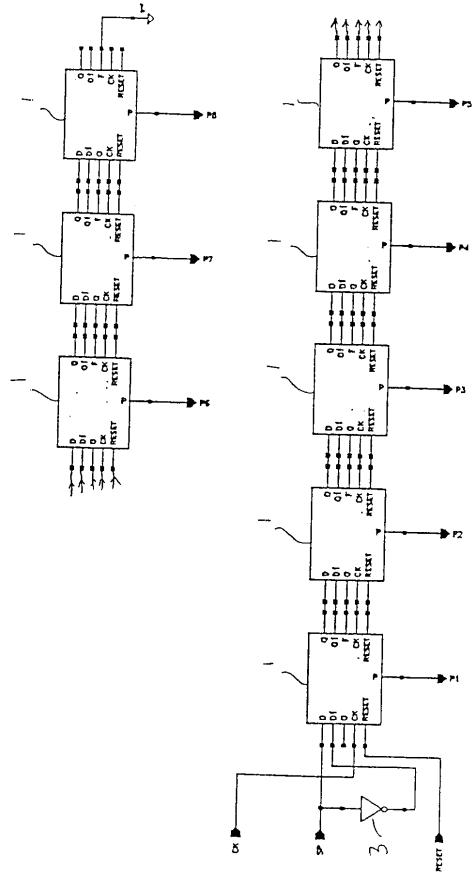

#### 【0051】

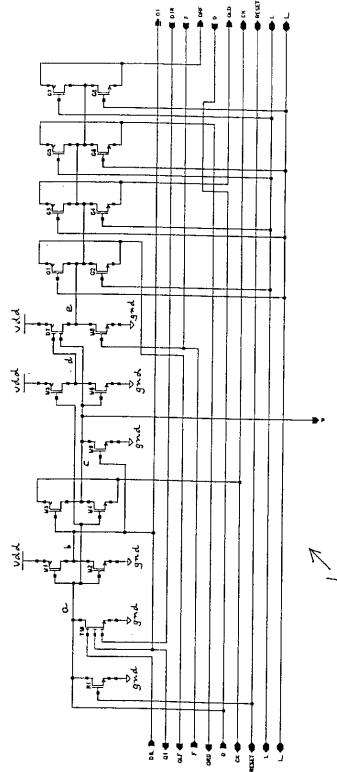

図16に示すステージ1は、それらが双方向に機能するように配置されている点で、それぞれ図11に示すものとは異なる。言い換えると、方向制御信号LおよびL-によって、クロックパルス発生器は、単一の論理ハイレベルを左から右へ、または右から左へ転送するシフトレジスタとして働き得る。これはトランスマッシュゲートの追加により、およびデュアルゲートトランジスタD10をトリプルゲートトランジスタT10（またはデュアルゲートトランジスタおよび直列に接続された单一ゲートトランジスタ、または直列に接続された3つの单一トランジスタ）と置き換えることにより達成される。

30

#### 【0052】

ステージ1は、トランジスタG1からG8のペアにより形成されるトランスマッシュゲートを備える。トランジスタペアのゲートは、方向制御ラインLおよびL-に接続される。トランスマッシュゲートの入力は、制御信号発生回路D7、M8からのゲート制御信号を受信するように共に接続される。トランスマッシュゲートG1、G2の出力は、右から左への動作のためにフィードバック出力QLFに接続される。トランスマッシュゲートG3、G4の出力は、左から右への動作のために出力クロックゲート制御信号ラインQLDに接続される。トランスマッシュゲートG5、G6の出力は、右から左への動作のために出力クロックゲート制御信号ラインQRDに接続される。トランスマッシュゲートG7、G8の出力は、左から右への動作のためにフィードバック出力QRFに接続される。トランジスタM8のゲートは、いずれかの方向における動作のためにフィードバック入力に接続される。インバータM1、M2の出力は、左および右の出力Q1、そしてトランジスタT10のゲートの1つに接続される。トランジスタT10の他のゲートは、左から入力D1Lに、右から入力D1Rに接続される。

40

#### 【0053】

50

ライン D は左または右からの入力クロックゲート制御信号を、ライン F は左または右からのフィードバック入力信号を、動作の電流方向に従って伝える。

#### 【0054】

方向制御信号 L がハイの場合、動作は左から右となる。トランスマッシュョンゲート G 1、G 2 および G 3、G 4 は、導電であり、一方トランスマッシュョンゲート G 5、G 6 および G 7、G 8 は、それらのハイインピーダンス状態にある。よって、ゲート制御信号は右ヘトランスマッシュョンゲート G 3、G 4 およびライン Q LD を介してバスされ、フィードバック信号は、左ヘトランスマッシュョンゲート G 1、G 2 およびライン Q LF を介してバスされる。反対に、方向制御信号 L がローの場合、動作は右から左となる。トランスマッシュョンゲートはそれらの反対の状態にあり、そしてゲート制御信号は左ヘゲート G 5、G 6 およびライン Q RD を介してバスされ、フィードバック信号は右ヘトランスマッシュョンゲート G 7、G 8 およびライン Q RF を介してバスされる。10

#### 【0055】

トリプルゲートトランジスタ T 10 は、どちらかの側にあるステージが起動したときには常に、インバータ M 1、M 2 の周りで作動するラッチが信号 D 1 L または D 1 R によりロックを解除されることを確実にする。このことは各ステージが双方向の様式において作動することを可能にする。なぜなら、それぞれが左または右からのクロックゲート制御信号を予測し得、適切に応答し得るためである。

#### 【0056】

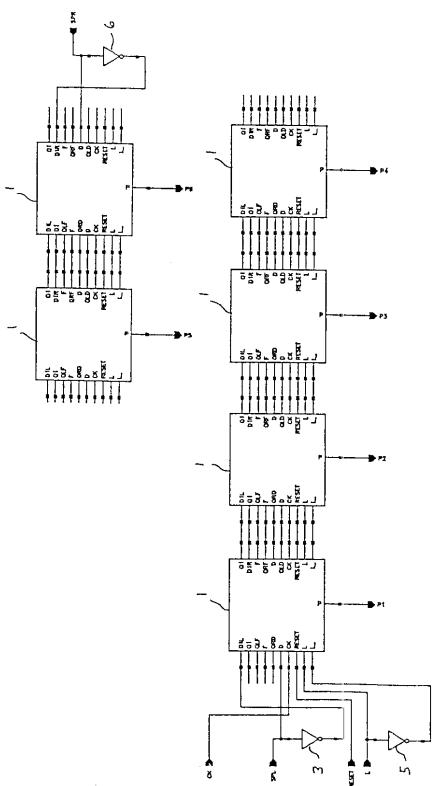

図 17 は、図 16 に示すタイプの 6 つのステージ 1 により形成されるクロックパルス発生器を図示する。上述されたインバータ 3 に加えてインバータ 5 が提供され、相補的方向制御信号 L - を方向制御信号 L から発生する。また、左スタートパルス S PL または右スタートパルス S PR も動作の方向によって提供され得、そしてインバータ 6 も右からの動作用に提供され、適切な静的 D 1 R を発生する。20

#### 【0057】

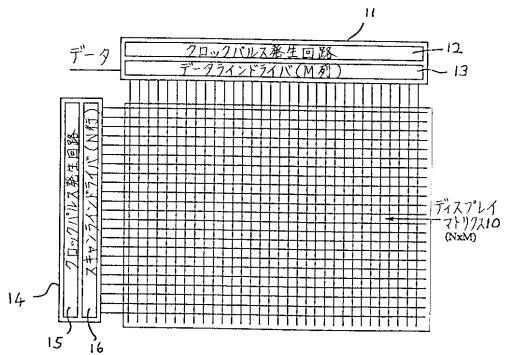

図 18 は、絵素（画素）の N 行 × M 列のディスプレイメトリクス 10 を備えるディスプレイ（例えば、液晶デバイスを備える空間光変調器の形において）を図示する。ディスプレイは、クロックパルス発生回路 12 およびデータラインドライバ 13 のセットを含むアドレス信号発生器 11 をさらに備える。クロックパルス発生回路 12 は、上述され、また図 4 から 17 に示される任意のタイプの発生器を備える。スキャン信号発生器 14 は、スキヤン信号を画素の行に供給し、クロックパルス発生回路 15 およびスキャンラインドライバ 16 のセットを備える。クロックパルス発生回路 15 は、上述され、また図 4 から 17 に示される任意のタイプの発生器を備える。クロックパルス発生器回路は、クロックパルスを回路 12 へは画素データ速度において、回路 15 へはラインデータ速度において生成する。30

#### 【0058】

クロック信号発生器は、クロック入力 CK および N 個のステージを備え、ここで N は 3 よりも大きい。各ステージは、トランスマッシュョンゲート M 3、M 4 を備え、これはクロック入力 CK からのクロックパルスを、先行するステージからの制御信号に応じてバスする。制御信号発生回路 M 5、M 6、D 7、M 8 は、先行するステージからの制御信号 a およびトランスマッシュョンゲート M 3、M 4 からのクロックパルスが終了した場合に、制御信号 e を後続のステージへ供給する。制御信号発生回路 M 5、M 6、D 7、M 8 は、後続のステージが制御信号 F を生成する場合に、制御信号 e を終了する。40

#### 【0059】

##### 【発明の効果】

本発明により、非常に高い最大動作周波数を有するクロックパルス発生器を提供することが可能である。特に、クロックパルスが 1 つのトランジスタのみを（トランスマッシュョンゲート出力が発生器の出力を構成する場合に、任意の外部負荷に加えて）一度に充電することが要求される発生器を提供することが可能である。また、クロック信号は完全にゲートされ得る。50

**【0060】**

第2に、トランジスタゲートによるクロック信号の容量性負荷が最小限化され得る。特に、ステージ毎に1つのゲートのみが充電されることとは別に、スイッチング状態にあるステージ内のトランジスタのゲートのみが充電される。これは結果的に電力消費量を削減し、特にクロック信号を伝える回路トラックのトラック抵抗において、より低い電力を損失することとなる。

**【図面の簡単な説明】**

【図1】公知であるタイプのシフトレジスタの2つのステージを示す回路図である。

【図2】図1に示すステージにおいて生じる波形を示す図である。

【図3】公知であるタイプのクロックパルス発生器を示すブロック回路図である。 10

【図4】本発明の実施形態を構成する動的クロックパルス発生器のステージを示す回路図である。

【図5】そのステージが図4に図示されるクロックパルス発生器を示すブロック図である。

【図6】図4および5に示すクロックパルス発生器において生じる波形を示す図である。

【図7】図5に示すクロックパルス発生器において生じる波形を示す図である。

【図8】図5に示すクロックパルス発生器において生じるさらなる波形を示す図である。

【図9】本発明の実施形態を構成する部分静的クロックパルス発生器のステージを示す回路図である。

【図10】本発明の実施形態を構成する擬似静的クロックパルス発生器のステージを示す回路図である。 20

【図11】リセット配置を備えて供給される図10に図示されるステージを示す回路図である。

【図12】そのステージが図11に図示されるクロックパルス発生器を示す図である。

【図13】図11に示すステージの相補的な型を示す回路図である。

【図14】よりロバストのある高速度動作のために改変された図11に示すタイプのステージを示す回路図である。

【図15】図14のクロックパルス発生器において生じる波形を示す図である。

【図16】一方向における動作のために改変された、図11に示すタイプのステージを示す回路図である。 30

【図17】そのステージが図16に図示されるクロックパルス発生器を示すブロック図である。

【図18】本発明の実施形態を構成する空間光変調器を示すブロック概略図である。

**【符号の説明】**

1 ステージ

3、5、6 インバータ

10 ディスプレイマトリクス

11 アドレス信号発生器

12 クロックパルス発生回路

13 データラインドライバ

14 スキャン信号発生器

15 クロックパルス発生回路

16 スキャンラインドライバ

40

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

審査官 石井 研一

(56)参考文献 特開平02-246511(JP,A)

特開平08-316802(JP,A)

特開平07-288447(JP,A)

特開2000-269787(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H03K 3/03