(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2009년04월10일

(11) 등록번호 10-0892501

(24) 등록일자 2009년04월01일

(51) Int. Cl.

G09G 3/36 (2006.01) G02F 1/133 (2006.01)

G09G 3/20 (2006.01)

(21) 출원번호 10-2007-0097470

(22) 출원일자 2007년09월27일

심사청구일자 2007년09월27일

(65) 공개번호 10-2008-0030508

(43) 공개일자 2008년04월04일

(30) 우선권주장

JP-P-2006-00264486 2006년09월28일 일본(JP)

JP-P-2007-00200434 2007년08월01일 일본(JP)

(56) 선행기술조사문헌

KR1020010006164 A

KR100523883 B1

KR100509986 B1

전체 청구항 수 : 총 11 항

심사관 : 이성현

(54) 액정 장치의 구동 회로, 구동 방법, 액정 장치 및 전자기기

### (57) 요약

본 발명은 액정을 사이에 유지하는 한 쌍의 기판에, 화소 용량을 구성하는 화소 전극 및 공통 전극을 구비하는 액정 장치에 있어서, 표시 품질의 저하를 억제하면서 소비 전력을 절감하는 것이다. 액정 장치(1)는 주사선 구동 회로(10), 데이터선 구동 회로(20), 제어 회로(30) 및 보조 회로(40)를 구비한다. 전(全) 화면 표시 모드 및 부분 표시 모드에 있어서의 표시 영역에서는, 제어 회로(30)에 의해 공통 전극(56)에 전압 VCOML 또는 전압 VCOMH를 공급한 후에, 데이터선 구동 회로(20)에 의해 데이터선(X)에 화상 신호를 공급한다. 부분 표시 모드에 있어서의 비표시 영역에서는, 제어 회로(30)에 의해 공통 전극(56)에 전압 VCOML을 공급함과 아울러, 보조 회로(40)에 의해 데이터선(X)에 전압 VCOML을 공급한다.

### 대표도

## 특허청구의 범위

### 청구항 1

제 1 기판과, 상기 제 1 기판에 대향 배치된 제 2 기판과, 상기 제 1 기판과 상기 제 2 기판 사이에 유지된 액정을 구비하고,

상기 제 1 기판은,

복수의 주사선과,

복수의 데이터선과,

상기 복수의 주사선에 대하여 1행마다 또는 복수행마다 마련된 복수의 공통 전극과,

상기 주사선과 상기 데이터선의 교차에 대응하여 마련되고, 각각은, 일단이 상기 데이터선에 접속되고, 또한 상기 주사선에 선택 전압이 인가되었을 때에 도통 상태로 되는 화소 스위칭 소자와, 일단이 상기 공통 전극에 접속되고, 타단이 상기 화소 스위칭 소자의 타단에 접속된 화소 용량을 포함하되, 상기 화소 용량의 유지 전압에 따른 계조로 되는 화소

를 갖고,

모든 화소를 이용하여 유효한 표시를 행하는 전체 화면 표시 모드와, 표시 영역에 관련된 주사선에 대응하는 화소만을 이용하여 유효한 표시를 행하고, 비표시 영역에 관련된 주사선에 대응하는 화소의 표시를 무효화시키는 부분 표시 모드 중 어느 것을 선택할 수 있는 액정 장치의 구동 회로로서,

상기 전체 화면 표시 모드의 경우 및 상기 부분 표시 모드의 경우, 상기 복수의 주사선에 상기 선택 전압을 순서대로 공급하는 주사선 구동 회로와,

상기 복수의 공통 전극에, 제 1 전압을, 또는 그 제 1 전압보다 고전위의 제 2 전압을 공급하는 제 1 제어 회로로서, 상기 전체 화면 표시 모드의 경우에 있어서 하나의 주사선에 상기 선택 전압이 인가되기 전, 및 상기 부분 표시 모드에 있어서 표시 영역에 관련된 하나의 주사선에 상기 선택 전압이 인가되기 전에, 그 하나의 주사선에 대응하는 공통 전극에 인가하는 전압을, 상기 제 1 전압 또는 상기 제 2 전압 중 어느 한쪽으로부터 다른 쪽으로 전환하고,

상기 부분 표시 모드에 있어서 비표시 영역에 관련된 주사선에 대응하는 공통 전극에 인가하는 전압을, 상기 제 1 전압 또는 상기 제 2 전압으로 유지하는 제 1 제어 회로와,

상기 전체 화면 표시 모드의 경우에 있어서 상기 복수의 주사선 중 어느 것에 선택 전압이 인가된 경우, 및 상기 부분 표시 모드에 있어서 상기 표시 영역에 관련된 주사선 중 어느 것에 선택 전압이 인가된 경우에,

상기 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 1 전압으로 전환되어 있었을 때, 상기 선택 전압이 인가된 주사선에 대응하는 화소에 대하여, 그 화소의 계조에 따른 전압으로서, 상기 제 1 전압보다 고전위로 한 정극성의 화상 신호를 상기 데이터선에 공급하고,

상기 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 2 전압으로 전환되어 있었을 때, 그 화소에 대하여, 그 화소의 계조에 따른 전압으로서, 상기 제 2 전압보다 저전위로 한 부극성의 화상 신호를 상기 데이터선에 공급하는 데이터선 구동 회로와,

상기 부분 표시 모드에 있어서 비표시 영역에 관련된 주사선 중 어느 것에 선택 전압이 인가된 경우에, 상기 선택 전압이 인가된 주사선에 대응하는 공통 전극에 인가한 전압을 상기 데이터선에 공급하는 제 2 제어 회로를 구비하는 것을 특징으로 하는 액정 장치의 구동 회로.

### 청구항 2

제 1 항에 있어서,

상기 데이터선 구동 회로는, 상기 주사선이 선택될 때마다, 상기 정극성의 화상 신호와 상기 부극성의 화상 신호를 교대로 전환하는 것을 특징으로 하는 액정 장치의 구동 회로.

### 청구항 3

제 1 항에 있어서,

상기 제 1 제어 회로는 래치 회로 및 선택 회로를 갖고,

상기 래치 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 래치 회로를 갖고,

상기 단위 래치 회로의 각각은, 상기 데이터선 구동 회로에 대하여 화상 신호의 정극성 및 부극성을 지시하는 극성 신호를, 상기 공통 전극에 대응하는 주사선에 대하여 서로 인접하는 2행의 주사선 중 어느 한쪽에 상기 선택 전압이 인가되었을 때에 래치하고,

상기 선택 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 선택 회로를 포함하고,

상기 전체 화면 표시 모드에 있어서의 모든 단위 선택 회로, 및 상기 부분 표시 모드에 있어서의 상기 표시 영역에 관련된 주사선에 대응하는 공통 전극에 따른 단위 선택 회로는, 상기 래치 회로에 의해 래치된 극성 신호에 따라 상기 제 1 또는 제 2 전압 중 어느 것을 상기 공통 전극에 인가하고,

상기 부분 표시 모드에 있어서의 상기 비표시 영역에 관련된 주사선에 대응하는 공통 전극에 따른 단위 선택 회로는, 상기 제 1 전압 또는 그 제 1 전압보다 고전위의 제 2 전압을, 상기 공통 전극에 인가하는

것을 특징으로 하는 액정 장치의 구동 회로.

### 청구항 4

제 1 항에 있어서,

상기 제 1 제어 회로는 래치 회로 및 선택 회로를 갖고,

상기 래치 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 래치 회로를 갖고,

상기 단위 래치 회로의 각각은 상기 데이터선 구동 회로에 대하여 화상 신호의 정극성 및 부극성을 지시하는 극성 신호를, 상기 공통 전극에 대응하는 주사선보다 1행 전의 주사선에 상기 선택 전압이 인가되었을 때에 래치하고,

상기 선택 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 선택 회로를 포함하고,

상기 전체 화면 표시 모드에 있어서의 모든 단위 선택 회로, 및 상기 부분 표시 모드에 있어서의 상기 표시 영역에 관련된 주사선에 대응하는 공통 전극에 따른 단위 선택 회로는, 상기 래치 회로에 의해 래치된 극성 신호에 따라 상기 제 1 또는 제 2 전압 중 어느 것을 상기 공통 전극에 인가하며,

상기 부분 표시 모드에 있어서의 상기 비표시 영역에 관련된 주사선에 대응하는 공통 전극에 따른 단위 선택 회로는, 상기 제 1 전압 또는 그 제 1 전압보다 고전위의 제 2 전압을, 상기 공통 전극에 인가하는

것을 특징으로 하는 액정 장치의 구동 회로.

### 청구항 5

제 1 항에 있어서,

상기 제 1 제어 회로는 래치 회로 및 선택 회로를 갖고,

상기 래치 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 래치 회로를 갖고,

상기 단위 래치 회로의 각각은 상기 데이터선 구동 회로에 대하여 화상 신호의 정극성 및 부극성을 지시하는 극성 신호를, 상기 공통 전극에 대응하는 주사선보다 1행 전의 주사선에 상기 선택 전압이 인가되었을 때에 래치하고,

상기 선택 회로는 미리 정해진 표시 영역에 관련된 주사선에 대응하는 공통 전극을 따라 마련되는 제 1 단위 선택 회로와, 미리 정해진 비표시 영역에 관련된 주사선에 대응하는 공통 전극을 따라 마련되는 제 2 단위 선택 회로를 갖고,

상기 제 1 단위 선택 회로는 상기 래치 회로에 의해 래치된 극성 신호에 따라 상기 제 1 또는 제 2 전압 중 어

느 것을 상기 공통 전극에 인가하고,

상기 제 2 단위 선택 회로는, 상기 전체 화면 표시 모드의 경우에, 상기 래치 회로에 의해 래치된 극성 신호에 따라 상기 제 1 또는 제 2 전압 중 어느 것을 상기 공통 전극에 인가하고, 상기 부분 표시 모드의 경우에, 상기 제 1 전압 또는 그 제 1 전압보다 고전위의 제 2 전압을 상기 공통 전극에 인가하는

것을 특징으로 하는 액정 장치의 구동 회로.

#### 청구항 6

복수의 주사선과,

복수의 데이터선과,

상기 복수의 주사선에 대하여 1행마다 또는 복수행마다 마련된 복수의 공통 전극과,

상기 주사선과 상기 데이터선의 교차에 대응하여 마련되고, 각각은, 일단이 상기 데이터선에 접속되고, 또한 상기 주사선에 선택 전압이 인가되었을 때에 도통 상태로 되는 화소 스위칭 소자와, 일단이 상기 공통 전극에 접속되고, 타단이 상기 화소 스위칭 소자의 타단에 접속된 화소 용량을 포함하되, 상기 화소 용량의 유지 전압에 따른 계조로 되는 화소

를 갖고,

상기 복수의 주사선 중 일부의 주사선에 관련된 화소에 표시를 시키는 액정 장치의 구동 회로로서,

상기 복수의 주사선을 선택하는 주사선 구동 회로와,

상기 복수의 공통 전극을 구동하는 제 1 제어 회로와,

선택된 주사선에 관련된 화소에 대하여, 그 화소의 계조에 따른 전압의 데이터 신호를, 데이터선을 거쳐 공급하는 데이터선 구동 회로와,

선택된 주사선에 관련된 화소에 대하여, 제 1 전압, 및 상기 제 1 전압보다 고전위의 제 2 전압 중 어느 하나를 공급하는 제 2 제어 회로

를 구비하고,

상기 일부의 주사선이 선택되었을 때에는, 상기 제 1 제어 회로는, 선택된 주사선에 관련된 화소에 대응하는 공통 전극의 전압을, 상기 제 1 전압, 및 상기 제 2 전압 중 어느 한쪽으로부터 다른 쪽으로 전환하고, 또한 상기 데이터선 구동 회로가, 선택된 주사선에 관련된 화소에 대하여 그 화소의 계조에 따른 전압의 데이터 신호를 공급하고,

상기 일부의 주사선 이외의 주사선이 선택되었을 때에는, 상기 제 1 제어 회로는, 선택된 주사선에 관련된 화소에 대응하는 공통 전극에 상기 제 1 전압 및 상기 제 2 전압 중 어느 한쪽을 공급하고, 또한 상기 제 2 제어 회로가, 선택된 주사선에 관련된 화소에 대하여 상기 제 1 전압, 및 상기 제 2 전압 중 어느 한쪽을 공급하는 것

을 특징으로 하는 액정 장치의 구동 방법.

#### 청구항 7

제 1 기판과, 상기 제 1 기판에 대향 배치된 제 2 기판과, 상기 제 1 기판과 상기 제 2 기판 사이에 유지된 액정을 구비하고,

상기 제 1 기판은,

복수의 주사선과,

복수의 데이터선과,

상기 복수의 주사선에 대하여 1행마다 또는 복수행마다 마련된 복수의 공통 전극과,

상기 주사선과 상기 데이터선의 교차에 대응하여 마련되고, 각각은, 일단이 상기 데이터선에 접속되고, 또한 상기 주사선에 선택 전압이 인가되었을 때에 도통 상태로 되는 화소 스위칭 소자와, 일단이 상기 공통 전극에 접속되고, 타단이 상기 화소 스위칭 소자의 타단에 접속된 화소 용량을 포함하되, 상기 화소 용량의 유지 전압에

따른 계조로 되는 화소

를 갖고,

모든 화소를 이용하여 유효한 표시를 행하는 전체 화면 표시 모드와, 표시 영역에 관련된 주사선에 대응하는 화소만을 이용하여 유효한 표시를 행하고, 비표시 영역에 관련된 주사선에 대응하는 화소의 표시를 무효화시키는 부분 표시 모드 중 어느 것을 선택할 수 있고,

상기 전체 화면 표시 모드 및 상기 부분 표시 모드에 있어서, 상기 복수의 주사선에 상기 선택 전압을 공급하는 액정 장치의 구동 방법으로서,

전체 화면 표시 모드에 있어서,

하나의 주사선에 상기 선택 전압이 인가되기 전에, 상기 하나의 주사선에 대응하는 공통 전극에 인가하는 전압을, 제 1 전압 또는 그 제 1 전압보다 고전위의 제 2 전압 중 어느 한쪽으로부터 다른쪽으로 전환하고,

하나의 주사선에 상기 선택 전압이 인가된 경우에,

상기 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 1 전압으로 전환되었을 때, 상기 선택 전압이 인가된 주사선에 대응하는 화소에 대하여, 그 화소의 계조에 따른 전압으로서, 상기 제 1 전압보다 고전위로 한 정극성의 화상 신호를 상기 데이터선에 공급하고,

상기 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 2 전압으로 전환되었을 때, 그 화소에 대하여, 그 화소의 계조에 따른 전압으로서, 상기 제 2 전압보다 저전위로 한 부극성의 화상 신호를 상기 데이터선에 공급하며,

부분 표시 모드에 있어서, 상기 표시 영역에 대해서는,

상기 표시 영역에 관련된 하나의 주사선에 상기 선택 전압이 인가되기 전에, 상기 하나의 주사선에 대응하는 공통 전극에 인가하는 전압을, 상기 제 1 전압 또는 상기 제 2 전압의 한쪽으로부터 다른쪽으로 전환하고,

하나의 주사선에 상기 선택 전압이 인가된 경우에, 상기 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 1 전압으로 전환되었을 때, 상기 선택 전압이 인가된 주사선에 대응하는 화소에 대하여, 그 화소의 계조에 따른 전압으로서, 상기 제 1 전압보다 고전위로 한 정극성의 화상 신호를 상기 데이터선에 공급하고,

상기 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 2 전압으로 전환되었을 때, 그 화소에 대하여, 그 화소의 계조에 따른 전압으로서, 상기 제 2 전압보다 저전위로 한 부극성의 화상 신호를 상기 데이터선에 공급하며,

부분 표시 모드에 있어서, 상기 비표시 영역에 대해서는,

상기 비표시 영역에 관련된 하나의 주사선에 대응하는 공통 전극에 인가하는 전압을, 상기 제 1 전압 또는 상기 제 2 전압으로 유지하고,

상기 하나의 주사선에 선택 전압이 인가된 경우에, 상기 하나의 주사선에 대응하는 공통 전극에 인가한 전압을 상기 데이터선에 공급하는

것을 특징으로 하는 액정 장치의 구동 방법.

## 청구항 8

제 1 기판과, 상기 제 1 기판에 대향 배치된 제 2 기판과, 상기 제 1 기판과 상기 제 2 기판 사이에 유지된 액정을 구비하고,

상기 제 1 기판은,

복수의 주사선과,

복수의 데이터선과,

상기 복수의 주사선에 대하여 1행마다 또는 복수행마다 마련된 복수의 공통 전극과,

상기 주사선과 상기 데이터선과의 교차에 대응하여 마련되고, 각각은, 일단이 상기 데이터선에 접속되고, 또한 상기 주사선에 선택 전압이 인가되었을 때에 도통 상태로 되는 화소 스위칭 소자와, 일단이 상기 공통 전극에

접속되고, 타단이 상기 화소 스위칭 소자의 타단에 접속된 화소 용량을 포함하되, 상기 화소 용량의 유지 전압에 따른 계조로 되는 화소

를 갖고,

모든 화소를 이용하여 유효한 표시를 행하는 전체 화면 표시 모드와, 표시 영역에 관련된 주사선에 대응하는 화소만을 이용하여 유효한 표시를 행하고, 비표시 영역에 관련된 주사선에 대응하는 화소의 표시를 무효화시키는 부분 표시 모드 중 어느 것을 선택할 수 있는 액정 장치로서,

상기 전체 화면 표시 모드의 경우 및 상기 부분 표시 모드의 경우, 상기 복수의 주사선에 상기 선택 전압을 공급하는 주사선 구동 회로와,

상기 복수의 공통 전극에, 제 1 전압 또는 그 제 1 전압보다 고전위의 제 2 전압을 공급하는 제 1 제어 회로로서, 상기 전체 화면 표시 모드의 경우에 있어서 하나의 주사선에 상기 선택 전압이 인가되기 전, 및 상기 부분 표시 모드에 있어서 표시 영역에 관련된 하나의 주사선에 상기 선택 전압이 인가되기 전에, 상기 하나의 주사선에 대응하는 공통 전극에 인가하는 전압을, 상기 제 1 전압 및 상기 제 2 전압 중 어느 한쪽으로부터 다른쪽으로 전환하고,

상기 부분 표시 모드에 있어서, 비표시 영역에 관련된 주사선에 대응하는 공통 전극에 인가하는 전압을, 상기 제 1 전압 또는 상기 제 2 전압으로 유지하는 제 1 제어 회로와,

상기 전체 화면 표시 모드의 경우에 있어서 상기 복수의 주사선 중 어느 것에 선택 전압이 인가된 경우, 및 상기 부분 표시 모드에 있어서 상기 표시 영역에 관련된 주사선 중 어느 것에 선택 전압이 인가된 경우에,

상기 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 1 전압으로 전환되어 있었을 때, 상기 선택 전압이 인가된 주사선에 대응하는 화소에 대하여, 그 화소의 계조에 따른 전압으로서, 상기 제 1 전압보다 고전위로 한 정극성의 화상 신호를 상기 데이터선에 공급하며,

상기 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 2 전압으로 전환되어 있었을 때, 그 화소에 대하여, 그 화소의 계조에 따른 전압으로서, 상기 제 2 전압보다 저전위로 한 부극성의 화상 신호를 상기 데이터선에 공급하는 데이터선 구동 회로와,

상기 부분 표시 모드에 있어서 비표시 영역에 관련된 주사선 중 어느 것에 선택 전압이 인가된 경우에, 상기 선택 전압이 인가된 주사선에 대응하는 공통 전극에 인가한 전압을 상기 데이터선에 공급하는 제 2 제어 회로를 구비하는 것을 특징으로 하는 액정 장치.

## 청구항 9

제 8 항에 있어서,

상기 복수의 공통 전극은, 상기 복수의 주사선의 1행씩에 대응하고, 또한 상기 주사선의 연장 방향을 따라 화소 전극의 1행분에 걸쳐 대향하도록 마련되며,

상기 공통 전극의 각각에 보조 공통선이, 상기 주사선 및 상기 공통 전극의 연장 방향을 따라 각각 마련되고, 또한 1조의 공통 전극 및 보조 공통선은, 화소마다 마련된 콘택트 배선을 통해 서로 접속된 것을 특징으로 하는 액정 장치.

## 청구항 10

복수의 주사선과,

복수의 데이터선과,

상기 복수의 주사선에 대하여 1행마다 또는 복수행마다 마련된 복수의 공통 전극과,

상기 주사선과 상기 데이터선의 교차에 대응하여 마련되고, 각각은, 일단이 상기 데이터선에 접속되고, 또한 상기 주사선에 선택 전압이 인가되었을 때에 도통 상태로 되는 화소 스위칭 소자와, 일단이 상기 공통 전극에 접속되고, 타단이 상기 화소 스위칭 소자의 타단에 접속된 화소 용량을 포함하되, 상기 화소 용량의 유지 전압에 따른 계조로 되는 화소

를 갖고,

상기 복수의 주사선 중 일부의 주사선에 따른 화소에 표시를 시키는 것이 가능한 액정 장치로서,

상기 복수의 주사선을 선택하는 주사선 구동 회로와,

상기 복수의 공통 전극을 구동하는 제 1 제어 회로와,

선택된 주사선에 관련된 화소에 대하여, 그 화소의 계조에 따른 전압의 데이터 신호를, 데이터선을 거쳐 공급하는 데이터선 구동 회로와,

선택된 주사선에 관련된 화소에 대하여, 제 1 전압, 및 상기 제 1 전압보다 고전위의 제 2 전압 중 어느 하나를 공급하는 제 2 제어 회로

를 구비하고,

상기 일부의 주사선이 선택되었을 때에는, 상기 제 1 제어 회로는, 선택된 주사선에 관련된 화소에 대응하는 공통 전극의 전압을, 상기 제 1 전압, 및 상기 제 2 전압 중 어느 한쪽으로부터 다른 쪽으로 전환하고, 또한 상기 데이터선 구동 회로가, 선택된 주사선에 관련된 화소에 대하여 그 화소의 계조에 따른 전압의 데이터 신호를 공급하고,

상기 일부의 주사선 이외의 주사선이 선택되었을 때에는, 상기 제 1 제어 회로는, 선택된 주사선에 관련된 화소에 대응하는 공통 전극에 상기 제 1 전압 및 상기 제 2 전압 중 어느 한쪽을 공급하고, 또한 상기 제 2 제어 회로가, 선택된 주사선에 관련된 화소에 대하여 상기 제 1 전압, 및 상기 제 2 전압 중 어느 한쪽을 공급하는 것을 특징으로 하는 액정 장치.

## 청구항 11

청구항 8 내지 청구항 10 중 어느 한 항에 기재된 액정 장치를 구비하는 것을 특징으로 하는 전자기기.

## 명세서

### 발명의 상세한 설명

#### 기술분야

<1> 본 발명은 한쪽의 기판에 화소 전극 및 공통 전극을 마련한 액정 장치에 있어서, 표시 품질의 향상을 도모하는 기술에 관한 것이다.

#### 배경기술

<2> 종래부터 액정을 이용하여 화상을 표시하는 액정 장치가 알려져 있다. 이 액정 장치는, 예컨대, 액정 패널과 이 액정 패널에 대향 배치된 백라이트를 구비한다. 이 중 액정 패널은 한 쌍의 기판과, 이들 한 쌍의 기판 사이에 액정을 유지한 구성이며, 복수의 주사선과, 복수의 데이터선의 교차에 대응하여 화소가 마련된 구성으로 되어있다. 또, 복수의 주사선 각각에 대응하도록 용량선이 마련된다.

<3> 각 주사선과 각 데이터선의 교차 부분에는 화소가 마련된다. 각 화소는 화소 전극 및 공통 전극으로 이루어지는 화소 용량과, 박막 트랜지스터(Thin Film Transistor, 이후 단지 TFT라고 표기함)와, 한쪽 전극이 용량선에 접속되고 다른쪽 전극이 화소 전극에 접속된 축적 용량을 구비한다. 이 화소는 매트릭스 형상으로 복수 배열되어 표시 영역을 형성한다. TFT의 게이트에는 주사선이 접속되고, TFT의 소스에는 데이터선이 접속되며, TFT의 드레인에는 화소 전극 및 축적 용량의 다른쪽 전극이 접속되어 있다.

<4> 또한, 상술한 액정 패널에는, 복수의 주사선을 각각 구동하는 주사선 구동 회로와, 복수의 데이터선을 각각 구동하는 데이터선 구동 회로와, 복수의 용량선을 각각 구동하는 용량선 구동 회로가 마련된다. 이 중, 주사선 구동 회로는 주사선을 선택하는 선택 전압을 복수의 주사선에 순차 공급한다. 예컨대, 어떤 주사선에 선택 전압을 공급하면, 이 주사선에 접속된 TFT가 모두 온 상태로 되어, 이 주사선에 관한 화소가 모두 선택된다. 또한, 데이터선 구동 회로는, 주사선이 선택되었을 때에, 화상 신호를 복수의 데이터선에 공급하고, 온 상태의 TFT를 통해, 이 화상 신호에 근거하는 화상 전압을 화소 전극에 기입한다.

- <5> 여기서, 데이터선 구동 회로는, 공통 전극의 전압보다 전위가 높은 전압(배경 기술의 항목에서 정극성이라 함)의 화상 신호를 데이터선에 공급하고, 이 정극성의 화상 신호에 근거하는 화상 전압을 화소 전극에 기입하는 정극성 기입과, 공통 전극의 전압보다 전위가 낮은 전압(배경 기술의 항목에서 부극성이라 함)의 화상 신호를 데이터선에 공급하고, 이 부극성의 화상 신호에 근거하는 화상 전압을 화소 전극에 기입하는 부극성 기입을 소정 기간마다 교대로 실행한다.

- <6> 또, 용량선 구동 회로는 소정의 전압을 각 용량선에 공급한다.

- <7> 이 액정 장치는 다음과 같이 동작한다.

- <8> 즉, 주사선에 선택 전압을 순차 공급하는 것, 어떤 주사선에 접속된 TFT를 모두 온 상태로 하여, 이 주사선에 관한 화소를 모두 선택한다. 그리고, 이들 화소의 선택에 동기하여, 데이터선에 화상 신호를 공급한다. 그렇게 하면, 선택한 모든 화소에, 온 상태의 TFT를 거쳐 화상 신호가 공급되고, 이 화상 신호에 근거하는 화상 전압이 화소 전극에 기입된다.

- <9> 화소 전극에 화상 전압이 기입되면, 화소 전극과 공통 전극의 전위차에 의해, 액정에 구동 전압이 인가된다. 액정에 구동 전압이 인가되면, 액정의 배향이나 질서가 변화되고, 액정을 투과하는 백라이트로부터의 광이 변화되어, 계조 표시가 행해진다. 또, 액정에 인가되는 구동 전압은, 축적 용량에 의해, 화상 전압이 기입되는 기간보다 3자리수 정도 긴 기간에 걸쳐 유지된다.

- <10> 그런데, 이러한 액정 장치는, 예컨대, 휴대기기에 이용되지만, 휴대기기에서는, 최근, 소비 전력의 절감이 요청되고 있다. 그래서, 화상 전압을 화소 전극에 기입한 후에, TFT를 오프 상태로 함과 아울러 용량선의 전압을 변동시킴으로써, 소비 전력을 절감할 수 있는 액정 장치가 제안되어 있다(예컨대, 특히 문헌 1 참조).

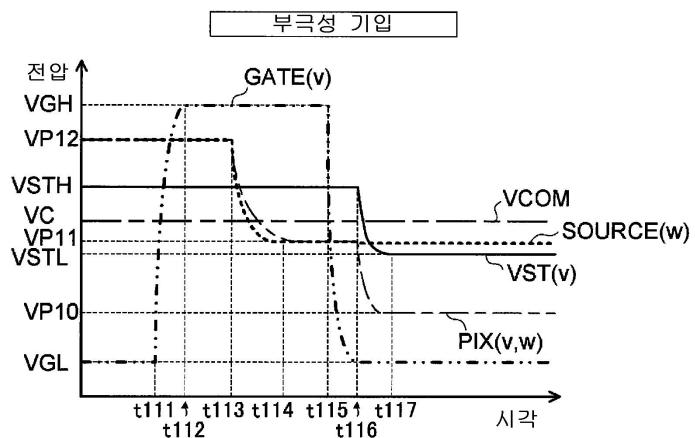

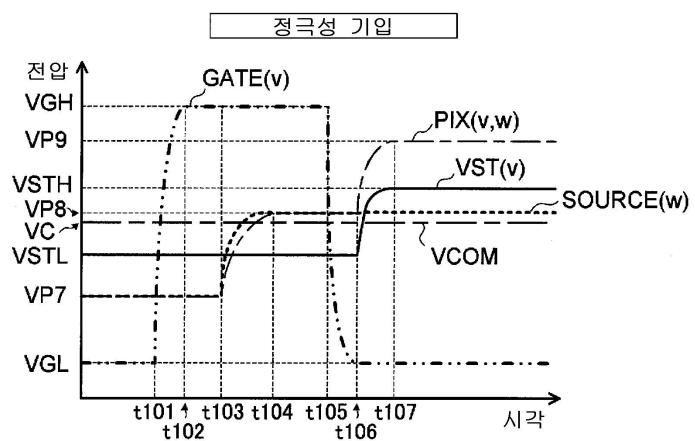

- <11> 이 기술과 같이, 용량선의 전압을 변동시키는, 종래예에 관한 액정 장치의 동작에 대하여, 도 32 및 도 33을 참조하여 설명한다. 종래예에 관한 액정 장치에 있어서, 화소에 대하여 전압 기입을 하는 경우에, 도 32는 정극성 기입 시의 각 부(部) 전압의 파형을 나타내는 도면이고, 도 33은 부극성 기입 시의 각 부 전압의 파형을 나타내는 도면이다.

- <12> 여기서, 종래예에 관한 액정 장치는, 예컨대, 320행의 주사선 및 용량선과, 240열의 데이터선을 갖는 것으로 하면, 도 32 및 도 33에서, GATE(v)는 320행의 주사선 중, v행 째( $v$ 는  $1 \leq v \leq 320$ 을 만족하는 정수) 주사선의 전압을 나타내고, VST(v)는 320행의 용량선 중, v행 째 용량선의 전압을 나타낸다. 또한, SOURCE(w)는 240열의 데이터선 중, w열 째( $w$ 는,  $1 \leq w \leq 240$ 을 만족하는 정수) 데이터선의 전압을 나타낸다. 또한, PIX(v, w)는 v행 째 주사선과, w열 째 데이터선의 교차에 대응하여 마련된 v행 w열의 화소가 구비하는 화소 전극의 전압을 나타내고, VCOM은 각 화소에 대하여 공통으로 마련된 공통 전극의 전압을 나타낸다.

- <13> 우선, 도 32의 정극성 기입 시의 시각 t101에서, 주사선 구동 회로가 v행 째 주사선에 선택 전압을 공급하면, v행 째 주사선의 전압 GATE(v)는 상승하여, 시각 t102에서는 전압 VGH로 된다. 이에 따라, v행 째 주사선에 접속된 TFT가 모두 온 상태로 된다.

- <14> 시각 t103에서, 데이터선 구동 회로가 w열 째 데이터선에 정극성의 화상 신호를 공급하면, w열 째 데이터선의 전압 SOURCE(w)는 상승하여, 시각 t104에서는 전압 VP8로 된다.

- <15> w열 째 데이터선의 전압 SOURCE(w)는, 정극성의 화상 신호에 근거하는 화상 전압으로서, v행 째 주사선에 접속된 온 상태의 TFT를 거쳐, v행 w열의 화소가 구비하는 화소 전극에 기입된다. 이 때문에, v행 w열의 화소가 구비하는 화소 전극의 전압 PIX(v, w)는 상승하여, 시각 t104에서는 w열 째 데이터선의 전압 SOURCE(w)와 동 전위인 전압 VP8로 된다.

- <16> 시각 t105에서, 주사선 구동 회로가 v행 째 주사선에 선택 전압을 공급하는 것을 정지하고, 대신 비선택 전압을 인가하면, v행 째 주사선의 전압 GATE(v)는 저하하여, 시각 t106에서 전압 VGL로 된다. 이에 따라, v행 째 주사선에 접속된 TFT가 모두 오프 상태로 된다.

- <17> 시각 t106에서, 용량선 구동 회로가 v행 째 용량선에 소정의 전압을 공급하면, v행 째 용량선의 전압 VST(v)는 상승하여, 시각 t107에서는 전압 VSTH로 된다. v행 째 용량선의 전압 VST(v)이 상승하면, v행 째 용량선에 관한 모든 화소에서는, 이 상승한 전압에 상당하는 전하가 축적 용량과 화소 용량 사이에서 분배된다. 이 때문에, v행 w열의 화소가 구비하는 화소 전극의 전압 PIX(v, w)는 재차 상승하여, 시각 t107에서 전압 VP9로 된다.

- <18> 이와 같이 종래예에 관한 액정 장치에서는, 정극성 기입에서, 정극성의 화상 신호에 근거하는 화상 전압을 화소 전극에 기입한 후에, 용량선의 전압을 상승시키므로, 화소 전극의 전압은 화상 전압에 의해 상승한 전압과, 용량선의 전압 변화에 의해 재상승한 전압을 합친 만큼 상승한다.

- <19> 다음에, 도 33을 이용하여, 부극성 기입 시의 동작에 대하여 설명한다.

- <20> 시각 t111에서, 주사선 구동 회로가 v행 째 주사선에 선택 전압을 공급하는, v행 째 주사선의 전압 GATE(v)는 상승하여, 시각 t112에서는 전압 VGH로 된다. 이에 따라, v행 째 주사선에 접속된 TFT가 모두 온 상태로 된다.

- <21> 시각 t113에서, 데이터선 구동 회로가 w열 째 데이터선에 부극성의 화상 신호를 공급하면, w열 째 데이터선의 전압 SOURCE(w)는 저하하여, 시각 t114에서는 전압 VP11로 된다.

- <22> w열 째 데이터선의 전압 SOURCE(w)는 부극성의 화상 신호에 근거하는 화상 전압으로서, v행 째 주사선에 접속된 온 상태의 TFT를 거쳐, v행 w열의 화소가 구비하는 화소 전극에 기입된다. 이 때문에, 화소 전극의 전압 PIX(v, w)는 저하하여, 시각 t114에서는 w열 째 데이터선의 전압 SOURCE(w)과 동(同) 전위인 전압 VP11로 된다.

- <23> 시각 t115에서, 주사선 구동 회로가 v행 째 주사선에 선택 전압을 공급하는 것을 정지하여, 비선택 전압을 인가하면, v행 째 주사선의 전압 GATE(v)는 저하하여, 시각 t116에서 전압 VGL로 된다. 이에 따라, v행 째 주사선에 접속된 TFT가 모두 오프 상태로 된다.

- <24> 시각 t116에서, 용량선 구동 회로가 v행 째 용량선에 소정의 전압을 공급하면, v행 째 용량선의 전압 VST(v)는 저하하여, 시각 t117에서는 전압 VSTL로 된다.

- <25> v행 째 용량선의 전압 VST(v)이 저하하면, v행 째 용량선에 관한 모든 화소에서는, 이 저하한 전압에 상당하는 전하가 축적 용량과 화소 용량 사이에서 분배된다. 이 때문에, v행 w열의 화소가 구비하는 화소 전극의 전압 PIX(v, w)는 재차 저하하여, 시각 t117에서는 전압 VP10으로 된다.

- <26> 이와 같이 종래예에 따른 액정 장치에서는, 부극성 기입에서, 부극성의 화상 신호에 근거하는 화상 전압을 화소 전극에 기입한 후에, 용량선의 전압을 저하시키므로, 화소 전극의 전압은 화상 전압에 의해 저하한 전압과, 용량선의 전압 변화에 의해 재차 저하한 전압을 합친 만큼 저하한다.

- <27> 종래예에 따른 액정 장치에서는, 화상 전압을 화소 전극에 기입한 후에, 용량선의 전압을 변동시킴으로써, 화상 전압의 진폭을 작게 하여도, 공통 전극의 전압과 화소 전극의 전압의 전위차를 크게 할 수 있다. 따라서 액정에 인가하는 구동 전압의 진폭을 확보하여 표시 품질의 저하를 억제하면서, 화상 전압의 진폭을 작게 하여 소비 전력을 절감할 수 있다.

- <28> (특허 문현 1) 일본 공개 특허 공보 제2002-196358호

### 발명의 내용

#### 해결 하고자하는 과제

- <29> 상술한 종래예에 따른 액정 장치에서는, 용량선의 전압을 변동시켜, 축적 용량과 화소 용량 사이에서 전하를 이동시킴으로써 화소 전극의 전압을 변동시킨다. 이 때문에, 축적 용량에 특성 편차가 발생하면, 축적 용량과 화소 용량 사이에서 이동하는 전하의 양에 영향을 미친다. 따라서, 각 화소 전극에 동일한 화상 전압을 기입하여도, 각 화소 전극의 전압이 서로 다르고, 각 화소의 밝기가 균일하지 않게 되어, 표시 품질이 저하하는 경우가 있었다.

- <30> 또한, 상술한 종래예에 따른 액정 장치에서는, 용량선의 전압을, 화소 전극이나 공통 전극과는 다른 전압으로 변동시키므로, 용량선에 접속된 축적 용량의 한쪽 전극을, 화소 전극이나 공통 전극과는 별개로 형성해야 했다. 이 때문에, 액정을 사이에 유지하는 한 쌍의 기판 중, 한쪽의 기판에 화소 용량을 구성하는 화소 전극 및 공통 전극이 일체적으로 형성되는 IPS(In-Plane Switching)나 FFS(Fringe-Field Switching)와 같은 액정 장치에는, 상술한 배경 기술을 적용하는 것은 곤란했다.

- <31> 본 발명은, 상술한 사정에 감안해서 행해진 것으로서, 그 목적의 하나는, 액정을 사이에 유지하는 한 쌍의 기판 중, 한쪽 기판에, 화소 전극 및 공통 전극을 구비하는 액정 장치에 있어서, 표시 품질의 저하를 억제하면서 소비 전력을 절감할 수 있는 구동 회로, 액정 장치, 전자기기 및 액정 장치의 구동 방법을 제공하는 것에 있다.

#### 과제 해결수단

<32> 상기 목적을 달성하기 위해, 본 발명에 따른 액정 장치의 구동 회로는 제 1 기판과, 해당 제 1 기판에 대향 배치된 제 2 기판과, 상기 제 1 기판과 상기 제 2 기판 사이에 유지된 액정을 구비하고, 상기 제 1 기판은 복수의 주사선과, 복수의 데이터선과, 상기 복수의 주사선에 대하여 소정수마다 마련된 복수의 공통 전극과, 상기 주사선과 상기 데이터선의 교차에 대응하여 마련되고, 각각은 일단이 상기 데이터선에 접속됨과 아울러, 상기 주사선에 선택 전압이 인가되었을 때에 도통 상태로 되는 화소 스위칭 소자와, 일단이 상기 공통 전극에 접속되고, 타단이 상기 화소 스위칭 소자의 타단에 접속된 화소 용량을 포함하고, 해당 화소 용량의 유지 전압에 따른 계조로 되는 화소를 갖고, 모든 화소를 이용하여 유효한 표시를 하는 전 화면 표시 모드와, 표시 영역에 관한 주사선에 대응하는 화소만을 이용하여 유효한 표시를 행하고, 비표시 영역에 관한 주사선에 대응하는 화소의 표시를 무효화시키는 부분 표시 모드 중, 어느 것을 선택 가능한 액정 장치의 구동 회로로서, 상기 전 화면 표시 모드의 경우 및 상기 부분 표시 모드의 경우, 상기 복수의 주사선에 상기 선택 전압을 소정의 순서로 공급하는 주사선 구동 회로와, 상기 복수의 공통 전극에, 제 1 전압, 해당 제 1 전압보다 고전위의 제 2 전압, 또는 소정 전압 중 어느 하나를 공급하는 제 1 제어 회로로서, 상기 전 화면 표시 모드의 경우에 하나의 주사선에 상기 선택 전압이 인가되기 전 및 상기 부분 표시 모드에서 표시 영역에 관한 하나의 주사선에 상기 선택 전압이 인가되기 전에, 해당 하나의 주사선에 대응하는 공통 전극에 인가하는 전압을, 상기 제 1 전압 또는 상기 제 2 전압 중 어느 한쪽으로부터 다른쪽으로 전환하고, 상기 부분 표시 모드에서 비표시 영역에 관한 주사선에 대응하는 공통 전극에 인가하는 전압을, 상기 제 1 전압, 상기 제 2 전압 또는 상기 소정의 전압 중, 어느 하나로 유지하는 제 1 제어 회로와, 상기 전 화면 표시 모드의 경우에 상기 복수의 주사선 중, 어느 하나에 선택 전압이 인가된 경우, 및 상기 부분 표시 모드에서 상기 표시 영역에 관한 주사선 중, 어느 하나에 선택 전압이 인가된 경우에, 해당 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 1 전압으로 전환되고 있었을 때, 해당 선택 전압이 인가된 주사선에 대응하는 화소에 대하여, 해당 화소의 계조에 따른 전압으로서, 상기 제 1 전압보다 고전위로 한 정극성의 화상 신호를 상기 데이터선에 공급하고, 해당 선택 전압이 인가된 주사선에 대응하는 공통 전극이 상기 제 2 전압으로 전환되어 있었을 때, 해당 화소에 대하여, 해당 화소의 계조에 따른 전압으로서, 상기 제 2 전압보다 저전위로 한 부극성의 화상 신호를 상기 데이터선에 공급하는 데이터선 구동 회로와, 상기 부분 표시 모드에서 비표시 영역에 관한 주사선 중, 어느 하나에 선택 전압이 인가된 경우에, 해당 선택 전압이 인가된 주사선에 대응하는 공통 전극에 인가한 전압을 상기 데이터선에 공급하는 제 2 제어 회로를 구비하는 것을 특징으로 한다.

<33> 이 구동 회로에 의하면, 전 화면 표시 모드에 있어서의 표시 영역과, 부분 표시 모드에 있어서의 표시 영역에서는 제 1 전압을 공통 전극에 공급한 후에 정극성 기입을 실행하고, 제 2 전압을 공통 전극에 공급한 후에, 부극성 기입을 실행하므로, 화소 용량에 있어 기입 후에 전하가 이동하기 어렵다. 이 때문에, 축적 용량의 특성이 불균일하여도, 화소 전극의 전압에 편차가 발생하기 어렵기 때문에, 각 화소에서의 표시가 정렬되게 되어, 표시 품질의 저하를 억제할 수 있다. 또한, 이 구동 회로에 의하면, 별개의 용량선이 불필요해지므로, 용량선의 전압을, 화소 용량이 갖는 화소 전극이나 공통 전극과는 다른 전압으로 변동시킬 필요성이 없어진다. 제 1 기판에 화소 전극 및 공통 전극의 쌍방이 형성되므로, IPS나 FFS와 같은 액정 장치에 용이하게 적용할 수 있게 된다. 더하여, 상기 구동 회로에 의하면, 부분 표시 모드에서의 비표시 영역에서는, 화소 전극에 인가되는 전압과 같은 전압이 공통 전극에 인가되므로, 화소 전극에 유지되는 전압은 0으로 된다. 이 때문에, 비표시 영역의 화소에서 소비되는 전력을 억제할 수 있다.

<34> 본 발명에 따른 구동 회로에 있어서, 상기 데이터선 구동 회로는 상기 주사선이 상기 소정수 선택될 때마다, 상기 정극성의 화상 신호와 상기 부극성의 화상 신호를 교대로 전환하는 구성으로 하여도 좋다. 이와 같이 교대로 전환하면, 정극성 기입이 이루어진 화소와 부극성 기입이 이루어진 화소끼리 폴리커를 상쇄시킬 수 있으므로, 표시 품질의 저하를 더욱 억제할 수 있다. 특히, 공통 전극은 주사선의 각각에 대응하여 마련되는 구성이 바람직하다.

<35> 또한, 본 발명에 따른 구동 회로에 있어서, 상기 제 1 제어 회로는 래치 회로 및 선택 회로를 갖고, 상기 래치 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 래치 회로를 갖고, 상기 단위 래치 회로의 각각은 상기 데이터선 구동 회로에 대하여 화상 신호의 정극성 및 부극성을 지시하는 극성 신호를, 해당 공통 전극에 대응하는 주사선에 대하여 서로 인접하는 2행의 주사선 중, 어느 한쪽에 상기 선택 전압이 인가되었을 때에 래치하고, 상기 선택 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 선택 회로를 포함하고, 상기 전 화면 표시 모드에서의 모든 단위 선택 회로 및 상기 부분 표시 모드에서의 상기 표시 영역에 관한 주사선에 대응하는 공통 전극에 따른 단위 선택 회로는 상기 래치 회로에 의해 래치된 극성 신호에 따라 상기 제 1 또는 제 2 전압 중 어느 하나를, 해당 공통 전극에 인가하고, 상기 부분 표시 모드에서의 상기 비표시 영역에 관한 주사선에 대응하는

공통 전극에 따른 단위 선택 회로는 상기 제 1 전압, 상기 제 2 전압 또는 상기 소정의 전압 중 어느 하나를, 해당 공통 전극에 인가하는 구성으로 하여도 좋다. 이 구성에 의하면, 제 1 제어 회로는 인접하는 주사선 중, 어느 하나에 선택 전압이 인가되었을 때에, 공통 전극의 전압을 전환하므로, 주사선에 선택 전압이 인가되는 방향을 한정하지 않는다.

<36> 한편, 본 발명에 따른 구동 회로에 있어서, 상기 제 1 제어 회로는 래치 회로 및 선택 회로를 갖고, 상기 래치 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 래치 회로를 갖고, 상기 단위 래치 회로의 각각은 상기 데이터선 구동 회로에 대하여 화상 신호의 정극성 및 부극성을 지시하는 극성 신호를, 해당 공통 전극에 대응하는 주사선보다 1행전의 주사선에 상기 선택 전압이 인가되었을 때에 래치하고, 상기 선택 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 선택 회로를 포함하고, 상기 전 화면 표시 모드에서의 모든 단위 선택 회로 및 상기 부분 표시 모드에서의 상기 표시 영역에 관한 주사선에 대응하는 공통 전극에 따른 단위 선택 회로는 상기 래치 회로에 의해 래치된 극성 신호에 따라 상기 제 1 또는 제 2 전압 중 어느 하나를, 해당 공통 전극에 인가하고, 상기 부분 표시 모드에서의 상기 비표시 영역에 관한 주사선에 대응하는 공통 전극에 따른 단위 선택 회로는 상기 제 1 전압, 상기 제 2 전압 또는 상기 소정의 전압 중 어느 하나를, 해당 공통 전극에 인가하는 구성으로 하여도 좋다. 이 구성에 의하면, 제 1 제어 회로는 선택 전압이 인가되는 주사선을, 이전의 1행만을 착안하면 좋으므로, 인접하는 2행의 주사선 중, 어느 하나에 선택 전압이 인가되는지 여부를 검출하는 구성과 비교하여, 구성의 간이화를 도모하는 것이 가능해진다.

<37> 또한, 본 발명에 따른 구동 회로에 있어서, 상기 제 1 제어 회로는 래치 회로 및 선택 회로를 갖고, 상기 래치 회로는 상기 복수의 공통 전극마다 각각 마련된 단위 래치 회로를 갖고, 상기 단위 래치 회로의 각각은 상기 데이터선 구동 회로에 대하여 화상 신호의 정극성 및 부극성을 지시하는 극성 신호를, 해당 공통 전극에 대응하는 주사선보다 1행전의 주사선에 상기 선택 전압이 인가되었을 때에 래치하고, 상기 선택 회로는 미리 정해진 표시 영역에 관한 주사선에 대응하는 공통 전극에 따라 마련되는 제 1 단위 선택 회로와, 미리 정해진 비표시 영역에 관한 주사선에 대응하는 공통 전극에 따라 마련되는 제 2 단위 선택 회로를 갖고, 상기 제 1 단위 선택 회로는 상기 래치 회로에 의해 래치된 극성 신호에 따라 상기 제 1 또는 제 2 전압 중 어느 하나를, 해당 공통 전극에 인가하고, 상기 제 2 단위 선택 회로는, 상기 전 화면 표시 모드의 경우에, 상기 래치 회로에 의해 래치된 극성 신호에 따라 상기 제 1 또는 제 2 전압 중 어느 하나를, 해당 공통 전극에 인가하고, 상기 부분 표시 모드의 경우에, 상기 제 1 전압, 상기 제 2 전압 또는 상기 소정의 전압 중 어느 하나를, 해당 공통 전극에 인가하는 구성으로 하여도 좋다. 이 구성에 있어서, 제 1 단위 선택 회로는 전 화면 표시 모드와 부분 표시 모드와 관계없이, 래치 회로에 의해 래치된 극성 신호에 따라 제 1 또는 제 2 전압 중 어느 하나를, 공통 전극에 인가하므로, 제 2 단위 선택 회로로서 간략화된다.

<38> 본 발명은, 액정 장치의 구동 회로뿐만 아니라, 액정 장치의 구동 방법으로서도, 또한 액정 장치로서도 개념하는 것이 가능하다. 여기서, 액정 장치로서 개념하는 경우, 상기 복수의 공통 전극은 상기 복수의 주사선의 1행 쪽에 대응함과 아울러, 상기 주사선의 연장 방향을 따라 상기 화소 전극의 1행분에 걸쳐 대향하도록 마련되고, 해당 공통 전극의 각각에 각각 보조 공통선이 상기 주사선 및 상기 공통 전극의 연장 방향을 따라 마련됨과 아울러, 1조의 공통 전극 및 보조 공통선은 소정의 간격마다 마련된 콘택트 배선을 거쳐 상호 접속된 구성이 바람직하다. 이러한 구성에서는, 공통 전극은 보조 공통선과의 병렬화에 따라 시정수가 저하하므로, 과형이 무뎌지는 것 등에 기인하는 표시 품질의 저하가 방지된다. 또한, 본 발명은 해당 액정 장치를 갖는 전자기기로서도 개념하는 것이 가능하다.

## 효과

<39> 본 발명에 의하면, 액정을 사이에 유지하는 한 쌍의 기판 중, 한쪽 기판에, 화소 전극 및 공통 전극을 구비하는 액정 장치에 있어서, 표시 품질의 저하를 억제하면서 소비 전력을 절감할 수 있는 구동 회로, 액정 장치, 전자기기 및 액정 장치의 구동 방법을 제공할 수 있다.

## 발명의 실시를 위한 구체적인 내용

<40> 이하, 본 발명의 실시예에 대하여 도면을 참조하여 설명한다. 또, 이하의 설명에서 동일 구성 요건에 대해서는 동일 부호를 부여하고, 그 설명을 생략 또는 간략화하는 경우가 있다.

<41> (실시예 1)

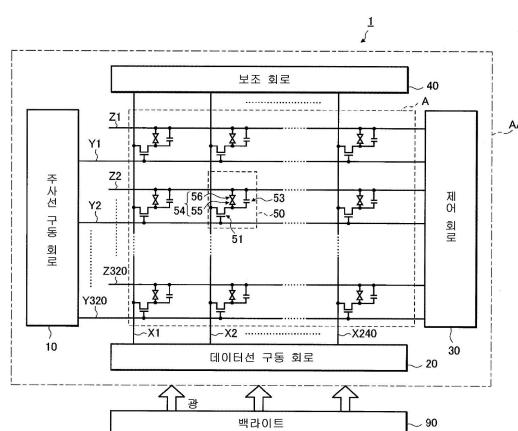

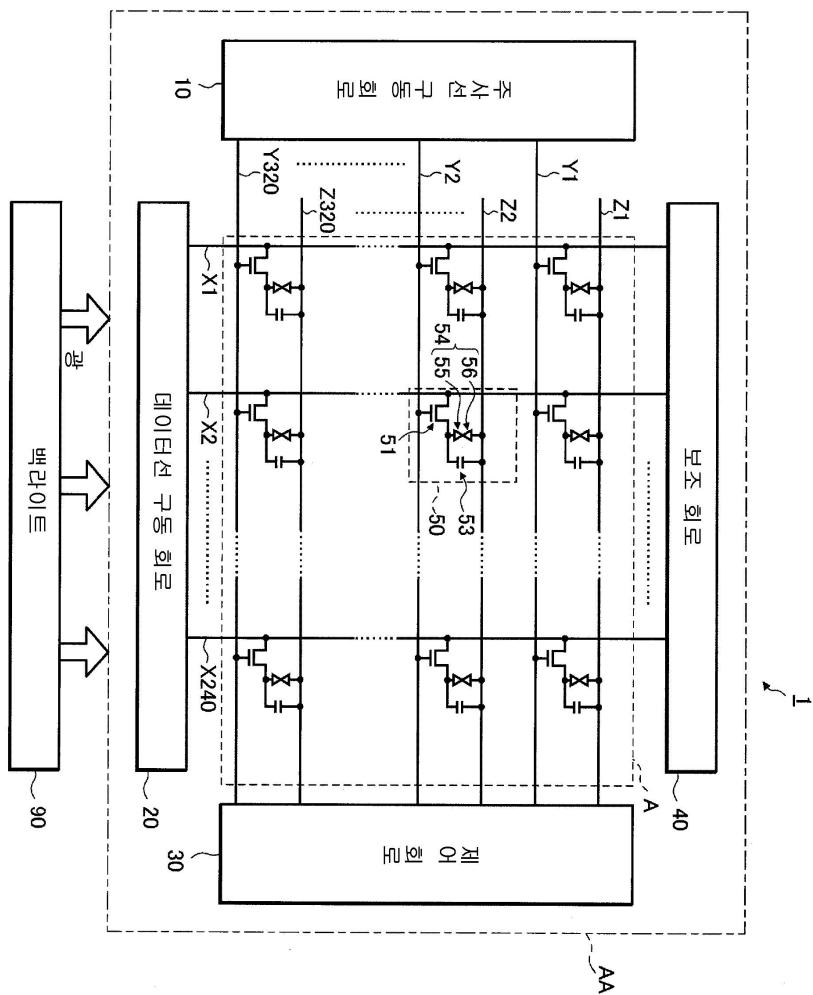

<42> 우선, 본 발명의 실시예 1에 따른 액정 장치에 대하여 설명한다. 도 1은 실시예 1에 따른 액정 장치(1)의 구성

을 나타내는 블력도이다.

<43> 이 도면에 나타내는 바와 같이, 액정 장치(1)는, 액정 패널(AA)와, 해당 액정 패널(AA)에 대향 배치되어 광을 출사하는 백라이트(90)를 포함한다. 이 액정 장치(1)는 백라이트(90)로부터의 광을 이용하여, 투과형의 표시를 행하는 것이다.

<44> 액정 패널(AA)은 표시 화면(A), 주사선 구동 회로(10), 데이터선 구동 회로(20), 제어 회로(30) 및 보조 회로(40)를 갖는다. 이 중, 표시 화면(A)에서는, 복수의 화소(50)가 매트릭스 형상으로 배열되어 화상을 표시한다. 주사선 구동 회로(10) 및 데이터선 구동 회로(20)는 표시 화면(A)의 주변에 마련되어 표시 패널(AA)을 구동하는 구동 회로로서 기능하고, 제어 회로(30)는 제 1 제어 회로로서 기능하며, 보조 회로(40)는 제 2 제어 회로로서 기능한다.

<45> 이 액정 패널(AA)은 표시 화면(A)의 전 영역을 표시 영역으로 하는 전 화면 표시 모드와, 표시 화면(A)의 전 영역 중 일부의 영역을 표시 영역으로 하고, 다른 영역을 비표시 영역으로 하는 부분 표시 모드를 선택 가능하게 하는 것이다.

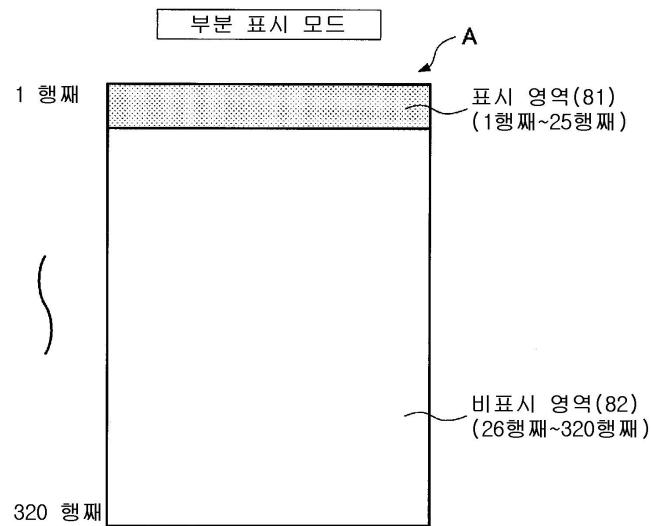

<46> 도 2는 부분 표시 모드에 있어서의 표시 화면(A)을 나타내는 도면이다.

<47> 부분 표시 모드에 있어서, 표시 화면(A)은 주사선의 연장 방향(행)을 따른 표시 영역(81)과 비표시 영역(82)으로 분할된다. 표시 영역(81)에는, 전지 잔량이나 시각 표시와 같은 화상이 표시되고, 비표시 영역(82)에는, 오프 표시 화상이 표시된다. 또, 본 실시예에 따른 액정 장치는, 노멀리 블랙 모드로 동작하기 때문에, 비표시 영역(82)에는, 오프 표시 화상으로서 흑 화상이 표시되어, 표시가 무효화된다.

<48> 본 실시예 1에서는, 표시 영역(81) 및 비표시 영역(82)은 고정이 아니라, 가변이지만, 설명의 편의상, 표시 영역(81)은 1행 째로부터 25행 째까지의 화소(50)로 이루어지고, 비표시 영역(82)은 26행 째로부터 320행 째까지의 화소(50)로 이루어지는 것으로 한다.

<49> 도 1에 되돌아가면, 백라이트(90)는 광을 표시 패널(AA)의 배면 측으로부터 광을 출사하는 것이다. 이 백라이트(90)는, 예컨대, 냉음극 형광관(Cold Cathode Fluorescent Lamp)이나, 발광 다이오드(Light Emitting Diode), 전계 발광(Electro Luminescence)으로 구성된다.

<50> 다음에, 액정 패널(AA)의 구성에 대하여 상술한다.

<51> 액정 패널(AA)에는, 소정 간격을 두고 교대로 마련된 320행의 주사선(Y1~Y320) 및 320행의 공통선(Z1~Z320)과, 이를 주사선(Y1~Y320) 및 공통선(Z1~Z320)에 교차하고, 또한 소정 간격을 두고 마련된 240열의 데이터선(X1~X240)이 마련된다. 여기서, 1행에 대하여, 주사선과 공통선은 쌍을 이룬다.

<52> 또, 주사선(Y1~Y320) 중, 특별히 행을 지정하지 않고 일반적으로 나타낼 때에 주사선(Y)으로 표기하는 경우가 있다. 마찬가지로, 공통선(Z1~Z320) 중, 특별히 행을 지정하지 않고 나타낼 때에 공통선(Z)으로 표기하며, 데이터선(X1~X240) 중, 특별히 열을 지정하지 않고 나타낼 때에 데이터선(X)으로 표기하는 경우가 있다.

<53> 화소(50)는 주사선(Y1~Y320) 및 데이터선(X1~X240)의 각 교차 부분에 각각 마련되고, 각 화소(50)는 TFT(51)와 화소 전극(55) 및 공통 전극(56)을 갖는 화소 용량(54)과, 한쪽 전극이 공통선(Z)에 접속되고, 다른쪽 전극이 화소 전극(55)에 접속된 축적 용량(53)을 구비한다. 여기서, 공통 전극(56)은 1행마다 전기적으로 분할되어 있고, 각각 공통선이다.

<54> TFT(51)의 게이트에는 주사선(Y)이 접속되고, TFT(51)의 소스에는 데이터선(X)이 접속되며, TFT(51)의 드레인에는 화소 전극(55) 및 축적 용량(53)의 다른쪽 전극이 접속되어 있다. 따라서 이 TFT(51)는 주사선(Y)에 선택 전압이 인가되면 온 상태로 되고, 데이터선(X)과 화소 전극(55) 및 축적 용량(53)의 다른쪽 전극과의 사이를 도통 상태로 한다.

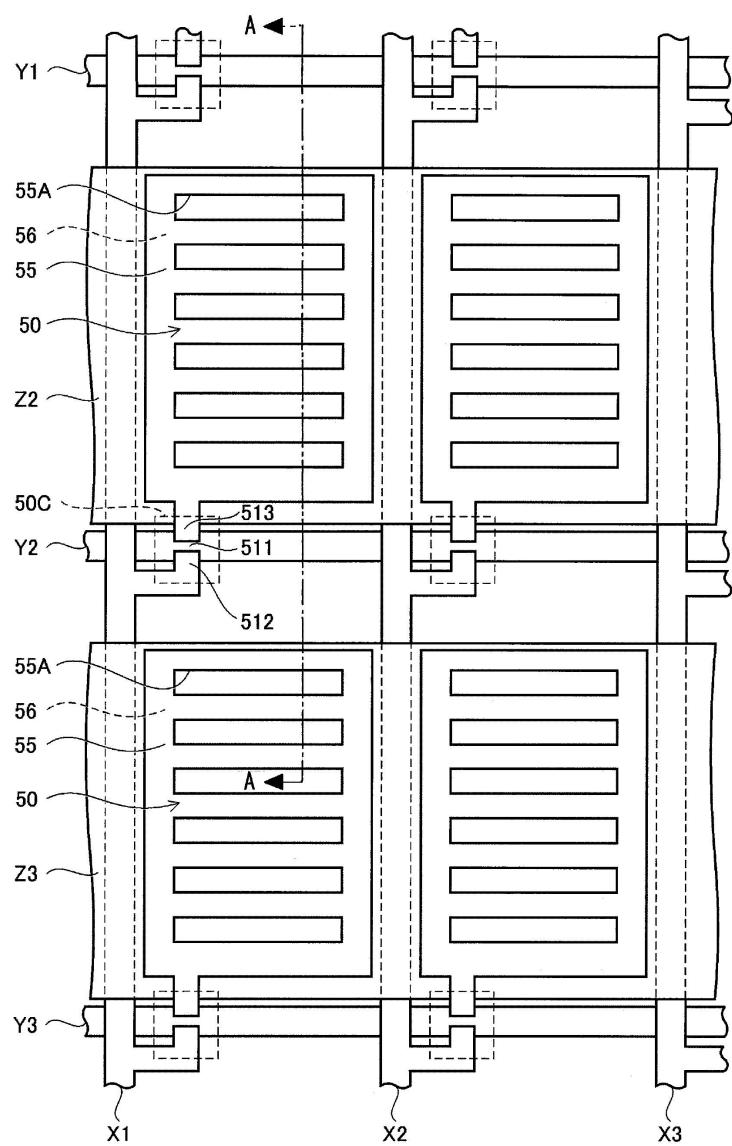

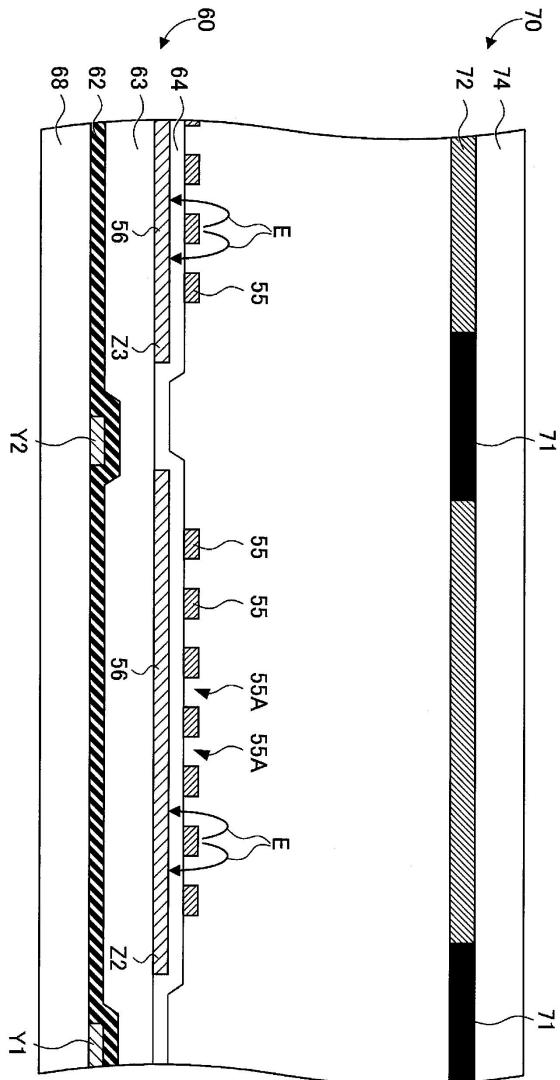

<55> 도 3은 화소(50)의 확대 평면도이며, 도 4는 도 3에 나타내는 화소(50)의 A-A선 단면도이다. 또, 도 3에는, 2 행 째 주사선(Y2) 및 3행 째 주사선(Y3)과, 1열 째 데이터선(X1) 및 2열 째 데이터선(X2)의 각 교차에 대응하는 4화소 분량의 구성이 표시된다.

<56> 액정 패널(AA)은 제 1 기판으로서의 소자 기판(60)과, 이 소자 기판(60)에 대향 배치된 제 2 기판으로서의 대향 기판(70)과, 소자 기판(60)과 대향 기판(70) 사이에 유지된 액정을 구비한다.

<57> 소자 기판(60)에는, 주사선(Y1~Y320), 공통선(Z1~Z320) 및 데이터선(X1~X240)이 형성되어 있고, 각 화소(50)는

서로 인접하는 2행의 주사선(Y)과, 서로 인접하는 2열의 데이터선(X)으로 둘러싸인 영역으로 되어있다. 즉, 각 화소(50)는 주사선(Y)과 데이터선(X)으로 구획되어 있다.

<58> 본 실시예에서는, TFT(51)는 역스태거형 아몰퍼스 실리콘 TFT이며, 주사선(Y)과 데이터선(X)의 교차부 근방에는, 이 TFT(51)가 형성되는 영역(50C)(도 3에서 파선으로 둘러싸인 부분)이 마련되어 있다.

<59> 소자 기판(60)의 상세에 대하여 설명한다.

<60> 소자 기판(60)은 유리 기판(68)을 갖고, 이 유리 기판(68)의 위에는, 유리 기판(68)의 표면 거칠기나 오염에 의한 TFT(51)의 특성의 변화를 방지하기 위해, 소자 기판(60)의 전면에 걸쳐 하지 절연막(도시 생략)이 형성되어 있다.

<61> 하지 절연막의 위에는, 도전 재료로 이루어지는 주사선(Y)이 형성되어 있다.

<62> 주사선(Y)은 인접하는 화소(50)의 경계를 따라 마련되고, 데이터선(X)과의 교차부의 근방에서, TFT(51)의 게이트 전극(511)을 구성한다.

<63> 주사선(Y)(게이트 전극(511)) 및 하지 절연막의 위에는, 소자 기판(60)의 전면에 걸쳐, 게이트 절연막(62)이 형성되어 있다.

<64> 게이트 절연막(62) 위의 TFT(51)가 형성되는 영역(50C)에는, 게이트 전극(511)에 대향하여, 아몰퍼스 실리콘으로 이루어지는 반도체층(도시 생략), N+아몰퍼스 실리콘으로 이루어지는 오믹 콘택트층(도시 생략)이 적층되어 있다. 이 오믹 콘택트층에는, 소스 전극(512) 및 드레인 전극(513)이 적층되고, 이에 따라, 아몰퍼스 실리콘 TFT가 형성되어 있다.

<65> 소스 전극(512)은 데이터선(X)과 동일한 도전 재료로 형성되어 있다. 즉, 데이터선(X)으로부터 소스 전극(512)이 연장되는 구성으로 되어 있고, 양자는 일체이므로, 전기적으로 구별할 필요는 없다. 데이터선(X)은 주사선(Y)에 대하여 교차하도록 형성되어 있다.

<66> 상술한 바와 같이, 주사선(Y) 위에는, 게이트 절연막(62)이 형성되고, 이 게이트 절연막(62) 위에는, 데이터선(X)이 형성되어 있다. 이 때문에, 데이터선(X)은 주사선(Y)과는 게이트 절연막(62)에 의해 절연되어 있다.

<67> 데이터선(X)(소스 전극(512)), 드레인 전극(513) 및 게이트 절연막(62) 위에는, 소자 기판(60)의 전면에 걸쳐, 제 1 절연막(63)이 형성되어 있다.

<68> 제 1 절연막(63) 위에는, ITO(Indium Tin Oxide)나 IZO(Indium Zinc Oxide)와 같은 투명 도전 재료로 이루어지는 공통선(Z)이 형성되어 있다. 공통선(Z)은 주사선(Y)을 따라 형성되고, 이 공통선(Z)은 공통 전극(56)으로부터 연장된 것이고, 양자는 일체이므로, 전기적으로 구별할 필요는 없다.

<69> 공통선(Z)(공통 전극(56)) 및 제 1 절연막(63) 위에는, 소자 기판(60)의 전면에 걸쳐 제 2 절연막(64)이 형성되어 있다.

<70> 제 2 절연막(64) 위에는, 공통 전극(56)에 대향하는 영역에, ITO나 IZO와 같은 투명 도전 재료로 이루어지는 화소 전극(55)이 형성되어 있다. 화소 전극(55)은 상술한 제 1 절연막(63) 및 제 2 절연막(64)에 형성된 콘택트홀(도시 생략)을 통해, 드레인 전극(513)에 전기적으로 접속되어 있다.

<71> 이 화소 전극(55)에는, 자신과 공통 전극(56) 사이에서, 플린지 필드(전계 E)를 발생시키기 위한 복수의 슬릿(55A)이 소정 간격을 두고 마련된다. 즉, 액정 장치(1)는 FFS 방식의 액정 장치이다.

<72> 화소 전극(55) 및 제 2 절연막(64) 위에는, 소자 기판(60)의 전면에 걸쳐, 폴리이미드막 등의 유기막으로 이루어지는 배향막(도시 생략)이 형성되어 있다.

<73> 계속해서, 대향 기판(70)의 상세에 대하여 설명한다.

<74> 대향 기판(70)은 유리 기판(74)을 갖고, 이 유리 기판(74)의 위 중, 화소 전극(55)과 대향하지 않는 영역에는, 블랙 매트릭스로서의 차광막(71)이 형성되어 있다. 또한, 유리 기판(74)의 위 중, 차광막(71)이 형성되어 있는 영역을 제외하는 영역, 즉 화소 전극(55)과 대향하는 영역에는, 컬러 필터(72)가 형성되어 있다.

<75> 차광막(71) 및 컬러 필터(72) 위에는, 대향 기판(70)의 전면에 걸쳐, 배향막(도시 생략)이 형성되어 있다.

<76> 설명을 다시 도 1로 되돌리면, 제어 회로(30)는 제 1 전압으로서의 전압 VCOML, 해당 전압 VCOML보다 전위가 높은 제 2 전압으로서의 전압 VCOMH, 또는 소정의 전압으로서의 전압 VCOML 중 어느 하나를 공통선(Z1~Z320)에 각

각 개별적으로 공급한다.

<77> 주사선 구동 회로(10)는 선택 전압을 주사선(Y1~Y320)에 순차 공급한다. 여기서, 어떤 주사선(Y)에 선택 전압을 공급하면, 이 주사선(Y)에 접속된 TFT(51)가 모두 온 상태로 되고, 이 주사선(Y)에 관한 화소(50)가 전부 선택된다.

<78> 데이터선 구동 회로(20)는 화상 신호를 데이터선(X1~X240)에 공급하고, 온 상태의 TFT(51)를 거쳐, 이 화상 신호에 근거하는 화상 전압을 화소 전극(55)에 기입한다. 여기서, 데이터선 구동 회로(20)는 전압 VCOML보다 전위가 높은 정극성의 화상 신호를 데이터선(X)에 공급하고, 이 정극성의 화상 신호에 근거하는 화상 전압을 화소 전극(55)에 기입하는 정극성 기입과, 전압 VCOMH보다 전위가 낮은 부극성의 화상 신호를 데이터선(X)에 공급하며, 이 부극성의 화상 신호에 근거하는 화상 전압을 화소 전극(55)에 기입하는 부극성 기입을 1수평 주사 기간마다 교대로 실행한다.

<79> 또한, 보조 회로(40)는 부분 표시 모드에서 비표시 영역(82)에 관한 주사선에 선택 전압이 인가되었을 때, 소정의 전압으로서의 전압 VCOML을 데이터선(X1~X240)에 공급한다.

<80> 이 액정 장치(1)는 전 화면 표시 모드에서는 대략 다음과 같이 동작한다.

<81> 즉, 우선, 제어 회로(30)가 a행 째(a는,  $1 \leq a \leq 320$ 을 만족하는 정수)의 공통선(Z(a))에 전압 VCOML 또는 전압 VCOMH를 공급한다.

<82> 구체적으로는, 제어 회로(30)는 공통선(Z(a))에 1프레임 기간마다 전압 VCOML과 전압 VCOMH를 교대로 공급한다. 예컨대, 제어 회로(30)는 어느 1프레임 기간에 공통선(Z(a))에 전압 VCOML을 공급한 경우, 다음 1프레임 기간에서, 공통선(Z(a))에 전압 VCOMH를 공급한다. 한편, 제어 회로(30)는 어느 1프레임 기간에 공통선(Z(a))에 전압 VCOMH를 공급한 경우, 다음 1프레임 기간에서, 공통선(Z(a))에 전압 VCOML을 공급한다.

<83> 또한, 제어 회로(30)는 서로 인접하는 공통선(Z)에 서로 다른 전압을 공급한다. 예컨대, 제어 회로(30)는 어느 1프레임 기간에 공통선(Z(a))에 전압 VCOML을 공급하는 경우, 동일한 1프레임 기간에 (a-1)행 째의 공통선(Z(a-1))과 (a+1)행 째의 공통선(Z(a+1))에 전압 VCOMH를 공급한다. 한편, 제어 회로(30)는 어느 1프레임 기간에 공통선(Z(a))에 전압 VCOMH를 공급하는 경우, 동일한 1프레임 기간에서 공통선(Z(a-1))과 공통선(Z(a+1))에 전압 VCOML을 공급한다.

<84> 주사선 구동 회로(10)는 주사선(Y(a))에 선택 전압을 공급하는 것으로, 주사선(Y(a))에 접속된 모든 TFT(51)을 온 상태로 하여, 주사선(Y(a))에 관한 모든 화소(50)를 선택한다.

<85> 한편, 주사선(Y(a))에 관한 화소(50)의 선택에 동기하여, 데이터선 구동 회로(20)는 데이터선(X1~X240)에 공통선(Z(a))의 전압에 따라, 정극성의 화상 신호와 부극성의 화상 신호를 1수평 주사 기간마다 교대로 공급한다. 구체적으로는, 공통선(Z(a))의 전압이 전압 VCOML이면, 정극성의 화상 신호를 데이터선(X1~X240)에 공급하고, 공통선(Z(a))의 전압이 전압 VCOMH이면, 부극성의 화상 신호를 데이터선(X1~X240)에 공급한다.

<86> 주사선(Y(a))에 선택 전압이 공통되면, a행 째에서 1~240열의 화소(50)에, 데이터선 구동 회로(20)로부터 데이터선(X1~X240) 및 온 상태의 TFT(51)을 거쳐 화상 신호가 공급되고, 이 화상 신호에 근거하는 화상 전압이 화소 전극(55)에 기입된다. 이에 따라, 화소 전극(55)과 공통 전극(56) 사이에 전위차가 발생하여, 구동 전압이 액정에 인가된다.

<87> 액정에 구동 전압이 인가되면, 액정의 배향이나 질서가 변화하여, 액정을 투과하는 백라이트(90)로부터의 광이 변화된다. 이 변화된 광이 컬러 필터(72)를 투과하는 것에 의해, 화상이 표시된다.

<88> 한편, 이 액정 장치(1)는 부분 표시 모드에서 대략 다음과 같이 동작한다.

<89> 즉, 우선, 공통선(Z(a))이 표시 영역(81)에 관한 공통선(Z1~Z25) 중 어느 하나이면, 제어 회로(30)는 전 화면 표시 모드와 마찬가지로, 해당 공통선(Z(a))에 전압 VCOML 또는 전압 VCOMH를 공급한다. 한편, 공통선(Z(a))이 비표시 영역(82)에 관한 공통선(Z26~Z320) 중 어느 하나이면, 제어 회로(30)는 공통선(Z(a))에 소정의 전압으로서의 전압 VCOML을 공급한다.

<90> 주사선 구동 회로(10)는 주사선(Y(a))에 선택 전압을 공급하는 것으로, 주사선(Y(a))에 접속된 모든 TFT(51)을 온 상태로 하고, 주사선(Y(a))에 관한 모든 화소(50)를 선택한다.

<91> 여기서, 선택되는 화소(50)가 표시 영역(81)에 관한 화소(50)이면, 상술한 바와 같이, 데이터선 구동 회로(20)

는 이들 화소(50)의 선택에 동기하고, 데이터선(X1~X240)에, 공통선(Z(a))의 전압에 따라, 정극성의 화상 신호와 부극성의 화상 신호를 1수평 주사 기간마다 교대로 공급한다.

<92> 그렇게 하면, 선택된 표시 영역(81)에 관한 화소(50)에, 데이터선 구동 회로(20)로부터 데이터선(X1~X240) 및 온 상태의 TFT(51)을 통해 화상 신호가 공급되고, 이 화상 신호에 근거하는 화상 전압이 화소 전극(55)에 기입된다. 이에 따라, 화소 전극(55)과 공통 전극(56) 사이에 전위차가 발생하여, 구동 전압이 액정에 인가된다.

<93> 액정에 구동 전압이 인가되면, 액정의 배향이나 질서가 변화하여, 액정을 투과하는 백라이트(90)로부터의 광이 변화된다. 이 변화된 광이 컬러 필터(72)를 투과하는 것에 의해, 표시 영역(81)에서는, 화상이 표시된다.

<94> 한편, 선택된 화소(50)가 비표시 영역(82)에 관한 화소(50)이면, 이들 화소(50)의 선택에 동기하여, 보조 회로(40)로부터 데이터선(X1~X240)에 소정의 전압으로서의 전압 VCOML이 공급된다.

<95> 그렇게 하면, 선택된 비표시 영역(82)의 화소(50)에, 보조 회로(40)로부터 데이터선(X1~X240) 및 온 상태의 TFT(51)를 거쳐 전압 VCOML이 공급되고, 이 전압 VCOML이 화소 전극(55)에 기입된다.

<96> 여기서, 비표시 영역(82)에 관한 공통선(Z(a))에는, 전압 VCOML이 공급되고 있으므로, 공통선(Z(a))에 관한 공통 전극(56)의 전압도 전압 VCOML이다. 이 때문에, 화소 전극(55)과 공통 전극(56) 사이에 전위차가 발생하지 않으므로, 액정에는 구동 전압이 인가되지 않는다.

<97> 액정에 구동 전압이 인가되지 않으면, 액정의 배향이나 질서가 변화하지 않으므로, 비표시 영역(82)에서는, 노멀리 블랙 모드에 있어서 오프 상태의 흑 화상이 표시된다.

<98> 또, 액정에 인가되는 구동 전압은, 축적 용량(53)에 의해, 화상 전압이 기입되는 기간보다 대략 3자리수 정도 긴 기간에 걸쳐 유지된다.

<99> 액정 장치(1)는, 이와 같이, 전 화면 표시 모드 및 부분 표시 모드에서 동작한다. 그래서 다음에, 이 동작을 행하기 위한 각 부에 대하여 순서대로 상술한다.

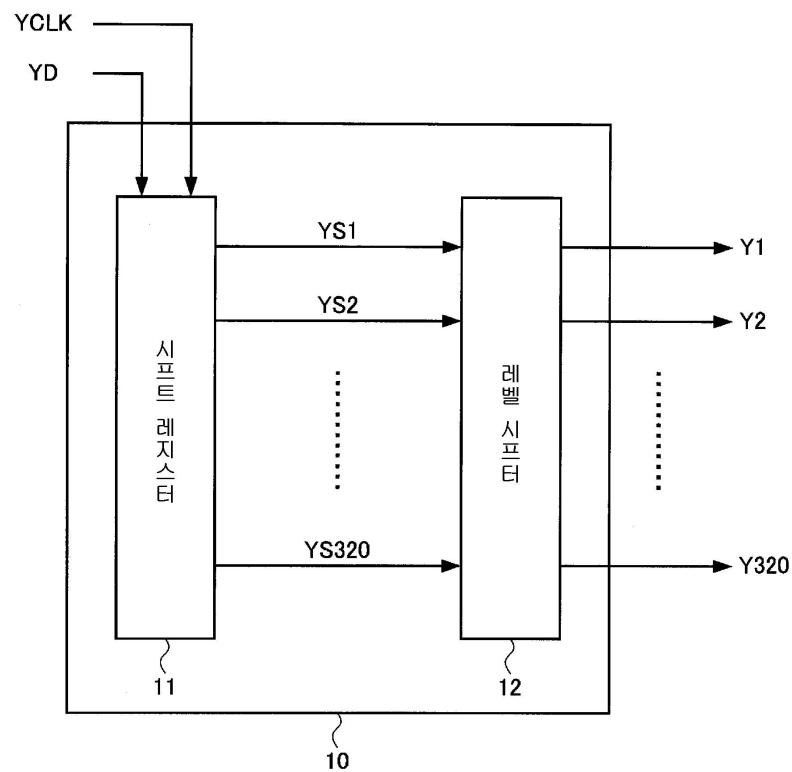

<100> 우선, 주사선 구동 회로(10)에 대하여 설명한다. 도 5는 주사선 구동 회로(10)의 구성을 나타내는 블럭도이다.

<101> 이 도면에 나타내는 바와 같이, 주사선 구동 회로(10)는 시프트 레지스터(11) 및 레벨 시프터(12)를 구비한다. 이 중, 시프트 레지스터(11)는 특별히 도시하지 않지만, 주사선(Y)의 개수와 같은 단수, 즉 본 실시예에서는 320단의 전송 회로를 종속 접속한 구성이다.

<102> 여기서, 어떤 행에 대응하는 단(段)의 전송 회로는 입력 신호를 클럭 신호 YCLK의 1주기분 만큼 지연시켜 해당 행에 대응하는 단의 시프트 신호로서 출력함과 아울러, 다음 행, 즉 1행 아래의 행에 대응하는 단의 전송 회로의 입력 신호로 하는 것이다. 단, 최초의 제 1 단의 전송 회로에의 입력 신호는 클럭 신호 YCLK의 1주기 분량의 기간에 걸쳐 H레벨로 되는 단발의 개시 펄스 YD이며, 1프레임 기간의 최초에 공급된다.

<103> 1단 째로부터 320단 째까지의 전송 회로에 의한 시프트 신호를 YS1~YS320이라고 표기하면, 시프트 신호 YS1, YS2, YS3, …, YS320은 개시 펄스 YD를 클럭 신호 YCLK의 1주기마다 순차 지연시킨 것으로 되므로, 이 순서로 배타적으로 H레벨로 된다.

<104> 레벨 시프터(12)는 저진폭의 논리 신호인 시프트 신호 YS1~YS320을 고진폭의 논리 신호로 변환하여, 각각 주사선(Y1~Y320)에 공급한다.

<105> 또, 본 실시예에 있어서, 고진폭의 논리 신호의 H레벨은 선택 전압으로서 전압 VGH에 상당하고, 고진폭의 논리 신호의 L레벨은 비선택 전압으로서 전압 VGL에 상당한다. 따라서, 시프트 신호 YS1~YS320이 각각 H레벨로 되는 기간은 주사선(Y1~Y320)에서 선택 전압이 인가되는 기간이며, 해당 기간은 클럭 신호 YCLK의 1주기분에 상당하는 것으로 된다.

<106> 이러한 구성의 주사선 구동 회로(10)는 다음과 같이 동작한다.

<107> 즉, 1프레임 기간이 시작되면, 시프트 레지스터(11)에 의해, 1수평 주사 기간에 걸쳐 H레벨로 되는 펄스 신호가 1수평 주사 기간씩 순서대로 시프트되어, 전송 신호 YS1~YS320으로서 출력된다. 이 전송 신호 YS1~YS320의 논리 레벨은 레벨 시프터(12)에 의해, 각각 소정 전압까지 레벨 시프트되어 주사선(Y1~Y320)에 공급된다.

<108> 이에 따라, 주사선 구동 회로(10)는 1수평 주사 기간에 걸쳐 H레벨로 되는 펄스를, 1프레임의 기간 개시로부터 1수평 주사 기간씩 순서대로 시프트시킴과 아울러, 시프트 순으로 주사선(Y1~Y320)에 각각 공급한다. 또, 주사선 구동 회로(10)는 선택 전압인 H레벨을 공급하는 기간 이외에는, 주사선(Y1~Y320)을 비선택 전압인 L레벨로

한다(도 10 및 도 13 참조).

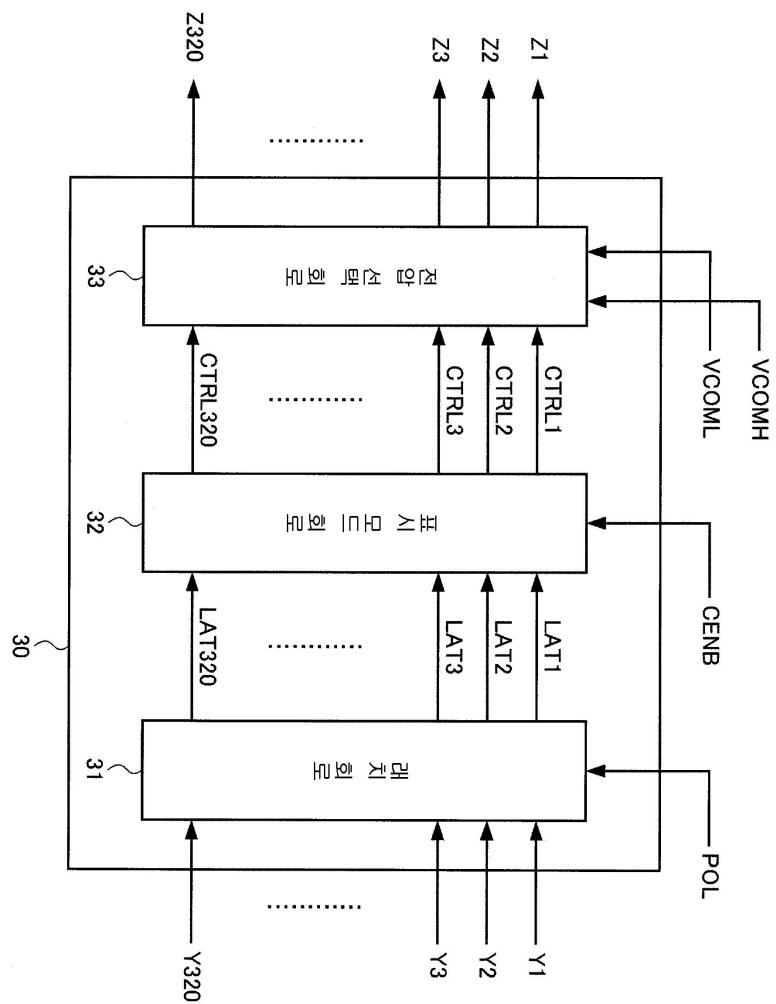

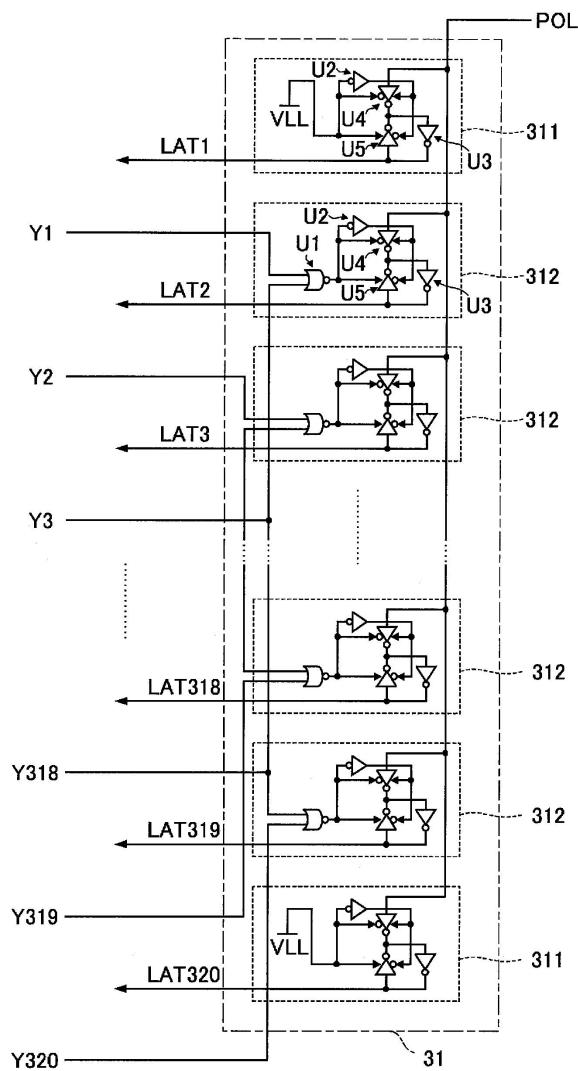

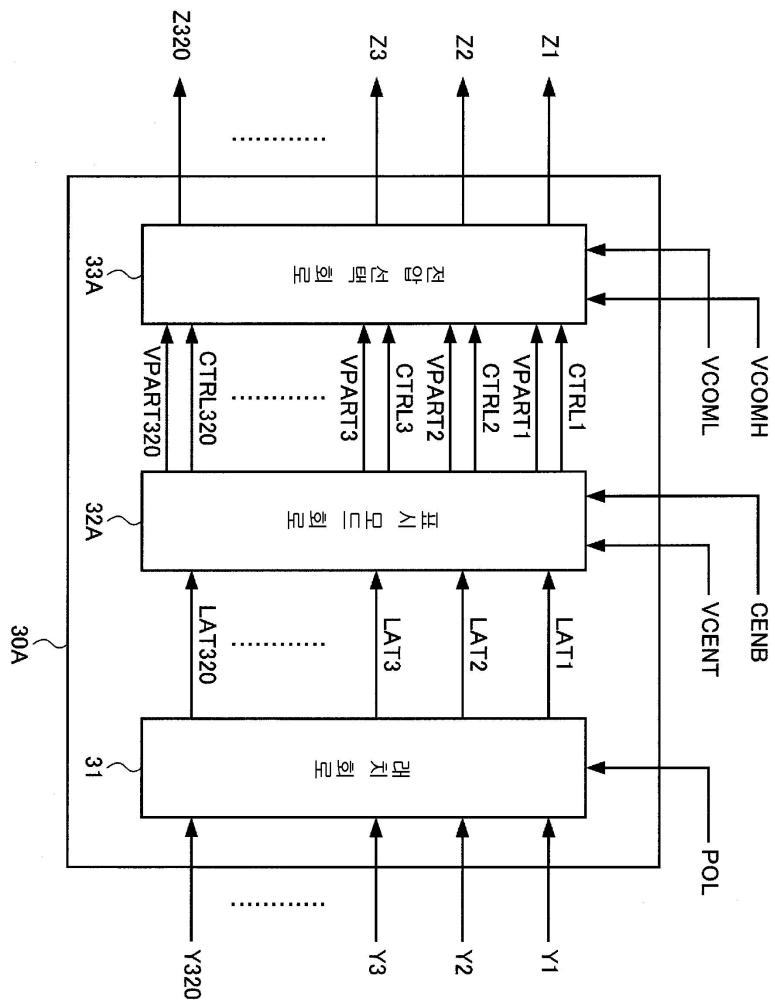

<109> 다음에, 제어 회로(30)에 대하여 설명한다. 도 6은 제어 회로(30)의 개략 구성을 나타내는 블럭도이다.

<110> 이 도면에 나타내는 바와 같이, 제어 회로(30)는 래치 회로(31)와, 표시 모드 회로(32)와, 전압 선택 회로(33)를 구비한다. 또, 표시 모드 회로(32)와 전압 선택 회로(33)가 선택 회로로서 기능한다.

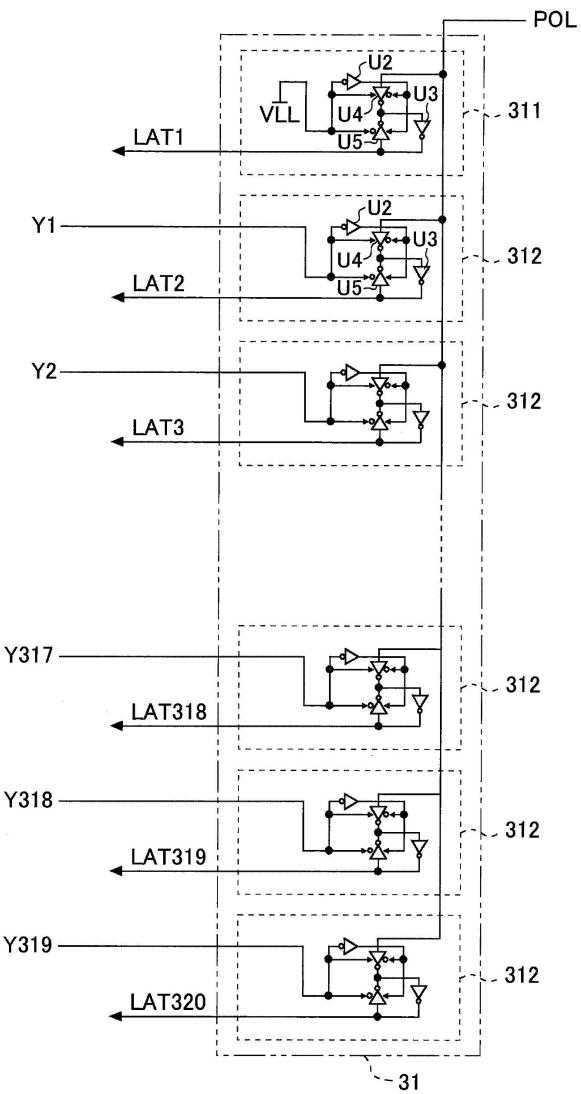

<111> 우선, 래치 회로(31)에 대하여 설명하면, 도 7은 래치 회로(31)의 구성을 나타내는 블럭도이다. 이 도면에 나타내는 바와 같이, 래치 회로(31)는 1행 째의 주사선(Y1)과 최종행의 주사선(Y320)의 각각에 대응하여 마련된 제 1 단위 래치 회로(311)와, 그 이외의 주사선(Y2~Y319)의 각각에 대응하여 마련된 제 2 단위 래치 회로(312)를 구비한다.

<112> 여기서, 제 2 단위 래치 회로(312)에 대하여, b행 째(b는  $2 \leq b \leq 319$ 를 만족하는 정수)의 주사선(Y(b))에 대응하여 마련된 제 2 단위 래치 회로(312(b))를 이용하여 설명한다. 제 2 단위 래치 회로(312(b))는 부정 논리합 연산 회로(이후, NOR 회로라고 함)(U1), 제 1 인버터(U2), 제 2 인버터(U3), 제 1 클럭 인버터(U4) 및 제 2 클럭 인버터(U5)를 구비한다.

<113> b행 째 주사선(Y(b))에 대응하는 제 2 단위 래치 회로(312)에서, NOR 회로(U1)의 2개의 입력 단자 중, 한쪽 입력 단자는 1행의 위로부터 인접하는 (b-1)행 째 주사선(Y(b-1))에 접속되고, 다른쪽 입력 단자는 1행의 아래로부터 인접하는 (b+1)행 째 주사선(Y(b+1))에 접속되어 있다. NOR 회로(U1)의 출력 단자는 제 1 인버터(U2)의 입력 단자와 제 1 클록 인버터(U4)의 반전 입력 제어 단자와 제 2 클록 인버터(U5)의 비반전 입력 제어 단자와 각각 접속되어 있다.

<114> 제 1 인버터(U2)의 입력 단자는 NOR 회로(U1)의 출력 단자에 접속되고, 제 1 인버터(U2)의 출력 단자는 제 1 클록 인버터(U4)의 비반전 입력 제어 단자와 제 2 클록 인버터(U5)의 반전 입력 제어 단자와 각각 접속되어 있다.

<115> 제 1 클록 인버터(U4)의 입력 단자에는, 극성 신호 POL이 입력되고, 제 1 클록 인버터(U4)의 출력 단자는 제 2 인버터(U3)의 입력 단자에 접속되어 있다. 또한, 제 1 클록 인버터(U4)의 반전 입력 제어 단자는 NOR 회로(U1)의 출력 단자가 접속되고, 제 1 클록 인버터(U4)의 비반전 입력 제어 단자는 제 1 인버터(U2)의 출력 단자가 접속되어 있다.

<116> 제 2 인버터(U3)의 입력 단자는 제 1 클록 인버터(U4)의 출력 단자와, 제 2 클록 인버터(U5)의 출력 단자와 접속되며, 제 2 인버터(U3)의 출력 단자는 b행 째의 제 2 단위 래치 회로(312)에서의 래치 신호 LAT(b)를 출력함과 아울러, 제 2 클록 인버터(U5)의 입력 단자에 접속되어 있다.

<117> 또, 제 2 클록 인버터(U5)의 입력 단자는 제 2 인버터(U3)의 출력 단자에 접속되고, 제 2 클록 인버터(U5)의 출력 단자는 제 2 인버터(U3)의 입력 단자에 접속되어 있다. 또한, 제 2 클록 인버터(U5)의 반전 입력 제어 단자는 제 1 인버터(U2)의 출력 단자에 접속되고, 제 2 클록 인버터(U5)의 비반전 입력 제어 단자는 NOR 회로(U1)의 출력 단자에 접속되어 있다.

<118> 이와 같이 구성된 b행 째의 제 2 단위 래치 회로(312(b))는 다음과 같이 동작한다.

<119> 즉, 주사선(Y(b-1)) 또는 주사선(Y(b+1)) 중, 적어도 한쪽에 선택 전압으로서 H레벨의 신호가 공급되면, NOR 회로(U1)는 L레벨의 신호를 출력한다. NOR 회로(U1)로부터 출력된 L레벨의 신호는 제 1 클록 인버터(U4)의 반전 입력 제어 단자에 입력됨과 아울러, 제 1 인버터(U2)에 의해 논리 레벨이 반전되어 H레벨의 신호로 되어, 제 1 클록 인버터(U4)의 비반전 입력 제어 단자에 입력된다. 이 때문에, 제 1 클록 인버터(U4)는 부정 동작이 허가되는 온 상태로 되므로, 극성 신호 POL의 논리 레벨을 반전하여 출력한다. 이 제 1 클록 인버터(U4)에 의해 논리 레벨이 반전되어 출력된 신호는 제 2 인버터(U3)에 의해 논리 레벨이 재차 반전되어 극성 신호 POL에 되돌아가므로, 래치 신호 LAT(b)는 극성 신호 POL과 동일 논리 레벨로 된다.

<120> 한편, 주사선(Y(b-1)) 및 주사선(Y(b+1))의 양쪽에 비선택 전압으로서 L레벨의 신호가 공급되면, NOR 회로(U1)는 H레벨의 신호를 출력한다.

<121> NOR 회로(U1)로부터 출력된 H레벨의 신호는 제 1 클록 인버터(U4)의 반전 입력 제어 단자에 입력됨과 아울러, 제 1 인버터(U2)에 의해 논리 레벨이 반전되어 L레벨의 신호로 되어, 제 1 클록 인버터(U4)의 비반전 입력 제어 단자에 입력된다. 이 때문에, 제 1 클록 인버터(U4)는 부정 동작이 금지되는 오프 상태로 된다. 또한, NOR 회로(U1)로부터 출력된 H레벨의 신호는 제 2 클록 인버터(U5)의 비반전 입력 제어 단자에 입력됨과 아울러, 제 1 인버터(U2)에 의해 논리 레벨이 반전되어 L레벨의 신호로 되어, 제 2 클록 인버터(U5)의 반전 입력 제어 단자에

입력된다. 이 때문에, 제 2 클록 인버터(U5)는 부정 동작이 허가되는 온 상태로 된다.

<122> 따라서 래치 신호 LAT(b)는 제 2 인버터(U3) 및 제 2 클록 인버터(U5)에 의해서 래치되게 된다.

<123> 이와 같이, b행 째의 제 2 단위 래치 회로(312(b))는 주사선(Y(b-1)) 또는 주사선(Y(b+1)) 중, 적어도 한쪽에 선택 전압이 공급되면, 극성 신호 POL을 취입하고, 극성 신호 POL과 동일 논리 레벨의 래치 신호 LAT(b)를 출력하며, 주사선(Y(b-1)) 및 주사선(Y(b+1))의 양쪽에 비선택 전압이 공급되면, 래치 신호 LAT(b)를, 제 2 인버터(U3) 및 제 2 클록 인버터(U5)에 의해 유지하면서 출력하는 것으로 된다.

<124> 다음에, 제 1 단위 래치 회로(311)에 대하여 설명한다.

<125> 제 1 단위 래치 회로(311)는 제 2 단위 래치 회로(312)와 비교해서, NOR 회로(U1)를 폐하여, 제 1 인버터(U2)의 입력 단자, 제 1 클록 인버터(U4)의 반전 입력 제어 단자 및 제 2 클록 인버터(U5)의 비반전 입력 제어 단자를 각각 L레벨에 상당하는 전압 VLL로 고정화한 것이다. 또, 전압 VLL은 실질적으로는 비선택 전압의 전압 VGL과 같고, 이를 전압 VLL, VGL은 전압 기준의 0전위로 하고 있다.

<126> 이러한 구성의 제 1 단위 래치 회로(311)는 제 2 단위 래치 회로(312)에서의 NOR 회로(U1)가 L레벨로 되는 경우가 마찬가지의 동작으로 된다. 즉, 제 1 단위 래치 회로(311)는 항상 극성 신호 POL을 취입하고, 극성 신호 POL과 동일 논리 레벨의 래치 신호 LAT1, LAT320을 출력한다.

<127> 또, 본 실시예에서는, 주사선(Y1, Y320)의 각각에 대응하여 마련된 제 1 단위 래치 회로(311)에서, 제 1 인버터(U2)의 입력 단자와 제 1 클록 인버터(U4)의 반전 입력 제어 단자와 제 2 클록 인버터(U5)의 비반전 입력 제어 단자를 L레벨의 전압 VLL로 했지만, 이것에 한정되는 것은 아니다. 예컨대, 주사선(Y1)에 대응하여 마련된 제 1 단위 래치 회로(311)에서, 제 1 인버터(U2)의 입력 단자와 제 1 클록 인버터(U4)의 반전 입력 제어 단자와 제 2 클록 인버터(U5)의 비반전 입력 제어 단자와 주사선(Y1)을 접속하여도 좋다. 또한, 주사선(Y320)에 대응하여 마련된 제 1 단위 래치 회로(311)에서, 제 1 인버터(U2)의 입력 단자와 제 1 클록 인버터(U4)의 반전 입력 제어 단자와 제 2 클록 인버터(U5)의 비반전 입력 제어 단자에 주사선(Y320)을 접속하여도 좋다.

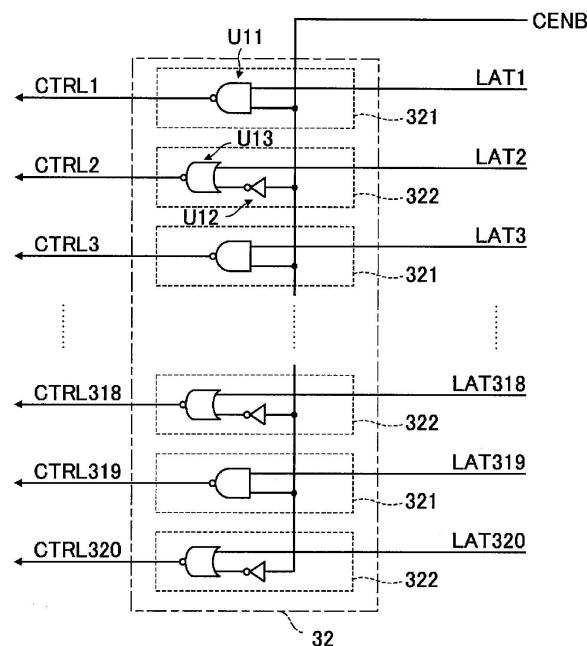

<128> 계속해서, 도 6에 있어서의 표시 모드 회로(32)에 대하여 설명한다. 도 8은 표시 모드 회로(32)의 구성을 나타내는 블럭도이다.

<129> 이 도면에 나타내는 바와 같이, 표시 모드 회로(32)는 기수행의 각각에 대응하여 마련된 제 1 단위 표시 모드 회로(321)와 우수행의 각각에 대응하여 마련된 제 2 단위 표시 모드 회로(322)를 구비한다.

<130> 여기서, 제 1 단위 표시 모드 회로(321)에 대하여, c행 째(c는  $1 \leq c \leq 319$ 를 만족하는 기수)의 주사선(Y(c))에 대응하여 마련된 제 1 단위 표시 모드 회로(321(c))를 이용하여 설명한다.

<131> 기수 c행 째에 대응하는 제 1 단위 표시 모드 회로(321(c))는 부정 논리곱 연산 회로(이후, NAND 회로라고 함)(U11)를 구비한다. NAND 회로(U11)의 2개의 입력 단자 중, 한쪽의 입력 단자에는, 기수 c행 째의 래치 회로(31)로부터 출력된 래치 신호 LAT(c)가 입력되고, 다른쪽의 입력 단자에는, 표시 모드 선택 신호 CENB가 입력되어, 양자의 부정 논리곱 신호가 전압 지시 신호 CTRL(c)로서 출력된다.

<132> 이 때문에, 기수 c행 째의 제 1 단위 표시 모드 회로(321(c))에서, H레벨의 표시 모드 선택 신호 CENB가 입력되고, 기수 c행 째의 래치 회로(31)로부터 출력된 래치 신호 LAT(c)가 H레벨이면, L레벨의 전압 지시 신호 CTRL(c)가 출력되고, 래치 신호 LAT(c)가 L레벨이면, H레벨의 전압 지시 신호 CTRL(c)가 출력된다. 한편, L레벨의 표시 모드 선택 신호 CENB가 입력되면, 래치 신호 LAT(c)의 논리 레벨에 관계없이, H레벨의 전압 지시 신호 CTRL(c)가 출력된다.

<133> 즉, 기수 c행 째의 제 1 단위 표시 모드 회로(321(c))는 표시 모드 선택 신호 CENB가 H레벨이면, 래치 신호 LAT(c)의 논리 레벨을 반전시킨 전압 지시 신호 CTRL(c)를 출력하는 한편, 표시 모드 선택 신호 CENB가 L레벨이면, 래치 신호 LAT(c)의 논리 레벨에 관계없이, H레벨의 전압 지시 신호 CTRL(c)를 출력한다.

<134> 다음에, 제 2 단위 표시 모드 회로(322)에 대하여, d행 째(d는  $2 \leq d \leq 320$ 을 만족하는 우수)의 주사선(Y(d))에 대응하여 마련된 제 2 단위 표시 모드 회로(322(d))를 이용하여 설명한다.

<135> 우수 d행 째에 대응하는 제 2 단위 표시 모드 회로(322(d))는 인버터(U12) 및 NOR 회로(U13)를 구비한다. 인버터(U12)의 입력 단자에는, 표시 모드 선택 신호 CENB가 입력되고, 인버터(U12)의 출력 단자는 NOR 회로(U13)의 2개의 입력 단자 중 다른쪽의 입력 단자에 접속되어 있다.

- <136> NOR 회로(U13)의 2개의 입력 단자 중, 한쪽의 입력 단자에는, 우수 d행 째의 래치 회로(31)로부터 출력된 래치 신호 LAT(d)가 입력되고, 다른쪽의 입력 단자는 인버터(U12)의 출력 단자가 접속되어, 양자의 부정 논리합 신호가 전압 지시 신호 CTRL(d)로서 출력된다.

- <137> 이 때문에, 우수 d행 째의 제 2 단위 표시 모드 회로(322(d))에서, H레벨의 표시 모드 선택 신호 CENB가 입력되면, NOR 회로(U13)의 다른쪽의 입력 단자에는, 인버터(U12)를 통해 L레벨의 신호가 입력되기 때문에, 래치 신호 LAT(d)가 H레벨이면, L레벨의 전압 지시 신호 CTRL(d)가 출력되고, 래치 신호 LAT(d)가 L레벨이면, H레벨의 전압 지시 신호 CTRL(d)가 출력된다. 한편, L레벨의 표시 모드 선택 신호 CENB가 입력되면, NOR 회로(U13)의 다른쪽의 입력 단자에는, 인버터(U12)를 거쳐 H레벨의 신호가 입력되기 때문에, 래치 신호 LAT(d)의 논리 레벨에 관계없이, L레벨의 전압 지시 신호 CTRL(d)가 출력된다.

- <138> 즉, 우수 d행 째의 제 2 단위 표시 모드 회로(322(d))는 표시 모드 선택 신호 CENB가 H레벨이면, 래치 신호 LAT(c)의 논리 레벨을 반전시킨 전압 지시 신호 CTRL(c)를 출력하는 한편, 표시 모드 선택 신호 CENB가 L레벨이면, 래치 신호 LAT(c)의 논리 레벨에 관계없이, L레벨의 전압 지시 신호 CTRL(c)를 출력한다.

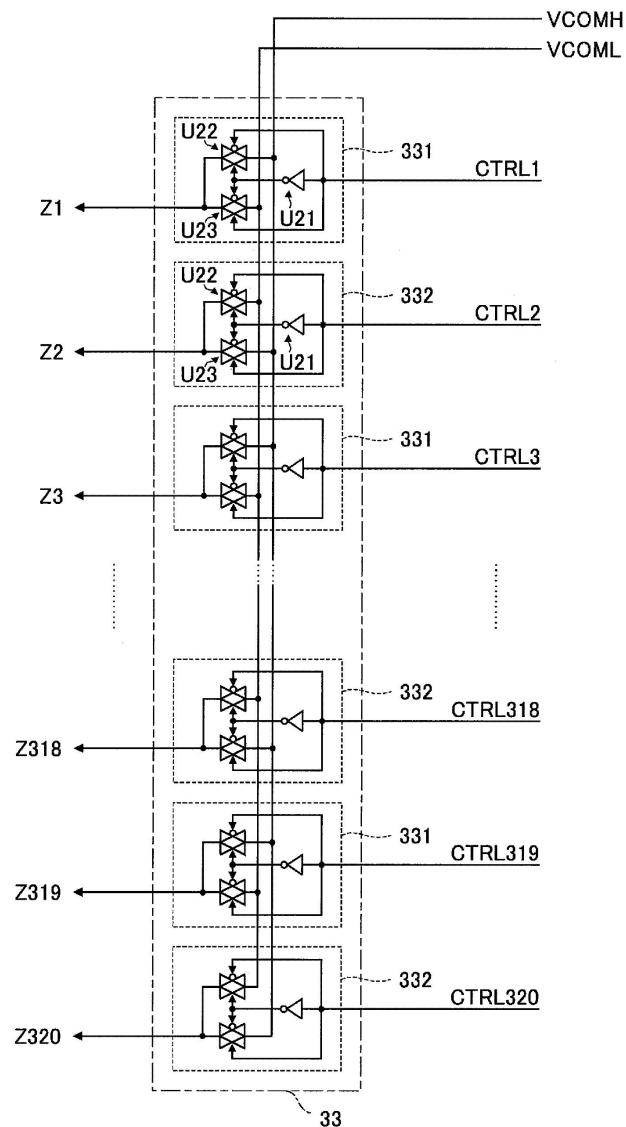

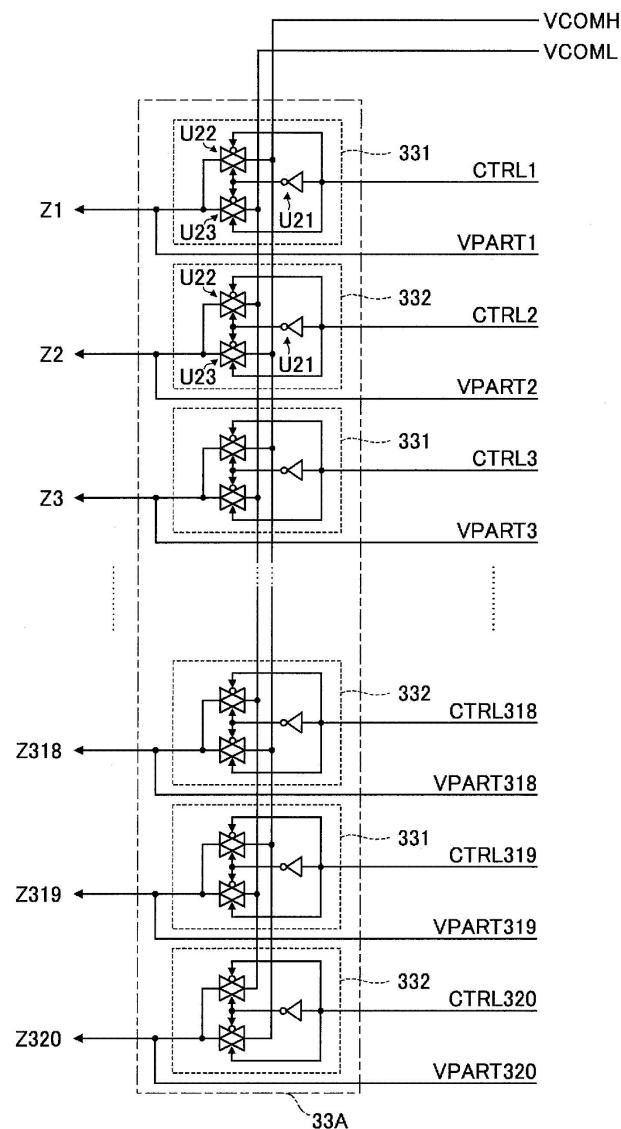

- <139> 다음에, 도 6에서의 전압 선택 회로(33)에 대하여 설명한다. 도 9는 전압 선택 회로(33)의 구성을 나타내는 블럭도이다.

- <140> 이 도면에 나타내는 바와 같이, 전압 선택 회로(33)는 기수행의 각각에 대응하여 마련된 제 1 단위 전압 선택 회로(331)와, 우수행의 각각에 대응하여 마련된 제 2 단위 전압 선택 회로(332)를 구비한다.

- <141> 여기서, 제 1 단위 전압 선택 회로(331)에 대하여, e행 째(e는  $1 \leq e \leq 319$ 를 만족하는 기수)에 대응하여 마련된 제 1 단위 전압 선택 회로(331(e))를 이용하여 설명한다.

- <142> 기수 e행 째의 단위 전압 선택 회로(331(e))는 인버터(U21), 제 1 트랜스퍼 게이트(U22) 및 제 2 트랜스퍼 게이트(U23)를 구비한다. 이 중, 인버터(U21)의 입력 단자에는 e행 째의 표시 모드 회로(32)로부터 출력된 전압 지시 신호 CTRL(e)가 입력되고, 인버터(U21)의 출력 단자는 제 1 트랜스퍼 게이트(U22)의 비반전 입력 제어 단자와, 제 2 트랜스퍼 게이트(U23)의 반전 입력 제어 단자가 각각 접속되어 있다.

- <143> 제 1 트랜스퍼 게이트(U22)의 입력 단자에는 전압 VCOMH가 공급된다. 또한, 제 1 트랜스퍼 게이트(U22)의 비반전 입력 제어 단자는 인버터(U21)의 출력 단자에 접속되고, 제 1 트랜스퍼 게이트(U22)의 반전 입력 제어 단자에는 전압 지시 신호 CTRL(e)가 입력된다. 제 2 트랜스퍼 게이트(U23)의 입력 단자에는 전압 VCOML이 공급된다. 또한, 제 2 트랜스퍼 게이트(U23)의 반전 입력 제어 단자는 인버터(U21)의 출력 단자에 접속되고, 제 2 트랜스퍼 게이트(U23)의 비반전 입력 제어 단자에는 전압 지시 신호 CTRL(e)가 입력된다. 그리고 제 1 트랜스퍼 게이트(U22)의 출력 단자 및 제 2 트랜스퍼 게이트(U23)의 출력 단자는 기수 e행 째의 공통선(Z(e))에 공통 접속된다.

- <144> 이 때문에, 기수 e행 째의 제 1 단위 전압 선택 회로(331(e))에 있어서, 전압 지시 신호 CTRL(e)가 H레벨이면, 제 1 트랜스퍼 게이트(U22)가 오프 상태로 되고, 제 2 트랜스퍼 게이트(U23)가 온 상태로 되므로, 해당 제 2 트랜스퍼 게이트(U23)의 입력 단자에 공급된 전압 VCOML이 공통선(Z(e))에 출력된다. 한편, 전압 지시 신호 CTRL(e)가 L레벨이면, 제 1 트랜스퍼 게이트(U22)가 온 상태로 되고, 제 2 트랜스퍼 게이트(U23)가 오프 상태로 되므로, 해당 제 1 트랜스퍼 게이트(U22)의 입력 단자에 공급된 전압 VCOMH가 공통선(Z(e))에 출력된다.

- <145> 즉, 기수 e행 째의 제 1 단위 전압 선택 회로(331(e))는 전압 지시 신호 CTRL(e)가 H레벨이면, 공통선(Z(e))에 전압 VCOML을 공급하는 한편, 전압 지시 신호 CTRL(e)가 L레벨이면, 공통선(Z(e))에 전압 VCOMH를 공급한다.

- <146> 여기서, 전압 VCOMH, COML은 주사선(Y1~Y320)에 인가되는 전압 VGH, VGL에 대하여 VGL<VCOML<VCOMH<VGH라는 관계에 있다(도 11 등 참조).

- <147> 다음에, 제 2 단위 전압 선택 회로(332)에 대하여, f행 째(f는  $2 \leq f \leq 320$ 을 만족하는 우수)에 대응하여 마련된 제 2 단위 전압 선택 회로(332(f))를 이용하여 설명한다.

- <148> 우수 f행 째의 제 2 단위 전압 선택 회로(332(f))는 기수 e행 째의 제 1 단위 전압 선택 회로(331(e))와 비교해서, 제 1 트랜스퍼 게이트(U22)의 입력 단자에 공급되는 전압을 VCOML로 하고, 제 2 트랜스퍼 게이트(U23)의 입력 단자에 입력되는 전압을 VCOMH로, 각각 교체한 관계에 있다. 또, 그 밖의 구성은, 제 1 단위 전압 선택 회로(331(e))와 마찬가지이다.

- <149> 이 때문에, 우수 f 행 째의 제 1 단위 전압 선택 회로(331(e))는, 전압 지시 신호 CTRL(f)가 H레벨이면, 공통선 (Z(e))에 전압 VCOMH를 공급하는 한편, 전압 지시 신호 CTRL(f)가 L레벨이면, 공통선(Z(e))에 전압 VCOML을 공급한다.

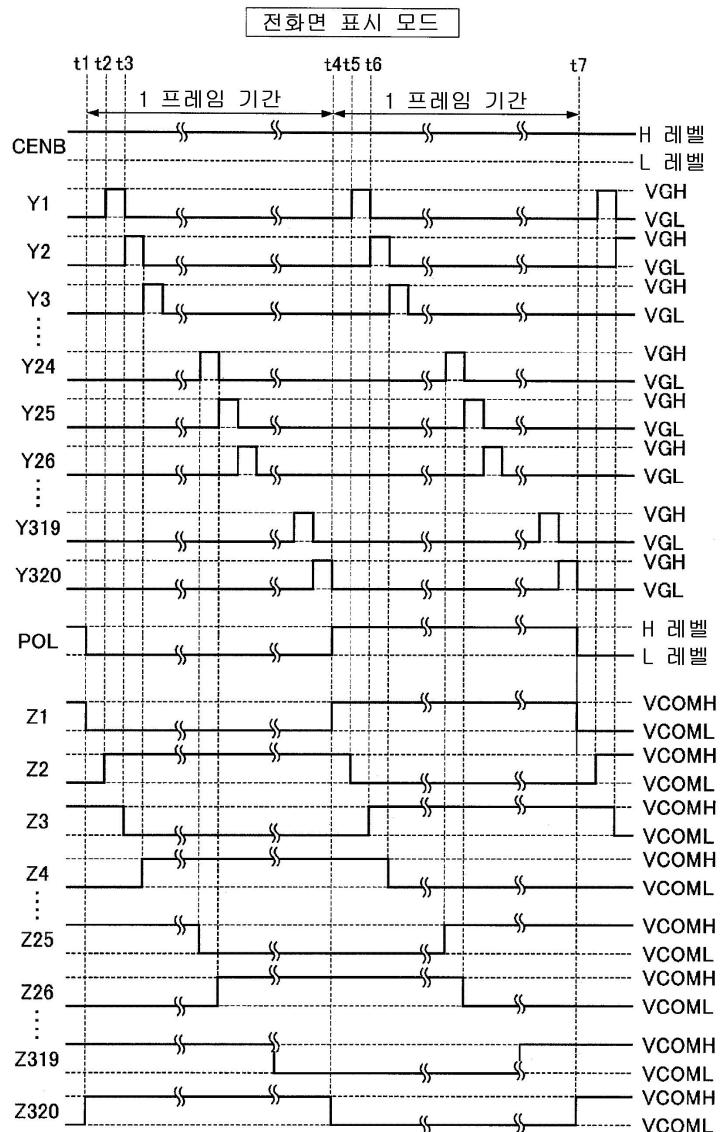

- <150> 다음에, 전 화면 표시 모드에서, 제어 회로(30)에 의해 공통선(Z1~Z320)의 전압이 어떻게 변화되는가에 대하여, 주사선(Y1~Y320)에서의 전압 변화와 관련지어 설명한다. 도 10은 전 화면 표시 모드에서의 제어 회로(30)의 타이밍 차트이다.

- <151> 또, 전 화면 표시 모드에서, 표시 모드 선택 신호 CENB는 H레벨로 고정된다. 또한, 이 도면에서, 전압 VGH는 주사선(Y1~Y320)에 있어서의 선택 전압(H레벨)에 상당하고, 전압 VGL은 주사선(Y1~Y320)에 있어서의 비선택 전압(L레벨)에 상당한다.

- <152> 여기서는, 우선, 공통선(Z1) 및 공통선(Z320)에 주목하여 전 화면 표시 모드에서의 제어 회로(30)의 동작에 대하여 설명한다.

- <153> 1프레임 기간의 개시 타이밍인 시각 t1에서, 극성 신호 POL을 L레벨로 한다. 그렇게 하면, 1,320행 째의 제 1 단위 래치 회로(311)는 L레벨의 극성 신호 POL을 취입하여, L레벨의 래치 신호 LAT1, LAT320을 출력한다. 이 L레벨의 래치 신호 LAT1이 입력되면, 1행 째의 제 1 단위 표시 모드 회로(321)는 H레벨의 전압 지시 신호 CTRL1을 1행 째의 제 2 단위 전압 선택 회로(331)로 출력한다. 또한, L레벨의 래치 신호 LAT320이 입력되면, 320행 째의 제 2 단위 표시 모드 회로(322)는 H레벨의 전압 지시 신호 CTRL320을 320행 째의 제 2 단위 전압 선택 회로(332)로 출력한다. 그렇게 하면, 1행 째의 제 1 단위 전압 선택 회로(331)는 전압 VCOML을 공통선(Z1)에 공급하고, 320행 째의 제 2 단위 전압 선택 회로(332)는 전압 VCOMH를 공통선(Z320)에 공급한다. 이 때문에, 시각 t1에서, 공통선(Z1)은 전압 VCOML로 되고, 공통선(Z320)은 전압 VCOMH로 된다.

- <154> 다음에, 시각 t1로부터 1프레임 기간 경과하여, 다음 1프레임 기간의 개시 타이밍인 시각 t4에 이르렀을 때에, 극성 신호 POL을 반전시켜 H레벨로 한다. 그렇게 하면, 1,320행 째의 각각에 대응하여 마련된 제 1 단위 래치 회로(311)는 H레벨의 극성 신호 POL을 취입하여, H레벨의 래치 신호 LAT1, LAT320을 출력한다. 이 H레벨의 래치 신호 LAT1이 입력되면, 1행 째의 제 1 단위 표시 모드 회로(321)는 L레벨의 전압 지시 신호 CTRL1을 1행 째의 제 1 단위 전압 선택 회로(331)로 출력한다. 또한, H레벨의 래치 신호 LAT320이 입력되면, 320행 째의 제 2 단위 표시 모드 회로(322)는 L레벨의 전압 지시 신호 CTRL320을 320행 째의 제 2 단위 전압 선택 회로(332)로 출력한다. 그렇게 하면, 1행 째의 제 1 단위 전압 선택 회로(331)는 전압 VCOMH를 공통선(Z1)에 공급하고, 320행 째의 제 2 단위 전압 선택 회로(332)는 전압 VCOML을 공통선(Z320)에 공급한다. 이 때문에, 시각 t4에서, 공통선(Z1)은 전압 VCOMH로 되고, 공통선(Z320)은 전압 VCOML로 된다.

- <155> 그리고 시각 t4로부터 1프레임 기간 더 경과하여, 다음 1프레임 기간의 개시 타이밍인 시각 t7에 이르렀을 때에, 극성 신호 POL을 재반전시켜 L레벨로 되돌린다. 그렇게 하면, 시각 t1과 마찬가지로, 주사선(Y1)에 대응하여 마련된 제 1 단위 전압 선택 회로(331)는 전압 VCOML을 공통선(Z1)에 공급하고, 주사선(Y320)에 대응하여 마련된 제 2 단위 전압 선택 회로(332)는 전압 VCOMH를 공통선(Z320)에 공급한다. 이 때문에, 시각 t7에서, 공통선(Z1)은 전압 VCOML로 되고, 공통선(Z320)은 전압 VCOMH로 된다.

- <156> 다음에, 공통선(Z2)에 주목하여, 제어 회로(30)의 동작에 대하여 설명한다.

- <157> 시각 t1로부터 1수평 주사 기간 경과한 시각 t2에 이르면, 주사선 구동 회로(10)는 주사선(Y1)에 선택 전압을 공급하여, 전압 VGH로 한다.

- <158> 여기서, 2행 째의 제 2 단위 래치 회로(312)로부터 보면, 하나 위의 행의 주사선(Y1)에 선택 전압이 인가된 것으로 되므로, 해당 2행 째의 제 2 단위 래치 회로(312)는 L레벨의 극성 신호 POL을 취입하여, L레벨의 래치 신호 LAT2를 출력한다. 이 L레벨의 래치 신호 LAT2가 입력되면, 2행 째의 제 2 단위 표시 모드 회로(322)는 H레벨의 전압 지시 신호 CTRL2를 2행 째의 제 2 단위 전압 선택 회로(332)로 출력한다. 그렇게 하면, 2행 째의 제 2 단위 전압 선택 회로(332)는 전압 VCOMH를 공통선(Z2)에 공급한다. 이 때문에, 공통선(Z2)의 전압은 시각 t2에서 전압 VCOMH로 된다.

- <159> 또, 시각 t2로부터 1수평 주사 기간 경과하여 시각 t3에 이르면, 주사선(Y1)이 전압 VGL로 되고, 주사선(Y2)이 전압 VGH로 되어, 주사선(Y1, Y3)이 모두 비선택 전압으로 된다. 이 때문에, 2행 째의 제 2 단위 래치 회로(312)로부터 보면, 하나 위의 행의 주사선(Y1)과 하나 아래의 행의 주사선(Y3)의 양쪽이 비선택 전압으로 되므로, 해당 2행 째의 제 2 단위 래치 회로(312)는 L레벨의 래치 신호 LAT2를 유지·출력하는 것으로 되어, 공통선

(Z2)은 전압 VCOMH로 유지된다.

<160> 시각 t3으로부터 1수평 주사 기간 경과하면, 주사선(Y2)이 전압 VGL로 되고, 주사선(Y3)이 전압 VGH로 된다. 이 때문에, 2행 째의 제 2 단위 래치 회로(312)로부터 보면, 하나 아래의 행의 주사선(Y3)에 선택 전압이 인가된 것으로 되므로, 해당 2행 째의 제 2 단위 래치 회로(312)는 L레벨의 극성 신호 POL을 재차 취입하여, L레벨의 래치 신호 LAT2를 출력한다. 이 때문에, 공통선(Z2)의 전압 VCOMH로 된다.

<161> 주사선(Y3)이 전압 VGH로 되고 나서 1수평 주사 기간 경과하면, 주사선(Y3)이 전압 VGL로 된다. 이 때, 주사선(Y1)은 이미 시각 t3에서 전압 VGL로 되어 있다. 이 때문에, 2행 째의 제 2 단위 래치 회로(312)로부터 보면, 주사선(Y2)이 전압 VGH로 되었을 때 마찬가지로, L레벨의 래치 신호 LAT2를 유지·출력하는 것으로 되어, 공통선(Z2)은 전압 VCOMH로 유지되게 된다.

<162> 다음 프레임 기간에서, 주사선 구동 회로(10)가 주사선(Y1)에 선택 전압을 공급하여, 주사선(Y1)의 전압을 전압 VGH로 하는 시각 t5에서는, 2행 째의 제 2 단위 래치 회로(312)는 H레벨의 극성 신호 POL을 취입하여, H레벨의 래치 신호 LAT2를 출력한다. 이 H레벨의 래치 신호 LAT2가 입력되면, 2행 째의 단위 표시 모드 회로(322)는 L레벨의 전압 지시 신호 CTRL2를 2행 째의 제 2 단위 전압 선택 회로(332)로 출력한다. 그렇게 하면, 주사선(Y2)에 대응하여 마련된 제 2 단위 전압 선택 회로(332)는 전압 VCOML을 공통선(Z2)에 공급한다. 이 때문에, 시각 t5에서, 공통선(Z2)은 전압 VCOMH에서 전압 VCOML로 바뀐다.

<163> 전압 VCOML에 바뀌면, 차례대로의 프레임 기간에서 주사선(Y1)이 다시 선택 전압인 VGH로 될 때까지, 공통선(Z2)은 전압 VCOML로 유지된다.

<164> 다음에, 공통선(Z3)에 주목하여, 제어 회로(30)의 동작에 대하여 설명한다.

<165> 시각 t3에서, 주사선(Y2)이 전압 VGH로 되면, 3행 째의 제 2 단위 래치 회로(312)로부터 보면, 하나 위의 행의 주사선(Y2)에 선택 전압이 인가된 것으로 되므로, 해당 3행 째의 제 2 단위 래치 회로(312)는 L레벨의 극성 신호 POL을 취입하여, L레벨의 래치 신호 LAT3을 출력한다. 이 L레벨의 래치 신호 LAT3이 입력되면, 3행 째의 제 1 단위 표시 모드 회로(321)는 H레벨의 전압 지시 신호 CTRL3을 3행 째의 제 1 단위 전압 선택 회로(331)로 출력한다. 그렇게 하면, 3행 째의 제 1 단위 전압 선택 회로(331)는 전압 VCOML을 공통선(Z3)에 공급한다. 이 때문에, 공통선(Z3)은 시각 t3에서 전압 VCOML로 된다. 또, 공통선(Z3)은 다음 프레임 기간의 시각 t6에서 주사선(Y2)이 다시 전압 VGH로 될 때까지, 전압 VCOML로 유지되게 된다.

<166> 다음 프레임 기간의 시각 t6에서, 주사선(Y2)이 다시 전압 VGH로 되면, 3행 째의 제 2 단위 래치 회로(312)는 H레벨의 극성 신호 POL을 취입하여, H레벨의 래치 신호 LAT3을 출력한다. 이 H레벨의 래치 신호 LAT3이 입력되면, 3행 째의 제 1 단위 표시 모드 회로(321)는 L레벨의 전압 지시 신호 CTRL3을 3행 째의 제 1 단위 전압 선택 회로(331)로 출력한다. 그렇게 하면, 3행 째의 제 1 단위 전압 선택 회로(331)는 전압 VCOMH를 공통선(Z3)에 공급한다. 이 때문에, 시각 t6에서, 공통선(Z3)은 전압 VCOML에서 전압 VCOMH로 바뀐다. 전압 VCOMH로 바뀌면, 차례대로의 프레임 기간에서 주사선(Y1)이 다시 선택 전압인 VGH로 될 때까지, 공통선(Z3)은 전압 VCOMH로 유지된다.

<167> 여기서, 공통선(Z1~Z320) 중, 이미 설명한 공통선(Z1, Z3)을 제외하는 기수행 째의 공통선(Z(g))(g는  $5 \leq g \leq 319$ 를 만족하는 기수)에 대한 제어 회로(30)의 동작을 설명한다.

<168> 제어 회로(30)는 주사선(Y2)에 선택 전압이 공급되는데 동기하여 공통선(Z3)에 전압 VCOMH를 공급한 경우, 동일한 1프레임 기간에서, 주사선(Y(g-1))에 선택 전압이 공급되는데 동기하여, 공통선(Z(g))에 전압 VCOMH를 공급하고, 이후, 다음 프레임의 기간에서 주사선(Y(g-1))에 선택 전압이 다시 공급될 때까지, 공통선(Z(g))을 해당 전압 VCOML로 유지한다.

<169> 한편, 제어 회로(30)는 주사선(Y2)에 선택 전압이 공급되는데 동기하여 공통선(Z3)에 전압 VCOML을 공급한 경우, 동일한 1프레임 기간에서, 주사선(Y(g-1))에 선택 전압이 공급되는데 동기하여, 공통선(Z(g))에 전압 VCOML을 공급하고, 이후, 다음 프레임의 기간에서 주사선(Y(g-1))에 선택 전압이 다시 공급될 때까지, 공통선(Z(g))을 해당 전압 VCOMH로 유지한다.

<170> 다음에, 공통선(Z1~Z320) 중, 이미 설명한 공통선(Z2, Z320)을 제외하는 우수행 째의 공통선(Z(h))(h는  $4 \leq h \leq 318$ 을 만족하는 우수)에 대한 제어 회로(30)의 동작을 설명한다.

<171> 제어 회로(30)는 주사선(Y1)에 선택 전압이 공급되는데 동기하여 공통선(Z2)에 전압 VCOMH를 공급한 경우, 동일한 1프레임 기간에서, 공통선(Z(h))에, 주사선(Y(h-1))에 선택 전압이 공급되는데 동기하여, 전압 VCOMH를 공급

하고, 이후, 다음 프레임의 기간에서 주사선(Y(h-1))에 선택 전압이 다시 공급될 때까지, 공통선(Z(h))을 해당 전압 VCOMH로 유지한다.

<172> 한편, 제어 회로(30)는 주사선(Y1)에 선택 전압이 공급되는데 동기하여 공통선(Z2)에 전압 VCOML을 공급한 경우, 동일한 1프레임 기간에서, 주사선(Y(h-1))에 선택 전압이 공급되는데 동기하여, 공통선(Z(h))에 전압 VCOML을 공급하고, 이후, 다음 프레임의 기간에서 주사선(Y(h-1))에 선택 전압이 다시 공급될 때까지, 공통선(Z(g))을 해당 전압 VCOMH로 유지한다.

<173> 즉, 공통선은 대응하는 주사선에 선택 전압이 인가되는 타이밍보다 전(1수평 주사 기간 전)에, 전압 VCOMH 또는 전압 VCOML의 한쪽으로부터 다른쪽으로 바뀌는 구성으로 되어있다.

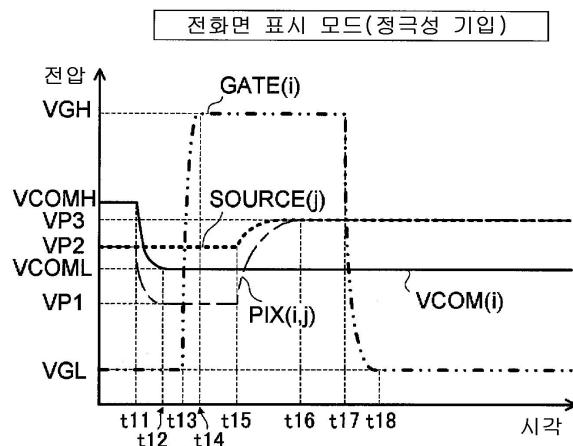

<174> 다음에, 이러한 제어 회로(30)를 갖는 액정 장치(1)의 전 화면 표시 모드에서의 동작에 대하여 설명한다. 전 화면 모드에서, 도 11은 정극성 기입 시의 각 부 전압의 파형을 나타내는 도면이고, 도 12는 부극성 기입 시의 각 부 전압의 파형을 나타내는 도면이다.

<175> 도 11 및 도 12에서, GATE(i)는 i행 째(i는  $1 \leq i \leq 320$ 을 만족하는 정수)의 주사선(Y(i))의 전압이며, SOURCE(j)는 j열 째(j는  $1 \leq j \leq 240$ 을 만족하는 정수)의 데이터선(X(j))의 전압이다. 또한, PIX(i, j)는 i행 째 주사선(Y(i))과, j열 째 데이터선(X(j))의 교차에 대응하여 마련된 i행 j열의 화소(50)가 구비하는 화소 전극(55)의 전압이다. 또한, VCOM(i)은 i행 째의 공통선(Z(i))의 전압이다.

<176> 우선, 도 11을 이용하여, 전 화면 표시 모드에서의 정극성 기입 시의 동작에 대하여 설명한다.

<177> 정극성 기입이 실행되는 경우, i행 째 주사선(Y(i))의 전압 GATE(i)을 선택 전압 VGH로 하기 전의 시각 t11에서, 제어 회로(30)는 공통선(Z(i))에 전압 VCOML을 공급한다. 이 때문에, 공통선(Z(i))의 전압 VCOM(i)은 전압 VCOMH에서 서서히 저하하여, 시각 t12에서 전압 VCOML로 된다.

<178> 여기서, 시각 t11에서는, 주사선(Y(i))의 전압 GATE(i)은 비선택 전압 VGL이며, TFT(51)가 오프 상태이므로, j열 째 데이터선(X(j))과 i행 j열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태에 있다. 또한, i행 j열의 화소(50)가 구비하는 화소 전극(55)과, 공통선(Z(i))인 공통 전극(56) 사이에는, 축적 용량(53) 및 화소 용량(54)에 의해 용량 결합이 발생하고 있다.

<179> 이 때문에, i행 j열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(i, j)는 전압 VCOM(i)과 전압 PIX(i, j)의 전위차를 유지하도록 저하하여, 시각 t12에서는 전압 VP1로 된다.

<180> 다음에, 시각 t13에서, 주사선 구동 회로(10)에 의해, 주사선(Y(i))에 선택 전압이 공급된다. 이 때문에, 주사선(Y(i))의 전압 GATE(i)은 상승하고, 시각 t14에서 전압 VGH로 된다. 이에 따라, 주사선(Y(i))에 게이트가 접속된 TFT(51)가 모두 온 상태로 된다.

<181> 주사선(Y(i))의 전압 GATE(i)가 선택 전압 VGH인 시각 t15에서, 데이터선 구동 회로(20)가 데이터선(X(j))에 정극성의 화상 신호를 공급한다. 그렇게 하면, 데이터선(X(j))의 전압 SOURCE(j)은 상승하여, 시각 t16에서 전압 VP3으로 된다.

<182> 데이터선(X(j))의 전압 SOURCE(j)은 정극성의 화상 신호에 근거하는 화상 전압으로서, 주사선(Y(i))에 게이트 접속된 온 상태의 TFT(51)를 거쳐, i행 j열의 화소(50)가 구비하는 화소 전극(55)에 기입된다. 이 때문에, i행 j열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(i, j)는 상승하여, 시각 t16에서는, 데이터선(X(j))의 전압 SOURCE(j)과 동 전위인 전압 VP3으로 된다.

<183> 시각 t17에서, 주사선 구동 회로(10)에 의해, 주사선(Y(i))에 인가되는 전압이 선택 전압으로부터 비선택 전압으로 바뀐다. 그렇게 하면, 주사선(Y(i))의 전압 GATE(i)은 저하하여, 시각 t18에서는 전압 VGL로 된다. 이에 따라, 주사선(Y(i))에 게이트가 접속된 TFT(51)가 모두 오프 상태로 된다.

<184> 또, TFT(51)가 오프 상태가 되더라도, 화소 용량(54)은 자신 및 축적 용량(53)의 용량성에 의해, 화소 전극(55)에 기입된 전압 PIX(i, j)와 공통선(Z(i))의 전압 VCOM(i)의 차 전압을 유지하는 것으로 된다.

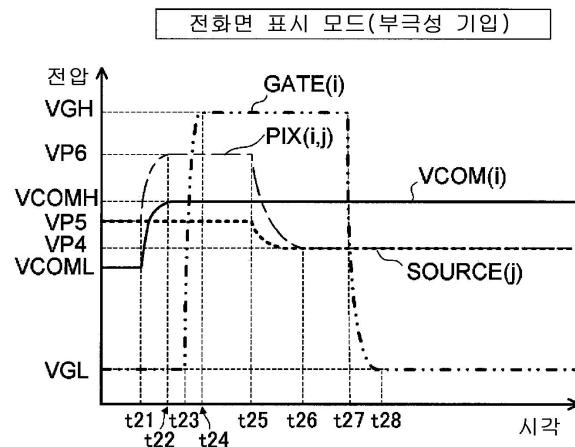

<185> 다음에, 도 12를 이용하여, 전 화면 표시 모드에서의 부극성 기입 시의 동작에 대하여 설명한다.

<186> 부극성 기입이 실행되는 경우, i행 째 주사선(Y(i))의 전압 GATE(i)를 선택 전압 VGH로 하기 전의 시각 t21에서, 제어 회로(30)는 공통선(Z(i))에 전압 VCOMH를 공급한다. 이 때문에, 공통선(Z(i))의 전압 VCOM(i)은 서서히 전압 VCOMH로부터 상승하여, 시각 t22에서 전압 VCOMH로 된다.

- <187> 여기서, 시각 t21에서는, 주사선(Y(i))의 전압 GATE(i)은 비선택 전압 VGL이며, TFT(51)가 오프 상태이므로, j 열 째 데이터선(X(j))과 i 행 j 열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태에 있다. 또한, i 행 j 열의 화소(50)가 구비하는 화소 전극(55)과 공통선(Z(i))인 공통 전극(56) 사이에는, 용량 결합이 발생하고 있다.

- <188> 이 때문에, i 행 j 열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(i, j)는 전압 VCOM(i)과 전압 PIX(i, j)의 전위차를 유지하도록 상승하여, 시각 t22에서는 전압 VP6으로 된다.

- <189> 시각 t23에서, 주사선 구동 회로(10)에 의해, 주사선(Y(i))에 인가되는 전압이 비선택 전압으로부터 선택 전압으로 바뀐다. 그렇게 하면, 주사선(Y(i))의 전압 GATE(i)은 상승하고, 시각 t24에서는 전압 VGH로 된다. 이에 따라, 주사선(Y(i))에 게이트가 접속된 TFT(51)가 모두 온 상태로 된다.

- <190> 주사선(Y(i))의 전압 GATE(i)가 선택 전압 VGH인 시각 t25에서, 데이터선 구동 회로(20)가 데이터선(X(j))에 부극성의 화상 신호를 공급한다. 그렇게 하면, 데이터선(X(j))의 전압 SOURCE(j)는 저하하여, 시각 t26에서는 전압 VP4로 된다.

- <191> 데이터선(X(j))의 전압 SOURCE(j)은 부극성의 화상 신호에 근거하는 화상 전압으로서, 주사선(Y(i))에 게이트가 접속된 온 상태의 TFT(51)를 거쳐, i 행 j 열의 화소(50)가 구비하는 화소 전극(55)에 기입된다. 이 때문에, i 행 j 열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(i, j)는 저하하여, 시각 t26에서는, 데이터선(X(j))의 전압 SOURCE(j)와 동 전위인 전압 VP4로 된다.

- <192> 시각 t27에서, 주사선 구동 회로(10)에 의해, 주사선(Y(i))에 인가되는 전압이 선택 전압으로부터 비선택 전압으로 바뀐다. 그렇게 하면, 주사선(Y(i))의 전압 GATE(i)은 저하하여, 시각 t28에서는 전압 VGL로 된다. 이에 따라, 주사선(Y(i))에 게이트가 접속된 TFT(51)가 모두 오프 상태로 된다.

- <193> 또, TFT(51)가 오프 상태가 되더라도, 화소 용량(54)은 자신 및 축적 용량(53)의 용량성에 의해, 화소 전극(55)에 기입된 전압 PIX(i, j)와 공통선(i)의 전압 VCOM(i)의 차 전압을 유지하는 것으로 된다.

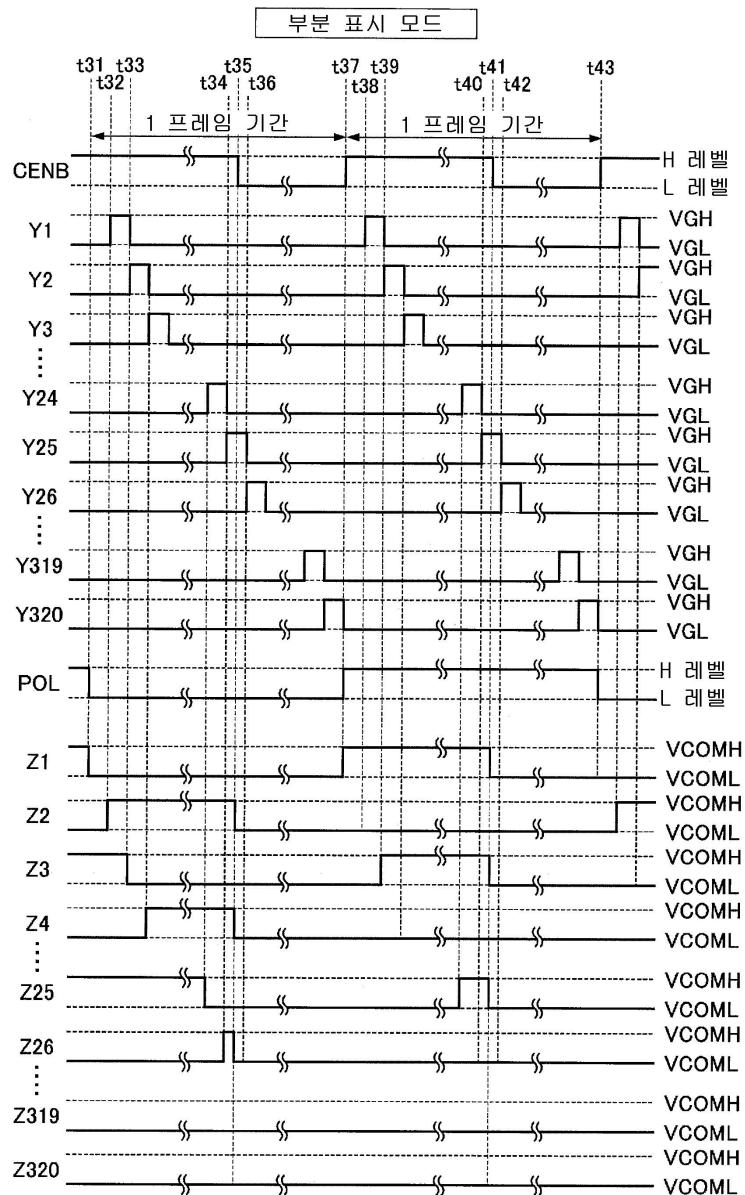

- <194> 다음에, 부분 표시 모드에서의 제어 회로(30)의 동작에 대하여 설명한다. 도 13은 부분 표시 모드에서의 제어 회로(30)의 동작을 나타내는 도면으로, 주사선의 선택에 대하여 공통선의 전압이 어떻게 변화되는가를 나타내는 도면이다.

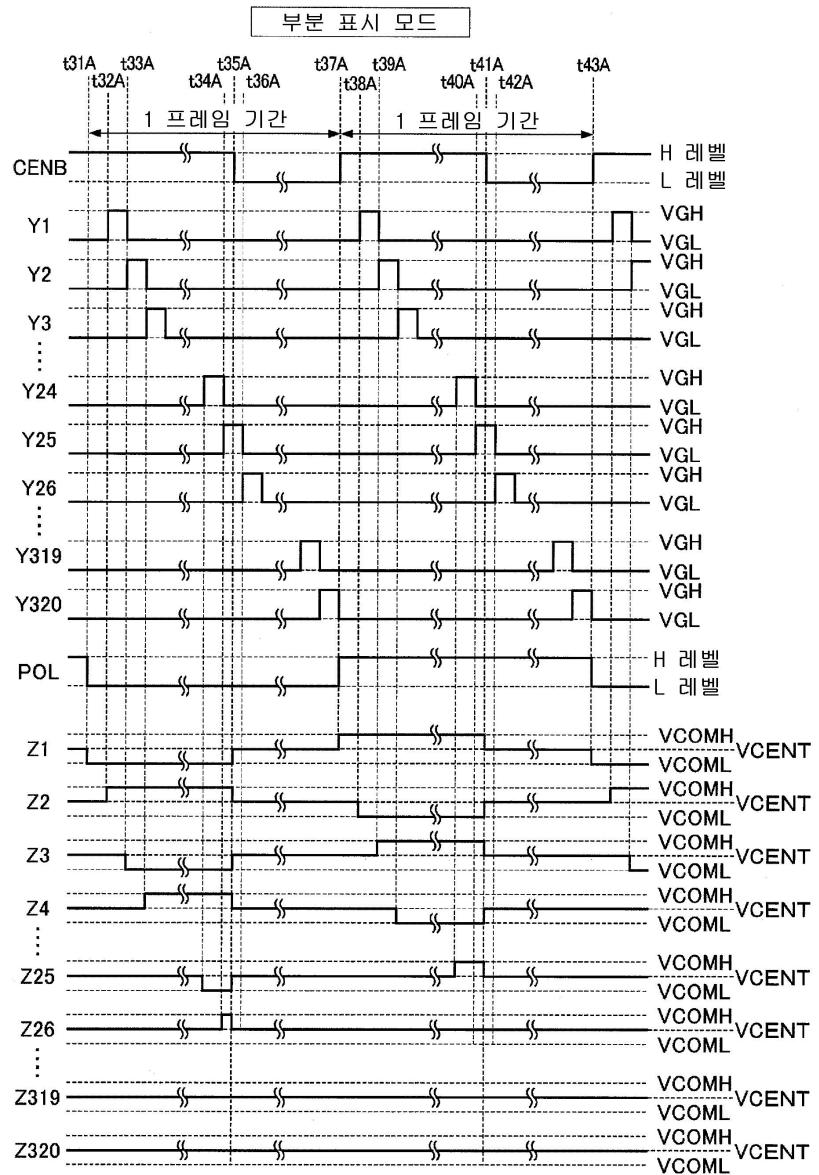

- <195> 또, 부분 표시 모드에서, 표시 모드 선택 신호 CENB는 비표시 영역(82)의 개시행보다 1행전의 주사선에 선택 전압이 인가되는 기간 도중부터, 비표시 영역(82)의 최종행 째의 주사선에 선택 전압이 인가되는 기간의 종료까지에 걸쳐 L레벨로 되고, 다른 기간에는 H레벨로 된다. 실시예 1에서는, 표시 영역(81)에 관한 화소(50)를 1~25 행 째로 하고, 비표시 영역(82)에 관한 화소(50)를 26~320 행 째로 하고 있으므로, 표시 모드 선택 신호 CENB는, 도 13에 나타내는 바와 같이, 시각 t35로부터 t37까지의 기간 및 시각 t41~t43까지의 기간에 걸쳐 L레벨로 된다.

- <196> 또, 표시 모드 선택 신호 CENB에 대해서는, 비표시 영역(82)의 개시행의 주사선에 선택 전압이 인가되는 기간으로부터, L레벨로 변화되는 구성으로 하여도 좋다.

- <197> 우선, 공통선(Z1)에 주목하여, 부분 표시 모드에서의 제어 회로(30)의 동작에 대하여 설명한다.

- <198> 1프레임 기간의 개시 타이밍인 시각 t31에서, 극성 신호 POL을 L레벨로 한다. 시각 t31에서는, 표시 모드 선택 신호 CENB가 H레벨이므로, 도 10의 시각 t1과 마찬가지로, 1행 째의 제 1 단위 전압 선택 회로(331)는 전압 VCOML을 공통선(Z1)에 공급한다. 이 때문에, 공통선(Z1)은 전압 VCOML로 된다.

- <199> 시각 t35에서, 표시 모드 선택 신호 CENB가 L레벨이 되면, 1행 째의 제 1 단위 표시 모드 회로(321)는 H레벨의 전압 지시 신호 CTRL1을 1행 째의 제 1 단위 전압 선택 회로(331)로 출력하므로, 해당 1행 째의 제 1 단위 전압 선택 회로(331)는 소정의 전압으로서의 전압 VCOML을 공통선(Z1)에 공급한다. 이 때문에, 공통선(Z1)은 전압 VCOML을 유지한다.

- <200> 다음 프레임 기간의 개시 타이밍인 시각 t37에서, 극성 신호 POL을 H레벨로 한다. 여기서, 시각 t37에서는, 표시 모드 선택 신호 CENB가 H레벨로 되므로, 도 10의 시각 t4와 마찬가지로, 1행 째의 제 1 단위 전압 선택 회로(331)는 전압 VCOMH를 공통선(Z1)에 공급한다. 이 때문에, 공통선(Z1)은 전압 VCOMH로 된다.

- <201> 시각 t41에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 1행 째의 제 1 단위 표시 모드 회로(321)는 H레벨의 전압 지시 신호 CTRL1을 1행 째의 제 1 단위 전압 선택 회로(331)로 출력하므로, 해당 1행 째의 제 1 단위 전압

선택 회로(331)는 소정의 전압으로서의 전압 VCOML을 공통선(Z1)에 공급한다. 이 때문에, 공통선(Z1)은 전압 VCOML로 된다.

<202> 또, 차례대로의 프레임 기간의 개시 타이밍인 시각 t43에서, 극성 신호 POL을 L레벨로 한다. 여기서, 시각 t43에서는, 표시 모드 선택 신호 CENB가 H레벨로 되므로, 도 10의 시각 t7과 마찬가지로, 1행 째의 제 1 단위 선택 회로(331)는 전압 VCOML을 공통선(Z1)에 공급한다. 이 때문에, 공통선(Z1)은 전압 VCOML을 유지한다.

<203> 다음에, 공통선(Z2)에 주목하여, 제어 회로(30)의 동작에 대하여 설명한다.

<204> 시각 t31로부터 1수평 주사 기간 경과한 시각 t32에 이르면, 주사선 구동 회로(10)는 주사선(Y1)에 선택 전압을 공급하여, 전압 VGH로 한다. 여기서, 시각 t32에서는, 표시 모드 선택 신호 CENB가 H레벨이므로, 도 10의 시각 t2와 마찬가지로, 2행 째의 제 2 단위 선택 회로(332)는 전압 VCOMH를 공통선(Z2)에 공급한다. 이 때문에, 공통선(Z2)은 전압 VCOMH로 된다.

<205> 시각 t35에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 2행 째의 제 2 단위 표시 모드 회로(322)는 L레벨의 전압 지시 신호 CTRL2를 2행 째의 제 2 단위 전압 선택 회로(332)로 출력하므로, 해당 2행 째의 제 2 단위 전압 선택 회로(332)는 소정의 전압으로서의 전압 VCOML을 공통선(Z2)에 공급한다. 이 때문에, 공통선(Z2)은 전압 VCOML로 된다.

<206> 다음 프레임 기간의 시각 t38에서, 주사선(Y1)의 전압이 전압 VGH로 되면, 이 시각 t38에서는, 표시 모드 선택 신호 CENB가 H레벨이므로, 도 10의 시각 t5와 마찬가지로, 2행 째의 제 2 단위 전압 선택 회로(332)는 전압 VCOML을 공통선(Z2)에 공급한다. 이 때문에, 공통선(Z2)은 전압 VCOML을 유지한다.

<207> 시각 t41에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 2행 째의 제 2 단위 표시 모드 회로(322)는 L레벨의 전압 지시 신호 CTRL2를 2행 째의 제 2 단위 전압 선택 회로(332)로 출력하므로, 해당 2행 째의 제 2 단위 전압 선택 회로(332)는 소정의 전압으로서의 전압 VCOML을 공통선(Z2)에 공급한다. 이 때문에, 공통선(Z2)은 전압 VCOML을 유지한다.

<208> 다음에, 공통선(Z3)에 주목하여, 제어 회로(30)의 동작에 대하여 설명한다.

<209> 시각 t32로부터 1수평 주사 기간 경과한 시각 t33에 이르면, 주사선 구동 회로(10)는 주사선(Y2)에 선택 전압을 공급하여, 전압 VGH로 한다. 여기서, 시각 t33에서는, 표시 모드 선택 신호 CENB가 H레벨이므로, 도 10의 시각 t3과 마찬가지로, 전압 VCOML을 공통선(Z3)에 공급한다. 이 때문에, 공통선(Z3)은 전압 VCOML로 된다.

<210> 시각 t35에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 3행 째의 제 1 단위 표시 모드 회로(321)는 H레벨의 전압 지시 신호 CTRL3를 3행 째의 제 1 단위 전압 선택 회로(331)로 출력하므로, 해당 3행 째의 제 1 단위 전압 선택 회로(331)는 소정의 전압으로서의 전압 VCOML을 공통선(Z3)에 공급한다. 이 때문에, 공통선(Z3)은 전압 VCOML을 유지한다.

<211> 다음 프레임 기간의 시각 t39에서, 주사선(Y2)의 전압이 전압 VGH가 되면, 이 시각 t39에서는, 표시 모드 선택 신호 CENB가 H레벨이므로, 도 10의 시각 t6과 마찬가지로, 3행 째의 제 1 단위 전압 선택 회로(331)는 전압 VCOMH를 공통선(Z3)에 공급한다. 이 때문에, 공통선(Z3)은 전압 VCOMH로 된다.

<212> 시각 t41에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 3행 째의 제 1 단위 표시 모드 회로(321)는 H레벨의 전압 지시 신호 CTRL3를 3행 째의 제 1 단위 전압 선택 회로(331)로 출력하므로, 해당 3행 째의 제 1 단위 전압 선택 회로(331)는 소정의 전압으로서의 전압 VCOML을 공통선(Z3)에 공급한다. 이 때문에, 공통선(Z3)은 전압 VCOML로 된다.

<213> 다음에, 표시 영역(81)에 따른 1~25행 째에 대응한 공통선(Z1~Z25) 중, 이미 설명한 공통선(Z1, Z3)을 제외하는 기수행 째의 공통선(Z(k))(k는  $5 \leq g \leq 25$ 를 만족하는 기수)에 대한 제어 회로(30)의 동작을 설명한다.

<214> 제어 회로(30)는 주사선(Y2)에의 선택 전압의 공급에 동기하여 공통선(Z3)에 전압 VCOMH를 공급한 경우, 동일한 1프레임 기간에서, 공통선(Z(k))에, 주사선(Y(k-1))에의 선택 전압의 공급에 동기하여, 전압 VCOMH를 공급한다. 한편, 제어 회로(30)는 주사선(Y2)에의 선택 전압의 공급에 동기하여 공통선(Z3)에 전압 VCOML을 공급한 경우, 동일한 1프레임 기간에서, 공통선(Z(k))에, 주사선(Y(k-1))에의 선택 전압의 공급에 동기하여, 전압 VCOML을 공급한다. 또, 제어 회로(30)는 표시 모드 선택 신호 CENB가 L레벨이 되는데 동기하여, 공통선(Z(k))에 소정의 전압으로서의 전압 VCOML을 공급한다.

<215> 계속해서, 표시 영역(81)에 대한 1~25행 째에 대응한 공통선(Z1~Z25) 중, 이미 설명한 공통선(Z2)을 제외하는

우수행 째의 공통선(Z(m))(m은  $4 \leq m \leq 24$ 를 만족하는 우수)에 대한 제어 회로(30)의 동작을 설명한다.

<216> 제어 회로(30)는 주사선(Y1)에의 선택 전압의 공급에 동기하여 공통선(Z2)에 전압 VCOMH를 공급한 경우, 동일한 1프레임 기간에서, 공통선(Z(m))에, 주사선(Y(m-1))에의 선택 전압의 공급에 동기하여, 전압 VCOMH를 공급한다. 한편, 제어 회로(30)는 주사선(Y1)에의 선택 전압의 공급에 동기하여 공통선(Z2)에 전압 VCOML을 공급한 경우, 동일한 1프레임 기간에서, 공통선(Z(m))에, 주사선(Y(m-1))에의 선택 전압의 공급에 동기하여, 전압 VCOML을 공급한다. 또, 제어 회로(30)는 표시 모드 선택 신호 CENB가 L레벨로 되는데 동기하여, 공통선(Z(m))에 소정의 전압으로서의 전압 VCOML을 공급한다.

<217> 다음에, 비표시 영역(82)에 관한 26~320행 째에 대응한 공통선(Z26~Z320)에 대한 제어 회로(30)의 동작을 설명한다.

<218> 우선, 비표시 영역(82)에서, 가장 위에 위치하는 26행 째의 공통선(Z26)에 대한 제어 회로(30)의 동작을 설명하지만, 이 동작은, 상술한 표시 영역(81)에 있어서의 우수행의 공통선(Z(m))에 대한 동작과 마찬가지이다. 즉, 제어 회로(30)는, 주사선(Y1)에의 선택 전압의 공급에 동기하여 공통선(Z2)에 전압 VCOMH를 공급한 경우, 동일한 1프레임 기간에서, 공통선(Z26)에, 주사선(Y25)에의 선택 전압의 공급에 동기하여, 전압 VCOMH를 공급하는 한편, 주사선(Y1)에의 선택 전압의 공급에 동기하여 공통선(Z2)에 전압 VCOML을 공급한 경우, 동일한 1프레임 기간에서, 공통선(Z26)에, 주사선(Y25)에의 선택 전압의 공급에 동기하여, 전압 VCOML을 공급한다. 또, 제어 회로(30)는 표시 모드 선택 신호 CENB가 L레벨로 되는데 동기하여, 공통선(Z26)에 소정의 전압으로서의 전압 VCOML을 공급한다.

<219> 계속해서, 비표시 영역(82)에서, 가장 위에 위치하는 26행 째 이외의 27~320행 째의 공통선(Z27~Z320)에 대한 제어 회로(30)의 동작에 대하여, 공통선(Z(n))(n은  $27 \leq n \leq 320$ 을 만족하는 정수)로 일반화하여 설명한다.

<220> 주사선(Y(n-1))에 선택 전압이 공급되는 시각과, 주사선(Y(n+1))에 선택 전압이 공급되는 시각에, 표시 모드 선택 신호 CENB는 모두 L레벨이므로, 제어 회로(30)는 공통선(Z(n))에 전압 VCOML의 공급을 계속한다.

<221> 다음에, 액정 장치(1)의 부분 표시 모드에서의 동작에 대하여 설명한다.

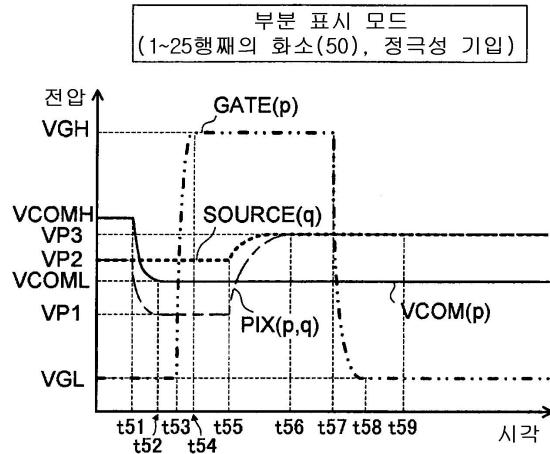

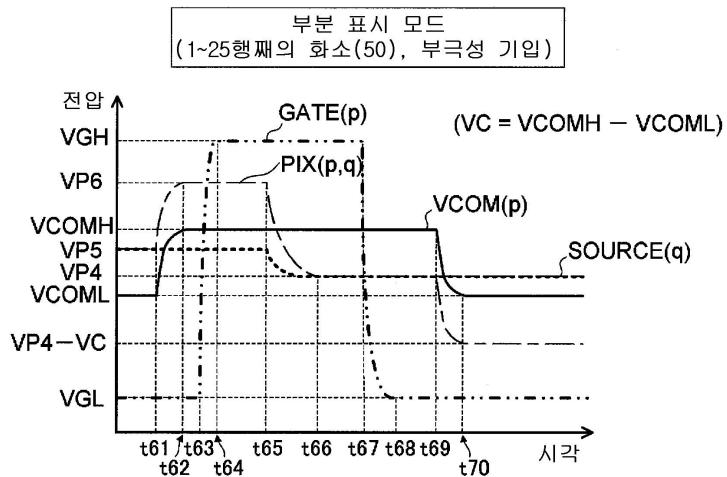

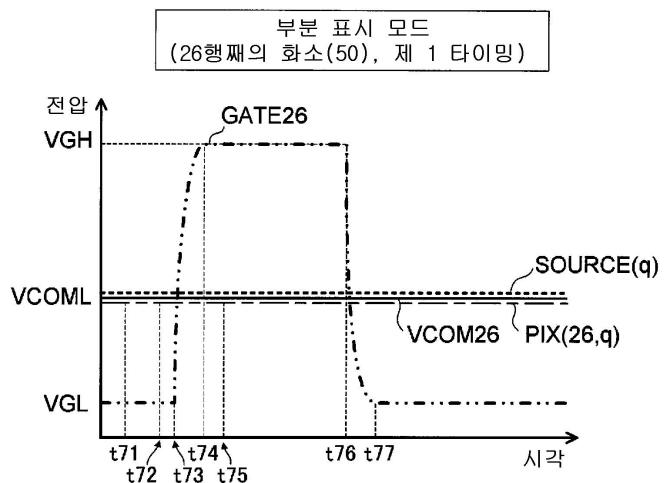

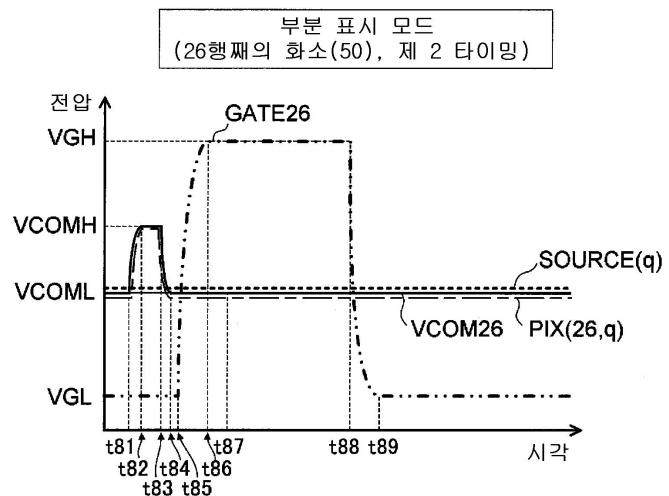

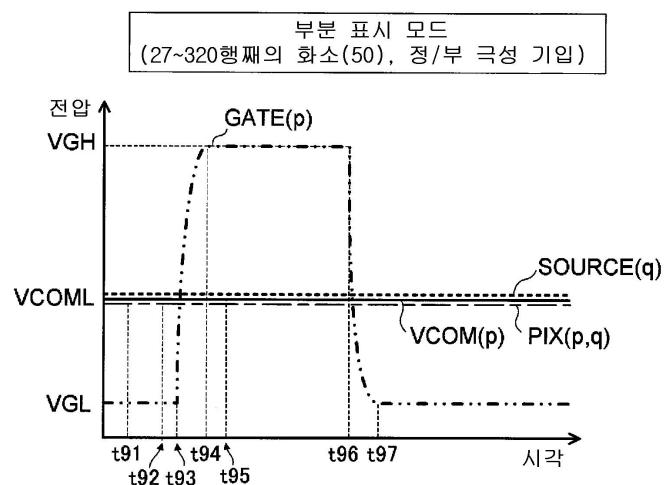

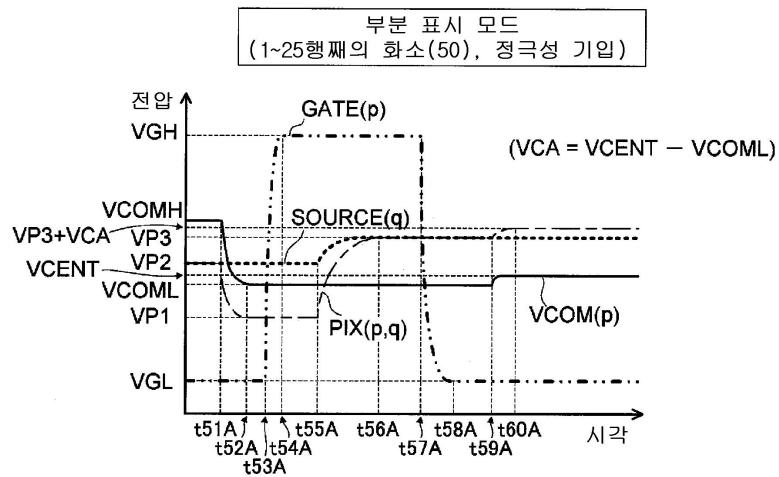

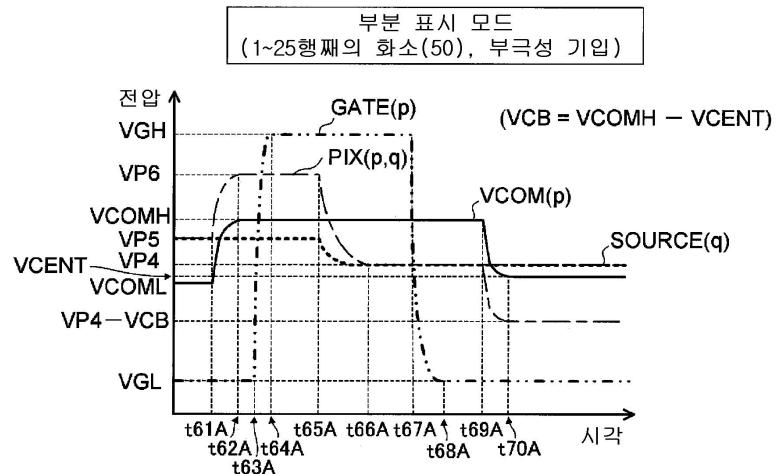

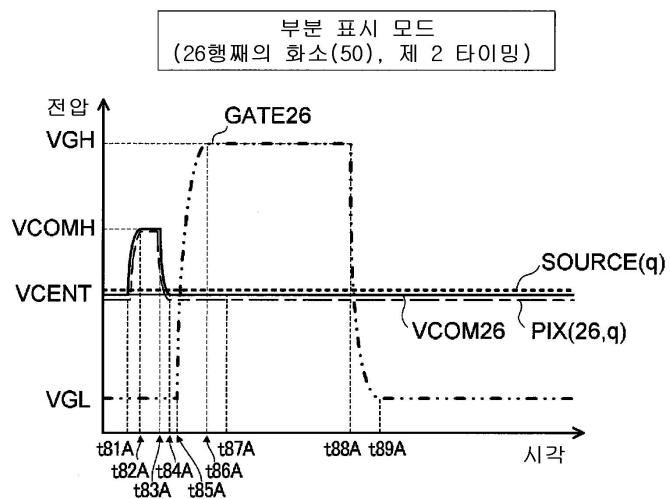

<222> 액정 장치(1)의 부분 표시 모드에서, 표시 영역(81)에 관한 1행 째~25행 째의 화소(50)에 대하여 전압 기입을 하는 경우에, 도 14는 정극성 기입 시의 각 부 전압의 파형을 나타내는 도면이고, 도 15는 부극성 기입 시의 각 부 전압의 파형을 나타내는 도면이다. 도 16 및 도 17은, 각각 부분 표시 모드에서, 비표시 영역(82)으로 가장 위에 위치하는(26)행의 화소(50)에 대하여 전압 기입을 행하는 경우의 각 부 전압의 파형을 나타내는 도면이다. 또한, 도 18은 부분 표시 모드에서, 비표시 영역에 관한 25~320행 째 중, 26행 째를 제외하는 행의 화소(50)에 대하여 전압 기입을 행하는 경우의 각 부 전압의 파형을 나타내는 도면이다.

<223> 도 14 내지 도 18에서, GATE(p)는 p행 째(p는  $1 \leq p \leq 320$ 을 만족하는 정수)의 주사선(Y(p))의 전압이며, SOURCE(q)는 q열 째(q는  $1 \leq q \leq 240$ 을 만족하는 정수)의 데이터선(X(q))의 전압이다. 또한, PIX(p, q)은 p행 째 주사선(Y(p))과, q열 째 데이터선(X(q))의 교차에 대응하여 마련된 p행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압이다. 또한, VCOM(p)은 p행 째의 공통선(Z(p))의 전압이다.

<224> 우선, 도 14를 이용하여, 부분 표시 모드에서, 표시 영역(81)에 관한 1~25행 째의 화소(50)에 대한 정극성 기입 시의 동작에 대하여 설명한다.

<225> 시각 t51로부터 t58까지의 기간에는, 도 11에 나타낸 시각 t11로부터 t18까지의 기간과 마찬가지로 동작하므로, 그 설명은 생략한다. 도 14에서 시각 t59는 시각 t51로부터 시각 t58까지의 기간과 동일한 1프레임 기간으로서, 표시 모드 선택 신호 CENB가 L레벨로 되는 타이밍이다.

<226> 시각 t59에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 제어 회로(30)는 소정의 전압으로서의 전압 VCOML을 공통선(Z(p))에 공급한다. 여기서, 공통선(Z(p))의 전압은 시각 t51로부터 t58까지의 기간에도, 전압 VCOML이므로, 계속해서 전압 VCOML로 유지되게 된다.

<227> 또, 시각 t59에서는, 주사선(Y(p))에 선택 전압이 공급되어 있지 않으므로, q열 째 데이터선(X(q))과 p행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태다. 또한, p행 q열의 화소(50)가 구비하는 화소 전극(55)과, 공통선(Z(p)) 사이에는 용량 결합이 발생하고 있다. 이 때문에, p행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(p, q)는 전압 VCOM(p)과 전압 PIX(p, q) 전위차를 유지하기 위해 전압 VP3을 유지한다.

<228> 다음에, 도 15를 이용하여, 부분 표시 모드에서, 표시 영역(81)에 관한 1~25행 째의 화소(50)에 대한 부극성 기

입 시의 동작에 대하여 설명한다.

- <229> 시각 t61로부터 t68까지의 기간에는, 도 12에 나타낸 시각 t21로부터 t28까지의 기간과 마찬가지로 동작하므로, 그 설명은 생략한다. 도 15에서 시각 t69는 시각 t61로부터 시각 t68까지의 기간과 동일한 1프레임 기간으로서, 표시 모드 선택 신호 CENB가 L레벨로 되는 타이밍이다.

- <230> 시각 t69에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 제어 회로(30)는 소정의 전압으로서의 전압 VCOML을 공통선(Z(p))에 공급한다. 이 때문에, 공통선(Z(p))의 전압 VCOM(p)은 저하하여, 시각 t70에서 전압 VCOML로 된다.

- <231> 시각 t69에서는, 주사선(Y(p))에 선택 전압이 공급되어 있지 않으므로, q열 째 데이터선(X(q))과 p행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태이다. 또한, p행 q열의 화소(50)가 구비하는 화소 전극(55)과, 공통선(Z(p)) 사이에는 용량 결합이 발생하고 있다. 이 때문에, p행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(p, q)는 전압 VCOM(p)과 전압 PIX(p, q)의 전위차를 유지하도록 저하하여, 시각 t70에서 전압 (VP4-VC)로 된다. 여기서, 전압 VC는 시각 t69로부터 t70까지의 기간에, 공통선(Z(p))의 전압 VCOM(p)의 전압이 저하한 만큼, 즉 전압 (VCOMH-VCOML)로 같다.

- <232> 계속해서, 액정 장치(1)의 부분 표시 모드에서, 비표시 영역(82)에 관한 26행 째~320행 째의 화소(50)에 대한 기입 동작에 대하여, 26행 째의 화소(50)와 27~320행 째의 화소(50)로 나눠 설명한다.

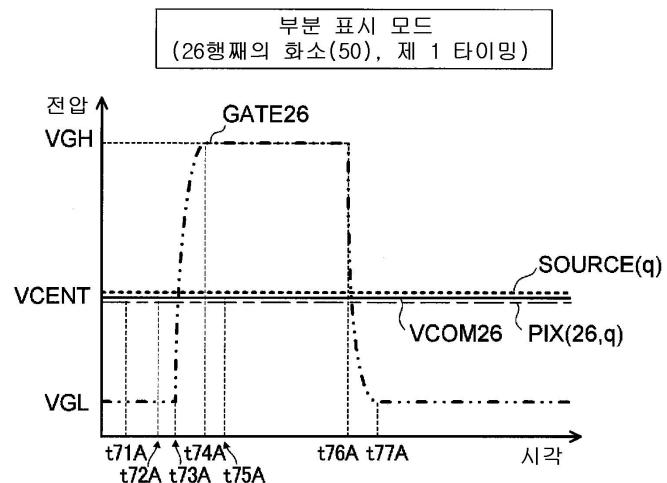

- <233> 우선, 26행 째의 화소(50)에 대한 기입 동작에 대하여 설명한다.

- <234> 도 16은, 부분 표시 모드에서, 26행 째의 화소(50)에 대한 기입 동작 시의 각 부 전압의 파형을 나타내는 도면이고, 특히, 주사선(Y1)에의 선택 전압의 공급에 동기하여 공통선(Z2)에 전압 VCOML을 공급한 경우와 동일한 1프레임 기간에서의 기입을 나타내고 있다(제 1 타이밍). 또, 도면에서 시각 t72는 표시 모드 선택 신호 CENB가 L레벨로 되는 타이밍이며, 도 13에서의 시각 t41에 상당한다.

- <235> 시각 t71에서, 26행 째에서 1행상의 주사선(Y25)에의 선택 전압의 공급에 동기하여, 제어 회로(30)는 공통선(Z26)에 전압 VCOML을 공급한다. 여기서, 공통선(Z26)의 전압은 시각 t71보다 이전 기간에도, 전압 VCOML이므로, 시각 t71에서는, 공통선(Z26)의 전압 VCOM26은 전압 VCOML로 유지된다.

- <236> 여기서, 시각 t71에서는, 주사선(Y26)에 선택 전압이 공급되기 전이므로, q열 째 데이터선(X(q))과 26행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태이다. 또한, 26행 q열의 화소(50)가 구비하는 화소 전극(55)과 공통선(Z26) 사이에는, 용량 결합이 발생하고 있다.

- <237> 이 때문에, 26행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(26, q)는 전압 VCOM(26)과 전압 PIX(26, q)의 전위차를 유지하기 위해, 전압 VCOML을 유지한다.

- <238> 시각 t72에서, 표시 모드 선택 신호 CENB를 L레벨로 하면, 제어 회로(30)는 소정의 전압으로서의 전압 VCOML을 공통선(Z26)에 공급한다. 여기서, 공통선(Z26)은 시각 t71로부터 t72의 기간에도, 전압 VCOML이므로, 시각 t72에서는, 변화되지 않고, 전압 VCOML을 유지하는 것으로 된다.

- <239> 시각 t72에서는, 주사선(Y26)에 선택 전압이 공급되기 전이므로, q열 째 데이터선(X(q))과 26행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태에 있다. 또한, 26행 q열의 화소(50)가 구비하는 화소 전극(55)과, 공통선(Z26) 사이에는, 용량 결합이 발생하고 있다. 이 때문에, 26행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(26, q)는 전압 VCOM(26)과 전압 PIX(26, q)의 전위차를 유지하기 위해, 전압 VCOML을 유지한다.

- <240> 시각 t73에서, 주사선 구동 회로(10)가 주사선(Y26)에 선택 전압을 공급하면, 주사선(Y26)의 전압 GATE26은 상승하고, 시각 t74에서는 전압 VGH로 된다. 이에 따라, 주사선(Y26)에 접속된 TFT(51)가 모두 온 상태로 된다.

- <241> 한편, 시각 t75에서, 보조 회로(40)가 소정의 전압으로서의 전압 VCOML을 데이터선(X(q))에 공급한다. 그렇게 하면, 데이터선(X(q))의 전압 SOURCE(q)는 전압 VCOML로 된다.

- <242> 데이터선(X(q))의 전압 SOURCE(q)는 주사선(Y26)에 접속된 온 상태의 TFT(51)를 통해, 26행 q열의 화소(50)가 구비하는 화소 전극(55)에 기입된다. 이 때문에, 26행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(26, q)는 데이터선(X(q))의 전압 SOURCE(q)와 동 전위인 전압 VCOML로 된다.

- <243> 여기서, 공통 전극 Z26의 전압 VCOM26은 전압 VCOML이므로, 화소 용량(54)에서의 화소 전극(55) 및 공통 전극

(56)의 차 전압은 0이다. 이 때문에, 26행 q열의 화소(50)는 노멀리 블랙 모드의 오프인 흑 표시로 된다.

<244> 시각 t76에서, 주사선 구동 회로(10)에 의해, 주사선(Y26)에 인가되는 전압이 선택 전압으로부터 비선택 전압으로 바뀐다. 그렇게 하면, 주사선(Y26)의 전압 GATE26은 저하하여, 시각 t77에서 전압 VGL로 된다. 이에 따라, 주사선(Y26)에 게이트가 접속된 TFT(51)가 모두 오프 상태로 된다.

<245> 또, TFT(51)가 오프 상태로 되어도, 화소 용량(54)은 자신 및 축적 용량(53)의 용량성에 의해 차 전압 0을 유지하는 것으로 된다.

<246> 도 17은, 부분 표시 모드에서, 26행 째의 화소(50)에 대한 기입 동작 시의 각 부 전압의 과정을 나타내는 도면이고, 특히, 주사선(Y1)에의 선택 전압의 공급에 동기하여 공통선(Z2)에 전압 VCOMH를 공급한 경우와 동일한 1프레임 기간에서의 기입을 나타내고 있다(제 2 타이밍). 또, 도면에서 시각 t83은 표시 모드 선택 신호 CENB가 L레벨로 되는 타이밍이며, 도 13에서의 시각 t35에 상당한다.

<247> 시각 t81에서, 주사선(Y25)에의 선택 전압의 공급에 동기하여, 제어 회로(30)가 공통선(Z26)에 전압 VCOMH를 공급하면, 공통선(Z26)의 전압 VCOM26은 서서히 상승하여, 시각 t82에서 전압 VCOMH로 된다.

<248> 여기서, 시각 t81에서는, 주사선(Y26)에 선택 전압이 공급되기 전이므로, q열 째 데이터선(X(q))과, 26행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태에 있다. 또한, 26행 q열의 화소(50)가 구비하는 화소 전극(55)과 공통선(Z26) 사이에는, 용량 결합이 발생하고 있다. 이 때문에, 26행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(26, q)는 전압 VCOM(26)과 전압 PIX(26, q)의 전위차 0을 유지하도록 상승하여, 시각 t82에서 전압 VCOMH로 된다.

<249> 시각 t83에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 제어 회로(30)는 소정 전압으로서의 전압 VCOML을 공통선(Z26)에 공급한다. 이 때문에, 공통선(Z26)의 전압 VCOML은 서서히 저하하여, 시각 t84에서 전압 VCOML로 된다.

<250> 여기서, 시각 t83에서는, 주사선(Y26)에 선택 전압이 공급되기 전이므로, q열 째 데이터선(X(q))과 26행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태에 있다. 또한, 26행 q열의 화소(50)가 구비하는 화소 전극(55)과 공통선(Z26) 사이에는, 용량 결합이 발생하고 있다. 이 때문에, 26행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(26, q)는 전압 VCOM(26)과 전압 PIX(26, q)의 전위차 0을 유지하도록 저하하고, 시각 t84에서 전압 VCOML로 된다.

<251> 또, 도 17에서의 시각 t85로부터 t89까지의 기간에는, 도 16에 나타낸 시각 t73으로부터 t77까지의 기간과 마찬가지로 동작한다.

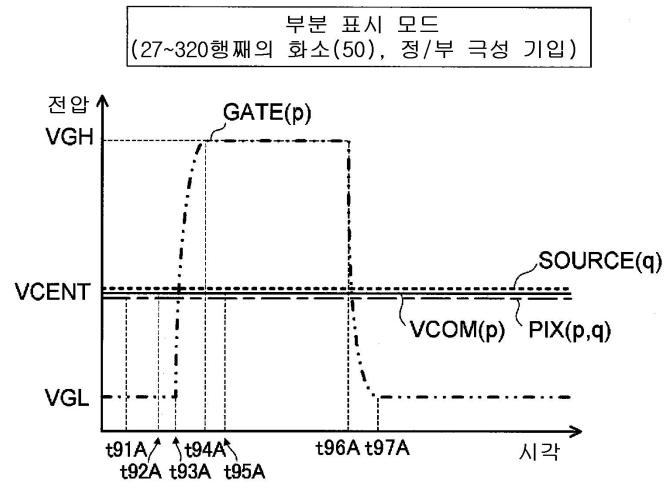

<252> 다음에, 27~320행 째의 화소(50)에 대한 기입 동작에 대하여 설명한다.

<253> 도 18은, 부분 표시 모드에서, 27~320행 째의 화소(50)에 대한 기입 동작을 나타내는 도면이다. 부분 표시 모드에서, 27~320행 째의 공통선(Z27~Z320)은 극성 신호 POL의 논리 레벨과 관계없이 전압 VCOML로 유지된다. 27~320행 째 주사선에 순서대로 선택 전압이 되었을 때, 보조 회로(40)는 공통선과 같은 전압 VCOML을 각각 1~240열의 데이터선에 공급하므로, 해당 비표시 영역에 관한 27~320행 째의 화소(50)에서, 화소 용량(54)의 차 전압은 0으로 유지되어, 노멀리 블랙 모드의 오프인 흑 표시로 된다.

<254> 즉, 도 18에서 시각 t91로부터 t97까지의 기간에는, 도 16에 나타낸 시각 t71로부터 t77까지의 기간과 마찬가지로 동작한다.

<255> 이와 같은 실시예 1에 따르면, 이하와 같은 효과가 있다.

<256> (1) 전 화면 표시 모드의 전체 행과, 부분 표시 모드에 있어서의 표시 영역(81)에 관한 행에서 보면, 전압 VCOML을 공통선(공통 전극(56))에 공급한 후에, 정극성 기입을 행하고, 전압 VCOMH를 공통 전극(56)에 공급한 후에, 부극성 기입을 행하므로, 상술한 종래예와 같이, 축적 용량(53)과 화소 용량(54) 사이에서 전하가 이동하지 않는다. 이 때문에, 축적 용량(53)끼리의 특성이 불균일하게 되어도, 동일 전압을 기입했을 때에, 화소 전극(55)의 전압에 편차가 발생하지 않는다. 이 때문에, 각 화소(50)의 밝기가 불균일하게 되는 것이 방지되어, 표시 품질의 저하를 억제할 수 있다.

<257> (2) 제어 회로(30)는 320행의 각각에 대응하여, 래치 회로(31)가 갖는 제 1 단위 래치 회로(311) 또는 제 2 단위 래치 회로(312)와, 표시 모드 회로(32)가 갖는 제 1 단위 표시 모드 회로(321) 또는 제 2 단위 표시 모드 회로(322)와, 전압 선택 회로(33)가 갖는 제 1 단위 전압 선택 회로(331) 또는 제 2 단위 전압 선택 회로(332)를

갖는다. 이 때문에, 각 행의 공통선(공통 전극(56))에 대하여, 전압 VCOML 또는 전압 VCOMH를 선택적으로 공급할 수 있다.

<258> 또한, 각 행의 공통선에 전압 VCOML 또는 전압 VCOMH 중 어느 하나를 인가할지에 대해서는, 기입 극성에 맞추어진다. 이 때문에, 상술한 종래예와 같이, 축적 용량(53)의 한쪽 전극에 접속된 용량선의 전압을, 화소 용량(54)에 있어서의 화소 전극(55)이나 공통 전극(56)과는 다른 전압으로 변동시킬 필요가 없다. 바꾸어 말하면, 본 실시예에 있어서는, 축적 용량(53)의 한쪽 전극에서의 전압이 공통 전극(56)의 전압과 마찬가지로 변동하므로, 축적 용량(53)의 다른쪽 전극과, 공통 전극(56)을 일체적으로 형성할 수 있다. 또한, 상술한 바와 같이, 축적 용량(53)의 다른쪽 전극은 화소 전극(55)에 접속되어 있으므로, 축적 용량(53)의 다른쪽 전극과 화소 전극(55)은 동 전위이며, 일체적으로 형성할 수 있다.

<259> 따라서, 액정을 사이에 유지하는 소자 기판(60) 및 대향 기판(70) 중, 소자 기판(60)에, 축적 용량(53)과 화소 용량(54)을 일체적으로 형성하는 IPS나 FFS와 같은 액정 장치에 바람직하게 된다.

<260> (3) 부분 표시 모드에서의 비표시 영역(82)의 각 행에서는, 공통선(공통 전극(56))이 소정의 전압으로서의 전압 VCOML로 유지된 후에, 주사선이 선택 전압으로 되었을 때에, 데이터선에 소정의 전압으로서의 전압 VCOML이 공급된다. 즉, 공통선을 전압 VCOML로 하여 위로부터, 화소 전극(55)에 전압 VCOML이 기입된다. 이 때문에, 공통 전극(56) 및 화소 전극(55)은 모두 전압 VCOML로 되므로, 액정에는, 구동 전압이 인가되지 않는다. 즉, 부분 표시 모드에서의 비표시 영역(82)에서는, 액정에 구동 전압이 인가되지 않으므로, 소비 전력을 절감할 수 있다.

<261> (41) 행마다 공통 전극(56)이 분할됨과 아울러, 전 화면 표시 모드에서는 전체 행의 공통 전극에, 부분 표시 모드에서는 표시 영역(81)에 관한 행의 공통 전극에, 각각 1행마다 전압 VCOML과 전압 VCOMH를 공급하고, 1행마다 정극성 기입 및 부극성 기입을 했다. 이 때문에, 1프레임 기간에서 정극성 기입이 이루어진 화소(50)와 부극성 기입이 이루어진 화소(50)가 혼재하고, 이를 화소(50)끼리 플리커를 상쇄시킬 수 있으므로, 표시 품질의 저하를 더욱 억제할 수 있다.

<262> (실시예 1의 개량 · 응용)

<263> 상술한 실시예 1에서는, 다음과 같은 개량 · 응용이 가능하다.

<264> (소정의 전압)

<265> 상술한 실시예 1에서는, 제어 회로(30)가 소정의 전압으로서 전압 VCOML을 공통선(Z1~Z320)에 공급하고, 보조 회로(40)가 소정의 전압으로서 전압 VCOML을 데이터선(X1~X240)에 공급했지만, 이것에 한정되지 않고, 예컨대, 제어 회로(30)가 소정의 전압으로서 전압 VCOMH를 공통선(Z1~Z320)에 공급하고, 보조 회로(40)가 소정의 전압 역시 전압 VCOMH를 데이터선에 공급하여도 좋다.

<266> (쌍 방향 · 한쪽 방향)

<267> 상술한 실시예 1에서는, 주사선에 선택 전압을 Y1, Y2, Y3, …, Y319, Y320이라는 순서로 인가했지만, 표시 패널(AA)을 회전시킨 경우에도 대처할 수 있도록, Y320, Y319, Y318, …, Y1과 같이 역의 순서로 전압을 인가하여도 좋다.

<268> 주사선에 선택 전압을 역의 순서로 인가하는 경우, 도 5에 나타낸 시프트 레지스터(11)에서, 어떤 행에 대응하는 단의 전송 회로는 출력 신호를 1행상의 행에 대응하는 단의 전송 회로에의 입력 신호로 함과 아울러, 개시 펄스 YD를 제320단의 전송 회로의 입력 신호로 하는 구성으로 된다.

<269> 또, 제어 회로(30)에 대해서는, 구성에 대하여 변경없이 그대로 이용할 수 있다. 이것은, 도 7에 나타낸 래치 회로(31)에서, 1,320행 째를 제외하는 행에 대응하는 제 2 단위 래치 회로(312)에서, 1행 위 또는 1행 아래의 어느 하나에 주사선이 H레벨로 되면, NOR 회로(U1)의 출력 신호가 L레벨로 되어 극성 신호 POL을 취입하고 래치 신호로서 출력하는 구성으로 되어있기 때문이다.

<270> 반대로 말하면, 제어 회로(30)에서, 주사선에 선택 전압을 인가하는 순서를 1→320행 째의 방향과 320→1행 째의 방향의 쌍 방향으로 대응시킬 필요가 없이, 예컨대, 1→320행 째의 방향에만 대응하면 충분하다고 하는 것이면, 도 19에 나타내는 바와 같이, 래치 회로(31)의 제 1 단위 래치 회로(311) 및 제 2 단위 래치 회로(312)에서, NOR 회로(U1)를 생략함과 아울러, 이 생략에 맞춰 부 논리 구성의 정합성을 취하기 위해, 제 1 클록 인버터(U4) 및 제 2 클록 인버터(U5)에서, 도 7과 비교하여 반전 입력단 및 비반전 입력단의 접속을 교체

한 구성으로 하면 좋다.

<271> 또한, 320행 째에 대해서는 제 2 단위 래치 회로(312)로 한다. 이러한 구성에 의하면, 1행상의 주사선이 H레벨로 되었을 때에, 극성 신호 POL을 취입하여 래치 신호로서 출력할 수 있으므로, NOR 회로(U1)를 생략하는 만큼, 회로 구성을 간략화할 수 있다.

<272> (전압 선택 회로)

<273> 도 9에 나타낸 전압 선택 회로(33) 중, 제 1 단위 전압 선택 회로(331)에서의 트랜스퍼 게이트(U22)의 입력 단자 및 제 2 단위 전압 선택 회로(332)에서의 트랜스퍼 게이트(U23)의 입력 단자에는, 각각 상대적으로 높은 전압 VCOMH가 공급되고, 제 1 단위 전압 선택 회로(331)에서의 트랜스퍼 게이트(U23)의 입력 단자 및 제 2 단위 전압 선택 회로(332)에서의 트랜스퍼 게이트(U22)의 입력 단자에는, 각각 상대적으로 낮은 전압 VCOML이 공급되어 있다.

<274> 본 실시예에 있어서, 트랜스퍼 게이트(U22, U23)는 반전 제어 입력 단자 및 비반전 제어 입력 단자의 논리 레벨로 온오프 제어되는 것으로부터 알 수 있는 바와 같이, p채널형 트랜지스터와 n채널형 트랜지스터를 병렬 접속한 구성을 상정하고 있지만, 입력 단자에 공급되는 전압은 고정이므로, 양 채널의 트랜지스터를 병렬 접속할 필요는 없고, 어느 채널형 트랜지스터로 구성하여도 좋은 것이다.

<275> 즉, 제 1 단위 전압 선택 회로(331)에서의 트랜스퍼 게이트(U22) 및 제 2 단위 전압 선택 회로(332)에서의 트랜스퍼 게이트(U23)를, 단순한 n채널형 트랜지스터로 하여, 그 소스 전극에 전압 VCOMH를 공급하고, 드레인 전극을 공통선에 접속함과 아울러, 게이트 전극에 인버터(U21)에 의한 전압 지시 신호의 반전 신호를 공급하는 한편, 제 1 단위 전압 선택 회로(331)에서의 트랜스퍼 게이트(U23) 및 제 2 단위 전압 선택 회로(332)에서의 트랜스퍼 게이트(U22)를, 단순한 p채널형 트랜지스터로 하여, 그 소스 전극에 전압 VCOML을 공급하고, 드레인 전극을 공통선에 접속함과 아울러, 게이트 전극에 전압 지시 신호를 공급하는 구성으로 하여도 좋다.

<276> 또, 트랜스퍼 게이트를 이용하다고 하여도, 한쪽 채널형 트랜지스터를 이용한다고 하여도, 전압 VCOMH, VCOML에 접속되는 트랜지스터의 채널 길이에 대해서는, 다른 트랜지스터의 채널 길이보다 짧게 하는 것이 바람직하다.

<277> (표시 영역 · 비표시 영역의 변경 · 고정화)

<278> 상술한 실시예에서는, 표시 영역(81)에 관한 화소(50)를 1~25행 째로 하고, 비표시 영역(82)에 관한 화소(50)를 26~320행 째로 했지만, 표시 영역(81) 및 비표시 영역(82)에 관한 행의 할당은 이것에 한정되지 않는다. 예컨대, 표시 영역(81)에 관한 화소(50)를 하반부의 161~320행 째로 하고, 비표시 영역(82)에 관한 화소(50)를 상반부의 1~160행 째로 하여도 좋다. 이와 같이 표시 영역(81)을 161~320행 째로 하고, 비표시 영역(82)을 1~160행 째로 하는 경우, 주사선(Y1~Y320)에의 선택 전압의 인가 동작에서, 1프레임 기간의 최초인 시간(도 13으로 말하면 t31, t37)보다 이후에 있고, 주사선(Y1)에 선택 전압에의 인가가 시작하는 시각(도 13으로 말하면 t32, t38)보다 앞선 시각에서, 동일한 1프레임 기간에서 주사선(Y160)에의 선택 전압에의 인가가 종료하는 시각까지, 표시 모드 선택 신호 CENB를 L레벨로 하면 좋다.

<279> 또한, 표시 영역(81) 및 비표시 영역(82)을 변경 가능하게 하는 것이 아니라 고정화하여도 좋다. 즉, 실시예 1과 같은 표시 영역(81)을 1~25행 째로 하고, 비표시 영역(82)을 26~320행 째로 고정화하여도 좋다.

<280> 이와 같이 고정화하는 경우, 도 20에 나타내는 바와 같이, 표시 모드 회로(32) 중, 표시 영역(81)에 고정화되는 1~25행 째에 대응하는 래치 신호 LAT1~LAT25와 표시 모드 선택 신호 CENB를 논리 연산하는 구성을 불필요해진다. 또, 표시 영역(81) 및 비표시 영역(82)을 고정화하는 경우더라도, 비표시 영역(82)으로 고정화되는 26~320행 째에 대해서는, 전 화면 표시 모드에서 표시 모드 선택 신호 CENB가 H레벨로 되므로, 도 20에 나타내는 바와 같이, 표시 모드 선택 신호 CENB와 논리 연산하는 구성을 배치시킬 필요가 있다.

<281> 바꾸어 말하면, 표시 영역(81)에 관한 행에서는, 래치 회로(31)에서의 제 1 단위 래치 회로(311) 또는 제 2 단위 래치 회로(312)와, 전압 선택 회로(33)에서의 제 1 단위 전압 선택 회로(331) 또는 제 2 단위 전압 선택 회로(332)로 제 1 단위 선택 회로를 구성할 수 있는데 대하여, 비표시 영역(82)에 걸리는 행에서는, 표시 모드 회로(32)에서의 제 1 단위 표시 모드 회로(321) 또는 제 2 단위 표시 모드 회로(322)를 더 부가하여 제 2 단위 선택 회로가 구성되게 된다.

<282> 또, 표시 영역(81) 및 비표시 영역(82)을 고정화하는 경우, 래치 회로(31)에 대해서는, 쌍 방향에 대응하는 도 7에 나타낸 구성 외에, 한쪽 방향에 대응한 도 19에 나타낸 구성도 적용 가능하다.

<283> (실시예 2)

다음에, 본 발명의 실시예 2에 따른 액정 장치에 대하여 설명한다.

<285> 이 실시예 2에 따른 액정 장치는 실시예 1에 있어서의 제어 회로(30)(도 6 참조)의 회로 구성을 변경한 것이고, 도 21은 변경한 제어 회로(30A)의 구성을 나타내는 블럭도이다.

<286> 또한, 실시예 2에 있어서 보조 회로(40)는 부분 표시 모드에서 비표시 영역(82)에 관한 주사선에 선택 전압이 인가되었을 때에, 소정의 전압으로서의 전압 VCENT를 데이터선(X1~X240)에 공급한다. 또, 그 밖의 구성에 대해서는, 실시예 1과 마찬가지이므로, 설명을 생략한다.

<287> 이 도면에 나타내는 바와 같이, 제어 회로(30A)는 실시예 1과 마찬가지의 래치 회로(31)를 갖지만, 회로 구성이 다른 표시 모드 회로(32A) 및 전압 선택 회로(33A)를 구비한다.

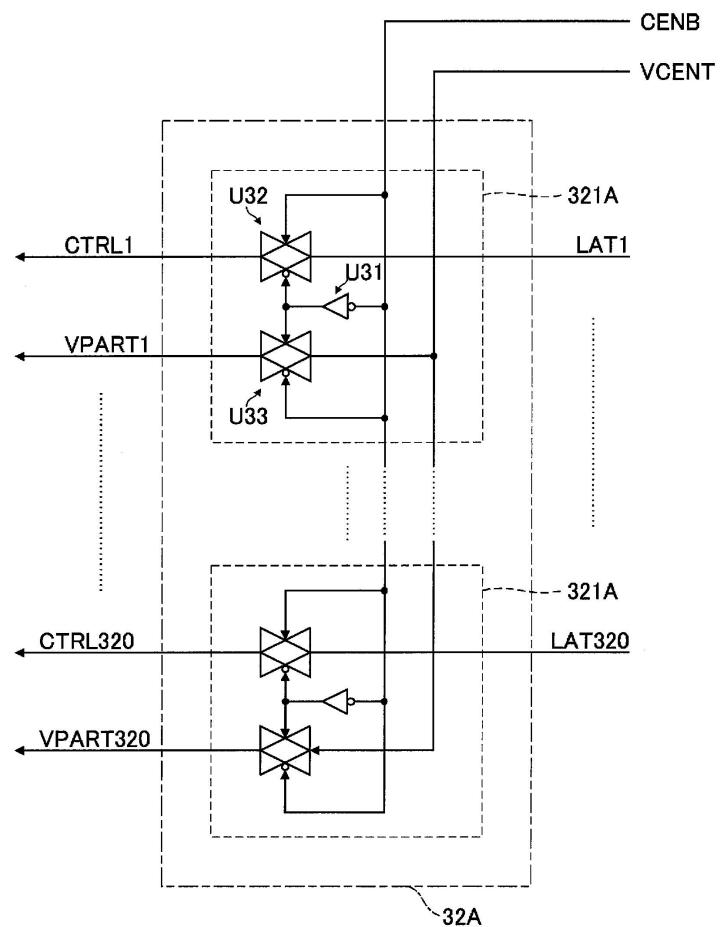

<288> 우선, 표시 모드 회로(32A)에 대하여 설명한다. 도 22는 표시 모드 회로(32A)의 구성을 나타내는 블럭도이다.

<289> 이 도면에 나타내는 바와 같이, 표시 모드 회로(32A)는 주사선(Y1~Y320)의 각각에 대응하여 마련된 단위 표시 모드 회로(321A)를 갖고, 이 단위 표시 모드 회로(321A)는 인버터(U31), 제 1 트랜스퍼 게이트(U32) 및 제 2 트랜스퍼 게이트(U33)를 갖는다.

<290> 인버터(U31)의 입력 단자에는, 표시 모드 선택 신호 CENB가 입력되고, 인버터(U31)의 출력 단자는 제 1 트랜스퍼 게이트(U32)의 반전 입력 제어 단자와, 제 2 트랜스퍼 게이트(U33)의 비반전 입력 제어 단자에 각각 접속되어 있다.

<291> 제 1 트랜스퍼 게이트(U32)의 입력 단자에는, 동일행의 래치 회로(31)로부터 출력된 래치 신호 LAT가 입력된다. 또한, 제 1 트랜스퍼 게이트(U32)의 반전 입력 제어 단자에는, 인버터(U31)의 출력 단자가 접속되고, 제 1 트랜스퍼 게이트(U32)의 비반전 입력 제어 단자에는, 표시 모드 선택 신호 CENB가 입력된다.

<292> 제 2 트랜스퍼 게이트(U33)의 입력 단자에는, 소정의 전압으로서의 전압 VCENT이 입력된다. 여기서, 전압 VCENT은 전압 VCOML과 전압 VCOMH의 중간 전압이다. 또한, 제 2 트랜스퍼 게이트(U33)의 반전 입력 제어 단자에는 표시 모드 선택 신호 CENB가 입력되고, 제 2 트랜스퍼 게이트(U33)의 비반전 입력 제어 단자에는 인버터(U31)의 출력 단자가 접속되어 있다.

<293> 이러한 구성의 단위 표시 모드 회로(321A)에서, H레벨의 표시 모드 선택 신호 CENB가 입력되면, 이 H레벨의 표시 모드 선택 신호 CENB는 제 1 트랜스퍼 게이트(U32)의 비반전 입력 제어 단자에 입력됨과 아울러, 인버터(U31)에 의해 극성이 반전되어 L레벨의 신호로 되고, 제 1 트랜스퍼 게이트(U32)의 반전 입력 제어 단자에 입력된다. 이 때문에, 제 1 트랜스퍼 게이트(U32)가 온 상태로 되며, 이 온 상태에 있는 제 1 트랜스퍼 게이트(U32)의 입력 단자에 입력된 래치 신호 LAT가 전압 지시 신호 CTRL로서 출력된다.

<294> 한편, L레벨의 표시 모드 선택 신호 CENB가 입력되면, 이 L레벨의 표시 모드 선택 신호 CENB는 제 2 트랜스퍼 게이트(U33)의 반전 입력 제어 단자에 입력됨과 아울러, 인버터(U31)에 의해 극성이 반전되어 H레벨의 신호로 되어, 제 2 트랜스퍼 게이트(U33)의 비반전 입력 제어 단자에 입력된다. 이 때문에, 제 2 트랜스퍼 게이트(U33)가 온 상태로 되고, 이 온 상태에 있는 제 2 트랜스퍼 게이트(U33)의 입력 단자에 입력된 소정의 전압으로서의 전압 VCENT가 신호 VPART로서 출력된다.

<295> 또, 단위 표시 모드 회로(321A)는, 상술한 바와 같이, 표시 모드 선택 신호 CENB가 H레벨이면, 래치 신호 LAT를 전압 지시 신호 CTRL로서 출력하고, 표시 모드 선택 신호 CENB가 L레벨이면, 소정의 전압으로서의 전압 VCENT을 신호 VPART로 하여 출력한다. 즉, 단위 표시 모드 회로(321A)는 전압 지시 신호 CTRL과 소정의 전압으로서의 전압 VCENT인 신호 VPART를 배타적으로 출력한다.

<296> 다음에, 도 21에서의 전압 선택 회로(33A)에 대하여 설명한다. 도 23은 전압 선택 회로(33A)의 구성을 나타내는 블럭도이다.

<297> 이 도면에 나타내는 바와 같이, 전압 선택 회로(33A)는, 실시예 1(도 9 참조)과 마찬가지로, 기수행의 각각에 대응하여 마련된 제 1 단위 전압 선택 회로(331)와 우수행의 각각에 대응하여 마련된 제 2 단위 전압 선택 회로(332)를 구비한다. 단, 기수행의 공통선에는, 같은 행의 제 1 단위 전압 선택 회로(331)의 출력단에 더하여, 같은 행의 신호 VPART가 공급되는 신호선에 접속되고, 우수행의 공통선에는, 같은 행의 제 2 단위 전압 선택 회로(332)의 출력단에 더하여, 같은 행의 신호 VPART가 공급되는 신호선에 접속되어 있다.

<298> 이 전압 선택 회로(33A)는 다음과 같이 동작한다.

<299> 즉, 기수  $r$  ( $r$ 은  $1 \leq r \leq 319$ 를 만족하는 기수) 행에 대하여 보았을 때, 전압 선택 회로(33A)는, 표시 모드 회로(32A)에서 H레벨의 전압 지시 신호 CTRL( $r$ )를 입력하면, 기수  $r$  행 째의 공통선( $Z(r)$ )에 전압 VCOML을 공급하고, L레벨의 전압 지시 신호 CTRL( $r$ )를 입력하면, 공통선( $Z(r)$ )에 전압 VCOMH를 공급한다. 또, 전압 선택 회로(33A)는, 표시 모드 회로(32A)에서 소정의 전압으로서의 전압 VCENT인 신호 VPART( $r$ )를 입력하면, 공통선( $Z(r)$ )에 전압 VCENT을 공급한다.

<300> 한편, 우수  $s$  ( $s$ 는  $2 \leq s \leq 320$ 을 만족하는 우수) 행에 대하여 보았을 때, 전압 선택 회로(33A)는, 표시 모드 회로(32A)에서 H레벨의 전압 지시 신호 CTRL( $s$ )를 입력했을 때, 우수  $s$  행 째의 공통선( $Z(s)$ )에 전압 VCOMH를 공급하고, L레벨의 전압 지시 신호 CTRL( $s$ )를 입력했을 때, 공통선( $Z(s)$ )에 전압 VCOML을 공급한다. 또, 전압 선택 회로(33A)는, 표시 모드 회로(32A)에서 소정의 전압으로서의 전압 VCENT인 신호 VPART( $s$ )를 입력하면, 공통선( $Z(s)$ )에 전압 VCENT를 공급한다.

<301> 이러한 제어 회로(30A)는, 전 화면 표시 모드에서는, 실시예 1에 따른 제어 회로(30)(도 10 참조)와 마찬가지로 동작한다. 이 때문에, 제어 회로(30A)에 대해서는, 부분 표시 모드에서의 동작을 중심으로 설명한다. 도 24는 부분 표시 모드에서의 제어 회로(30A)의 동작을 나타내는 도면이고, 주사선의 선택에 대하여 공통선의 전압이 어떻게 변화되는가를 나타내는 도면이다.

<302> 또, 실시예 2에 있어서도, 표시 영역(81)에 관한 화소(50)를 1~25 행 째로 하고, 비표시 영역(82)에 관한 화소(50)를 26~320 행 째로 하고 있으므로, 표시 모드 선택 신호 CENB는, 도 24에 나타내는 바와 같이, 시각 t35A에서 시각 t37A까지의 기간, 및 시각 t41A에서 시각 t43A까지의 기간에 걸쳐 L레벨로 된다.

<303> 실시예 1에 따른 제어 회로(30)는, 부분 표시 모드인 경우, 도 13에 나타내는 바와 같이, 시각 t35로부터 시각 t37까지의 기간 및 시각 t41로부터 시각 t43까지의 기간(즉, 표시 모드 선택 신호 CENB가 L레벨로 되는 기간)에 걸쳐, 소정의 전압으로서 전압 VCOML을 공통선에 공급한다.

<304> 한편, 본 실시예에 따른 제어 회로(30A)는, 도 24에 나타내는 바와 같이, 표시 모드 선택 신호 CENB가 L레벨로 되는 기간에 걸쳐, 소정의 전압으로서 전압 VCENT을 공통선에 공급한다.

<305> 이러한 제어 회로(30A)를 구비한 액정 장치의 부분 표시 모드에서의 동작에 대하여 설명한다.

<306> 실시예 2에서 부분 표시 모드로 되는 경우, 표시 영역(81)에 관한 1 행 째~25 행 째의 화소(50)에 대하여 전압 기입을 행할 때에, 도 25는 정극성 기입 시의 각 부 전압의 파형을 나타내는 도면이며, 도 26은 부극성 기입 시의 각 부 전압의 파형을 나타내는 도면이다.

<307> 도 27 및 도 28은, 각각 부분 표시 모드에서, 비표시 영역(82)으로 가장 위에 위치하는 26 행 째의 화소(50)에 대하여 전압 기입을 행하는 경우의 각 부 전압의 파형을 나타내는 도면이다. 또한, 도 28은, 부분 표시 모드에서, 비표시 영역에 관한 25~320 행 째 중, 26 행 째를 제외하는 행의 화소(50)에 대하여 전압 기입을 행하는 경우의 각 부 전압의 파형을 나타내는 도면이다.

<308> 우선, 도 25를 이용하여, 부분 표시 모드에서 표시 영역에 관한 1 행 째~25 행 째의 화소(50)에 대한 정극성 기입 시의 동작에 대하여 설명한다.

<309> 시각 t51A에서 t59A까지의 기간에는, 도 14에 나타낸 시각 t51로부터 t59까지의 기간과 마찬가지로 동작한다.

<310> 시각 t59A에서, 표시 모드 선택 신호 CENB가 L레벨로 되는데 동기하여, 제어 회로(30A)에 의해, 소정의 전압으로서의 전압 VCENT을 공통선( $Z(p)$ )에 공급하면, 공통선( $Z(p)$ )의 전압 VCOM( $p$ )은 점차 상승하여, 시각 t60A에서 전압 VCENT로 된다.

<311> 시각 t59A에서는, 주사선( $Y(p)$ )에 선택 전압이 공급되어 있지 않으므로,  $q$  열 째 데이터선( $X(q)$ )과,  $p$  행  $q$  열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태이다. 또한,  $p$  행  $q$  열의 화소(50)가 구비하는 화소 전극(55)과, 공통선( $Z(p)$ )에 접속된 공통 전극(56) 사이에는 용량 결합이 발생하고 있다. 이 때문에,  $p$  행  $q$  열의 화소(50)가 구비하는 화소 전극(55)의 전압  $PIX(p, q)$ 는 전압 VCOM( $p$ )과 전압  $PIX(p, q)$ 의 전위차를 유지하도록 상승하여, 시각 t60A에서, 전압 (VP3+VCA)로 된다. 여기서, 전압 VCA는, 시각 t59A에서 t60A까지의 기간에, 공통선( $Z(p)$ )에 접속된 공통 전극(56)의 전압 VCOM( $p$ )의 전압이 상승한 만큼, 즉 전압 (VCENT-VCOML)과 같다.

<312> 다음에, 도 26을 이용하여, 부분 표시 모드에서 1 행 째~25 행 째의 화소(50)에 대한 부극성 기입 시의 동작에 대

하여 설명한다.

<313> 시각 t61A에서 t69A까지의 기간에는, 도 15에 나타낸 시각 t61로부터 t69까지의 기간과 마찬가지로 동작한다.

<314> 시각 t69A에서, 표시 모드 선택 신호 CENB가 L레벨로 되는데 동기하여, 제어 회로(30A)에 의해, 소정의 전압으로서의 전압 VCENT을 공통선(Z(p))에 공급하면, 공통선(Z(p))에 접속된 공통 전극(56)의 전압 VCOM(p)은 점차로 저하하여, 시각 t70A에서 전압 VCENT로 된다.

<315> 시각 t69A에서는, 주사선(Y(p))에 선택 전압이 공급되어 있지 않으므로, q열 째 데이터선(X(q))과, p행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태이다. 또한, p행 q열의 화소(50)가 구비하는 화소 전극(55)과, 공통선(Z(p))에 접속된 공통 전극(56) 사이에는 용량 결합이 발생하고 있다. 이 때문에, p행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(p, q)는 전압 VCOM(p)과 전압 PIX(p, q)의 전위차를 유지하도록 저하하여, 시각 t70A에서는 전압 (VP4-VCB)로 된다. 여기서, 전압 VCB는 시각 t69A에서 t70A까지의 기간에, 공통선(Z(p))에 접속된 공통 전극(56)의 전압 VCOM(p)의 전압이 저하한 만큼, 즉 전압 (VCOMH-VCENT)과 같다.

<316> 계속해서, 실시예 2의 부분 표시 모드에서, 비표시 영역(82)에 관한 26행 째~320행 째의 화소(50)에 대한 기입 동작에 대하여, 26행 째의 화소(50)와 27~320행 째의 화소(50)로 나눠 설명한다.

<317> 우선, 26행 째의 화소(50)에 대한 기입 동작에 대하여 설명한다.

<318> 도 27은, 부분 표시 모드에서, 26행 째의 화소(50)에 대한 기입 동작 시의 각 부 전압의 과정을 나타내는 도면이고, 특히, 주사선(Y1)에의 선택 전압의 공급에 동기하여 공통선(Z2)에 전압 VCOML을 공급한 경우와 동일한 1프레임 기간에서의 기입을 나타내고 있다(제 1 타이밍). 또, 도면에서 시각 t72A는 표시 모드 선택 신호 CENB가 L레벨로 되는 타이밍이며, 도 22에 있어서의 시각 t41A에 상당한다.

<319> 시각 t71A에서, 26행 째에서 1행상의 주사선(Y25)에의 선택 전압의 공급에 동기하여, 제어 회로(30A)는 공통선(Z26)에 전압 VCENT을 공급한다. 여기서, 공통선(Z26)의 전압은 시각 t71A보다 전의 기간에도, 전압 VCENT이므로, 시각 t71A에서는, 공통선(Z)56의 전압 VCOM26은 전압 VCENT로 유지된다.

<320> 여기서, 시각 t71A에서는, 주사선(Y26)에 선택 전압이 공급되기 전이므로, q열 째 데이터선(X(q))과, 26행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태이다. 또한, 26행 q열의 화소(50)가 구비하는 화소 전극(55)과 공통선(Z26) 사이에는 용량 결합이 발생하고 있다.

<321> 이 때문에, 26행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(26, q)는 전압 VCOM(26)과 전압 PIX(26, q)의 전위차를 유지하기 위해, 전압 VCENT를 유지한다.

<322> 시각 t72A에서, 표시 모드 선택 신호 CENB가 L레벨로 되면, 제어 회로(30)는 소정의 전압으로서의 전압 VCENT을 공통선(Z26)에 공급한다. 여기서, 공통선(Z26)의 전압은 시각 t71A로부터 t72A의 기간에도, 전압 VCENT이므로, 시각 t72A에서는 변화되지 않고, 전압 VCENT를 유지하는 것으로 된다.

<323> 시각 t72A에서는, 주사선(Y26)에 선택 전압이 공급되어 있지 않으므로, q열 째 데이터선(X(q))과, 26행 q열의 화소(50)가 구비하는 화소 전극(55)은 서로 비접속 상태에 있다. 또한, 26행 q열의 화소(50)가 구비하는 화소 전극(55)과, 공통선(Z26) 사이에는, 용량 결합이 발생하고 있다. 이 때문에, 26행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(26, q)는 전압 VCOM(26)과 전압 PIX(26, q)의 전위차를 유지하기 위해, 전압 VCENT을 유지한다.

<324> 시각 t73A에서, 주사선 구동 회로(10)가 주사선(Y26)에 선택 전압을 공급하면, 주사선(Y26)의 전압 GATE26은 상승하여, 시각 t74A에서는 전압 VGH로 된다. 이에 따라, 주사선(Y26)에 접속된 TFT(51)가 모두 온 상태로 된다.

<325> 한편, 시각 t75A에서, 보조 회로(40)가 소정의 전압으로서의 전압 VCENT을 데이터선(X(q))에 공급하면, 데이터선(X(q))의 전압 SOURCE(q)는 전압 VCENT로 된다.

<326> 데이터선(X(q))의 전압 SOURCE(q)은 주사선(Y26)에 접속된 온 상태의 TFT(51)를 거쳐, 26행 q열의 화소(50)가 구비하는 화소 전극(55)에 기입된다. 이 때문에, 26행 q열의 화소(50)가 구비하는 화소 전극(55)의 전압 PIX(26, q)는 데이터선(X(q))의 전압 SOURCE(q)과 동 전위인 전압 VCENT로 된다.

<327> 여기서, 공통 전극 Z26의 전압 VCOM26은 전압 VCENT이므로, 화소 용량(54)에서의 화소 전극(55) 및 공통 전극(56)의 차 전압은 0이다. 이 때문에, 26행 q열의 화소(50)는 노멀리 블랙 모드의 오프인 흑 표시로 된다. 또, 시각 t76A에서 t77A까지의 기간의 동작은, 도 16에 나타낸 시각 t76으로부터 t77까지의 기간에 대하여, 전압

VCOML을 전압 VCENT로 하여 재판독한 동작과 마찬가지이다.

<328> 도 28은, 실시예 2의 부분 표시 모드에서, 26행 째의 화소(50)에 대한 기입 동작 시에서의 각 부 전압의 파형을 나타내는 도면이고, 특히, 주사선(Y1)에의 선택 전압의 공급에 동기하여 공통선(Z2)에 전압 VCOMH를 공급한 경우와 동일한 1프레임 기간에서의 기입을 나타내고 있다(제 2 타이밍). 단, 시각 t81A에서 t89A까지의 기간의 동작은, 도 17에 나타낸 시각 t81로부터 t89까지의 기간에 대하여, 전압 VCOML을 전압 VCENT로 하여 재판독한 동작과 마찬가지이다.

<329> 다음에, 27~320행 째의 화소(50)에 대한 기입 동작에 대하여 설명한다.

<330> 도 29는, 실시예 2의 부분 표시 모드에서, 27~320행 째의 화소(50)에 대한 기입 동작을 나타내는 도면이다. 부분 표시 모드에서, 27~320행 째의 공통선(Z27~Z320)은, 도 24에 나타내는 바와 같이, 전압 VCENT로 유지된다. 27~320행 째의 주사선에 순서대로 선택 전압이 되었을 때, 보조 회로(40)는 공통선과 같은 전압 VCENT를 각각 1~240열의 데이터선에 공급하므로, 해당 비표시 영역에 관한 27~320행 째의 화소(50)에서, 화소 용량(54)의 차 전압은 0으로 유지되어, 노멀리 블랙 모드의 오프인 후 표시로 된다.

<331> 즉, 도 29에서 시각 t91로부터 t97까지의 기간에는, 도 27에 나타낸 시각 t71로부터 t77까지의 기간과 마찬가지로 동작한다.

<332> 이러한 실시예 2에 따르면, 상술한 실시예 1과 마찬가지의 효과를 얻을 수 있다.

<333> 또한, 상술한 실시예 2에서는, 소정의 전압으로서의 전압 VCENT은 전압 VCOML과 전압 VCOMH의 중간 전압으로 했지만, 이것에 한정되지 않고, 예컨대, 전압 VCOML 또는 전압 VCOMH의 한쪽과 동 전위이더라도 좋다.

<334> (실시예 3)

<335> 다음에, 본 발명의 실시예 3에 따른 액정 장치에 대하여 설명한다.

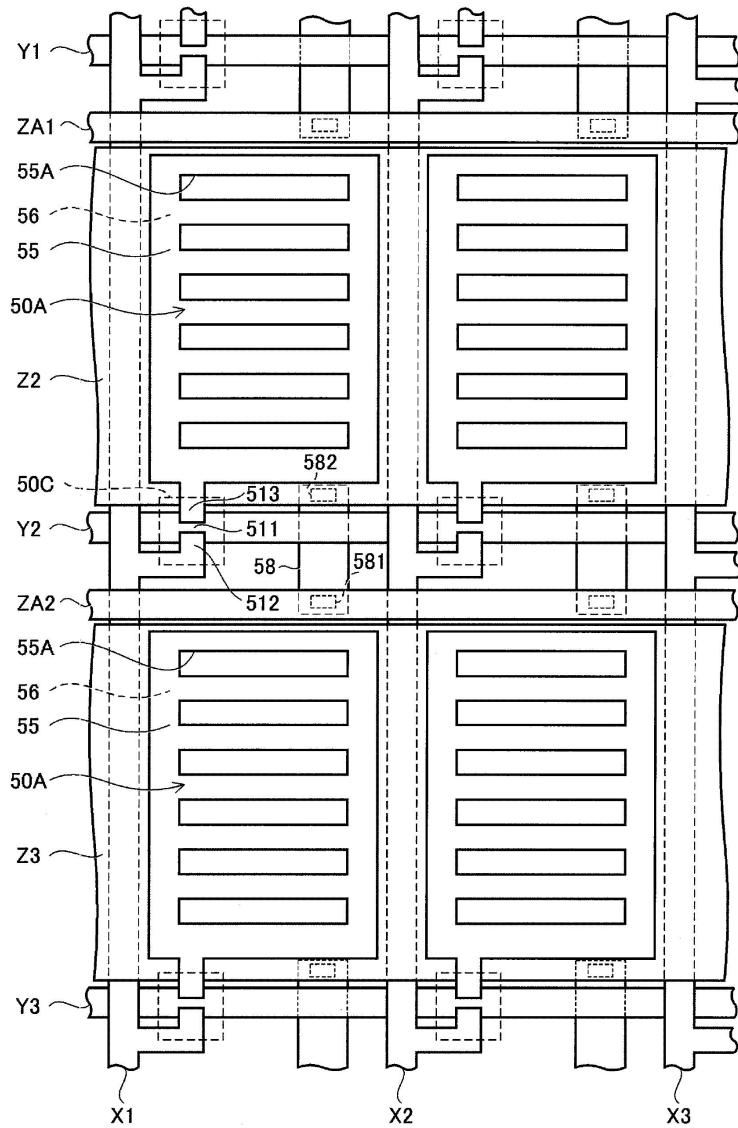

<336> 이 실시예 3에 따른 액정 장치는, 실시예 1에 있어서의 화소(50)(도 3 참조)를 변경한 것이다. 도 30은 실시예 3에 따른 화소(50A)의 구성을 나타내는 확대 평면도이다. 또, 실시예 3에 따른 화소(50A)는 보조 공통선(ZA) 및 콘택트 배선(58)을 구비하는 점에서, 실시예 1의 화소(50)와는 다르다. 그 밖의 구성에 대해서는, 실시예 1과 마찬가지이므로, 설명을 생략한다.

<337> 보조 공통선(ZA)은 도전성의 금속막으로 이루어지고, 1행마다 분할하고, 즉, 공통 전극(56)(공통선)에 대응하도록, 주사선(Y)을 따라 형성되어 있다. 상세하게는, 어떤 행의 보조 공통선(ZA)은 해당 행의 주사선과 해당 행보다 1행 아래의 행의 공통 전극(56)(공통선) 사이에서 주사선을 따른 방향으로 형성되어 있다.

<338> 콘택트 배선(58)은 화소(50A)마다 마련된 도전성의 금속막이며, 영역(581)에서 보조 공통선(ZA)과 접속되고, 영역(582)에서 공통 전극(56)(공통선)에 접속되어 있다.

<339> 상술한 바와 같이, 공통 전극(56)은 ITO 등의 투명 전극으로 구성되므로, 저항율이 비교적 높고, 시정수가 커지는 경향에 있지만, 본 실시예 3에 의하면, 각 행의 공통 전극(56)은 각각 보조 공통선(ZA)과 별별 접속되어, 합성 저항이 저하하므로, 각 행의 공통 전극(56)의 시정수를 저하시키는 것이 가능해진다.

<340> (변형예)

<341> 또, 본 발명은 상술한 각 실시예에 한정되는 것이 아니라, 본 발명의 목적을 달성할 수 있는 범위에서의 변형, 개량 등은 본 발명에 포함되는 것이다.

<342> 예컨대, 제어 회로(30)는 어디까지나 일레이며, 공통선(Z1~Z320)의 전압을, 전 화면 표시 모드에서는 도 10에 표시되는 것과 같은 파형으로 하고, 부분 표시 모드에서는 도 13에 표시되는 것과 같은 파형으로 하는 것이면, 도 6~도 8에 나타낸 구성에 한정되지 않는다. 마찬가지로, 제어 회로(30A)는 어디까지나 일레이며, 공통선(Z1~Z320)의 전압을, 전 화면 표시 모드에서는 도 10에 표시되는 것과 같은 파형으로 하고, 부분 표시 모드에서는 도 24에 표시되는 것과 같은 파형으로 하는 것이면, 도 21~도 23에 나타낸 구성에 한정되지 않는다.

<343> 상술한 각 실시예에서는, 320행의 주사선(Y)과, 240열의 데이터선(X)을 구비하는 것으로 했지만, 이것에 한하지 않고, 예컨대, 480행의 주사선(Y)과, 640열의 데이터선(X)을 구비하여도 좋다.

<344> 또한, 상술한 각 실시예에서는, 투파형의 표시를 행하는 것으로 했지만, 이것에 한정되지 않고, 예컨대, 백라이트(90)로부터의 광을 이용하는 투파형 표시와, 외광의 반사광을 이용하는 반사형 표시를 겸비한 반투과 반사형

의 표시를 하여도 좋다.

<345> 상술한 각 실시예에서는, 액정은 노멀리 블랙 모드로 동작하는 것으로 했지만, 이것에 한정되지 않고, 예컨대, 노멀리 화이트 모드로 동작하는 것이라도 좋다.

<346> 상술한 각 실시예에서는, TFT로서 아몰퍼스 실리콘으로 이루어지는 TFT(51)를 마련했지만, 이것에 한정되지 않고, 예컨대, 저온 폴리 실리콘으로 이루어지는 TFT를 마련하여도 좋다.

<347> 상술한 각 실시예에서는, 공통 전극(56) 위에 제 2 절연막(64)을 형성하고, 이 제 2 절연막(64) 위에 화소 전극(55)을 형성했지만, 이것에 한정되지 않고, 예컨대, 화소 전극(55) 위에 제 2 절연막(64)을 형성하고, 이 제 2 절연막(64) 위에 공통 전극(56)을 형성하여도 좋다. 즉, 화소마다 직사각형 형상의 화소 전극(55)과 띠형의 공통 전극(56)은 어느 한쪽이 상층 쪽으로 되고, 다른 쪽이 하층 쪽으로 되어도 좋다. 단, 슬릿 형상의 개구부(55A)는 상층 쪽, 즉 액정에 가까운 쪽에 마련된다.

<348> 또, 상술한 각 실시예에서는, 액정이 FFS 모드로 동작하는 것으로 했지만, 예컨대, IPS 모드로 동작하는 것이라도 좋다.