(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-41657

(P2013-41657A)

(43) 公開日 平成25年2月28日(2013.2.28)

(51) Int.Cl.

G 11 C 11/417 (2006.01)

F 1

G 11 C 11/34 305

テーマコード(参考)

5 B 0 1 5

審査請求 未請求 請求項の数 20 O L 外国語出願 (全 12 頁)

(21) 出願番号 特願2012-132108 (P2012-132108)

(22) 出願日 平成24年6月11日 (2012.6.11)

(31) 優先権主張番号 61/499,959

(32) 優先日 平成23年6月22日 (2011.6.22)

(33) 優先権主張国 米国(US)

(71) 出願人 509336211

マーベル・イスラエル・(エム・アイ・エス・エル)・リミテッド

Marvell Israel (M. I. S. L.) Ltd.

イスラエル国 20692 ヨクニアム

ハマダ・ストリート6 モルドット・ハカーメル・インダストリアル・パーク

6 Hamada Street, Mordot HaCarmel Industrial Park, Yokneam,

Israel 20692

(74) 代理人 110000877

龍華国際特許業務法人

最終頁に続く

(54) 【発明の名称】共通の列マルチプレクサ及びセンスアンプハードウェアを有するランダムアクセスメモリコントローラ

(57) 【要約】 (修正有)

【課題】ランダムアクセスメモリコントローラのためのシステム及び方法を提供する。

【解決手段】ランダムアクセスメモリコントローラであって、列マルチプレクサ及びセンスアンプ対を備え、列マルチプレクサ及びセンスアンプ対は、共通回路を利用するよう構成された列マルチプレクサ及びセンスアンプを含む。共通回路は、メモリコントローラが列マルチプレクサ及びセンスアンプ対について1つのインスタンスの共通回路を含むように、列マルチプレクサとセンスアンプとの間で共有される。共通回路は、共通プリチャージ回路、共通イコライザ、または、共通キーパ回路を含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

ランダムアクセスメモリコントローラであって、

列マルチプレクサ及びセンスアンプ対を備え、

前記列マルチプレクサ及びセンスアンプ対は、共通回路を利用するよう構成された列マルチプレクサ及びセンスアンプを含み、前記共通回路は、前記メモリコントローラが前記列マルチプレクサ及びセンスアンプ対について1つのインスタンスの前記共通回路を含むように、前記列マルチプレクサと前記センスアンプとの間で共有され、前記共通回路は、共通プリチャージ回路、共通イコライザ、または、共通キーパ回路を含む、ランダムアクセスメモリコントローラ。

10

**【請求項 2】**

前記列マルチプレクサ及びセンスアンプ対は、スタティックランダムアクセスメモリアレイに接続するよう構成されている請求項1に記載のランダムアクセスメモリコントローラ。

**【請求項 3】**

前記メモリアレイの一列と前記列マルチプレクサ及びセンスアンプ対との間には、バスデバイストランジスタが1つだけ直列接続されている請求項2に記載のランダムアクセスメモリコントローラ。

**【請求項 4】**

前記共通回路はさらに、タイミング回路を含み、前記タイミング回路は、前記列マルチプレクサ及びセンスアンプ対の競合条件がなくなるように構成されている請求項1に記載のランダムアクセスメモリコントローラ。

20

**【請求項 5】**

前記列マルチプレクサ及びセンスアンプ対は、列選択処理を実行するよう構成されており、前記列選択処理は前記共通回路を利用し、前記列マルチプレクサ及びセンスアンプ対はさらに、センス増幅処理を実行するよう構成されており、前記センス増幅処理にも同じ共通回路を利用する請求項1に記載のランダムアクセスメモリコントローラ。

**【請求項 6】**

前記センス増幅処理は、メモリアレイの選択された列から受けたデータのビットラインの電圧差を増幅して、前記選択された列は、前記列選択処理で選択される請求項5に記載のランダムアクセスメモリコントローラ。

30

**【請求項 7】**

前記共通回路は、前記センス増幅処理中にストローブ信号の受信と協調させて前記ビットラインの電圧差を増幅するよう構成されている請求項6に記載のランダムアクセスメモリコントローラ。

**【請求項 8】**

前記列マルチプレクサ及びセンスアンプ対にデータ値及びメモリ位置を送信して、前記データ値を前記スタティックランダムアクセスメモリの前記メモリ位置へ書き込む処理を促す書き込み回路をさらに備える請求項2に記載のランダムアクセスメモリコントローラ。

40

**【請求項 9】**

前記列マルチプレクサは、前記メモリの複数の列のいずれか1つに対してデータを送受信するよう構成されている請求項2に記載のランダムアクセスメモリコントローラ。

**【請求項 10】**

前記列マルチプレクサは、差動データ信号を利用してデータを送受信するよう構成されている請求項9に記載のランダムアクセスメモリコントローラ。

**【請求項 11】**

前記共通回路は、後続するアクセスのために第1のデータ信号レベルを受け取り保持するよう構成されている共通キーパ回路を含む請求項1に記載のランダムアクセスメモリコントローラ。

50

**【請求項 1 2】**

前記列マルチプレクサ及びセンスアンプ対は、前記メモリアレイと同じ集積回路上に形成される請求項 2 に記載のランダムアクセスメモリコントローラ。

**【請求項 1 3】**

前記メモリアレイは、前記列マルチプレクサ及びセンスアンプ対が形成されている集積回路の外部にある請求項 2 に記載のランダムアクセスメモリコントローラ。

**【請求項 1 4】**

プロセッサキャッシュの一部である請求項 1 に記載のランダムアクセスメモリコントローラ。

**【請求項 1 5】**

レベル 1 (L1)、レベル 2 (L2)、レベル 3 (L3) のキャッシュの一部である請求項 1 4 に記載のランダムアクセスメモリコントローラ。

**【請求項 1 6】**

ルックアップテーブル、バッファ管理、またはロジックブロックを実装するときに動作するよう構成されている請求項 1 に記載のランダムアクセスメモリコントローラ。

**【請求項 1 7】**

スタティックランダムアクセスメモリからデータを読み取る方法であって、

スタティックランダムアクセスメモリの一列から列マルチプレクサでデータ信号を受信して、前記列マルチプレクサが、前記スタティックランダムアクセスメモリの複数のビットラインのデータにアクセスして、アクセスした前記データを差動信号形式のデータ信号として出力する段階と、

共通プリチャージ回路と共通イコライザ回路とを利用して前記データ信号にセンス増幅信号処理を行う段階と

を備え、

前記センス増幅信号処理では、前記データ信号が差動形式で受信され、差動形式の前記データ信号の電圧差を増幅し、前記増幅されたデータ信号は出力アレイに提供されて格納される、方法。

**【請求項 1 8】**

前記データ信号を、前記アクセスしたデータの前記差動形式のデータ信号としての出力と、前記センス増幅信号処理の実行との間に、単一のバスデバイスを介して送信する段階をさらに備える請求項 1 7 に記載の方法。

**【請求項 1 9】**

前記メモリの列にデータ値を書き込めとのコマンドを受信する段階と、

同じ共通プリチャージ回路と前記共通イコライザ回路とを利用して、前記データ値を書き込みデータ信号に変換する段階と、

前記書き込みデータ信号を前記メモリの列にダイレクトする段階と

をさらに備える請求項 1 7 に記載の方法。

**【請求項 2 0】**

前記データ信号を受信したときに、前記メモリの列に同時に読み書きアクセスが行われないようにタイマを設定する段階と、

前記メモリの列にデータ値を書き込めとのコマンドを受信する段階と、

前記タイマをチェックして、前記データ信号が前記メモリの列から読み出されたかを判断する段階と、

時間が予め規定した条件になって初めて、前記メモリの列に前記データ値に書き込む処理を進める段階と

をさらに備える請求項 1 9 に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

ここに記載する技術は、概してメモリコントローラに係り、より詳しくは、共通回路を

10

20

30

40

50

有する共通モジュールを備えたメモリコントローラに係る。

【背景技術】

【0002】

本願は、「書き込み可能センスアンプ」というタイトルで2011年6月22日に提出された米国仮特許出願第61/499,959号明細書の優先権を主張しており、この全体をここに参照として組み込む。

【0003】

ランダムアクセスメモリは、格納しているデータ、データ群への任意の順序のアクセスを許可するタイプのコンピュータデータストレージである。ランダムアクセスメモリは、メモリへの電力が失われると格納されているデータも失われてしまう揮発性メモリである場合が多い。例えば、動的ランダムアクセスメモリは、データを信頼性高く格納するためには定期的にリフレッシュする必要がある。これに対して、スタティックランダムアクセスメモリは、電力が供給され続けている限りは、リフレッシュしなくてもデータを保持することができる。

10

【0004】

上述した記載は、当技術分野の関連技術の一般的な概略として提示されており、ここに含まれる情報のいずれであっても本特許出願に対する先行技術を構成するとの自認の表れであるとみなされるべきではない。

20

【発明の概要】

【0005】

ランダムアクセスメモリコントローラに関するシステム及び方法を例示する。本開示の一実施形態では、ランダムアクセスメモリコントローラが、列マルチプレクサ及びセンスアンプ対を含み、この列マルチプレクサ及びセンスアンプ対は、共通回路を利用するよう構成されている列マルチプレクサ及びセンスアンプを含む。共通回路は、列マルチプレクサ及びセンスアンプとの間で共有され、メモリコントローラが、列マルチプレクサ及びセンスアンプ対について共通回路の単一のインスタンスを含むようにされている。共通回路は、共通プリチャージ回路、共通イコライザ、または、共通キーパ回路(keeper circuit)を含む。

【0006】

本開示の別の実施形態では、スタティックランダムアクセスメモリからデータを読み取る方法であって、スタティックランダムアクセスメモリの一列から列マルチプレクサでデータ信号を受信する段階を含む。列マルチプレクサが、スタティックランダムアクセスメモリの複数のビットラインのデータにアクセスして、アクセスしたデータを差動信号形式のデータ信号として出力する。共通プリチャージ回路と共通イコライザ回路とを利用してデータ信号にセンス増幅信号処理を行う。センス増幅信号処理では、データ信号が差動形式で受信され、差動形式のデータ信号の電圧差を増幅し、増幅されたデータ信号は出力アレイに提供されて格納される。

30

【図面の簡単な説明】

【0007】

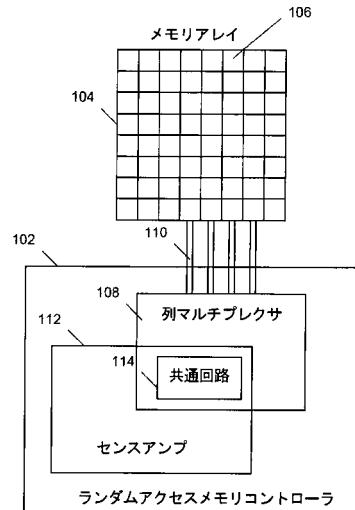

【図1】本開示の一実施形態におけるランダムアクセスメモリコントローラを説明する簡略化されたブロック図である。

40

【0008】

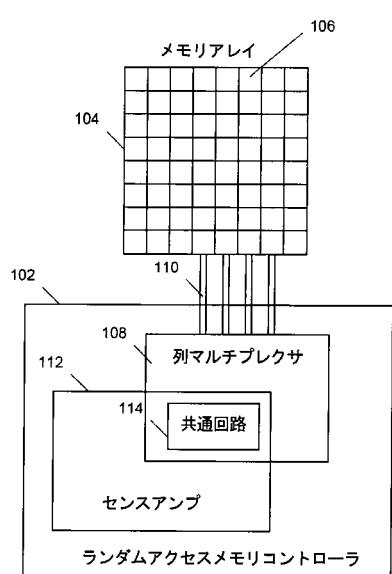

【図2】図1のランダムアクセスメモリコントローラの実施形態のさらなる詳細を示すブロック図である。

【0009】

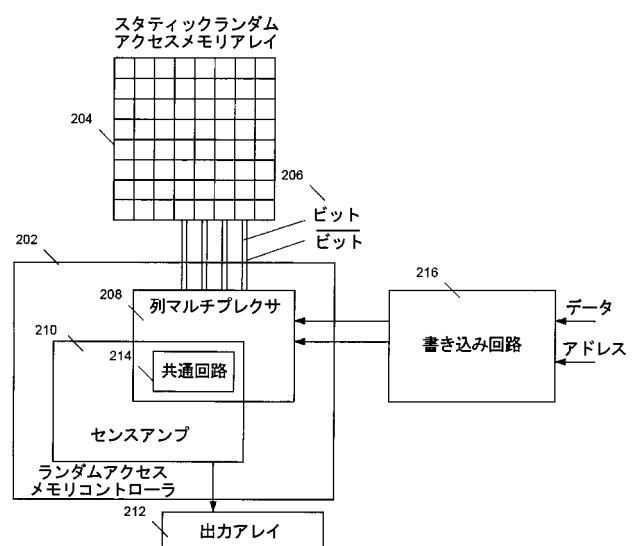

【図3】一実施形態では、共通回路の詳細を含む図2に示すセンスアンプ列マルチプレクサ対の拡大図を示すブロック図である。

【0010】

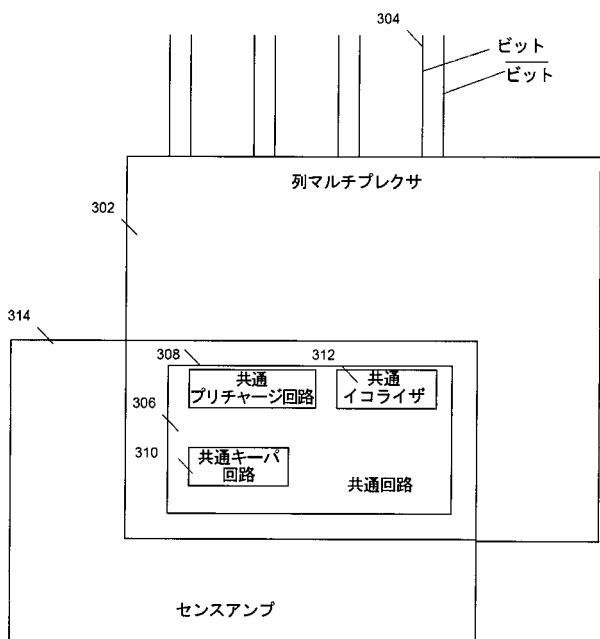

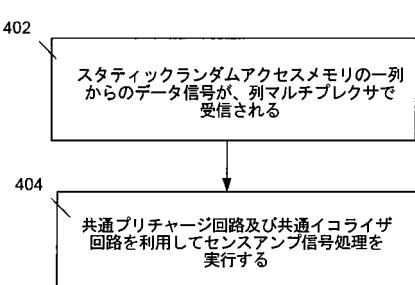

【図4】スタティックランダムアクセスメモリからデータを読み出す方法を示すフロー図である。

50

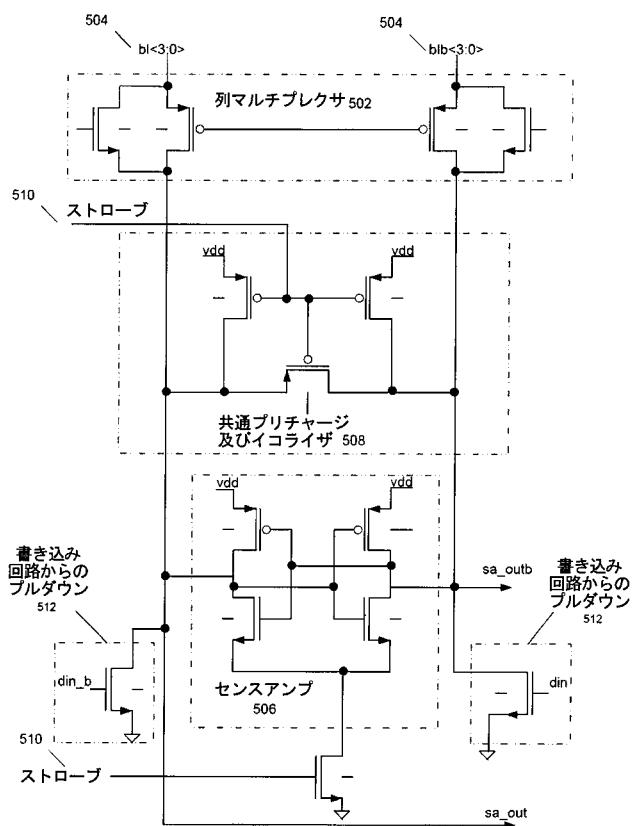

## 【0011】

【図5】列マルチプレクサセンスアンプ対の実装例を示す回路図である。

## 【発明を実施するための形態】

## 【0012】

図1は、本開示の一実施形態におけるランダムアクセスメモリコントローラ102を説明する簡略化されたブロック図である。ランダムアクセスメモリコントローラ102は、メモリアレイ104とインタフェースして、メモリアレイ104からのデータの読み出し、または、メモリアレイ104へのデータの書き込みを促す。メモリアレイ104は様々な形態をとることができる。例えば、メモリアレイ104は、スタティックランダムアクセスメモリ、不揮発性メモリ、データプロセッサ及びその他の形態のメモリと関連付けられているオンチップまたはオフチップのキャッシュメモリ（レベル1（L1）、レベル2（L2）、レベル3（L3））キャッシュ等のランダムアクセスメモリのコンポーネントであってよい。通常のメモリアレイ104のセルは、行列に分けられ、各セルには、ビット等のデータの一部が関連付けられる。メモリアレイ104は、列ごとにアクセス可能であり、メモリアレイ104の1列のデータ値の全てまたは一部が、データ要求に応じて直列または並列で出力される。例えば六列目106からの1以上のデータ値のメモリアレイ104に対する読み書きが要求された場合、ランダムアクセスメモリコントローラ102は、1以上のデータライン110を介して、六列目106からのデータ値全てを出力する、または書き込む。一実施形態では、ランダムアクセスメモリコントローラ102は、メモリアレイ104から受信するデータ値をフィルタリングして組み合わせ、読み出したデータ要求に見合うデータを、要求を出した側のアプリケーションに提供する。10

## 【0013】

ランダムアクセスメモリコントローラ102は、メモリアレイの読み書きに適した回路を含む。一実施形態では、ランダムアクセスメモリコントローラ102は、列マルチプレクサ108を含む。読み出し処理においては、メモリアレイ104の1以上のアドレスのデータにアクセスせよとのコマンドが、ランダムアクセスメモリコントローラ102から受信される。列マルチプレクサ108は、メモリアレイの1以上のデータライン110を介してメモリアレイ104の列からデータ値を受信する。一例では、列マルチプレクサ108は、要求されている列の8ビットのデータに、その列のデータに関連付けられている出力データライン110を介してアクセスする。一例では、出力データライン110は差動データラインであり、データライン110は、様々なビット値を表すために、所定のパターンでそれぞれ補間しあう高い電圧及び低い電圧を提供する。20

## 【0014】

一実施形態では、列マルチプレクサ108は、データ値を受信して、データ値に一定の前処理を施してアクセスの信頼度を高める。一例では、列マルチプレクサ108は、データ読み出しプロセスにおいて下流回路がアクセスするデータ値に対するアクセス、処理、及び一時的格納を行う、プリチャージ回路、イコライザ回路、及びキーパ回路を含む。30

## 【0015】

一実施形態では、読み出し処理で列マルチプレクサがデータ値に前処理を行った後で、データ値がセンスアンプ112に提供され、さらなる処理にそなえる。一実施形態では、センスアンプ112は、差動形式のデータ値を表すデータ信号を列マルチプレクサ108から受け取り、これらデータ信号を増幅して、各差動データ信号の2つのコンポーネント間のビットライン電圧差を増幅する。一実施形態では、センスアンプ112は列マルチプレクサ108が利用する回路コンポーネントに類似した、増幅を実行するための様々な回路コンポーネントを利用する。例えばセンスアンプ112は、センスアンプ112処理を実行するために、プリチャージ回路、イコライザ回路、及びキーパ回路を利用するが、これらコンポーネントは列マルチプレクサ108でも利用される。40

## 【0016】

列マルチプレクサ108は、さらに、データ書き込み処理の一部として機能することもできる。ランダムアクセスメモリコントローラ102からの、書き込むデータ値とメモリ50

アレイ 104 のアドレスとを識別するデータ書き込みコマンドを受け取ると、列マルチプレクサ 108 は、データ値を利用して一定の書き込み前処理を実行して、これらデータ値を、メモリアレイ 104 への書き込みに適した形式で表すデータ信号にする。一例では、列マルチプレクサ 108 は、上述したものと同じプリチャージ回路、イコライザ回路、及びキーパ回路を利用して、データ値を前処理する読み出し処理を実行して、結果生じるデータ信号をメモリアレイ 104 の適切な列にダイレクトして、格納させる。

#### 【0017】

従来の構成では、ランダムアクセスメモリコントローラの列マルチプレクサ及びセンスアンプは、銘々について設計された機能を実行するべくそれぞれ別のハードウェアを利用する別個の実態である。例えば従来の列マルチプレクサは、専用のプリチャージ、イコライザ、及びキーパ回路を含むのが普通である。さらに、従来のセンスアンプも、専用のプリチャージ、イコライザ、及びキーパ回路を含むものが普通である。このような構成によれば、従来の列マルチプレクサ及び従来のセンスアンプそれぞれが専用ハードウェアを利用して、他の部材の処理状況に関わらず、それぞれ自立して機能を発揮するようなロバストな機能が提供される。

10

#### 【0018】

しかし、一定の回路を列マルチプレクサ 108 とセンスアンプ 112との間で共有するようなランダムアクセスメモリコントローラ 102 を実装することで、例えばコンポーネント数の低減、電流リークの低減、電力要件の緩和、及びよりパフォーマンスを上げること、等の一定のシナジー効果を達成することができる。一実施形態では、ランダムアクセスメモリコントローラ 102 は、一対の列マルチプレクサ 108 及びセンスアンプ 112 を含み、この対に、共通回路 114 を利用するよう構成されている列マルチプレクサ 108 及びセンスアンプ 112 が含まれている。共通回路 114 を列マルチプレクサ 108 とセンスアンプ 112 との間で共有させることで、ランダムアクセスメモリコントローラ 102 は、各列マルチプレクサ 108 及びセンスアンプ 112 において共通回路 114 のインスタンスを 1 つ含めればよいことになる。一実施形態では、共通回路 114 は、共通プリチャージ回路、共通イコライザ回路、及び共通キーパ回路のうち 1 以上を含んでよい。

20

#### 【0019】

一実施形態では、共通回路 114 は、メモリアレイ 104 に関する上述した処理のうち複数を実行するために利用することができる。一例では、共通回路 114 の一部を、読み取り処理列多重化処理、読み取り処理センス増幅処理、及び、書き込み処理列多重化処理のそれぞれの実行のために利用することができる。

30

#### 【0020】

読み取り処理列多重化、読み取り処理センス増幅、及び、書き込み処理列多重化のそれぞれの実行のために、別個の専用回路の代わりに共通回路 114 を利用すると、複数の利点が生じる。例えば、このような共通回路 114 の利用によって、ランダムアクセスメモリコントローラ 102 のパーティの数を減らすことができる。一実施形態では、共通回路 114 を利用すると、ランダムアクセスメモリコントローラ 102 の実装に必要となるトランジスタ数が減る。必要なパーティの数が減ると、ランダムアクセスメモリコントローラ 102 の寄生リークが低減し、集積回路等のランダムアクセスメモリコントローラ 102 の実装に必要な物理的領域も減らすことができ、ひいては読み取り及び／または書き込み処理を実行するために必要な時間も短くすることができるが、これは、ランダムアクセスメモリコントローラ 102 の各パーティが、ランダムアクセスメモリコントローラ 102 のパフォーマンス全体を遅延させかねない過渡電流を有している可能性があるからである。ランダムアクセスメモリコントローラ 102 の低減可能なパーティの一例として、列マルチプレクサ 108 とセンスアンプ 112 との間の読み出し回路経路のパスデバイス数を、单一パスデバイスに低減させることができる（従来は少なくとも 2 つのパスが必要であった）。

40

#### 【0021】

図 2 は、図 1 のランダムアクセスメモリコントローラの実施形態のさらなる詳細を示す

50

ブロック図である。図2の例では、ランダムアクセスマリコントローラ202は、スタティックランダムアクセスマモリアレイ204とインタフェースして、スタティックランダムアクセスマモリアレイ204からデータを読み出し、スタティックランダムアクセスマモリアレイ204にデータを書き込むことを含む処理を実行する。ランダムアクセスマリコントローラ202及びスタティックランダムアクセスマモリアレイ204は、206で示すように差動データ信号ラインを介して通信する。このようなデータ信号ライン206は、一例では、信号ラインの1つが高データ信号を表し、他の信号ラインが低データ信号を表すようにして1ビットの値を表させるように、対とされる。変化するビット値を表すには、信号ラインの1つが低データ信号を表し、他の信号ラインが高データ信号を表すようにしてよい。

10

#### 【0022】

ランダムアクセスマリコントローラ202は、列マルチプレクサ208及びセンスアンプ210対を含み、これらが、スタティックランダムアクセスマモリアレイ204の複数の列から1以上のデータ値を読み出し、読み出したデータ値を出力アレイ212に送信して格納及び利用させることに関する処理を実行するよう構成されている。列マルチプレクサ208及びセンスアンプ210対は、データ読み取り処理に関する、列マルチプレクサ208処理及びセンスアンプ210処理の両方の少なくとも一部を実行するよう構成されている共通回路を含む。

#### 【0023】

図2の例にはさらに、1以上のデータ値のスタティックランダムアクセスマモリアレイ204への書き込みを命令する書き込み回路216が含まれている。書き込み回路216は、ランダムアクセスマリコントローラ202とは別個であってもよいし、ランダムアクセスマリコントローラ202と統合されていてもよい。書き込み回路216は、スタティックランダムアクセスマモリアレイ204に書き込むデータ値を、スタティックランダムアクセスマモリアレイ204に書き込むデータの対象アドレスとともに受信するよう構成されている。書き込み回路216は、データを処理して、ビットラインの値を列マルチプレクサ208に設定して、列マルチプレクサ208は、これらのビットラインの値を、アドレスが指定する、スタティックランダムアクセスマモリアレイの適切な列に送信する。列マルチプレクサ208はさらに、上述したように、共通回路214を利用して、書き込み回路216のビットライン上のデータ信号を処理して（例えば、データ信号を均等化する）、スタティックランダムアクセスマモリアレイ204へのデータ書き込みの信頼性に影響を及ぼす。

20

#### 【0024】

図3は、一実施形態では、共通回路の詳細を含む図2に示すセンスアンプ列マルチプレクサ対の拡大図を示すブロック図である。ランダムアクセスマリコントローラは、データの読み書き処理中にメモリアレイとインタフェースする列マルチプレクサ302を含む。列マルチプレクサ302は、304に示すような差動データライン等のデータライン経由で、ランダムアクセスマリコントローラの次に、または付近に、ランダムアクセスマリコントローラの外部に、または遠隔に生成されるメモリとインタフェースする。他のタイプの符号化も、メモリとのインタフェースのときに同様に利用することができ、他のデータライン構成及び信号スキームを同様に実装することができる。

30

#### 【0025】

一実施形態では、列マルチプレクサ302は、データ読み出し処理のために一定の共通回路306を利用する。例えばメモリの列のデータにアクセスするときには、列マルチプレクサは、共通プリチャージ回路308を利用して、メモリの識別された列のデータ値を迅速に検知して、データを共通キーパ回路310に一時的保存目的に提供することができる。一実施形態では、列マルチプレクサ302はさらに、共通イコライザ312を利用して、次の処理のための準備として、プリチャージ中にビットラインのレベルを均等化させておくことができる。

40

#### 【0026】

50

この例では、センスアンプ314は、列マルチプレクサ302から読み出したデータをサンプリングして、読み取りデータ値を表すデータ信号を外部メモリアレイ等に出力する前に、適宜データ信号を増幅する。一実施形態では、センスアンプ314は、ビットライン電圧差を、差動符号化信号に増幅して、送信のロバスト性を高める。センスアンプ314は、増幅処理を実行するときに一定の共通回路306を利用する。一例では、センスアンプ314は、列マルチプレクサ302により共通キーパ回路310に格納されているデータ値にアクセスして、これらデータ値を表すデータ信号を増幅する。一例では、センスアンプ314は、図5を参照して後で詳述するように、増幅の準備のできたデータ信号を示すストローブ信号を受信すると、データ信号を増幅する。増幅は、共通プリチャージ回路308を利用して、データを受信してから増幅するまでの搭載待ち時間なしに行うことで、迅速化することができる。共通イコライザ312は、データ信号を出力する前に信号レベルを均等化する目的で利用される。

10

## 【0027】

一実施形態では、共通回路306の一部は、データ書き込み処理を実行するときに列マルチプレクサにより利用される。書き込みのアドレス及びデータが列マルチプレクサ302により受信される。書き込みデータは、共通キーパ回路310に格納される。共通キーパ回路310に格納されるデータを現すデータ信号は、共通プリチャージ回路308を利用して関連メモリに書き込むための適切な電圧に増幅され、信号の均等化処理は、データをメモリに書き込む前に共通イコライザ312を利用して実行される。

20

## 【0028】

図4は、スタティックランダムアクセスメモリからデータを読み出す方法を示すフロー図である。スタティックランダムアクセスメモリの一列からのデータ信号が、列マルチプレクサで受信される(402)。列マルチプレクサは、スタティックランダムアクセスメモリの複数のビットラインのデータにアクセスして、アクセスしたデータを、差動形式のデータ信号として出力する。404で、共通プリチャージ回路及び共通イコライザ回路を利用してデータ信号にセンスアンプ信号処理を実行する。センスアンプ信号処理では、差動形式のデータ信号を受け取り、データ信号の電圧差を差動形式に増幅する。増幅されたデータ信号は、格納するべく出力アレイに提供される。

## 【0029】

図5は、列マルチプレクサセンスアンプ対の実装例を示す回路図である。列マルチプレクサ502は、センスアンプ506のビットラインを介してメモリに接続される4ビットの差動データライン504間で双方向の多重化を提供する。共通プリチャージ及びイコライザ回路508は、列マルチプレクサ502とセンスアンプ506との間で共有されて、データの読み書き処理中に一定の処理を実行する。例えばデータ読み取り中には、共通プリチャージ及びイコライザ回路508は、センスアンプ506の出力ビットラインを予め搭載する。この読み取り処理中に、センスアンプ506は、センスアンプ出力(sa\_out及びsa\_out\_b)の間の電圧差を増幅して、1つをVDDにプルして、他方をVSSにプルすることで、列マルチプレクサ502がアクセスしたデータ値を表すようになる。このような増幅は、データ値がアクセスされ増幅準備が整った旨を通信するストローブ信号510を受信すると、行うことができる。プルダウン部512は、書き込み回路からコマンドを受信して、din及びdin\_b入力に提供されたデータに基づく書き込み処理中に列マルチプレクサ502の上位側から、センスアンプビットライン及び関連するビットラインをプルダウンする。

30

## 【0030】

特許請求項の範囲には、ここに特に記載しなかった例も含まれる場合がある。例えばランダムアクセスメモリコントローラは、複数の異なる構成で実装することができ、数多くの他の実装例の一部として動作してもよい。例えば1以上のランダムアクセスメモリコントローラは、メモリ集積回路(チップ)上でメモリアレイとともに形成されてもよい。別の例としては、ランダムアクセスメモリコントローラが、異なる集積回路上といったメモリアレイから離れた位置にあってもよい。ランダムアクセスメモリコントローラは、さら

40

50

に、データプロセッサ集積回路に組み込まれても良い。例えば、ランダムアクセスメモリコントローラ及び関連するメモリアレイは、オンチップキャッシュ（レベル1（L1）、レベル2（L2）、またはレベル3（L3））キャッシュの一部として実装されることで、オンチップメモリアクセスをデータプロセッサに提供してよい。ランダムアクセスメモリコントローラは、ルックアップテーブル、データバッファ、論理ブロックその他多くの任意の数の処理の実行に参加するよう構成されていてよい。

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 メニー ヤニ

アメリカ合衆国、95054 カリフォルニア州、サンタ クララ、マーベル レーン 5488

マーベル セミコンダクター インコーポレイテッド内

F ターム(参考) 5B015 HH01 HH03 JJ32 KB03 KB06 KB12

【外國語明細書】

2013041657000001.pdf