(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7587380号**

**(P7587380)**

(45)発行日 令和6年11月20日(2024.11.20)

(24)登録日 令和6年11月12日(2024.11.12)

(51)国際特許分類

F I

|                         |               |

|-------------------------|---------------|

| H 04 N 25/40 (2023.01)  | H 04 N 25/40  |

| H 04 N 25/76 (2023.01)  | H 04 N 25/76  |

| H 04 N 25/779 (2023.01) | H 04 N 25/779 |

請求項の数 17 (全20頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2020-157865(P2020-157865) |

| (22)出願日  | 令和2年9月18日(2020.9.18)        |

| (65)公開番号 | 特開2022-51408(P2022-51408A)  |

| (43)公開日  | 令和4年3月31日(2022.3.31)        |

| 審査請求日    | 令和5年9月11日(2023.9.11)        |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74)代理人  | 100094112<br>弁理士 岡部 譲                      |

| (74)代理人  | 100101498<br>弁理士 越智 隆夫                     |

| (74)代理人  | 100106183<br>弁理士 吉澤 弘司                     |

| (74)代理人  | 100136799<br>弁理士 本田 亜希                     |

| (72)発明者  | 識名 紀之<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| (72)発明者  | 鳴谷 美子                                      |

最終頁に続く

(54)【発明の名称】 光電変換装置、光電変換システム及び移動体

**(57)【特許請求の範囲】****【請求項1】**

複数の行をなすように配された複数の画素と、

前記複数の画素から行ごとに順次信号を出力させるための第1走査及び第2走査を行う走査部と、

外部からの入力に応じて、前記第1走査における複数行の画素の読み出し動作の設定を示す第1設定値を記憶する第1記憶部と、

外部からの入力に応じて、前記第2走査における複数行の画素の読み出し動作の設定を示す第2設定値を記憶する第2記憶部と、

を有し、

前記走査部は、前記第1設定値に基づく前記第1走査と、前記第2設定値に基づく前記第2走査とを1フレーム期間に行い、

前記第1記憶部による前記第1設定値の記憶と、前記第2記憶部による前記第2設定値の記憶がともに、前記第1走査の開始及び前記第2走査の開始に先立って行われることを特徴とする光電変換装置。

**【請求項2】**

第3記憶部及び第4記憶部を更に有し、

前記第3記憶部は、外部から入力される前記第1設定値を記憶して、前記第1記憶部に出力し、

前記第4記憶部は、外部から入力される前記第2設定値を記憶して、前記第2記憶部に

10

20

出力する

ことを特徴とする請求項 1 に記載の光電変換装置。

**【請求項 3】**

前記第 3 記憶部に前記第 1 設定値が入力される時刻は、前記 1 フレーム期間が開始する時刻よりも前である

ことを特徴とする請求項 2 に記載の光電変換装置。

**【請求項 4】**

前記第 4 記憶部に前記第 2 設定値が入力される時刻は、前記 1 フレーム期間が開始する時刻よりも前である

ことを特徴とする請求項 2 又は 3 に記載の光電変換装置。

10

**【請求項 5】**

前記第 3 記憶部から前記第 1 記憶部に前記第 1 設定値が出力される時刻は、前記 1 フレーム期間が開始される時刻である

ことを特徴とする請求項 2 乃至 4 のいずれか 1 項に記載の光電変換装置。

**【請求項 6】**

前記第 4 記憶部から前記第 2 記憶部に前記第 2 設定値が出力される時刻は、前記 1 フレーム期間が開始される時刻である

ことを特徴とする請求項 2 乃至 5 のいずれか 1 項に記載の光電変換装置。

**【請求項 7】**

前記第 1 記憶部に記憶されている前記第 1 設定値と、前記第 2 記憶部に記憶されている前記第 2 設定値との一方を選択的に有効化する選択部を更に有する

20

ことを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の光電変換装置。

**【請求項 8】**

前記選択部が前記第 2 設定値を有効化する時刻は、前記 1 フレーム期間が開始される時刻よりも後である

ことを特徴とする請求項 7 に記載の光電変換装置。

**【請求項 9】**

前記走査部は、前記第 2 走査を 1 フレーム期間に N 回 (N は 2 以上の整数) 行う

ことを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載の光電変換装置。

**【請求項 10】**

30

N 回の前記第 2 走査の設定を示す N 個の第 2 設定値をそれぞれ記憶する N 個の前記第 2 記憶部を有する

ことを特徴とする請求項 9 の記載の光電変換装置。

**【請求項 11】**

N 個の前記第 2 記憶部に対応して設けられた N 個の第 4 記憶部を更に有し、

N 個の前記第 4 記憶部の各々は、外部から入力される前記第 2 設定値を記憶して、対応する前記第 2 記憶部に出力する

ことを特徴とする請求項 10 に記載の光電変換装置。

**【請求項 12】**

前記第 1 記憶部に記憶されている前記第 1 設定値と、N 個の前記第 2 記憶部にそれぞれ記憶されている N 個の前記第 2 設定値とのうちの 1 つを選択的に有効化する選択部を更に有する

40

ことを特徴とする請求項 10 又は 11 に記載の光電変換装置。

**【請求項 13】**

前記選択部は、前記 N 回の前記第 2 走査に対応して、前記 N 個の前記第 2 設定値を順次有効化する

ことを特徴とする請求項 12 に記載の光電変換装置。

**【請求項 14】**

前記第 1 走査によって前記複数の行のうちの第 1 行の画素から信号が出力されている期間に、前記第 2 走査によって前記複数の行のうちの前記第 1 行とは異なる第 2 行の画素か

50

ら信号が出力される

ことを特徴とする請求項1乃至13のいずれか1項に記載の光電変換装置。

**【請求項15】**

前記第1走査の開始から終了までの期間の長さは、前記第2走査の開始から終了までの期間の長さと異なる

ことを特徴とする請求項1乃至14のいずれか1項に記載の光電変換装置。

**【請求項16】**

請求項1乃至15のいずれか1項に記載の光電変換装置と、

前記光電変換装置から出力される信号を処理する信号処理部と、

を有することを特徴とする光電変換システム。

10

**【請求項17】**

移動体であって、

請求項1乃至15のいずれか1項に記載の光電変換装置と、

前記光電変換装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と、

を有することを特徴とする移動体。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

20

本発明は、光電変換装置、光電変換システム及び移動体に関する。

**【背景技術】**

**【0002】**

特許文献1には、2次元画素アレイをローリングシャッタにより画素行単位で走査するCMOSイメージセンサが開示されている。また、特許文献1には、一実施形態として、AF制御に用いる測距用信号の読み出し動作を、撮像用画像の読み出し動作のブランク期間に行う例も開示されている。この例では、撮像動作中にAF制御を行うことができる。

**【先行技術文献】**

**【特許文献】**

**【0003】**

30

【文献】特開2004-140479号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

しかしながら、特許文献1に開示されているような1フレーム期間に複数の走査を行う複雑な走査手法においては、走査の設定に関する情報の通信が複雑化し、通信時間を十分に確保することが難しい場合がある。

**【0005】**

そこで、本発明は、1フレーム期間に複数の走査を行う構成において、より簡便な制御を実現し得る光電変換装置、光電変換システム及び移動体を提供することを目的とする。

40

**【課題を解決するための手段】**

**【0006】**

本発明の一観点によれば、複数の行をなすように配された複数の画素と、前記複数の画素から行ごとに順次信号を出力させるための第1走査及び第2走査を行う走査部と、外部からの入力に応じて、前記第1走査における複数行の画素の読み出し動作の設定を示す第1設定値を記憶する第1記憶部と、外部からの入力に応じて、前記第2走査における複数行の画素の読み出し動作の設定を示す第2設定値を記憶する第2記憶部と、を有し、前記走査部は、前記第1設定値に基づく前記第1走査と、前記第2設定値に基づく前記第2走査とを1フレーム期間に行い、前記第1記憶部による前記第1設定値の記憶と、前記第2記憶部による前記第2設定値の記憶とともに、前記第1走査の開始及び前記第2走査の開

50

始に先立って行われることを特徴とする光電変換装置が提供される。

**【発明の効果】**

**【0007】**

本発明によれば、1フレーム期間に複数の走査を行う構成において、より簡便な制御を実現し得る光電変換装置、光電変換システム及び移動体を提供することができる。

**【図面の簡単な説明】**

**【0008】**

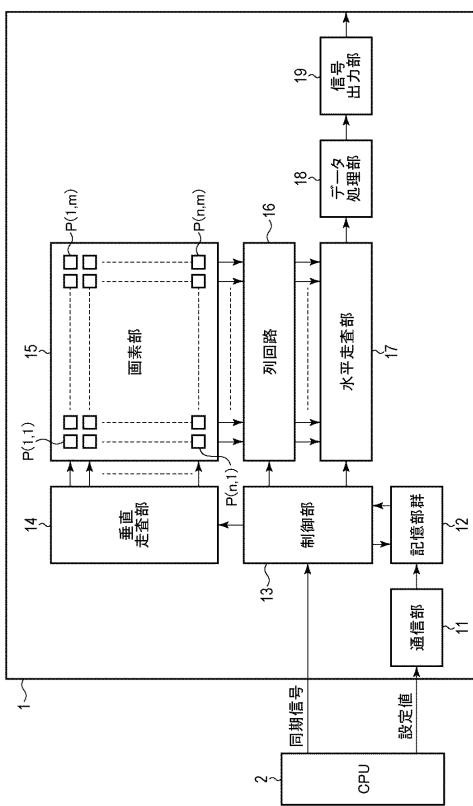

**【図1】**第1実施形態に係る光電変換装置の構成例を示すブロック図である。

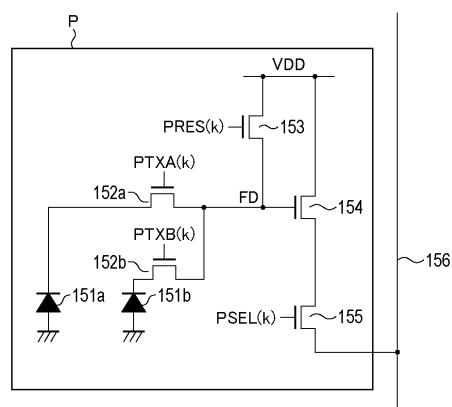

**【図2】**第1実施形態に係る画素の構成例を示す等価回路図である。

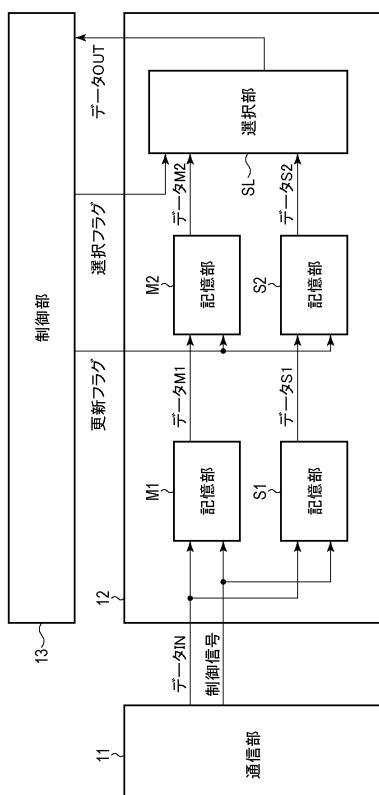

**【図3】**第1実施形態に係る記憶部群の構成例を示すブロック図である。

10

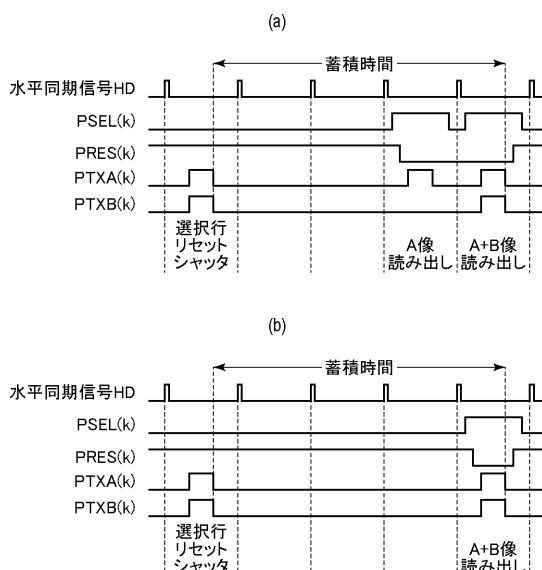

**【図4】**第1実施形態に係る1行の画素の駆動方法を示すタイミングチャートである。

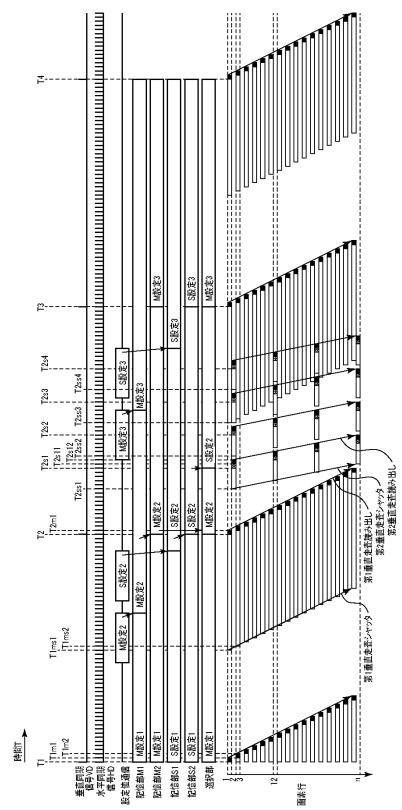

**【図5】**第1実施形態に係る画素部の駆動方法を示すタイミングチャートである。

**【図6】**第2実施形態に係る記憶部群の構成例を示すブロック図である。

**【図7】**第2実施形態に係る画素部の駆動方法を示すタイミングチャートである。

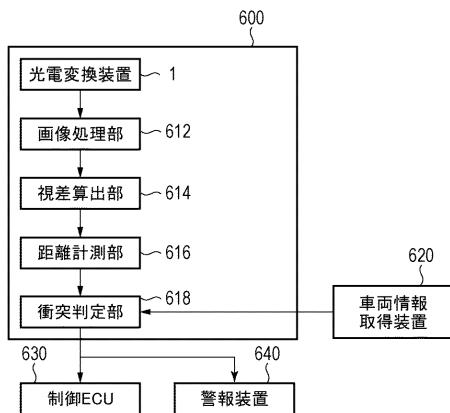

**【図8】**第3実施形態に係る撮像システムの概略構成を示すブロック図である。

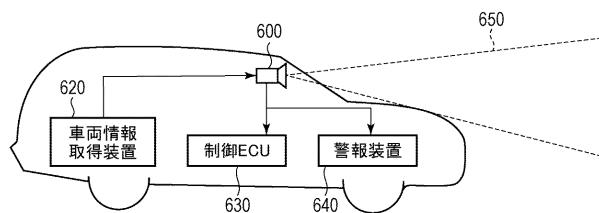

**【図9】**第4実施形態に係る撮像システム及び移動体の構成例を示す図である。

**【発明を実施するための形態】**

**【0009】**

以下、図面を参照しつつ、本発明の実施形態を説明する。複数の図面にわたって同一の要素又は対応する要素には共通の符号が付されており、その説明は省略又は簡略化されることがある。

20

**【0010】**

**[第1実施形態]**

図1は、本実施形態に係る光電変換装置1の構成例を示すブロック図である。光電変換装置1は、通信部11、記憶部群12、制御部13、垂直走査部14、画素部15、列回路16、水平走査部17、データ処理部18及び信号出力部19を有している。本実施形態においては、本発明が適用され得る光電変換装置1の一種である固体撮像装置の例を説明するが、これに限定されるものではない。本発明が適用され得る光電変換装置としては、固体撮像装置、焦点検出装置、測距装置、TOF (Time - Of - Flight) カメラ等が例示され得る。

30

**【0011】**

画素部15には、複数の行及び複数の列に渡って配された複数の画素Pが配されている。図1には、n行×m列の2次元状に配された画素P(1, 1)から画素P(n, m)が示されている。ここで、画素P(X, Y)の表記においては、Xが行番号を表しており、Yが列番号を表している。先頭行の行番号は1行目であり、先頭列の列番号は1列目であるものとする。なお、本明細書では、画素部15内の特定の位置に配された画素Pを示すときは「画素P(n, m)」のように行番号及び列番号とともに表記し、画素部15内の位置を特定しない場合には単に「画素P」と表記するものとする。

**【0012】**

垂直走査部14(走査部)は、行ごとに設けられた制御線を介して画素Pに接続されている。垂直走査部14は、画素P内の読み出し回路を駆動するための制御信号を、制御線を介して画素Pに供給する回路部である。垂直走査部14は、制御部13からの信号を受けて動作し、画素部15の画素Pから順次信号を出力させるための垂直走査を行う。垂直走査はシャッタ動作と読み出し動作とを含む。この垂直走査におけるシャッタ動作とは、画素部15の一部又は全部の行の画素Pに対して、光電変換素子のリセット及びリセットの解除を行単位で順次行い、露光(電荷の蓄積)を開始させる動作をいう。この垂直走査における読み出し動作とは、画素部15の一部又は全部の行の画素Pに対して、光電変換素子に蓄積された電荷に基づく画素信号を行単位で順次出力させる動作をいう。

40

**【0013】**

列回路16は、増幅回路、アナログ・デジタル変換(AD変換)回路、メモリ等を備え

50

る。列回路 16 は、画素 P から各列に対応して配された出力線を介して出力される画素信号を増幅し、A/D 変換を行い、デジタル画素信号としてメモリに保持する。

#### 【 0 0 1 4 】

水平走査部 17 は、制御部 13 からの信号を受けて動作し、列回路 16 の各列のメモリに順次、制御信号を出力する。水平走査部 17 から制御信号を受信した列回路 16 は、対応する列のメモリに保持されたデジタル画素信号をデータ処理部 18 へと出力する。

#### 【 0 0 1 5 】

データ処理部 18 は、所定のデジタル信号処理、パラレル・シリアル変換等を行うデジタル回路である。処理後のデータは信号出力部 19 へと出力される。信号出力部 19 は、LVDS (Low Voltage Differential Signaling) 回路等の外部インターフェース等を備える。信号出力部 19 は、取得されたデジタル画素信号をシリアルデータとして光電変換装置 1 の外部に出力する。

#### 【 0 0 1 6 】

制御部 13 は、垂直走査部 14、列回路 16、水平走査部 17 等に、これらが実行する動作及び動作タイミングを制御する制御信号を供給するための回路部である。

#### 【 0 0 1 7 】

CPU 2 は、光電変換装置 1 の動作を制御する演算処理回路である。CPU 2 は、例えば、光電変換装置 1 が搭載される光電変換システム内、すなわち光電変換装置 1 の外部に設けられ得る。CPU 2 は、制御部 13 に同期信号を送信する。また、CPU 2 は、通信部 11 に走査のタイミング等の設定を示す設定値を送信する。通信部 11 により受信された設定値は、記憶部群 12 に記憶され、その後、制御部 13 に供給される。

#### 【 0 0 1 8 】

図 2 は、本実施形態に係る画素 P の構成例を示す等価回路図である。画素 P は、光電変換部 151a、151b、転送トランジスタ 152a、152b、リセットトランジスタ 153、増幅トランジスタ 154 及び選択トランジスタ 155 を含む。また、1 つの画素 P には 1 つのマイクロレンズが対応して設けられている。言い換えると、2 つの、光電変換部 151a、151b は 1 つのマイクロレンズを共有している。これにより、光電変換部 151a、151b は、光学系の異なる射出瞳を通過した光を受けるように配されている。なお、図 2 には一例として、複数の画素 P のうちの k 列目に配された 1 つの画素 P を示しているが、他の画素 P も同様である。なお、図 2 に示されている制御信号の名称の括弧内の「k」は行番号を示している。すなわち、k は、1 以上 n 以下の整数である。

#### 【 0 0 1 9 】

光電変換部 151a、151b は、光電変換素子であり、例えばフォトダイオードである。光電変換部 151a、151b を構成するフォトダイオードのアノードは、接地ノードに接続されている。光電変換部 151a、151b を構成するフォトダイオードのカソードは、転送トランジスタ 152a、152b のソースにそれぞれ接続されている。転送トランジスタ 152a、152b のドレインは、リセットトランジスタ 153 のソース及び増幅トランジスタ 154 のゲートに接続されている。転送トランジスタ 152a、152b のドレイン、リセットトランジスタ 153 のソース及び増幅トランジスタ 154 のゲートの接続ノードは、いわゆるフローティングディフュージョン FD である。フローティングディフュージョン FD は、容量成分を含み、電荷保持部として機能するとともに、この容量成分からなる電荷電圧変換部を構成する。リセットトランジスタ 153 のドレイン及び増幅トランジスタ 154 のドレインは、電源ノード（電圧 VDD）に接続されている。増幅トランジスタ 154 のソースは、選択トランジスタ 155 のドレインに接続されている。選択トランジスタ 155 のソースは、出力線 156 に接続されている。出力線 156 には、図示しない電流源が接続されている。なお、トランジスタのソースとドレインの呼称は、トランジスタの導電型又は着目する機能等に応じて異なることがあり、上述のソースとドレインとは逆の名称で呼ばれることがある。

#### 【 0 0 2 0 】

図 2 に示す回路構成の場合、各行の制御線は、2 つの転送ゲート信号線と、リセット信

10

20

30

40

50

号線と、選択信号線とを含む。2つの転送ゲート信号線は、対応する行に属する画素Pの転送トランジスタ152a、152bのゲートに接続されており、垂直走査部14から供給される制御信号PTXA、PTXBを転送トランジスタ152a、152bのゲートに供給する。例えば、k行目の画素Pには、k行目の2つの転送ゲート信号線を介して制御信号PTXA(k)、PTXB(k)が供給される。

#### 【0021】

リセット信号線は、対応する行に属する画素Pのリセットトランジスタ153のゲートに接続されており、垂直走査部14から供給される制御信号PRESをリセットトランジスタ153のゲートに供給する。例えば、k行目の画素Pには、k行目のリセット信号線を介して制御信号PRES(k)が供給される。

10

#### 【0022】

選択信号線は、対応する行に属する画素Pの選択トランジスタ155のゲートに接続されており、垂直走査部14から供給される制御信号PSELを選択トランジスタ155のゲートに供給する。例えば、k行目の画素Pには、k行目の選択信号線を介して制御信号PSEL(k)が供給される。

#### 【0023】

画素Pの各トランジスタがNチャネルトランジスタで構成される場合、垂直走査部14からハイレベルの制御信号が供給されると対応するトランジスタがオンとなり、垂直走査部14からローレベルの制御信号が供給されると対応するトランジスタがオフとなる。ここでは、ハイレベルが論理値「1」に対応し、ローレベルが論理値「0」に対応するものとする。なお、画素Pの各トランジスタは、Pチャネルトランジスタで構成してもよい。画素Pの各トランジスタをPチャネルトランジスタで構成する場合、各トランジスタを駆動する制御信号の信号レベルはNチャネルトランジスタの場合とは逆になる。

20

#### 【0024】

被写体の光学像が画素部15に入射すると、各画素Pの光電変換部151a、151bは、入射光をその光量に応じた量の電荷に変換（光電変換）するとともに、生じた電荷を蓄積する。転送トランジスタ152a、152bは、オンになることで光電変換部151a、151bにそれぞれ蓄積された電荷をフローティングディフュージョンFDに転送する。

#### 【0025】

30

フローティングディフュージョンFDは、光電変換部151a、151bから転送された電荷を保持するとともに、その容量成分による電荷電圧変換によって、光電変換部151a、151bから転送された電荷の量に応じた電圧となる。增幅トランジスタ154は、ドレインに電圧VDDが供給され、ソースに選択トランジスタ155を介してバイアス電流が供給される構成となっており、ゲートを入力ノードとする増幅部（ソースフォロワ回路）を構成する。これにより増幅トランジスタ154は、フローティングディフュージョンFDの電圧に基づく画素信号を、選択トランジスタ155を介して出力線156に出力する。

#### 【0026】

リセットトランジスタ153は、オンになることでフローティングディフュージョンFDを電圧VDDに応じた電圧にリセットする。また、リセットトランジスタ153と転送トランジスタ152a、152bとが同時にオンになることで、光電変換部151a、151bを電圧VDDに応じた電圧にリセットすることができる。

40

#### 【0027】

図3は、本実施形態に係る記憶部群12の構成例を示すブロック図である。記憶部群12は、記憶部M1（第3記憶部）、記憶部M2（第1記憶部）、記憶部S1（第4記憶部）、記憶部S2（第2記憶部）及び選択部SLを有している。記憶部M1、M2、S1、S2は、走査に関する設定値を含む情報を記憶する記憶素子である。選択部SLは、入力された選択フラグに応じて複数の入力信号のうちの1つを選択して出力する選択回路である。

50

**【 0 0 2 8 】**

C P U 2 からの出力信号に応じて、通信部 1 1 は、これらの記憶部 M 1、S 1 におけるデータ入出力を制御する制御信号と、走査のタイミング等の設定を示す設定値に関するデータ(データ I N)とを記憶部 M 1、S 1 に出力する。記憶部 M 1、S 1 は、それぞれ、1 フレーム期間内に行われる別の走査の設定値を記憶することができる。ここで、記憶部 M 1 が記憶する設定値をデータ M 1 と呼び、記憶部 S 1 が記憶する設定値をデータ S 1 と呼ぶ。

**【 0 0 2 9 】**

記憶部 M 1 は、データ M 1 を記憶部 M 2 に出力し、記憶部 S 1 は、データ S 1 を記憶部 S 2 に出力する。記憶部 M 2 は、制御部 1 3 から入力される更新フラグに基づくタイミングで、記憶部 M 1 から入力されるデータ M 1 を記憶することにより、記憶部 M 2 が記憶している設定値を更新する。記憶部 S 2 は、制御部 1 3 から入力される更新フラグに基づくタイミングで、記憶部 S 1 から入力されるデータ S 1 を記憶することにより、記憶部 S 2 が記憶している設定値を更新する。ここで、記憶部 M 2 が記憶する設定値をデータ M 2 と呼び、記憶部 S 2 が記憶する設定値をデータ S 2 と呼ぶ。

10

**【 0 0 3 0 】**

記憶部 M 2、S 2 は、データ M 2、S 2 をそれぞれ選択部 S L に出力する。選択部 S L は、制御部 1 3 から入力される選択フラグに基づいて、データ M 2 とデータ S 2 の一方を選択的に有効化する。選択部 S L は、選択されたデータをデータ O U T として制御部 1 3 に出力する。

20

**【 0 0 3 1 】**

図 4 ( a ) は、第 1 実施形態に係る 1 行の画素 P の駆動方法の一例を示すタイミングチャートである。図 4 ( b ) は、第 1 実施形態に係る 1 行の画素 P の駆動方法の別の例を示すタイミングチャートである。図 4 ( a ) 及び図 4 ( b ) は、画素部 1 5 の各行におけるシャッタ動作及び読み出し動作の概略を示している。なお、図 4 ( a ) 及び図 4 ( b ) には、k 行目の画素 P に関する制御信号のみを例示している。

**【 0 0 3 2 】**

まず、図 4 ( a ) を参照して、駆動方法の第 1 の例を説明する。本例は、一方の光電変換部 1 5 1 a で生成された電荷のみに基づく画素信号( A 像)と、光電変換部 1 5 1 a 及び光電変換部 1 5 1 b の両方で生成された電荷に基づく画素信号( A + B 像)との読み出しを連続して行う駆動方法である。

30

**【 0 0 3 3 】**

シャッタ動作では、制御信号 P R E S ( k )、P T X A ( k )、P T X B ( k ) をハイレベルに制御し、転送トランジスタ 1 5 2 a、1 5 2 b 及びリセットトランジスタ 1 5 3 を同時にオン状態にする。これにより、光電変換部 1 5 1 a、1 5 1 b を転送トランジスタ 1 5 2 a、1 5 2 b 及びリセットトランジスタ 1 5 3 を介して電源ノードに接続し、光電変換部 1 5 1 a、1 5 1 b を電圧 V D D に応じた電位にリセットする。この後に、制御信号 P T X A ( k )、P T X B ( k ) をローレベルに制御して光電変換部 1 5 1 a、1 5 1 b のリセットを解除するタイミングが、光電変換部 1 5 1 a、1 5 1 b における電荷の蓄積期間の開始時刻となる。

40

**【 0 0 3 4 】**

A 像の読み出し動作では、制御信号 P R E S ( k ) をローレベルに、制御信号 P S E L ( k )、P T X A ( k ) をハイレベルに制御し、リセットトランジスタ 1 5 3 がオフの状態で、転送トランジスタ 1 5 2 a と選択トランジスタ 1 5 5 を同時にオン状態にする。これにより、光電変換部 1 5 1 a に蓄積されている電荷がフローティングディフュージョン F D へと転送される。増幅トランジスタ 1 5 4 は、フローティングディフュージョン F D の電位に応じた A 像の画素信号を、選択トランジスタ 1 5 5 を介して出力線 1 5 6 に出力する。このようにして、光電変換部 1 5 1 a で生成された電荷に基づく A 像の読み出しが行われる。

**【 0 0 3 5 】**

50

A 像の読み出し動作に続いて、A + B 像の読み出し動作が行われる。A + B 像の読み出し動作では、制御信号 P R E S ( k ) をローレベルに、制御信号 P S E L ( k ) 、 P T X A ( k ) 、 P T X B ( k ) をハイレベルに制御する。このとき、リセットトランジスタ 153 がオフの状態で、転送トランジスタ 152a 、 152b 及び選択トランジスタ 155 が同時にオン状態になる。これにより、光電変換部 151a に蓄積されている電荷と光電変換部 151b に蓄積されている電荷とがフローティングディフュージョン F D へと転送される。増幅トランジスタ 154 は、フローティングディフュージョン F D の電位に応じた A + B 像の画素信号を、選択トランジスタ 155 を介して出力線 156 に出力する。このようにして、光電変換部 151a 、 151b で生成された電荷に基づく A + B 像の読み出しが行われる。

#### 【 0 0 3 6 】

A + B 像の画素信号から A 像の画素信号を減算することにより、光電変換部 151b で生成された電荷に基づく画素信号 ( B 像 ) を得ることができる。このようにして得られた A 像の画素信号及び B 像の画素信号は、焦点検出等の測距の用途に用いられ得る。焦点検出の結果は、撮像システムの合焦動作等に利用可能である。また、A + B 像の画素信号は画像の生成に用いられ得る。このように本例では、測距用の画素信号と画像用の画素信号を取得することができる。

#### 【 0 0 3 7 】

次に、図 4 ( b ) を参照して、駆動方法の第 2 の例を説明する。本例は、光電変換部 151a 及び光電変換部 151b の両方で生成された電荷に基づく画素信号 ( A + B 像 ) のみの読み出しを行う駆動方法である。本例では、図 4 ( a ) に示されている第 1 の例に対して、A 像の読み出し動作が省略されている。それ以外の点は、図 4 ( b ) と概ね同様であるため説明を省略する。本例では、A 像及び B 像の画素信号を得ることはできないが、より簡略な駆動により画像用の画素信号を取得することができる。

#### 【 0 0 3 8 】

なお、図 4 ( a ) において、A 像の画素信号を取得してから、A + B 像に代えて B 像の画素信号を取得してもよい。この駆動方法であっても、測距用の画素信号を取得することができる。また、A 像の画素信号と B 像の画素信号の取得後にこれらを加算することにより、画像用の A + B 像の画素信号を取得することもできる。

#### 【 0 0 3 9 】

図 4 ( a ) 及び図 4 ( b ) においては明示されていないが、制御信号 P R E S ( k ) をローレベルにした直後、すなわち、制御信号 P T X A ( k ) 、 P T X B ( k ) をハイレベルにする前に、N 信号の読み出しを行ってもよい。N 信号は、リセット解除後のフローティングディフュージョンの電位に応じた信号であり、リセットにより生じ得るリセットノイズのレベルを示している。A 像、B 像又は A + B 像の画素信号から N 信号を減算する相関二重サンプリング処理を行うことで、リセットノイズの影響を低減することができる。

#### 【 0 0 4 0 】

図 5 は、本実施形態に係る画素部 15 の駆動方法を示すタイミングチャートである。本実施形態では、第 1 垂直走査 ( 第 1 走査 ) により ( 2 k - 1 ) 行目の画素 P から画像用の画素信号 ( A + B 像 ) を取得し、第 2 垂直走査 ( 第 2 走査 ) により ( 10 k - 8 ) 行目の画素 P から測距用の画素信号 ( A 像と A + B 像 ) を取得する例を説明する。すなわち、第 1 垂直走査における各行の駆動方法は、例えば図 4 ( b ) に示すものであり、第 2 垂直走査における各行の駆動方法は、例えば図 4 ( a ) に示すものである。なお、垂直走査の種類、読み出しを行う行の番号、読み出しを行う行の割合等は、あくまでも一例であり、例示したものに限定されるものではない。

#### 【 0 0 4 1 】

図 5 の上段には、垂直同期信号 V D 及び水平同期信号 H D が入力されるタイミングが示されている。図 5 の中段の「設定値通信」におけるボックスは、通信部 11 から記憶部群 12 に入力される設定値を示している。図 5 の中段の「記憶部 M 1 」から「記憶部 S 2 」におけるボックスは、対応する記憶部に記憶されている設定値を示している。図 5 の中段

10

20

30

40

50

の「選択部」におけるボックスは、選択部 S L から出力されている設定値を示している。図 5 の下段は、各画素行の画素におけるシャッタ動作と読み出し動作のタイミングを示している。各画素行におけるボックスは、シャッタ動作から読み出し動作の間の期間を示している。

#### 【 0 0 4 2 】

まず、図 5 に示されている第 1 フレーム（時刻 T 1 から時刻 T 2 ）の動作について説明する。第 1 フレームは、第 1 垂直走査のみを行い、第 2 垂直走査を行わない場合の例を示すものである。

#### 【 0 0 4 3 】

時刻 T 1 において、垂直同期信号 V D と同期して、第 1 垂直走査の読み出し動作が開始される。なお、第 1 フレームの前のフレーム、すなわち、時刻 T 1 以前の期間において、あらかじめシャッタ動作が行われているものとする。

10

#### 【 0 0 4 4 】

時刻 T 1 から時刻 T 1 m 1 の期間において、水平同期信号 H D と同期して、1 行目の画素 P から画像用の A + B 像の画素信号の読み出し動作が行われる。次に、時刻 T 1 m 1 から時刻 T 1 m 2 の期間において、水平同期信号 H D と同期して、3 行目の画素 P から画像用の A + B 像の画素信号の読み出し動作が行われる。以下同様に、水平同期信号 H D と同期して、( 2 k - 1 ) 行目の画素 P の読み出し動作が順次行われる。

10

#### 【 0 0 4 5 】

また、第 1 フレームにおいて、時刻 T 1 m s 1 から第 1 垂直走査のシャッタ動作が開始される。これは、第 2 フレームの読み出し動作のための電荷蓄積を開始するためのものである。時刻 T 1 m s 1 において、水平同期信号 H D と同期して、1 行目の画素 P のリセットを解除するシャッタ動作が行われる。次に、時刻 T 1 m s 2 において、水平同期信号 H D と同期して、3 行目の画素 P のリセットを解除するシャッタ動作が行われる。以下同様に、水平同期信号 H D と同期して、( 2 k - 1 ) 行目の画素 P のシャッタ動作が順次行われる。

20

#### 【 0 0 4 6 】

次に、図 5 に示されている第 2 フレーム（時刻 T 2 から時刻 T 3 ）の動作について説明する。第 2 フレームは、1 回の第 1 垂直走査と 4 回の第 2 垂直走査とを行う例を示すものである。なお、第 1 垂直走査及び第 2 垂直走査のいずれよりも前に、第 1 記憶部である記憶部 M 2 による M 設定 2 の記憶と、第 2 記憶部である記憶部 S 2 による S 設定 2 の記憶が行われている。

30

#### 【 0 0 4 7 】

時刻 T 2 において、垂直同期信号 V D と同期して、第 1 垂直走査の読み出し動作が開始される。時刻 T 2 から時刻 T 2 m 1 の期間において、水平同期信号 H D と同期して、1 行目の画素 P から画像用の A + B 像の画素信号の読み出し動作が行われる。以下同様に、水平同期信号 H D と同期して、( 2 k - 1 ) 行目の画素 P の読み出し動作が順次行われる。

#### 【 0 0 4 8 】

また、時刻 T 2 s s 3 において、水平同期信号 H D と同期して、1 行目の画素 P のリセットを解除するシャッタ動作が開始される。これは、第 3 フレームの読み出し動作のための電荷蓄積を開始するためのものである。時刻 T 2 s s 3 において、水平同期信号 H D と同期して、1 行目の画素 P のリセットを解除するシャッタ動作が行われる。以下同様に、水平同期信号 H D と同期して、( 2 k - 1 ) 行目の画素 P のシャッタ動作が順次行われる。

40

#### 【 0 0 4 9 】

以上のように、本例においては、第 2 フレームにおける第 1 垂直走査は、第 1 フレームにおける第 1 垂直走査と概ね同様であるものとする。しかしながら、第 1 垂直走査の設定内容がフレーム間で異なっていてもよい。

#### 【 0 0 5 0 】

第 2 フレームでは、上述の第 1 垂直走査と並行して 4 回の第 2 垂直走査が行われる。時刻 T 2 s s 1 から、1 回目の第 2 垂直走査が開始される。時刻 T 2 s s 1 において、水平

50

同期信号HDと同期して、2行目の画素Pのリセットを解除するシャッタ動作が行われる。時刻T2s1から時刻T2s11の期間において、水平同期信号HDと同期して、2行目の画素Pから測距用のA像の画素信号の読み出し動作が行われる。その後、時刻T2s11から時刻T2s12の期間において、水平同期信号HDと同期して、2行目の画素Pから測距及び画像用のA+B像の画素信号の読み出し動作が行われる。上述のように、A+B像の画素信号及びA像の画素信号から、B像の画素信号を算出することができ、A像の画素信号とB像の画素信号は測距に用いることができる。

#### 【0051】

時刻T2ss1から水平同期信号HDの2周期後の時刻において、12行目の画素に対するシャッタ動作が行われる。その後、12行目の画素Pに対しても同様に2つの画素信号の読み出し動作が行われる。以下、同様にして、水平同期信号HDの2周期ごとに、(10k-8)行目の画素Pのシャッタ動作及び2つの画素信号の読み出し動作が順次行われる。

10

#### 【0052】

時刻T2ss2から、2回目の第2垂直走査が開始され、時刻T2ss3から、3回目の第2垂直走査が開始され、時刻T2ss4から、4回目の第2垂直走査が開始される。2回目から4回目の第2垂直走査の内容は、1回目の第2垂直走査と同様であるため説明を省略する。

#### 【0053】

次に、図5に示されている第3フレーム(時刻T3から時刻T4)の動作について説明する。第3フレームは、第1垂直走査のみを行い、第2垂直走査を行わない場合の例であり、第1フレームと同様であるため説明を省略する。

20

#### 【0054】

次に、上述の第1垂直走査及び第2垂直走査における読み出し動作の設定に関する記憶部群12の動作について図5を参照して説明する。ここで、図5における「M設定#」(#は自然数)は、第1垂直走査の設定値(第1設定値)を意味し、「S設定#」(#は自然数)は、第2垂直走査の設定値(第2設定値)を意味するものとする。

#### 【0055】

第1フレームの時刻T1の時点においては、記憶部M1及び記憶部M2にM設定1が記憶されており、記憶部S1及び記憶部S2にS設定1が記憶されている。ここで、選択部SLは、記憶部M2に記憶されているM設定1を選択して制御部13に出力している。これにより、時刻T1から開始される第1垂直走査の読み出し動作は、M設定1に基づいて行われる。

30

#### 【0056】

時刻T1と時刻T2の間、すなわち、第1フレームの期間内において、CPU2は、第2フレームにおける第1垂直走査の設定値であるM設定2を通信部11に送信する。通信部11がM設定2を受信すると、その直後に、M設定2は、記憶部M1に記憶される。その後、CPU2は、第1フレームの期間内に第2フレームにおける第2垂直走査の設定値であるS設定2を通信部11に送信する。通信部11がS設定2を受信すると、その直後に、S設定2は、記憶部S1に記憶される。

40

#### 【0057】

その後、時刻T2において、記憶部M1に記憶されているM設定2が記憶部M2に記憶され、記憶部S1に記憶されているS設定2が記憶部S2に記憶される。このとき、選択部SLの出力もM設定1からM設定2に変化する。これにより、時刻T2から開始される第1垂直走査の読み出し動作には、M設定2が適用される。

#### 【0058】

次に、時刻T2s1において、選択部SLによる信号の選択の切り替えが行われ、選択部SLの出力がM設定2からS設定2に変化する。これにより、時刻T2s1から開始される第2垂直走査の読み出し動作には、S設定2が適用される。

#### 【0059】

50

時刻 T<sub>2</sub>と時刻 T<sub>3</sub>の間、すなわち、第2フレームの期間内において、CPU2は、第3フレームにおける第1垂直走査の設定値であるM設定3を通信部11に送信する。通信部11がM設定3を受信すると、その後に、M設定3は、記憶部M1に記憶される。その後、CPU2は、第2フレームの期間内に第3フレームにおける第2垂直走査の設定値であるS設定3を通信部11に送信する。通信部11がS設定3を受信すると、その後に、S設定3は、記憶部S1に記憶される。

#### 【0060】

その後、時刻 T<sub>3</sub>において、記憶部M1に記憶されているM設定3が記憶部M2に記憶され、記憶部S1に記憶されているS設定3が記憶部S2に記憶される。更に、本例においては、第3フレームに第1垂直走査のみが行われるため、時刻 T<sub>3</sub>において選択部SLにより選択される信号が切り替えられる。したがって、選択部SLの出力は、S設定2からM設定3に変化する。これにより、時刻 T<sub>3</sub>から開始される第1垂直走査の読み出し動作には、M設定3が適用される。

10

#### 【0061】

本実施形態のように1フレーム期間に第1垂直走査と第2垂直走査の2つを行う走査手法においては、走査のタイミングに合わせて設定値の切り替えを高速に行う必要があり、走査の制御が複雑化し得る。そのため、例えば、設定値の通信時間の確保が難しくなる場合もあり得る。これに対し、本実施形態では、記憶部群12が第1垂直走査の設定値を記憶する記憶部M2と、第2垂直走査の設定値を記憶する記憶部S2とを有している。これにより、記憶部群12は、第1垂直走査の設定値と第2垂直走査の設定値の両方を同時に記憶することができる。したがって、第1垂直走査と第2垂直走査に先立って、あらかじめこれらの設定値を通信しておくことができるため、走査の制御を簡略化することができる。以上のように、本実施形態によれば、1フレーム期間に複数の走査を行う構成において、より簡便な制御を実現し得る光電変換装置1が提供される。

20

#### 【0062】

なお、本実施形態では、記憶部群12が外部から入力される第1垂直走査の設定値を一時的に記憶する記憶部M1と、外部から入力される第2垂直走査の設定値を一時的に記憶する記憶部S1とを更に有している。これにより、設定値が反映されるタイミングを通信のタイミングよりも遅らせることができるため、通信時間をより多く確保することができる。また、この構成により、記憶部M1に第1垂直走査の設定値が入力される時刻と記憶部S1に第2垂直走査の設定値が入力される時刻とを、これらの設定値が適用されるフレーム期間の開始よりも前にすることができます。これにより、設定値が用いられるフレーム期間の開始前に設定値の通信を完了することができ、通信時間の確保が容易になる。また、記憶部M1に記憶された設定値が記憶部M2に出力される時刻と、記憶部S1に記憶された設定値が記憶部S2に出力される時刻とは、フレームの開始時刻である。これにより、フレームの開始に合わせて設定値を有効化することができる。

30

#### 【0063】

また、本実施形態では、記憶部群12が記憶部M2に記憶されている設定値と、記憶部S2に記憶されている設定値とを選択的に出力する選択部SLを更に有している。これにより、第1垂直走査の設定値と第2垂直走査の設定値のいずれかを有効化するタイミングと記憶部M2、S2が設定値を記憶するタイミングとをずらすことができるため、通信時間をより多く確保することができる。また、この構成により、フレーム期間の開始時刻よりも後のタイミングで第1垂直走査の設定値と第2垂直走査の設定値のいずれかを有効化することができる。これにより、設定値を走査の直前に変更することができ、走査の自由度が向上する。

40

#### 【0064】

なお、上述のM設定#及びS設定#は、垂直走査の設定値だけではなく、ゲイン設定、データ補正設定等に関する設定値を含んでもよい。これにより、例えば、第1垂直走査のゲインを1倍とし、第2垂直走査のゲインを4倍とする等、第1垂直走査と第2垂直走査の間で異なるゲインを適用することができる。

50

**【 0 0 6 5 】**

また、図5に示す駆動方法の例では、第1垂直走査では、画像用の画素信号を取得し、第2垂直走査では、測距用の画素信号を取得できる例を説明したが、これに限られるものではない。例えば、第1垂直走査では、測距用の画素信号を取得し、第2垂直走査では、画像用の画素信号を取得してもよい。また、第1垂直走査と第2垂直走査の両方で画像用の画素信号を取得してもよく、第1垂直走査と第2垂直走査の両方で測距用の画素信号を取得してもよい。

**【 0 0 6 6 】**

また、図5に示す駆動方法における設定値の説明では、読み出し動作に関してのみ述べているが、シャッタ動作の設定値に関しても同様の処理が適用可能である。

10

**【 0 0 6 7 】****[ 第2実施形態 ]**

第1実施形態においては、第2フレームの4回の第2垂直走査において同一の設定値が用いられている。これに対し、本実施形態では、4回の第2垂直走査の各回において設定値を変更する例を説明する。第1実施形態と共通の要素については説明を簡略化又は省略する場合がある。

**【 0 0 6 8 】**

図6は、本実施形態に係る記憶部群12の構成例を示すブロック図である。記憶部群12は、記憶部M1、M2、S11、S12、S21、S22、S31、S32、S41、S42及び選択部SLを有している。すなわち、本実施形態においては、第1実施形態の記憶部S1が4個の記憶部S11、S21、S31、S41に置き換えられており、第1実施形態の記憶部S2が4個の記憶部S12、S22、S32、S42に置き換えられている。

20

**【 0 0 6 9 】**

記憶部S11、S12、S21、S22、S31、S32、S41、S42が記憶する設定値をそれぞれ、データS11、S12、S21、S22、S31、S32、S41、S42と呼ぶ。選択部SLは、制御部13から入力される選択フラグに基づいて、データM2、S12、S22、S32、S42のうちの1つを選択的に有効化する。選択部SLは、選択されたデータをデータOUTとして制御部13に出力する。

30

**【 0 0 7 0 】**

図7は、本実施形態に係る画素部15の駆動方法を示すタイミングチャートである。第1実施形態との相違点は、読み出し動作の設定に関する記憶部群12の動作であり、シャッタ動作及び読み出し動作のタイミングは第1実施形態と同様である。以下では、第1実施形態と相違する点のみを説明する。図7における「S1設定#」、「S2設定#」、「S3設定#」及び「S4設定#」は、それぞれ、第2フレームにおける1回目から4回目の第2垂直走査の設定値を意味するものとする。

40

**【 0 0 7 1 】**

第1フレームの時刻T1の時点においては、記憶部M1、M2にM設定1が記憶されている。また、記憶部S11、S12にはS1設定1が記憶されており、記憶部S21、S22にはS2設定1が記憶されている。また、記憶部S31、S32にはS3設定1が記憶されており、記憶部S41、S42にはS4設定1が記憶されている。ここで、選択部SLは、記憶部M2に記憶されているM設定1を選択して制御部13に出力している。これにより、時刻T1から開始される第1垂直走査の読み出し動作は、M設定1に基づいて行われる。

**【 0 0 7 2 】**

時刻T1と時刻T2の間、すなわち、第1フレームの期間内において、CPU2は、第2フレームにおける第1垂直走査の設定値であるM設定2を通信部11に送信する。通信部11がM設定2を受信すると、その直後に、M設定2は、記憶部M1に記憶される。その後、CPU2は、第1フレームの期間内に第2フレームにおける1回目の第2垂直走査の設定値であるS1設定2を通信部11に送信する。通信部11がS1設定2を受信する

50

と、その後に、S1設定2は、記憶部S11に記憶される。その後、同様にして、CPU2は、2から4回目の第2垂直走査の設定値であるS2設定2、S3設定2、S4設定2を順次通信部11に送信する。S2設定2、S3設定2、S4設定2は、それぞれ、記憶部S21、S31、S41に記憶される。

#### 【0073】

その後、時刻T2において、記憶部M1に記憶されているM設定2が記憶部M2に記憶される。また、記憶部S11、S21、S31、S41に記憶されているS1設定2、S2設定2、S3設定2、S4設定2が記憶部S12、S22、S32、S42にそれぞれ記憶される。このとき、選択部SLの出力もM設定1からM設定2に変化する。これにより、時刻T2から開始される第1垂直走査の読み出し動作には、M設定2が適用される。10

#### 【0074】

次に、時刻T2s1において、選択部SLによる信号の選択の切り替えが行われ、選択部SLの出力がM設定2からS1設定2に変化する。これにより、時刻T2s1から開始される2回目の第2垂直走査の読み出し動作には、S1設定2が適用される。

#### 【0075】

次に、時刻T2s2において、選択部SLによる信号の選択の切り替えが行われ、選択部SLの出力がS1設定2からS2設定2に変化する。これにより、時刻T2s2から開始される2回目の第2垂直走査の読み出し動作には、S2設定2が適用される。

#### 【0076】

以下、時刻T2s3、T2s4においても同様にして選択部SLによる信号の選択の切り替えが行われ、3回目と4回目の第2垂直走査の読み出し動作には、S3設定2、S4設定2がそれぞれ適用される。このように、1回目から4回目の第2垂直走査において、選択部SLは、S1設定2からS4設定2を順次有効化する。これにより、4回の第2垂直走査において異なる設定値が適用される。20

#### 【0077】

時刻T2と時刻T3の間、すなわち、第2フレームの期間内において、CPU2は、第3フレームにおける第1垂直走査の設定値であるM設定3を通信部11に送信する。通信部11がM設定3を受信すると、その後に、M設定3は、記憶部M1に記憶される。その後、CPU2は、第2フレームの期間内に第3フレームにおける1回目の第2垂直走査の設定値であるS1設定3を通信部11に送信する。通信部11がS1設定3を受信すると、その後に、S1設定3は、記憶部S11に記憶される。その後、同様にして、CPU2は、2から4回目の第2垂直走査の設定値であるS2設定3、S3設定3、S4設定3を順次通信部11に送信する。S2設定3、S3設定3、S4設定3は、それぞれ、記憶部S21、S31、S41に記憶される。30

#### 【0078】

その後、時刻T3において、記憶部M1に記憶されているM設定3が記憶部M2に記憶される。また、記憶部S11、S21、S31、S41に記憶されているS1設定3、S2設定3、S3設定3、S4設定3が記憶部S12、S22、S32、S42にそれぞれ記憶される。更に、本例においては、第3フレームに第1垂直走査のみが行われるため、時刻T3において選択部SLにより選択される信号が切り替えられる。したがって、選択部SLの出力は、S4設定2からM設定3に変化する。これにより、時刻T3から開始される第1垂直走査の読み出し動作には、M設定3が適用される。40

#### 【0079】

本実施形態では、記憶部群12が第2垂直走査の設定値を記憶する記憶部を4組有している。これにより、4回の第2垂直走査の各回において異なる設定値を設定することができ、第2垂直走査の設定の自由度が向上する。

#### 【0080】

なお、第2垂直走査の設定値を記憶する記憶部の数は4組に限定されるものではない。記憶部の数は設計に応じて適宜変更可能であり、例えば、1フレーム期間あたりの第2垂直走査の最大回数に応じて設定することができる。例えば、第2垂直走査の最大回数がN50

回（Nは2以上の整数）である場合には、第2垂直走査の設定値を記憶する記憶部をN組設けることにより、各回の第2垂直走査において異なる設定値を適用することができる。具体的には、図6の記憶部S11、S21、S31、S41をN個の記憶部（N個の第4記憶部）に置き換え、記憶部S12、S22、S32、S42をN個の記憶部（N個の第2記憶部）に置き換えることで、N回の設定値に基づく第2垂直走査が実現される。

#### 【0081】

なお、上述のM設定#、S1設定#、S2設定#、S3設定#及びS4設定#は、第1実施形態の場合と同様に、垂直走査の設定値だけではなく、ゲイン設定、データ補正設定等に関する設定値を含んでもよい。これにより、例えば、1回目の第2垂直走査のゲインを1倍とし、2回目の第2垂直走査のゲインを2倍とする等、複数の第2垂直走査の間で異なるゲインを適用することができる。10

#### 【0082】

##### [第3実施形態]

本発明の第3実施形態による撮像システムについて、図8を用いて説明する。図8は、本実施形態による撮像システムの概略構成を示すブロック図である。図8に示す光電変換装置1は、上述の第1又は第2実施形態で述べた光電変換装置1である。すなわち、本実施形態による撮像システム500は、上述の第1又は第2実施形態で述べた光電変換装置1が適用され得る光電変換システムの一例である。

#### 【0083】

本実施形態による撮像システム500は、特に限定されるものではないが、例えば、デジタルスチルカメラ、デジタルカムコーダ、カメラヘッド、複写機、ファックス、携帯電話、車載カメラ、観測衛星等に適用可能である。20

#### 【0084】

撮像システム500は、図8に示すように、光電変換装置1、レンズ502、絞り504、バリア506、信号処理部508、タイミング発生部520、全体制御・演算部518を有している。撮像システム500は、また、メモリ部510、記録媒体制御I/F部516、外部I/F部512を有している。

#### 【0085】

レンズ502は、被写体の光学像を光電変換装置1の画素部15に結像するためのものである。絞り504は、レンズ502を通った光量を可変にするためのものである。バリア506は、レンズ502の保護のためのものである。光電変換装置1は、先の実施形態で説明した光電変換装置1であって、レンズ502により結像された光学像に基づく信号を信号処理部508に出力するものである。光電変換装置1から出力される信号には、画素Pから読み出されるA信号、A+B信号、B信号等が含まれ得る。30

#### 【0086】

信号処理部508は、光電変換装置1より出力される信号に対して、所望の処理、補正、データ圧縮等を行うものである。信号処理部508により行われる処理には、補正が施された画像データの生成、A信号及びB信号に基づいて被写体までの距離情報を取得する処理等が含まれる。信号処理部508は、光電変換装置1と同じ基板に搭載されていてもよいし、別の基板に搭載されていてもよい。また、信号処理部508の一部の機能が光電変換装置1と同じ基板に搭載され、信号処理部508の他の一部の機能が別の基板に搭載されていてもよい。40

#### 【0087】

タイミング発生部520は、光電変換装置1及び信号処理部508に、各種タイミング信号を出力するためのものである。全体制御・演算部518は、撮像システム500の全体の駆動及び演算処理を司る制御部である。第1又は第2実施形態におけるCPU2は、全体制御・演算部518とタイミング発生部520の一方又は両方に対応するものであつてもよい。ここで、タイミング信号等の制御信号は撮像システム500の外部から入力されてもよく、撮像システム500は、少なくとも光電変換装置1と、光電変換装置1から出力された信号を処理する信号処理部508とを有していればよい。

10

20

30

40

50

**【 0 0 8 8 】**

メモリ部 510 は、画像データを一時的に記憶するためのフレームメモリ部である。記録媒体制御 I/F 部 516 は、記録媒体 514 への記録或いは記録媒体 514 からの読み出しを行うためのインターフェース部である。外部 I/F 部 512 は、外部コンピュータ等と通信するためのインターフェース部である。記録媒体 514 は、撮像データの記録又は読み出しを行うための半導体メモリ等の着脱可能な記録媒体である。

**【 0 0 8 9 】**

このようにして、第 1 又は第 2 実施形態による光電変換装置 1 を適用した撮像システム 500 を構成することにより、より簡便な制御を実現し得る撮像システム 500 を実現することができる。

10

**【 0 0 9 0 】****[ 第 4 実施形態 ]**

図 9 (a) 及び図 9 (b) は、本実施形態による撮像システム 600 及び移動体の構成を示す図である。図 9 (a) は、車載カメラに関する撮像システム 600 の一例を示したものである。撮像システム 600 は、上述の第 1 又は第 2 実施形態のいずれかに記載の光電変換装置 1 を有する。撮像システム 600 は、光電変換装置 1 により取得された複数の画像データに対し、画像処理を行う画像処理部 612 と、撮像システム 600 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差算出部 614 を有する。また、撮像システム 600 は、算出された視差に基づいて対象物までの距離を算出する距離計測部 616 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 618 と、を有する。ここで、視差算出部 614 及び距離計測部 616 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 618 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) 、ASIC (Application Specific Integrated Circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

20

**【 0 0 9 1 】**

撮像システム 600 は、車両情報取得装置 620 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 600 には、衝突判定部 618 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 630 が接続されている。すなわち、制御 ECU 630 は、距離情報に基づいて移動体を制御する移動体制御手段の一例である。また、撮像システム 600 は、衝突判定部 618 での判定結果に基づいて、ドライバーへ警報を発する警報装置 640 とも接続されている。例えば、衝突判定部 618 の判定結果として衝突可能性が高い場合、制御 ECU 630 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 640 は、音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与える等によりユーザに警告を行う。

30

**【 0 0 9 2 】**

本実施形態では、車両の周囲、例えば前方又は後方を撮像システム 600 で撮像する。図 9 (b) に、車両前方（撮像範囲 650）を撮像する場合の撮像システム 600 の構成を示す。車両情報取得装置 620 は、撮像システム 600 を動作させ撮像を実行させるように指示を送る。

40

**【 0 0 9 3 】**

このようにして、第 1 又は第 2 実施形態による光電変換装置 1 を適用した撮像システム 600 及び移動体を構成することにより、より簡便な制御を実現し得る移動体を実現することができる。

**【 0 0 9 4 】**

50

以上の説明では、他の車両と衝突しないように制御する例を述べたが、他の車両に追従して自動運転する制御、車線からはみ出さないように自動運転する制御等にも適用可能である。更に、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機、産業用ロボット等の移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

#### 【0095】

##### 【変形実施形態】

本発明は、上述の実施形態に限られるものではなく、種々の変形が可能である。例えば、いざれかの実施形態の一部の構成を、他の実施形態に追加した実施形態、あるいは他の実施形態の一部の構成と置換した実施形態も本発明を適用し得る実施形態であると理解されるべきである。

10

#### 【0096】

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

#### 【0097】

上述の実施形態は、いざれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

20

#### 【符号の説明】

#### 【0098】

|         |        |

|---------|--------|

| 1       | 光電変換装置 |

| 1 4     | 垂直走査部  |

| M 2、S 2 | 記憶部    |

| P       | 画素     |

30

40

50

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

【図9】

(a)

10

(b)

20

30

40

50

---

フロントページの続き

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 彦田 克文

(56)参考文献 特開2004-140479(JP,A)

特開2008-035425(JP,A)

特開2017-103537(JP,A)

特開2018-032976(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/40

H04N 25/779

H04N 25/76