(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-123785

(P2007-123785A)

(43) 公開日 平成19年5月17日(2007.5.17)

(51) Int.CI.

HO1F 21/12

(2006.01)

F1

HO1F 21/12

テーマコード(参考)

5E07O

審査請求 未請求 請求項の数 15 O L (全 18 頁)

(21) 出願番号

特願2005-317646 (P2005-317646)

(22) 出願日

平成17年10月31日 (2005.10.31)

(71) 出願人 000204284

太陽誘電株式会社

東京都台東区上野6丁目16番20号

(74) 代理人 100090413

弁理士 梶原 康穂

(72) 発明者 風間 智

東京都台東区上野6丁目16番20号 太

陽誘電株式会社内

(72) 発明者 井上 真

東京都台東区上野6丁目16番20号 太

陽誘電株式会社内

(72) 発明者 桜井 武夫

東京都台東区上野6丁目16番20号 太

陽誘電株式会社内

最終頁に続く

(54) 【発明の名称】可変インダクタ及びそれを利用したアンテナ装置

## (57) 【要約】

【課題】主コイルのQ値を低下させることなく、インダクタンス値の可変幅を大きくすることができる可変インダクタを提供する。

【解決手段】可変インダクタ10は、積層体12とスイッチ26を備えている。前記積層体12は、内部にメインインダクタ14と制御インダクタ18を隣接して対向配置した構成となっている。前記積層体12の表面には、メインインダクタ14及び制御インダクタ18の端部が接続される端子電極22A～22Fが、適宜位置に形成されている。制御インダクタ18の端部と接続される端子電極22D及び22Fの間には、スイッチ26が設けられる。このように積層方向にメインインダクタ14と制御インダクタ18を対向配置することにより、結合度を向上させ、Q値を低下させることなくインダクタンス値の可変幅を大きくすることができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

積層体の内部に積層方向に沿って巻回された主コイル導体と、該主コイル導体と対向するように前記積層体の内部に配置された調整用コイル導体と、前記積層体表面に設けられており、前記各コイル導体の端部が接続される端子電極と、前記調整用コイル導体の端部が接続された一対の端子電極間に、前記積層体の外部で接続されたスイッチ素子と、を備えたことを特徴とする可変インダクタ。

**【請求項 2】**

前記調整用コイル導体が、前記積層体の内部に積層方向に沿って1ターン以上巻回されたものであることを特徴とする請求項1記載の可変インダクタ。10

**【請求項 3】**

前記主コイル導体と前記調整用コイル導体とが、前記積層体内で積層方向に隣接して配置されたことを特徴とする請求項1記載の可変インダクタ。

**【請求項 4】**

前記積層体内に、前記調整用コイル導体を複数組備えるとともに、該複数組の調整用コイル導体が、前記主コイル導体を挟むように配置されたことを特徴とする請求項1記載の可変インダクタ。

**【請求項 5】**

前記積層体内において、前記調整用コイル導体の周回軌跡と前記主コイル導体の周回軌跡の一部とが、積層方向で重なるように配置されたことを特徴とする請求項1記載の可変インダクタ。20

**【請求項 6】**

前記積層体内に、前記調整用コイル導体を複数組備えたことを特徴とする請求項5記載の可変インダクタ。

**【請求項 7】**

前記積層体内において、前記複数組の調整用コイル導体が、前記積層体の積層方向で互いに重ならないように配置されていることを特徴とする請求項6記載の可変インダクタ。

**【請求項 8】**

前記主コイル導体及び前記調整用コイル導体の少なくとも一方が、異なる複数の巻回軸を備えており、該各巻回軸の周りに分割して巻回されていることを特徴とする請求項1記載の可変インダクタ。30

**【請求項 9】**

前記複数組の調整用コイル導体にそれぞれ対応する複数のスイッチ素子を備えるとともに、該複数のスイッチ素子が、前記各調整用コイル導体の開放端部間に、それぞれ個別に接続されていることを特徴とする請求項4又は7記載の可変インダクタ。

**【請求項 10】**

前記各調整用コイル導体の開放端部が接続された一対の端子電極は、他の調整用コイル導体に接続される他の端子電極を間に挟まないように隣接配置されていることを特徴とする請求項9記載の可変インダクタ。

**【請求項 11】**

前記積層体の内部であって、前記調整用コイル導体の一方の端部と、前記端子電極との間に、コンデンサを接続したことを特徴とする請求項1記載の可変インダクタ。

**【請求項 12】**

前記主コイル導体と前記複数組の調整用コイル導体のそれぞれとの間の結合係数の比が、前記調整用コイルをn個とした場合に、およそ $1 : 2 : 2^2 : \dots : 2^n$ の比で構成されていることを特徴とする請求項6記載の可変インダクタ。

**【請求項 13】**

前記複数組の調整用コイル導体のそれぞれ一端が、前記積層体表面の共通の端子電極に接続されていることを特徴とする請求項6記載の可変インダクタ。40

50

**【請求項 1 4】**

前記主コイル導体と前記調整コイル導体とがそれぞれ前記積層体内で積層方向に分割形成されており、前記分割形成した主コイル導体と調整用コイル導体とが、前記積層体内で交互に積層されていることを特徴とする請求項 1 記載の可変インダクタ。

**【請求項 1 5】**

請求項 1 ~ 8 のいずれかに記載の可変インダクタが整合回路に用いられていることを特徴とするアンテナ装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、可変インダクタ及びそれを利用したアンテナ装置に関し、更に具体的には、インダクタンスの可変幅の改善に関するものである。

**【背景技術】****【0 0 0 2】**

電子機器に使用される個々の部品偏差を吸収したり、回路に組み込んだ後にそのインダクタンスを調整したりするものとして、インダクタンス値の変更が可能な可変インダクタがあり、各種のものが提案されている。例えば、以下の特許文献 1 には、平面スパイラル状の主コイル（第 1 導体）の各周回部に対向するように、開放端間にスイッチが接続された單一周回調整用コイル（第 2 導体）を複数配置した可変インダクタ及びそれを利用した半導体集積回路が開示されている。また、特許文献 2 には、シリコン基板上に主コイル導体（主インダクタ）と調整用コイル導体（副インダクタ）とを同軸で内外に隣接配置し、調整用コイル導体の端部をスイッチで開閉自在にした電圧制御発振回路が開示されている。

【特許文献 1】特開平 08 - 162331 号公報（第 1 図）

【特許文献 2】特開 2002 - 151953 号公報（第 4 図、第 5 図）

**【発明の開示】****【発明が解決しようとする課題】****【0 0 0 3】**

しかしながら、以上のような背景技術は、高周波（100 MHz 以上）ではスイッチの影響が小さいものの、主コイル導体と調整用コイル導体との結合度が十分ではないため、主コイルのインダクタンス値の可変幅が狭いという不都合がある。

**【0 0 0 4】**

本発明は、以上の点に着目したもので、その目的は、主コイルの Q 値を低下させることなく、インダクタンス値の可変幅を広げることができる可変インダクタを提供することである。他の目的は、前記可変インダクタを利用したアンテナ装置を提供することである。

**【課題を解決するための手段】****【0 0 0 5】**

前記目的を達成するため、本発明の可変インダクタは、積層体の内部に積層方向に沿って巻回された主コイル導体と、該主コイル導体と対向するように前記積層体の内部に配置された調整用コイル導体と、前記積層体表面に設けられており、前記各コイル導体の端部が接続される端子電極と、前記調整用コイル導体の端部が接続された一対の端子電極間に、前記積層体の外部で接続されたスイッチ素子と、を備えたことを特徴とする。

**【0 0 0 6】**

本発明のアンテナ装置は、請求項 1 ~ 8 のいずれかに記載の可変インダクタを利用したことを特徴とする。本発明の前記目的、特徴、利点は、以下の詳細な説明及び添付図面から明瞭になろう。

**【発明の効果】****【0 0 0 7】**

本発明は、積層体内部に積層方向に沿って巻回された主コイル導体に対して、調整用コ

10

20

30

40

50

イル導体を積層体内で対向配置し、各コイル導体の端部を積層体表面の端子電極に接続するとともに、前記調整用コイル導体端部に接続する一対の端子電極間に、積層体外部でスイッチ素子を接続することとした。このため、主コイル導体にスイッチ素子が直接接続されないのでQ値の劣化を抑制しつつ、主コイル導体と調整用コイル導体との結合度を高めて、主コイル導体のインダクタンスの可変幅を広げるという効果が得られる。

**【発明を実施するための最良の形態】**

**【0008】**

以下、本発明を実施するための最良の形態を、実施例に基づいて詳細に説明する。

**【実施例1】**

**【0009】**

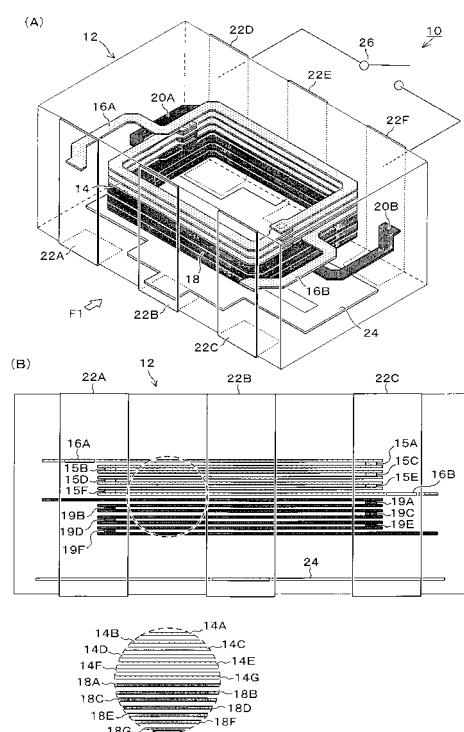

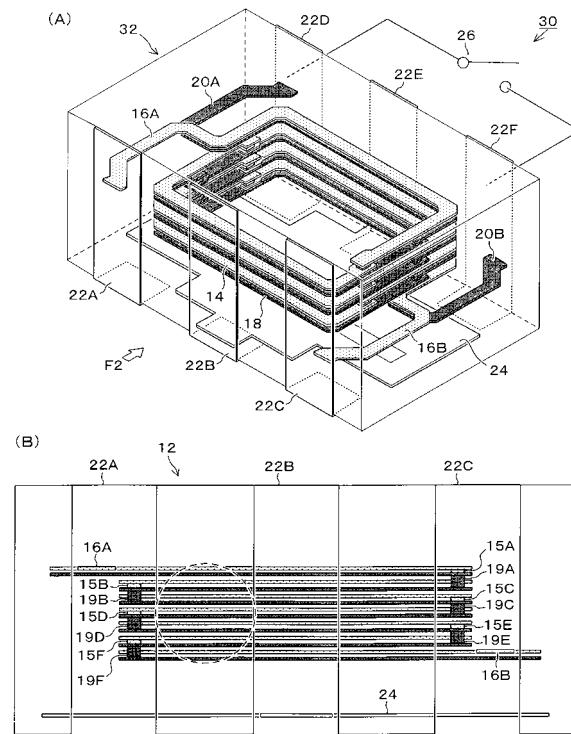

最初に、図1を参照しながら本発明の実施例1を説明する。図1(A)は、本実施例の可変インダクタのインダクタ配置(コイル配置)を示す斜視図であり、図1(B)は、前記(A)を矢印F1方向から見た側面図である。図1に示すように、本実施例の可変インダクタ10は、積層体12とスイッチ26を備えている。前記積層体12は、絶縁層を積層した積層体の内部に、メインインダクタ(主コイル導体)14と制御インダクタ(調整用コイル導体)18が隣接して対向配置された構成となっている。なお、理解を容易にするため、前記絶縁層は、図中から省略されている。また、積層体12の表面(側面)には、前記メインインダクタ14及び制御インダクタ18の端部が接続される端子電極22A～22Fが、適宜位置に形成されている。更に、積層体12の底面には、端子電極22Bと22Eを短絡するとともに配線基板への実装時の特性変化を少なくするためのシールド層24が設けられている。

**【0010】**

前記メインインダクタ14は、複数の導体パターン14A～14Gが、積層体12の積層方向に沿って巻回するように積層されており、これら導体パターン14A～14Gは、スルーホール15A～15Fによって接続されている。そして、メインインダクタ14の一方の端部16Aは、積層体12の表面の端子電極22Aに接続され、他方の端部16Bは、端子電極22Cに接続されている。同様に、制御インダクタ18も、複数の導体パターン18A～18Gが積層方向に沿って巻回するように積層されており、これら導体パターン18A～18Gは、スルーホール19A～19Fによって接続されている。そして、制御インダクタ18の一方の端部20Aは、端子電極22Dに接続され、他方の端部20Bは、端子電極22Fに接続される。更に、これら端子電極22D及び22F間には、積層体12の外部で、スイッチ26が接続されている。なお、上述した導体パターン14A～14G、18A～18Gとしては、例えばAg、Ni、Cuなどが用いられ、端子電極22A～22Fとしては、例えばAg、Ni、Cu、導電性樹脂などが用いられるが、他の公知の各種の材料を利用するようにしてもよい。可変インダクタ10を、以上のような構成にすることにより、メインインダクタ14にスイッチ等の余分な負荷を設けることなく、インダクタンス値を変更することができる。

**【0011】**

このように、実施例1によれば、次のような効果がある。

(1)積層体12の内部に、その積層方向に沿って巻回したメインインダクタ14と制御インダクタ18を、隣接して対向配置することとしたので、結合度を向上させてインダクタンス値の可変量を大きくすることができる。

(2)メインインダクタ14にスイッチ26が直接接続されず、余分な負荷を設ける必要がないため、メインインダクタ14のQ値の劣化を抑制することができる。

**【実施例2】**

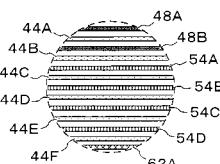

**【0012】**

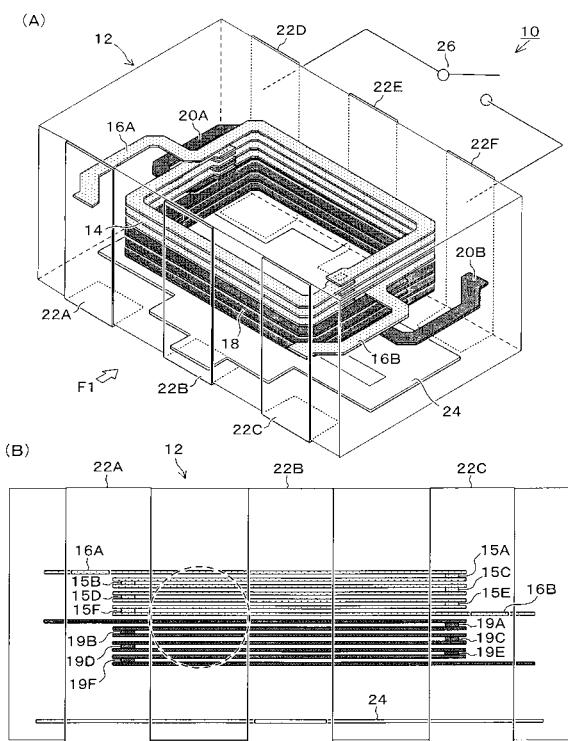

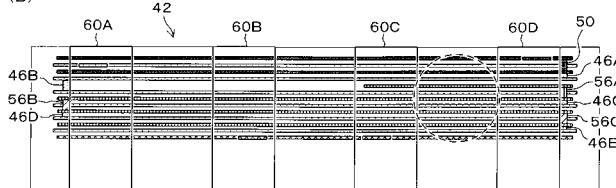

次に、図2を参照しながら本発明の実施例2を説明する。図2(A)は、本実施例の可変インダクタのインダクタ配置を示す斜視図であり、図2(B)は前記(A)を矢印F2方向から見た側面図である。なお、上述した実施例1と同一ないし対応する構成要素には同一の符号を用いることとする(以下の実施例1についても同様)。前記実施例1では、メインイ

ンダクタ 14 と制御インダクタ 18 を、単に積層方向に対向配置したが、本実施例では、図 2 に示すように、メインインダクタと制御インダクタの分割形成した導体パターンを、交互に積層した構成となっている。

### 【0013】

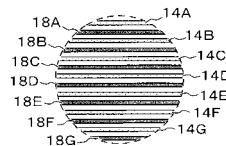

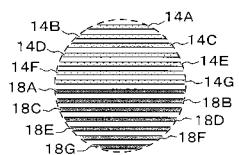

詳細に説明すると、メインインダクタ 14 は、導体パターン 14A ~ 14G が、積層体 12 の積層方向に沿って巻回するように積層されており、これら導体パターン 14A ~ 14G は、スルーホール 15A ~ 15F によって接続されている。同様に、制御インダクタ 18 は、導体パターン 18A ~ 18G が、積層方向に沿って巻回するように積層されており、これら導体パターン 18A ~ 18G は、スルーホール 19A ~ 19F によって接続されている。そして、これらメインインダクタ 14 の導体パターン 14A ~ 14G と、制御インダクタ 18 の導体パターン 18A ~ 18G は、交互に積層される。図 2 に示す例では、積層体 32 の上側から、導体パターン 14A, 18A, 14B, 18B, 14C, 18C, 14D, 18D, 14E, 18E, 14F, 18F, 14G, 18G となるように配置されている。10

### 【0014】

そして、メインインダクタ 14 の端部 16A 及び 16B は、それぞれ積層体 32 の表面の端子電極 22A 及び 22C に接続される。また、制御インダクタの端部 20A 及び 20B は、それぞれ端子電極 22D 及び 22F に接続され、これら端子電極 22D 及び 22F 間には、前記実施例 1 と同様にスイッチ 26 が接続される。本実施例の基本的作用・効果は、上述した実施例 1 と同様であるが、メインインダクタ 14 の導体パターンと、制御インダクタ 18 の導体パターンを交互に積層することとしたので、より結合度の向上を図ることができる。20

### 【実施例 3】

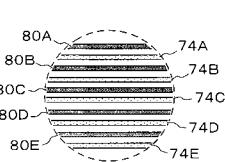

### 【0015】

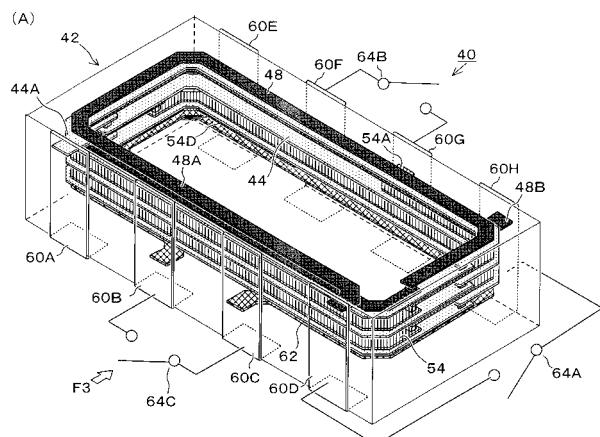

次に、図 3 を参照しながら本発明の実施例 3 を説明する。図 3 (A) は、本実施例の可変インダクタのインダクタ配置を示す斜視図であり、図 3 (B) は前記 (A) を矢印 F3 方向から見た側面図である。上述した実施例 1 及び 2 では、一つのメインインダクタに対して、一つの制御インダクタを設けた例であるが、本実施例は、一つのメインインダクタに対して 3 つの制御インダクタを設けたものである。図 3 に示すように、本実施例の可変インダクタ 40 は、積層体 42 内に、メインインダクタ 44 と制御インダクタ 48, 54 および 62 が対向配置されている。また、積層体 42 の表面には、前記メインインダクタ 44 及び制御インダクタ 48, 54, 62 の端部が接続される端子電極 60A ~ 60H が適宜位置に形成されている。30

### 【0016】

前記メインインダクタ 44 は、複数の導体パターン 44A ~ 44F が、積層体 42 の積層方向に沿って巻回するように積層されており、これら導体パターン 44A ~ 44F は、スルーホール 46A ~ 46E により接続されている。そして、メインインダクタ 44 の一方の端部（導体パターン 44A 側）は、端子電極 60A に接続され、他方の端部（導体パターン 44F 側）は、端子電極 60E に接続されている。一方、制御インダクタ 48 は、導体パターン 48A 及び 48B が、積層方向に沿って巻回するように積層されて、スルーホール 50 により接続されている。前記導体パターン 48A, 48B は、前記メインインダクタ 44 の導体パターン 44A を挟むように配置されている。そして、一方の端部（導体パターン 48A 側）が端子電極 60D に接続され、他方の端部（導体パターン 48B 側）は端子電極 60H に接続されている。更に、これら端子電極 60D 及び 60F 間には、積層体 42 の外部で、スイッチ 64A が接続されている。40

### 【0017】

また、制御インダクタ 54 は、導体パターン 54A ~ 54D が、積層方向に沿って巻回するように積層されており、スルーホール 56A ~ 56C により接続されている。前記導体パターン 54A ~ 54D は、前記メインインダクタ 44 の導体パターン 44B ~ 44F と交互になるように積層されている。そして、一方の端部（導体パターン 54A 側）が端

子電極 60G に接続され、他方の端部（導体パターン 54D 側）が端子電極 60F に接続されている。

更に、これら端子電極 60F 及び 60G 間には、積層体 42 の外部で、スイッチ 64B が接続されている。更に、制御インダクタ 62 は、略 C 字形の 1 ターンに満たない単一層の導体パターン 62A により構成されており、該導体パターン 62A は、前記メインインダクタ 44 の導体パターン 44F に対向するように、その下側に配置されている。そして、一方の端部が端子電極 60B に接続され、他方の端部は、端子電極 60C に接続されている。そして、これらの端子電極 60B 及び 60C 間には、積層体 42 の外部で、スイッチ 64C が接続されている。

なお、上述した導体パターン 44A ~ 44F, 48A, 48B, 54A ~ 54D, 62A や、端子電極 60A ~ 60H としては、上述した実施例 1 と同様の材料が用いられる。10

本実施例の作用・効果は、基本的には上述した実施例 2 と同様であるが、3 つの制御インダクタ 48, 54, 62 をメインインダクタ 44 の上部、中間部及び下部に重なるように配置することとしたので、メインインダクタ 44 に対して異なる結合係数を得ることが可能となり、メインインダクタ 44 のインダクタンス値を所望の値に変化させることができることが可能となる。また、制御インダクタ 48, 54 及び 62 のそれぞれの間に、20

メインインダクタ 44 の導体パターン 44B 及び 44F が配置されるので、それぞれの制御用インダクタ間の相互作用が抑制され、メインインダクタ 44 に対してそれぞれ独立して機能することができるという効果もある。

#### 【実施例 4】

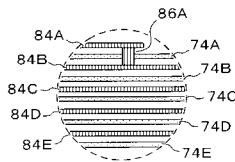

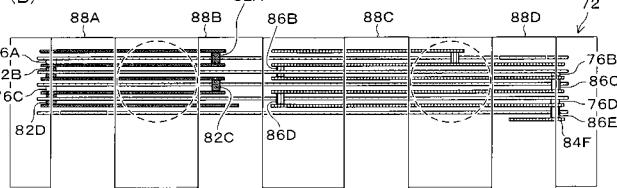

#### 【0018】

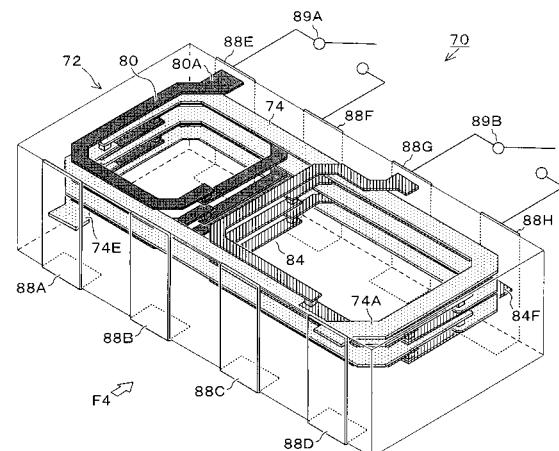

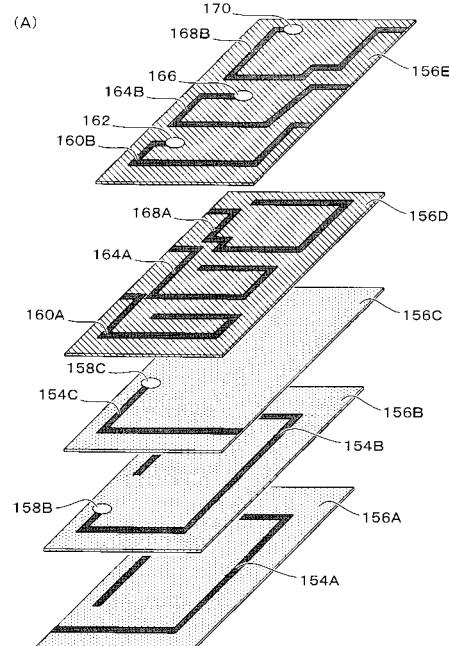

次に、図 4 を参照しながら本発明の実施例 4 を説明する。図 4 (A) は、本実施例の可変インダクタのインダクタ配置を示す斜視図であり、図 4 (B) は前記 (A) を矢印 F4 方向から見た側面図である。上述した実施例 3 では、一つのメインインダクタに、上部、中間部、下部で重なるように 3 つの制御インダクタを設けたが、本実施例は、一つのメインインダクタの左右に重なるように 2 つの制御インダクタを配置した構成となっている。図 4 に示すように、本実施例の可変インダクタ 70 は、積層体 72 内に、メインインダクタ 74 と、該メインインダクタ 74 の一部と重なる 2 つの制御インダクタ 80 及び 84 が配置されている。また、積層体 72 の表面には、前記メインインダクタ 74 及び制御インダクタ 80 及び 84 の端部が接続される端子電極 88A ~ 88H が適宜位置に形成されている。30

#### 【0019】

前記メインインダクタ 74 は、複数の導体パターン 74A ~ 74E が、積層体 72 の積層方向に沿って巻回するように積層されており、これら導体パターン 74A ~ 74E は、スルーホール 76A ~ 76D により接続されている。そして、メインインダクタ 74 の一方の端部（導体パターン 74A 側）は、端子電極 88D に接続され、他方の端部（導体パターン 74E 側）は、端子電極 88A に接続されている。一方、制御インダクタ 80 は、導体パターン 80A ~ 80E が、積層方向に沿って巻回するように積層されて、スルーホール 82A ~ 82D により接続されている。これら導体パターン 82A ~ 82E は、メインインダクタ 74 の一部（図示の例では左側）の導体パターン 74A ~ 74E と交互に重なり合うように積層配置されている。そして、一方の端部（導体パターン 80A 側）が端子電極 88E に接続され、他方の端部（導体パターン 80E 側）は端子電極 88F に接続されている。更に、これら端子電極 88E 及び 88F 間には、積層体 72 の外部で、スイッチ 89A が接続されている。40

#### 【0020】

また、制御インダクタ 84 は、導体パターン 84A ~ 84F が、積層方向に沿って巻回するように積層されており、スルーホール 86A ~ 86E により接続されている。前記導体パターン 84A ~ 84F は、前記メインインダクタ 74 の一部（図示の例では右側）の導体パターン 74A ~ 74E と交互に重なり合うように積層配置されている。そして、一方の端部（導体パターン 84A 側）が端子電極 88G に接続され、他方の端部（導体パターン 84F 側）が端子電極 88H に接続されている。更に、これら端子電極 88G 及び 88H 間には、積層体 72 の外部で、スイッチ 89B が接続されている。50

8 H 間には、積層体 7 2 の外部で、スイッチ 8 9 B が接続されている。本実施例の作用・効果は、上述した実施例 2 と同様であるが、2 つの制御インダクタ 8 0 及び 8 4 を、これらが積層方向で互いに重ならないようにメインインダクタ 7 4 に対向配置することとしたので、制御インダクタ間の相互作用をより確実に抑制することができるとともに、インダクタの結合の大きさがその対向面積で決まるため、メインインダクタ 7 4 のインダクタンス値の変化量の設計が容易になるという効果もある。また、スイッチ 8 9 A 及び 8 9 B が接続される端子電極が隣接しているため、外部に接続するスイッチへの回路設計が容易になるという効果もある。

#### 【実施例 5】

##### 【0 0 2 1】

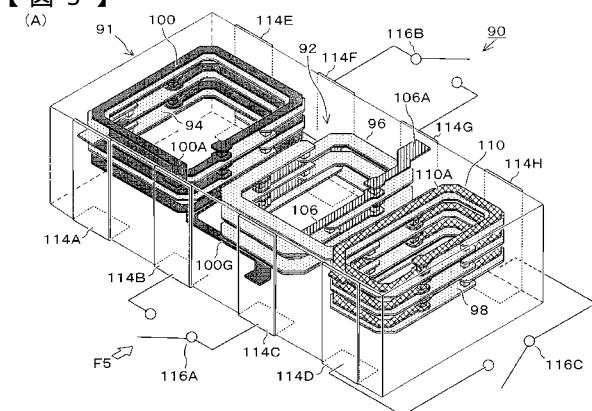

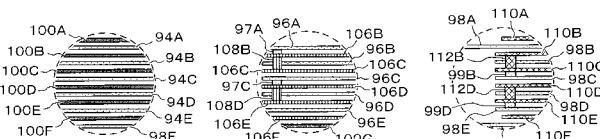

次に、図 5 を参照しながら本発明の実施例 5 を説明する。図 5 (A) は、本実施例の可変インダクタのインダクタ配置を示す斜視図であり、図 5 (B) は前記(A)を矢印 F 5 方向から見た側面図である。上述した実施例 4 は、2 つの制御インダクタを用いたものの、メインインダクタの巻回軸は一つであるが、本実施例は、メインインダクタが複数の巻回軸を備えた構成となっている。図 5 に示すように、本実施例の可変インダクタ 9 0 は、積層体 9 1 内に、3 つのインダクタ部 9 4 , 9 6 , 9 8 を備えたメインインダクタ 9 2 と、前記各インダクタ部 9 4 , 9 6 , 9 8 と導体パターンが交互に重なる 3 つの制御インダクタ 1 0 0 , 1 0 6 , 1 1 0 が配置されている。また、積層体 9 1 の表面には、前記メインインダクタ 9 2 及び制御インダクタ 1 0 0 , 1 0 6 , 1 1 0 の端部が接続される端子電極 1 1 4 A ~ 1 1 4 H が適宜位置に形成されている。

##### 【0 0 2 2】

前記メインインダクタ 9 2 は、3 つのインダクタ部 9 4 , 9 6 , 9 8 によって構成されている。インダクタ部 9 4 は、複数の導体パターン 9 4 A ~ 9 4 E が、積層体 9 1 の積層方向に沿って巻回するように積層されており、これら導体パターン 9 4 A ~ 9 4 E は、スルーホール 9 5 A ~ 9 5 D により接続されている。同様に、インダクタ部 9 6 は、複数の導体パターン 9 6 A ~ 9 6 E がスルーホール 9 7 A ~ 9 7 D により接続され、インダクタ部 9 8 は、複数の導体パターン 9 8 A ~ 9 8 F がスルーホール 9 9 A ~ 9 9 E により接続されている。なお、前記インダクタ部 9 4 と 9 6 は、同一面上にある導体パターン 9 4 E 及び 9 6 E により連続しており、インダクタ部 9 6 と 9 8 は、同一面上にある導体パターン 9 6 A と 9 8 A により連続している。このようなメインインダクタ 9 2 の一方の端部(導体パターン 9 4 A 側)は、端子電極 1 1 4 A に接続され、他方の端部である導体パターン 9 8 F は、インダクタ部 9 4 側まで延長されており、端子電極 1 1 4 E に接続されている。

##### 【0 0 2 3】

次に、制御インダクタ 1 0 0 は、導体パターン 1 0 0 A ~ 1 0 0 F が、積層方向に沿って巻回するように積層されて、スルーホール 1 0 2 A ~ 1 0 2 E により接続されている。また、導体パターン 1 0 0 F には、スルーホール 1 0 2 F を介して導体パターン 1 0 0 G が接続されており、インダクタ部 9 6 の下方まで延長されている。前記導体パターン 1 0 2 A ~ 1 0 2 E は、メインインダクタ 9 2 の一つ(図示の例では左側)のインダクタ部 9 4 の導体パターン 9 4 A ~ 9 4 E と交互に重なり合うように積層配置されている。そして、一方の端部(導体パターン 1 0 0 A 側)が端子電極 1 1 4 B に接続され、他方の端部(導体パターン 1 0 0 G 側)は端子電極 1 1 4 C に接続されている。更に、これら端子電極 1 1 4 B 及び 1 1 4 C 間には、積層体 9 1 の外部で、スイッチ 1 1 6 A が接続されている。

##### 【0 0 2 4】

また、制御インダクタ 1 0 6 は、導体パターン 1 0 6 A ~ 1 0 6 F が、積層方向に沿って巻回するように積層されて、スルーホール 1 0 8 A ~ 1 0 8 E により接続されている。これら導体パターン 1 0 6 A ~ 1 0 6 F は、メインインダクタ 9 2 の一つ(図示の例では中央)のインダクタ部 9 6 の導体パターン 9 6 A ~ 9 6 E と交互に重なり合うように積層配置されている。そして、一方の端部(導体パターン 1 0 6 A 側)が端子電極 1 1 4 G に

10

20

30

40

50

接続され、他方の端部（導体パターン 106 F 側）は端子電極 114 F に接続されている。更に、これら端子電極 114 F 及び 114 G 間には、積層体 91 の外部で、スイッチ 116 B が接続されている。

#### 【0025】

更に、制御インダクタ 110 は、導体パターン 110 A ~ 110 F が、積層方向に沿って巻回するように積層されて、スルーホール 112 A ~ 112 E により接続されている。これら導体パターン 110 A ~ 110 F は、メインインダクタ 92 の一つ（図示の例では右側）のインダクタ部 98 の導体パターン 98 A ~ 98 F と交互に重なり合うように積層配置されている。そして、一方の端部（導体パターン 110 A 側）が端子電極 114 D に接続され、他方の端部（導体パターン 110 F 側）は端子電極 114 H に接続されている。10

更に、これら端子電極 114 D 及び 114 H 間には、積層体 91 の外部で、スイッチ 116 C が接続されている。本実施例の作用・効果は、基本的には上述した実施例 2 と同様であるが、複数の巻回軸に沿ってメインインダクタ及び制御インダクタを巻回することとしたので、それぞれの制御インダクタ 100, 106, 110 とメインインダクタ 92 との結合度を容易に設計することができるという効果が得られる。

#### 【実施例 6】

#### 【0026】

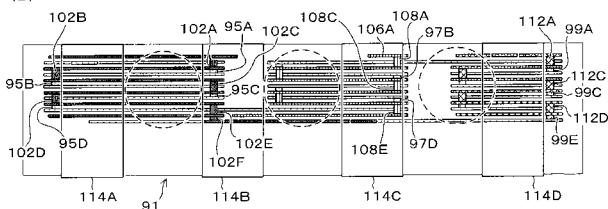

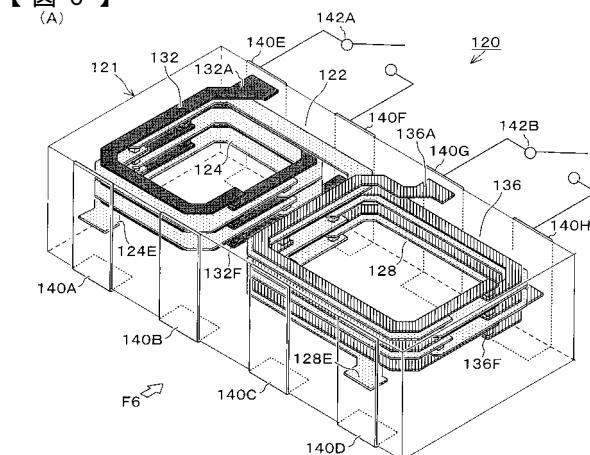

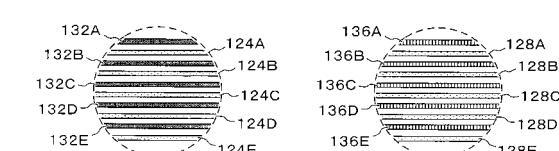

次に、図 6 を参照しながら本発明の実施例 6 を説明する。図 6 (A) は、本実施例の可変インダクタのインダクタ配置を示す斜視図であり、図 6 (B) は前記 (A) を矢印 F 6 方向から見た側面図である。上述した実施例 5 は、3 つの巻回軸に沿ってメインインダクタと制御インダクタを巻回した例であるが、本実施例は、2 つの巻回軸に沿ってメインインダクタ及び制御インダクタを配置した例である。図 6 に示すように、本実施例の可変インダクタ 120 は、積層体 121 内に、2 つのインダクタ部 124 及び 128 を備えたメインインダクタ 122 と、前記各インダクタ部 124 及び 128 と導体パターンが交互に重なる 2 つの制御インダクタ 132, 136 が配置されている。また、積層体 121 の表面には、前記メインインダクタ 122 及び制御インダクタ 132, 136 の端部が接続される端子電極 140 A ~ 140 H が適宜位置に形成されている。20

#### 【0027】

前記メインインダクタ 122 は、2 つのインダクタ部 124, 128 によって構成されている。インダクタ部 124 は、複数の導体パターン 124 A ~ 124 E が、積層体 121 の積層方向に沿って巻回するように積層されており、これら導体パターン 124 A ~ 124 E は、スルーホール 126 A ~ 126 D により接続されている。同様に、インダクタ部 128 は、複数の導体パターン 128 A ~ 128 E がスルーホール 130 A ~ 130 D により接続されている。なお、前記インダクタ部 124 と 128 は、同一面上にある導体パターン 124 A 及び 128 A により連続している。このようなメインインダクタ 122 の一方の端部（導体パターン 124 E 側）は、端子電極 140 A に接続され、他方の端部（導体パターン 128 E 側）は、端子電極 140 D に接続されている。30

#### 【0028】

次に、制御インダクタ 132 は、導体パターン 132 A ~ 132 F が、積層方向に沿って巻回するように積層されて、スルーホール 134 A ~ 134 E により接続されている。前記導体パターン 132 A ~ 132 F は、メインインダクタ 122 の一つ（図示の例では左側）のインダクタ部 124 の導体パターン 124 A ~ 124 E と交互に重なり合うように積層配置されている。そして、一方の端部（導体パターン 132 A 側）が端子電極 140 E に接続され、他方の端部（導体パターン 132 F 側）は端子電極 140 F に接続されている。更に、これら端子電極 140 E 及び 140 F の間には、積層体 121 の外部で、スイッチ 142 A が接続されている。40

#### 【0029】

また、制御インダクタ 136 は、導体パターン 136 A ~ 136 F が、積層方向に沿って巻回するように積層されて、スルーホール 138 A ~ 138 E により接続されている。これら導体パターン 136 A ~ 136 F は、メインインダクタ 122 の一つ（図示の例で50

は右側)のインダクタ部128の導体パターン128A~128Eと交互に重なり合うように積層配置されている。そして、一方の端部(導体パターン136A側)が端子電極140Gに接続され、他方の端部(導体パターン136F側)は端子電極140Hに接続されている。更に、これら端子電極140G及び140H間には、積層体121の外部で、スイッチ142Bが接続されている。本実施例の作用・効果は、基本的には上述した実施例5と同様である。

#### 【実施例7】

##### 【0030】

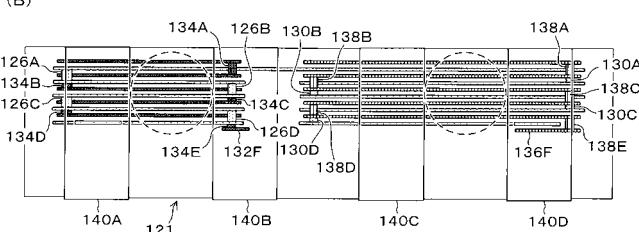

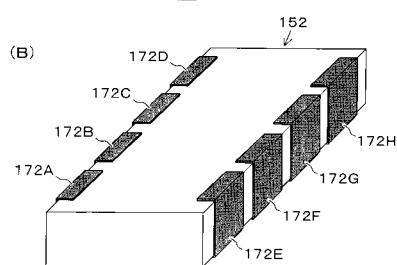

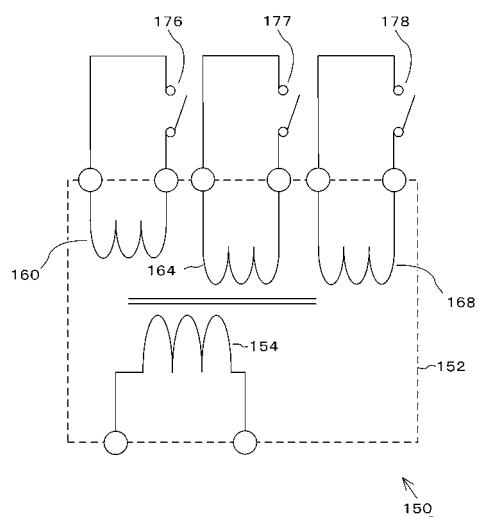

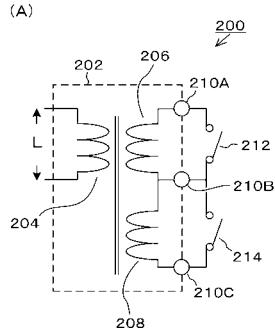

次に、図7及び図8を参照しながら、本発明の実施例7を説明する。図7(A)は、本実施例の可変インダクタの積層体の分解斜視図、図7(B)は前記積層体の外観斜視図である。図8は、本実施例の可変インダクタの回路構成を示す図である。図8に示すように、本実施例の可変インダクタ150は、積層体152内で、一つのメインインダクタ154の上に、3つの制御インダクタ160, 164, 168が対向配置されており、各制御インダクタに、スイッチ176, 177, 178が接続された構成となっている。前記制御インダクタ160, 164, 168は、互いに重なることがないように配置されている。

##### 【0031】

前記積層体152は、図7(A)に示すように、絶縁層156A~156Eを積層したものである。絶縁層156A~156Cの表面には、導体パターン154A~154Cが形成されており、絶縁層156Bに設けられたスルーホール158Bと、絶縁層156Cに設けられたスルーホール158Cを介して、前記導体パターン154A~154Cが接続され、メインインダクタ154を構成している。また、絶縁層156Dには、導体パターン160A, 164A, 168Aが形成されており、絶縁層156Eには、導体パターン160B, 164B, 168Bとともにスルーホール162, 166, 170が形成されている。

##### 【0032】

そして、前記導体パターン160Aと160Bがスルーホール162で接続されて制御インダクタ160を構成する。同様に、導体パターン164Aと164Bがスルーホール166で接続されて制御インダクタ164を構成し、導体パターン168Aと168Bがスルーホール170で接続されて制御インダクタ168を構成している。また、前記絶縁層156Aの下面や、絶縁層156Eの上面には、図示しない他の絶縁層が積層される。なお、絶縁層156A~156Eとしては、例えば、Ni-Zn-Cu系フェライト、アルミナセラミックス、MgO-CaO-SiO<sub>2</sub>系誘電体セラミックスなどが用いられる。

##### 【0033】

以上のようにして構成された積層体152の表面には、端子電極172A~172Hが設けられ、メインインダクタ154の両端は、端子電極172A及び172Eに接続される。制御インダクタ160の両端は、端子電極174B及び172Fに接続され、制御インダクタ164の両端は、端子電極172C及び172Gに接続され、制御インダクタ168の両端は、端子電極172D及び172Hに接続される。前記端子電極172B及び172F間には、図8に示すスイッチ176が接続され、端子電極172C及び172G間には、スイッチ177が接続され、端子電極172D及び172H間には、スイッチ178が接続される。

##### 【0034】

このような構成の可変インダクタ150では、3つのスイッチ176, 177, 178のON/OFFの組み合わせにより、8段階の切り替えが可能となっている。また、図示の例では、3つの制御インダクタを設けているが、結合の異なる複数の制御インダクタを設け、それを切り替えることにより、複数の値の可変インダクタとすることができる。n個の制御インダクタを利用すると仮定した場合、メインインダクタと複数の制御インダクタのそれぞれとの間の結合係数の比を、およそ2の階乗(1:2:4:8...2<sup>n</sup>)となるようにすると、nビットの可変インダクタを実現することができる。他の作用・効果

は、上述した実施例 1 と同様である。

**【実施例 8】**

**【0035】**

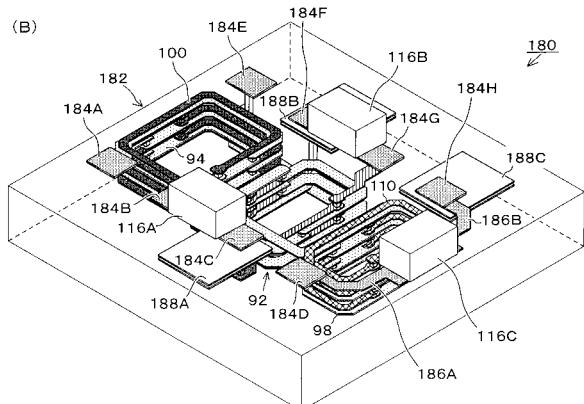

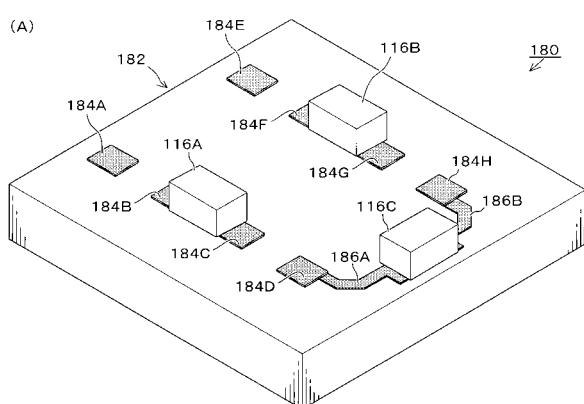

次に、図 9 を参照しながら、本発明の実施例 8 について説明する。図 9 (A) は本実施例の外観斜視図、図 9 (B) はインダクタ配置を示す斜視図である。本実施例の可変インダクタ 180 の積層体 182 の内側のインダクタ配置は、上述した実施例 5 と同様となっている。すなわち、3 つの巻回軸に沿ってそれぞれ巻回したインダクタ部 94, 96, 98 からなるメインインダクタ 92 と、これらインダクタ部 94, 96, 98 と導体パターンが交互になるように積層された制御インダクタ 100, 106, 110 を備えている。本実施例では、積層体 182 の側面ではなく、上面に 8 つの端子電極 184A ~ 184H が設けられている。そして、端子電極 184B と 184C の間にスイッチ 116A が接続され、端子電極 184F と 184G の間にスイッチ 116B が接続されている。また、スイッチ 116C は、前記端子電極 184D 及び 184H に接続された引出部 186A 及び 186B の間に接続されている。10

**【0036】**

このほか、前記端子電極 184C と導体パターン 100G の端部との間には、コンデンサ 188A が設けられている。同様に、端子電極 184F と導体パターン 106F の端部の間にはコンデンサ 188B が設けられ、端子電極 184H と導体パターン 110F の間にはコンデンサ 188C が設けられている。すなわち、本実施例では、コンデンサ 188A ~ 188C が、積層体 182 の内側に内蔵された構成となっている。従って、本実施例の可変インダクタ 180 の外観を見ると、図 9 (A) に示すように、積層体 182 の表面には、端子電極 184A ~ 184H, 引出部 186A 及び 186B, スイッチ 116A ~ 116C のみが見えるようになっている。本実施例の基本的効果は、上述した実施例 5 と同様であるが、コンデンサを内蔵させることができるために、周辺回路を小型化するとともに、スイッチング回路の部品点数を削減できるという効果も得られる。20

**【実施例 9】**

**【0037】**

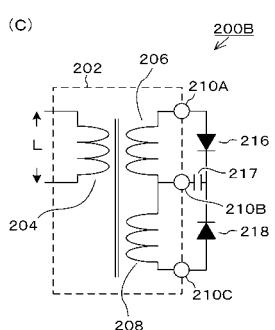

次に、図 10 を参照しながら、本発明の実施例 9 について説明する。図 10 は、本実施例の回路構成を示す図である。まず、図 10 (A) に示す可変インダクタ 200 は、積層体 202 の内側に、メインインダクタ 204 と、それに対向する 2 つの制御インダクタ 206 及び 208 が設けられた構成となっている。そして、制御インダクタ 206 は、端部が端子電極 210A 及び 210B に接続され、他方の制御インダクタ 208 は、端部が端子電極 210B 及び 210C に接続されている。すなわち、制御インダクタ 206 及び 208 は、それぞれ一方の端部が、共通の端子電極 210B に接続された構成となっている。そして、端子電極 210A 及び 210B 間にはスイッチ 212 が接続され、端子電極 210B 及び 210C 間には、スイッチ 214 が接続されている。30

**【0038】**

次に、図 10 (B) に示す可変インダクタ 200A は、制御インダクタ 206 及び 208 と端子電極との接続は、前記図 10 (A) に示した例と同様であるが、スイッチの接続構成が異なっており、スイッチ 214 は、端子電極 210A と 210C 間に接続されている。更に、図 10 (C) に示す可変インダクタ 200B は、前記図 10 (A) に示す例と同様の接続形態であるが、スイッチ 212 及び 214 の代わりに、PIN ダイオード 216 が端子電極 210A 及び 210B 間に、また、PIN ダイオード 218 が端子電極 210B 及び 210C 間に、カップリングコンデンサ 217 を介してそれぞれ接続されている。40

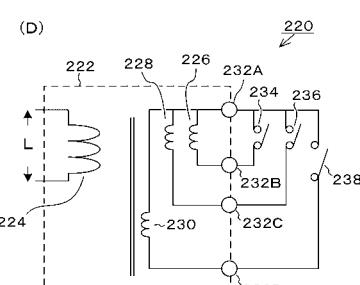

**【0039】**

また、図 10 (D) に示す可変インダクタ 220 は、積層体 222 の内側に、メインインダクタ 224 と、それに対向する 3 つの制御インダクタ 226, 228, 230 が設けられた構成となっている。これら制御インダクタ 226 ~ 230 は、積層体 222 の積層方向（図示の例では左右方向）に重ねて配置されている。そして、制御インダクタ 226 は、端部が端子電極 232A 及び 232B に接続され、制御インダクタ 228 は、端部が端子電極 232C 及び 232D に接続される。50

子電極 232A 及び 232C に接続され、制御インダクタ 230 は、端部が端子電極 232A 及び 232D に接続されている。すなわち、制御インダクタ 226～230 は、それ一方の端部が、共通の端子電極 232A に接続された構成となっている。そして、端子電極 232A 及び 232B 間には、スイッチ 234 が接続され、端子電極 232A 及び 232C 間には、スイッチ 236 が接続され、端子電極 232A 及び 232D 間には、スイッチ 238 が接続されている。このように、共通の端子電極を用いることにより、上述した実施例の効果に加えて、端子数を大幅に削減できるので、可変インダクタ 220 を小型化できるという効果が得られる。

#### 【実施例 10】

#### 【0040】

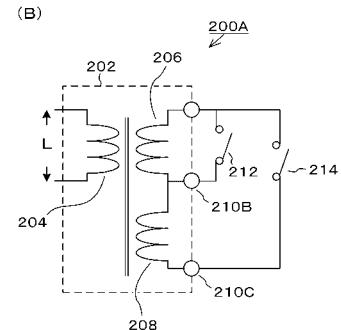

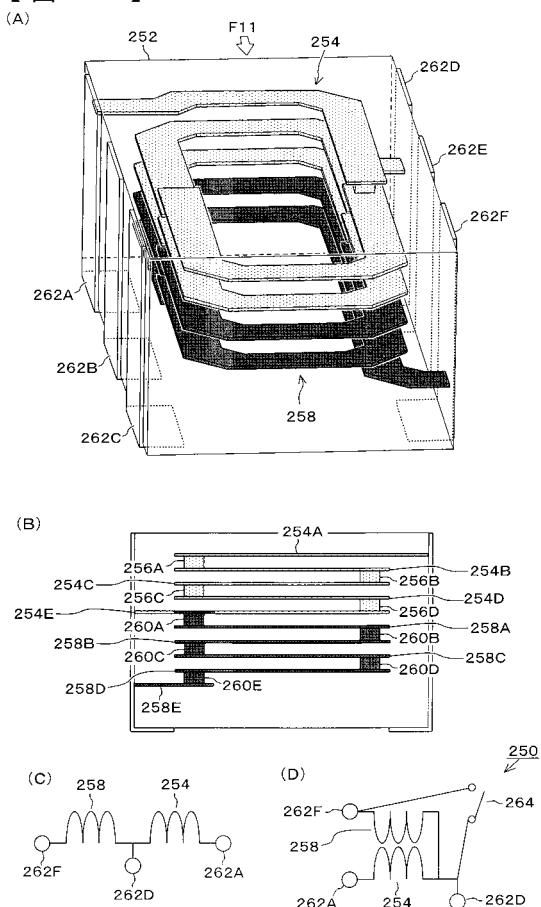

次に、図 11 を参照しながら本発明の実施例 11 を説明する。図 11(A)はインダクタ配置を示す斜視図、図 11(B)は前記(A)を矢印 F11 方向から見た側面図、図 11(C)は等価回路、図 11(D)はスイッチを含む回路である。上述した実施例 9 は、複数の制御インダクタのそれぞれ一つの端部が、共通の端子電極を利用した例であるが、本実施例は、メインインダクタと制御インダクタが、共通の端子電極に接続される例である。図 11 に示すように、可変インダクタ 250 は、積層体 252 とスイッチ 264 を備えている。前記積層体 252 内には、メインインダクタ 254 と制御インダクタ 258 が隣接して対向配置された構成となっている。また、積層体 252 の表面には、前記メインインダクタ 254 及び 258 の端部が接続される端子電極 262A～262F が適宜位置に形成されている。

#### 【0041】

前記メインインダクタ 254 は、複数の導体パターン 254A～254E が、積層体 252 の積層方向に沿って巻回するように積層されており、これら導体パターン 254A～254E は、スルーホール 256A～256D によって接続されている。そして、一方の端部（導体パターン 254A 側）は、積層体 252 の表面の端子電極 262A に接続され、他方の端部（導体パターン 254E 側）は、端子電極 262D に接続されている。同様に、制御インダクタ 258 も、複数の導体パターン 258A～258E が積層方向に沿って巻回するように積層されており、これら導体パターン 258A～258E は、スルーホール 260B～260E によって接続されている。また、前記導体パターン 258A は、スルーホール 260A によって、前記メインインダクタ 254 の導体パターン 254E に接続されている。そして、制御インダクタ 258 の一方の端部（導体パターン 258E 側）は端子電極 262F に接続され、他方の端部はメインインダクタ 254 の導体パターン 254E を介して端子電極 262D に接続される。更に、これら端子電極 262D 及び 262F の間には、積層体 252 の外部で、スイッチ 264 が接続されている。本実施例のように、メインインダクタと制御インダクタの端部を共通の端子電極に接続するようにしても、上述した実施例 1 と同様の効果が得られる。

#### 【0042】

なお、本発明は、上述した実施例に限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることができる。例えば、以下のものも含まれる。

- (1)前記実施例に示した材料、寸法は一例であり、必要に応じて適宜変更してよい。

- (2)前記実施例に示した導体パターン、端子電極の形状は一例であり、同様の効果を奏すように適宜変更可能である。

- (3)メインインダクタに対向配置する制御インダクタの数や、巻回軸の数も一例であり、必要に応じて適宜増減してよい。また、メインインダクタに対向するようであれば、制御インダクタの配置も適宜変更可能である。

- (4)メインインダクタや制御インダクタのターン数も一例であり、必要に応じて適宜変更してよい。例えば、制御インダクタは、3/4 ターン程度であっても、上述した実施例と同様の効果が得られる。

- (5)本発明の可変インダクタは、例えば、アンテナ装置などが好適な利用例であるが、他の公知の各種の電子機器に適用可能である。

## 【産業上の利用可能性】

## 【0043】

本発明によれば、積層体内部に積層方向に沿って巻回された主コイル導体に対して、調整用コイル導体を積層体内で対向配置し、各コイル導体の端部を積層体表面の端子電極に接続するとともに、前記調整用コイル導体端部に接続する一対の端子電極間に、積層体外部でスイッチ素子を接続することとした。このため、可変インダクタの用途に適用できる。特に、アンテナ装置などに用いられる可変インダクタの用途に好適である。

## 【図面の簡単な説明】

## 【0044】

【図1】本発明の実施例1を示す図であり、(A)はコイルの配置を示す斜視図、(B)は前記(A)を矢印F1方向から見た側面図である。10

【図2】本発明の実施例2を示す図であり、(A)はコイルの配置を示す斜視図、(B)は前記(A)を矢印F2方向から見た側面図である。

【図3】本発明の実施例3を示す図であり、(A)はコイルの配置を示す斜視図、(B)は前記(A)を矢印F3方向から見た側面図である。

【図4】本発明の実施例4を示す図であり、(A)はコイルの配置を示す斜視図、(B)は前記(A)を矢印F4方向から見た側面図である。

【図5】本発明の実施例5を示す図であり、(A)はコイルの配置を示す斜視図、(B)は前記(A)を矢印F5方向から見た側面図である。

【図6】本発明の実施例6を示す図であり、(A)はコイルの配置を示す斜視図、(B)は前記(A)を矢印F6方向から見た側面図である。20

【図7】本発明の実施例7を示す図であり、(A)は分解斜視図、(B)は外観斜視図である。

【図8】前記実施例7の回路構成を示す図である。

【図9】本発明の実施例8を示す図であり、(A)は外観斜視図、(B)はインダクタの配置を示す斜視図である。

【図10】本発明の実施例9の回路構成を示す図である。

【図11】本発明の実施例10を示す図であり、(A)はインダクタの配置を示す斜視図、(B)は前記(A)を矢印F11方向からみた側面図、(C)及び(D)は回路図である。

## 【符号の説明】

## 【0045】

30

10 : 可変インダクタ

12 : 積層体

14 : メインインダクタ(主コイル)

14A ~ 14G, 18A ~ 18G : 導体パターン

15A ~ 15F, 19A ~ 19F : スルーホール

16A, 16B, 20A, 20B : 端部

18 : 制御インダクタ(調整用コイル)

22A ~ 22F : 端子電極

24 : シールド層

26 : スイッチ

40

30 : 可変インダクタ

32 : 積層体

40 : 可変インダクタ

42 : 積層体

44 : メインインダクタ

44A ~ 44F, 48A, 48B, 54A ~ 54D, 62A : 導体パターン

46A ~ 46E, 50, 56A ~ 56C : スルーホール

48, 54, 62 : 制御インダクタ

60A ~ 60H : 端子電極

64A, 64B, 64C : スイッチ

50

7 0 : 可変インダクタ

7 2 : 積層体

7 4 : メインインダクタ

7 4 A ~ 7 4 E , 8 0 A ~ 8 0 E , 8 4 A ~ 8 4 F : 導体パターン

7 6 A ~ 7 6 D , 8 2 A ~ 8 2 D , 8 6 A ~ 8 6 E : スルーホール

8 0 , 8 4 : 制御インダクタ

8 8 A ~ 8 8 H : 端子電極

8 9 A , 8 9 B : スイッチ

9 0 : 可変インダクタ

9 1 : 積層体 10

9 2 : メインインダクタ

9 4 , 9 6 , 9 8 : インダクタ部

9 4 A ~ 9 4 E , 9 6 A ~ 9 6 E , 9 8 A ~ 9 8 F , 1 0 0 A ~ 1 0 0 F , 1 0 6 A ~

1 0 6 F , 1 1 0 A ~ 1 1 0 F : 導体パターン

9 5 A ~ 9 5 D , 9 7 A ~ 9 7 D , 9 9 A ~ 9 9 E , 1 0 2 A ~ 1 0 2 F , 1 0 8 A ~

1 0 8 E , 1 1 2 A ~ 1 1 2 E : スルーホール

1 0 0 , 1 0 6 , 1 1 0 : 制御インダクタ

1 1 4 A ~ 1 1 4 H : 端子電極

1 1 6 A ~ 1 1 6 C : スイッチ

1 2 0 : 可変インダクタ 20

1 2 1 : 積層体

1 2 2 : メインインダクタ

1 2 4 , 1 2 8 : インダクタ部

1 2 4 A ~ 1 2 4 E , 1 2 8 A ~ 1 2 8 E , 1 3 2 A ~ 1 3 2 E , 1 3 6 A ~ 1 3 6 E :

導体パターン

1 2 6 A ~ 1 2 6 D , 1 3 0 A ~ 1 3 0 D , 1 3 4 A ~ 1 3 4 E , 1 3 8 A ~ 1 3 8 E :

スルーホール

1 3 2 , 1 3 6 : 制御インダクタ

1 4 0 A ~ 1 4 0 H : 端子電極

1 4 2 A , 1 4 2 B : スイッチ 30

1 5 0 : 可変インダクタ

1 5 2 : 積層体

1 5 4 : メインインダクタ

1 5 4 A ~ 1 5 4 C , 1 6 0 A , 1 6 0 B , 1 6 4 A , 1 6 4 B , 1 6 8 A , 1 6 8 B :

導体パターン

1 5 6 A ~ 1 5 6 E : 絶縁層

1 5 8 B , 1 6 2 , 1 6 6 , 1 7 0 : スルーホール

1 6 0 , 1 6 4 , 1 6 8 : 制御インダクタ

1 7 2 A ~ 1 7 2 H : 端子電極

1 7 6 , 1 7 7 , 1 7 8 : スイッチ 40

1 8 0 : 可変インダクタ

1 8 2 : 積層体

1 8 4 A ~ 1 8 4 H : 端子電極

1 8 6 A , 1 8 6 B : 引出部

1 8 8 A ~ 1 8 8 C : コンデンサ

2 0 0 , 2 0 0 A , 2 0 0 B : 可変インダクタ

2 0 2 : 積層体

2 0 4 : メインインダクタ

2 0 6 , 2 0 8 : 制御インダクタ

2 1 0 A ~ 2 1 0 C : 端子電極 50

212, 214 : スイッチ

216, 218 : PINダイオード

217 : カップリングコンデンサ

220 : 可変インダクタ

222 : 積層体

224 : メインインダクタ

226, 228, 230 : 制御インダクタ

232A ~ 232D : 端子電極

234, 236, 238 : スイッチ

250 : 可変インダクタ

252 : 積層体

254 : メインインダクタ

254A ~ 254E, 258A ~ 258E : 導体パターン

256A ~ 256D, 260A ~ 260E : スルーホール

258 : 制御インダクタ

262A ~ 262F : 端子電極

264 : スイッチ

10

【図1】

【図2】

【図3】

【 図 4 】

(B)

(B)

( 5 )

(B)

[ 义 6 ]

(B)

【図7】

【図8】

【図9】

【図10】

## 【図11】

---

フロントページの続き

(72)発明者 徳永 敏

東京都台東区上野 6 丁目 16 番 20 号 太陽誘電株式会社内

(72)発明者 横山 直人

東京都台東区上野 6 丁目 16 番 20 号 太陽誘電株式会社内

F ターム(参考) 5E070 AA20 AB06 NN02