(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3951738号

(P3951738)

(45) 発行日 平成19年8月1日(2007.8.1)

(24) 登録日 平成19年5月11日(2007.5.11)

(51) Int.C1.

F 1

|                    |                  |             |      |

|--------------------|------------------|-------------|------|

| <b>HO1L 29/861</b> | <b>(2006.01)</b> | HO1L 29/91  | D    |

| <b>HO1L 29/872</b> | <b>(2006.01)</b> | HO1L 29/48  | F    |

| <b>HO1L 29/47</b>  | <b>(2006.01)</b> | HO1L 21/265 | Z    |

| <b>HO1L 21/265</b> | <b>(2006.01)</b> | HO1L 21/265 | W    |

| <b>HO1L 21/329</b> | <b>(2006.01)</b> | HO1L 21/265 | 602A |

請求項の数 2 (全 25 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2002-45632 (P2002-45632)    |

| (22) 出願日     | 平成14年2月22日 (2002.2.22)        |

| (65) 公開番号    | 特開2003-152198 (P2003-152198A) |

| (43) 公開日     | 平成15年5月23日 (2003.5.23)        |

| 審査請求日        | 平成16年7月13日 (2004.7.13)        |

| (31) 優先権主張番号 | 特願2001-48631 (P2001-48631)    |

| (32) 優先日     | 平成13年2月23日 (2001.2.23)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

| (31) 優先権主張番号 | 特願2001-259928 (P2001-259928)  |

| (32) 優先日     | 平成13年8月29日 (2001.8.29)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                     |

|-----------|-----------------------------------------------------|

| (73) 特許権者 | 503361248<br>富士電機デバイステクノロジー株式会社<br>東京都品川区大崎一丁目11番2号 |

| (74) 代理人  | 100133167<br>弁理士 山本 浩                               |

| (72) 発明者  | 根本 道生<br>神奈川県川崎市川崎区田辺新田1番1号<br>富士電機株式会社内            |

| (72) 発明者  | 西浦 彰<br>神奈川県川崎市川崎区田辺新田1番1号<br>富士電機株式会社内             |

| (72) 発明者  | 内藤 達也<br>神奈川県川崎市川崎区田辺新田1番1号<br>富士電機株式会社内            |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

第1導電型の第1ドリフト層となるバルクウェハの一方の正面に、第1導電型の不純物をイオン注入し、第1ドリフト層より高濃度のバッファ層を形成する工程と、該バッファ層上に、該バッファ層より低濃度の第1導電型の第2ドリフト層をエピタキシャル成長で形成する工程と、該第2ドリフト層に、第2導電型の不純物をイオン注入し、アノード層を形成する工程と、該アノード層上にアノード電極を形成する工程と、前記バルクウェハの他方の正面をバックグラインドして、表面から所定の深さの前記バルクウェハを除去する工程と、前記バックグラインドされた前記バルクウェハの表面上に、前記第1ドリフト層より高濃度の第1導電型の不純物イオンをイオン注入し、カソード層を形成する工程と、該カソード層上にカソード電極を形成する工程とを含むことを特徴とする半導体装置の製造方法。

## 【請求項2】

前記バッファ層を形成するイオン注入のイオン注入量が  $5 \times 10^{11} \text{ cm}^{-2}$  以下とすることを特徴とする請求項1に記載の半導体装置の製造方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

この発明は、ダイオードなどの半導体装置とその製造方法に関する。

## 【0002】

### 【従来の技術】

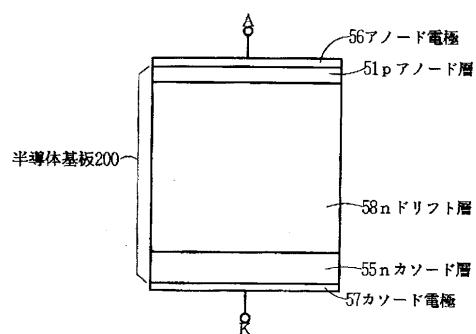

図25は、従来のpinダイオードの要部断面図である。低比抵抗のn型カソード層55となる第1のn型半導体基材上に、高抵抗の第2のn型半導体基材をエピタキシャル成長(以下、エピ成長という)させる。その後、表面の鏡面処理等を施して、熱酸化膜を形成、パターニング後、第2のn型半導体基材の表面層にp型アノード層51を形成する。このp型アノード層51が形成されない領域がn型ドリフト層58となる。その後、白金などのライフタイム制御のための重金属拡散をした後、p型アノード層51表面およびn型カソード層55表面(裏面)にメタリゼーションにより、アノード電極56およびカソード電極57をそれぞれ形成する。

### 【0003】

また、図示しないが、前記のエピタキシャル基板200を用いず、例えば、EZ基板などを用いて、イオン注入や熱拡散で形成する場合もある。その場合は、n型半導体基板の一方の表面層に、p型アノード層を拡散で形成し、他方の表面層にn型カソード層をイオン注入や熱拡散で形成する。このp型アノード層およびn型カソード層が形成されないn型半導体基板がn型ドリフト層となる。

### 【0004】

その後、白金などのライフタイム制御のための重金属拡散した後、p型アノード層上とn型カソード層上に、メタリゼーションでアノード電極およびカソード電極をそれぞれ形成する。

現在、広く用いられている、従来のpinダイオードは、オン状態からオフ状態にスイッチするときには、過渡的に大きな逆方向の電流、所謂、逆回復電流が流れる。この逆回復電流と、逆回復電圧の積により、ダイオードに、大きな電気的損失を生じる。この逆回復損失を小さくし、さらに、スイッチング速度を高速化することが、ダイオードに強く要求されている。

### 【0005】

また、逆回復状態では、ダイオード内部には、定常状態の場合に比べて高い電気的責務(印加される電圧・電流・損失のこと)が生じる。ダイオードに流れる定常電流を大きくしたり、逆阻止状態の電圧を大きくすると、この電気的責務が大きくなり、そのため、ダイオードが破壊することがある。電力用途のダイオードにおいて高い信頼性を確保するためには、この電気的責務に耐えられうるように、逆回復耐量を大きくすることが強く要求される。

### 【0006】

現在、ダイオードの逆回復特性および逆回復耐量を改善するための対策として、重金属拡散や電子線照射などを用いた少数キャリアのライフタイム制御が広く行われている。すなわち、ライフタイムを小さくすることで、定常状態における総キャリア濃度を低減させ、逆回復中に、空間電荷領域の広がりで掃き出されるキャリア濃度を減少させ、逆回復時間や逆回復電流(ピーク値)および逆回復電荷を小さくして、逆回復損失を低減している。

### 【0007】

また、正孔濃度を減少させることにより、正孔が空間電荷領域を走り抜けることによって生じる逆回復中の電界強度を緩和し、逆回復時の責務を小さくして、逆回復耐量を向上させ、ダイオードを破壊し難くしている。一方、ダイオードのソフトリカバリー化も重要な課題である。近年、環境問題などにより、パワーエレクトロニクス機器から発生する電磁ノイズを低減することが要求されており、その対応策の一つに、ダイオードの逆回復電流をソフトリカバリー化して、逆回復電流・電圧波形が発振するのを抑制して、発振によって生じる電磁ノイズを低減する方法がある。

### 【0008】

ソフトリカバリー化する手段としては、アノード側からの少数キャリアの注入効率を抑制する構造がある。代表的な構造として、例えば、参考文献[1]に開示されているMerged Pin / Schottky Diode(MPS)や、例えば、参考文献[2]

10

20

30

40

50

]に開示されているSoft and Fast Recovery Diode(SFD)などがある。

#### 【0009】

##### 【発明が解決しようとする課題】

参考文献〔3〕に開示されているように、ダイオードの逆回復動作の高速化・低損失化とソフトリカバリー化の間にはトレードオフの関係がある。

ダイオードをソフトリカバリー化するためには、オン時に、ドリフト層に蓄積する総キャリア量を多くして、カソード側に蓄積する少数キャリア量を多くし、逆回復時に、空間電荷領域がアノード側からカソード側に向かって広がる過程で、カソード側の少数キャリアができるだけ残留するようにして、逆回復電流の減少率、所謂、逆回復電流減少率  $d i r / d t$  を小さくする方法がある。 10

#### 【0010】

しかし、この方法では、オン時に蓄積するドリフト層内のキャリア量が多いために、逆回復損失が増加し、逆回復が終了するまでに時間を要する(逆回復時間が長くなる)。

一方、ダイオードを高速化および低損失化するということは、前記とは逆に、ドリフト層に一様にライフタイムキラーを導入するライフタイム制御やドリフト層を薄くするなどにより、オン時にドリフト層に蓄積するキャリア量を少なくするということである。しかしながら、ドリフト層に蓄積するキャリア量が少なくなると、カソード側に蓄積する少数キャリア量も少なくなり、所謂、スナッピー(前記の  $d i r / d t$  が大きいこと)なハードリカバリーとなり、逆回復電圧・電流ともに発振波形になる場合がある。 20

#### 【0011】

また、ダイオードをソフトリカバリー化する方法としては、前記の参考文献〔1〕、〔2〕に開示されている低注入型ダイオードであるMPSやSFDなどがあるが、これらの構造では、同一厚さのドリフト層を有する通常のpinダイオード構造に比べて、シットキー接合や低濃度アノード層により、耐圧の低下や逆バイアス時の漏れ電流の増加が起き易い。

#### 【0012】

また、ソフトリカバリー化の他の方法として、プロトンやヘリウムイオン等の軽イオン粒子線の照射により、ライフタイムの局所制御を行う場合、ウェハあたりの照射コストがまだ高く、製造コストが高くなる。ドリフト層の厚みを薄くし、前記のMPS構造やSFD構造である低注入ダイオードにするか、または、ドリフト層の厚みを薄くし、ライフタイムの局所制御をして、高速化・低損失化とソフトリカバリー化のトレードオフの向上を図ったとしても、ドリフト層の厚みを薄くすると、ソフトリカバリー化に必要なドリフト層のカソード側の余剰キャリアが存在する領域が不足し、逆回復電流がハードリカバリーとなり、逆回復電流・電圧が発振波形になり易くなる。また、耐圧の確保も一層困難となる。 30

#### 【0013】

この発明の目的は、前記の課題を解決して、耐圧を確保しながら、高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる薄いドリフト層を有する半導体装置を提供することである。 40

#### 【0014】

##### 【課題を解決するための手段】

前記の目的を達成するために、第1導電型の第1ドリフト層となるバルクウェハの一方の正面に、第1導電型の不純物をイオン注入し、第1ドリフト層より高濃度のバッファ層を形成する工程と、該バッファ層上に、該バッファ層より低濃度の第1導電型の第2ドリフト層をエピタキシャル成長で形成する工程と、該第2ドリフト層に、第2導電型の不純物をイオン注入し、アノード層を形成する工程と、該アノード層上にアノード電極を形成する工程と、前記バルクウェハの他方の正面をバックグラインドして、表面から所定の深さの前記バルクウェハを除去する工程と、前記バックグラインドされた前記バルクウェハの表面に、前記第1ドリフト層より高濃度の第1導電型の不純物イオンをイオン注入し、

カソード層を形成する工程と、該カソード層上にカソード電極を形成する工程とを含む製造方法とする。

【0015】

【0016】

【0017】

【0018】

【0019】

【0020】

【0021】

【0022】

10

以下の説明では、前記の第1導電型をn型、第2導電型をp型とする。

この発明の特徴は、例えば、p-i-n構造のダイオードを例にとると、i層すなわち高比抵抗のn型ドリフト層内に、p型アノード層およびn型カソード層に接触しないように、n型ドリフト層よりは低比抵抗で、n型カソード層よりは高比抵抗であるようなn型バッファ層を、一様にもしくは選択的に形成する構成としたことにある。このような構造にすることで、n型ドリフト層を薄くしても発振せずソフトリカバリーにでき、耐圧も損なわずにすむ。すなわち、逆回復時に広がる空間電荷領域がn型バッファ層で一旦止まるため、n型バッファ層よりアノード側の少数キャリアは空間電荷領域によりすばやく掃き出される。一方n型バッファ層よりカソード側では、空間電荷領域は、n型バッファ層を超えて少しだけ残りのカソード側のn型ドリフト層に進入し、それ以上は広がらない。このために、カソード側の少数キャリアは、空間電荷領域には掃き出されずに、再結合のみにより減少する。従って、従来型のn型バッファ層を持たないp-i-nダイオードに比べて十分キャリアが残るので、電流減少率が抑えられて、ソフトリカバリーとなる。従って、全n型ドリフト層厚を薄くすることができ、結果として、従来ダイオードに比べてソフトリカバリーかつ高速・低損失な逆回復動作にもすることが可能になる。

【0023】

ここで素子耐圧BVは、従来ダイオードに比べてもほとんど低下せず、同様の値となる。これは、逆バイアス時にアノード側から空乏層が広がるときにn型バッファ層も空乏化するため、印加電圧をn型ドリフト層全体で担うことができるからである。

【0024】

30

**【発明の実施の形態】**

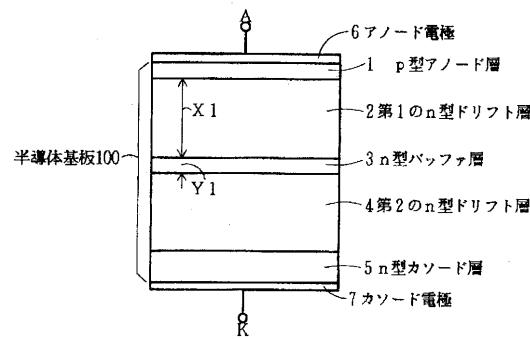

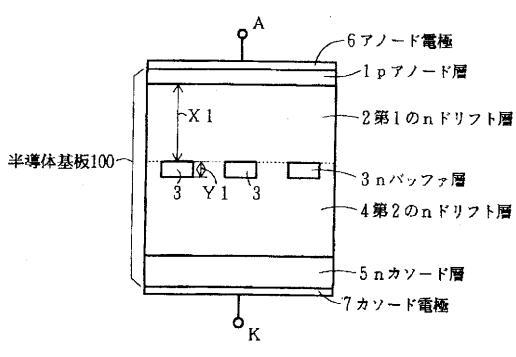

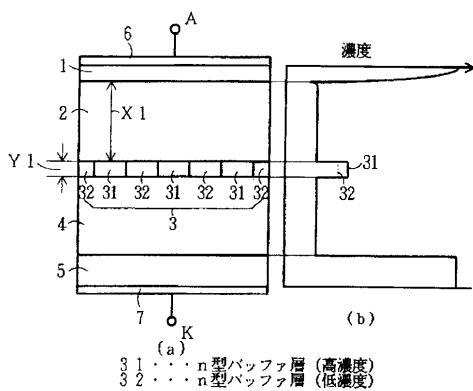

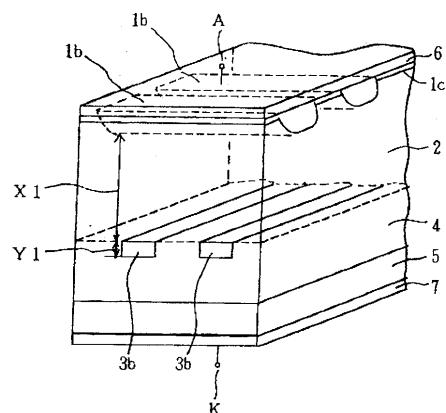

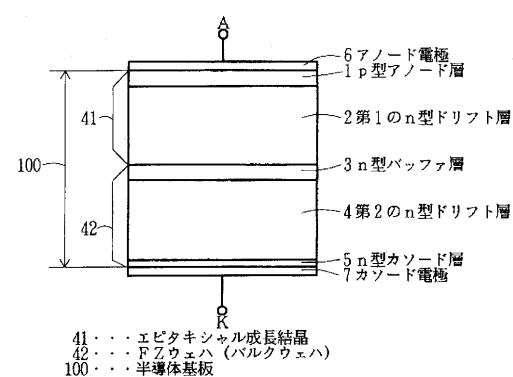

以下の説明で、第1導電型をn型、第2導電型をp型とする。勿論、逆であっても構わない。図1は、この発明の第1実施例の半導体装置の要部断面図である。この図は、耐圧構造部を除いた活性部におけるn型バッファ層を形成したp-i-nダイオードの要部断面図を示している。

【0025】

例えば、Sb(アンチモン)で、約0.01 - cmの低比抵抗のn型カソード層5となるn型半導体基材上に、例えばP(リン)で、55 - cmの第2のn型ドリフト層4を約55 μmエピ成長させる。その後、連続的に、例えばPで、5 - cmのn型バッファ層3を5 μmエピ成長させる。再び、連続的に、例えばPで、55 - cmのn型半導体層(後述の第1のn型バッファ層2とp型アノード層1となる)を60 μmエピ成長させる。その後、表面の鏡面処理等を施して、通常のエピ基板と同様に、半導体プロセス処理を開始する。熱酸化膜を形成し、パターニング後、イオン注入および熱拡散により、前記60 μmの半導体層の表面層に5 μm厚のp型アノード層1を形成する。このp型アノード層1が形成されない領域が第1のn型ドリフト層2となる。

【0026】

pアノード層1と第1のn型ドリフト層2とのpn接合からnバッファ層3までの最短距離X1と、n型バッファ層3の幅Y1は図示した通りである。このX1は、ここでは第1のn型ドリフト層2で、55 μmとなり、Y1は、n型バッファ層の幅で、5 μmとなる。第1のn型ドリフト層2、n型バッファ層3、第2のドリフト層4を合わせて全体の

40

50

n型ドリフト層と称す。また、n型カソード層5と、第2のn型ドリフト層4と、n型バッファ層3と、前記のn型半導体層が、エピタキシャル成長で製作された半導体基板100(エピ基板)である。

#### 【0027】

その後、白金などのライフタイム制御のための重金属拡散した後、p型アノード層1表面およびn型カソード層5表面(裏面)にメタリゼーションにより、アノード電極6およびカソード電極7をそれぞれ形成する。これらの電極6、7にアノード端子Aとカソード端子Kが接続する。この様に、エピ成長のドーピング濃度制御以外は、すべて、図25の従来のpinダイオードと同じ工程で形成可能である。ライフタイム制御は重金属拡散以外にも、電子線やHe等の軽イオン照射等があり、いずれでも構わない。

10

#### 【0028】

前記のX1とY1を後述する所定の範囲に設定することで、耐圧を確保しながら、高速化・低損失化とソフトリカバリー化の間のトレードオフを改善することができる。

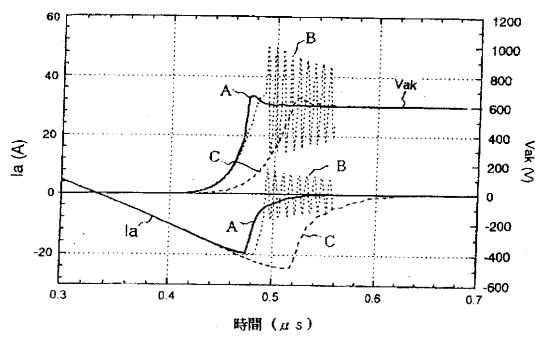

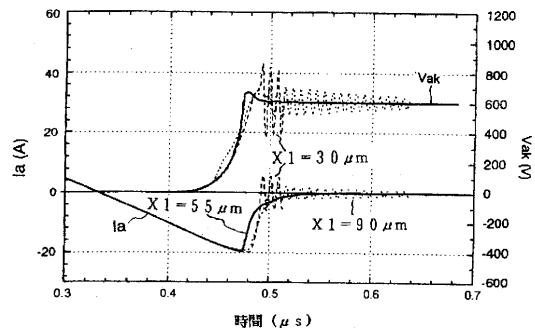

図2は、本発明のpinダイオード(本発明品)と、従来のpinダイオード(従来品)との室温における逆回復波形を示す図である。Iaはアノード電流でVakはアノード・カソード間の電圧で、図では、正方向の電圧(プラス側の電圧)は、pinダイオードの逆方向電圧を示す。また、Iaが零を切って負になる時点以降から逆回復過程となる。本発明品Aの全体のn型ドリフト層の厚さは115μm、従来品のn型ドリフト層の厚さは、115μm(B)および135μm(C)の2通りである。また、従来品のp型アノード層、n型カソード層の厚さは本発明品と同じである。試験条件は、順電流(アノード電流)のピーク値は50Aで、逆方向の印加電圧は600V(素子耐圧BVの1/2)である。

20

#### 【0029】

いずれの素子も室温で定格電流50A(定格電流密度170Acm<sup>-2</sup>に相当)での順電圧降下が1.7Vとなるように、電子線照射によりライフタイムを制御している。従来品では、n型ドリフト層が135μm(C)の場合は発振せずにソフトリカバリーであるのに対し、n型ドリフト層が115μm(B)の場合ではハードリカバリー、すなわち逆回復電流減少率dir/dtがある時刻で急に増加し(逆回復電流が急激に減少し)、スナップーリカバリー、つまり、ハードリカバリーとなり、逆回復電流(アノード電流Iaが零になる時点以降の電流)が発振するようになる。このため、回路のインダクタンスLと逆回復電流減少率dir/dtの積(L·(dir/dt))で発生する逆回復電圧もスパイク状に増加し、逆回復電圧が振動するようになる。ここでは、見やすくするために、115μm(B)の従来品については、0.55μs以降の振動波形を省略している。

30

#### 【0030】

一方、本発明品(A)は、全体のn型ドリフト層が115μmであるにもかかわらず、発振せずにソフトリカバリーとなっている。つまり、115μm(B)の従来品と同等の高速化・低損失化を達成しながら、ソフトリカバリー化も図られており、高速化・低損失化とソフトリカバリー化の間のトレードオフが大幅に改善されている。

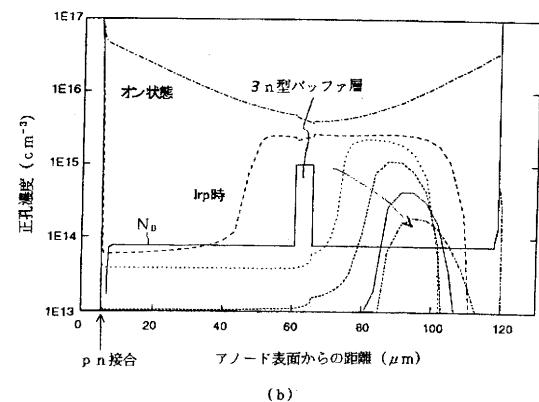

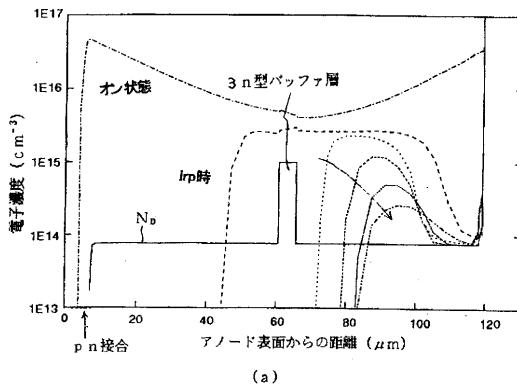

#### 【0031】

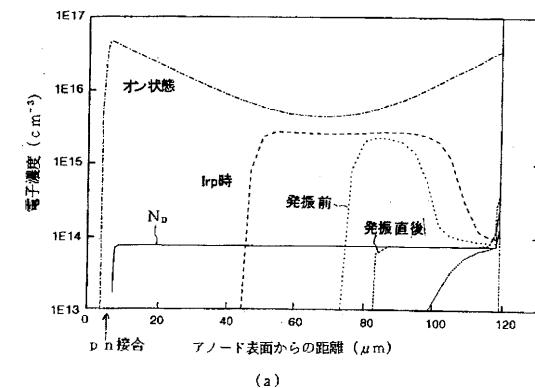

さらに、ソフトリカバリー品同士(AとC)で比較すると、逆回復電荷Qrrは、従来品(135μm(C))が2.95μCであるのに対し、本発明品(A)は1.65μCであり、約55%まで減少できている。従って、本発明品(A)は、逆回復特性(逆回復電荷Qrr)も大きく改善していることが分かる。図3は、図2の逆回復過程において、本発明品の逆回復時におけるキャリア濃度の変化をデバイスシミュレーションにより計算したもので、同図(a)は電子濃度、同図(b)は正孔濃度である。横軸は、p型アノード層1表面からの深さ方向の距離、縦軸はキャリア濃度を示す。図中のN<sub>D</sub>はn型ドリフト層の不純物濃度でドナー濃度であり、1E13の表現は1×10<sup>13</sup>を意味する。また、p型アノード電極からpn接合までの距離(p型アノード層の厚み)は、5μmであり、全体のn型ドリフト層(n型バッファ層を含む)の厚さは、115μmである。

40

#### 【0032】

50

p n 接合から n 型ドリフト層（図 1 の第 1 の n 型ドリフト層 2 のこと）に空間電荷領域（空乏層）が広がり、逆回復電流がピークを過ぎた後（I rp 時）、空間電荷領域は、n 型バッファ層 3 で、その広がりは一旦阻止され、その後、n 型バッファ層 3 を越えて、カソード側の n 型ドリフト層に達する。n 型バッファ層 3 があり、逆方向の印加電圧が素子耐圧 BV (1200V) の半分であるため、空間電荷領域の広がりは、この n 型ドリフト層内で停止し、カソード側の n 型ドリフト層（図 1 の第 2 の n 型ドリフト層 4 のこと）内に残留した多くのキャリアは、その後、矢印で示すように再結合によりスムースに減少する。従って、逆回復過程で、キャリア（電子と正孔）が十分残り、逆回復電流減少率（d i r / d t）は小さく抑えられ、ソフトリカバリーとなる。

## 【0033】

10

図 4 は、図 2 の逆回復動作において、115 μm (B) の従来品における逆回復時のキャリア濃度の変化をデバイスシミュレーションにより計算したもので、同図 (a) は電子濃度、同図 (b) は正孔濃度である。この図は、図 3 に相当し、本発明品 (A) と比較するための図である。

図 3 との違いは、図 3 の n 型バッファ層 3 のある位置よりカソード側でのキャリアの減少の具合が異なる。従来品 (B) の空間電荷領域は、n 型バッファ層がないため、n 型バッファ層で遮られることなく、カソード側へ進行する。その結果、カソード側の n 型ドリフト層に残留しているキャリアは、カソード側の n 型ドリフト層に広がった空間電荷領域より掃き出されて、n 型ドリフト層内の残存キャリアは、ドナー濃度 N<sub>D</sub> 以下に急激に減少し、カソード側の n 型ドリフト層内の正孔（少数キャリア）は枯渇する。

20

## 【0034】

この状態は、図 4 に示されており、発振前にあった蓄積したキャリア（電子と正孔）は、発振直前（図の発振直後とほぼ同じ状態）に枯渇状態となる。このとき、図 4 (b) に示す正孔濃度は、矢印の先、 $1 \times 10^{13} \text{ cm}^{-3}$  よりはるかに小さな状態となる。この枯渇状態が急激に起こるために、逆回復電流減少率 d i r / d t が大きくなり、ハードリカバリーとなる。その結果、逆回復電流・電圧が発振を開始する。

## 【0035】

図 5 は、本発明品 (A) において、p 型アノード層と n 型ドリフト層の p n 接合から n 型バッファ層までの最短距離 X 1 をパラメータとした逆回復電圧・電流波形の比較図である。

30

X 1 は 30 μm、55 μm、90 μm である。図 2 に示す従来品 (115 μm 品 (B)) よりは発振の程度は良いものの、本発明品 (A) の 30、90 μm ともに発振している。このように、n 型バッファ層 3 の位置 (X 1 の大きさ) によりソフトリカバリー効果に違いがある。

## 【0036】

以下、ソフトリカバリー化するための、n 型バッファ層の位置と幅について説明する。

逆回復中の空間電荷領域について、ポアソンの式を解けば、p n 接合から n 型ドリフト層に広がった空間電荷領域端までの距離 L は、

## 【0037】

【数 1】と表される。この  $[(J_F / q v_{sat}) + N_D]$  は、ポアソンの式の電荷量に相当し、 $(J_F / q v_{sat})$  を逆回復動作による電荷とする。

40

この式により、素子耐圧 BV (素子のアバランシェ電圧) と、素子の定格電流密度 J<sub>F</sub> と、n 型ドリフト層の不純物濃度 N<sub>D</sub> を決めると、 $[(J_F / q v_{sat}) + N_D]$  と置いた電荷量に相当する、p n 接合から n 型ドリフト領域に広がった空間電荷領域の距離 L がポアソンの式により決まる。ここでは、この距離 L を、空間電荷領域の広がりを示す指標（以下、距離指標という）として用いる。

## 【0038】

ここで、式中の定格電流密度 J<sub>F</sub> は、素子耐圧 BV と以下のような関係がある。印加電圧 V<sub>ak</sub> にて、インパクトイオン化（アバランシェ状態）を起こす電流密度 J<sub>ii</sub> は、

## 【0039】

50

【数2】と表される。この式は、参考文献〔4〕に開示されている。尚、式の5.3e13の表現は、 $5.3 \times 10^{13}$ を意味する。

素子の定格電流密度 $J_F$ は、一般的には余裕を見て、インパクトイオン化を起こす電流密度 $J_{i,i}$ の1/3に設定する。即ち、定格電流密度 $J_F$ の3倍以上で、アバランシェ降伏を起こすように設定する。素子耐圧 $BV$ と定格電流密度 $J_F$ の関係は、

#### 【0040】

#### 【数3】と表される。

つぎに、前記の(4)式を用いて、距離指標 $L$ を具体的に算出する。

例えば、 $BV = 1200V$ (アバランシェ電圧)、 $N_D = 8.4 \times 10^{13} cm^{-3}$ 、キャリアの飽和速度 $v_{sat}$ は $1 \times 10^7 cm/s$ とすると、上式により、 $J_F = 170 A/cm^2$ となり、(4)式にこれらの値を代入すると、距離指標 $L$ は $64 \mu m$ となる。当然、距離指標 $L$ は、素子耐圧 $BV$ 、定格電流密度 $J_F$ 、不純物濃度 $N_D$ 、飽和速度 $v_{sat}$ に依存する。

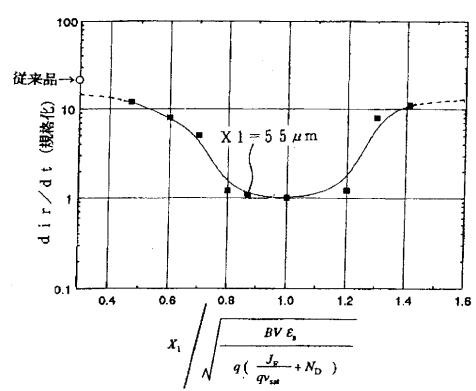

#### 【0041】

図6は、この距離指標 $L$ を基準にし、pn接合からn型バッファ層までの最短距離 $X_1$ を変化させたときのソフトリカバリーの度合いの変化を示したものである。この図6は、横軸に $X_1$ と $L$ との割合、縦軸に逆回復電流の電流減少率(逆回復電流減少率 $d_{ir}/dt$ )を示している。 $d_{ir}/dt$ が小さければソフトリカバリーとなる。全体のn型ドリフト層の厚さは $115 \mu m$ である。縦軸は、 $X_1$ と距離指標 $L$ と同じとき( $X_1/L = 1$ の値)の $d_{ir}/dt$ の値で規格化している。従来品の場合は $d_{ir}/dt$ の値が大きく、本発明品の約20倍である。尚、 $d_{ir}/dt$ の値は、傾斜が最大になる値で定義している。

#### 【0042】

図6に示すように、本発明品のようにn型バッファ層を形成すれば、従来品よりも $d_{ir}/dt$ を抑制する効果が得られ、本発明品では、その効果が得られる範囲は、 $X_1/L$ は0.3から1.6の範囲である。また、 $X_1/L$ が1のときが最も $d_{ir}/dt$ が小さくなり、0.8から1.2の範囲であれば $d_{ir}/dt$ は小さくできて、発振せずにソフトリカバリーにできる。尚、図中の点線は推定値である。

#### 【0043】

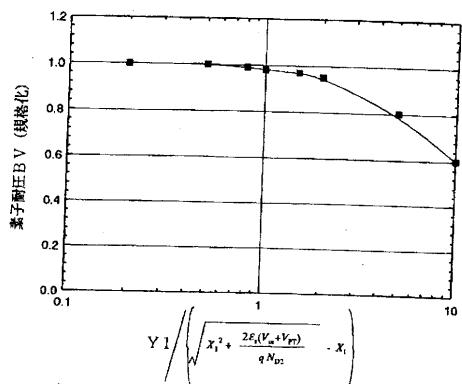

本発明品は、n型ドリフト層内にn型バッファ層を含んでいるため、このn型バッファ層で空間電荷領域の伸びが抑制され、pn接合での電界強度が上昇する。そのため、素子耐圧 $BV$ が減少しないようにn型バッファ層の位置と幅を決める必要がある。

素子耐圧 $BV$ の低下を防止するには、逆バイアス時にn型バッファ層が空乏化し、空間電荷領域がn型バッファ層を乗り越えるように設計することである。

#### 【0044】

こうすることで、n型バッファ層よりもカソード側のn型ドリフト層も空乏化することができるため、素子耐圧 $BV$ を従来品と同等にすることができます。本発明品で、逆バイアス電圧が素子耐圧 $BV$ の1/2の電圧にて空間電荷領域がn型バッファ層を越えるという条件で、算出したn型バッファ層の幅の値を $W$ とすると、 $W$ は、

#### 【0045】

【数4】と表せる。この式の $W$ をn型バッファ層の幅を示す幅指標として用いる。尚、第1導電型(n型)バッファ層の平均濃度とは、n型バッファ層内で濃度を積分し、n型バッファ層の幅 $Y_1$ で割った値である。

#### 【0046】

図7は、 $Y_1/W$ の値と素子耐圧 $BV$ の関係を示した図である。ただし、 $Y_1$ は実素子でのn型バッファ層の幅である。図の横軸は $Y_1/W$ を示し、縦軸は、従来品の素子耐圧 $BV$ で規格化してある。図7によれば、 $Y_1/W$ が2以上で素子耐圧 $BV$ が急激に低下する。従って、 $Y_1/W$ の値が2以下になるようにn型バッファ層の幅 $Y_1$ およびn型バッファ層の濃度 $N_{D2}$ を設定すれば、素子耐圧 $BV$ は十分確保できる。

#### 【0047】

10

20

50

30

40

50

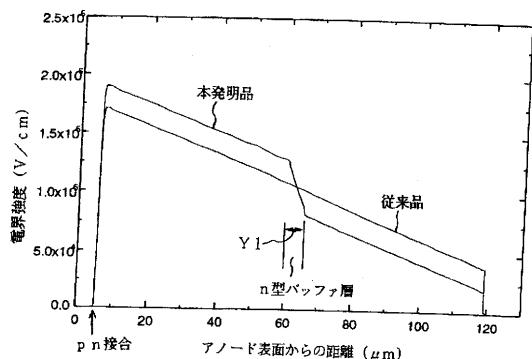

図 8 は、 $Y_1 / W$  が等しくなるようにした本発明品 ( $Y_1 / W = 1$ ) と従来品における、逆バイアス電圧を印加したときの電界強度分布図である。ここでは、印加電圧を 120 V とした。この電圧は、本発明品ではアバランシェを起こす電圧 (素子耐圧 BV) である。

本発明品 ( $Y_1 / W$  の値が 2 以下) では、従来品と比べて、電界強度が多少高くなるが、n 型バッファ層が空乏化することで、空間電荷領域が n 型カソード層に達しており、逆バイアス電圧を n 型ドリフト層全域で担っていることが分かる。

#### 【0048】

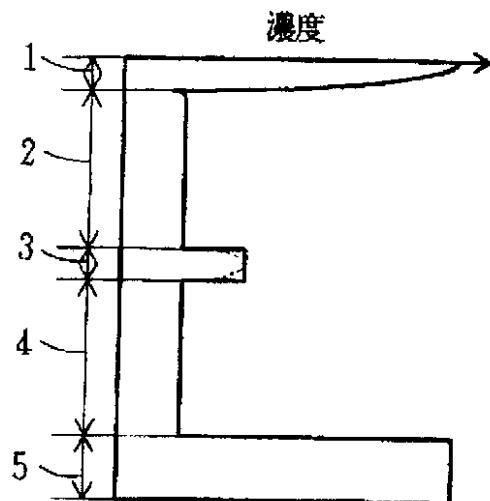

図 9 は、図 1 の不純物プロファイルを示す図である。n 型バッファ層 3 の濃度が階段状の場合が実線で傾斜した場合は点線で示した。図の濃度は、p 型アノード層 1 の領域は p 型不純物の濃度であり、第 1 の n 型ドリフト層 2、n 型バッファ層 3、第 2 の n 型ドリフト層 4 および n 型カソード層 5 の領域の濃度は n 型不純物の濃度である。10

#### 【0049】

階段状の不純物プロファイルは、エピタキシャル成長で、比較的熱処理温度を低くして形成した場合に得られ、点線で示す傾斜した不純物プロファイルは、エピタキシャル成長で形成するとき、熱処理温度が高く、処理時間を長くする場合や、イオン注入や熱拡散で形成する場合に得られる。傾斜したプロファイルの場合でも、平均濃度を用いることで、前記の(5)式を適用することができる。

#### 【0050】

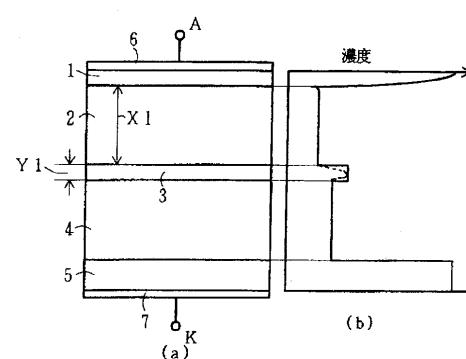

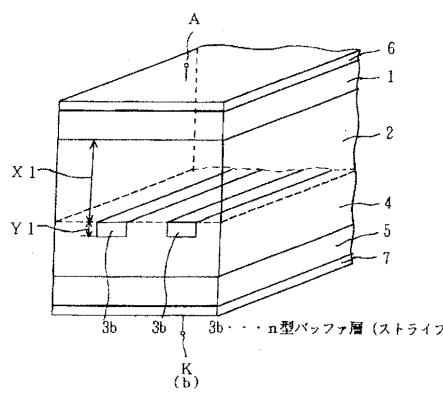

図 10 は、この発明の第 2 実施例の半導体装置の要部断面図である。図 1 との違いは、半導体基板 100 の正面と平行な方向に n 型バッファ層 3 を選択的に複数個形成している点である。n 型バッファ層 3 を含む不純物プロファイルは、図 9 の点線と同じである。この n 型バッファ層 3 の形状については、後述の図 13 から図 23 の実施例で説明する。20

#### 【0051】

n 型バッファ層 3 の間に挟まれた第 2 の n 型ドリフト層 4 は高比抵抗であるために、空乏層が広がりをしやすくなり、耐圧の確保が容易にできる。この構造は、エピ成長を 2 回に分け、1 回目の n 型ドリフト層 (第 2 の n 型ドリフト層 4) 形成後に、例えば P (リン) を選択的にイオン注入かつ熱処理することで n 型バッファ層 3 を形成する。その後、第 1 の n 型ドリフト層 2 をエピ成長させる。つまり、n 型バッファ層 3 を選択的なイオン注入と熱処理で形成する。30

#### 【0052】

この場合も、 $X_1 / L$  および  $Y_1 / W$  の値を第 1 実施例と同じにすることで、第 1 実施例と同様の効果が期待できるが、素子耐圧 BV に関しては、n 型バッファ層 3 の間に挟まれた第 2 の n 型ドリフト層 4 で空乏層が広がり易くなるために、図 1 より高くなる。

図 11 は、この発明の第 3 実施例の半導体装置であり、同図 (a) は要部断面図、同図 (b) は不純物プロファイルである。図 10 との違いは、複数個の n 型バッファ層を濃度の異なる領域で構成し、しかもそれらの n 型バッファ層を互いに隣接させた点である。n 型バッファ層は高濃度の n 型バッファ層 31 と低濃度の n 型バッファ層 32 で構成され、それらの不純物プロファイルは、図では階段状にしたが、傾斜させる場合もある。

#### 【0053】

この場合も、 $X_1 / L$  および  $Y_1 / W$  の値を第 1 実施例と同じにすることで、第 1 実施例と同様の効果が期待できるが、素子耐圧 BV に関しては、図 1 と図 10 の中間的な値となる。図 12 は、この発明の第 4 実施例の半導体装置であり、同図 (a) は要部断面図、同図 (b) は不純物プロファイルである。40

#### 【0054】

図 1 との違いは、n 型ドリフト層の濃度を、アノード側とカソード側で分け、カソード側の第 2 の n 型ドリフト層 4 を、アノード側の第 1 のドリフト層 2 より高濃度にする。言い換えると、アノード側の第 1 の n 型ドリフト層 2 を、カソード側の第 2 の n 型ドリフト層 4 を高比抵抗にする。n 型バッファ層 3 の不純物プロファイルは、実線で示すように階段状の場合と、点線で示すように傾斜させる場合がある。50

## 【0055】

このようにすると、第1のn型ドリフト層2とn型バッファ層3で広がった空間電荷領域を第2のn型ドリフト層4の効果的に止めることができて、図1と比べて、素子耐圧B Vを確保し易くできる。また、X1/LおよびY1/Wの値を第1実施例と同じにすることで、第1実施例と同様の効果が期待できる。

尚、n型バッファ層3が、図10や図11のように複数個となっていても構わない。

## 【0056】

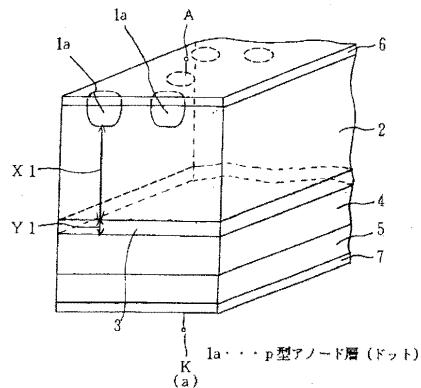

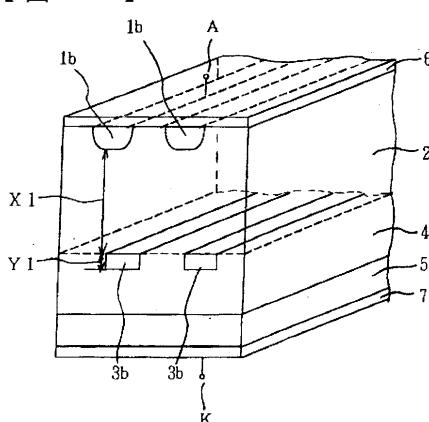

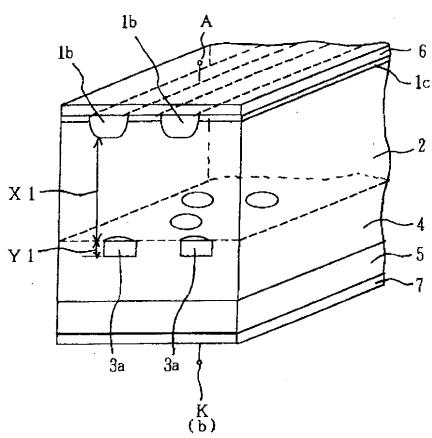

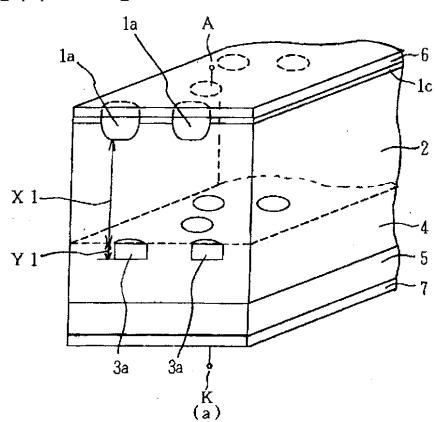

図13は、図10のn型バッファ層の形状を説明する半導体装置の斜視図で、同図(a)はドット(島状)の場合、同図(b)はストライプの場合である。

図中の3aはドット状をしたn型バッファ層であり、3bはストライプ状のn型バッファ層である。

10

どちらの場合もX1/WおよびY1/Lの範囲を図6、図7で説明した範囲に設定することで、耐圧を確保しながら、高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる。なお、これらの実施例の各図は、活性領域の部分について記載して説明しているが、通常はこの活性領域の外周にガードリング、フィールドプレートあるいはRESURF等の耐圧構造が形成される。そして、チップの外周端にはp型領域あるいは高濃度のn型領域のストップ領域とその上のストップ電極が形成される。このストップ領域を設けることで、空乏層を理想的な位置で終端させることができるので、ドット状あるいはストライプのn型バッファ層がチップ側面に露出していても問題がない。このため、チップ側面に特別な耐圧確保のための対策を施す必要がない。

20

## 【0057】

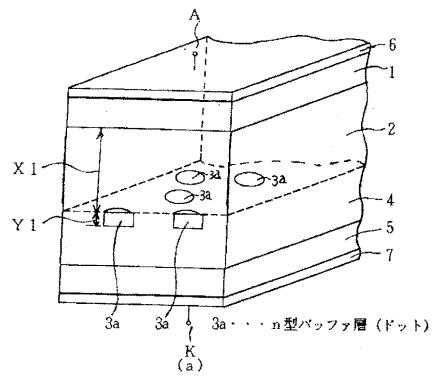

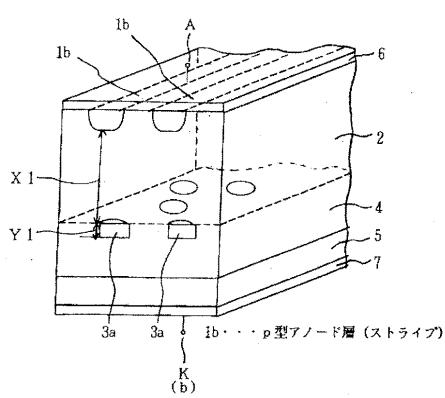

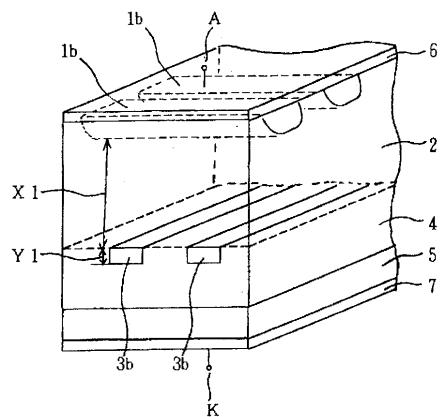

図14は、この発明の第5実施例で、MPS構造のダイオードのドリフト層に第1実施例のn型バッファ層を適用した半導体装置の要部斜視図であり、同図(a)はMPS構造がドットの場合、同図(b)はMPS構造がストライプの場合である。図中の1aはp型アノード層で、このp型アノード層に挟まれた第1のドリフト層2表面とアノード電極6の接合部は、ショットキー接合となっている。

## 【0058】

MPS構造により、アノード側からの少数キャリアが図1の場合より減少することでソフトリカバリー化が一層図られる。従って、X1/LおよびY1/Wの範囲を図6、図7で説明した範囲に設定することで、耐圧を確保しながら、第1実施例より高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる。

30

## 【0059】

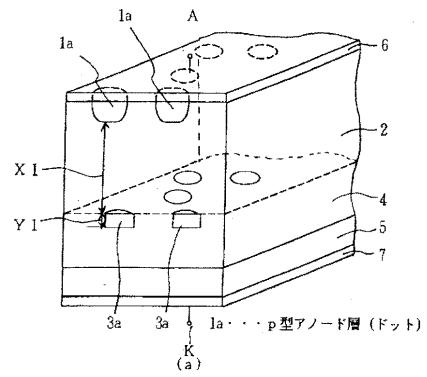

図15は、この発明の第6実施例で、MPS構造のダイオードのドリフト層に図13(a)に示した島状のn型バッファ領域を適用した半導体装置の要部斜視図であり、同図(a)はMPS構造がドットの場合、同図(b)はMPS構造がストライプの場合である。

MPS構造により、アノード側からの少数キャリアが図10の場合より減少することでソフトリカバリー化が一層図られる。従って、X1/LおよびY1/Wの範囲を図6、図7で説明した範囲に設定することで、耐圧を確保しながら、第2実施例より高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる。

## 【0060】

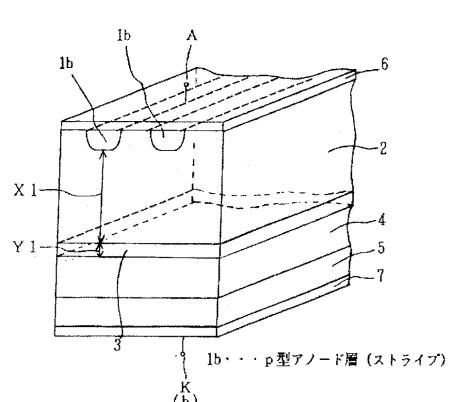

図16から図18は、この発明の第7実施例で、MPS構造のダイオードのドリフト層に図13(b)に示したストライプ状のn型バッファ領域を適用した半導体装置の要部斜視図であり、図16はMPS構造がドットの場合、図17はn型バッファ層のストライプとMPS構造のストライプが平行する場合、図18はn型バッファ層のストライプとMPS構造のストライプが直交する場合である。尚、図18で必ずしも直交せず、所定の角度をもって交差しても構わない。

40

## 【0061】

MPS構造により、アノード側からの少数キャリアが図10の場合より減少することでソフトリカバリー化が一層図られる。従って、X1/LおよびY1/Wの範囲を図6、図7で説明した範囲に設定することで、耐圧を確保しながら、第2実施例より高速化・低損

50

### 失化とソフトリカバリー化の間のトレードオフが改善できる

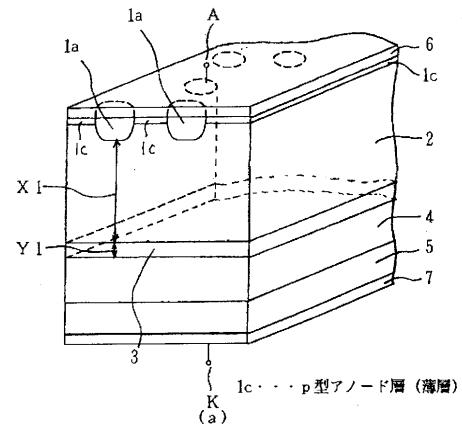

以下の実施例では、前記MPS構造のショットキー接合の代わりに薄いp<sup>-</sup>層（薄層のp型アノード層1c）を形成したSFD構造のダイオードのドリフト層に、前記の実施例のn型バッファ層を形成した半導体装置の場合である。このp<sup>-</sup>層の製造方法について説明する。アノード電極として、p型アクセプタとなる元素、例えばA1と、半導体基板の元素、例えばSiを含む金属、A1-3%SiもしくはA1-5%Si-0.5%Cu等をスパッタや真空蒸着にて形成する。その後、水素や窒素雰囲気にて熱処理をする。例えばSiを含むAl金属でショットキーバリアを形成すると、表層にごく浅いp層を形成することができ、Alのみよりもバリアを高くできる。これは、Al-Si金属がSiを数%含んでいるため、熱処理時にSi表層にエピタキシャルな再成長層を形成でき、その層にAlをアクセプタとして含んでいるためである。熱処理温度を上げると再成長層の厚さが増加するので実効的なショットキーバリア高さもそれに伴い増加する。熱処理の温度は400から500程度である。また実際にSIMS等で観測したところ約120の厚さでエピタキシャルな再成長層が形成され、それが約10<sup>17</sup>cm<sup>-3</sup>のAl（アクセプタ）を含むp<sup>-</sup>層となっていること確認した。この薄いp<sup>-</sup>層が形成されたショットキー接合の障壁高さは、このp<sup>-</sup>層がない場合と比べて、10%程高くなり、漏れ電流が小さくなる。また、p<sup>-</sup>層があるために、オン電圧が低減され、高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる。

#### 【0062】

以下にこの薄いp<sup>-</sup>層が形成されたショットキー接合を有するSFD構造のダイオードに本発明を適用した実施例について説明する。

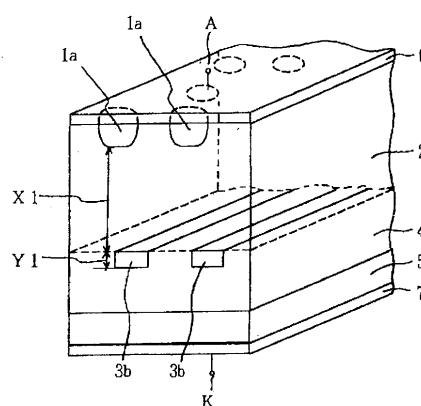

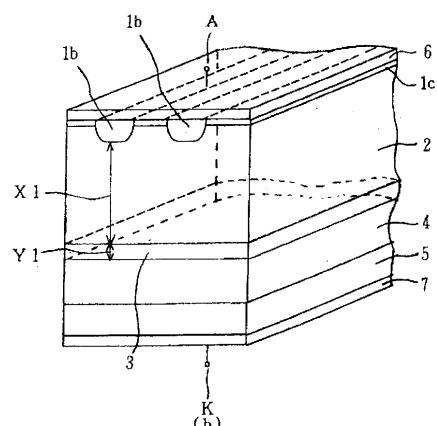

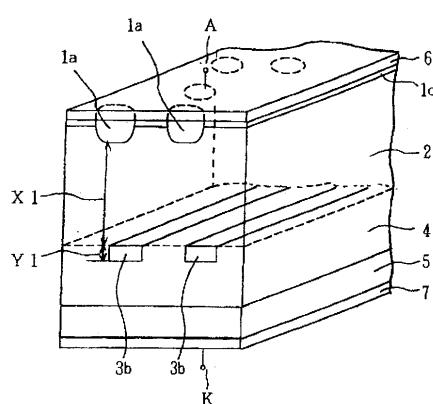

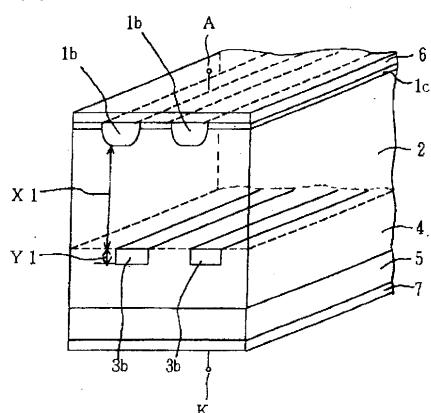

図19は、この発明の第8実施例で、SFD構造のダイオードのドリフト層に第1実施例のn型バッファ層を適用した半導体装置の要部斜視図であり、同図(a)はSFD構造がドットの場合、同図(b)はSFD構造がストライプの場合である。

#### 【0063】

SFD構造により、アノード側からの少数キャリアが図1の場合より減少することでソフトリカバリー化が一層図られる。従って、X1/LおよびY1/Wの範囲を図6、図7で説明した範囲に設定することで、耐圧を確保しながら、第1実施例より高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる。

#### 【0064】

図20は、この発明の第9実施例で、SFD構造のダイオードのドリフト層に第2実施例のドット状のn型バッファ層を適用した半導体装置の要部斜視図であり、同図(a)はSFD構造がドットの場合、同図(b)はSFD構造がストライプの場合である。

SFD構造により、アノード側からの少数キャリアが図10の場合より減少することでソフトリカバリー化が一層図られる。従って、X1/LおよびY1/Wの範囲を図6、図7で説明した範囲に設定することで、耐圧を確保しながら、第2実施例より高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる。

#### 【0065】

図21から図23は、この発明の第10実施例で、SFD構造のダイオードのドリフト層に第2実施例のストライプ状のn型バッファ層を適用した半導体装置の要部斜視図であり、図21はSFD構造がドットの場合、図22はn型バッファ層のストライプとSFD構造のストライプが平行する場合、図23はn型バッファ層のストライプとSFD構造のストライプが直交する場合である。尚、図23で必ずしも直交せず、所定の角度をもって交差しても構わない。

#### 【0066】

SFD構造により、アノード側からの少数キャリアが図10の場合より減少することでソフトリカバリー化が一層図られる。従って、X1/LおよびY1/Wの範囲を図6、図7で説明した範囲に設定することで、耐圧を確保しながら、第2実施例より高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる。

#### 【0067】

10

20

30

40

50

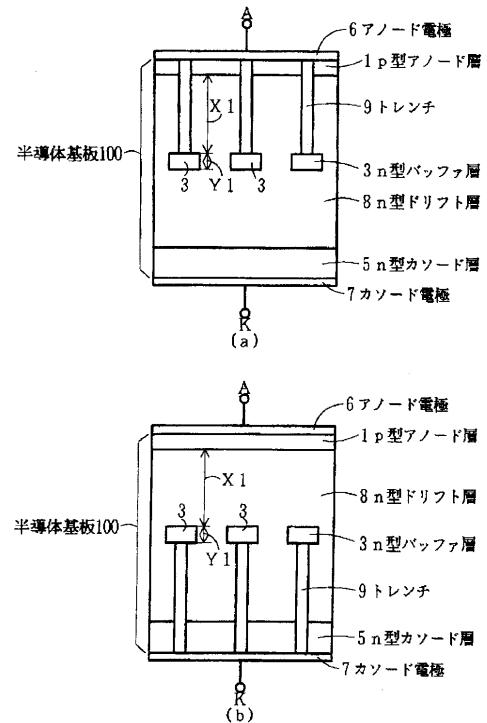

図24は、この発明の第11実施例で、n型バッファ層をトレンチ溝の底部に形成した半導体装置であり、同図(a)はアノード側にトレンチを形成した場合、同図(b)はカソード側にトレンチを形成した場合である。

この構造は、トレンチ9を掘り、その底にn型バッファ層3を形成し、その後トレンチ9は酸化膜で埋め込んで形成される。このようにトレンチ9を掘ることで、エピ成長させることなく、n型バッファ層3をn型ドリフト層8内に形成することができる。

#### 【0068】

この場合も、X1/LおよびY1/Wの範囲を図6、図7で説明した範囲に設定することで、耐圧を確保しながら、第2実施例と同等の高速化・低損失化とソフトリカバリー化の間のトレードオフが改善できる。

10

さらに、図示しないが、サイリスタや、MOSFETの寄生ダイオードのドリフト層(高比抵抗層)に、前記のバッファ層を適用することで、高速化・低損失化とソフトリカバリー化の間のトレードオフを改善することができる。

#### 【0069】

図26は、この発明の第12実施例になる半導体装置の要部断面図である。

図1との違いは、n型カソード層5をイオン注入で形成し、その厚さが、図1の場合の数十μmに対して、1μm以下と極めて薄くした点である。このように、n型カソード層5を薄く形成することで、ライフタイムキラーの導入を抑制しても、耐圧を確保しながら、図1よりもさらに、高速化・低損失化とソフトリカバリー化の間のトレードオフを改善することができる。

20

#### 【0070】

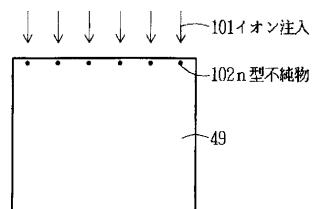

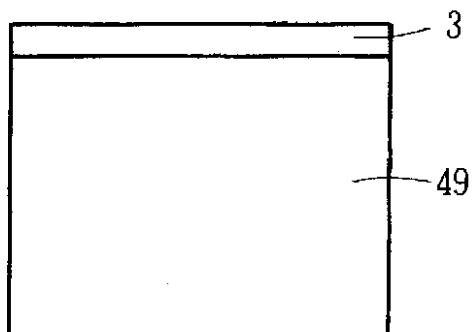

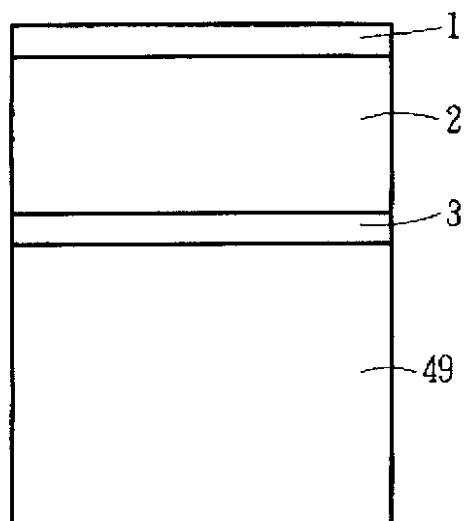

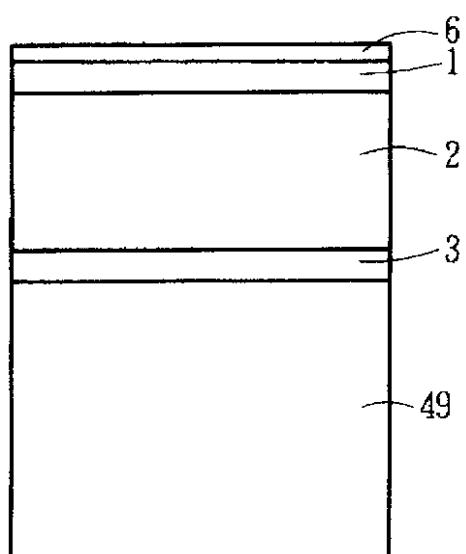

図27から図35は、この発明の第13実施例になる半導体装置の製造方法で、工程順に示した要部製造工程断面図である。この図は、第12実施例の半導体装置(図26)の製造方法である。

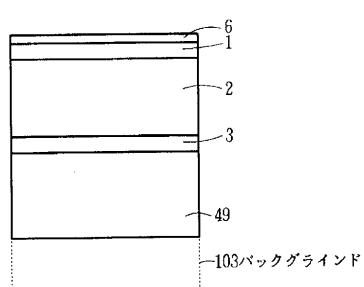

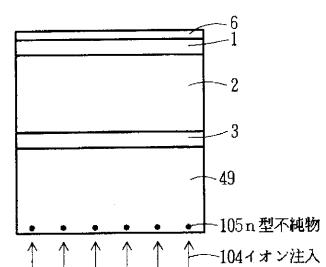

例えば、比抵抗が55-cmのバルクウェハ49(例えば、FZウェハ:フローティング・ゾーン法で製作したウェハ)で、後で、第2のn型ドリフト層4となる)の表面にドーズ量 $1 \times 10^{11} \text{ cm}^{-2}$ から $5 \times 10^{11} \text{ cm}^{-2}$ 、100keVのリンやAsなどのn型不純物102のイオン注入101を行い(図27)、その後、熱処理(800以上)を施し、n<sup>-</sup>バルク(バルクウェハ49)の濃度より濃いn型バッファ層3を形成する。このときのn型バッファ層3の厚さは5μm程度とする(図28)。次に、リンを混入し、55-cmで約60μmの膜厚のエピタキシャル成長結晶48(エピタキシャル成長させた単結晶で、後で、第1のn型ドリフト層2となる)を形成する(図29)。その後、表面の鏡面処理等を施し、熱酸化膜を形成して、パターンニング後、イオン注入(ボロンを $1 \times 10^{13} \text{ cm}^{-2}$ で100keV)および熱拡散(1150で3時間)を行い、5μm程度のp型アノード層1を形成する(図30)。その後、Al-Siをスパッタで成膜・パターン形成を行い、アノード電極6を形成する(図31)。さらに図示しない窒化膜などの保護膜を成膜後にバックグラインド103を行い、全体の厚さが120μm程度になるまで行う(図32)。さらにリンなどのn型不純物105のイオン注入104を実施し(図33)、アノード電極6を形成するAl-Si膜の膜質が変質しない温度(例えば、400程度)の低温アニールを行い、不純物濃度が $1 \times 10^{17} \text{ cm}^{-3}$ 以上で、拡散深さが0.5μm程度のn型カソード層5を形成する(図34)。最後に、裏面側のカソード電極7を形成する(図35)。

30

40

#### 【0071】

この製造方法では、FZウェハであるバルクウェハ49の上に、一回のエピタキシャル成長結晶48を形成した半導体基板100を用いることで、製造コストを大幅に低減することができる。

また、この製造方法を第1実施例から第11実施例の半導体装置に適用することで、製造コストの低減効果を付加することができる。図36(a)~(g)は、この発明の第14実施例の半導体装置の製造方法を工程順に示した要部製造工程断面図である。なお、同図の(e)は(d)の断面図における不純物プロファイル図であり、(g)は(f)の断面

50

図における不純物プロファイル図である。

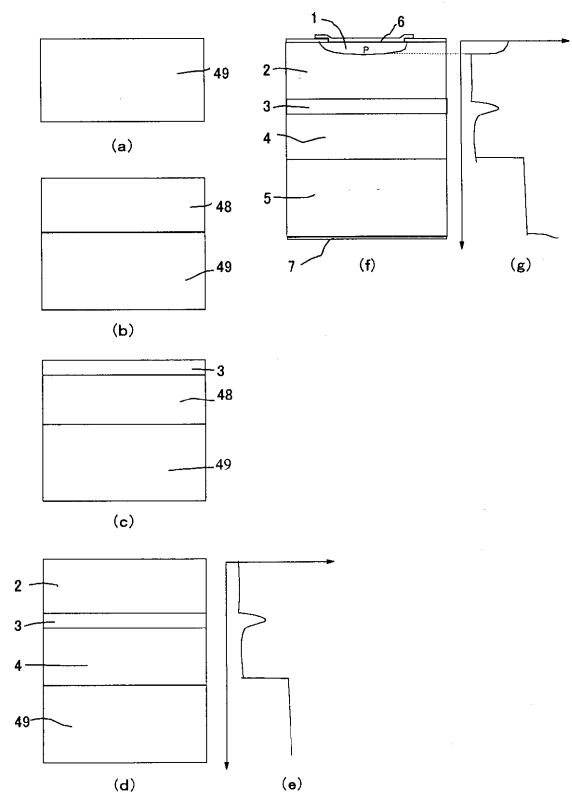

#### 【0072】

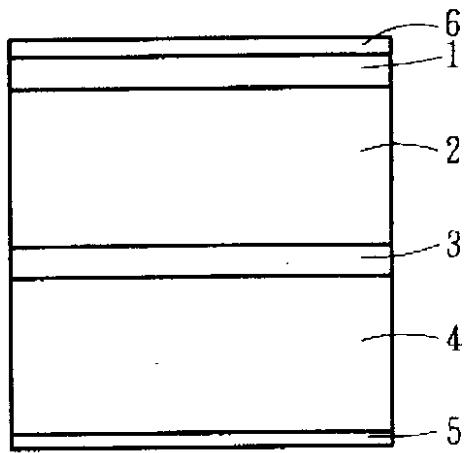

まず、比抵抗が $0.02 - \text{cm}$ 以下のn型バルクウエハ49(同図(a))に $55 - \text{cm}$ 、約 $55 \mu\text{m}$ でn型の第1ドリフト層4となるエピタキシャル成長結晶48をエピタキシャル成長させる(同図(b))。次に厚さが $15 \mu\text{m}$ 以下(好ましくは $5 \mu\text{m}$ )、最大不純物濃度が $5 \times 10^{14} \text{ cm}^{-3}$ となるようにn型バッファ層3をエピタキシャル成長にて形成する(同図(c))。このような、厚さと最大不純物濃度とすることで、耐圧の低下を抑えられる。次にn型の第2ドリフト層2と同じく $55 - \text{cm}$ 、約 $60 \mu\text{m}$ でエピタキシャル成長にて形成する(同図(d))。こうして形成された半導体基板表面の鏡面処理等を施し、熱酸化膜を形成して、パターニング後、イオン注入(ボロンを $1 \times 10^{13} \text{ cm}^{-2}$ の注入量で $100 \text{ keV}$ )および熱拡散( $1150$ で3時間)を行い、 $5 \mu\text{m}$ 程度のp型アノード層1を形成する。その後、白金を約 $900$ で拡散させてからAl-Siをスパッタで成膜・パターン形成を行い、アノード電極6を形成する(同図(f))。なお、裏面のカソード電極7に接するnカソード層5表面を、さらにリンやヒ素等のn型不純物層を浅く( $0.5 \mu\text{m}$ 程度)かつ高濃度(表面濃度 $10^{19} \text{ cm}^{-3}$ )に形成しておけば、半導体基板とカソード電極間の良好なオーミック接触が得られる。なお、(b)～(d)のエピタキシャル成長は、連続して行ってもよいし、エピタキシャル成長工程の間に表面洗浄工程および熱処理等の欠陥回復工程を行ってもよい。また、第2ドリフト層2を第1ドリフト層4よりも高比抵抗(例えば $80 - \text{cm}$ )にすることで、アノード層のpn接合での電界強度を緩和でき、耐圧の低下を抑えることができる。20

#### 【0073】

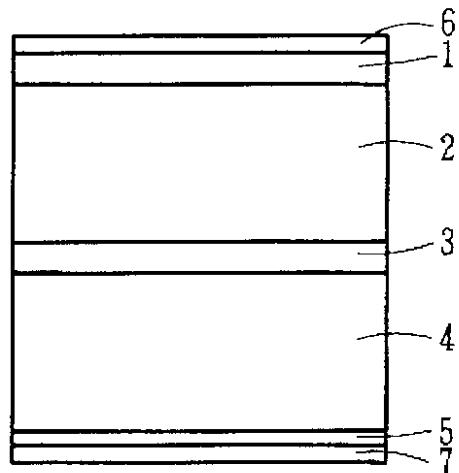

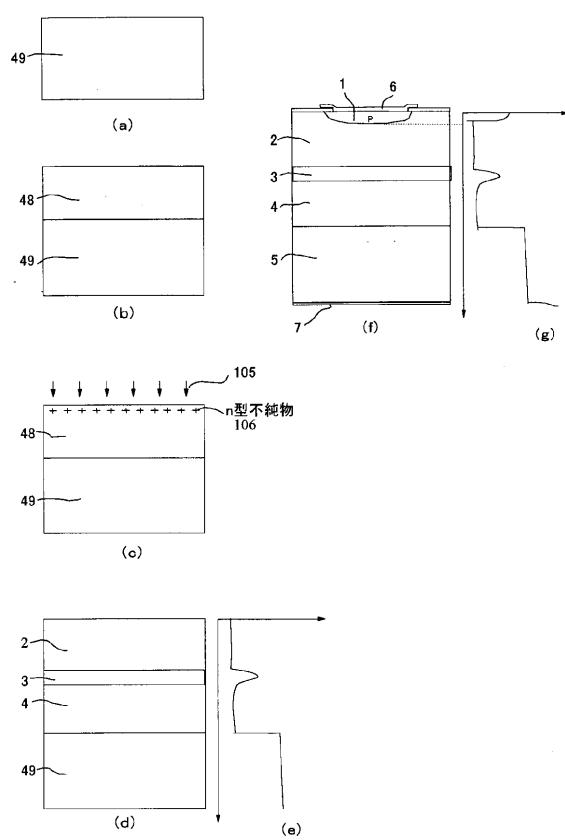

図37(a)～(g)は、この発明の第15実施例の半導体装置の製造方法を工程順に示した要部製造工程断面図である。なお、同図の(e)は(d)の断面図における不純物プロファイル図であり、(g)は(f)の断面図における不純物プロファイル図である。

まず、比抵抗が $0.02 - \text{cm}$ 以下のn型バルクウエハ49(同図(a))にn型の第1ドリフト層4となるエピタキシャル成長結晶48を $55 - \text{cm}$ 、 $60 \mu\text{m}$ にてエピタキシャル成長させる(同図(b))。次にエピタキシャル成長結晶48にn型の不純物、例えばリンを $1 \times 10^{11} \text{ cm}^{-2} \sim 5 \times 10^{11} \text{ cm}^{-2}$ の範囲でイオン注入する(同図(c))。その後、イオン注入時に生じた格子欠陥を回復するために、 $800$ 以上で熱処理を施す。こうしてn型バッファ層3を形成する。なお、n型バッファ層3の形成のためのイオン注入のドーザ量は $5 \times 10^{11} \text{ cm}^{-2}$ 以下としておくことで、耐圧低下を抑えることができる。次に表面洗浄を施し、n型の第2ドリフト層2と同じく $55 - \text{cm}$ 、 $60 \mu\text{m}$ でエピタキシャル成長にて形成する(同図(d))。こうして形成された半導体基板表面の鏡面処理等を施し、熱酸化膜を形成して、パターニング後、イオン注入(ボロンを $1 \times 10^{13} \text{ cm}^{-2}$ の注入量で $100 \text{ keV}$ )および熱拡散( $1150$ で3時間)を行い、 $5 \mu\text{m}$ 程度のp型アノード層1を形成する。その後、白金を約 $900$ で拡散させてからAl-Siをスパッタで成膜・パターン形成を行い、アノード電極6を形成する(同図(f))。なお、裏面のカソード電極7に接するnカソード層5表面を、さらにリンやヒ素等のn型不純物層を浅く( $0.5 \mu\text{m}$ 程度)かつ高濃度(表面濃度 $10^{19} \text{ cm}^{-3}$ )に形成しておけば、半導体基板とカソード電極間の良好なオーミック接触が得られる。また、第2ドリフト層2を第1ドリフト層4よりも高比抵抗(例えば $80 - \text{cm}$ )にすることで、アノード層のpn接合での電界強度を緩和でき、耐圧の低下を抑えることができる。30

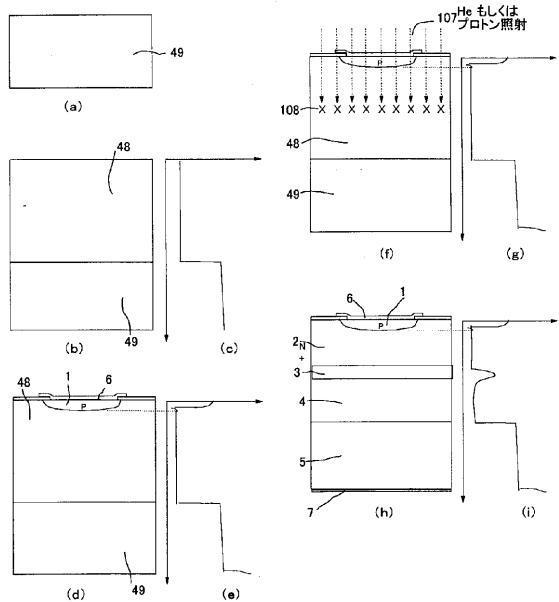

図38(a)～(i)は、この発明の第16実施例の半導体装置の製造方法を工程順に示した要部製造工程断面図である。なお、同図の(e)は(d)の断面図における不純物プロファイル図であり、(g)は(f)の断面図における不純物プロファイル図であり、(i)は(h)の断面図における不純物プロファイル図である。40

#### 【0074】

まず、アンチモン等のn型で低比抵抗( $0.02 - \text{cm}$ )のCZ又はFZによるバルクウエハ49(同図(a))にn型の第1ドリフト層4となるエピタキシャル成長結晶48を $55 - \text{cm}$ 、 $120 \mu\text{m}$ でエピタキシャル成長させる(同図(b))。この時の濃50

度分布は( c )のように一様でよい。こうして形成された半導体基板表面の鏡面処理等を施し、熱酸化膜を形成して、パターニング後、イオン注入(ボロンを $1 \times 10^{13} \text{ cm}^{-2}$ の注入量で $100 \text{ keV}$ )および熱拡散(1150、3時間)を行い、 $5 \mu\text{m}$ 程度のp型アノード層1を形成する。その後、Al-Siをスパッタで成膜・パターン形成を行い、アノード電極6を形成する(同図( d ))。次にアノード側より軽イオン $107$ を照射する。軽イオンは、ヘリウムイオン、プロトン及びデュトロン等が用いられるが、ここではヘリウムイオンを $1 \times 10^{12} \text{ cm}^{-2}$ 、 $24 \text{ MeV}$ で照射した。この軽イオンの照射により所望の深さの位置に局所的に欠陥 $108$ を生成する(同図( f ))。その後、熱処理を400にて1時間施すことによって、欠陥が回復するだけでなく、欠陥の局在している領域のドナー濃度が増加し、所謂軽イオンのドナー化が生じ、n型バッファ層3が形成される(同図( h ))。この製造方法では、( d )の表面形成プロセスの後の工程にて、n型バッファ層3が形成できるので、工程数減少によるコスト削減が可能となる。図39(a)~(k)は、この発明の第17実施例の半導体装置の製造方法を工程順に示した要部製造工程断面図である。なお、同図の( e )は( d )の断面図における不純物プロファイル図であり、( g )は( f )の断面図における不純物プロファイル図であり、( i )は( h )の断面図における不純物プロファイル図であり、( k )は( j )の断面図における不純物プロファイル図である。

10

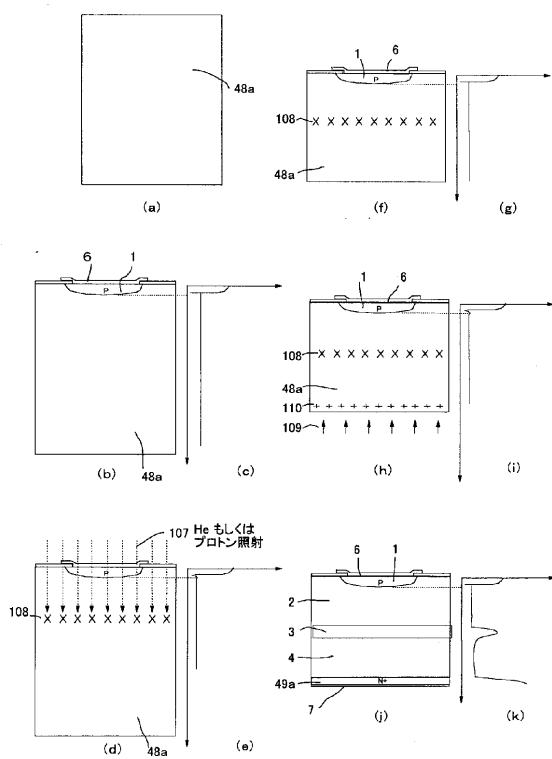

#### 【0075】

まず、リン等のn型で高比抵抗のFZによるバルクウェハ48a(同図( a ))を用いる。この半導体基板表面の鏡面処理等を施し、熱酸化膜を形成して、パターニング後、イオン注入(ボロンを $1 \times 10^{13} \text{ cm}^{-2}$ の注入量で $100 \text{ keV}$ )および熱拡散(1150、3時間)を行い、 $5 \mu\text{m}$ 程度のp型アノード層1を形成する。その後、Al-Siをスパッタで成膜・パターン形成を行い、アノード電極6を形成する(同図( b ))。次にアノード側より軽イオン $107$ を照射する。軽イオンは、ヘリウムイオン、プロトン及びデュトロン等が用いられるが、ここではヘリウムイオンを $1 \times 10^{12} \text{ cm}^{-2}$ 、 $24 \text{ MeV}$ で照射した。この軽イオンの照射により所望の深さの位置に局所的に欠陥 $108$ を生成する(同図( d ))。次に半導体基板のカソードをバックグラインドを行い、全体の厚さが $120 \mu\text{m}$ 程度になるようにする(同図( f ))。さらにリンなどのn型不純物 $110$ のイオン注入 $109$ を行う(同図( h ))。その後、熱処理を400にて1時間施すことによって、高濃度なn型カソード層49aが形成され、かつ欠陥が回復するだけでなく、欠陥の局在している領域のドナー濃度が増加し、所謂軽イオンのドナー化が生じ、n型バッファ層3が形成される(同図( j ))。この製造方法では、( d )の表面形成プロセスの後の工程にて、n型バッファ層3が形成できるので、工程数減少によるコスト削減が可能となる。

20

30

#### 【0076】

##### 【発明の効果】

この発明により、n型ドリフト層内に、所定の位置で所定の厚みのn型バッファ層を形成することで、n型ドリフト層を薄くしても、ソフトリカバリー化することができ、かつ耐圧を確保しながら、高速化・低損失化とソフトリカバリー化の間のトレードオフを改善することができる。

40

#### 【0077】

また、ソフトリカバリー化を図ることで、放射電磁ノイズが発生し難い半導体装置にすることができる。

さらに、バルクウェハ(例えば、FZウェハ)を用い、エピタキシャル成長の回数を一回とすることで、低コストの半導体装置を製造することができる。

参考文献[1] B.J.Baliga, "The Pinch Rectifier," IEEE Electron. Dev. Lett., ED-5, pp194, 1984.[2] M. Mori, et. al., "A Novel Soft and Fast Recovery Diode (SFD) with Thin P-layer Formed by Al-Si Electrode," Proceedings of ISPSD'91, pp113-117, 1991.[3] M. Nemoto, et. al., "An Advanced FWD Design Concept with Superior Soft Reverse Recovery Characteristics," Proceedings of ISPSD2000, pp119-122, 2000.[4] 50

] B.J.Baliga, "Power Semiconductor Devices," PWS Publishing Company, 1996.

**【図面の簡単な説明】**

**【図 1】**この発明の第 1 実施例となる半導体装置の要部断面図

**【図 2】**本発明の p i n ダイオード(本発明品)と、従来の p i n ダイオード(従来品)との室温における逆回復波形を示す図

**【図 3】**図 2 の逆回復動作において、本発明品の逆回復時におけるキャリア濃度の変化をデバイスシミュレーションにより計算したもので、(a)は電子濃度、(b)は正孔濃度を示す図

**【図 4】**図 2 の逆回復動作において、 $115 \mu m$ (B)の従来品における逆回復時のキャリア濃度の変化をデバイスシミュレーションにより計算したもので、(a)は電子濃度、(b)は正孔濃度を示す図

**【図 5】**本発明品(A)において、p型アノード層とn型ドリフト層のp n 接合からn型バッファ層までの最短距離X 1をパラメータとした逆回復電圧・電流波形の比較図

**【図 6】**

距離指標 L を基準にし、p n 接合からn型バッファ層までの最短距離 X 1 を変化させたときのソフトリカバリーの度合いの変化を示した図

**【図 7】**

$Y_1 / W$ の値と素子耐圧  $BV$  の関係を示した図

**【図 8】**

$Y_1 / W$ が等しい本発明品( $Y_1 / W = 1$ )と従来品における、逆バイアス電圧を印加したときの電界強度分布図

**【図 9】**図 1 の不純物プロファイルを示す図

**【図 10】**この発明の第 2 実施例となる半導体装置の要部断面図

**【図 11】**この発明の第 3 実施例の半導体装置であり、(a)は要部断面図、(b)は不純物プロイフィル図

**【図 12】**この発明の第 4 実施例の半導体装置であり、(a)は要部断面図、(b)は不純物プロフィル図

**【図 13】**図 10 の n 型バッファ層の形状を説明する半導体装置の斜視図で、(a)はドット(島状)の場合、(b)はストライプの場合の図

**【図 14】**この発明の第 5 実施例で、MPS 構造のダイオードのドリフト層に第 1 実施例の n 型バッファ層を適用した半導体装置の要部斜視図であり、(a)は MPS 構造がドットの場合、(b)は MPS 構造がストライプの場合の図

**【図 15】**この発明の第 6 実施例で、MPS 構造のダイオードのドリフト層に第 2 実施例のドット状の n 型バッファ層を適用した半導体装置の要部斜視図であり、(a)は MPS 構造がドットの場合、(b)は MPS 構造がストライプの場合の図

**【図 16】**この発明の第 7 実施例で、MPS 構造のダイオードのドリフト層に第 2 実施例のストライプ状の n 型バッファ層を適用した半導体装置の要部斜視図であり、MPS 構造がドットの場合の図

**【図 17】**この発明の第 7 実施例で、MPS 構造のダイオードのドリフト層に第 2 実施例のストライプ状の n 型バッファ層を適用した半導体装置の要部斜視図であり、n 型バッファ層のストライプと MPS 構造のストライプが平行する場合の図

**【図 18】**この発明の第 7 実施例で、MPS 構造のダイオードのドリフト層に第 2 実施例のストライプ状の n 型バッファ層を適用した半導体装置の要部斜視図であり、n 型バッファ層のストライプと MPS 構造のストライプが直交する場合の図

**【図 19】**この発明の第 8 実施例で、SFD 構造のダイオードのドリフト層に第 1 実施例の n 型バッファ層を適用した半導体装置の要部斜視図であり、(a)は SFD 構造がドットの場合、(b)は SFD 構造がストライプの場合の図

**【図 20】**この発明の第 9 実施例で、SFD 構造のダイオードのドリフト層に第 2 実施例のドット状の n 型バッファ層を適用した半導体装置の要部斜視図であり、(a)は SFD 構造がドットの場合、(b)は SFD 構造がストライプの場合の図

10

20

30

40

50

【図21】この発明の第10実施例で、SFD構造のダイオードのドリフト層に第2実施例のストライプ状のn型バッファ層を適用した半導体装置の要部斜視図であり、SFD構造がドットの場合の図

【図22】この発明の第10実施例で、SFD構造のダイオードのドリフト層に第2実施例のストライプ状のn型バッファ層を適用した半導体装置の要部斜視図であり、n型バッファ層のストライプとSFD構造のストライプが平行する場合の図

【図23】この発明の第10実施例で、SFD構造のダイオードのドリフト層に第2実施例のストライプ状のn型バッファ層を適用した半導体装置の要部斜視図であり、n型バッファ層のストライプとSFD構造のストライプが直交する場合の図

【図24】この発明の第11実施例で、n型バッファ層をトレンチ溝の底部に形成した半導体装置であり、(a)はアノード側にトレンチを形成した場合、(b)はカソード側にトレンチを形成した場合の図 10

【図25】従来のpinダイオードの要部断面図

【図26】この発明の第12実施例となる半導体装置の要部断面図

【図27】この発明の第13実施例となる半導体装置の要部製造工程断面図

【図28】図27に続く、この発明の第13実施例となる半導体装置の要部製造工程断面図

【図29】図28に続く、この発明の第13実施例となる半導体装置の要部製造工程断面図

【図30】図29に続く、この発明の第13実施例となる半導体装置の要部製造工程断面図 20

【図31】図30に続く、この発明の第13実施例となる半導体装置の要部製造工程断面図

【図32】図31に続く、この発明の第13実施例となる半導体装置の要部製造工程断面図

【図33】図32に続く、この発明の第13実施例となる半導体装置の要部製造工程断面図

【図34】図33に続く、この発明の第13実施例となる半導体装置の要部製造工程断面図

【図35】図34に続く、この発明の第13実施例となる半導体装置の要部製造工程断面図 30

【図36】この発明の第14実施例となる半導体装置の要部製造工程を示す図であり、(a)～(d)、(f)は各工程の断面図であり、(e)は(d)の断面図での不純物プロファイル図であり、(g)は(f)の断面図での不純物プロファイル図

【図37】この発明の第15実施例となる半導体装置の要部製造工程を示す図であり、(a)～(d)、(f)は各工程での断面図であり、(e)は(d)の断面図での不純物プロファイル図であり、(g)は(f)の断面図での不純物プロファイル図

【図38】この発明の第16実施例となる半導体装置の要部製造工程を示す図であり、(a)、(b)、(d)、(f)、(h)は各工程での断面図であり、(c)は(b)の断面図での不純物プロファイル図であり、(e)は(d)の断面図での不純物プロファイル図であり、(g)は(f)の断面図での不純物プロファイル図であり、(i)は(h)の断面図での不純物プロファイル図 40

【図39】この発明の第17実施例となる半導体装置の要部製造工程を示す図であり、(a)、(b)、(d)、(f)、(h)、(j)は各工程での断面図であり、(c)は(b)の断面図での不純物プロファイル図であり、(e)は(d)の断面図での不純物プロファイル図であり、(g)は(f)の断面図での不純物プロファイル図であり、(i)は(h)の断面図での不純物プロファイル図であり、(k)は(j)の断面図での不純物プロファイル図

#### 【符号の説明】

- 1 a p型アノード層(ドット)

1 b p型アノード層(ストライプ)

1 c p型アノード層(薄層)

2 第1のn型ドリフト層

3 n型バッファ層

3 a n型バッファ層(ドット)

3 b n型バッファ層(ストライプ)

4 第2のn型ドリフト層

5 n型カソード層

6 アノード電極

7 カソード電極

8 n型ドリフト層

9 トレンチ

3 1 n型バッファ層(高濃度)

3 2 n型バッファ層(低濃度)

4 8 エピタキシャル成長結晶

4 9 バルクウェハ

1 0 0 半導体基板

1 0 1、1 0 4、1 0 9 イオン注入

1 0 2、1 0 5、1 1 0 n型不純物

1 0 3 バックグラインド

1 0 7 軽イオン

1 0 8 欠陥

X 1 p n接合からn型バッファ層までの最短距離

Y 1 n型バッファ層の幅

A アノード端子

K カソード端子

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図12】

【図11】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図27】

【図26】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図3-4】

【図3-5】

【図3-6】

【図3-7】

【図38】

【図39】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 21/265

Q

H 0 1 L 29/91

B

審査官 國島 明弘

(56)参考文献 特開2000-223720(JP,A)

特開昭58-216473(JP,A)

特開2000-323488(JP,A)

特開昭62-194682(JP,A)

特開平02-180015(JP,A)

特開昭55-018073(JP,A)

特開平04-252078(JP,A)

特開平04-262579(JP,A)

特開平05-102161(JP,A)

特開平08-125200(JP,A)

特開平09-219511(JP,A)

特開2002-246597(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/861

H01L 21/265

H01L 21/329

H01L 29/47

H01L 29/872