(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5401453号

(P5401453)

(45) 発行日 平成26年1月29日(2014.1.29)

(24) 登録日 平成25年11月1日(2013.11.1)

(51) Int.Cl.

F 1

|             |             |                  |      |      |      |

|-------------|-------------|------------------|------|------|------|

| <b>H03K</b> | <b>5/00</b> | <b>(2006.01)</b> | H03K | 5/00 | K    |

| <b>H03K</b> | <b>5/15</b> | <b>(2006.01)</b> | H03K | 5/15 | P    |

| <b>H03K</b> | <b>5/19</b> | <b>(2006.01)</b> | H03K | 5/19 | T    |

| <b>G06F</b> | <b>1/04</b> | <b>(2006.01)</b> | G06F | 1/04 | 301Z |

請求項の数 18 (全 14 頁)

(21) 出願番号 特願2010-514118 (P2010-514118)

(86) (22) 出願日 平成20年6月30日 (2008.6.30)

(65) 公表番号 特表2010-532124 (P2010-532124A)

(43) 公表日 平成22年9月30日 (2010.9.30)

(86) 國際出願番号 PCT/GB2008/002265

(87) 國際公開番号 WO2009/004330

(87) 國際公開日 平成21年1月8日 (2009.1.8)

審査請求日 平成23年6月28日 (2011.6.28)

(31) 優先権主張番号 0712788.9

(32) 優先日 平成19年6月29日 (2007.6.29)

(33) 優先権主張国 英国(GB)

(73) 特許権者 501176037

イマジネイション テクノロジーズ リミテッド

イギリス ハートフォードシャー ダブリューディー4 8エルゼット キングス

ラングリー ホーム パーク エステイト

(番地なし)

(74) 代理人 100092093

弁理士 辻居 幸一

(74) 代理人 100082005

弁理士 熊倉 賢男

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100086771

弁理士 西島 孝喜

最終頁に続く

(54) 【発明の名称】半導体デバイスのためのクロック周波数調整

## (57) 【特許請求の範囲】

## 【請求項1】

異なる平均クロック周波数を要求するデータ処理モジュール(2、4、6)をクロック制御し、かつ、前記モジュールにおいてデータを転送するための方法であって、

共通クロック信号を各データ処理モジュールに関連付けられた各クロックゲーティング回路に供給する段階と、

前記共通クロック信号から前記関連付けられたクロックゲーティング回路(22、25)に供給されるクロックパルスを、各データ処理モジュールにより要求されるクロッキング周波数の一つに従って削除する段階と、

データが転送されるべきデータ処理モジュールにおいてハンドシェイク動作を実行する段階と、

データ転送が実行されるべき時に、データが転送されるべき前記データ処理モジュールにクロックパルスを適用する段階と、

データが転送されるべき前記データ処理モジュールに適用されたクロックパルスに適切なパターンが存在する場合においてのみ、データ転送が生じるように、前記ハンドシェイク動作を制御する段階と、を含むことを特徴とする方法。

## 【請求項2】

クロックパルスを適用する前記段階が、

データを転送する準備ができていることを示す第1のデータ処理モジュールからの信号を供給する段階と、

10

20

前記第1のデータ処理モジュールからの前記信号に応答して前記データを受信するためには、前記クロックパルスを前記第1のデータ処理モジュール及び第2のデータ処理モジュールに適用する段階と、

を含む、請求項1に記載の方法。

【請求項3】

前記クロックパルスを前記第1のデータ処理モジュール及び前記第2のデータ処理モジュールに適用する段階が、前記削除する段階を制御して、クロックパルスが前記第1のデータ処理モジュール及び前記第2のデータ処理モジュールに対して同期して供給されること、を含む、請求項2に記載の方法。

【請求項4】

前記クロックパルスを適用する段階が、前記削除する段階を阻止することによって、該削除する段階が阻止されている間、すべてのクロックパルスが前記第1のデータ処理モジュール及び前記第2のデータ処理モジュールに渡されるようにすること、を含む、請求項3に記載の方法。

【請求項5】

前記ハンドシェイク動作が、

データを転送する準備ができていることを示す第1のデータ処理モジュールからの第1の信号、及び、データを受信することができるることを示す第2のデータ処理モジュールからの第2の信号を供給することと、

前記第1のデータ処理モジュール及び前記第2のデータ処理モジュールに適用される適切なクロック信号に応答して、当該ハンドシェイク動作において、前記第2のデータ処理モジュールに前記第1の信号を渡し、前記第1のデータ処理モジュールに前記第2の信号を渡すことと、

を含む、請求項1に記載の方法。

【請求項6】

前記クロック信号が、前記第1のデータ処理モジュール及び前記第2のデータ処理モジュールについてのそれぞれのクロックゲーティング回路に適用される同時クロックゲーティング制御信号に応答して、前記第1のデータ処理モジュール及び前記第2のデータ処理モジュールに適用される、請求項5に記載の方法。

【請求項7】

前記クロックゲーティング回路が前記削除する段階を実行する、請求項6に記載の方法。

。

【請求項8】

異なる平均クロック周波数を要求するデータ処理モジュール(4、6)をクロック制御し、かつ、前記データ処理モジュール間においてデータを転送するための装置であって、

共通クロック信号を各データ処理モジュールに関連付けられた各クロックゲーティング回路に供給する手段と、

前記クロックゲーティング回路に供給される前記共通クロック信号から、クロックパルスを、前記データ処理モジュールの各々により要求されるクロッキング周波数に従って削除するように構成された、クロックゲーティング回路(22、25)と、

データ転送が実行されるべき時に、データが転送されるべき前記データ処理モジュールにクロックパルスを適用する手段と、

データが転送されるデータ処理モジュール間においてハンドシェイク動作を実行する手段と、

データが転送されるべき前記データ処理モジュールに適用されたクロックパルスに適切なパターンが存在する場合においてのみ、データ転送が生じるように、前記ハンドシェイク動作を制御する手段と、

を具備することを特徴とする装置。

【請求項9】

前記データ処理モジュールにクロックパルスを適用する手段が、

10

20

30

40

50

データを転送する準備ができていることを示す第1のデータ処理モジュールについての信号を供給する手段と、

前記第1のデータ処理モジュールからの前記信号に応答して前記データを受信するために、前記クロックパルスを前記第1のデータ処理モジュール及び第2のデータ処理モジュールに適用する手段と、

を含む、請求項8に記載の装置。

【請求項10】

前記クロックパルスを前記第1のデータ処理モジュール及び前記第2のデータ処理モジ

ュールに適用する手段が、前記削除することを制御することによって、クロックパルスが前記第1のデータ処理モジュール及び前記第2のデータ処理モジュールに対して同期して供給されるようにする、請求項9に記載の装置。 10

【請求項11】

前記クロックパルスを適用する手段が、

前記削除することを阻止することによって、前記削除する手段が阻止されている間、すべてのクロックパルスが前記第1のデータ処理モジュール及び前記第2のデータ処理モジ

ュールに渡されるようにする、請求項10に記載の装置。

【請求項12】

前記ハンドシェイク動作を実行する手段が、

データを転送する準備ができていることを示す第1のデータ処理モジュールからの第1

の信号、及び、データを受信することができることを示す第2のデータ処理モジュールから

の第2の信号を供給する手段と、 20

前記第1のデータ処理モジュール及び前記第2のデータ処理モジュールに適用される適

切なクロック信号に応答して、当該ハンドシェイク動作において、前記第2のデータ処理

モジュールに前記第1の信号を渡し、前記第1のデータ処理モジュールに前記第2の信号

を渡す手段と、

を含む、請求項8に記載の装置。

【請求項13】

クロック信号を前記第1のデータ処理モジュール及び前記第2のデータ処理モジ

ュールに適用する手段が、

前記第1のデータ処理モジュール及び前記第2のデータ処理モジ

ュールについてのそれ

ぞのゲーティング回路に適用される同時ゲーティング制御信号に応答して、前記クロック

信号を前記第1のデータ処理モジ

ュール及び前記第2のデータ処理モジ

ュールに適用する、請求項11に記載の装置。 30

【請求項14】

前記削除する手段が前記クロックゲーティング回路を含む、請求項13に記載の装置。

【請求項15】

異なる平均クロック周波数を要求する複数のデータ処理モジ

ュールをクロック制御し、

かつ、前記データ処理モジ

ュール間ににおいてデータを転送するための装置であって、

前記データ処理モジ

ュール毎のクロック削除回路ユニットとクロックゲーティングユニ

ットであり、各クロック削除回路ユニットと各クロックゲーティングユニットが、共通の

クロック信号を受信し、各クロック削除回路ユニットが、該クロック削除回路ユニットに

関係する前記データ処理モジ

ュールのクロック制御信号を受信する、クロック削除回路ユニットとクロックゲーティングユニットと、 40

各クロック削除制御ユニットと各クロックゲーティングユニットとの間のゲートであつ

て、前記ゲートが、前記クロック削除制御ユニットからの出力と、データを第2のデータ

処理モジ

ュールに転送する準備が出来ている第1のデータ処理モジ

ュールからのクロック強制信号とを受信し、前記クロック強制信号が、各ゲートの前記出力をイネ

ブルにし、前記クロックゲーティングユニットが、前記ゲートの出力を受信し、前記出力

がイネーブルの場合に、クロックゲーティングが、前記共通クロック信号から受信された

クロック信号を対応する前記データ処理モジ

ュールに渡す、前記ゲートと、 50

前記クロック強制信号が各ゲートに存在する状態で、前記第1のデータ処理モジュール及び第2のデータ処理モジュールは同期してクロックされ、前記データが前記第1のデータ処理モジュールから前記第2のデータ処理モジュールへ転送される、装置。

【請求項16】

異なる平均クロック周波数を要求する複数のデータ処理モジュールをクロック制御し、かつ、前記データ処理モジュール間ににおいてデータを転送するための方法であって、

前記データ処理モジュール毎のクロック削除回路ユニットとクロックゲーティングユニットに、共通クロック信号を提供する段階と、

関係する前記データ処理モジュールに対する各クロック削除制御ユニットにクロック制御信号を提供する段階と、

前記クロック削除制御ユニットからの出力と、第2のデータ処理モジュールにデータを転送する準備が出来ている第1のデータ処理モジュールからのクロック強制信号とをゲートに提供し、前記クロック強制信号が各ゲートの出力がイネーブルになるようにする段階と、そして、

前記ゲートの前記出力を前記クロックゲーティングユニットで受信し、前記出力がイネーブルになると、前記クロックゲーティングユニットが、前記共通クロック信号から受信されるクロック信号を前記関係するデータ処理モジュールに渡す段階と、を含み

各ゲートへの前記クロック信号が存在すると、前記第1のデータ処理モジール及び前記第2のデータ処理モジールが同時にクロックされ、前記データは前記第1のデータ処理モジールから前記第2のデータ処理モジールへ転送される、前記方法。

10

20

【請求項17】

異なる平均クロック周波数を要求するデータ処理モジュールをクロック制御し、かつ、前記モジール間ににおいてデータを転送するための装置であって、

前記データ処理モジール毎のクロック削除回路ユニットとクロックゲーティングユニットであり、各クロック削除回路ユニットと各クロックゲーティングユニットが、共通クロック信号を受信し、各クロック削除回路ユニットが、関係する前記データ処理モジールのクロック制御信号を受信する、クロック削除回路ユニットとクロックゲーティングユニットと、

各クロック削除制御ユニットの出力を受信する第1のゲーティング構成であって、クロック削除制御ユニットの各々から同時発生したイネーブル信号に応答して、前記第1のデータ処理モジールと第2のデータ処理モジールの間の第2のゲーティング構成にイネーブル信号の各々を提供する第1のゲーティング構成であり、前記第2のゲーティング構成が、

30

前記第1のモジールから、データを転送することが可能であることを示す有効信号を受信し、クロック削除制御ユニットが前記イネーブル信号の各々を対応するクロックゲーティングユニットに与え、クロックパルスが前記第1のデータ処理モジール及び第2のデータ処理モジールに渡されることを可能にする、第1ゲートと、

前記第2のデータ処理モジールから、該第2のデータ処理モジールがデータを受信することを示すイネーブル信号を受信し、且つ前記第1のゲーティング構成からイネーブル信号を受信して、その出力に、第2のモジールがデータを受信することができることを示すイネーブル信号を提供する、第2のゲートを含み、

40

もし第1のデータ処理モジールが第1のゲートに前記有効信号を発生し、第2のデータ処理モジールが第2のゲートに前記イネーブル信号を発生する場合、前記有効信号及び前記イネーブル信号が、前記第1のデータ処理モジール及び前記第2のデータ処理モジールにそれぞれ渡され、

関係するクロック削除制御ユニットがイネーブル信号を関係するクロックゲーティングユニット提供することが可能であることを示すイネーブル信号を、前記第1ゲーティング構成が提供する時に、有効信号及びイネーブル信号がそれぞれ第1のデータ処理モジール及び第2のデータ処理モジールに渡されることを特徴とする装置。

【請求項18】

50

異なる平均クロック周波数を要求する複数のデータ処理モジュールをクロック制御し、かつ、前記データ処理モジュール間においてデータを転送するための方法であって、

前記データ処理モジュール毎のクロックゲーティングユニットとクロック削除回路ユニットに、共通クロック信号を提供する段階と、

関係する前記データ処理モジュールに関係する各クロック削除制御ユニットに、クロック制御信号を提供する段階と、

各クロック削除制御ユニットの出力を第1のゲーティング構成により受信する段階と、

前記第1のゲーティング構成が、各クロック削除制御ユニットからのイネーブル信号の各々に同時に応答して、第1のデータ処理モジュールと第2のデータ処理モジュールとの間の第2のゲーティング構成にイネーブル信号を提供する段階と、

前記第2のゲーティング構成内の第1のゲートで、データを転送することが可能であることを示す有効信号を第1のデータ処理モジュールから受信する段階と、

クロック削除制御ユニットの各々が前記イネーブル信号の各々を関係するクロックゲーティングユニットに提供し、クロックパルスが前記第1のモジュール及び前記第2のモジュールに渡されることを可能にすることを示す、前記第1のゲーティング構成からのイネーブル信号を前記第2のゲーティング構成内の前記第1のゲートで受信する、段階と、

前記第2のゲーティング構成内の第2ゲートで、前記第2のデータ処理モジュールがデータを受信することが可能であることを示すイネーブル信号を第2のデータ処理モジュールから受信する段階と、

前記第2のゲーティング構成内の第2のゲートで、前記第1のゲーティング構成からの前記イネーブル信号を受信する段階と、

前記第2のデータ処理モジュールがデータを受信することが可能であることを示すイネーブル信号を、前記第2のゲートの出力で前記第1のデータ処理モジュールに提供する段階と、を有し、

前記第1のデータ処理モジュールが前記第1のゲートに有効信号を提供し、関係するクロック削除制御ユニットが関係するクロックゲーティングユニットにイネーブル信号を提供することを示すイネーブル信号を前記第2のデータ処理モジュールが前記第2のゲートに提供するときに、前記有効信号及び前記イネーブル信号が、それぞれ、第1及び第2のデータ処理モジュールに渡される、方法。

【発明の詳細な説明】

30

【技術分野】

【0001】

本発明は、半導体デバイスのためのクロック周波数調整に関し、より具体的には、異なる速度でクロック制御される複数のモジュールに関し、最も典型的にはシステム・オン・チップ（S o C）上に設けられた多重処理要素を含む半導体デバイスのためのクロック周波数の調整に関する。

【背景技術】

【0002】

半導体デバイスがますます小型化するのに伴い、システム・オン・チップ・デバイスは、ますます多くの異なる処理要素を同じチップ上に統合して製造されるようになっている。これらの処理要素は、以前は、別々の半導体デバイスとして与えられていた。

【0003】

半導体デバイスは、クロック信号に応答してその機能を実行し、このクロック信号は、デバイスへの1つ又はそれ以上の入力で供給され、分割されて、種々の処理要素に内部で分散される。異なる処理要素が同じシステムの部分を形成し、信号がそれらの間で転送される場合、共通クロックが通常用いられる。種々の処理要素が異なるクロック周波数要件を有する場合には、それらのモジュール間でデータがどのように転送されるべきかについて、いくつかの検討が必要になる。モジュールが、互いに対して整数のクロック比でクロック制御される場合、データ転送は、単純なままにしておくことができる。しかしながら、任意のクロック比が要求される場合には、より費用のかかる複雑な同期化が必要になり

40

50

10

、これはデータ転送の際の待ち時間の増加という不利益をもたらす可能性があることが分かる。

【0004】

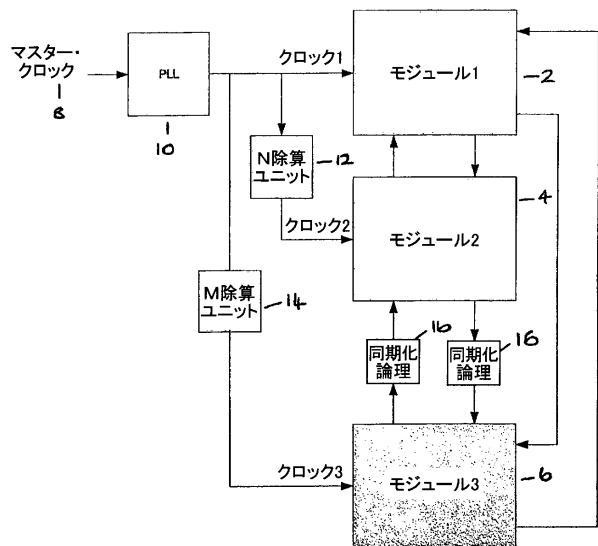

典型的な例示的S o Cデバイスを図1に示す。これは、複数のモジュール2、4及び6を含む。これらは、クロックによって駆動されるS o Cが必要とする、中央処理装置、コプロセッサ、インターフェース、調停ユニット、又はその他の回路の任意の組み合わせとすることもできる。

【0005】

マスター・クロック信号8が、位相ロック・ループ(PLL)10に供給される。モジュール1は、PLL10からクロック1としてクロック信号を取得し、このクロッキング速度でその機能を実行する。

10

【0006】

モジュール2及びモジュール3は、モジュール1に供給されるクロック1の周波数ほど高速で動作する必要はない。したがって、モジュール2へのクロック信号(クロック2)は、N除算ユニット12を通り、モジュール3へのクロック入力(クロック3)は、M除算ユニット14を通る。この場合、N及びMは整数の量である。モジュール2及びモジュール3を低速でクロック制御することにより、これらのモジュールによる電力消費が最小になる。

【0007】

M及びNが単純な整数比に保たれ、3つクロック全てが注意深く同期されれば、モジュール間のデータ転送は、比較的単純なままにしておくことができる事が理解されるであろう。例えば、モジュール1は、Nクロック・サイクル毎においてのみ、モジュール2への出力を更新し、モジュール2からの入力を読み取るように構成することができる。同様に、モジュール1は、Mクロック・サイクル毎に1回のみ、モジュール3にデータを転送し、モジュール3からの入力を読み取る。

20

【0008】

M及びNの他の比率(即ち、非整数値)を用いる場合、モジュール間のデータ転送は、より複雑になる可能性があり、先入れ先出しバッファ(FIFO)、又は、図1においてモジュール2とモジュール3との間に示されるような何らかの特別な同期化論理16を挿入することが必要となり得る。

30

【発明の概要】

【発明が解決しようとする課題】

【0009】

いくつかの処理システムは、動的に変化する処理要件を有する。したがって、図1のような回路は、モジュール2がどのような処理も実行する前に、モジュール1を用いてかなりの量の処理を実行することができる。モジュール2が、モジュール1と同じ速度でクロック制御された場合には、プロセスの第1段階で、モジュール2による無用な電力消費がある。モジュール2がより低いクロック周波数で動作される場合には、プロセスの第2の部分は、第1の部分よりも低速で実行される。クロック速度の動的変動は、こうした状況で最適な処理速度を与えることが望ましいが、とりわけ、異なるクロック周波数で動作しているモジュール間でデータを転送する要件がある場合には、実現するのは困難である。

40

【課題を解決するための手段】

【0010】

本発明の好ましい実施形態は、どのようなモジュールの実効クロック速度も微調整することができるシステムを提供する。これは、S o C内の各モジュールに、同期されたクロック信号を供給することによって実現され、各クロック信号は同じ基本速度で流れている。モジュールのためのクロッキング速度を落とすために、クロック・ゲーティング・セルが、クロック入力ラインに設けられる。これは、明らかに低いクロック速度又は可変クロック速度を実現するために、要求されないクロック・パルスを削除するようにクロック・

50

ゲーティング・セルを制御するクロック削除制御ユニットの制御下にある。

【0011】

好ましくは、クロック削除制御ユニットは、設定された期間内で、どのような任意の数のクロック・パルスもマスター・クロック信号から削除して、要求された実効クロック周波数を実現するように設置することができる。さらに、クロック削除制御ユニットは、処理要素又はモジュール上で流れるアルゴリズムによる要件に応じて、実効クロック周波数を調節するように修正することができる。この制御は、レジスタ設定によるものとすることができる、場合によっては、SoC上で稼働するソフトウェアによって修正可能であり、又は代替的には、クロック・パルスが供給されるモジュール内部で流れるアルゴリズム内で生成されたメトリックによって最適値に動的に設定することができる。

10

【0012】

SoC内の各モジュールは、それ専用のクロック削除制御ユニット及びクロック・ゲーティング・セルを有することができ、各々は、異なるクロッキング速度で稼働させることができる。転送されるデータがあるときに、クロック・パルスを送信側モジュール及び受信側モジュールに強制的に与えるか、又は、既存の2ウェイ・ハンドシェイクを利用して、適切なクロック・パルスが送信側モジュール及び受信側モジュールの両方に生じるまで、データの転送を意図的にストールするかのいずれかによって、異なるクロッキング速度で稼働するモジュール間での安全なデータ転送が行われる。これらのことの組み合わせも用いることができる。

20

【図面の簡単な説明】

【0013】

【図1】上記で参照された従来技術のシステムである。

【図2】本発明の実施形態による、クロック・ゲーティング・セル及びクロック削除制御ユニットを示す。

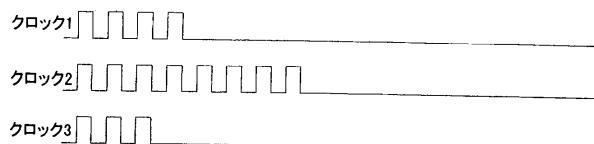

【図3】非ストール（有効のみ）プロトコルのタイミング波形を示す。

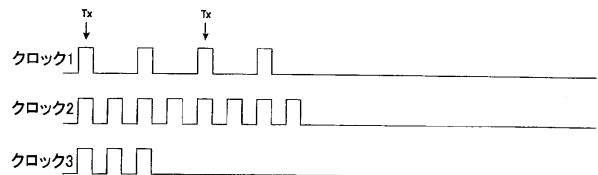

【図4】特有の2ウェイ・ハンドシェイク（有効-イネーブル・プロトコル）を用いるモジュール間のデータ転送のためのタイミング波形を示す。

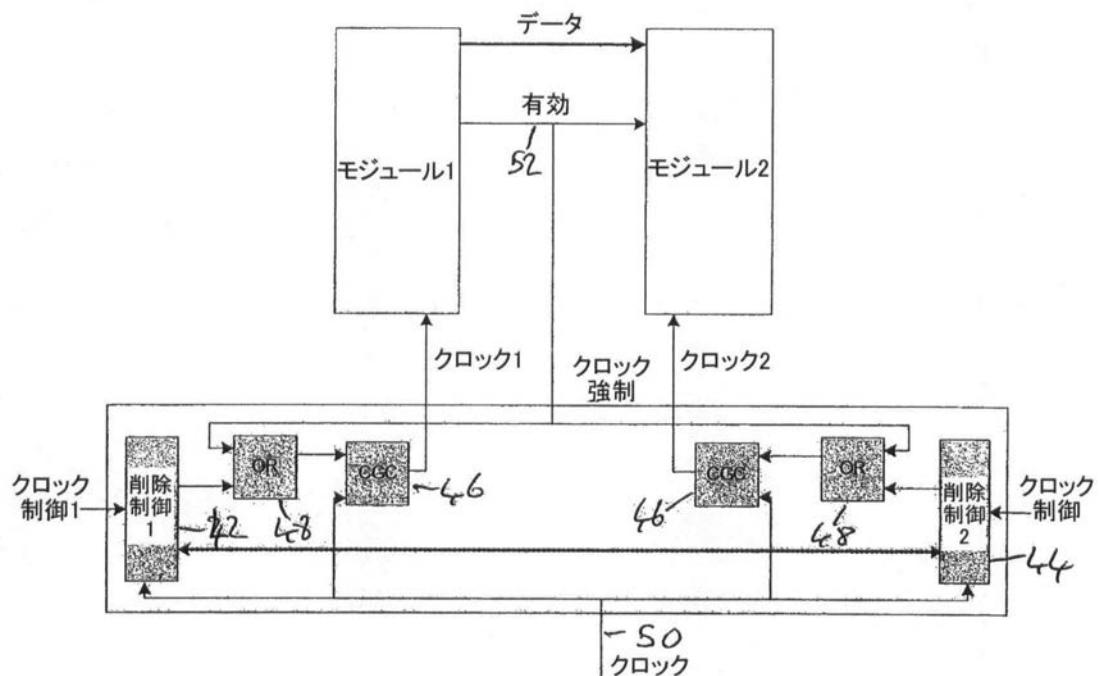

【図5】正確なデータ転送を確保するために、クロック・パルスがモジュールに強制的に与えられた、本発明の実施形態を示す。

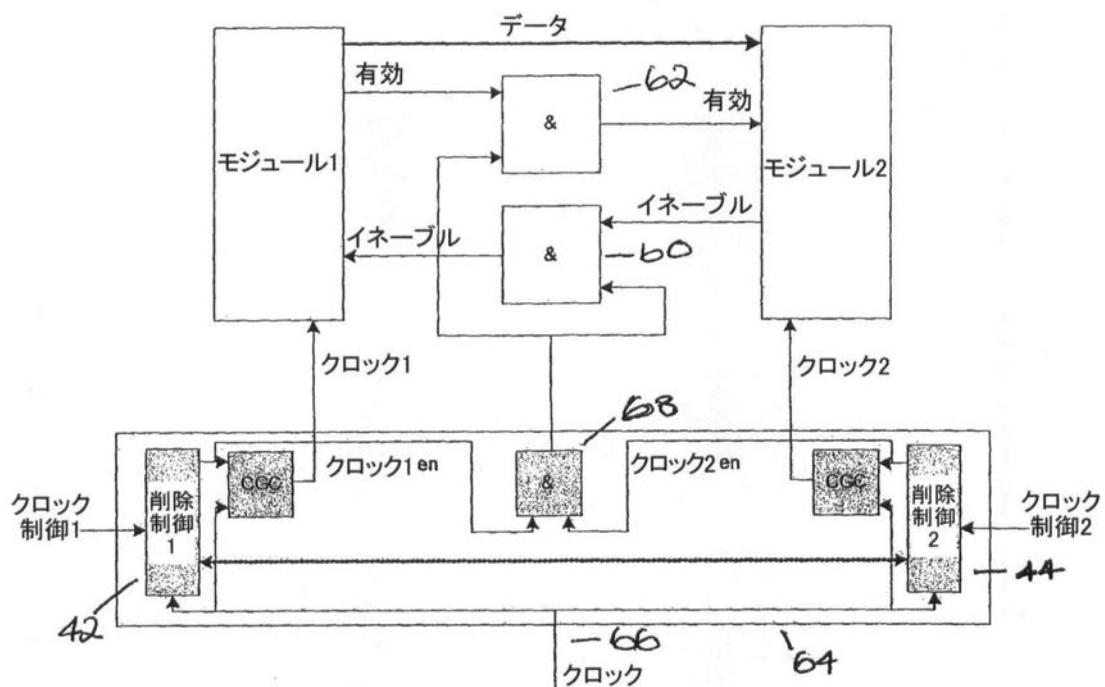

【図6】正確なデータ転送を確保するために、2ウェイ・ハンドシェイク・プロトコルが修正された、本発明の実施形態を示す。

30

【図7】実施形態で用いるためのクロッキング構成の1つの配置を示す。

【図8】図6のモジュール1とモジュール2との間での転送のための最適化されたクロッキング構成を示す。

【発明を実施するための形態】

【0014】

ここで、本発明の実施形態が、添付の図面を参照して、一例としてより詳細に説明されるであろう。

【0015】

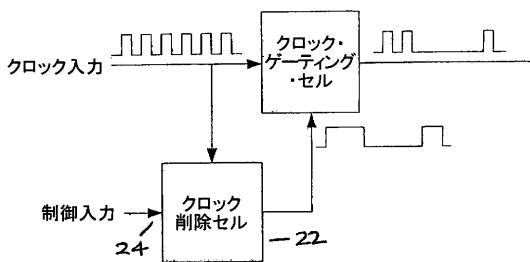

本発明の好ましい実施形態において、図1のN除算ユニット12及びM除算ユニット14は、図2のクロック削除ユニットに置き換える。これは、クロックとモジュールへのクロック入力との間に配置されるクロック・ゲーティング・セル20を含む。このクロック・ゲーティング・セル20はまた、クロック削除制御ユニット22からの入力を受信する。このクロック削除制御ユニット22も、クロック・ゲーティング・セルと同じクロック入力を受信する。さらに、クロック削除制御ユニットは、当該モジュールに与えられるべき、要求されたクロッキング速度に関するデータを含む制御入力24を受信する。制御入力24に応答して、クロック削除制御ユニット22は一連のパルスを生成し、これは、クロック・ゲーティング・セル20に与えられ、これは次いで、クロック・パルスがモジュールにおいて生成されるようにする。

40

【0016】

50

したがって、図2のクロック削除制御ユニットは、設定されたクロック周期内のマスター・クロック信号から、いずれかの任意のクロック・パルスを削除して、いずれかの任意の順序で要求される実効クロック周波数を実現するように設定することができる。さらに、制御入力24は、モジュール上で実行されるアルゴリズムによって必要とされるように、実効クロック周波数を変更するように、いつでも修正することができる。

#### 【0017】

好みの実施形態において、図1のN除算ユニット12及びM除算ユニット14の各々が、図2に示される形式のクロック削除ユニットに置き換えられる。実際は、図1の3つのモジュールの各々にクロック削除ユニットを設け、これにより、各々をさまざまな速度で制御できることを確実にすることが好ましく、それによって、特定の時間に処理を実行することを必要としないいずれのモジュールも、そのクロッキング・パルスをクロック削除ユニットによって除去することができる。

10

#### 【0018】

SOCが動作中であるとき、2つ又はそれ以上のモジュール間でデータを転送することが、時々に必要になるであろう。これが必要である場合は、モジュールが適切な時間にクロック制御されることを確実にすることが必要である。これは、下記を含む多くの方法で実現することができる。すなわち、

1. 転送する有効データがあるときには、適切な時間に、クロック・パルスを両方のモジュールに強制的に与えることによって実現するか、又は、

2. 転送が両方の側で認識される場合、既存の2ウェイ・ハンドシェイク線を利用して、一方のモジュールから他方のモジュールへのデータ・フローを自然に制御することによって実現される。ハンドシェイク信号の使用は、同時クロック・パルスが両方のモジュール上に生じているときに、データだけが流れるのを可能にするように覆される。

20

#### 【0019】

例示のために本明細書で用いられる2ウェイ・ハンドシェイク・プロトコルは、「有効・イネーブル」と名づけられ、これは、同じクロック上の1つのモジュールから次のモジュールへのデータ転送を認識する。

#### 【0020】

異なるクロック上の転送を認識する2ウェイ・ハンドシェイク・プロトコルに対応することも可能である。これらは、データ転送のためのインターフェース・プロトコルを基にして設計された異なる特有の論理を必要とする。

30

#### 【0021】

本発明の実施形態で用いることができるモジュール間でデータを転送する2つの方法の例をここで説明する。特に、異なる実効速度でクロック制御されるモジュール間でデータを転送するための方法を示す。両方の技術は、いずれの数の実効クロック速度で実行されるいずれの数のモジュール間でも、同じSOC上で用いることができる。選択された方法についての最適な選択肢は、1ウェイ又は2ウェイのハンドシェイク・プロトコルが利用可能であるかどうかによって決まる。これはまた、選択されたインターフェースによるデータ転送の予測される特性によっても決まる。

#### 【0022】

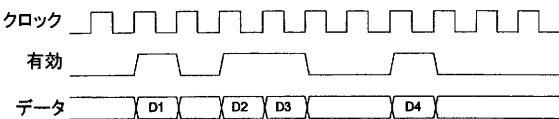

第1の例は、適切なモジュール・インターフェースにおいて用いることができる、非ストール（ここでは、「有効のみ」として知られる）・プロトコルである。データ転送に用いられる信号を図3に示す。図から分かるように、クロック信号が、一番上のラインに示される。二番目のラインは、「有効」というハンドシェイク線を表し、これは、高いときに、「データ」線が転送される値を有することを示す。転送される有効データは、図3においてD1、D2、D3及びD4として示される。

40

#### 【0023】

両方のモジュールが同じクロックによって駆動される場合には、「有効のみ」プロトコルは、問題なく機能する。しかしながら、モジュールが、異なるクロック制御設定の異なる速度で駆動される場合には、有効データが消失するか、又は、有効データの単一の語が

50

多数の語として間違って解釈される可能性がある。こうした出来事を回避するために、有効信号を取得し、それをクロック制御ユニットの各々からのクロック・ゲーティング信号と組み合わせ、転送される有効データがあるときはいつでも、クロック・パルスを各モジュールに強制的に与える。

【0024】

具体的な実施形態が図5に示される。これは、データが転送される準備ができたときに、同時クロック・パルスが、送信側モジュール及び受信側モジュールの両方に強制的に与えられるシステムである。図5は、それぞれのクロック削除回路によって、異なる実効クロック速度でクロック制御することができる2つのモジュールを示す。2つのモジュールは、モジュール1及びモジュール2である。モジュール1は、クロック制御1を受信するクロック削除制御ユニット42を有する。モジュール2は、その制御入力においてクロック制御2を受信するクロック削除制御ユニット44を有する。

10

【0025】

クロック削除制御ユニット42及び44の各々は、それぞれのORゲート48を介して、それぞれのクロック・ゲーティング・セル46に制御信号を供給する。同じクロック信号50が、各々のクロック削除制御ユニット42及び44、並びに2つのクロック・ゲーティング・セル46に供給される。

【0026】

モジュール1は、データをモジュール2に転送しなくてはならない。モジュール1が、そのデータを転送する準備ができたとき、モジュール1は、モジュール2に与えられ、かつ、ORゲート48の各々の第2の入力にも適用される、有効信号52を生成する。これには、各ORゲート48の出力を、クロック削除制御ユニットの出力にかかわりなくイネーブルにするという効果がある。

20

【0027】

したがって、ORゲート48は、それぞれのクロック削除制御ユニット42及び44の出力の有効信号52に応答して、イネーブル信号をそれぞれのクロック・ゲーティング回路46に与え、それぞれのORゲート48の出力がイネーブルにされたときに、クロック信号50が、それぞれのクロック・ゲーティング・セル46を通るようにする。

【0028】

高度な実装は、余分なパルスを後で削除することにより付加的なパルスを明らかにするので、全体のクロック・カウントが、ある期間にわたって必要とする速度と一致する。

30

【0029】

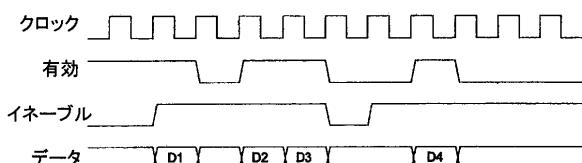

受信側モジュールがデータ転送のストールを可能にするハンドシェイク機構が存在する場合、代替的な機構が用いられ、モジュールが異なる実効速度でクロック制御されるとときに正確なデータ転送を確実にする。説明のために用いられる例示的なプロトコルは、ここでは、2ウェイ・ハンドシェイク・プロトコルである有効-イネーブル転送として知られる。プロトコルは、図4に示される。一番目のラインは、クロック信号を示す。二番目のラインは、送信側モジュールから発信される「有効」信号を示し、データ線上の値が関心あるものであり、受信側モジュールに送信されることを示す。三番目のラインは、受信側モジュールから発信される「イネーブル信号」を示し、モジュールがデータを受信する準備ができていることを示す。有効信号及びイネーブル信号の両方が高いとき、D1、D2、D3、及びD4として図4に示されるデータは、送信側モジュールから受信側モジュールに転送される。特別な処理を行わなければ送信側モジュール及び受信側モジュールが異なる実効クロック速度によってクロック制御された場合、このプロトコルもまた不正確なデータ転送に悩まされる。これを回避するために、ハンドシェイク信号自体を利用して、両方のモジュール上に適切なクロックがある場合、データの転送を試みるだけであることを確実にする。

40

【0030】

システム・オン・チップ内のモジュール間でデータを転送するためのこの代替的な配置の具体的な実施形態を、図6を参照して示す。この形式の配置は、1つの処理要素が、デ

50

ータ転送を行いたいと望む別の処理要素をストールバックすることができる 2 ウェイ・ハンドシェイクをモジュール間で用いる。これには、送信側モジュール及び受信側モジュールの両方に適用される同時クロック・パルスが発生したときのみ、データ転送が可能であることを保証するという効果がある。

【 0 0 3 1 】

この配置において、モジュール 1 は、AND ゲート 6 0 の出力に応答してアサートされるイネーブル入力を有する。これに対応して、モジュール 2 は、AND ゲート 6 2 の出力によってアサートされる有効入力を有する。モジュール 1 へのイネーブル入力は、データをモジュール 2 に送ることを可能にし、モジュール 2 の有効入力は、これがモジュール 1 からデータを受信することを可能にする。

10

【 0 0 3 2 】

AND ゲート 6 0 の第 1 の入力は、データをモジュール 1 から受信する準備ができる状態にあるときに、モジュール 2 によって生成されたイネーブル信号である。AND ゲート 6 2 の第 1 の入力は、データをモジュール 2 に送信するのが可能であるときに生成された、モジュール 1 からの有効出力である。AND ゲート 6 0 及び 6 2 のそれぞれの第 2 の入力は、クロッキング回路 6 4 によって与えられる。

【 0 0 3 3 】

クロッキング回路 6 4 は、クロック入力 6 6 を有する。このクロッキング信号は、図 2 を参照して説明される形式の 2 つのクロック・ゲーティング回路に送られる。モジュール 1 は、そのクロック制御入力においてクロック制御信号 1 を受信するクロック削除制御ユニット 4 2 を含むクロック・ゲーティング・ユニットを有する。この出力及びクロック信号 6 6 は、そのクロック・ゲーティング・セル 4 8 に供給され、これはクロック信号をモジュール 1 に供給する。

20

【 0 0 3 4 】

これに対応して、モジュール 2 に関しては、クロック削除制御ユニット 4 4 は、その制御入力においてクロック制御信号を受信し、出力をそのクロック・ゲーティング・セル 4 8 に供給し、次いで、クロッキング信号をモジュール 2 に供給する。

【 0 0 3 5 】

2 つのクロック削除制御ユニット 4 2 及び 4 4 の出力は、更に別の AND ゲート 6 8 にも供給される。この出力は、2 つの AND ゲート 6 0 及び 6 2 への第 2 の入力を形成する。したがって、2 つのクロック制御信号により、それぞれのクロック削除制御ユニット 4 2 及び 4 4 がイネーブリング・パルスを各々のクロック・ゲーティング・セル 4 8 に供給するときに、AND ゲート 6 8 の出力がアサートされ、これにより、モジュール 1 がその有効出力ライン上に有効信号を生成し、モジュール 2 がそのイネーブル・ライン上にイネーブル信号を生成する場合、即ち、モジュール 1 がデータを送信する準備ができ、モジュール 2 もデータを受信する準備ができたときに、データがモジュール 1 からモジュール 2 に渡されることを可能にする。この場合、データは、それぞれのクロック・ゲーティング・セルによってそれぞれのクロック入力で供給されるクロック信号に応答して、モジュール 1 からモジュール 2 に送られる。

30

【 0 0 3 6 】

この配置は、クロック削除回路がそれらの間に最大数の同時クロック・パルスを有するときに最も効果的に機能し、したがって、一方のモジュールが、他方のモジュールへのデータ転送を待機している間に不必要にストールされる機会が最小になる。図 6 の 2 つのクロック削除制御ユニットの間には点線が示され、これは、何らかの同期化を与え、これにより最大数の同時クロック・パルスを確実にする、2 つのクロック制御入力間のリンクエージを表わす。

40

【 0 0 3 7 】

本発明のこれらの実施形態においては、クロック制御信号がクロック速度の制御を必要としない場合には、一定のものに有線接続されてもよい。代替的に、プロセッサ上で実行されるソフトウェアによってクロック速度を制御できるように、クロック制御信号を接続

50

することもできる。代替的に、クロックが制御されているモジュールによって、又は、実際に他のモジュールのクロッキング速度の制御を担う他のいずれかのモジュールによって、制御信号を動的に調整することもできる。

#### 【0038】

動的な制御の場合、メトリックを用いて、クロック制御されているモジュールがそのリアルタイム要件を満たす際に正確に動作しているかどうか、又は、クロッキング速度に対する何らかの調整を必要とするかどうかを表示することができる。このメトリックは、例えば、適切なFIFO（先入れ先出しバッファ）の完全性、又は、モジュールの働きの過不足の程度についての表示を与えるように構築できる他のハードウェアを用いて、生成することができる。次に、このメトリックをフィードバックし、好適なスケーリング及びオフセットを介してクロック制御信号を直接駆動することができる。10

#### 【0039】

複数のモジュールの各々が、いずれかの所定の期間に、最小可能数のクロック・パルスでクロック制御されることは好ましい。一般に、各モジュールがそのタスクを動作させるためにクロック制御する必要がある最小クロック周波数を計算又は推定することが可能である。クロッキングは、無活動周期及びクロッキングが動作しているシステム内のデータの流れが、これを必要とすることを示す場合には、より高い周波数でのクロッキング周期を有するように、ある期間内で制御することができる。

#### 【0040】

モジュール間の同時発生クロック・パルス数を最大にすることは好ましいので、データは、利用可能になる限り、待機しなければならず、場合によってはシステムの動きを鈍くするよりも、モジュール間で転送される可能性が高い。例えば、システムは、クロック1、クロック2及びクロック3によって駆動される又は共通のマスター・クロックにより駆動される3つのモジュールを有することができる。クロック1、クロック2、及びクロック3に必要な新しいクロック速度は、それぞれ16クロック周期毎に、4、8及び3パルスであると推定することができる。このための可能な構成を、クロック1、クロック2及びクロック3に必要なクロック・パルスと共に、図7に示す。この例では、それぞれの最小クロック・サイクル数について、全てのクロック・パルスが16周期サイクルの初めに生じ、同時発生クロック・パルス数を最大にする。20

#### 【0041】

モジュールがデータを生成又は受信する予測される速度を考慮に入れて、クロッキング・パターンを適切に修正することも望ましい。例えば、モジュール1が、2クロック・パルス毎に平均して1語で、データをモジュール2に送る場合には、モジュール2は、受信する各語を処理するために4クロック・パルスを必要とし、図7に示すクロック・パルスの配置は適切ではない。こうした状況のために、モジュール間のFIFOバッファが、円滑なデータ・フローを維持するために必要とされる。代替的に、図8に示すように、この要件は、波形を異なった配置にすることにより排除することができる。ここでは、クロック1に与えられたクロック・パルスが広がって、モジュール2がモジュール1からデータを受信したときに、モジュール2がこのデータを処理することを可能にする。30

#### 【0042】

図8に示すような特性をもつ波形を生成するために、クロック削除制御ユニットは、特定のサイクルが再開する前に、クロック周期の数に対応するフレーム長で構成する必要がある。また、アクティブなサイクルの数、即ち、クロック・パルスが生成されるフレーム内のクロック周期数、及び出力パルス間のクロック周期数を知ることも必要である。次いで、このことは、そのクロック・パルスを変更して、モジュール間のデータの最適なフローを確実にすることを可能にする。40

【図1】

Figure 1

【図2】

Figure 2

【図3】

Figure 3

【図4】

Figure 4

【図7】

Figure 7

【図8】

Figure 8

【図5】

【図6】

---

フロントページの続き

(74)代理人 100109070

弁理士 須田 洋之

(74)代理人 100109335

弁理士 上杉 浩

(74)代理人 100143823

弁理士 市川 英彦

(72)発明者 ローランド ポール

イギリス エイエル3 5キュージー ハートフォードシャー セント オルバンズ ノーマンディー ロード 17

審査官 石田 勝

(56)参考文献 特開2005-050030(JP, A)

特開2007-140686(JP, A)

米国特許出願公開第2005/0055592(US, A1)

(58)調査した分野(Int.Cl., DB名)

H03K 5/00

G06F 1/04

H03K 5/15

H03K 5/19