(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-275209

(P2007-275209A)

(43) 公開日 平成19年10月25日(2007.10.25)

(51) Int.C1.

**A63F 7/02**

(2006.01)

F 1

A 6 3 F 7/02 3 2 4 C

A 6 3 F 7/02 3 2 6 Z

テーマコード(参考)

2 C 0 8 8

審査請求 未請求 請求項の数 1 O L (全 22 頁)

(21) 出願番号

特願2006-103754 (P2006-103754)

(22) 出願日

平成18年4月5日(2006.4.5.)

(71) 出願人 398057880

株式会社大万

愛知県名古屋市中村区鴨付町1丁目22番地

(72) 発明者 市原 高明

愛知県北名古屋市沖村西ノ川1番地 株式会社大万内

(72) 発明者 中村 昌則

愛知県北名古屋市沖村西ノ川1番地 株式会社大万内

(72) 発明者 奥村 尚之

愛知県北名古屋市沖村西ノ川1番地 株式会社大万内

最終頁に続く

(54) 【発明の名称】遊戯機

## (57) 【要約】

**【課題】** 払出コマンドの信頼性を向上しつつ、主制御基板の負担を軽減する技術を提供する。 **【解決手段】** 主制御基板70は、払出制御基板20に2バイトの払出コマンドを1バイト単位に分割してシリアルで送信する。 扟出制御基板70の払出CPU710は、定時割り込み処理において、払出コマンドを正常に受信したか否か判断し、正常に受信したと判断した場合は、主制御基板20に対して、ACK信号をパラレルで送信する。 **【選択図】** 図3

**【特許請求の範囲】****【請求項 1】**

遊技機であって、遊技の進行を制御する主制御基板と、

前記主制御基板から送信される遊技球または遊技メダルの払い出しに関するコマンドである払出コマンドに基づいて、遊技球または遊技メダルの払い出しを制御する払出制御基板と、

を備え、前記主制御基板は、前記払出制御基板に、電気的ノイズの影響を受けない低速の通信速度で、シリアルでコマンドを送信する主制御基板シリアル送信部と、該主制御基板における汎用パラレルポートのうちの一部のポートである主制御基板パラレル受信ポートと、を備え、前記払出制御基板は、前記主制御基板から、電気的ノイズの影響を受けない低速の通信速度で、シリアルでコマンドを受信する払出制御基板シリアル受信部と、該払出制御基板における汎用パラレルポートのうちの一部のポートである払出制御基板パラレル送信ポートと、定時間割り込み処理を繰り返し実行して、前記払い出しに関する処理を行う払出制御基板中央演算処理装置と、を備え、前記払出制御基板シリアル受信部は、1バイトの記憶容量を有し、前記主制御基板からシリアルで送信されるコマンドをパラレルデータに変換して記憶する受信シフトレジスタと、1バイトの記憶容量を有し、記憶状態がクリアである場合に、前記受信シフトレジスタに記憶されたコマンドを受け取って記憶する受信バッファレジスタと、を備え、前記払出制御基板は、前記払出制御基板中央演算処理装置から出力されるセット信号に応じて、前記受信バッファレジスタをクリアするバッファクリア部を備え、前記払出コマンドは、前記主制御基板シリアル送信部から前記払出制御基板シリアル受信部へシリアルで送信されて前記受信バッファレジスタに記憶され、前記払出制御基板中央演算処理装置は、前記受信バッファレジスタに記憶されている払出コマンドを読み出すと、前記セット信号を前記バッファクリア部に出力し、更に、前記払出コマンドを正常に受信したと判断した場合は、払出コマンド確認信号を、前記払出制御基板パラレル送信ポートを介して出力し、前記払出コマンド確認信号は、前記払出制御基板パラレル送信ポートから前記主制御基板パラレル受信ポートへパラレルで送信されることを特徴とする、遊技機。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、遊技機における、遊技の進行を制御する主制御基板と、遊技球または遊技メダルの払い出しを制御する払出制御基板との間の通信に関する。

**【背景技術】****【0002】**

遊技機において、遊技の進行を制御する主制御基板から、遊技球または遊技メダルの払い出しを制御する払出制御基板には、遊技球等の払い出しに関する払出コマンドが送信されている。遊技機に不正な行為をして遊戯球等の払い出しを行わせようとする者は、該払出コマンドが送信される信号線に不正な加工を施して払出コマンドを変更することにより、不正に遊戯球等を払い出させようとすることがある。従来、主制御基板から払出制御基板にはパラレルで払出コマンドが送信されていた。パラレルでは、例えば8ビットの払出コマンドが同時に送信されるため、所定のタイミングで1ビット分ずつデータを送信するシリアルの通信と比較すると、不正者に払出コマンドを変更される可能性が高かった。よって、主制御基板から払出制御基板への通信の信頼性を向上させ、不正に遊戯球等が払い出されることを抑制するために、主制御基板から払出制御基板への通信はシリアルで行うことが提案されている。

**【0003】**

ところで、遊技機においては、遊技球等とその通路との間の摩擦や、遊技球同士の摩擦や、遊技機と帯電した人体との接触などによって静電気が発生することが多い。払出コマンドが、このような静電気の発生に起因する電気的ノイズの影響で誤信されることを懸念し

10

20

30

40

50

て、払出コマンドをシリアルで送信する場合、払出コマンドの送信速度を低速化する。これにより、主制御基板から払出制御基板へ送信される払出コマンドの信頼性を向上させる。払出コマンドの送信速度は、例えば、1200 b p s (Bit Per Second)とされる。送信速度が1200 b p s であるとすると、2バイトのコマンドを送信するためにかかる時間は約16.7 m s となる。

#### 【0004】

更に、主制御基板から払出制御基板への通信の信頼性を向上させるために、払出コマンドを受信した払出制御基板が、払出コマンドを受信したことを主制御基板に通知する技術も提案されている（例えば、特許文献1）。主制御基板は、払出コマンドを送信した後、払出制御基板から、払出コマンドを受信したことを示す確認信号（アック信号、ACK信号）を受信することにより、払出制御基板が払出コマンドを受信したことを確認することができる。

#### 【0005】

【特許文献1】特開2003-190615号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

上記したように、主制御基板から払出制御基板へ送信される払出コマンドの信頼性を向上するため、シリアルで払出コマンドを送信したり、払出コマンドの送信速度を低速化したり、アック信号を送受信したりしている。しかしながら、そのために、上記したように、払出コマンドの送受信に関する処理速度は低速である。そして、主制御基板は、払出制御基板からアック信号を受信しなければ、払出制御基板との間の通信の信頼性が疑わしいため、払出制御基板に次の払出コマンドを送信しない構成となっている。つまり、アック信号を受信しない間、払出制御基板に送信すべき払出コマンドが主制御基板において記憶されている状態であり、このことが主制御基板の負担となっている。以下、主制御基板の負担について具体的に説明する。

#### 【0007】

主制御基板は、始動口に遊技球が入球すると、乱数を取得して抽選を行ったり、始動口に遊技球が入賞したときに変動中であるときは、取得した乱数を記憶したりするなど、様々な処理を、遊技の進行に応じて実行している。その中で、主制御基板は、始動口、一般入賞口といった幾つかの入賞口に対して個々に予め設定されている賞球数に応じた払出コマンドを、遊技球が1つ入賞口に入賞する度に、払出制御基板に送信する処理を実行しなければならない。特に、大当たり遊技状態になると、大入賞口が開口状態となり、大量の遊技球が大入賞口に入賞する。そのため、始動口や一般入賞口への入賞に応じた払出コマンドに加え、大入賞口へ入賞する大量の遊技球に応じた払出コマンドを次々に払出制御基板に送信する処理を実行しなければならない。このように、主制御基板は、不定期に起きる状態変化に対応した様々な処理を実行しなければならない。それにも関わらず、アック信号を受信せず、払出制御基板が払出コマンドを受信したことが確認できない間は、払出制御基板に送信すべき払出コマンドを記憶しておかなければならない状態であり、このことが主制御基板の負担となっている。

#### 【0008】

これに対し、払出制御基板は、主に、払出コマンドに応じて遊技球等を払い出す処理を行うだけのものである。よって、主制御基板の負担を減らすために、払出コマンドは、払出制御基板に早期に送信することが望ましい。

#### 【0009】

本発明は、上記した問題点を解決するためになされたものであり、払出コマンドの信頼性を向上しつつ、主制御基板の負担を軽減する技術を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

上記した課題を解決するため、本発明の遊技機は、遊技機であって、遊技の進行を制

10

20

30

40

50

御する主制御基板と、

前記主制御基板から送信される遊技球または遊技メダルの払い出しに関するコマンドである払出コマンドに基づいて、遊技球または遊技メダルの払い出しを制御する払出制御基板と、

を備え、前記主制御基板は、前記払出制御基板に、電気的ノイズの影響を受けない低速の通信速度で、シリアルでコマンドを送信する主制御基板シリアル送信部と、該主制御基板における汎用パラレルポートのうちの一部のポートである主制御基板パラレル受信ポートと、を備え、前記払出制御基板は、前記主制御基板から、電気的ノイズの影響を受けない低速の通信速度で、シリアルでコマンドを受信する払出制御基板シリアル受信部と、該払出制御基板における汎用パラレルポートのうちの一部のポートである払出制御基板パラレル送信ポートと、定時間割り込み処理を繰り返し実行して、前記払い出しに関する処理を行う払出制御基板中央演算処理装置と、を備え、前記払出制御基板シリアル受信部は、1バイトの記憶容量を有し、前記主制御基板からシリアルで送信されるコマンドをパラレルデータに変換して記憶する受信シフトレジスタと、1バイトの記憶容量を有し、記憶状態がクリアである場合に、前記受信シフトレジスタに記憶されたコマンドを受け取って記憶する受信バッファレジスタと、を備え、前記払出制御基板は、前記払出制御基板中央演算処理装置から出力されるセット信号に応じて、前記受信バッファレジスタをクリアするバッファクリア部を備え、前記払出コマンドは、前記主制御基板シリアル送信部から前記払出制御基板シリアル受信部へシリアルで送信されて前記受信バッファレジスタに記憶され、前記払出制御基板中央演算処理装置は、前記受信バッファレジスタに記憶されている払出コマンドを読み出すと、前記セット信号を前記バッファクリア部に出力し、更に、前記払出コマンドを正常に受信したと判断した場合は、払出コマンド確認信号を、前記払出制御基板パラレル送信ポートを介して出力し、前記払出コマンド確認信号は、前記払出制御基板パラレル送信ポートから前記主制御基板パラレル受信ポートへパラレルで送信されることを特徴とする。

#### 【0011】

本発明では、複数ビットからなる重要な払出コマンドを、電気的ノイズの影響を受けない低速の通信速度でシリアル送信するのに対し、その払出コマンドを受信できることに対する応答（払出コマンド確認信号）については、シリアルで時間をかけて応答するのではなく、パラレルポートの一部のポートで、いち早く応答するようにした。これにより、主制御基板は、パラレルポートの一部のポートの状態が前回の状態から変化したか否かといった、1ステップの単純な処理を実行することにより、払出制御基板が払出コマンドを受信できることを知ることができる。したがって、主制御基板は、払出制御基板が払出コマンドを受信できることをいち早く知ることができるので、不定期に起きる状態変化（始動入賞口への遊技球の入球など）に対応した処理を数々実行する中で、送信すべき払出コマンドをいつまでも記憶しておくことがなくなり、処理を円滑に実行することができる。つまり、本発明によれば、払出コマンドの信頼性を向上しつつ、主制御基板の負担を軽減することが可能である。

#### 【0012】

前記主制御基板は、前記払出制御基板から、電気的ノイズの影響を受けない低速の通信速度で、シリアルでコマンドを受信する主制御基板シリアル受信部と、前記主制御基板における汎用パラレルポートのうちの一部のポートである主制御基板パラレル送信ポートと、定時間割り込み処理を繰り返し実行して、前記遊技の進行の制御に関する処理を行う主制御基板中央演算処理装置と、を備え、前記払出制御基板は、前記主制御基板に、電気的ノイズの影響を受けない低速の通信速度で、シリアルでコマンドを送信する払出制御基板シリアル送信部と、前記払出制御基板における汎用パラレルポートのうちの一部のポートである払出制御基板パラレル受信ポートと、を備え、前記払出制御基板中央演算処理装置は、遊技機の所定の動作状態を検知し、該動作状態を示すコマンドである動作状態コマンドを、前記払出制御基板シリアル送信部を介して出力し、前記動作状態コマンドは、前記払出制御基板シリアル送信部から前記主制御基板シリアル

10

20

30

40

50

受信部へシリアルで送信され、前記主制御基板中央演算処理装置は、前記動作状態コマンドを正常に受信したと判断した場合は、動作状態コマンド確認信号を、前記主制御基板パラレル送信ポートを介して出力し、前記動作状態コマンド確認信号は、前記主制御基板パラレル送信ポートから前記払出制御基板パラレル受信ポートへパラレルで送信されることを特徴とするものとしても良い。

#### 【0013】

これによれば、電気的ノイズの影響を受けない低速の通信速度で動作状態コマンドを払出制御基板から主制御基板に送信するので、動作状態コマンドの信頼性も向上することができる。また、動作状態コマンド確認信号（アック信号）はパラレルで送信される。シリアルとパラレルの2系統で送受信を行う構成であるので、送受信の信頼性を向上させることができる。10

#### 【0014】

前記払出制御基板シリアル受信部と、前記払出制御基板における汎用パラレルポートと、前記バッファクリア部は、1チップに集積されていることを特徴とするものとしても良い。10

#### 【0015】

これによれば、これらの部品を1チップに集積しているので、払出制御基板上のスペースを節約することができる。

#### 【0016】

なお、本発明の遊技機は、パチンコ機やスロットマシンであっても良く、本発明は遊技機を制御する制御方法や、遊技機を制御するプログラムなどの種々の態様に適用することができる。20

#### 【発明を実施するための最良の形態】

#### 【0017】

以上説明した本発明の構成および作用を一層明らかにするために、以下本発明を適用した遊技機について説明する。なお、本明細書において、信号名の先頭に「#」が付されているものは、負論理であることを意味している。「ハイレベル」は2値信号の2つのレベルのうちの「1」レベルを意味し、「ロー・レベル」は「0」レベルを意味している。

#### 【0018】

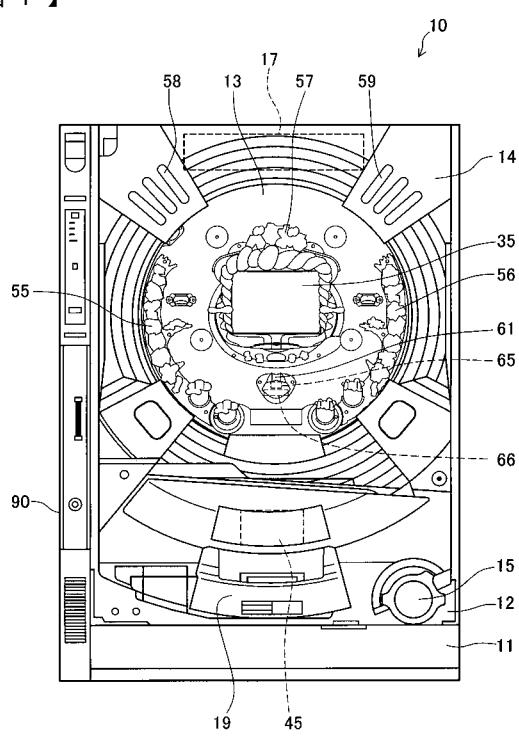

A．パチンコ機10の構成：本発明の実施例の1つであるパチンコ機10の構成について説明する。図1は、パチンコ機10の全体構成を示す正面図である。図1に示すように、パチンコ機10は、パチンコ店のいわゆる島に固定される外枠11、外枠11に嵌め込まれる内枠12、内枠12の中央上寄りに配置され遊技球による遊技が行われる遊技板13、遊技板13の前面に配置され中央部にガラス板を有するガラス枠14、遊技板13に遊技球を発射するための遊技者による操作を受け付けるハンドル15、パチンコ機10の裏面に配置され払出用の遊技球を貯留する球タンク17、遊技者に対して払い出された遊技球を貯留する下皿19、プリペイドカードによる遊技球の貸し出しを受け付けるカードユニット90などを備える。30

#### 【0019】

遊技板13の中央部には、液晶ディスプレイ（Liquid Crystal Display、以下、LCDという）35が設けられ、このLCD35の下方には、遊技球の入賞を受け付ける入賞口61が設けられている。この入賞口61は、入賞した遊技球を検知する遊技球センサ65、所定の場合に遊技球の導入経路を拡縮する遊技板駆動部66を備える。パチンコ機10は、発光ダイオード（Light Emitting Diode、LED）を有する電飾55、56、57、58、59を備える。電飾55、56は遊技板13の左右の端にそれぞれ設けられ、電飾57はLCD35の上部に設けられ、電飾58、59は、ガラス枠14の上部の左右にそれぞれ設けられている。内枠12の正面中央には、音声を出力するスピーカ45が内蔵されている。40

#### 【0020】

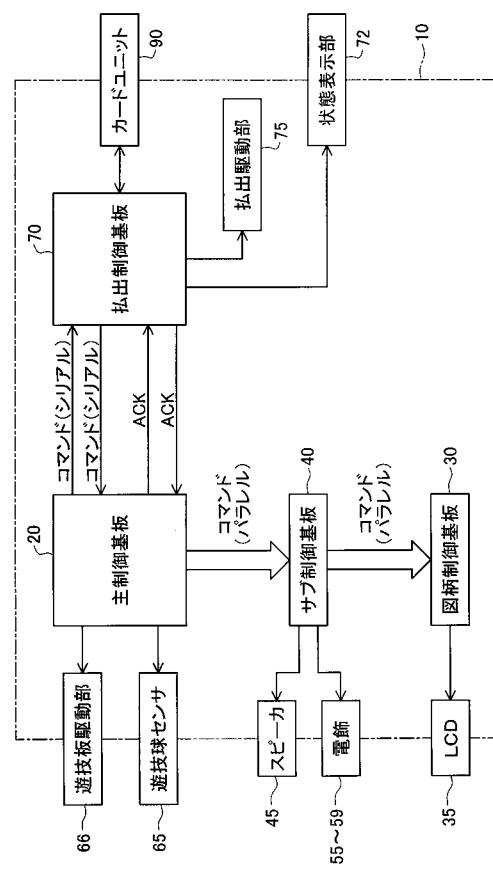

図2は、パチンコ機10の電気的な概略構成を示すブロック図である。パチンコ機10は50

、遊技の進行を制御する主制御基板20と、主制御基板20からのコマンドに基づいて遊技球の払出を制御する払出制御基板70と、遊技進行に応じてLCD35やスピーカ45、電飾55～59を用いた演出を制御するサブ制御基板40と、LCD35における動画表示を制御する図柄制御基板30とを備える。払出制御基板70は、遊技球の払い出しを実行する払出駆動部75と、遊技球の払い出しに関する状態をLEDによって外部に表示する状態表示部72とに接続されている。これら各基板および払出駆動部75、状態表示部72は、図1に示した内枠12の裏面(図示しない)に設けられている。

#### 【0021】

主制御基板20、払出制御基板70、サブ制御基板40、図柄制御基板30の各基板は、種々の演算処理を行うセントラルプロセッシングユニット(Central Processing Unit、中央演算処理装置、以下、CPUという)、CPUの演算処理を規定したプログラムを予め記憶するリードオンリーメモリ(Read Only Memory、以下、ROMという)、CPUが取り扱うデータを一時的に記憶するランダムアクセスメモリ(Random Access Memory、以下、RAMという)などの各基板に応じた電子部品が実装された回路基板である。

#### 【0022】

主制御基板20と払出制御基板70との間では、種々のコマンドがシリアルで送信される。主制御基板20と払出制御基板70との間のコマンドは、2バイト単位で構成され、1バイト単位に分割してシリアルで送信される。コマンドを正常に受信した基板は、コマンドを送信した基板に対して、正常にコマンドを受け取ったことを伝える確認信号であるACK(アック、Acknowledge)信号を送信する。主制御基板20と払出制御基板70との間のコマンドの送受信について詳しくは後述する。

#### 【0023】

主制御基板20からサブ制御基板40に対してや、サブ制御基板40から図柄制御基板30に対しては、それぞれ種々のコマンドがパラレルで送信される。主制御基板20からサブ制御基板40に対する主なコマンドとしては、いわゆる「大当たり」や「はずれ」などの遊技に関する基本的な演出を指示するコマンドがある。サブ制御基板40から図柄制御基板30に対する主なコマンドとしては、主制御基板20からのコマンドに基づくLCD35における動画像の表示態様を指示するコマンドがある。

#### 【0024】

図3は、主制御基板20および払出制御基板70の電気的な構成の詳細を示すブロック図である。主制御基板20は、主制御基板20における種々の演算処理を行うCPUとして、外部とのシリアル通信機能およびパラレル通信機能を有する主CPU200を備える。主CPU200には、演算処理を行う演算処理部210と、外部とのシリアル通信を行うシリアルIF部220と、外部とのパラレル通信を行うパラレルIF部230とが回路構成されている。パラレルIF部230は、本発明における汎用パラレルポートに相当する。

#### 【0025】

シリアルIF部220は、演算処理部210からパラレルデータTDAを受け取り記憶する送信バッファレジスタ240と、送信バッファレジスタ240に記憶されたデータを受け取りシリアルデータDabに変換して払出制御基板70にシリアルで送信する送信シフトレジスタ250と、払出制御基板70からシリアルデータDb-aを受け取り記憶する受信シフトレジスタ260と、受信シフトレジスタ260に記憶されたデータを受け取り演算処理部210によってパラレルデータRDAとして読み出し可能に記憶する受信バッファレジスタ270と、シリアルIF部220における各部の動作状態を管理するシリアル管理部280とを備え、これらシリアルIF部220の構成回路は1チップに集積されている。送信バッファレジスタ240、送信シフトレジスタ250、受信シフトレジスタ260、受信バッファレジスタ270は、それぞれ1バイトの記憶容量を有するレジスタである。送信バッファレジスタ240と、送信シフトレジスタ250と、シリアル管理部280は、本発明の主制御基板シリアル送信部に相当する。

#### 【0026】

10

20

30

40

50

シリアル管理部 280 は、送信シフトレジスタ 250 および送信バッファレジスタ 240 について、送信シフトレジスタ 250 がシリアルの送信中でない場合に、送信バッファレジスタ 240 から送信シフトレジスタ 250 へのデータの受け渡しを許可しデータが受け渡された後、送信バッファレジスタ 240 からデータを消去するように回路構成されている。

#### 【 0027 】

シ

リアル管理部 280 は、受信シフトレジスタ 260 および受信バッファレジスタ 270 について、受信バッファレジスタ 270 にデータが記憶されていない場合に、受信シフトレジスタ 260 から受信バッファレジスタ 270 へのデータの受け渡しを許可し、演算処理部 210 が受信バッファレジスタ 270 からパラレルデータ RDa を読み出した後に、受信バッファレジスタ 270 からデータを消去するように回路構成されている。 10

#### 【 0028 】

なお、シリアル IF 部 220 によるシリアルの送信レートは、主 CPU 200 を動作させるためのクロック信号を分周した信号に基づいて決定される。この送信レートを決定するクロック信号の分周比は、シリアル IF 部 220 に内蔵されたレジスタ（図示しない）の値によって設定することができる。

#### 【 0029 】

演算処理部 210 は、送信バッファレジスタ 240 に対して書き込み信号 # W Ra を立ち下げるこことによって、送信バッファレジスタ 240 へのパラレルデータ T Da の書き込みを行い、受信バッファレジスタ 270 に対して読み出し信号 # RE a を立ち下げるこことによって、受信バッファレジスタ 270 からのパラレルデータ R Da の読み出しを行う。 20

#### 【 0030 】

演算処理部 210 は、シリアル IF 部 220 における種々の状態を示す信号を、シリアル管理部 280 から受ける。演算処理部 210 がシリアル管理部 280 から受ける信号としては、送信バッファレジスタ 240 がクリアされている際にハイレベルとされる送信バッファ空き信号 TE a と、送信シフトレジスタ 250 がシリアルで送信中である際にハイレベルとされるシリアル送信中信号 TC a と、受信バッファレジスタ 270 にデータが記憶されている際にハイレベルとされる受信データ有り信号 DF a とがある。 30

#### 【 0031 】

図 3 に示すように、払出制御基板 70 は、払出制御基板 70 における種々の演算処理を行う払出 CPU 710 と、外部とのシリアル通信およびパラレル通信を行う回路が形成されたシリパラ IF チップ 720 とを備える。

#### 【 0032 】

シリパラ IF チップ 720 は、払出 CPU 710 からパラレルデータ TDb を受け取り記憶する送信バッファレジスタ 740 と、送信バッファレジスタ 740 に記憶されたデータを受け取りシリアルデータ Db a に変換して主制御基板 20 にシリアルで送信する送信シフトレジスタ 750 と、主制御基板 20 からシリアルデータ Da b を受け取り記憶する受信シフトレジスタ 760 と、受信シフトレジスタ 760 に記憶されたデータを受け取り払出 CPU 710 によってパラレルデータ RD b として読み出し可能に記憶する受信バッファレジスタ 770 と、シリパラ IF チップ 720 における各部の動作状態を管理するシリアル管理部 780 と、外部とのパラレル通信を行うパラレル IF 部 730 とを備え、これらシリパラ IF チップの構成回路は 1 チップに集積されている。送信バッファレジスタ 740、送信シフトレジスタ 750、受信シフトレジスタ 760、受信バッファレジスタ 770 は、それぞれ 1 バイトの記憶容量を有するレジスタである。受信シフトレジスタ 760 と、受信バッファレジスタ 770 は、本発明の払出制御基板シリアル受信部に相当する。シリアル管理部 780 は、本発明のバッファクリア部に相当する。パラレル IF 部 730 は、本発明における汎用パラレルポートに相当する。 40

#### 【 0033 】

シリアル管理部 780 は、受信バッファレジスタ 770 をクリアするために払出 CPU 7 50

10から出力されるセット信号C B bを受けてセットされるクリアレジスタ782を備える。シリアル管理部780は、クリアレジスタ782がセットされた場合に、受信バッファレジスタ770からデータを消去し、受信バッファレジスタ770からデータがクリアされるのに応じて、クリアレジスタ782をリセットするように回路構成されている。シリアル管理部780は、受信バッファレジスタ770にデータが記憶されていない場合に、受信シフトレジスタ760から受信バッファレジスタ770へのデータの受け渡しを許可するようにも回路構成されている。

#### 【0034】

シリアル管理部780は、送信シフトレジスタ750および送信バッファレジスタ740について、送信シフトレジスタ750がシリアルで送信中でない場合に、送信バッファレジスタ740から送信シフトレジスタ750へのデータの受け渡しを許可しデータが受け渡された後に、送信バッファレジスタ740からデータを消去するように回路構成されている。

10

#### 【0035】

なお、シリパラIFチップ720がシリアルで送信されたコマンドをサンプリングするタイミングは、主制御基板20の主CPU200を動作させるためのクロック信号を分周回路(図示しない)によって分周したサンプリングクロックに基づいて決定される。このサンプリングクロックを決定するクロック信号からの分周比は、分周回路がシリパラIFチップ720に内蔵される場合には、シリパラIFチップ720に内蔵されたレジスタ(図示しない)の値を変更することによって設定可能に構成しても良い。

20

#### 【0036】

払出CPU710は、送信バッファレジスタ740に対して書き込み信号#WRbを立ち下げるによって、送信バッファレジスタ740へのパラレルデータTDbの書き込みを行い、受信バッファレジスタ770に対して読み出し信号#REbを立ち下げるによって、受信バッファレジスタ770からのパラレルデータRDbの読み出しを行う。

#### 【0037】

払出CPU710は、シリパラIFチップ720における種々の状態を示す信号を、シリアル管理部780から受ける。払出CPU710がシリアル管理部780から受ける信号としては、送信バッファレジスタ740がクリアされている際にハイレベルとされる送信バッファ空き信号TEbと、送信シフトレジスタ750がシリアルで送信中である際にハイレベルとされるシリアル送信中信号TCbと、受信バッファレジスタ770にデータが記憶されている際にハイレベルとされる受信データ有り信号DFbとがある。

30

#### 【0038】

主制御基板20が払出制御基板70に送信するコマンドは、遊技球の払い出しに関する払出コマンドである。払出コマンドは、例えば、遊技球の払い出し個数を指定するコマンドであり、複数ビットのコマンドである。払出コマンドは、送信シフトレジスタ250から受信シフトレジスタ760にシリアルで送信される。払出CPU710は、払出コマンドを正常に受信したと判断すると、アック信号(本発明の払出コマンド確認信号に相当)を主制御基板20に送信する。アック信号は、パラレルIF部730からパラレルIF部230にパラレルで送信される。図示は省略したが、パラレルIF部730とパラレルIF部230には複数のパラレルポートが備えられている。アック信号は1ビットの信号であり、パラレルIF部730とパラレルIF部230の間で、各々複数のパラレルポートのうち1ビット分のポートを利用して送受信される。該1ビット分のポートが、本発明における払出制御基板パラレル送信ポートと、主制御基板パラレル受信ポートに相当する。

40

#### 【0039】

払出制御基板70が主制御基板20に送信するコマンドは、払出CPU710が検知するパチンコ機10の動作状態を、主制御基板20に通知するための動作状態コマンドである。払出コマンドは複数ビットのコマンドであり、動作状態コマンドには、例えば、遊技球が賞球ユニット内に十分ないことを示す球切れ情報と、カードユニット90がパチンコ

50

機 1 0 に接続されていないことを示す情報と、主制御基板 2 0 と払出制御基板 7 0 の間でコマンドを正常に送受信できないことを示す情報が含まれる。動作状態コマンドは、送信シフトレジスタ 7 5 0 から受信シフトレジスタ 2 6 0 にシリアルで送信される。主 C P U 2 0 0 は、動作状態コマンドを正常に受信したと判断すると、アック信号を払出制御基板 7 0 に送信する。アック信号は 1 ビットの信号であり、パラレル I F 部 2 3 0 とパラレル I F 部 7 3 0 の間で、各々複数のパラレルポートのうち 1 ビット分のポートを利用して送受信される。

#### 【 0 0 4 0 】

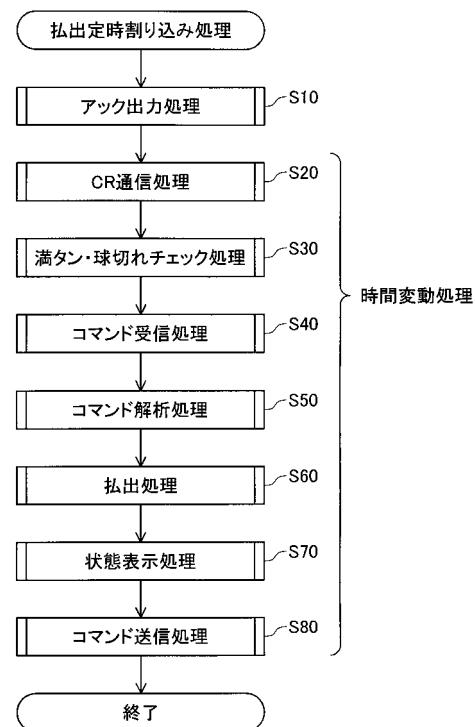

B . パチンコ機 1 0 の動作 : B - 1 . 扟出制御基板 7 0 による払出定時割り込み処理 :

パチンコ機 1 0 の動作の一つとして、払出制御基板 7 0 における払出定時割り込み処理について説明する。図 4 は、払出制御基板 7 0 による払出定時割り込み処理を示すフローチャートである。払出定時割り込み処理は、払出制御基板 7 0 の払出 C P U 7 1 0 によって、所定の間隔（本実施例では、1 ミリセカンド（以下、m s と表記））で繰り返し実行される。

#### 【 0 0 4 1 】

払出制御基板 7 0 の払出 C P U 7 1 0 は、払出定時割り込み処理において種々の処理を実行する。本実施例では、払出 C P U 7 1 0 は、アック出力処理（ステップ S 1 0 ）、C R 通信処理（ステップ S 2 0 ）、満タン・球切れチェック処理（ステップ S 3 0 ）、コマンド受信処理（ステップ S 4 0 ）、コマンド解析処理（ステップ S 5 0 ）、払出処理（ステップ S 6 0 ）、状態表示処理（ステップ S 7 0 ）、コマンド送信処理（ステップ S 8 0 ）の順に種々の処理を実行する。払出定時割り込み処理における各処理（ステップ S 1 0 ～ S 8 0 ）は、遊技の進行状態に応じて処理内容が異なってくるため、完了までに要する時間が遊技の進行に応じて変動する。払出定時割り込み処理におけるアック出力処理（ステップ S 1 0 ）の処理は、他の処理（ステップ S 2 0 ～ S 8 0 ）の処理に優先し、本実施例では、アック出力処理（ステップ S 1 0 ）の処理は、払出定時割り込み処理の先頭で実行される。

#### 【 0 0 4 2 】

アック出力処理（ステップ S 1 0 ）は、主制御基板 2 0 からコマンドを正常に受信した際に主制御基板 2 0 に対してアック信号を出力するための処理である。アック出力処理（ステップ S 1 0 ）の詳細は後述する。

#### 【 0 0 4 3 】

C R 通信処理（ステップ S 2 0 ）は、カードユニット 9 0 と間で遊技球の貸し出しに関するデータを取り取りするための処理である。満タン・球切れチェック処理（ステップ S 3 0 ）は、下皿 1 9 に貯留されている遊技球が満杯となっていないか、球タンク 1 7 に貯留されている遊技球が空となっていないかを確認することによって、遊技球の払い出しに障害となる物理的な状態を検出するための処理である。

#### 【 0 0 4 4 】

コマンド受信処理（ステップ S 4 0 ）は、主制御基板 2 0 から 1 バイト単位でシリアルで送信された払出コマンドを受信するための処理である。コマンド受信処理（ステップ S 4 0 ）の詳細は後述する。コマンド解析処理（ステップ S 5 0 ）は、コマンド受信処理（ステップ S 4 0 ）にて受信された払出コマンドの内容を解析するための処理である。具体的には、コマンド解析処理（ステップ S 5 0 ）では、払出コマンドが示す払い出し個数が正常値（例えば 1 個～ 1 5 個）の範囲内であるか否か判断し、正常値の範囲内でなければ、遊技球の払い出しを行わないものとして、払出コマンドを無視する。払い出し個数が正常値の範囲内であれば、払出コマンドが示す払い出し個数を、払い出し個数バッファで記憶している総払い出し個数に加算する。払い出し個数バッファは、パチンコ機 1 0 が払い出すべき遊技球の総数を記憶するバッファである。

#### 【 0 0 4 5 】

払出処理（ステップ S 6 0 ）は、遊技球の払い出しを実行するための処理である。払出処理（ステップ S 6 0 ）において、C R 通信処理（ステップ S 2 0 ）にて得られた貸し出し

10

20

30

40

50

の指示や、払い出し個数バッファの内容に応じて、払出CPU710は、払出駆動部75に対して動作を指示するための信号を出力する。本実施例では、カードユニット90や主制御基板20から払い出しを要求された遊技球の個数に異常な変化があった場合や、満タン・球切れチェック処理(ステップS30)にて物理的な障害が確認された場合には、払出CPU710は、遊技球の払い出しを一時的に停止する。

#### 【0046】

状態表示処理(ステップS70)は、状態表示部72に払出CPU710が検知するパチンコ機10の動作状態を表示させるための処理である。本実施例では、状態表示部72における動作状態の表示は、各状態に対応する数字を表示することによって行われ、例えば、主制御基板20と払出制御基板70とのコマンドの送受信に異常が発生した場合には状態表示部72に「0」が表示され、球タンク17において球切れが発生した場合には状態表示部72に「1」が表示され、カードユニット90が払出制御基板70に接続されていない場合には状態表示部72に「7」が表示される。

#### 【0047】

コマンド送信処理(ステップS80)は、払出制御基板70から主制御基板20に2バイト単位の動作状態コマンドを1バイト単位で送信するための処理である。コマンド送信処理の詳細は後述する。

#### 【0048】

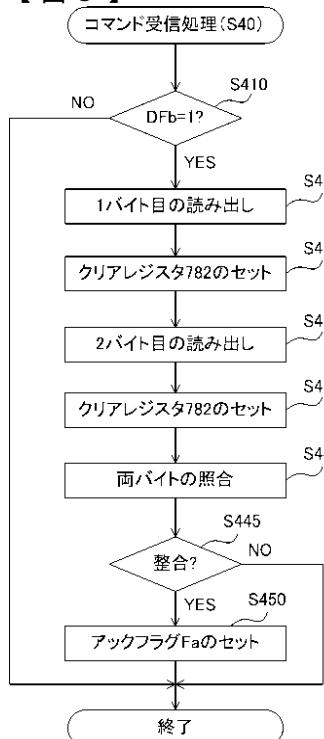

B-2. 払出定時割り込み処理におけるコマンド受信処理：図5は、払出定時割り込み処理において実行されるコマンド受信処理(ステップS40)の詳細を示すフローチャートである。コマンド受信処理(ステップS40)は、前述した通り、図4に示した払出定時割り込み処理における種々の処理のうちの一つであり、払出制御基板70の払出CPU710によって実行される。コマンド受信処理は、主制御基板20からシリアルで送信された払出コマンドを受信するための処理である。

#### 【0049】

払出CPU710は、図5に示したコマンド受信処理を開始すると、「受信データ有り信号DFbがハイレベル」であるか否か、すなわち、「受信バッファレジスタ770にデータが記憶されている場合」であるか否かを判断する(ステップS410)。ここで、コマンド受信処理において「受信データ有り信号DFbがハイレベル」であると判断される場合(ステップS410)には、主制御基板20から払出制御基板70に対して送信された2バイトの払出コマンドのうち、1バイト目が受信バッファレジスタ770に記憶された状態である。

#### 【0050】

「受信データ有り信号DFbがハイレベル」である場合(ステップS410)には、払出CPU710は、受信バッファレジスタ770に記憶されている払出コマンドの1バイト目を読み出した後(ステップS412)、払出CPU710は、シリパラIFチップ720のクリアレジスタ782にセット信号CBbを出力し、クリアレジスタ782のビットをセットする(ステップS420)。クリアレジスタ782がセットされることによって、シリパラIFチップ720のシリアル管理部780は、受信バッファレジスタ770に記憶された払出コマンドの1バイト目をクリアし、受信シフトレジスタ760に記憶されていた払出コマンドの2バイト目が、受信バッファレジスタ770に受け渡される。その後、クリアレジスタ782は自動的にリセットされる。

#### 【0051】

払出CPU710は、クリアレジスタ782をセットした後(ステップS420)、受信バッファレジスタ770に記憶されている払出コマンドの2バイト目を読み出し(ステップS422)、シリパラIFチップ720のクリアレジスタ782にセット信号CBbを出力し、クリアレジスタ782のビットをセットする(ステップS430)。これによって、シリパラIFチップ720のシリアル管理部780は、受信バッファレジスタ770に記憶された払出コマンドの2バイト目をクリアする。

#### 【0052】

10

20

30

40

50

払出 C P U 7 1 0 は、クリアレジスタ 7 8 2 をセットした後（ステップ S 4 3 0）、読み出した払出コマンドの 1 バイト目と、読み出したコマンドの 2 バイト目とを照合して（ステップ S 4 4 0）、両者が整合するか否かを判断する（ステップ S 4 4 5）。本実施例では、払出コマンドの 2 バイト目は、主制御基板 2 0 において払出コマンドの 1 バイト目の各ビットを反転して生成されたデータである。読み出した払出コマンドの 1 バイト目と 2 バイト目とが整合する場合には（ステップ S 4 4 5）、払出 C P U 7 1 0 は、主制御基板 2 0 に対してアック信号を送信するためのアックフラグ F a をセットし（ステップ S 4 5 0）、コマンド送信処理を終了する。アックフラグ F a は、前述したアック出力処理（ステップ S 1 0）において用いられ、払出 C P U 7 1 0 に内蔵のレジスタや R A M（図示しない）に格納されるデータである。アックフラグ F a は、払出 C P U 7 1 0 の起動時には「0」に設定されている。10

#### 【 0 0 5 3 】

一方、読み出したコマンドの 1 バイト目と 2 バイト目とが整合しない場合には（ステップ S 4 4 5）、払出 C P U 7 1 0 は、アックフラグ F a をセットすることなくコマンド受信処理を終了する。これによって、払出コマンドが正常でない場合、アック信号は主制御基板 2 0 に出力されず、主制御基板 2 0 側では、アック信号が返信されないことにより払出コマンドの送信に異常が生じたことを判断することができる。

#### 【 0 0 5 4 】

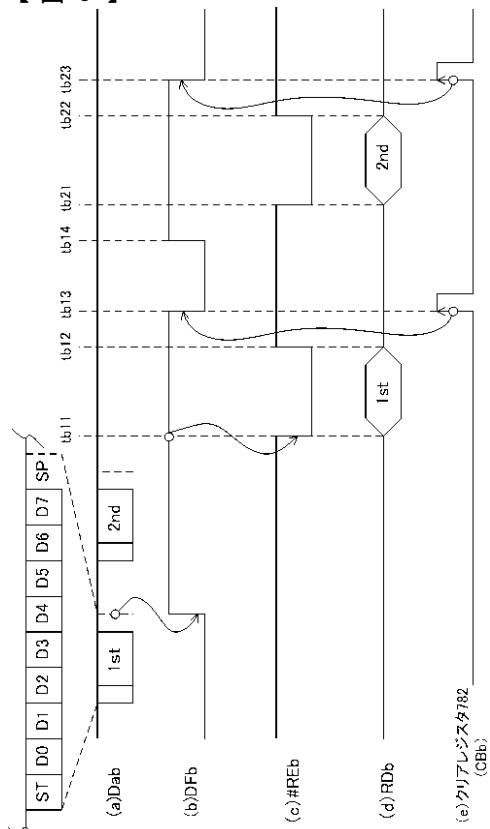

図 6 は、コマンド受信処理（ステップ S 4 0）が実行される際の払出制御基板 7 0 における各信号の様子を示すタイムチャートである。なお、説明の便宜上、図 6 では、払出コマンドの 1 バイト目と 2 バイト目とのシリアルの送信時間のスケールは、払出 C P U 7 1 0 の演算処理時間のスケールと比べ縮小されている。20

#### 【 0 0 5 5 】

図 5 に示したコマンド受信処理にて、「受信データ有り信号 D F b がハイレベル」であると判断されると（図 5 中のステップ S 4 1 0）、読み出し信号 # R E b の立ち下がりによって、受信バッファレジスタ 7 7 0 からパラレルデータ R D b に払出コマンドの 1 バイト目が出力される。つまり、払出コマンドの 1 バイト目が、払出 C P U 7 1 0 によって受信バッファレジスタ 7 7 0 から読み出される（タイミング t b 1 1 ~ t b 1 2、図 5 中のステップ S 4 1 2）。

#### 【 0 0 5 6 】

払出コマンドの 1 バイト目の読み出しが完了した後、クリアレジスタ 7 8 2 のセットに応じて受信バッファレジスタ 7 7 0 がクリアされ、受信データ有り信号 D F b はローレベルとなる（タイミング t b 1 3、図 5 中のステップ S 4 2 0）。その後、受信シフトレジスタ 7 6 0 から受信バッファレジスタ 7 7 0 へと払出コマンドの 2 バイト目が受け渡されると、受信データ有り信号 D F b はハイレベルとなる（タイミング t b 1 4）。

#### 【 0 0 5 7 】

その後、払出コマンドの 2 バイト目が、コマンドの 1 バイト目と同様にして受信バッファレジスタ 7 7 0 から読み出される（タイミング t b 2 1 ~ t b 2 2、図 5 中のステップ S 4 2 2）。払出コマンドの 2 バイト目の読み出しが完了した後、クリアレジスタ 7 8 2 のセットに応じて受信バッファレジスタ 7 7 0 がクリアされ、受信データ有り信号 D F b はローレベルとなる（タイミング t b 2 3、図 5 中のステップ S 4 3 0）。

#### 【 0 0 5 8 】

本実施例では、シリパラ I F チップ 7 2 0 のサンプリングタイミングは、送信レート（1 2 0 0 b p s）の 1 6 倍である 1 9 . 2 キロヘルツ（k H z）に設定されている。本実施例では、シリパラ I F チップ 7 2 0 は、スタートビット S T、払出コマンドの各データビット D 0 ~ D 7、トップビット S P のビット毎に、それぞれ 3 回のサンプリングを行い、この 3 回のサンプリングで検出された値を多数決判定する。これによって、払出コマンド受信の信頼性の向上が図られている。

#### 【 0 0 5 9 】

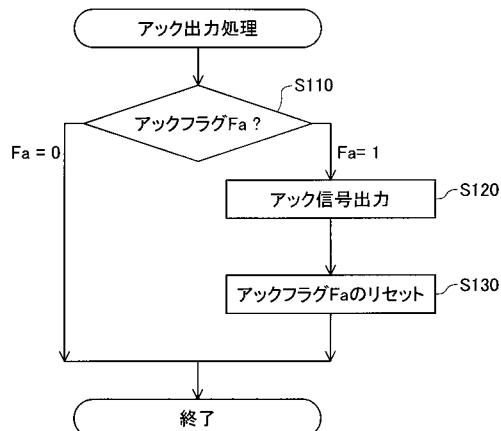

B - 3 . 払出定時割り込み処理におけるアック出力処理： 図 7 は、払出定時割り込み処理におけるアック出力処理のフロー図である。40

10

20

30

40

50

理において実行されるアック出力処理（ステップS10）の詳細を示すフローチャートである。アック出力処理（ステップS10）は、前述した通り、図4に示した払出定時割り込み処理における種々の処理のうちの一つであり、払出制御基板70の払出CPU710によって実行される。

#### 【0060】

払出CPU710は、図7に示したアック出力処理（ステップS10）を開始すると、アックフラグFaがセットされている場合には（ステップS110）、アック信号をシリパラIFチップ720のパラレルIF部730を介して主制御基板20に出力する（ステップS120）。その後、払出CPU710は、アックフラグFaをリセットした後（ステップS130）、アック出力処理を終了する。アックフラグFaがセットされていない場合には（ステップS110）、払出CPU710は、アック信号を出力せずにアック出力処理を終了する。

#### 【0061】

アックフラグFaがセットされている場合とは、図5に示したコマンド受信処理（ステップS40）において、払出コマンドが正常に受信された際にアックフラグFaがセットされた場合（図5中のステップS450）である。図4に示したように、定時割り込み処理において、アック出力処理（ステップS10）の処理は、コマンド受信処理（ステップS40）の処理に優先して先に実行されるため、アックフラグFaがセットされた際には、次回の定時割り込み処理におけるアック出力処理（ステップS10）にてアック信号が出力されることとなる。

#### 【0062】

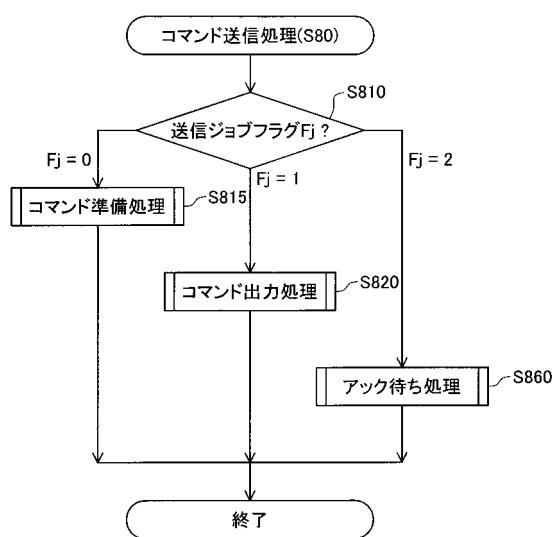

B-4. 払出定時割り込み処理におけるコマンド送信処理：図8は、払出定時割り込み処理において実行されるコマンド送信処理（ステップS80）の詳細を示すフローチャートである。コマンド送信処理（ステップS80）は、前述した通り、図4に示した払出定時割り込み処理における種々の処理のうちの一つであり、払出制御基板70の払出CPU710によって実行される。コマンド送信処理は、動作状態コマンドを主制御基板20にシリアルで送信するための処理である。

#### 【0063】

払出CPU710は、図8に示したコマンド送信処理を開始すると、送信ジョブフラグFjの値を判断する（ステップS810）。送信ジョブフラグFjは、コマンド送信処理における状態を示すフラグであり、払出CPU710の起動時には「0」に設定されており、払出CPU710に内蔵のレジスタやRAM（図示しない）に格納されるデータである。

#### 【0064】

「送信ジョブフラグFj = 0」の場合には、払出CPU710は、主制御基板20に対して送信すべき動作状態コマンドを準備するためのコマンド準備処理（ステップS815）を実行する。コマンド準備処理では、払出CPU710は、シリパラIFチップ720の複数のポートに入力される各センサからの信号に基づいて、動作状態コマンドを送信する必要があると判断すると、該センサからの信号に基づいて動作状態コマンドの1バイト目を生成する。そして、送信ジョブフラグFjを「1」に設定した後、コマンド準備処理（ステップS815）を終了する。

#### 【0065】

「送信ジョブフラグFj = 1」の場合には、払出CPU710は、主制御基板20に対して2バイト単位の動作状態コマンドを出力するためのコマンド出力処理を実行し（ステップS820）、「送信ジョブフラグFj = 2」の場合には、主制御基板20からのアック信号を確認するためのアック待ち処理を実行する（ステップS860）。払出CPU710は、コマンド準備処理（ステップS815），コマンド出力処理（ステップS820），アック待ち処理（ステップS860）のいずれかを終了した後、コマンド送信処理（ステップS80）を終了する。なお、コマンド出力処理（ステップS820），アック待ち

10

20

30

40

50

処理（ステップ S 8 6 0）の詳細については後述する。

#### 【0066】

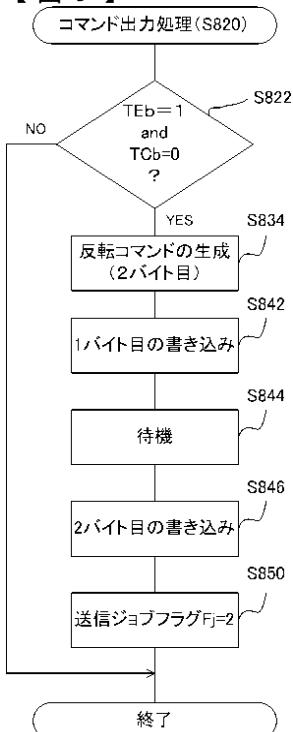

図9は、コマンド送信処理（ステップ S 8 0）におけるコマンド出力処理（ステップ S 8 2 0）の詳細を示すフローチャートである。払出 C P U 7 1 0は、図9に示すコマンド出力処理（ステップ S 8 2 0）を開始すると、「送信バッファ空き信号 T E bがハイレベル」かつ「シリアル送信中信号 T C bがローレベル」であるか否か、すなわち、「送信バッファレジスタ 7 4 0にデータが記憶されていない場合」かつ「送信シフトレジスタ 7 5 0がシリアルでの送信中でない場合」であるか否かを判断する（ステップ S 8 2 2）。 「送信バッファ空き信号 T E bがハイレベル」かつ「シリアル送信中信号 T C bがローレベル」である場合（ステップ S 8 2 2）には、払出 C P U 7 1 0は、動作状態コマンドの1バイト目の各ビットを反転して、すなわち、1バイト目のビットのうち、「0」であるビットを「1」とし、「1」であるビットを「0」として、動作状態コマンドの残りの下位1バイトである2バイト目を生成する（ステップ S 8 3 4）。本実施例では、動作状態コマンドの1バイト目は、動作状態コマンドとしての実質的な意味を持つデータであり、動作状態コマンドの2バイト目は、主制御基板 2 0側で動作状態コマンドの正誤を判断するためのデータである。

10

#### 【0067】

そして、動作状態コマンドの2バイト目を生成した後（ステップ S 8 3 4）、動作状態コマンドの1バイト目を、送信バッファレジスタ 7 4 0に書き込む（ステップ S 8 4 2）。その後、予め設定された書込待機期間 L w a の待機を行った後（ステップ S 8 4 4）、生成した動作状態コマンドの2バイト目を、送信バッファレジスタ 7 4 0に書き込む（ステップ S 8 4 6）。払出 C P U 7 1 0は、動作状態コマンドを出力した後、送信ジョブフラグ F j を「2」に設定し（ステップ S 5 0）、コマンド出力処理を終了する。

20

#### 【0068】

ここで、書込待機期間 L w a は、送信バッファレジスタ 7 4 0への動作状態コマンドの1バイト目の書き込みから、この1バイト目が送信シフトレジスタ 7 5 0へと受け渡しされるまでの期間である送信レジスタ引渡し期間 L b s よりも長い期間であり、その定時割り込み処理の終了までに2バイト目の書き込み処理（図9のステップ S 8 4 6）を実行可能な十分な時間を残す期間であり、次の定時割り込み処理の開始まで長引くような期間ではない。また、書込待機期間 L w a は、動作状態コマンドの1バイト目のシリアルでの送信が完了するまでの期間であるシリアル送信期間 L s c よりも短い期間であり、定時割り込み処理の間隔である 1 m s よりも短い期間である。本実施例では、書込待機期間 L w a は、2.5マイクロセカンドに設定されている。なお、本実施例のシリパラ I F チップ 7 2 0 のハードウェア仕様による送信レジスタ引渡し期間 L b s は、約 1.25 マイクロセカンドである。また、2バイト目の書き込み処理（図9のステップ S 8 4 6）に要する払出 C P U 7 1 0の演算処理時間が、シリパラ I F チップ 7 2 0の送信レジスタ引渡し期間 L b s 以上である場合には、図9に示したコマンド待機処理のソフトウェアによる待機処理（ステップ S 8 4 4）は不要である。

30

#### 【0069】

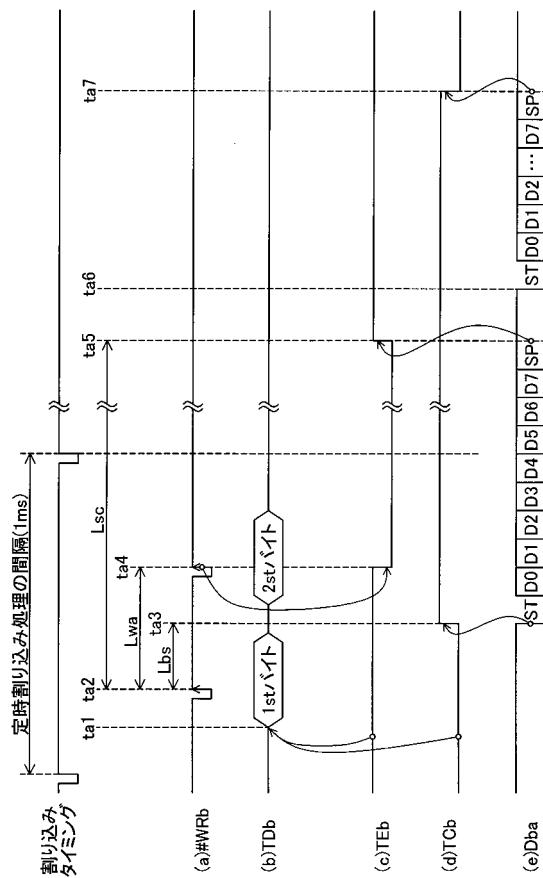

図10は、コマンド出力処理（ステップ S 8 2 0）が実行される際の払出制御基板 7 0における各信号の様子を示すタイムチャートである。図9に示したコマンド出力処理にて、「送信バッファ空き信号 T E bがハイレベル」かつ「シリアル送信中信号 T C bがローレベル」であると判断され（図9中のステップ S 8 2 2）、1バイト目の書き込みが実行される場合には（図9中のステップ S 8 4 2）、パラレルデータ T D b に動作状態コマンドの1バイト目の出力が開始され（タイミング t a 1）、その後、書き込み信号 # W R b の立ち下がりによって、送信バッファレジスタ 7 4 0に動作状態コマンドの1バイト目が書き込まれる（タイミング t a 2）。

40

#### 【0070】

送信バッファレジスタ 7 4 0は、書き込まれた動作状態コマンドの1バイト目を送信シフトレジスタ 7 5 0に引き渡し、この引き渡しが完了するとシリアル管理部 7 8 0によって

50

クリアされる。送信シフトレジスタ750は、送信バッファレジスタ740から受け取った動作状態コマンドの1バイト目をシリアルデータDbaに出力する。シリアル送信中のシリアルデータDbaには、スタートビットSTに続いて、コマンドの1ビット目D0から8ビット目D7までの各ビットが続き、最後にストップビットSPが出力される。このように、動作状態コマンドの1バイト目のシリアルでの送信が開始されると、シリアル送信中信号TCbはハイレベルとなる(タイミングta3)。

#### 【0071】

動作状態コマンドの1バイト目の書き込み(タイミングta2, 図9中のステップS842)から、書込待機期間Lwaの待機を経た後(図9中のステップS844)、動作状態コマンドの1バイト目と同様に、送信バッファレジスタ740に動作状態コマンドの2バイト目が書き込まれる(タイミングta4, 図9中のステップS846)。この際、送信シフトレジスタ750は、動作状態コマンドの1バイト目をシリアルで送信中であり、動作状態コマンドの2バイト目を送信バッファレジスタ740から受け取ることができないため、送信バッファレジスタ740は、書き込まれた動作状態コマンドの2バイト目を記憶して保持し、送信バッファ空き信号TEbはローレベルとなる(タイミングta4)。

10

20

30

40

#### 【0072】

その後、送信シフトレジスタ750による動作状態コマンドの1バイト目のシリアルでの送信が終了すると、送信バッファレジスタ740は、記憶する動作状態コマンドの2バイト目を送信シフトレジスタ750に引き渡し、この引き渡しが完了するとシリアル管理部780によってクリアされ、送信バッファ空き信号TEbはハイレベルとなる(タイミングta5)。その後、送信シフトレジスタ750は、動作状態コマンドの1バイト目と同様に、送信バッファレジスタ740から受け取った動作状態コマンドの2バイト目をシリアルデータDbaに出力する(タイミングta6~ta7)。

20

30

#### 【0073】

本実施例では、派出CPU710は、1msの間隔で定時割り込み処理を繰り返し実行するのに対し、シリパラIFチップ720は、1200bps(Bit Per Second)の送信レートでシリアルでの送信を実行する。1200bpsは、比較的安価なフォトカプラなどの、応答速度が低速の送受信素子を使用することができ、かつ、電気的ノイズの影響を受けない低速の通信速度である。シリアル送信における送信レートを1200bpsとすると、電気的ノイズに対するコマンドの送信の信頼性を確保できる。送信レートが1200bpsなので、本実施例では、シリパラIFチップ720が2バイトの動作状態コマンドをシリアルで送信する時間は約16.7msとなり、派出CPU710は、その間に定時割り込み処理を約16回繰り返し実行することとなる。このように、派出CPU710は、送信バッファレジスタ740にコマンドを書き込んでしまえば、主制御基板20に対する動作状態コマンドのシリアルでの送信をシリパラIFチップ720に任せることができる。つまり、派出CPU710は、シリアルでの送信中(送信バッファレジスタ740に動作状態コマンドが有る状態)であっても、制御処理を中断することなく実行することができる。

30

#### 【0074】

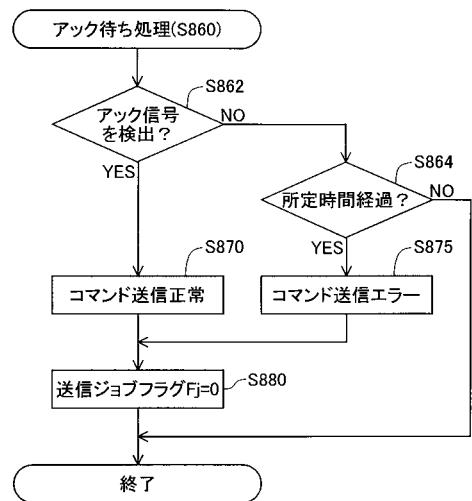

図11は、コマンド送信処理(ステップS80)におけるアック待ち処理(ステップS860)の詳細を示すフローチャートである。派出CPU710は、図11に示すアック待ち処理を開始すると、パラレルIF部730が主制御基板20からのアック信号を検出したか否かを判断する(ステップS862)。アック信号を検出した場合には(ステップS862)、派出CPU710は、コマンドが主制御基板20へと正常に送信されたと判断し(ステップS870)、送信ジョブフラグFjを「0」に設定し(ステップS880)、アック待ち処理を終了する。

40

#### 【0075】

一方、アック信号を検出しない場合には(ステップS862)、派出CPU710は、コマンドの書き込み(図9中のステップS846)を終えてから所定の時間が経過したか否

50

かを判断する（ステップS864）。この所定の時間は、主制御基板20からのアック信号の返答を待つ時間であり、本実施例では、100msに設定されている。所定の時間が経過していない場合には（ステップS864）、払出CPU710は、そのままアック待ち処理を終了し、所定の時間が経過している場合には（ステップS864）、主制御基板20へのコマンド送信がエラーであると判断し（ステップS875）、送信ジョブフラグFjを「0」に設定した後（ステップS880）、アック待ち処理を終了する。本実施例では、払出CPU710は、動作状態コマンドの主制御基板20への送信がエラーであると判断した場合には（ステップS875）、送信エラーとなつた動作状態コマンドを再送する。

#### 【0076】

ところで、主CPU200が払出コマンドを払出制御基板70に送信した場合も、上記と同様にアック待ち処理を実行する。なお、主CPU200は、アック待ち処理中に入賞口61に遊技球が入賞した場合、払出コマンドを生成する必要がある。主CPU200は、アック待ち処理において、所定時間以上アック信号を受信せずに、払出コマンドの払出制御基板70への送信がエラーであると判断した場合には

、払出コマンドの再送に代えて、払出制御基板70からアック信号が返ってくるか否かを再度確認するための確認コマンドを送信する。払出コマンドを再送すると、計2回送信された払出コマンドに基づき、払出制御基板70が払出コマンド2回分の賞球を払い出す可能性があるためである。払出制御基板70は、該確認コマンドを受信した場合は、主制御基板20にアック信号を送信する。なお、払出制御基板70は、該確認コマンドを受信した場合は、動作状態コマンドを送信するものとしても良い。主CPU200は、アック信号を受信すると、次の払出コマンドを払出制御基板70に送信する。

#### 【0077】

以上では、払出CPU710における定時割り込み処理について説明したが、主CPU200においても同様に定時割り込み処理を実行しており、該定時割り込み処理の中で、動作状態コマンドを受信する処理や、アック信号を送信する処理や、払出コマンドを送信する処理や、アック待ち処理を実行する。

#### 【0078】

なお、主制御基板20が、払出制御基板70に対して払出コマンドやアック信号を送信する動作は、払出CPU710に代えて演算処理部210、送信バッファレジスタ740に代えて送信バッファレジスタ240、送信シフトレジスタ750に代えて送信シフトレジスタ250、パラレルIF部730に代えてパラレルIF部230が、それぞれ上述した払出制御基板70のアック出力処理（ステップS10）やコマンド送信処理（ステップS80）と同様の動作を行うことによって実現される。

#### 【0079】

また、主制御基板20が、払出制御基板70から動作状態コマンドやアック信号を受信する動作は、払出CPU710に代えて演算処理部210、受信シフトレジスタ760に代えて受信シフトレジスタ260、受信バッファレジスタ770に代えて受信バッファレジスタ270、パラレルIF部730に代えてパラレルIF部230が、それぞれ上述した払出制御基板70のコマンド受信処理（ステップS40）やアック待ち処理（ステップS860）と同様の動作を行うことによって実現される。

#### 【0080】

以上説明した本実施例のパチンコ機10によれば、複数ビットからなる重要な払出コマンドを、電気的ノイズの影響を受けない低速の通信速度でシリアル送信するのに対し、その払出コマンドを受信できたことに対する応答（払出コマンド確認信号）については、シリアルで時間をかけて応答するのではなく、パラレルポートの一部のポートで、いち早く応答するようにした。これにより、主制御基板20は、パラレルポートの一部のポートの状態が前回の状態から変化したか否かといった、1ステップの単純な処理を実行することにより、払出制御基板70が払出コマンドを受信できたことを知ることができる。したがって、主制御基板20は、払出制御基板70が払出コマンドを受信できたことをいち早く

10

20

30

40

50

知ることができるので、不定期に起きる状態変化（始動入賞口への遊技球の入球など）に対応した処理を数々実行する中で、送信すべき払出コマンドをいつまでも記憶しておくことがなくなり、処理を円滑に実行することができる。つまり、本実施例のパチンコ機10によれば、払出コマンドの信頼性を向上しつつ、主制御基板20の負担を軽減することが可能である。そして、本実施例のパチンコ機10では、更に、払出CPU710で払出コマンドを正常に受信したか否か判断し、正常に受信したと判断した場合にACK信号を送信する。これらの手順で払出コマンドの送受信を行うことにより、払出コマンドの送受信の信頼性を向上させている。

#### 【0081】

また、本実施例のパチンコ機10では、電気的ノイズの影響を受けない低速の通信速度でシリアルで動作状態コマンドを払出制御基板から主制御基板に送信するので、動作状態コマンドの信頼性も向上することができる。更に、動作状態コマンドを正常に受信することにより、主制御基板20から払出制御基板70に送信されるACK信号は、パラレルで送信される。シリアルとパラレルの2系統で送受信を行う構成であるので、送受信の信頼性を向上させることができる。

#### 【0082】

更に、本実施例のパチンコ機10では、シリパラIFチップ720として、シリアルの送受信を行う受信シフトレジスタ760と、受信バッファレジスタ770と、シリアル管理部780と、送信バッファレジスタ740と、送信シフトレジスタ750と、パラレルの送受信を行うパラレルIF部730が1チップに集積されているので、払出制御基板70のスペースを節約することができる。また、1チップに集積することにより、ノイズの影響を受けにくくなる。なお、本実施例では、シリパラIFチップ720を払出制御基板70に使用しているが、主制御基板20に使用するものとしても良い。主制御基板20に使用すると、主制御基板20のスペースを節約することができる。これら基板のスペースを節約することにより、基板の面積自体が小さくなるので、基板の配置の自由度が高くなる。これにより、パチンコ機10に備えるセンター役物など他の部品の配置の自由度も高くなり、パチンコ機10の興奮を高めるべく部品を配置することができるようになる。

#### 【0083】

また、払出制御基板70側において、払出コマンドを受信した払出定時割り込み処理（図4）の期間内に、払出コマンドに応じた対応を迅速に処理し、後続の払出定時割り込み処理において、毎回同じタイミングで、主制御基板20に対するACK信号を確実に出力することができる。したがって、払出制御を滞らせることなく、払出コマンドの送信の正常性の確認を確実に実施することができる。その結果、主制御基板20と払出制御基板70との間でコマンドを分割してシリアル送信する際ににおけるコマンドの送信の信頼性を向上させることができる。また、払出定時割り込み処理（図4）では、コマンド受信処理（ステップS40）の後に払出処理（ステップS60）を実行するため、払出制御基板70において払出コマンドを受信した払出割り込み処理の期間内に、払出駆動部75に対して払出コマンドに応じた動作を迅速に指示することができる。

#### 【0084】

C. その他の実施形態： 以上、本発明の実施の形態について説明したが、本発明はこうした実施の形態に何ら限定されるものではなく、本発明の趣旨を逸脱しない範囲内において様々な形態で実施し得ることは勿論である。例えば、本実施例では、ステップS445の判断で、払出コマンドを正常に受信したと判断し、ACKフラグFaをセットしているが、払出コマンドを正常に受信したと判断する場合は、これに限らず、様々である。例えば、ステップS445に加え、ステップS50のコマンド解析処理で払出コマンドが示す賞球個数が正常値（例えば1個～15個）の範囲内であると判断した場合に、払出コマンドを正常に受信したと判断し、ACKフラグFaをセットするものとしても良い。

#### 【0085】

更に、シリアルIF部220の受信バッファレジスタ270と、受信シフトレジスタ260や、シリパラIFチップ720の送信バッファレジスタ740と、送信シフトレジスタ

10

20

30

40

50

750は、本発明の趣旨を逸脱しない範囲において、適宜省略可能である。

#### 【0086】

また、本発明の適用は、複数の制御基板を備えた遊技機であれば良く、パチンコ機に限らず、アレンジボールやスロットマシンなどの遊技機にも適用することもできる。また、コマンドを正常に受信できなかった側の基板は、そのコマンドを送信した側の基板に対して、コマンドの再送を要求することとしても良い。この場合に、再送の要求は、シリアルの送信で行うこととしても良いし、パラレルの送信で行うこととしても良い。これによって、コマンドの送信の信頼性を向上させることができる。

#### 【0087】

また、払出定時割り込み処理における種々の処理についての処理は、図4に示した実施例のものに限るものではなく、アック出力処理(ステップS10)が、時間変動処理よりも優先して実行されるものであれば良い。例えば、完了までに要する時間が遊技の進行に応じて割り込み処理毎に一定である処理を、アック出力処理(ステップS10)の前に実行することとしても良い。

#### 【図面の簡単な説明】

#### 【0088】

【図1】パチンコ機10の全体構成を示す正面図である。

【図2】パチンコ機10の電気的な概略構成を示すブロック図である。

【図3】主制御基板20および払出制御基板70の電気的な構成の詳細を示すブロック図である。

【図4】払出制御基板70による払出定時割り込み処理を示すフローチャートである。

【図5】払出定時割り込み処理において実行されるコマンド受信処理(ステップS40)の詳細を示すフローチャートである。

【図6】コマンド受信処理(ステップS40)が実行される際の払出制御基板70における各信号の様子を示すタイムチャートである。

【図7】払出定時割り込み処理において実行されるアック出力処理(ステップS10)の詳細を示すフローチャートである。

【図8】払出定時割り込み処理において実行されるコマンド送信処理(ステップS80)の詳細を示すフローチャートである。

【図9】コマンド送信処理(ステップS80)におけるコマンド出力処理(ステップS820)の詳細を示すフローチャートである。

【図10】コマンド出力処理(ステップS820)が実行される際の払出制御基板70における各信号の様子を示すタイムチャートである。

【図11】コマンド送信処理(ステップS80)におけるアック待ち処理(ステップS860)の詳細を示すフローチャートである。

#### 【符号の説明】

#### 【0089】

|                       |                    |                    |                   |                    |          |

|-----------------------|--------------------|--------------------|-------------------|--------------------|----------|

| 10 ... パチンコ機          | 11 ... 外枠          | 12 ... 内枠          | 13 ... 遊技板        | 14 ... ガラス枠        |          |

| 15 ... ハンドル           | 17 ... 球タンク        | 19 ... 下皿          | 20 ... 主制御基板      | 30 ... 図柄制御基板      | 30 ... 図 |

| 35 ... L C D          | 40 ... サブ制御基板      | 45 ... スピーカ        | 55 , 56           |                    | 40       |

| , 57 , 58 , 59 ... 電飾 | 61 ... 入賞口         | 65 ... 遊技球センサ      | 66 ... 遊技板駆動部     |                    |          |

| 70 ... 払出制御基板         | 72 ... 状態表示部       | 75 ... 払出駆動部       | 90 ... カードユニット    |                    |          |

| 200 ... 主C P U        | 210 ... 演算処理部      | 220 ... シリアルI F部   | 230 ... パラレルI F部  | 240 ... 送信バッファレジスタ | 26       |

| ... 受信シフトレジスタ         | 270 ... 受信バッファレジスタ | 280 ... シリアル管理部    | 10 ... 払出C P U    | 250 ... 送信シフトレジスタ  | 7        |

| 720 ... シリパラI Fチップ    | 730 ... パラレルI F部   | 740 ... 送信バッファレジスタ | 750 ... 送信シフトレジスタ | 760 ... 受信シフトレジスタ  | 77       |

| 750 ... 送信シフトレジスタ     | 760 ... 受信シフトレジスタ  | 770 ... 受信バッファレジスタ | 780 ... シリアル管理部   | 782 ... クリアレジスタ    | C B b    |

| ... セット信号             | F a ... アックフラグ     | F j ... ジョブフラグ     | D a b ... シリアルデータ | D b a ... シリアルデータ  | L        |

| L b s ... 送信レジスタ引渡期間  | L s c ... シリアル送信期間 | L                  |                   |                    | 50       |

wa...書込待機期間

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 秋山 大

愛知県北名古屋市沖村西ノ川1番地 株式会社大万内

(72)発明者 寺部 明伸

愛知県北名古屋市沖村西ノ川1番地 株式会社大万内

(72)発明者 加藤 肇

愛知県北名古屋市沖村西ノ川1番地 株式会社大万内

F ターム(参考) 2C088 BC54