(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6914245号

(P6914245)

(45) 発行日 令和3年8月4日(2021.8.4)

(24) 登録日 令和3年7月15日(2021.7.15)

|                         |              |

|-------------------------|--------------|

| (51) Int.Cl.            | F 1          |

| HO 1 L 25/065 (2006.01) | HO 1 L 25/08 |

| HO 1 L 25/07 (2006.01)  | HO 5 K 3/46  |

| HO 1 L 25/18 (2006.01)  | HO 5 K 3/46  |

| HO 5 K 3/46 (2006.01)   | HO 5 K 3/46  |

請求項の数 14 (全 31 頁)

|                    |                               |           |                                                                        |

|--------------------|-------------------------------|-----------|------------------------------------------------------------------------|

| (21) 出願番号          | 特願2018-503557 (P2018-503557)  | (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド                                          |

| (86) (22) 出願日      | 平成28年7月28日 (2016.7.28)        |           | アメリカ合衆国 カリフォルニア 921<br>21 サンディエゴ モアハウス ドラ<br>イブ 5775                   |

| (65) 公表番号          | 特表2018-523919 (P2018-523919A) | (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                 |

| (43) 公表日           | 平成30年8月23日 (2018.8.23)        | (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                 |

| (86) 國際出願番号        | PCT/US2016/044487             | (72) 発明者  | ホン・ボク・ワイ<br>アメリカ合衆国・カリフォルニア・921<br>21-1714・サン・ディエゴ・モアハ<br>ウス・ドライブ・5775 |

| (87) 國際公開番号        | W02017/019866                 |           |                                                                        |

| (87) 國際公開日         | 平成29年2月2日 (2017.2.2)          |           |                                                                        |

| 審査請求日              | 令和1年7月4日 (2019.7.4)           |           |                                                                        |

| (31) 優先権主張番号       | 14/812,476                    |           |                                                                        |

| (32) 優先日           | 平成27年7月29日 (2015.7.29)        |           |                                                                        |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |           |                                                                        |

最終頁に続く

(54) 【発明の名称】複数のダイを含むパッケージオンパッケージ(POP)構造

## (57) 【特許請求の範囲】

## 【請求項1】

空洞があけられたコア層と、

前記コア層の空洞内に位置する第1のダイと、

第2のダイと、

前記第1のダイと前記第2のダイとの間に配設されたフォトイメージング誘電体(PID)層と、

前記第1のダイから前記PID層を通って前記第2のダイに至る第1の導電性経路であつて、前記PID層の第1の領域を直接通つて前記第1のダイと前記第2のダイとの間で延びる、第1の導電性経路と、

前記第1のダイから前記PID層を通つて前記第2のダイに至る第2の導電性経路であつて、前記第2の導電性経路の特定の部分が前記第1の導電性経路に直角であり、前記第1のダイと前記第2のダイとの間で直接的にではなく、前記PID層の第2の領域を通つて延びる、第2の導電性経路とを備える、パッケージオンパッケージ(POP)構造。

## 【請求項2】

前記第1の導電性経路および前記第2の導電性経路が、前記第1のダイの第1の表面から前記第2のダイの第2の表面まで延びる、請求項1に記載のPOP構造。

## 【請求項3】

前記第1のダイから前記第2の導電性経路の前記特定の部分の第1の端部までの、前記第2の導電性経路の第1の部分が、前記第1の導電性経路に平行であり、前記第2の導電

性経路の前記特定の部分の第2の端部から前記第2のダイまでの、前記第2の導電性経路の第2の部分が、前記第1の導電性経路に平行である、請求項1に記載のPOP構造。

【請求項4】

前記PID層を通るビアをさらに備える、請求項1に記載のPOP構造。

【請求項5】

前記第1の導電性経路が、前記ビアを通って前記第2のダイまで延びる、請求項4に記載のPOP構造。

【請求項6】

前記第1の導電性経路が、シード層、前記ビア、第1の導電層、はんだ、および第2の導電層を通って前記第2のダイまで延びる、請求項4に記載のPOP構造。 10

【請求項7】

前記ビアが銅を含む、請求項4に記載のPOP構造。

【請求項8】

前記第1のダイがプロセッサを含む、請求項1に記載のPOP構造。

【請求項9】

前記プロセッサが、アプリケーションプロセッサ、デジタル信号プロセッサ、グラフィックスプロセッサ、またはそれらの組合せを備える、請求項8に記載のPOP構造。

【請求項10】

前記第2のダイがメモリを含む、請求項1に記載のPOP構造。

【請求項11】

前記メモリがキャッシュメモリを備える、請求項10に記載のPOP構造。 20

【請求項12】

前記第1のダイ、前記第2のダイ、および前記PID層が、コンピュータ、通信デバイス、携帯情報端末(PDA)、エンターテインメントユニット、ナビゲーションデバイス、音楽プレーヤ、ビデオプレーヤ、固定ロケーションデータユニット、セットトップボックス、またはそれらの組合せに組み込まれる、請求項1に記載のPOP構造。

【請求項13】

空洞があけられたコア層、前記コア層の空洞内に位置する第1のダイおよびフォトイメージング誘電体(PID)層を含む第1の集積回路(IC)をパッケージングするための第1の手段と、 30

第2のダイを含む第2のICをパッケージングするための第2の手段とを含み、前記第1のダイから前記PID層を通って前記第2のダイに至る第1の導電性経路が、前記PID層を直接通って前記第1のダイから前記第2のダイに延び、前記第1のダイから前記PID層を通って前記第2のダイに至る第2の導電性経路の一部が、前記第1の導電性経路に直角であり、前記第1のダイと前記第2のダイとの間で直接的にではなく、前記PID層の領域を通って延びる、装置。

【請求項14】

パッケージングするための前記第1の手段およびパッケージングするための前記第2の手段が、コンピュータ、通信デバイス、携帯情報端末(PDA)、エンターテインメントユニット、ナビゲーションデバイス、音楽プレーヤ、ビデオプレーヤ、固定ロケーションデータユニット、セットトップボックス、またはそれらの組合せに組み込まれる、請求項13に記載の装置。 40

【発明の詳細な説明】

【技術分野】

【0001】

優先権の主張

本出願は、参照によりその内容全体が本明細書に明確に組み込まれる、同一出願人が所有する2015年7月29日に出願の米国非仮特許出願第14/812,476号の優先権を主張する。

【0002】

10

20

30

40

50

本開示は、一般に、複数のダイを含むパッケージオンパッケージ（POP）構造に関する。

#### 【背景技術】

##### 【0003】

技術の進歩は、より小型で、より強力なコンピューティングデバイスをもたらしてきた。たとえば、小型で軽量であり、ユーザによって容易に携帯される、モバイルフォンおよびスマートフォンなどのワイヤレス電話、タブレットおよびラップトップコンピュータを含む、様々なポータブルパーソナルコンピューティングデバイスが存在する。これらのデバイスは、ワイヤレスネットワークを介して音声およびデータパケットを伝達することができる。さらに、多くのそのようなデバイスは、デジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤなどの追加の機能を組み込んでいる。また、そのようなデバイスは、インターネットへのアクセスに使用することができるウェブブラウザアプリケーションなどのソフトウェアアプリケーションを含む、実行可能命令を処理することができる。したがって、これらのデバイスは、高度の計算能力を含むことができる。

10

##### 【0004】

ワイヤレス電話などの電子デバイスは、半導体デバイス内の集積回路を含み得る。半導体デバイスは、第1の集積回路（IC）パッケージと第2のICパッケージとを含み得る。第1のICパッケージはメモリを含んでよく、第2のICパッケージはプロセッサを含んでもよい。第1のICパッケージおよび第2のICパッケージは同一平面内にあってもよい。金属トレースは、第1のICパッケージと第2のICパッケージとの間に経路を形成するために使用され得る。

20

#### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

第1のICパッケージと第2のICパッケージとの間の導電性経路の数は、その数が増えると半導体デバイスを製造する複雑さおよびコストが実質的に増加する場合があるため、制限される場合がある。

##### 【課題を解決するための手段】

##### 【0006】

30

本開示は、第1のダイおよび第2のダイを含むパッケージオンパッケージ（POP）構造を提供する。フォトイメージング誘電体（PID）層は、第1のダイと第2のダイとの間に配設され得る。POP構造は、第1のダイからPID層を通って第2のダイに至る1つまたは複数の導電性経路を含み得る。

##### 【0007】

特定の態様では、パッケージオンパッケージ（POP）構造は、第1のダイと、第2のダイと、フォトイメージング誘電体（PID）層とを含む。PID層は、第1のダイと第2のダイとの間に配設される。また、POP構造は、第1のダイからPID層を通って第2のダイに至る第1の導電性経路を含む。第1の導電性経路は、PID層の第1の領域を直接的に通って第1のダイと第2のダイとの間で直接的に延びる。POP構造は、第1のダイからPID層を通って第2のダイに至る第2の導電性経路をさらに含む。第2の導電性経路の一部は第1の導電性経路に直角であり、第1のダイと第2のダイとの間で直接的にではなく、PID層の第2の領域を通って延びる。

40

##### 【0008】

別の態様では、パッケージオンパッケージ（POP）構造を形成する方法は、フォトイメージング可能誘電体材料を、第1のダイが埋め込まれているパッケージの表面上に堆積させるステップを含む。また、方法は、フォトイメージング誘電体（PID）層を形成するためにフォトイメージング可能誘電体材料をパテーニングするステップを含む。方法は、PID層を通って第1のダイに至る第1の導電性経路および第2の導電性経路を形成するために導電材料をPID層上に堆積させるステップをさらに含む。また、方法は、第2

50

のダイが第1の導電性経路および第2の導電性経路を介して第1のダイに電気的に接続されるように、第2のダイをパッケージに結合するステップを含む。第1の導電性経路は、P I D層を通じて第1のダイから第2のダイに直接的に延びる。第2の導電性経路の一部は第1の導電性経路に直角であり、第1のダイと第2のダイとの間で直接的にではなく、P I D層の領域を通じて延びる。

【0009】

別の態様では、パッケージオンパッケージ（P O P）構造を形成するための方法は、フォトイメージング可能誘電体材料を、第1のダイが埋め込まれているパッケージの表面上に堆積させるステップを含む。また、方法は、フォトイメージング誘電体（P I D）層を形成するためにフォトイメージング可能誘電体材料をパターニングするステップを含む。方法は、第1のダイからP I D層を経由して第2のダイに至る第1の導電性経路および第2の導電性経路を形成するステップをさらに含む。第1の導電性経路は、P I D層を通じて第1のダイから第2のダイに直接的に延びる。第2の導電性経路の一部は第1の導電性経路に直角であり、第1のダイと第2のダイとの間で直接的にではなく、P I D層の領域を通じて延びる。

【0010】

開示する態様のうちの少なくとも1つによって提供される1つの特有の利点は、パッケージオンパッケージ（P O P）構造が、第1のダイと第2のダイとの間の他の導電性経路に加えて真っすぐな導電性経路を含み得ることである。第1のダイと第2のダイとの間で直接的に延びるいくつかの導電性経路を有することで、P O P構造を製造する複雑さおよびコストが低減され得る。別の特有の利点は、P I D層を含むP O P構造が、P I D層を除外する別の同様のサイズのP O P構造より多数の導電性経路を第1のダイと第2のダイとの間に含み得ることである。たとえば、P I D層を通るフォトビアは、スルーシリコンビア（T S V）より薄い（たとえば、より小さい直徑を有する）場合がある。P I D層を有するP O P構造は、P I D層を除外する別の同様のサイズのP O P構造より多数の導電性経路を第1のダイと第2のダイとの間に含み得る。なぜならば、P I D層のフォトビアを通る各導電性経路は、P I D層を除外するP O P構造のT S Vを通る導電性経路より薄い場合があるからである。第1のダイは、第2のダイと異なるサイズを有し得る。たとえば、P O P構造は、第1のダイの第1の表面から第2のダイの第2の表面に至る導電性経路を含み得る。第1の表面は、第2の表面の第2の表面領域より大きい（または小さい）第1の表面領域を有し得る。第1の表面と第2の表面との間で真っすぐな導電性経路に直角である一部を有するいくつかの導電性経路を有することで、P O P構造が第1の表面の一部と第2の表面との間で導電性経路を有することが可能になる場合があり、ここで第1の表面の一部は第2の表面を越えて延びる。

【0011】

本開示の他の態様、利点、および特徴は、以下のセクション、すなわち、図面の簡単な説明、発明を実施するための形態、および特許請求の範囲を含む本出願全体の検討後に明らかになるであろう。

【図面の簡単な説明】

【0012】

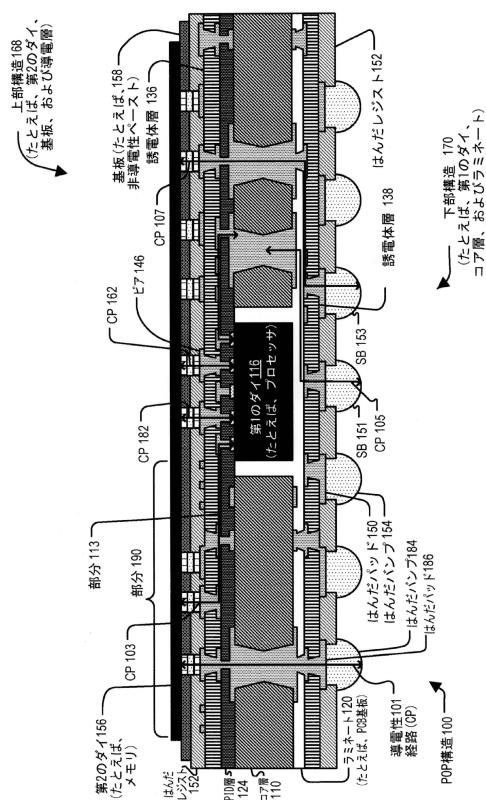

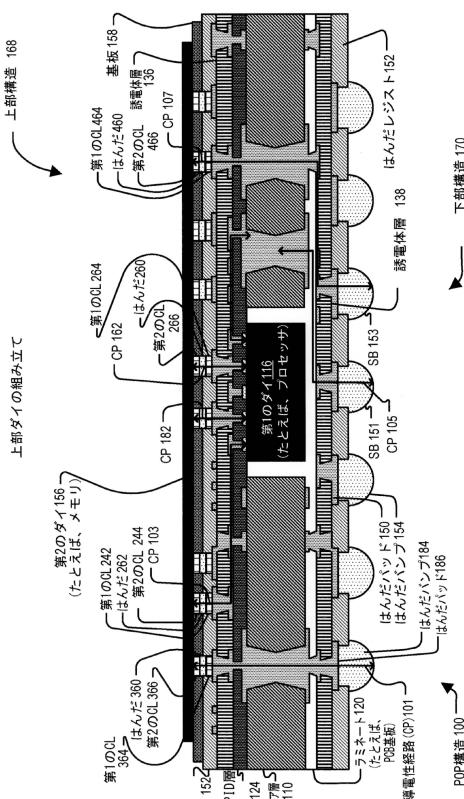

【図1】パッケージオンパッケージ（P O P）構造の断面図である。

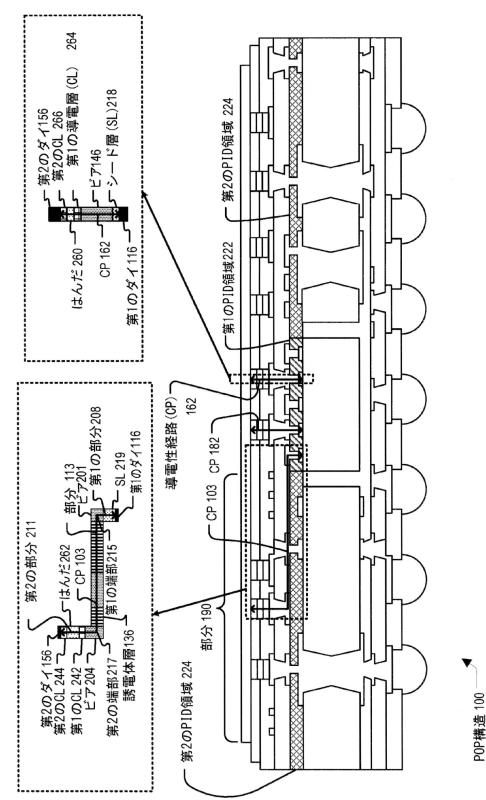

【図2】図1のP O P構造の横断面図を示す図である。

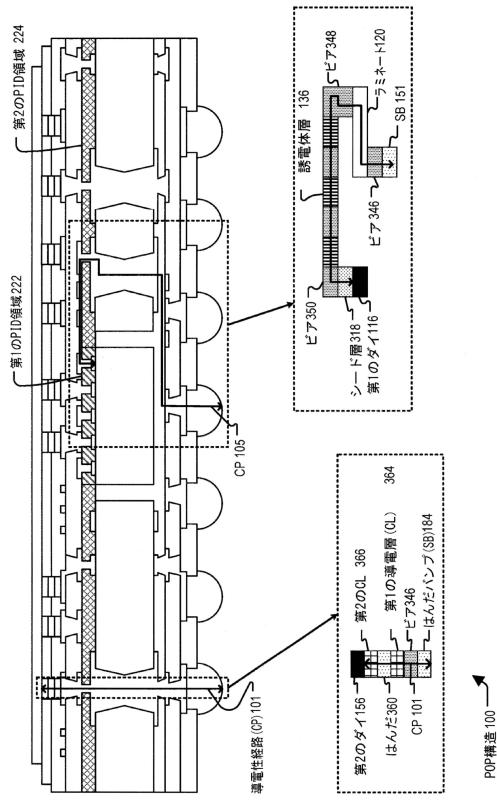

【図3】図1のP O P構造の横断面図を示す図である。

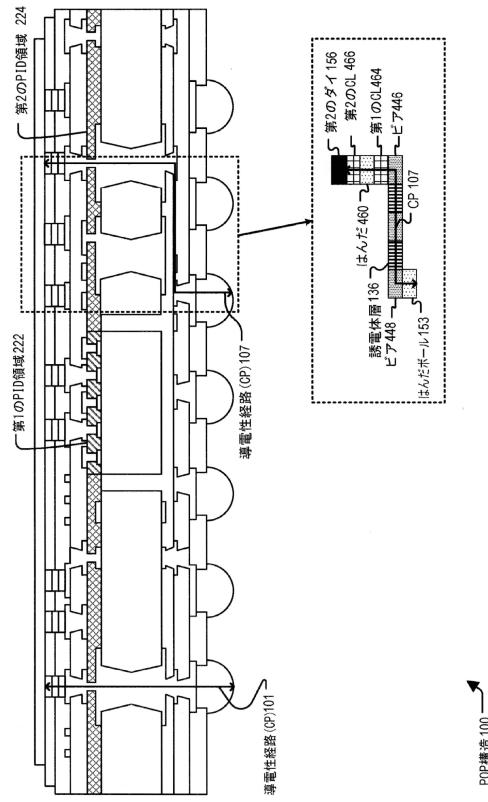

【図4】図1のP O P構造の横断面図を示す図である。

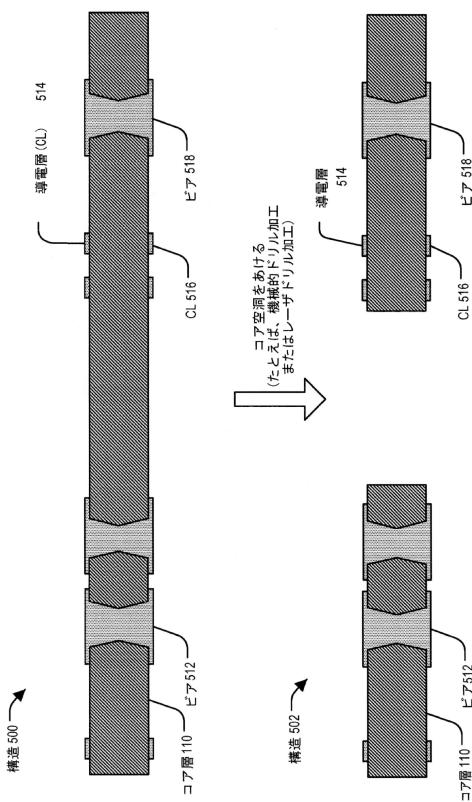

【図5】図1のP O P構造を作製する少なくとも1つの段階の間に形成された構造の横断面図を示す図である。

【図6】図1のP O P構造を作製する少なくとも1つの段階の間に形成された構造の横断面図を示す図である。

【図7】図1のP O P構造を作製する少なくとも1つの段階の間に形成された構造の横断面図を示す図である。

10

20

30

40

50

【図 8】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

【図 9】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

【図 10】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

【図 11】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

【図 12】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

10

【図 13】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

【図 14】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

【図 15】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

【図 16】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

【図 17】図 1 の P O P 構造を作製する少なくとも 1 つの段階の間に形成された構造の横断面図を示す図である。

20

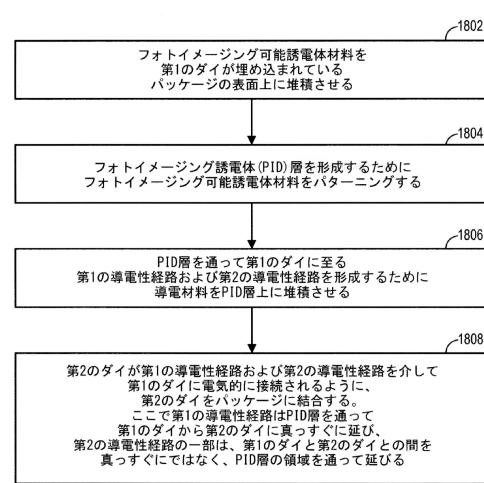

【図 18】図 1 の P O P 構造を形成する方法の特定の例示的な態様のフローチャートである。

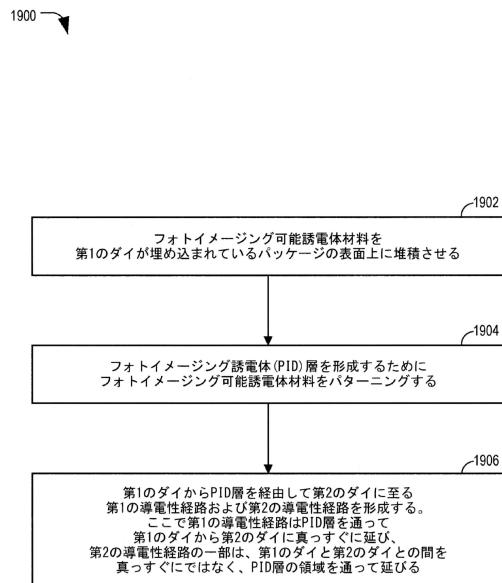

【図 19】図 1 の P O P 構造を形成する方法の別の態様のフローチャートである。

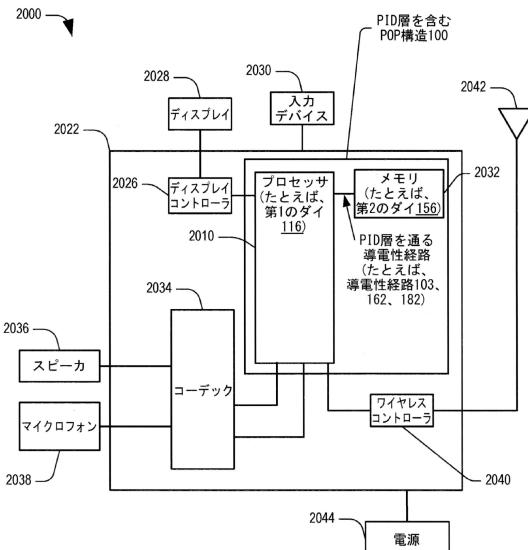

【図 20】P O P 構造を含む電子デバイスのブロック図である。

【図 21】P O P 構造を含む電子デバイスを製造するための製造プロセスの特定の例示的な態様のデータフロー図である。

【発明を実施するための形態】

【0013】

図 1 を参照すると、パッケージオンパッケージ ( P O P ) 構造の特定の例示的な態様が開示され、全体が 100 で示されている。P O P 構造 100 は、第 1 のダイ 116 ( たとえば、プロセッサ ) と第 2 のダイ 156 ( たとえば、メモリ ) とを含む。第 1 のダイ 116 は、アプリケーションプロセッサ ( A P ) 、デジタル信号プロセッサ ( D S P ) 、グラフィックスプロセッサ、または別のプロセッサのうちの少なくとも 1 つを含み得る。第 2 のダイ 156 は、キャッシュメモリ、別のメモリまたは両方を含み得る。特定の実装形態では、第 1 のダイ 116 はメモリ ( たとえば、キャッシュメモリ、別のメモリまたは両方 ) を含んでよく、第 2 のダイ 156 はプロセッサ ( たとえば、アプリケーションプロセッサ ( A P ) 、デジタル信号プロセッサ ( D S P ) 、グラフィックスプロセッサ、または別のプロセッサ ) を含んでもよい。

30

【0014】

第 1 のダイ 116 は、第 2 のダイ 156 の第 2 の寸法 ( たとえば、第 2 の高さ、第 2 の幅、および第 2 の長さ ) とは異なる第 1 の寸法 ( たとえば、第 1 の高さ、第 1 の幅、および第 1 の長さ ) を有し得る。たとえば、第 1 の高さは第 2 の高さと異なってよく、第 1 の幅は第 2 の幅と異なってよく、第 1 の長さは第 2 の長さと異なってよく、またはそれらの組合せであってもよい。

40

【0015】

フォトイメージング誘電体 ( P I D ) 層 124 ( たとえば、ポリアミド層 ) は、第 1 のダイ 116 と第 2 のダイ 156 との間に配設され得る。P O P 構造 100 は、上部構造 168 ( たとえば、上部パッケージ ) と下部構造 170 ( たとえば、下部パッケージ ) とを含み得る。下部構造 170 は、第 1 のダイ 116 とコア層 110 とを含み得る。コア層 110 は、シリコン ( S i ) 、有機材料または両方を含み得る。

50

## 【0016】

特定の態様では、下部構造 170 はまた、ラミネート 120、P I D 層 124、誘電体層 136、誘電体層 138、はんだレジスト 152、1つまたは複数のシード層、ピア 146、1つまたは複数の導電層、はんだパッド 150、はんだパッド 186、はんだバンプ 151、はんだバンプ 153、はんだバンプ 154、およびはんだバンプ 184 を含み得る。ラミネート 120 は、プリント回路基板 (P C B) 基板材料 (たとえば、ポリマー樹脂) を含み得る。ラミネート 120 は、非導電材料を含み得る。誘電体層 136、誘電体層 138 または両方は、ポリイミド、ベンゾシクロブテン (B C B)、シリコン、ハフニウム、ジルコニウム、バリウム、チタン、またはそれらの組合せの成分を含み得る。たとえば、誘電体層 136、誘電体層 138 または両方は、一酸化ケイ素、二酸化ケイ素、窒化ケイ素、酸化ハフニウム、酸化ジルコニウム、チタン酸バリウム、酸化チタン、またはそれらの組合せを含み得る。はんだレジスト 152 (たとえば、はんだマスク) は、ポリマーを含み得る。1つまたは複数のシード層は、銅または他の金属を含み得る。ピア 146、1つまたは複数の導電層、またはそれらの組合せは、導電材料 (たとえば銅、スズ、ニッケル、または別の金属) を含み得る。はんだパッド 150、はんだパッド 186、はんだバンプ 151、はんだバンプ 153、はんだバンプ 154、はんだバンプ 184、またはそれらの組合せは、可溶性金属合金を含み得る。たとえば、はんだパッド 150、はんだパッド 186、はんだバンプ 151、はんだバンプ 153、はんだバンプ 154、はんだバンプ 184、またはそれらの組合せは、スズ、鉛、銅、銀、ビスマス、インジウム、亜鉛、またはアンチモンのうちの少なくとも 1 つを含み得る。

10

20

## 【0017】

上部構造 168 は、第 2 のダイ 156、1つまたは複数の第 2 の導電層、および基板 158 (たとえば、メモリ基板) を含み得る。1つまたは複数の第 2 の導電層は、導電材料 (たとえば銅、スズ、ニッケル、または別の金属) を含み得る。基板 158 は、非導電性ペースト (たとえば、非導電性ポリマーペースト) を含み得る。

## 【0018】

P O P 構造 100 は、第 1 のダイ 116 から P I D 層 124 を通って第 2 のダイ 156 に至る 1 つまたは複数の導電性経路を含み得る。たとえば、P O P 構造 100 は、図 2 を参照しながらさらに説明するように、第 1 のダイ 116 からピア 146 (たとえば、金属ピア) を通って第 2 のダイ 156 に至る導電性経路 (C P) 162 を含む。ピア 146 は、P I D 層 124 を通過し得る。別の例として、P O P 構造 100 は、第 1 のダイ 116 から第 2 のダイ 156 に至る C P 182、C P 103 または両方を含み得る。

30

## 【0019】

P O P 構造 100 は、P O P 構造 100 の第 1 のダイ 116 からはんだバンプに至る 1 つまたは複数の導電性経路を含み得る。たとえば、P O P 構造 100 は、第 1 のダイ 116 から P I D 層 124 を通ってはんだバンプ 151 に至る C P 105 を含み得る。

## 【0020】

P O P 構造 100 は、P O P 構造 100 の第 2 のダイ 156 からはんだバンプに至る 1 つまたは複数の導電性経路を含み得る。たとえば、P O P 構造 100 は、第 2 のダイ 156 から P I D 層 124 を通ってはんだバンプ 153 に至る C P 107 を含み得る。別の例として、P O P 構造 100 は、第 2 のダイ 156 から P I D 層 124 を通ってはんだバンプ 184 に至る C P 101 を含み得る。C P 101 は、第 2 のダイ 156 からはんだバンプ 184 に至る真っすぐな (または実質的に真っすぐな) 経路を含み得る。

40

## 【0021】

P O P 構造 100 は、P I D 層 124 を通って第 1 のダイ 116 から第 2 のダイ 156 まで直接的に延びる 1 つまたは複数の導電性経路 (たとえば、C P 162、C P 182 または両方) を含み得る。C P 162、C P 182 または両方は、第 1 のダイ 116 と第 2 のダイ 156 との間の真っすぐな (または実質的に真っすぐな) 経路であり得る。C P 103、C P 162、C P 182、またはそれらの組合せは、第 1 のダイ 116 の第 1 の表面から第 2 のダイ 156 の第 2 の表面まで延び得る。第 1 のダイ 116 の第 1 の表面は、

50

第2のダイ156の第2の表面に対向することができる。CP101は、CP162、CP182または両方に平行（または実質的に平行）であり得る。CP103は、図2を参照しながらさらに説明するように、導電性経路162、導電性経路182または両方に直角（またはほぼ直角）である少なくとも1つの部分（たとえば、部分113）を含み得る。第2のダイ156は、CP162、CP182または両方に直角（またはほぼ直角）である軸（たとえば、図1の水平軸）に沿って第1のダイ116を越えて延びる少なくとも1つの部分（たとえば、部分190）を含み得る。CP103は、第1のダイ116の第1の表面から第2のダイ156の第2の表面まで延び得る。たとえば、CP103は、第1のダイ116の第1の表面から第2のダイ156の第2の表面に対応する部分190の表面まで延び得る。CP162、CP182または両方に直角（またはほぼ直角）である部分113を有することで、CP103は第2のダイ156の部分190から第1のダイ116まで延びることが可能になり、ここで部分190は、図1の水平軸に沿って第1のダイ116を越えて延びる。

#### 【0022】

PID層124を通るフォトビア（たとえば、ビア146）は、スルーシリコンビア（TSV）より薄い（たとえば、より小さい直径を有する）場合がある。PID層124を有するPOP構造100は、PID層124を除外する別の同様のサイズのPOP構造より多数の導電性経路を含み得る。

#### 【0023】

POP構造100は、図5～図8を参照しながら説明するように、第1のダイ116をコア層110内に埋め込むことによって、および図9～図17を参照しながら説明するように、導電性経路101、103、105、107、162および182を形成することによって形成され得る。特定の態様では、POP構造100は、図11を参照しながら説明するように、PID層124を形成するためにフォトイメージング可能誘電体材料を下部構造170上に堆積させることによって、および図12～図17を参照しながら説明するように、導電性経路101、103、105、107、162および182を形成することによって形成され得る。

#### 【0024】

本明細書で説明する図2～図4は、図1のPOP構造100の横断面図を示す。POP構造100の導電性経路の様々な態様は、図2～図4を参照しながらさらに説明する。

#### 【0025】

図2を参照すると、POP構造100の横断面図の例示的な図が示されている。POP構造100は、CP103、CP162または両方を含み得る。

#### 【0026】

CP103は、CP162、CP182または両方に直角（またはほぼ直角）である少なくとも1つの部分（たとえば、部分113）を含み得る。部分113は、第1の端部215から第2の端部217まで延び得る。第1のダイ116から第1の端部215に至るCP103の第1の部分208は、CP162、CP182または両方に平行（または実質的に平行）であり得る。第2の端部217から第2のダイ156に至るCP103の第2の部分211は、CP162、CP182または両方に平行（または実質的に平行）であり得る。

#### 【0027】

第1の部分208は、第1のダイ116からシード層（SL）219を通ってビア201まで延び得る。ビア201は、PID層124を通過し得る。部分113は、第1の端部215におけるビア201から第2の端部217におけるビア204まで延び得る。部分113は、誘電体層136の1つまたは複数の部分、およびビア201とビア204との間の1つまたは複数のビアを通過し得る。第2の部分211は、ビア204から第1の導電層（CL）242、はんだ262および第2のCL244を通って第2のダイ156まで延び得る。第2の部分211は、部分190まで延び得る。部分190は、部分113に平行である軸（たとえば、図2の水平軸）に沿って第1のダイ116を越えて延

10

20

30

40

50

び得る。

【0028】

C P 1 6 2 は、第1のダイ116からS L 2 1 8、ビア146、第1のC L 2 6 4、はんだ260、および第2のC L 2 6 6 を通って第2のダイ156まで延び得る。C P 1 6 2 は、第1のダイ116と第2のダイ156との間の真っすぐな（たとえば、実質的に真っすぐな）経路を含み得る。特定の態様では、図1の上部構造168は、第2のC L 2 6 6 を含み得る。

【0029】

S L 2 1 8、S L 2 1 9 または両方は、銅または他の金属を含み得る。ビア201、ビア204、第1のC L 2 4 2、第2のC L 2 4 4、第1のC L 2 6 4、第2のC L 2 6 6 10 、またはそれらの組合せは、導電材料（たとえば、銅、スズ、ニッケル、または別の金属）を含み得る。はんだ260、はんだ262 または両方は、可溶性金属合金を含み得る。はんだ260、はんだ262 または両方は、導電材料を含み得る。

【0030】

P I D層124は、第1のダイ116と第2のダイ156との間で真っすぐな第1のP I D領域222を含み得る。たとえば、第1のP I D領域222は、図2の水平軸に沿って第1のダイ116と重複し得る。P I D層124は、第1のダイ116と第2のダイ156との間で直接的ではない第2のP I D領域224を含み得る。たとえば、第2のP I D領域224は、第1のダイ116を越えて図2の水平軸に沿って一方または両方に延び得る。説明のために、第2のP I D領域224の第1の部分は、第1のダイ116を越えて図2の水平軸に沿って第1の方向に延びてよく、第2のP I D領域224の第2の部分は、第1のダイ116を越えて図2の水平軸に沿って第2の方向に延びてもよい。第2のP I D領域224は、（たとえば、図2の垂直軸に沿って）第1のダイ116と第2のダイ156との間にあり得る。しかしながら、第2のP I D領域224の表面に直角の平面は第2のダイ156と交差するが、第1のダイ116と交差しないので、第2のP I D領域224は、第1のダイ116と第2のダイ156との間で直接的になり得ない。第2のP I D領域224は、図2の水平軸に沿って第2のダイ156と重なることができる（たとえば、P I D領域224は、図2の水平軸に沿った一方向に第1のダイ116を越えて延び得る）。

【0031】

C P 1 6 2、C P 1 8 2 または両方は、第1のP I D領域222を通って第1のダイ116から第2のダイ156まで延び得る。第1の部分208は、第1のダイ116から第1のP I D領域222を通って第1の端部215まで延び得る。部分113は、第1の端部215から第1のP I D領域222、第2のP I D領域224 または両方を通って第2の端部217まで延び得る。第2の部分211は、第2の端部217から第2のP I D領域224を通って第2のダイ156まで延び得る。

【0032】

P O P構造100は、第1のダイ116と第2のダイ156との間で複数の導電性経路を含み得る。第1のダイ116と第2のダイ156との間の導電性経路のうちのいくつかは、真っすぐ（または実質的に真っすぐ）であり得る。真っすぐな導電性経路は、P I D層を通って第1のダイ116から第2のダイ156に直接的に延び得る。第1のダイ116と第2のダイ156との間の他の導電性経路は、第1のダイ116と第2のダイ156との間の真っすぐな導電性経路に直角（またはほぼ直角）である部分を含み得る。直角（またはほぼ直角）の部分を含む導電性経路は、第1のダイ116から第2のダイ156の部分190まで延び得る。直角の部分は、第1のダイ116と第2のダイ156との間で直接的にではなく、P I D層の領域（たとえば、第2のP I D領域224）を通って延び得る。たとえば、直角の部分は、図2の水平軸に沿って第1の方向に第1のダイ116を越えて延びる第2のP I D領域224の部分を通って延び得る。部分190は、ある軸（たとえば、図2の水平軸）に沿って第1のダイ116を越えて延び得る。

【0033】

10

20

30

40

50

図3を参照すると、POP構造100の横断面図の例示的な図が示されている。POP構造100は、CP101、CP105または両方を含み得る。

【0034】

CP101は、はんだバンプ(SB)184からビア346、第1のCL364、はんだ360および第2のCL366を通じて第2のダイ156まで延び得る。CP101は、SB184から第2のダイ156に至る真っすぐな(または実質的に真っすぐな)経路を含み得る。ビア346の少なくとも一部は、図1のPID層124を通過し得る。特定の態様では、ビア346は、複数のビアを含み得る。たとえば、ビア346は、誘電体層138を通じて延びる第1のビア、ラミネート120を通じて延びる第2のビア、コア層110を通じて延びる第3のビア、PID層124を通じて延びる第4のビア、誘電体層136を通じて延びる第5のビア、またはそれらの組合せを含み得る。第4のビアは、第2のPID領域224を通じて延び得る。

【0035】

CP105は、SB151からビア346、ラミネート120、ビア348、1つまたは複数の追加のビア、誘電体層136の1つまたは複数の部分、ビア350、およびシード層318を通じて第1のダイ116まで延び得る。ビア350は、第1のPID領域222を通じて延び得る。CP105の少なくとも一部は、CP101に直角(またはほぼ直角)であり得る。たとえば、ビア350からビア348までのCP105の一部は、CP101に直角(またはほぼ直角)であり得る。ビア348は、第2のPID領域224を通じて延び得る。CP105の少なくとも一部は、CP101に平行(または実質的に平行)であり得る。たとえば、ビア350から第1のダイ116に至るCP105の一部は、CP101に平行(または実質的に平行)であり得る。別の例として、ラミネート120からSB151に至るCP105の一部は、CP101に平行(または実質的に平行)であり得る。

【0036】

SB184、SB151、はんだ360またはそれらの組合せは、可溶性金属合金を含み得る。ビア346、ビア348、1つまたは複数の追加のビア、第1のCL364、第2のCL366、またはそれらの組合せは、導電材料(たとえば、銅、スズ、ニッケル、または別の金属)を含み得る。シード層318は、銅または他の金属を含み得る。はんだ360は、導電材料を含み得る。はんだ360は、可溶性金属合金を含み得る。

【0037】

POP構造100は、ダイからはんだバンプに至る導電性経路を含み得る。たとえば、POP構造100は、第2のダイ156からはんだバンプに至る真っすぐな(または実質的に真っすぐな)導電性経路を含み得る。第2のダイ156とはんだバンプとの間の導電性経路は、電力経路または信号経路に対応し得る。別の例として、POP構造100は、第1のダイ116からはんだバンプに至る導電性経路を含み得る。第1のダイ116とはんだバンプとの間の導電性経路は、電力経路または信号経路に対応し得る。

【0038】

図4を参照すると、POP構造100の横断面図の例示的な図が示されている。POP構造100は、CP107を含み得る。

【0039】

CP107は、はんだボール153からビア448、誘電体層136の1つまたは複数の部分、1つまたは複数の追加のビア、ビア446、第1のCL464、はんだ460、および第2のCL466を通じて第2のダイ156まで延び得る。ビア446の少なくとも一部は、図1のPID層124を通過し得る。CP107の少なくとも一部は、CP101に平行(または実質的に平行)であり得る。たとえば、ビア448からはんだボール153まで延びるCP107の一部は、CP101に平行(または実質的に平行)であり得る。別の例として、ビア446から第2のダイ156まで延びるCP107の一部は、CP101に平行(または実質的に平行)であり得る。CP107の少なくとも一部は、CP101に直角(またはほぼ直角)であり得る。たとえば、ビア448からビア446

まで延びる C P 1 0 7 の一部は、 C P 1 0 1 に直角（またはほぼ直角）であり得る。特定の態様では、ビア 4 4 6 は、複数のビアを含み得る。たとえば、ビア 4 4 6 は、ラミネート 1 2 0 を通って延びる第 1 のビア、コア層 1 1 0 を通って延びる第 2 のビア、 P I D 層 1 2 4 を通って延びる第 3 のビア、誘電体層 1 3 6 を通って延びる第 4 のビア、またはそれらの組合せを含み得る。第 3 のビアは、第 2 の P I D 領域 2 2 4 を通って延び得る。ビア 4 4 8 は、誘電体層 1 3 8 を通って延び得る。

【 0 0 4 0 】

はんだボール 1 5 3 、はんだ 4 6 0 または両方は、可溶性金属合金を含み得る。ビア 4 4 8 、 1 つまたは複数の追加のビア、ビア 4 4 6 、またはそれらの組合せは、導電材料（たとえば、銅、スズ、ニッケル、または別の金属）を含み得る。はんだ 4 6 0 は、可溶性金属合金を含み得る。はんだ 4 6 0 は、導電材料を含み得る。

10

【 0 0 4 1 】

P O P 構造 1 0 0 は、ダイからはんだバンプに至る複数の導電性経路を含み得る。たとえば、P O P 構造 1 0 0 は、第 2 のダイ 1 5 6 からはんだバンプに至る導電性経路を含み得る。第 2 のダイ 1 5 6 とはんだバンプとの間の導電性経路は、電力経路または信号経路に対応し得る。導電性経路は、第 2 のダイ 1 5 6 とはんだバンプとの間に真っすぐな（または実質的に真っすぐな）経路を含み得る。代替として、導電性経路は、第 2 のダイ 1 5 6 と別のはんだバンプとの間に、真っすぐな導電性経路に直角（またはほぼ直角）である部分を含み得る。

【 0 0 4 2 】

20

本明細書で説明するように、図 5 ~ 図 1 7 は、図 1 の P O P 構造 1 0 0 を作製する特定の段階の間に形成される構造の横断面図を示す。特定の態様では、図 5 ~ 図 1 7 に示す各構造は、電子デバイス（たとえば、半導体デバイス）を作製する特定の段階の間に形成される。電子デバイスは、P O P 構造 1 0 0 を含み得る。

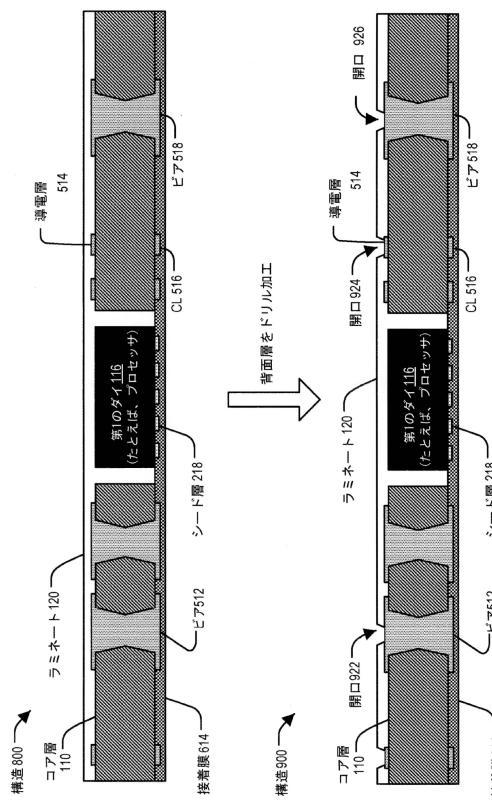

【 0 0 4 3 】

図 5 を参照すると、構造の横断面図の例示的な図が示され、全体が 5 0 0 で示されている。構造 5 0 0 は、図 1 の P O P 構造 1 0 0 を作製するプロセスにおいて少なくとも 1 つの段階の間に形成され得る。特定の態様では、構造 5 0 0 は、事前作製され得る。構造 5 0 0 は、図 1 のコア層 1 1 0 を含み得る。コア層 1 1 0 は、1 つまたは複数のビア（たとえば、ビア 5 1 2 、ビア 5 1 8 または両方）を含み得る。1 つまたは複数のビア（たとえば、ビア 5 1 2 、ビア 5 1 8 または両方）は、銅または他の金属を含み得る。コア層 1 1 0 の表面は、1 つまたは複数の導電層（たとえば、C L 5 1 4 、C L 5 1 6 または両方）を含み得る。1 つまたは複数の導電層（たとえば、C L 5 1 4 、C L 5 1 6 または両方）は、銅または他の金属を含み得る。構造 5 0 2 は、コア層 1 1 0 内に空洞をあけることによって形成され得る。たとえば、空洞は、機械的ドリル加工またはレーザドリル加工によって形成され得る。

30

【 0 0 4 4 】

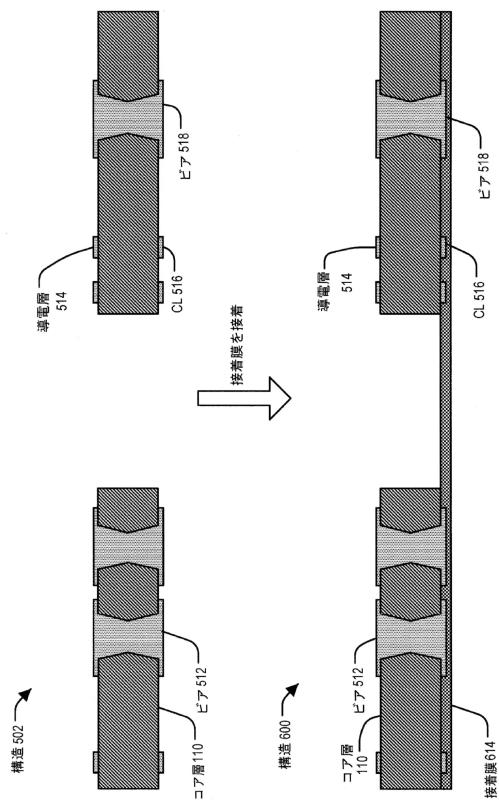

図 6 を参照すると、構造の横断面図の例示的な図が示され、全体が 6 0 0 で示されている。構造 6 0 0 は、図 1 の P O P 構造 1 0 0 を作製するプロセスにおいて少なくとも 1 つの段階の間に形成され得る。構造 6 0 0 は、接着膜 6 1 4 を図 5 の構造 5 0 2 に接着することによって形成され得る。たとえば、接着膜 6 1 4 は、コア層 1 1 0 の残りの部分が接着膜 6 1 4 上で離間されるように、コア層 1 1 0 に接着され得る。接着膜 6 1 4 は、粘着テープ（たとえば、ポリエチレンテープ）またはエポキシ接着剤を含み得る。

40

【 0 0 4 5 】

図 7 を参照すると、構造の横断面図の例示的な図が示され、全体が 7 0 0 で示されている。構造 7 0 0 は、図 1 の P O P 構造 1 0 0 を作製するプロセスにおいて少なくとも 1 つの段階の間に形成され得る。構造 7 0 0 は、第 1 のダイ 1 1 6 を図 6 の構造 6 0 0 上に設置することによって形成され得る。たとえば、第 1 のダイ 1 1 6 は、コア層 1 1 0 の残りの部分によって形成されるギャップ内の接着膜 6 1 4 上に、表を下にして設置され得る。1 つまたは複数のシード層（たとえば、シード層（S L ）2 1 8 、S L 2 1 9 、S L 3 1

50

8、またはそれらの組合せ)は、第1のダイ116に接着され得る。第1のダイ116を接着膜614上に設置するステップは、第1のダイ116を1つまたは複数のシード層(たとえば、SL118、SL219、SL318、またはそれらの組合せ)および接着膜614の上に設置する前に、1つまたは複数のシード層を接着膜614上に設置するステップを含み得る。

【0046】

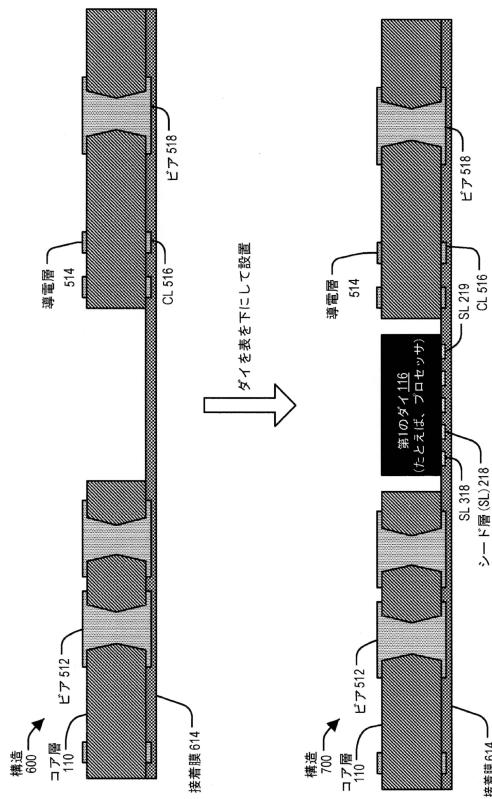

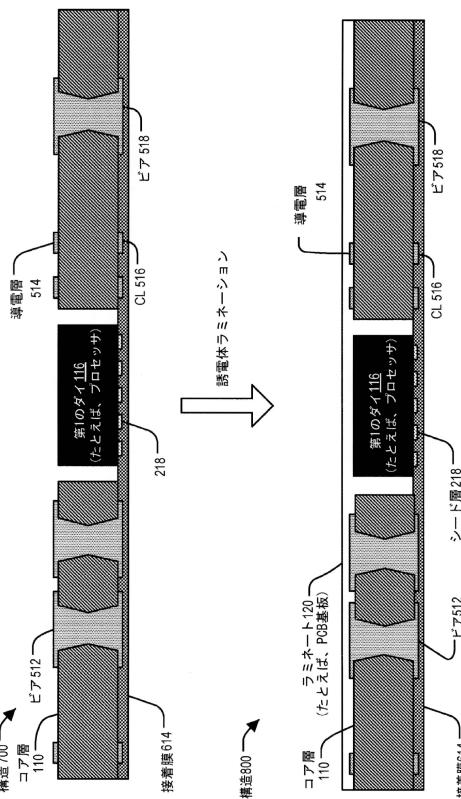

図8を参照すると、構造の横断面図の例示的な図が示され、全体が800で示されている。構造800は、図1のPOP構造100を作製するプロセスにおいて少なくとも1つの段階の間に形成され得る。構造800は、図7の構造700をラミネートすることによって形成され得る。たとえば、ラミネート120は、第1のダイ116を接着膜614上に設置した後で構造700上に堆積され得る。ラミネート120は、コア層110および第1のダイ116の上に液体状態で堆積され得る。ラミネート120は、第1のダイ116とコア層110との間の1つまたは複数のギャップを充填し得る。ラミネート120は、固体状態に遷移し得る。たとえば、ラミネート120を固化させるために、熱が構造800に加えられてもよい。

10

【0047】

図9を参照すると、構造の横断面図の例示的な図が示され、全体が900で示されている。構造900は、図1のPOP構造100を作製するプロセスにおいて少なくとも1つの段階の間に形成され得る。構造900は、図8の構造800をドリル加工することによって形成され得る。たとえば、ラミネート120の部分は、1つまたは複数の開口(たとえば、開口922、開口924、開口926、またはそれらの組合せ)を形成するためにドリル加工され得る。開口922は、ビア512上に(たとえば、ビア512と位置合わせされて)形成され得る。開口924は、導電層514上に(または導電層514と位置合わせされて)形成され得る。開口926は、ビア518上に(たとえば、ビア518と位置合わせされて)形成され得る。

20

【0048】

図10を参照すると、構造の横断面図の例示的な図が示され、全体が1000で示されている。構造1000は、図1のPOP構造100を作製するプロセスにおいて少なくとも1つの段階の間に形成され得る。構造1000は、接着膜614を図9の構造900から除去することによって形成され得る。特定の態様では、接着膜614は、はぎ取られる場合がある。代替態様では、粘着剝離剤(たとえば、エボキシ溶媒)が、接着膜614を除去するために構造900に塗布され得る。特定の態様では、接着膜614は、図9の1つまたは複数のビア(たとえば、開口922、開口924、開口926、またはそれらの組合せ)を形成する前に除去され得る。たとえば、接着膜614は、図8の構造800から除去されてよく、開口922は、接着膜614を除去した後に形成されてもよい。構造1000は、接着膜614を除去した後に(または除去する前に)反転され得る(たとえば、180度回転され得る)。

30

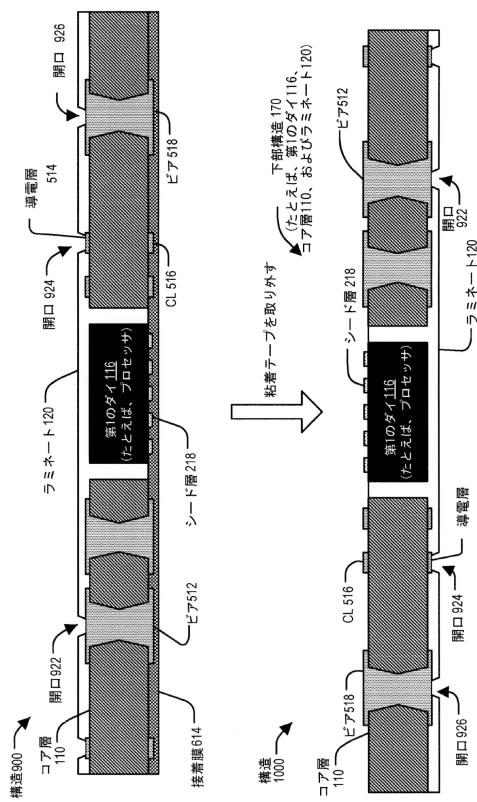

【0049】

図11を参照すると、構造の横断面図の例示的な図が示され、全体が1100で示されている。構造1100は、図1のPOP構造100を作製するプロセスにおいて少なくとも1つの段階の間に形成され得る。構造1100は、フォトイメーディング可能誘電体材料1124を図10の構造1000上に堆積させることによって形成され得る。たとえば、フォトイメーディング可能誘電体材料1124は、接着膜614を除去した後に、コア層110および第1のダイ116の上に堆積され得る。特定の態様では、下部構造170は、コア層110と第1のダイ116とを含み得る。下部構造170は、事前作製され得る。フォトイメーディング可能誘電体材料1124は、下部構造170上に堆積され得る。

40

【0050】

特定の態様では、図1のPID層124は、スピノンオン誘電体(SOD)層を含み得る。たとえば、フォトイメーディング可能誘電体材料1124は溶媒中に溶解され、コア層110および第1のダイ116の上に回転塗布され得る。PID層124を形成するために

50

、溶媒がベーキングおよび炉硬化によって除去され得る。代替態様では、フォトイメージング可能誘電体材料 1124 は、化学気相堆積 (CVD) を使用して塗布され得る。

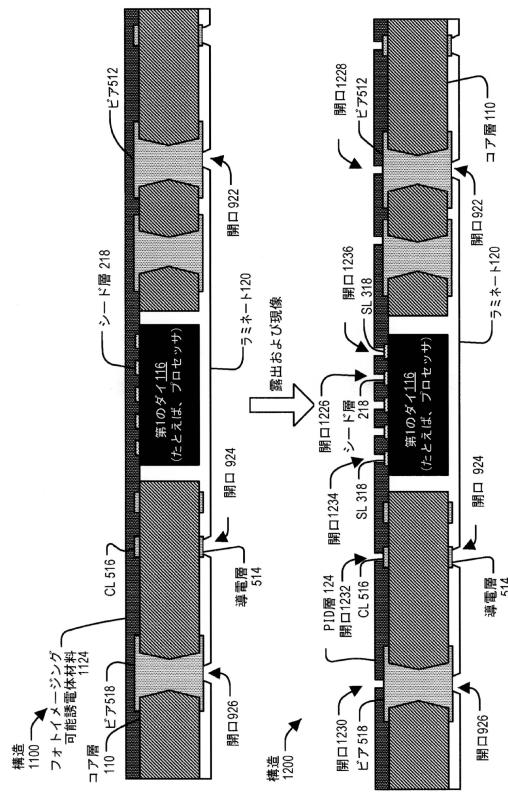

#### 【0051】

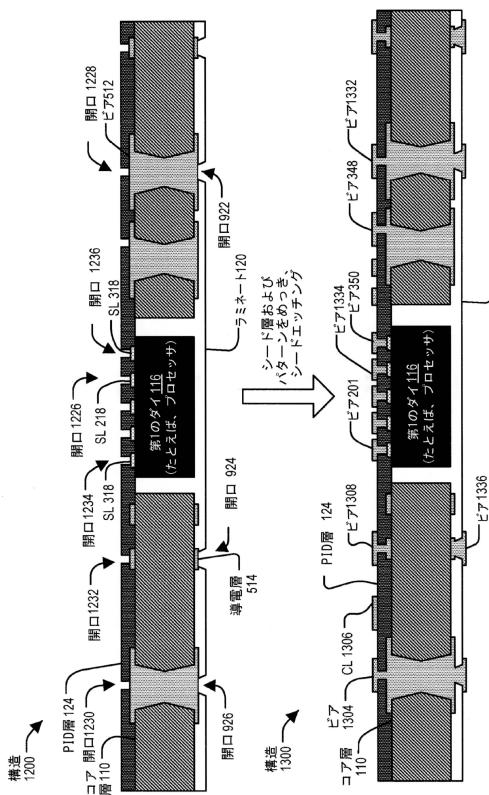

図 12 を参照すると、構造の横断面図の例示的な図が示され、全体が 1200 で示されている。構造 1200 は、図 1 の POP 構造 100 を作製するプロセスにおいて少なくとも 1 つの段階の間に形成され得る。構造 1200 は、図 11 の構造 1100 のフォトイメージング可能誘電体材料 1124 を露出して現像することによって形成され得る。フォトイメージング可能誘電体材料 1124 は、PID 層 124 を形成するためにパターン化され得る。たとえば、フォトイメージング可能誘電体材料 1124 は、フォトマスクを通して紫外光に露出され得る。露出されていない領域が、現像液を塗布することによって除去され得る。PID 層 124 の複数の部分が、1 つまたは複数の開口を形成するためにリソグラフィを使用して除去され得る。説明のために、PID 層 124 の複数の部分が、開口 1226、開口 1228、開口 1230、開口 1232、開口 1234、開口 1236、またはそれらの組合せを形成するために除去され得る。開口 1226 は、シード層 218 の少なくとも一部を露出し得る。開口 1228 は、ビア 512 上に形成され得る（またはビア 512 と位置合わせされ得る）。開口 1230 は、ビア 518 上に形成され得る（またはビア 518 と位置合わせされ得る）。開口 1230 は、開口 926 上に形成され得る（または開口 926 と位置合わせされ得る）。開口 1232 は、CL516 上に形成され得る（または CL516 と位置合わせされ得る）。開口 1234 は、シード層 318 の少なくとも一部を露出し得る。開口 1236 は、シード層 318 の少なくとも一部を露出し得る。

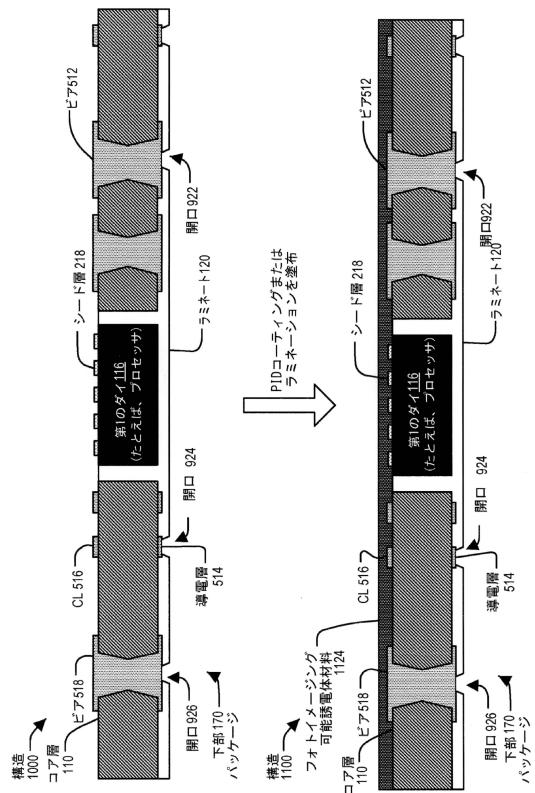

#### 【0052】

図 13 を参照すると、構造の横断面図の例示的な図が示され、全体が 1300 で示されている。構造 1300 は、図 1 の POP 構造 100 を作製するプロセスにおいて少なくとも 1 つの段階の間に形成され得る。構造 1300 は、図 12 の構造 1200 の 1 つまたは複数のビアを導電材料（たとえば、銅または他の金属）で充填することによって形成され得る。たとえば、開口 1228 および開口 922 は、ビア 1332 を形成するために導電材料（たとえば、銅）で充填され得る。ビア 1332 は、構造 1600 を通過し得る。別の例として、開口 1226 は、ビア 1334 を形成するために導電材料（たとえば、銅）で充填され得る。ビア 1334 は、シード層 218 を介して第 1 のダイ 116 に電気的に結合され得る。追加の例として、開口 924 は、ビア 1336 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1236 は、ビア 350 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1234 は、ビア 201 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1232 は、ビア 1308 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1230 および開口 926 は、ビア 1304 を形成するために導電材料（たとえば、銅）で充填され得る。導電材料の一部は、PID 層 124 上に 1 つまたは複数の導電性パッドを形成するために、開口 1230、開口 1232、開口 1234、開口 1226、開口 1236、開口 1228、またはそれらの組合せからオーバーフローしてもよい。導電材料の一部は、ラミネート 120 の表面上に 1 つまたは複数の導電性パッドを形成するために、開口 926、開口 924、開口 922、またはそれらの組合せからオーバーフローしてもよい。

#### 【0053】

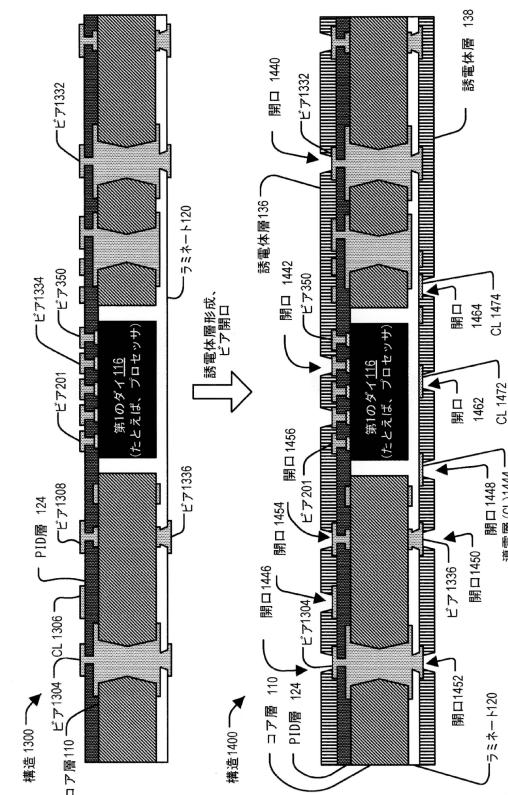

図 14 を参照すると、構造の横断面図の例示的な図が示され、全体が 1400 で示されている。構造 1400 は、図 1 の POP 構造 100 を作製するプロセスにおいて少なくとも 1 つの段階の間に形成され得る。構造 1400 は、図 13 の構造 1300 上に 1 つまたは複数の誘電体層を堆積させることによって形成され得る。たとえば、誘電体層 136 は、PID 層 124 上に堆積され得る。別の例として、誘電体層 138 は、ラミネート 120 上に堆積され得る。特定の態様では、1 つまたは複数の導電層（たとえば、CL1444、CL1472、CL1474、またはそれらの組合せ）は、誘電体層 138 を堆積させる前にラミネート 120 上に堆積され得る。

10

20

30

40

50

## 【0054】

誘電体層 136、誘電体層 138 または両方の部分は、開口を形成するために除去（エッティング）され得る。誘電体層 136 の 1 つまたは複数の開口（たとえば、開口 1440、開口 1442、開口 1446、開口 1456、またはそれらの組合せ）は、PID 層 124 のピアと位置合わせされ得る。たとえば、開口 1440 は、ピア 1332 上に形成され得る（またはピア 1332 と位置合わせされ得る）。別の例として、開口 1442 は、ピア 1334 上に形成され得る（またはピア 1334 と位置合わせされ得る）。開口 1442 は、シード層 218 と位置合わせされ得る。開口 1446 は、ピア 1304 上に形成され得る（またはピア 1304 と位置合わせされ得る）。開口 1456 は、ピア 1308 上に形成され得る（またはピア 1308 と位置合わせされ得る）。誘電体層 136 の 1 つまたは複数の開口（たとえば、開口 1454）は、PID 層 124 上に堆積された導電層 10 上に形成され得る（または導電層と位置合わせされ得る）。たとえば、開口 1454 は、CL 1306 上に形成され得る（または CL 1306 と位置合わせされ得る）。開口は、マスクを第 1 の誘電体層（たとえば、誘電体層 136 または誘電体層 138）に塗布することによって形成され得る。マスクは、第 1 の誘電体層の特定の領域を露出するためにパターン化され得る。特定の領域は、構造（たとえば、構造 1400）の別の部分と位置合わせされ得る。たとえば、マスクは、CL 1306 と位置合わせされている誘電体層 136 の領域を露出し得る。第 1 の誘電体層の特定の領域が、除去（エッティング）され得る。

## 【0055】

誘電体層 138 の 1 つまたは複数の開口（たとえば、開口 1448、開口 1462、開口 1464、またはそれらの組合せ）は、ラミネート 120 上に堆積された導電層と位置合わせされ得る。たとえば、開口 1448 は、導電層 1444 上に形成され得る（または導電層 1444 と位置合わせされ得る）。開口 1462 は、CL 1472 上に形成され得る（または CL 1472 と位置合わせされ得る）。開口 1464 は、CL 1474 上に形成され得る（または CL 1474 と位置合わせされ得る）。誘電体層 138 の 1 つまたは複数の開口（たとえば、開口 1452、開口 1450 または両方）は、ラミネート 120 のピアと位置合わせされ得る。たとえば、開口 1450 は、ピア 1336 上に形成され得る（またはピア 1336 と位置合わせされ得る）。開口 1452 は、ピア 1304 上に形成され得る（またはピア 1304 と位置合わせされ得る）。

## 【0056】

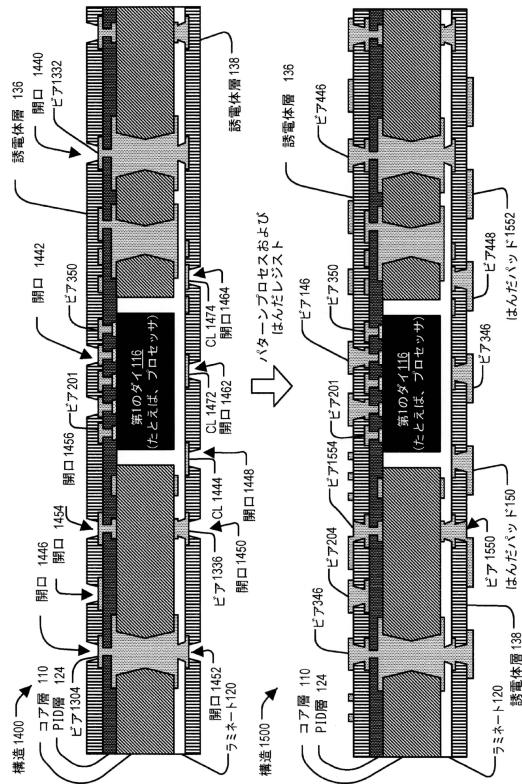

図 15 を参照すると、構造の横断面図の例示的な図が示され、全体が 1500 で示されている。構造 1500 は、図 1 の POP 構造 100 を作製するプロセスにおいて少なくとも 1 つの段階の間に形成され得る。構造 1500 は、誘電体層 136 の 1 つまたは複数のピア、誘電体層 138 の 1 つまたは複数のピア、またはそれらの組合せを導電材料（たとえば、銅）で充填することによって形成され得る。たとえば、開口 1442 は、ピア 146 を形成するために導電材料（たとえば、銅）で充填され得る。ピア 146 は、誘電体層 136 および PID 層 124 を通過してシード層 218 に至ることができる。別の例として、開口 1440 は、ピア 446 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1446 および開口 1452 は、ピア 346 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1454 は、ピア 204 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1456 は、ピア 1554 を形成するために導電材料（たとえば、銅）で充填され得る。導電材料の一部は、1 つまたは複数の導電性パッドが誘電体層 136 の表面上に形成されるように、開口 1440、開口 1442、開口 1446、開口 1454、開口 1456、またはそれらの組合せからオーバーフローしてもよい。特定の実装形態では、導電材料は、開口 1440、開口 1442、開口 1446、開口 1454、開口 1456、またはそれらの組合せを充填し、誘電体層 136 の表面上に層を形成してもよい。導電材料の層の複数の部分は、1 つまたは複数の導電性パッドを形成するために除去（たとえば、エッティング）されてもよい。

## 【0057】

開口 1448 は、はんだパッド 150 を形成するために導電材料（たとえば、銅）で充

10

20

30

40

50

填され得る。説明のために、導電材料の一部は、はんだパッド 150 を形成するために誘電体層 138 の表面上にオーバーフローしてもよい。別の例として、開口 1450 は、ビア 1550 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1462 は、ビア 346 を形成するために導電材料（たとえば、銅）で充填され得る。開口 1464 は、ビア 448 を形成するために導電材料（たとえば、銅）で充填され得る。

#### 【0058】

導電材料（たとえば、銅）は、1つまたは複数のはんだパッド（たとえば、はんだパッド 1552）を形成するために誘電体層 138 上に堆積され得る。特定の態様では、導電材料（たとえば、銅）は、誘電体層 138 上に堆積され得る。導電材料は、開口 1448、開口 1450、開口 1452、開口 1462、開口 1464、またはそれらの組合せを充填し得る。導電材料の複数の部分は、はんだパッド 150、はんだパッド 1552、ビア 346 に対応するはんだパッド、ビア 346 に対応するはんだパッド、ビア 448 に対応するはんだパッド、またはそれらの組合せを形成するために除去（たとえば、エッティング）されてもよい。

#### 【0059】

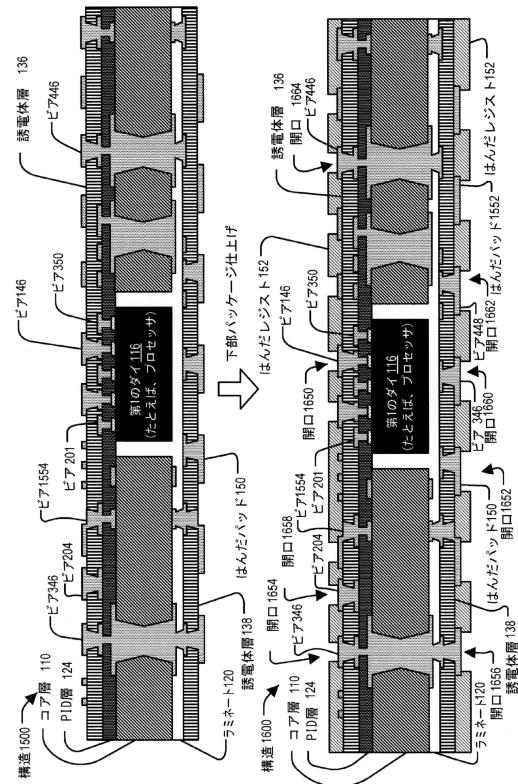

図 16 を参照すると、構造の横断面図の例示的な図が示され、全体が 1600 で示されている。構造 1600 は、図 1 の P O P 構造 100 を作製するプロセスにおいて少なくとも 1 つの段階の間に形成され得る。構造 1600 は、はんだレジスト 152 を図 15 の構造 1500 上に堆積させることによって形成され得る。たとえば、はんだレジスト 152 は、誘電体層 136、誘電体層 138 または両方の上に堆積され得る。はんだレジスト 152 の複数の部分は開口を形成するために除去（たとえば、エッティング）されてよく、それによって、1つまたは複数のビア（たとえば、ビア 346、ビア 204、ビア 146、ビア 446、ビア 346、ビア 448、またはそれらの組合せ）がカバーを取られ、1つまたは複数のはんだパッド（たとえば、はんだパッド 150、はんだパッド 1552 または両方）がカバーを取られる。たとえば、開口 1650 は、ビア 146 上に形成され得る（またはビア 146 と位置合わせされ得る）。別の例として、開口 1652 は、はんだパッド 150 上に形成され得る（またははんだパッド 150 と位置合わせされ得る）。開口 1654 および開口 1656 は、ビア 346 上に形成され得る（またはビア 346 と位置合わせされ得る）。開口 1654 および開口 1656 は、ビア 346 の対向面上に存在し得る。開口 1658 は、ビア 204 上に形成され得る（またはビア 204 と位置合わせされ得る）。開口 1664 は、ビア 446 上に形成され得る（またはビア 446 と位置合わせされ得る）。開口 1660 は、ビア 346 上に形成され得る（またはビア 346 と位置合わせされ得る）。開口 1662 は、ビア 448 上に形成され得る（またはビア 448 と位置合わせされ得る）。

#### 【0060】

図 17 を参照すると、P O P 構造 100 の横断面図の例示的な図が示されている。P O P 構造 100 は、図 16 の構造 1600 の1つまたは複数の開口を導電材料（たとえば、銅）で部分的に充填することによって形成され得る。たとえば、開口 1650 は、第 1 の導電層 264 を形成するために導電材料（たとえば、銅）で部分的に充填され得る。開口 1664 は、第 1 の C L 464 を形成するために導電材料（たとえば、銅）で部分的に充填され得る。開口 1658 は、第 1 の C L 242 を形成するために導電材料（たとえば、銅）で部分的に充填され得る。開口 1654 は、第 1 の C L 364 を形成するために導電材料（たとえば、銅）で部分的に充填され得る。

#### 【0061】

1つまたは複数のはんだバンプ（またははんだボール）は、構造 1600 上に堆積され得る。たとえば、はんだバンプ 154 は、はんだパッド 150 上に設置され得る。開口 1656 の一部は、はんだパッド 186 に対応し得る。はんだバンプ 184 は、はんだパッド 186 上に設置され得る。はんだバンプ 151 は、はんだパッドに対応するビア 346 の一部の上に設置され得る。はんだバンプ 153 は、はんだパッドに対応するビア 448 の一部の上に設置される。

10

20

30

40

50

## 【0062】

はんだ材料(たとえば、はんだペースト)は、はんだレジスト152の開口内に配設された導電材料上に堆積され得る。たとえば、はんだ260、はんだ460、はんだ262、はんだ360は、開口1650内の第1の導電層264、開口1664内の第1のCL464、開口1658内の第1のCL242、および開口1654内の第1のCL364の上にそれぞれ堆積され得る。基板材料(たとえば、非導電性ペースト)が、基板158を形成するためにはんだレジスト152上に塗布され得る。

## 【0063】

導電材料は、1つまたは複数の第2の導電層を形成するために第2のダイ156の複数の部分の上に配設され得る。たとえば、第2のCL244、第2のCL266、第2のCL366、第2のCL466、またはそれらの組合せが、第2のダイ156上に配設され得る。1つまたは複数の導電性経路が、上部構造168と下部構造170との間に形成され得る。たとえば、第2のダイ156が基板158上に設置されてよく、それによって、第2のダイ156上に配設された導電材料がはんだ材料と位置合わせされる。説明のために、第2のダイ156が基板158上に設置されてよく、それによって、第2のCL244がはんだ262と位置合わせされ、第2のCL266がはんだ260と位置合わせされ、第2のCL366がはんだ360と位置合わせされ、第2のCL466がはんだ460と位置合わせされ、またはそれらの組合せが存在する。

## 【0064】

第2のダイ156を基板158上に設置することで、導電材料(たとえば、第2のCL244、第2のCL266、第2のCL366、第2のCL466、またはそれらの組合せ)とはんだ材料(たとえば、はんだ262、はんだ260、はんだ360、はんだ460、またはそれらの組合せ)との間にある基板材料(たとえば、非導電性ペースト)の一部が導電材料およびはんだ材料の側に移動され得る。特定の態様では、第2のダイ156を基板158上に設置する前に導電材料(たとえば、第2のCL244、第2のCL266、第2のCL366、第2のCL466、またはそれらの組合せ)を露出させるために、基板材料の複数の部分が(たとえば、エッチングによって)除去され得る。

## 【0065】

リフローはんだ付けが、第2のダイ156を基板158上に設置した後に実行され得る。リフローはんだに続いて、第1の導電層264がはんだ260を介して第2の導電層266に付着(たとえば、はんだ付け)されてよく、第1のCL464がはんだ460を介して第2のCL466に付着されてよく、第1のCL242がはんだ262を介して第2のCL244に付着されてよく、第1のCL364がはんだ360を介して第2のCL366に付着されてよく、またはそれらの組合せが存在する。リフローはんだに続いて、はんだバンプ154がはんだパッド150に付着(はんだ付け)されてよく、はんだバンプ184がはんだパッド186に付着(はんだ付け)されてよく、はんだバンプ151がはんだパッドに対応するビア346の一部に付着されてよく、はんだバンプ153がはんだパッドに対応するビア448の一部に付着されてよく、またはそれらの組合せが存在する。

## 【0066】

特定の態様では、上部構造168は、第2のダイ156、基板158、第2の導電層266、第2のCL366、第2のCL244、第2のCL466、またはそれらの組合せを含み得る。上部構造168は、事前作製され得る。POP構造100は、はんだ260を第1の導電層264上に、第2のはんだ460を第1のCL464上に、はんだ262を第1のCL242上に、はんだ360を第1のCL364上に設置することによって形成され得る。第2の導電層266がはんだ260上に設置され、第2のCL466がはんだ460上に設置され、第2のCL244がはんだ262上に設置され、第2のCL366がはんだ360上に設置され、または何らかの組合せが存在するように、上部構造168が設置され得る。リフローはんだ付けは、上部構造168の設置に続いて実行され得る。

10

20

30

40

50

## 【0067】

POP構造100は、第1のダイ116からシード層218、ビア146、第1の導電層264、はんだ260、および第2の導電層266を経由して第2のダイ156に至る導電性経路162を含み得る。ビア146は、PID層124を通過し得る。導電性経路162は、真っすぐ（または実質的に真っすぐ）であり得る。POP構造100は、第2のダイ156から第2のCL366、はんだ360、第1のCL364、およびビア346を経由してはんだバンプ184に至る導電性経路101を含み得る。導電性経路101は、真っすぐ（または実質的に真っすぐ）であり得る。導電性経路101は、導電性経路162に平行（または実質的に平行）であり得る。

## 【0068】

POP構造100は、第2のダイ156から第2のCL244、はんだ262、第1のCL242、ビア204、誘電体層138の1つまたは複数の部分、1つまたは複数の追加のビア、ビア201、およびシード層219を経由して第1のダイ116に至る導電性経路103を含み得る。POP構造100は、第1のダイ116からシード層318、ビア350、誘電体層138の1つまたは複数の部分、1つまたは複数の追加の導電層、ビア348、ラミネート120、およびビア346を経由してはんだバンプ151に至る導電性経路105を含み得る。

## 【0069】

誘電体層（たとえば、誘電体層136または誘電体層138）は、1つまたは複数の第1のビアを含み得る。第1のビアは、導電材料（たとえば、銅）で充填され得る。誘電体層を通じて延びる導電性経路（たとえば、導電性経路103、導電性経路105、または導電性経路107）は、第1のビアを通じて延び得る。ラミネート（たとえば、ラミネート120）は、1つまたは複数の第2のビアを含み得る。第2のビアは、導電材料（たとえば、銅）で充填され得る。ラミネート120を通じて延びる導電性経路（たとえば、導電性経路105）は、第2のビアを通じて延び得る。

## 【0070】

POP構造100は、第2のダイ156から第2のCL466、はんだ460、第1のCL464、ビア446、誘電体層138の1つまたは複数の部分、1つまたは複数の追加の導電層、およびビア448を経由してはんだバンプ153に至る導電性経路107を含み得る。

## 【0071】

図5～図17を参照しながら説明するように形成されたPOP構造100は、第1のダイ116と第2のダイ156との間でPID層124を通じる1つまたは複数の導電性経路を含み得る。たとえば、POP構造100は、導電性経路162を含み得る。導電性経路162は、第1のダイ116からシード層218、ビア146、第1の導電層264、はんだ260、および第2の導電層266を通じて第2のダイ156まで延び得る。ビア146は、PID層124を通過し得る。

## 【0072】

図18は、図1のPOP構造100を形成する方法1800の特定の態様を示すフローチャートである。方法1800は、1802において、フォトイメージング可能誘電体材料を、第1のダイが埋め込まれているパッケージの表面上に堆積させるステップを含む。たとえば、図1のPOP構造100は、図11を参照しながら説明するように、フォトイメージング可能誘電体材料1124を構造1000上に堆積させることによって形成され得る。第1のダイ116は、図5～図10を参照して説明する構造1000の中に埋め込まれ得る。

## 【0073】

また、方法1800は、1804において、フォトイメージング誘電体（PID）層を形成するためにフォトイメージング可能誘電体材料をパターニングするステップを含む。たとえば、図1のPOP構造100を形成するステップは、図12を参照しながら説明するように、PID層124を形成するためにフォトイメージング可能誘電体材料1124

10

20

30

40

50

をパターニングするステップを含み得る。

【0074】

方法1800は、1806において、P I D層を通って第1のダイに至る第1の導電性経路および第2の導電性経路を形成するために導電材料をP I D層上に堆積させるステップをさらに含む。たとえば、図1のP O P構造100を形成するステップは、図13～図17を参照しながら説明するように、P I D層124を通る導電性経路162および導電性経路103を形成するために導電材料を堆積させるステップを含み得る。

【0075】

また、方法1800は、1808において、第2のダイが第1の導電性経路および第2の導電性経路を介して第1のダイに電気的に接続されるように、第2のダイをパッケージに結合するステップを含む。たとえば、P O P構造100は、図17を参照しながら説明するように、第2のダイ156が導電性経路162および導電性経路103を介して第1のダイ116に電気的に接続されるように第2のダイ156を下部構造170に結合することによって形成され得る。導電性経路162は、P I D層124を通って第1のダイ116から第2のダイ156に直接的に延び得る。たとえば、導電性経路162は、図2を参照しながら説明するように、第1のダイ116から第1のP I D領域222を通って第2のダイ156まで延び得る。導電性経路103の部分113は、図2を参照しながら説明するように、導電性経路162に直角（またはほぼ直角）であってよく、第1のダイ116と第2のダイ156との間で直接的にではなく、P I D層124の第2のP I D領域224を通って延び得る。たとえば、導電性経路103の部分113は、第1のP I D領域222、第2のP I D領域224または両方を通って延び得る。

【0076】

図19は、図1のP O P構造100を形成する方法の別の態様を示すフローチャートである。方法1900は、1902において、フォトイメージング可能誘電体材料を、第1のダイが埋め込まれているパッケージの表面上に堆積させるステップを含む。たとえば、図1のP O P構造100は、図11を参照しながら説明するように、フォトイメージング可能誘電体材料1124を構造1000上に堆積させることによって形成され得る。第1のダイ116は、図5～図10を参照して説明する構造1000の中に埋め込まれ得る。

【0077】

また、方法1900は、1904において、フォトイメージング誘電体（P I D）層を形成するためにフォトイメージング可能誘電体材料をパターニングするステップを含む。たとえば、図1のP O P構造100は、図12を参照しながら説明するように、P I D層124を形成するためにフォトイメージング可能誘電体材料1124をパターニングすることによって形成され得る。

【0078】

方法1900は、1906において、第1のダイからP I D層を経由して第2のダイに至る第1の導電性経路および第2の導電性経路を形成するステップをさらに含む。たとえば、図1のP O P構造100は、第1のダイ116からP I D層124を経由して第2のダイ156に至る導電性経路162および導電性経路103を形成することによって形成され得る。導電性経路162は、図2を参照しながら説明するように、P I D層124を通って第1のダイ116から第2のダイ156に直接的に延び得る。たとえば、導電性経路162は、図2を参照しながらさらに説明するように、第1のダイ116から第1のP I D領域222を通って第2のダイ156まで延び得る。導電性経路103の部分113は、図2を参照しながら説明するように、導電性経路162に直角（またはほぼ直角）であってよく、第1のダイ116と第2のダイ156との間で直接的にではなく、P I D層124の第2のP I D領域224を通って延び得る。たとえば、導電性経路103の部分113は、第1のP I D領域222、第2のP I D領域224または両方を通って延び得る。

【0079】

図20を参照すると、電子デバイスの特定の例示的な態様のブロック図が図示されてお

10

20

30

40

50

り、全体が 2000 で示されている。デバイス 2000 は、メモリ 2032 に結合された、デジタル信号プロセッサ (DSP) のようなプロセッサ 2010 を含む。特定の態様では、プロセッサ 2010 は図 1 の第 1 のダイ 116 に対応してよく、メモリ 2032 は第 2 のダイ 156 に対応してもよい。たとえば、デバイス 2000 は、図 1 のPOP構造 100 を含み得る。第 1 のダイ 116 は、プロセッサ 2010 に含まれてもよく、または結合されてもよい。第 2 のダイ 156 は、メモリ 2032 に含まれてもよく、または結合されてもよい。プロセッサ 2010 は、メモリ 2032 に結合され得る。たとえば、POP 構造 100 は、プロセッサ 2010 とメモリ 2032 との間に 1 つまたは複数の導電性経路 (たとえば、導電性経路 103、導電性経路 162、導電性経路 182、またはそれらの組合せ) を含み得る。例示的な態様では、POP 構造 100 は、図 5 ~ 図 19 を参照して説明する方法または動作のうちの 1 つまたは複数に従って形成され得る。

#### 【0080】

図 20 は、さらに、プロセッサ 2010 とディスプレイ 2028 とに結合されるディスプレイコントローラ 2026 を示す。コーダ / デコーダ (コーデック) 2034 が、さらに、プロセッサ 2010 に結合され得る。スピーカ 2036 およびマイクロフォン 2038 をコーデック 2034 に結合することができる。

#### 【0081】

図 20 は、さらに、ワイヤレスコントローラ 2040 をプロセッサ 2010 とアンテナ 2042 とに結合できることを示す。特定の態様では、プロセッサ 2010、ディスプレイコントローラ 2026、メモリ 2032、コーデック 2034、およびワイヤレスコントローラ 2040 は、システムインパッケージ 2022 内に含まれる。特定の態様では、入力デバイス 2030 および電源 2044 は、システムインパッケージデバイス 2022 に結合される。さらに、特定の態様では、図 20 に示されるように、ディスプレイ 2028、入力デバイス 2030、スピーカ 2036、マイクロフォン 2038、アンテナ 2042、および電源 2044 は、システムインパッケージデバイス 2022 の外部にある。しかしながら、ディスプレイ 2028、入力デバイス 2030、スピーカ 2036、マイクロフォン 2038、アンテナ 2042、および電源 2044 の各々は、インターフェースまたはコントローラなどのシステムインパッケージデバイス 2022 の構成要素に結合され得る。

#### 【0082】

説明する態様に関連して、第 1 のダイおよびフォトイメージング誘電体 (PID) 層を含む第 1 の集積回路 IC をパッケージングするための第 1 の手段を含み得る装置が開示される。たとえば、パッケージングするための第 1 の手段は、図 1 の下部構造 170、IC および PID 層をパッケージングするように構成された 1 つまたは複数の他のデバイスもしくは回路、またはそれらの組合せを含み得る。

#### 【0083】

また、装置は、第 2 のダイを含む第 2 の IC をパッケージングするための第 2 の手段を含み得る。たとえば、パッケージングするための第 2 の手段は、図 1 の上部構造 168、IC をパッケージングするように構成された 1 つまたは複数の他のデバイスもしくは回路、またはそれらの組合せを含み得る。第 1 のダイ 116 から PID 層 124 を通って第 2 のダイ 156 に至る導電性経路 162 は、PID 層 124 を通って第 1 のダイ 116 から第 2 のダイ 156 まで直接的に延び得る。第 1 のダイ 116 から PID 層 124 を通って第 2 のダイ 156 に至る導電性経路 103 の部分 113 は、導電性経路 162 に直角 (またはほぼ直角) であってよく、第 1 のダイ 116 と第 2 のダイ 156 との間で直接的にではなく、PID 層 124 の第 2 の PID 領域 224 を通って延び得る。

#### 【0084】

上記で開示したデバイスおよび機能は、コンピュータ可読媒体上に記憶されたコンピュータファイル (たとえば、RTL、GDSII、GERBER など) に設計および構成されてもよい。いくつかまたはすべてのそのようなファイルは、そのようなファイルに基づいてデバイスを製造する製造者に提供されてもよい。結果として得られる製品は、半導体

10

20

30

40

50

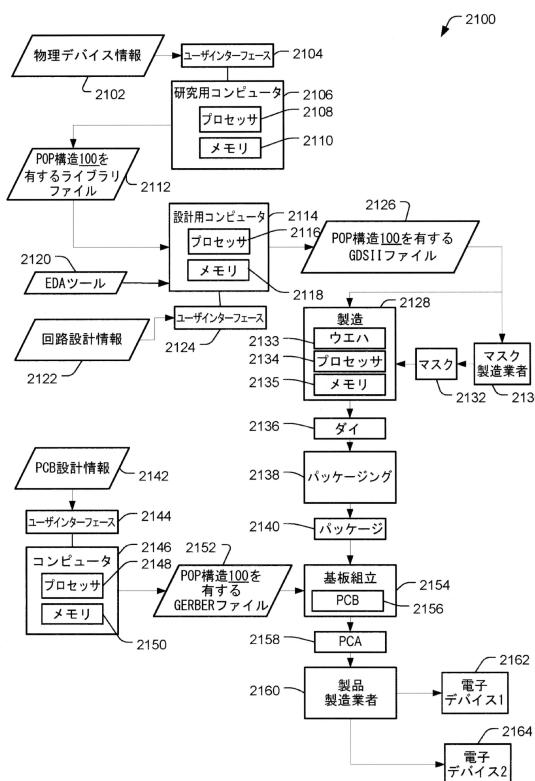

ウエハを含み、次いで、半導体ウエハは半導体ダイに切断され、半導体チップにパッケージングされる。次いでチップが、上で説明されたデバイスにおいて利用される。図21は、電子デバイス製造プロセス2100の特定の例示的な態様を示す。

【0085】

物理デバイス情報2102は、研究用コンピュータ2106などにおいて、製造プロセス2100において受け取られる。物理デバイス情報2102は、POP構造100など、半導体デバイスの少なくとも1つの物理的な特性を表す設計情報を含み得る。たとえば、物理デバイス情報2102は、物理パラメータ、材料特性、および、研究用コンピュータ2106に結合されたユーザインターフェース2104を介して入力された構造情報を含み得る。研究コンピュータ2106は、メモリ2110などのコンピュータ可読媒体に結合された、1つまたは複数の処理コアなどのプロセッサ2108を含む。メモリ2110は、プロセッサ2108に、ファイルフォーマットに準拠するように物理デバイス情報2102を変換させ、ライブラリファイル2112を生成させるように実行可能である、コンピュータ可読命令を記憶することができる。

【0086】

特定の態様では、ライブラリファイル2112は、変換された設計情報を含む、少なくとも1つのデータファイルを含む。たとえば、ライブラリファイル2112は、電子設計オートメーション(EDA)ツール2120とともに使用するために設けられているPOP構造100を含むデバイスを含む半導体デバイスのライブラリを含み得る。

【0087】

ライブラリファイル2112は、メモリ2118に結合された1つまたは複数の処理コアなどのプロセッサ2116を含む設計用コンピュータ2114において、EDAツール2120とともに使用され得る。EDAツール2120は、設計コンピュータ2114のユーザがライブラリファイル2112のPOP構造100を含む回路を設計することを可能にするために、メモリ2118においてプロセッサ実行可能命令として記憶され得る。たとえば設計コンピュータ2114のユーザは、設計コンピュータ2114に結合されたユーザインターフェース1824を介して回路設計情報を2122を入力することができる。回路設計情報2122は、POP構造100などの半導体デバイスの少なくとも1つの物理的な特性を表す設計情報を含み得る。例示するために、回路設計特性は、特定の回路の識別および回路設計における他の要素に対する関係、位置情報、フィーチャのサイズ情報、相互接続情報、または半導体デバイスの物理的な特性を表す他の情報を含み得る。

【0088】

設計用コンピュータ2114は、回路設計情報を2122を含む設計情報をファイルフォーマットに準拠するように変換するように構成することができる。例示するために、ファイル構成は、平面幾何学的形状と、テキストラベルと、グラフィックデータシステム(GDSII)ファイルフォーマットなどの階層的フォーマット内の回路レイアウトについての他の情報を表すデータベースバイナリファイルフォーマットを含み得る。設計コンピュータ2114は、他の回路または情報を加えて、POP構造100を記述する情報を含むGDSIIファイル2126などの変換された設計情報を含むデータファイルを生成するように構成され得る。説明のために、データファイルは、POP構造100を含み、同じくシステムインパッケージ内の追加の電子回路および構成要素を含むシステムインパッケージに対応する情報を含み得る。

【0089】

GDSIIファイル2126は、GDSIIファイル2126内の変換された情報に従ってPOP構造を製造するために、製造プロセス2128において受信され得る。たとえば、デバイス製造プロセスは、代表的なマスク2132として示される、フォトリソグラフィプロセスとともに使用されることになるマスクなどの、1つまたは複数のマスクを作製するために、マスク製造業者2130にGDSIIファイル2126を提供することを含み得る。マスク2132は、試験されて代表的なダイ2136などのダイへと分割され得る1つまたは複数のウエハ2134を生成するための製作プロセスの間、使用され得る

10

20

30

40

50

。ダイ2136は、POP構造100を含むデバイスを含む回路を含む。

【0090】

ダイ2136は、ダイ2136が代表的なパッケージ2140へと組み込まれるパッケージングプロセス2138に提供され得る。たとえば、パッケージ2140は、単一のダイ2136、またはシステムインパッケージ(SiP)構成などの複数のダイを含み得る。パッケージ2140は、電子デバイスエンジニアリング連合評議会(JEDEC)規格のような1つまたは複数の規格または仕様に準拠するように構成され得る。

【0091】

パッケージ2140に関する情報は、コンピュータ2146に記憶されているコンポーネントライブラリなどを介して、様々な製品設計者に配布され得る。コンピュータ2146は、メモリ2150に結合された、1つまたは複数の処理コアなどのプロセッサ2148を含み得る。プリント回路基板(PCB)ツールは、ユーザインターフェース2144を介してコンピュータ2146のユーザから受け取られたPCB設計情報2142を処理するために、プロセッサ実行可能命令としてメモリ2150に記憶され得る。PCB設計情報2142は、回路板上にパッケージングされた半導体デバイスの物理的位置情報を含んでもよく、パッケージングされた半導体デバイスはPOP構造100を含むパッケージ2140に対応する。

【0092】

コンピュータ2146は、PCB設計情報2142を変換して、回路板上にパッケージングされた半導体デバイスの物理的位置情報とともに、配線およびビアなどの電気的接続のレイアウトを含むデータを有するGERBERファイル2152などのデータファイルを生成するように構成されてもよく、パッケージングされた半導体デバイスはPOP構造100を含むパッケージ2140に対応する。他の態様では、変換されたPCB設計情報によって生成されたデータファイルは、GERBERフォーマット以外のフォーマットを有し得る。

【0093】

GERBERファイル2152は、基板組立プロセス2154において受け取られてよく、GERBERファイル2152内に記憶されている設計情報に従って製造される代表的なPCB2156などのPCBを作成するために使用されてよい。たとえばGERBERファイル2152は、PCB製造プロセスの様々なステップを実行するために、1つまたは複数の機械にアップロードされ得る。PCB2156は、代表的なプリント回路アセンブリ(PCA)2158を形成するために、パッケージ2140を含む電子構成要素を装着され得る。

【0094】

PCA2158は、製品製造プロセス2160において受け取られ、第1の代表的な電子デバイス2162および第2の代表的な電子デバイス2164などの1つまたは複数の電子デバイスに組み込まれ得る。例示的かつ非限定的な例として、第1の代表的な電子デバイス2162、第2の代表的な電子デバイス2164、またはこれら両方は、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、コンピュータというグループから選択されてもよく、その中に、POP構造100が組み込まれる。別の例示的で非限定的な例として、電子デバイス2162および2164のうちの1つもしくは複数は、モバイルフォン、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末などのポータブルデータユニット、全地球測位システム(GPS)対応デバイス、ナビゲーションデバイス、メータ検針機器などの固定位置データユニット、または、データもしくはコンピュータ命令を記憶するか、もしくは引き出す任意の他のデバイス、またはそれらの任意の組合せなどの、遠隔ユニットとすることができる。図21は、本開示の教示による遠隔ユニットを示しているが、本開示は、これらの例示されたユニットに限定されない。本開示の態様は、メモリおよびオンチップ回路を含む能動集積回路を含む任意のデバイスにおいて適切に利用され得る。

10

20

30

40

50

**【0095】**

POP構造100を含むデバイスは、例示的プロセス2100において説明したように、製造し、処理し、電子デバイスに組み込むことができる。図1～図20に関して開示する態様のうちの1つまたは複数の態様は、ライブラリファイル2112、GDSIIファイル2126、およびGERBERファイル2152内など、様々な処理ステージにおいて含まれ、ならびに、調査コンピュータ2106のメモリ2110、設計コンピュータ2114のメモリ2118、コンピュータ2146のメモリ2150、基板アセンブリプロセス2154においてなど様々なステージにおいて使用される1つまたは複数の他のコンピュータまたはプロセッサ(図示せず)のメモリにおいて格納され、また、マスク2132、ダイ2136、パッケージ2140、PCA2158、プロトタイプ回路もしくはデバイス(図示せず)などの他の製品、またはその任意の組合せなどの1つまたは複数の他の物理的態様に組み込まれ得る。物理的デバイス設計から最終製品までの製品の様々な代表的な段階が示されているが、他の態様では、より少数の段階が使用されてよく、または、追加の段階が含まれてもよい。同様に、プロセス2100は、単一のエンティティによって、またはプロセス2100の様々な段階を実行する1つまたは複数のエンティティによって実行され得る。

**【0096】**

さらに、本明細書で開示された態様に関して説明された様々な例示的な論理ブロック、構成、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、プロセッサによって実行されるコンピュータソフトウェア、または両方の組合せとして実装され得ることを、当業者は理解されよう。様々な例示的な構成要素、ブロック、構成、モジュール、回路、およびステップについて、上記では概してそれらの機能性に関して説明された。そのような機能性がハードウェアとして実装されるか、プロセッサ実行可能命令として実装されるかは、特定の適用例および全体的なシステムに課された設計制約に依存する。当業者は、記載された機能性を特定の適用例ごとに様々な方法で実現することができるが、そのような実施態様の決定は、本開示の範囲からの逸脱を引き起こすものと解釈されるべきではない。

**【0097】**

本明細書で開示した態様に関して説明した方法またはアルゴリズムのステップは、ハードウェアにおいて直接、プロセッサによって実行されるソフトウェアモジュールにおいて、またはその2つの組合せにおいて具現される場合がある。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み出し専用メモリ(ROM)、プログラマブル読み出し専用メモリ(PROM)、消去可能プログラマブル読み出し専用メモリ(E PROM)、電気的消去可能プログラマブル読み出し専用メモリ(EEPROM)、レジスタ、ハードディスク、取外し可能ディスク、コンパクトディスク読み出し専用メモリ(CD-ROM)、または当技術分野で既知の任意の他の形態の非一時的記憶媒体に存在することができる。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み出し、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替では、記憶媒体はプロセッサに一体化されてもよい。プロセッサおよび記憶媒体は、特定用途向け集積回路(ASIC)に存在することができる。ASICは、コンピューティングデバイスまたはユーザ端末に存在することができる。代替では、プロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末に個別の構成要素として存在することができる。

**【0098】**

開示した態様の上記の説明は、開示した態様を当業者が作成または使用できるようにするため提供される。これらの態様への様々な修正は当業者には容易に明らかになり、本明細書で定義された原理は、本開示の範囲から逸脱することなく、他の態様に適用されてもよい。したがって、本開示は、本明細書に示す態様に限定されることを意図するものではなく、以下の特許請求の範囲によって定義される原理および新規の特徴と可能な限り一致する最も広い範囲が与えられるべきである。

## 【符号の説明】

## 【0099】

|     |                       |    |

|-----|-----------------------|----|

| 100 | パッケージオンパッケージ (POP) 構造 |    |

| 101 | 導電性経路 (CP)            |    |

| 103 | CP                    |    |

| 105 | CP                    |    |

| 107 | CP                    |    |

| 110 | コア層                   |    |

| 113 | CP の一部                |    |

| 116 | 第1のダイ                 | 10 |

| 120 | ラミネート                 |    |

| 124 | フォトイメージング誘電体 (PID) 層  |    |

| 136 | 誘電体層                  |    |

| 138 | 誘電体層                  |    |

| 146 | ビア                    |    |

| 150 | はんだパッド                |    |

| 151 | はんだバンプ                |    |

| 152 | はんだレジスト               |    |

| 153 | はんだバンプ                |    |

| 154 | はんだバンプ                | 20 |

| 156 | 第2のダイ                 |    |

| 158 | 基板                    |    |

| 162 | CP                    |    |

| 168 | 上部構造                  |    |

| 170 | 下部構造                  |    |

| 182 | CP                    |    |

| 184 | はんだバンプ                |    |

| 186 | はんだパッド                |    |

| 190 | CP の一部                |    |

| 201 | ビア                    | 30 |

| 204 | ビア                    |    |

| 208 | CP の一部                |    |

| 211 | CP の一部                |    |

| 215 | 第1の端部                 |    |

| 217 | 第2の端部                 |    |

| 218 | シード層 (SL)             |    |

| 219 | SL                    |    |

| 222 | 第1のPID領域              |    |

| 224 | 第2のPID領域              |    |

| 242 | 第1の導電層 (CL)           | 40 |

| 244 | 第2のCL                 |    |

| 260 | はんだ                   |    |

| 262 | はんだ                   |    |

| 264 | 第1のCL                 |    |

| 266 | 第2のCL                 |    |

| 318 | シード層                  |    |

| 346 | ビア                    |    |

| 348 | ビア                    |    |

| 350 | ビア                    |    |

| 360 | はんだ                   | 50 |

|         |                  |    |

|---------|------------------|----|

| 3 6 4   | 第 1 の C L        |    |

| 3 6 6   | 第 2 の C L        |    |

| 4 4 6   | ビア               |    |

| 4 4 8   | ビア               |    |

| 4 6 0   | はんだ              |    |

| 4 6 4   | 第 1 の C L        |    |

| 4 6 6   | 第 2 の C L        |    |

| 5 0 0   | 構造               |    |

| 5 0 2   | 構造               |    |

| 5 1 2   | ビア               | 10 |

| 5 1 4   | C L              |    |

| 5 1 6   | C L              |    |

| 5 1 8   | ビア               |    |

| 6 0 0   | 構造               |    |

| 6 1 4   | 接着膜              |    |

| 7 0 0   | 構造               |    |

| 8 0 0   | 構造               |    |

| 9 0 0   | 構造               |    |

| 9 2 2   | 開口               |    |

| 9 2 4   | 開口               | 20 |

| 9 2 6   | 開口               |    |

| 1 0 0 0 | 構造               |    |

| 1 1 0 0 | 構造               |    |

| 1 1 2 4 | フォトイメージング可能誘電体材料 |    |

| 1 2 0 0 | 構造               |    |

| 1 2 2 6 | 開口               |    |

| 1 2 2 8 | 開口               |    |

| 1 2 3 0 | 開口               |    |

| 1 2 3 2 | 開口               |    |

| 1 2 3 4 | 開口               | 30 |

| 1 2 3 6 | 開口               |    |

| 1 3 0 0 | 構造               |    |

| 1 3 0 4 | ビア               |    |

| 1 3 0 6 | C L              |    |

| 1 3 0 8 | ビア               |    |

| 1 3 3 2 | ビア               |    |

| 1 3 3 4 | ビア               |    |

| 1 3 3 6 | ビア               |    |

| 1 4 0 0 | 構造               |    |

| 1 4 4 0 | 開口               | 40 |

| 1 4 4 2 | 開口               |    |

| 1 4 4 4 | C L              |    |

| 1 4 4 6 | 開口               |    |

| 1 4 4 8 | 開口               |    |

| 1 4 5 0 | 開口               |    |

| 1 4 5 2 | 開口               |    |

| 1 4 5 4 | 開口               |    |

| 1 4 5 6 | 開口               |    |

| 1 4 6 2 | 開口               |    |

| 1 4 6 4 | 開口               | 50 |

|         |                                  |    |

|---------|----------------------------------|----|

| 1 4 7 2 | C L                              |    |

| 1 4 7 4 | C L                              |    |

| 1 5 0 0 | 構造                               |    |

| 1 5 5 0 | ビア                               |    |

| 1 5 5 2 | はんだパッド                           |    |

| 1 5 5 4 | ビア                               |    |

| 1 6 0 0 | 構造                               |    |

| 1 6 5 0 | 開口                               |    |

| 1 6 5 2 | 開口                               |    |

| 1 6 5 4 | 開口                               | 10 |

| 1 6 5 6 | 開口                               |    |

| 1 6 5 8 | 開口                               |    |

| 1 6 6 0 | 開口                               |    |

| 1 6 6 2 | 開口                               |    |

| 1 6 6 4 | 開口                               |    |

| 2 0 0 0 | 電子デバイスのブロック図                     |    |

| 2 0 1 0 | プロセッサ                            |    |

| 2 0 2 2 | システムインパッケージ                      |    |

| 2 0 2 6 | ディスプレイコントローラ                     |    |

| 2 0 2 8 | ディスプレイ                           | 20 |

| 2 0 3 0 | 入力デバイス                           |    |

| 2 0 3 2 | メモリ                              |    |

| 2 0 3 4 | コーデック                            |    |

| 2 0 3 6 | スピーカ                             |    |

| 2 0 3 8 | マイクロフォン                          |    |

| 2 0 4 0 | ワイヤレスコントローラ                      |    |

| 2 0 4 2 | アンテナ                             |    |

| 2 0 4 4 | 電源                               |    |

| 2 1 0 0 | 電子デバイス製造プロセス                     |    |

| 2 1 0 2 | 物理デバイス情報                         | 30 |

| 2 1 0 4 | ユーザインターフェース                      |    |

| 2 1 0 6 | 研究用コンピュータ                        |    |

| 2 1 0 8 | プロセッサ                            |    |

| 2 1 1 0 | メモリ                              |    |

| 2 1 1 2 | ライブラリファイル                        |    |

| 2 1 1 4 | 設計用コンピュータ                        |    |

| 2 1 1 6 | プロセッサ                            |    |

| 2 1 1 8 | メモリ                              |    |

| 2 1 2 0 | 電子設計オートメーション ( E D A ) ツール       |    |

| 2 1 2 2 | 回路設計情報                           | 40 |

| 2 1 2 4 | ユーザインターフェース                      |    |

| 2 1 2 6 | グラフィックデータシステム ( G D S I I ) ファイル |    |

| 2 1 2 8 | 製造プロセス                           |    |

| 2 1 3 0 | マスク製造業者                          |    |

| 2 1 3 2 | マスク                              |    |

| 2 1 3 3 | 1つまたは複数のウエハ                      |    |

| 2 1 3 5 | メモリ                              |    |

| 2 1 3 6 | ダイ                               |    |

| 2 1 3 8 | パッケージングプロセス                      |    |

| 2 1 4 0 | パッケージ                            | 50 |

2 1 4 2 プリント回路基板 ( P C B ) 設計情報

2 1 4 4 ユーザインターフェース

2 1 4 6 コンピュータ

2 1 4 8 プロセッサ

2 1 5 0 メモリ

2 1 5 2 G E R B E R ファイル

2 1 5 4 基板組立プロセス

2 1 5 6 P C B

2 1 5 8 プリント回路アセンブリ ( P C A )

2 1 6 0 製品製造プロセス

2 1 6 2 電子デバイス

2 1 6 4 電子デバイス

10

【 义 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 义 8 】

【図9】

【 図 1 0 】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

### 【図16】

【 図 1 7 】

【 囮 1 8 】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 ジエ・シク・イ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 ドン・ウク・キム

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 シチュン・グ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 平林 雅行

(56)参考文献 特開2010-205893(JP, A)

特開2014-195076(JP, A)

国際公開第2010/101163(WO, A1)

特開2008-166824(JP, A)

米国特許出願公開第2013/0234322(US, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12-23/15

H01L 25/00-25/07

H01L 25/10-25/11

H01L 25/16-25/18

H05K 3/46