Demande de brevet déposée pour la Suisse et le Liechtenstein Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

## (2) FASCICULE DE LA DEMANDE A3

639 810 G

(21) Numéro de la demande: 4526/78

(71) Requérant(s):

Kabushiki Kaisha Suwa Seikosha, Tokyo (JP)

(22) Date de dépôt:

26.04.1978

30) Priorité(s):

26.04.1977 JP 52-48290 26.04.1977 JP 52-48291

(72) Inventeur(s):

Tatsushi Asakawa, Suwa-shi/Nagano-ken (JP) Shinji Morozumi, Suwa-shi/Nagano-ken (JP)

(42) Demande publiée le:

15.12.1983

(74) Mandataire:

Bovard AG, Bern 25

(44) Fascicule de la demande

publié le:

15.12.1983

(56) Rapport de recherche au verso

### 64 Circuit intégré à semi-conducteur constituant un circuit détecteur de tension.

57) Afin d'améliorer à la fois la simplicité et la performance du circuit intégré constituant un circuit détecteur de tension, on a, outre une source de tension de référence (1) pour produire une tension de référence (W<sub>st</sub>), un circuit convertisseur de tension (2) pour produire une tension à comparer (W<sub>d</sub>) représentative de la tension dé-tectée, et des moyens comparateurs (3) recevant la tension de référence et la tension à comparer, un circuit régulateur de comparaison (4) connecté entre la source de tension de référence (1) ou le circuit convertisseur (2), d'une part, et les moyens comparateurs (3) d'autre part. Cet agencement permet d'ajuster l'une des tensions de référence (W<sub>st</sub>) ou à comparer (W<sub>d</sub>), en tant que réglage préalable dans le circuit intégré avant son montage. On évite ainsi des ajustages ultérieurs, de même que la nécessité d'éléments extérieurs d'ajustage.

Ce circuit intégré constituant un circuit détecteur de tension est avantageusement utilisé pour la détection de la tension de pile dans une pièce d'horlogerie électronique, tout particulièrement une montre-bracelet électro-

nique.

#### Bundesamt für geistiges Eigentum Office fédéral de la propriété intellectuelle Ufficio federale della proprietà intellettuale

### RAPPORT DE RECHERCHE RECHERCHENBERICHT

Demande de brevet No.: Patentgesuch Nr.: CH 4526/78

I.I.B. Nr.:

HO 13 283

|                        | Documents considérés comme pertinents<br>Einschlägige Dokumente                                                                                                           |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catégorie<br>Kategorie | Citation du document avec indication, en cas de besoin, des parties pertinentes.<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile | Revendications con-<br>cernées<br>Betrifft Anspruch<br>Nr. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A                      | <u>US- A - 3 984 620</u> (D.R. ROBILLARD)<br>*colonne 1, lignes 7-11 et 55-58 *                                                                                           | 1                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A                      | <u>US - A - 3 881 175</u> (F.M. WANLASS)<br>*colonne 2, lignes 14-26 *                                                                                                    | 1                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A                      | US - A - 3 975 648 (M.C. TOBEY) *résumé; colonne 1, lignes 6-13 *                                                                                                         | 3                                                          | : .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A                      | IBM TECHNICAL DISCLOSURE BULLETIN, vol. 19, no. 11, avril 1977 NEW YORK (US) M.D. LOESCH: "Digital Adjustment of Precision Regulators", page 4109. * page 4109*           | 3,6,7                                                      | Domaines techniques recherches Recherchierte Sachgebiete (INT. CL.2)  G 04 C 10/04 G 04 G 1/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A                      | US - A - 3 991 553 (J.M. BERGEY) *colonne 2, lignes 7-11; colonne 6, lignes 37-39                                                                                         | 3                                                          | G 05 F 1/46<br>3/20<br>H 01 L 27/08<br>23/56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A/P                    | ELECTRONICS, vol. 50, no. 15, juillet 1977 NEW YORK (US) C. VISWANATH: "D-a converter controls programmable power source", page 125.  * page 125 *                        |                                                            | G 01 R 31/28 G 01 R 31/36 35/00 19/165  Catégorie des documents cités Kategorie der genannten Dokumente: X: particulièrement pertinent von besonderer Bedeutung A: arrière-plan technologique technologischer Hintergrund O: divulgation non-écrite nichtschriftliche Offenbarung P: document intercalaire Zwischenliteratur T: théorie ou principe à la base de l'invention der Erfindung zugrunde liegende Theorien oder Grundsätze E: demande faisant interférence kollidierende Anmeldung L: document cité pour d'autres raisons aus andern Gründen angeführtes Dokument &: membre de la même famille, document correspondant Mitglied der gleichen Patentfamilie; übereinstimmendes Dokument |

| Etandua | de la | recherc | he/IIm | fano | der | Recherch | he |

|---------|-------|---------|--------|------|-----|----------|----|

| Erenaue | ae ia | recnerc | ne/ Um | lang | uei | RECHELCI | 16 |

Revendications ayant fait l'objet de recherches Recherchierte Patentansprüche:

ensemble

Revendications n'ayant pas fait l'objet de recherches Nicht recherchierte Patentansprüche: Raison: Grund:

| Date d'achèvement de la recherche/Abschlussdatum der Recherche |  |

|----------------------------------------------------------------|--|

| 24.08.1981                                                     |  |

#### REVENDICATIONS •

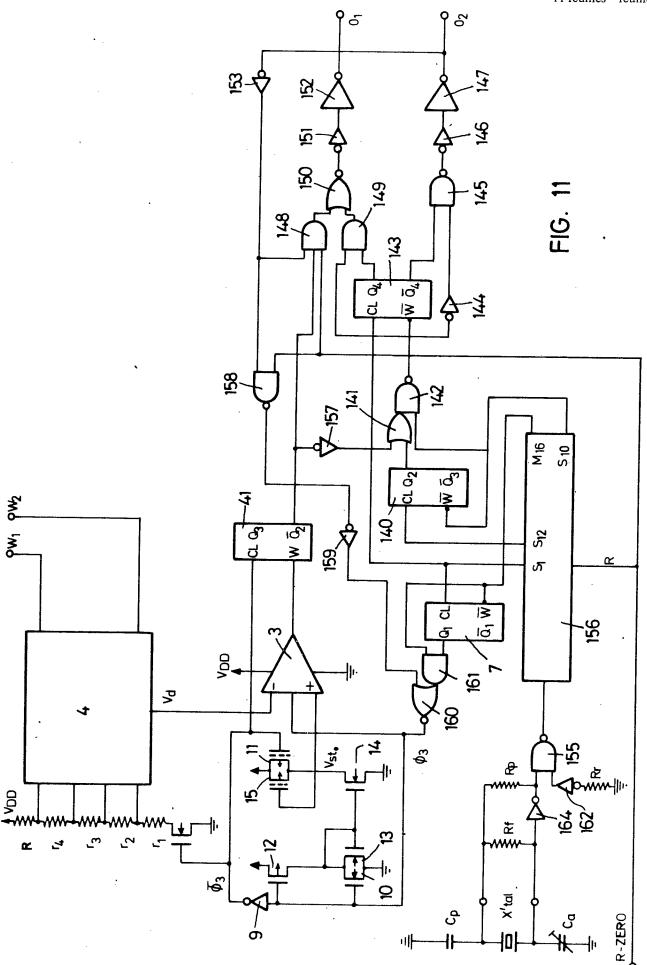

1. Circuit intégré à semi-conducteur constituant un circuit de détection de tension et comprenant une source de tension de référence (1, figs 1+2; 9-15, fig. 11) pour produire une tension de référence (W<sub>st</sub>), un circuit convertisseur de tension (2, figs 1+2;  $r_1$ ,  $r_2$ ,  $r_3$ ,  $r_4$ , R, fig. 11) pour produire une tension à comparer (W<sub>d</sub>) représentative de la tension détectée, et des moyens comparateurs (3, figs 1+2; 3, fig. 11) pour recevoir ladite tension de référence et ladite tension à comparer, et pour fournir un signal de comparaison en réponse à celles-ci, caractérisé en ce qu'un circuit régulateur de comparaison (4, figs 1+2; 4, fig. 11) est connecté entre ladite source de tension de référence (1, figs 1+2; 9-15, fig. 11) ou ledit circuit convertisseur (2, figs 1+2;  $r_1$ ,  $r_2$ ,  $r_3$ ,  $r_4$ ,  $R_1$ fig. 11) d'une part, et lesdits moyens comparateurs (3, figs 1, 2; 3, fig. 11) d'autre part, pour ajuster ladite tension de référence (W<sub>st</sub>) ou ladite tension à comparer (W<sub>d</sub>).

2. Circuit intégré selon la revendication 1, caractérisé en ce qu'il comprend, intégrés en un seul substrat, un circuit (1) convertisseur de tension (2), un circuit de comparaison (3) constituant lesdits moyens comparateurs et ledit circuit régu-

lateur de comparaison (4).

3. Circuit intégré selon la revendication 2, caractérisé en ce que ledit circuit de comparaison (3) est constitué par un amplificateur différentiel, ledit circuit (1) constituant la source de tension de référence ou ledit circuit convertisseur de tension (2) étant agencé pour effectuer une conversion en fonction d'un rapport de résistances.

4. Circuit intégré selon la revendication 2, caractérisé en ce qu'au moins un élément de mémoire non volatil est utilisé

dans ledit circuit régulateur de comparaison.

- 5. Circuit intégré selon la revendication 2, caractérisé en ce qu'il comprend des moyens (32-39) pour réaliser par ce de tension de référence, du circuit convertisseur de tension, du circuit de comparaison, et du circuit régulateur de comparaison.

- 6. Procédé de mise en action du circuit intégré selon la revendication 1, caractérisé en ce que la tension de référence ou la tension à comparer représentative de la tension détectée est ajustée à l'intérieur du circuit intégré avant la mise en place de celui-ci.

- 7. Procédé de mise en action selon la revendication 6, caractérisé en ce que la tension de référence ou la tension à comparer représentative de la tension détectée est ajustée di-

- 8. Procédé de mise en action selon la revendication 6, caractérisé en ce que la tension de référence ou la tension à comparer représentative de la tension détectée, est ajustée par la sélection de connexions lors de la mise en place du circuit intégré.

La présente invention concerne un circuit intégré à semiconducteur constituant un circuit détecteur de tension et comprenant une source de tension de référence pour produire une tension de référence, un circuit convertisseur de tension pour produire une tension à comparer représentative de la tension détectée, et des moyens comparateurs pour recevoir ladite tension de référence et ladite tension à comparer et pour fournir un signal de comparaison en réponse à cellesci. L'invention vise la constitution d'un tel circuit détecteur de tension en intégration complète, permettant un préajustage à l'intérieur du circuit intégré avant son montage et permettant d'éviter, ou tout au moins de limiter fortement, la nécessité d'avoir des éléments d'ajustage extérieurs au circuit intégré.

Jusqu'ici, avec de tels circuits détecteurs de tension, qui devaient être réglés relativement à un jeu donné de tensions auxquelles'une ou plusieurs tensions détectées devaient être comparées, on effectuait des réglages lors du montage et surtout après le montage du circuit intégré dans un appareil 10 électronique, à l'aide de résistances variables ou de résistances ajustables sélectivement de manière adéquate, et ces processus d'ajustage étaient externes au circuit intégré. Ce processus de réglage était, cela va de soi, compliqué, délicat et coûteux et, plus le réglage des différentes tensions du jeu de 15 tension à établir était sévère, plus le coût de ce réglage était élevé, ce qui fait que ce processus ne permettait pas d'atteindre des performances de coût avantageux. Les difficultés rencontrées sont particulièrement attribuables aux fluctuations des caractéristiques électriques des éléments passifs et constituant ladite source de tension de référence, ledit circuit 20 actifs qui sont inclus dans le circuit intégré et qui entrent en jeu pour l'établissement du circuit détecteur de tension. Le processus d'ajustage était donc très coûteux et ceci entrait en contradiction avec la recherche d'un rendement aussi bon que possible, que l'utilisation de circuits intégrés devrait fa-25 voriser. Ainsi, si l'ajustement nécessaire peut être réalisé facilement à l'intérieur du circuit intégré, avant le montage de celui-ci et en dépit des fluctuations des particularités de chacun des éléments du circuit intégré, le coût du processus d'ajustage pourra être notablement réduit conjointement à 30 une amélioration très appréciable du rendement de fabrication des circuits intégrés et des appareils électroniques comprenant des circuits intégrés.

Il faut considérer aussi que, dans les appareils électroniques et tout particulièrement dans les appareils électroniques échantillonnage la commande du circuit constituant la sour- 35 de très petites dimensions, les éléments passifs et actifs qui réalisent les fonctions comprennent ordinairement tout ou partie des composants formant un circuit détecteur de tension, ces composants se répartissant sur une ou souvent sur plusieurs plaquettes de circuit intégré, et, pour ces com-40 posants-là, sans parler de ceux qui ne pouvaient pas être intégrés, on pouvait au maximum attendre un rendement et des performances reflétant exactement les conditions qui règnent dans un circuit intégré (c'est-à-dire une assez forte dispersion), et l'on a longtemps espéré en vain arriver à réaliser 45 un ensemble de circuit tel que la régulation des tensions à établir pour la détection de tension soit simple et insensible aux possibles fluctuations respectives des caractéristiques des éléments entrant en jeu, chose qui aurait permis d'améliorer le rendement et les performances des circuits intégrés.

Une performance visée par la présente invention est donc 50 de fournir un circuit intégré régulateur de tension présentant des moyens par lesquels un ajustement interne dans le circuit intégré soit réalisable avant le montage de ce circuit intégré.

Comme illustration de l'art antérieur, il y a lieu de con-55 sidérer essentiellement les exposés US-A-3 984 620, et US-A-3 881 175. On remarque que le rapport de recherche qui les cite les considère comme «documents d'arrière-plan technologique», aptes à situer le domaine général de l'invention, mais sans porter atteinte à sa brevetabilité.

La première publication antérieure susmentionnée décrit un circuit intégré à semi-conducteurs multi-plaquettes. Elle donne une bonne illustration de la technique des circuits intégrés, mais ne divulgue nullement un circuit typiquement destiné à une détection de tension, et encore moins un circuit 65 comprenant des moyens régulateurs d'une comparaison entre deux tensions.

La deuxième publication antérieure susmentionnée décrit un circuit intégré du type particulier SOS, comprenant une

mémoire. Cette publication décrit la façon dont certains des éléments-mémoires sont sélectionnés à l'aide d'une pluralité d'éléments fusibles, pour déterminer un certain ordre dans un agencement de circuits-mémoires. Cette détermination, qui tient compte des aléas de fabrication, est effectuée lors du contrôle du circuit intégré, avant son montage. Ici aussi, il n'est toutefois pas question d'un circuit intégré du type détecteur de tension, et si la fig. 3 de cette publication comprend notamment un bloc comparateur et un bloc générateur de référence, il ne s'agit pas là d'éléments qui sont contenus dans le circuit intégré, mais d'éléments compris dans un appareillage extérieur de contrôle du circuit intégré et de sélection, dans celui-ci, d'une combinaison utilisable de plusieurs circuits-mémoires.

Aucune des publications antérieures citées ne concerne ainsi directement un circuit intégré à semi-conducteur constituant un circuit détecteur de tension, et à plus forte raison, elle ne présente aucune divulgation, ni même suggestion, de l'utilisation d'un circuit régulateur de comparaison dans un tel circuit intégré de détection.

Le but de l'invention est notamment, compte tenu des considérations précédemment énoncées, de fournir un circuit intégré à semi-conducteur constituant un circuit détecteur de tension simple, fiable, se prêtant aisément à une fabrication en série, et permettant d'éliminer ou de limiter dans une très grande mesure les opérations d'ajustage au moment du montage du circuit intégré, même compte tenu d'une notable dispersion de fabrication.

L'invention atteint ce but par la présence des caractères énoncés dans la revendication 1 annexée.

Dans des formes spécialement avantageuses de l'objet de l'invention, la configuration et l'agencement des parties de circuit sont tels que les fluctuations respectives des éléments qui constituent le détecteur de tension n'influent pas sur l'ensemble de ce circuit, les valeurs de tension à détecter pouvant 35 être fixées à volonté.

Le dessin annexé illustre, à titre d'exemple, des formes d'exécution de l'objet de l'invention; dans ce dessin:

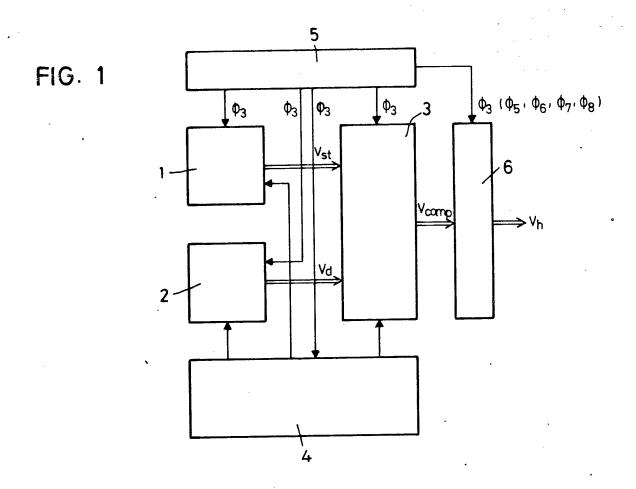

la fig. 1 est un schéma-bloc d'un circuit intégré à semiconducteur du type conforme à l'invention, réalisant un circuit détecteur de tension,

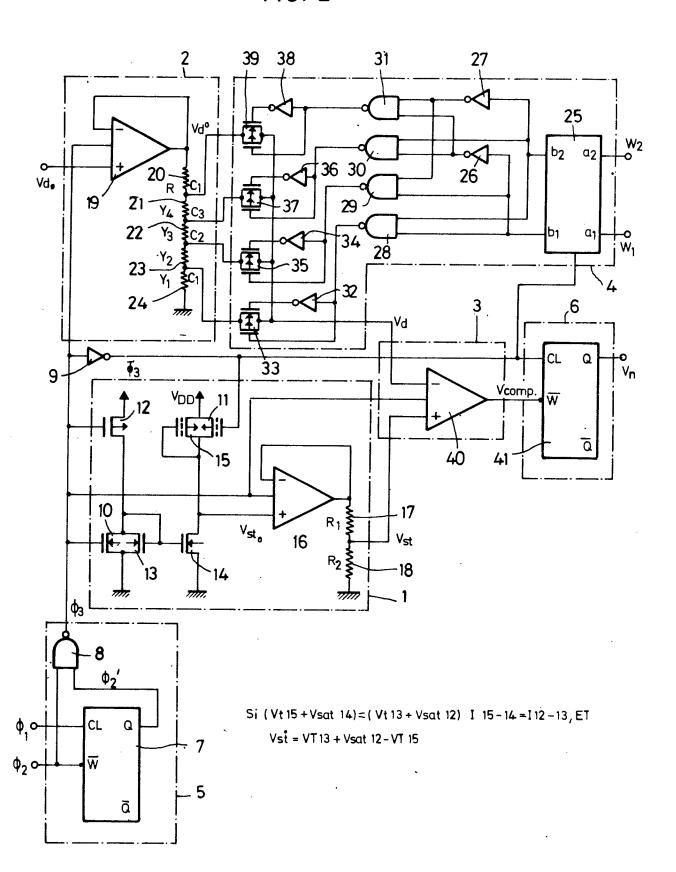

la fig. 2 est un schéma plus détaillé d'une forme d'exécution conforme à l'invention d'un circuit détecteur de tensions en circuit intégré, comprenant des moyens d'ajustage intégrés,

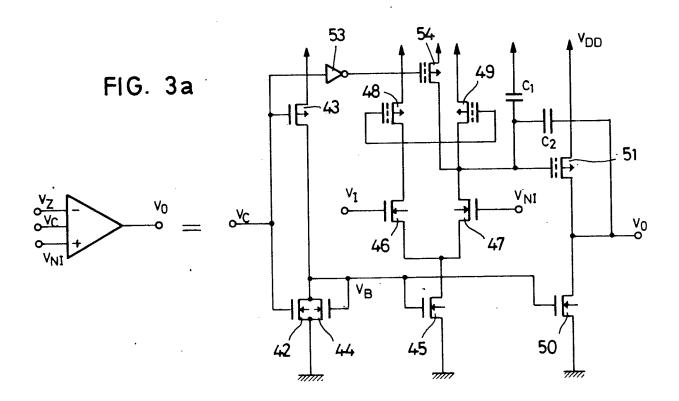

la fig. 3a est un schéma d'une forme d'exécution d'un amplificateur opérationnel, ou amplificateur différentiel, composé d'éléments CMOS et utilisé dans un circuit détecteur de tensions en circuit intégré conforme à l'invention,

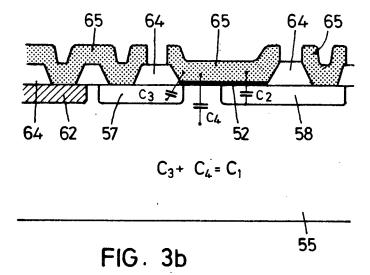

la fig. 3b est une vue en coupe schématique et à grande échelle d'une partie de circuit intégré MOS,

la fig. 4a est une vue en coupe, schématique et à grande échelle, d'une partie de circuit intégré MOS présentant des caractéristiques différentes de celles que représente la fig. 3b,

la fig. 4b est une représentation de la réalisation de résistances au sein d'un circuit intégré comme celui des figs 3b et 4a,

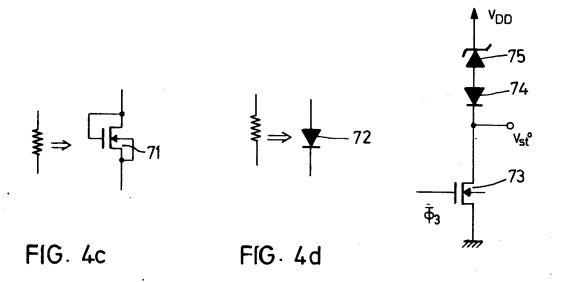

la fig. 4c est une représentation d'une résistance en circuit intégré réalisée par un composant MOS,

la fig. 4d est une représentation d'une résistance en circuit intégré réalisée par une diode,

la fig. 4e est un schéma d'une autre manière de réaliser un élément de référence de tension dans un circuit de référence de tension au sein d'un circuit détecteur de tension en circuit intégré, conforme à l'invention,

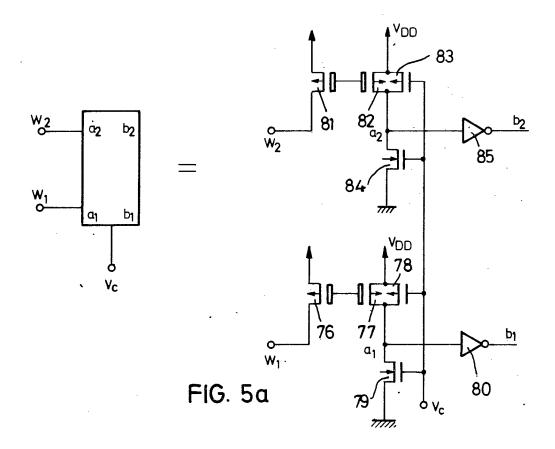

la fig. 5a est un schéma d'une forme d'exécution d'un circuit de commande d'un circuit détecteur de tension en circuit intégré, dans lequel sont compris des moyens d'ajustage de

paramètres des composants du circuit intégré,

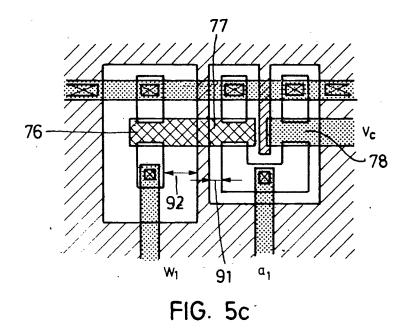

la fig. 5b est une vue en coupe, schématique et à plus grande échelle, d'une partie de circuit intégré comprenant des éléments MOS et FAMOS,

la fig. 5c est une vue de dessus d'une partie du circuit intégré MOS-FAMOS de la fig. 5b, représentant des éléments compris dans le schéma de la fig. 5a,

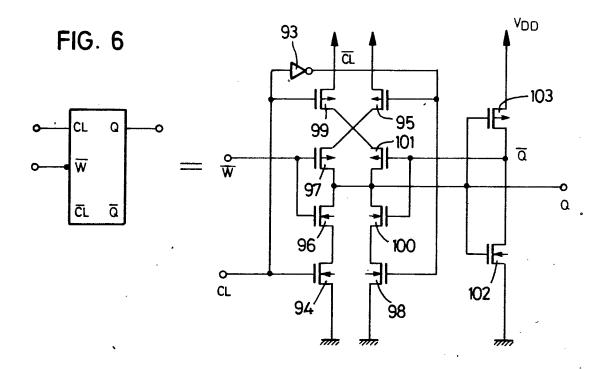

la fig. 6 est un schéma d'un flip-flop en circuit intégré utilisé dans le circuit détecteur de tension conforme à l'inven-10 tion,

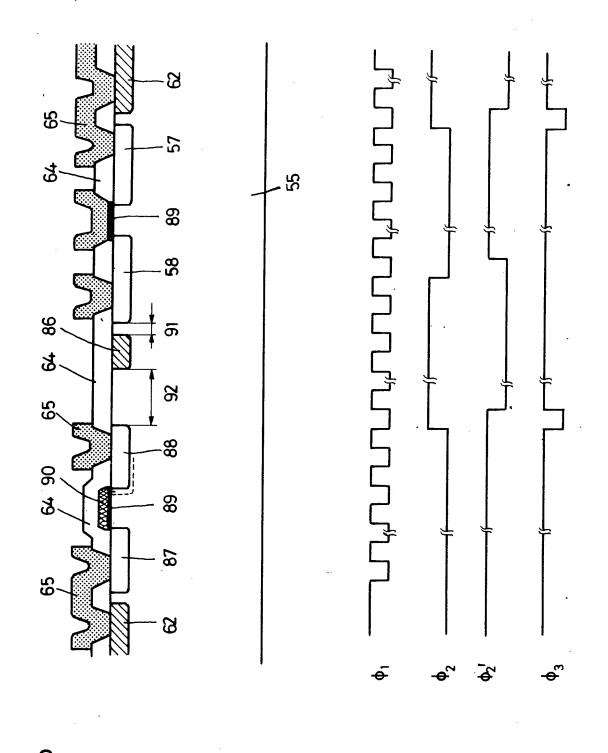

la fig. 7a est un diagramme des niveaux logiques en fonction du temps en différents endroits d'un circuit cadenceur compris dans le schéma détaillé de la fig. 2,

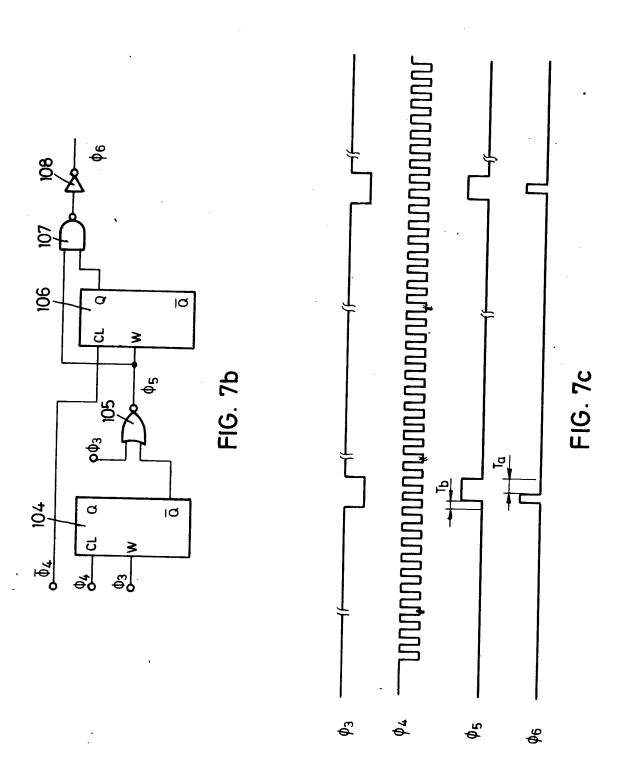

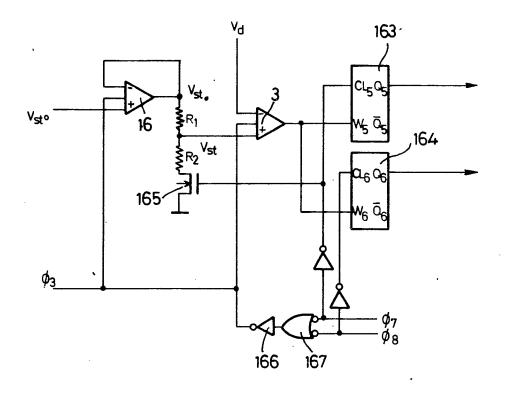

la fig. 7b est un schéma d'une autre forme d'exécution 15 d'un circuit cadenceur, ou générateur d'impulsions, utilisable pour le circuit détecteur de tension en circuit intégré constituant une forme d'exécution de l'invention,

la fig. 7c est un diagramme des niveaux logiques en fonction du temps en différents endroits du cadenceur selon le 20 schéma de la fig. 7b,

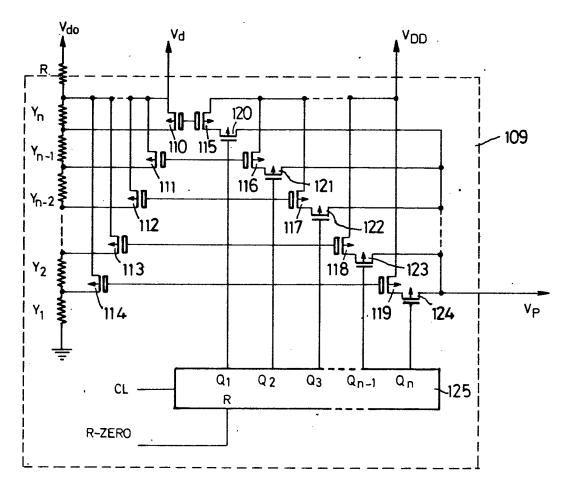

la fig. 8 est une forme d'exécution d'une variante d'un circuit de régulation automatique d'une tension établie dérivée d'une tension détectée dans un circuit détecteur de tension, comprenant des moyens d'ajustage internes au circuit intégré, conformément à l'invention,

la fig. 9 est un schéma représentant une manière d'utiliser le circuit de régulation selon la fig. 8, les moyens d'ajustage internes pour le circuit intégré selon l'invention étant employés d'une façon particulière pour l'établissement du cir30 cuit régulateur automatique de la tension détectée dans le circuit détecteur de tensions,

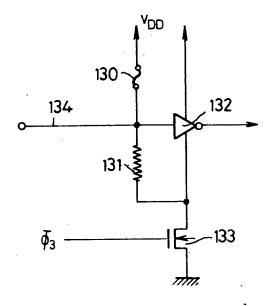

la fig. 10 est un schéma d'une variante concernant des moyens de mémorisation non volatile de la régulation des composants du circuit intégré selon l'invention,

la fig. 11 est un schéma général d'une forme d'exécution d'un circuit intégré conforme à l'invention utilisé pour réaliser au moins une partie des circuits d'une montre électronique.

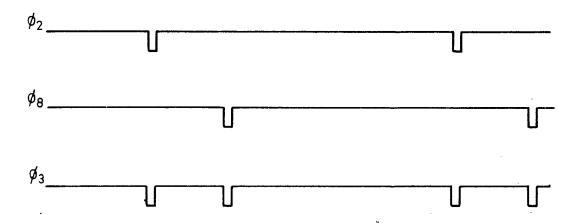

la fig. 12a est un schéma d'une forme d'exécution confor-40 me à l'invention d'un circuit détecteur de tension en circuit intégré, conforme à l'invention, et permettant la détection de deux niveaux de tension, et

la fig. 12b est un diagramme de niveaux logiques en fonction du temps pour les impulsions d'échantillonnage et de 45 maintien de mémorisation dans un circuit détecteur de tensions conforme à l'invention et apte à détecter deux niveaux de tension.

La constitution d'un circuit intégré à semi-conducteur réalisant les performances précédemment mentionnées est 50 représentée par le schéma-bloc de la fig. 1 qui concerne une forme d'exécution consistant en un circuit détecteur de tension. On y voit un circuit de tension de référence 1, qui engendre une tension de référence Vst qui ne dépend pas ou en tous les cas pas d'une manière complète de la tension sujette 55 à la détection. Le schéma comprend également un circuit 2 apte à produire une série de tensions qui découlent selon une proportion bien déterminée d'une tension détectée, ce circuit pouvant fournir aussi une tension directement liée à la tension détectée, ou, en d'autres termes, une tension qui corres-60 pond exactement à une valeur de tension à contrôler. Dans ce circuit 2, la tension détectée est convertie en une série de tensions de valeurs différentes mais dépendant de la tension détectée. Le schéma de la fig. 1 comprend également un circuit de comparaison qui compare la tension de référence, ou 65 une fraction de celle-ci, à la tension détectée Vd ou à une fraction de celle-ci. Le circuit de comparaison 3 compare donc les sorties des circuits 1 et 2, respectivement de tension de référence et de détection de tension, dont le rôle peut du

5 639 810 G

reste être interverti. La tension de référence (ou la tension de détection) est réellement une tension pouvant être choisie à volonté en tant qu'une fraction plus ou moins grande des tensions de référence et de détection, qui sont fournies au circuit de comparaison, le choix des fractions considérées dé- 5 pendant de la valeur à contrôler. Inversement, si l'on connaît exactement la valeur de tension à contrôler, ces circuits peuvent permettre de sélectionner adéquatement les fractions qui sont à comparer pour obtenir le résultat voulu, pour autant que la valeur de tension à établir soit bien déterminée. Le circuit 4 est, conformément à l'invention, un circuit comprenant des moyens d'ajustage pour sélectionner systématiquement la tension de référence du circuit 1 et la tension de détection convertie dans le circuit 2, c'est-à-dire que ce circuit 4 choisit l'une ou l'autre de deux tensions de référence (ou plus de deux tensions de référence) ou alors qu'il choisit l'une de quatre (ou davantage) fractions bien déterminées de la tension détectée, afin de provoquer la transmission de celle-ci au circuit de comparaison de tensions. Ces circuits 1, 2, 3 et 4 consomment naturellement une certaine puissance électrique, dans le cas au moins où l'alimentation leur serait appliquée en permanence. Toutefois, dans de petits appareils électroniques portatifs, alimentés par une pile de capacité limitée, on rend insignifiante la consommation de ces quatre circuits en appliquant un système d'échantillonnage qui rend 25 trée W est inversé et mémorisé en tant que signal W, au la consommation de puissance aussi faible que possible, du courant n'étant consommé alors que durant une très petite fraction du temps. Un circuit 5 engendre des impulsions  $\Phi_3$  $(\Phi_5, \Phi_6, \Phi_7, \Phi_8)$  requises pour la commande de l'échantillonnage, ces impulsions de commande d'échantillonnage étant transmises à chacun ou à certains des quatre circuits 1, 2, 3 et 4, et si nécessaire à d'autres circuits encore, pour réaliser la fonction d'échantillonnage. L'information de sortie du circuit de comparaison 3 est toutefois en général requise d'une façon permanente, et, pour cette raison, il est nécessaire de prévoir un circuit de maintien (ou de verrou de sortie) sur la sortie du circuit de comparaison, ce circuit de maintien fournissant l'information en dehors des brèves périodes d'échantillonnage. Ce circuit de maintien 6, reçoit depuis le circuit générateur d'impulsions 5 les impulsions nécessaires pour «l'inscription» dans sa mémoire, c'est-à-dire pour mémoriser l'information échantillonnée. Dans le circuit détecteur de tensions dans son ensemble, les parties principales sont le circuit de référence de tension 1, le circuit convertisseur de tension détectée 2, le circuit de comparaison 3, et le circuit de régulation 4. Des moyens d'ajustage sont adjoints au circuit intégré d'une quelconque manière. Si le circuit intégré réalise, par exemple, un circuit détecteur de tension, comme cela est présentement décrit, la tension à établir sera déterminée approximativement à la valeur recherchée à l'aide de ces moyens d'ajustage. Selon les exigences d'exactitude de la tension à établir, il pourra naturellement être parfois nécessaire d'effectuer une régulation dépendant de quelque façon des caractéristiques réelles des éléments en liaison avec lesquels l'établissement d'une tension déterminée est effectuée.

Le schéma de cette forme d'exécution est représenté à la fig. 2 en liaison avec laquelle seront décrits les moyens d'ajustage particuliers qui distinguent l'invention. Les parties de circuit entourées de cadre en traits mixtes correspondent aux blocs de la fig. 1. En tant qu'élément actif, cette forme d'exécution, en circuit intégré, utilise des transistors à effet de champ à électrode de commande isolée, dénommés ciaprès transistors ou éléments MOS, ceci simplement à titre d'exemple.

On donnera tout d'abord des explications concernant le circuit générateur d'impulsions 5. Ce dernier est composé d'un flip-flop (ou élément de registre à décalage) 7 et d'une

porte ET INVERSE 8. Lorsque des signaux  $\Phi_1$  et  $\Phi_2$ , représentés à la fig. 7a, sont appliqués aux entrées de ce circuit 5, l'évolution du signal  $\Phi_2$  est décalée d'une durée égale à  $\frac{1}{2}$ impulsion cadencée, c'est-à-dire à ½ période du signal Φ<sub>1</sub>, à l'aide du flip-flop 7, ce signal retardé  $\Phi_2$  apparaissant sur la sortie Q du flip-flop. On note que l'entrée de donnée w du flip-flop 7 est une entrée de préparation inverse, de sorte que le signal Φ2' est non seulement décalé mais encore inversé par rapport au signal Φ<sub>1</sub>. La porte OU INVERSE 8 com-10 bine ces deux signaux pour fournir à sa sortie le signal  $\Phi_3$ , représenté également à la fig. 7a. Si par exemple Φ, est de 64 Hz et  $\Phi_2$  de  $\frac{1}{2}$  Hz, le signal  $\Phi_3$  sera au niveau bas durant 1/128 de seconde et au niveau haut durant un temps valant  $(2^{-1}/_{128})$  sec. On voit donc que l'impulsion de niveau bas est 15 de très faible durée, et constitue donc ce que l'on nomme une «impulsion différentielle». Les circuits 1, 2, 3, 4 et 6 sont mis en fonction similairement par cette impulsion différentielle et seulement durant celle-ci (à l'exception du circuit de verrou de sortie 6).

Le schéma du flip-flop 7 est représenté à la fig. 6. Puisque le signal d'impulsions cadencées CL est inversé, pour devenir CL, à l'aide de l'inverseur 93, les transistors de commutation à canal N 94 et à canal P 95 sont passants lorsque le signal CL est au niveau haut, temps durant lequel le signal sur l'enmoyen de l'inverseur formé par le transistor à canal N 96 et le transistor à canal P 97. D'une façon générale, les transistors respectivement à canal N et P seront par la suite désignés simplement par NT et PT.

La sortie Q du flip-flop portant donc le signal W, inverse de W, le NT 102 et le PT 103 vont inverser ce signal Q, pour en faire  $\overline{Q} = W$ . A ce moment, NT 98 et PT 99 sont bloqués. Ils ne deviendront passants que lorsque l'impulsion cadencée CL sera au niveau bas, et alors l'inversion du signal  $\overline{Q} = W$ 35 en Q = W sera effectuée par les transistors 100 et 101, de sorte que la sortie Q sera maintenue. Les transistors NT 94 et PT 95 seront alors bloqués. Le fonctionnement de ce circuit est tel que Q ne subit pas de changement, même si W (ou W) est modifié, tant que le signal de commande impulsionnel 40 CL est au niveau bas, et le changement, par lequel Q s'aligne sur l'inverse de W, intervient juste au moment où CL passe au niveau haut. Ainsi donc, le signal sur la sortie Q répète l'inverse du signal sur l'entrée W, avec une demi-période d'impulsion cadencée CL de décalage. Lorsque W ne change 45 pas, Q ne change pas non plus une demi-période après. C'est ainsi que fonctionne le flip-flop de la fig. 6, que l'on retrouve en tant que flip-flop 7 du cadre 5 de la fig. 2.

Sur cette fig. 2, c'est seulement lorsque  $\Phi_3$  est au niveau bas que du courant circule respectivement à travers les cir-50 cuits 1, 2, 3 et 4 qui sont ainsi en fonction pour l'essentiel de leur effet. Il doit bien être compris, selon l'exemple ci-décrit, que la consommation de courant de chaque circuit est extrêmement faible, puisque, dans les conditions précédemment mentionnées, la consommation moyenne ne sera que  $55^{1}/_{256}$  de la consommation de pointe.

Le fait que le circuit détecteur de tensions ci-décrit est mis en fonction seulement durant les courtes impulsions différentielles constitue le premier caractère qui distingue le circuit détecteur de tension selon l'invention.

On va décrire maintenant en détail le circuit de référence de tension 1. NT 10 est bloqué lorsque  $\Phi_3$  est au niveau bas et PT 11 est également bloqué puisqu'il reçoit, par l'inverseur 9, le signal  $\overline{\Phi}_3$ , au niveau haut. Ainsi donc, les caractéristiques statiques du circuit de référence de tension 1 ne se-65 ront nullement affectées par les particularités de ces transistors 10 et 11. D'autre part, le circuit 1 comprend un amplificateur opérationnel 16 dont le circuit détaillé correspond à ce que montre la fig. 3a. On y voit que le fonctionnement de

cet amplificateur opérationnel n'est nullement en relation avec les transistors 42 et 54, lesquels sont bloqués durant l'impulsion négative de  $\Phi_3$ , comme le montre la fig. 3a. Au contraire, lorsque  $\Phi_3$  est à l'état haut, PT 12 est bloqué et NT 10 est passant (fig. 2) et le potentiel sur le drain de NT 10 est bas, bloquant NT 14 tandis que PT 11 est passant, ce qui fait qu'aucun courant ne peut trouver de voie conductrice pour y circuler. En ce qui concerne l'amplificateur opérationnel 16, PT 43 est bloqué et NT 42 est passant, de ce fait, les NT 44, 45 et 50 sont à l'état bloqué, et aucun courant ne circule. Simultanément, PT 54 est passant tandis que PT 51 est bloqué, aucune circulation de courant n'ayant donc lieu à travers les résistances 17 et 18.

Le circuit de tension de référence, qui fournit une tension de référence lorsque  $\Phi_3$  est bas, ne doit pas dépendre de la tension détectée et de la tension d'alimentation (VDD) et il ne doit pas non plus avoir une caractéristique de température défavorable, c'est-à-dire que la tension de référence ne doit pas varier avec la température. C'est pour cette raison que l'on a choisi, dans la présente forme d'exécution, de déterminer la tension de référence par la différence de deux tensions de seuil de transistors MOS. Pour produire des tensions de seuil différentes dans les éléments MOS, il est de pratique connue de procéder par dopage d'une partie au moins de l'électrode de commande et du canal à l'aide d'implantation d'ions; cela est avantageux du fait que, dès qu'il y a une différence, par exemple dans l'épaisseur du film isolant, ou dans la concentration du substrat, la caractéristique de température de la tension de seuil et du cœfficient de conductance (mobilité α) particuliers à l'élément MOS accuse une grande différence d'un élément MOS à l'autre, avec différentes valeurs de tension de seuil. En dopant l'élément à l'endroit de la partie inférieure de l'électrode de commande et du canal (dopage de donneur d'ions pour le transistor de type P et dopage d'accepteur d'ions pour le transistor de type N), on obtient un grand effet sur la caractéristique de température, similairement à ce qui résulte d'une différence de concentrations dans le substrat. En fin de compte, le dopage du canal constitue la meilleure méthode pour doper en accepteur d'ions le transistor P et en donneur d'ions le transistor N.

La tension de seuil subit, lors du dopage, un décalage de diminution donné par la formule I

# q Nnet τοχ

Dans cette formule, la quantité de charge «net» est q, la constante diélectrique relative du film isolant de l'électrode de commande est sox, la constante diélectrique dans le vide est so, l'épaisseur du fil isolant de l'électrode de commande tox, et la quantité d'ions d'implantation est N net, et l'on peut par ailleurs remarquer qu'il n'y a pas de caractéristique de température (ou pas de cœfficient de température) pour la quantité de décalage elle-même, ce qui est avantageux pour l'utilisation que l'on en fait dans la présente invention. Egalement en ce qui concerne le cœfficient de conductance (mobilité α), les variations de la valeur absolue pour de mêmes dimensions géométriques peuvent être expérimentalement corrigées, et la variation de la caractéristique de température est également plus faible que dans les autres cas, comme cela a déjà été mentionné. L'accepteur d'ions pour le dopage sur le transistor de type P est par exemple 11 B+ tandis que le donneur d'ions pour doper le transistor de type N est par exemple 31P+. Sur la fig. 2, des transistors qui ont des tensions de seuil ayant ainsi été décalées par dopage du canal sont désignés par une ligne additionnelle en traits pointillés à l'endroit de leur électrode de commande. Puisque le dopage n'est utilisé que pour les transistors de type P dans cette forme d'exécution, les transistors de type N doivent être déterminés, relativement à leur concentration de substrat, de façon à présenter des valeurs de tension de seuil correspondantes à celles des transistors de type P qui ont été dopés.

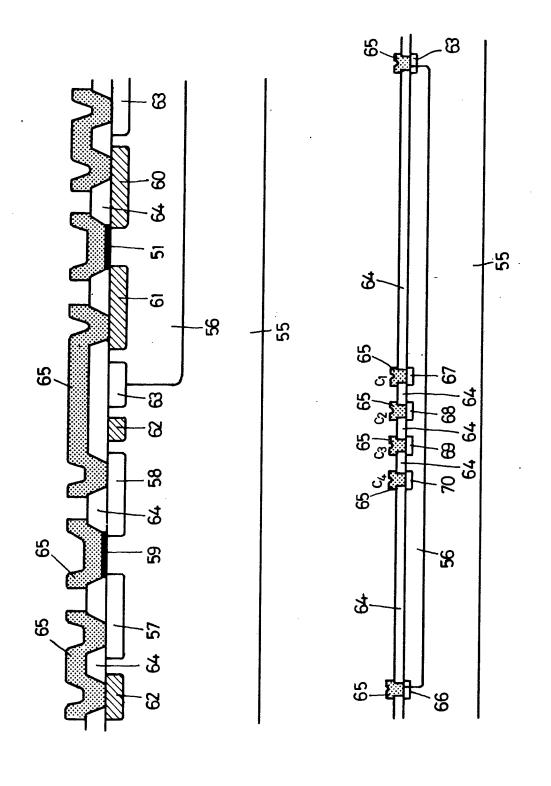

La constitution d'un circuit intégré contenant de tels transistors MOS à tension de seuil rabaissée (il s'agit en général d'éléments MOS complémentaires, également dénommés CMOS) va être maintenant expliquée en liaison avec la fig. 4a. Un îlot 56 de type P est formé dans le substrat de 10 silicone N<sup>-</sup> 55, et une couche d'isolation 63 pour les transistors de type N est formée par diffusion de type P ou par implantation d'ions, conjointement ou non avec la source 57 et le drain 58 pour le transistor de type P. La couche d'isolation 62 pour le transistor de type P est formée par une diffusion 15 de type N ou par une implantation d'ions simultanément ou non avec la source 60 et le drain 61 pour le transistor de type N. On voit encore en 59 un film d'isolement de propreté, en 64 un film d'isolation de champ et, en 65, les moyens voulus pour établir les connexions avec l'électrode de commande, le 20 substrat, la source ou le drain, un des moyens les plus souvent utilisés pour la câblage consiste en un dépôt d'aluminium. Après qu'un masque résistant 59 ait été formé pour couvrir tous les canaux autres que ceux dans lesquels on désire effectuer un traitement de dopage, des ions sont appliqués pour doper les canaux désirés à partir du film d'isolation de l'électrode de commande. On obtient ainsi, comme déjà mentionné plus haut, un transistor ayant un seuil de tension faible, tandis que les transistors qui ont été couverts avec un masque résistant n'ont pas subi de changement. En 30 fait, il est possible également de doper tout d'abord tous les canaux des transistors ayant la même polarité, et ensuite de doper d'une façon particulière le seul transistor désiré (ou les seuls transistors désirés). De toute façon, ce que l'on tient à obtenir, et que l'on obtient, notamment de la façon précé-35 demment décrite - est une différence entre les tensions de seuil de différents éléments de même polarité.

Afin de donner au transistor de type N une valeur de seuil compatible avec celle des transistors de type P qui ont une faible valeur de seuil, il est bon de diminuer adéquate-40 ment la concentration de l'îlot P 56 seulement lorsque celui-ci est formé, ou alors il est également avantageux de donner un dopage d'ions donneurs à tous les canaux des transistors de type N après que le film isolant d'électrode de commande a été formé, nonobstant le fait que l'îlot P 56 pré-45 sente une concentration relativement haute. En tous les cas, l'avantage qu'il y a à établir une différence de tension de seuil par dopage du canal lorsqu'il s'agit de créer une tension de référence consiste, d'une part, dans la stabilité à l'égard des variations de température et des vatiations de tension 50 d'alimentation que l'on obtient ainsi, et, d'autre part, dans le fait que l'on obtient une tension de référence uniforme dans le cadre du processus de fabrication seulement si la stabilité des seuls «Nnet» et «ox» se trouve assurée, étant donné que seule la différence est sujette à des difficultés.

Le fait d'avoir, par le biais des mesures précédemment décrites, une tension de référence stable à l'égard des variations de température, des variations de tension d'alimentation, et de la dispersion au cours du procédé de fabrication, constitue un second caractère qui distingue le circuit de dé-60 tection de tension qui constitue une forme d'exécution typique et particulièrement avantageuse de l'invention.

On va maintenant expliquer le principe de fonctionnement du circuit de référence de tension. Le rapport du cœfficient de conductance

(mobilité

$$\alpha \times \frac{\epsilon o \epsilon o x}{\tau o x} \times \frac{\text{largeur du canal}}{\text{longueur du canal}}$$

dans le PT 12 au cœfficient de conductance dans le PT 15 est

639 810 G

rendu égal au rapport du cœfficient de conductance dans le NT 13 au cœfficient de conductance dans le NT 14. Le NT 13 et le NT 14 sont disposés de façon adjacente l'un à l'autre dans la plaquette de circuit intégré, de sorte que les valeurs de tension de seuil sont améliorées quant à leur égalité. Il en résulte qu'une valeur de tension VTP - VGTP = Vst<sub>0</sub> correspondant à la différence de la tension de seuil VTP du PT 12 et de la tension de seuil VGTP du PT 15, est obtenue en direction positive par rapport à la masse, en tant que potentiel de référence. Plus exactement, on a:  $Vst_0 = V\tilde{T}_{13} +$  $Vsat_{12} - VT_{15}$ .

A titre d'exemple, pour simplifier, le rapport des cœfficients de conductance peut être admis comme étant 1. Naturellement, les longueurs des canaux du PT 12 et du PT 15, de même que les longueurs des canaux du NT 11 et NT 14, sont 15 rendues égales. Sinon, il serait difficile de donner au rapport des cœfficients de conductance la valeur désirée, étant donné qu'il y aurait une variété de fluctuations de profondeur résultant de différents types de diffusion, etc... La tension de référence Vsto ainsi obtenue est en général reproduite à plus basse impédance par un amplificateur répéteur de tension 16 dont la tension de sortie est théoriquement égale à Vsto. Puisque cette tension est divisée ensuite par les résistances de haute valeur 17 et 18, la tension de référence finalement obtenue est

$$Vst = \frac{R_2}{R_1 + R_2} Vst_0.$$

L'amplificateur opérationnel constituant l'étage répéteur de tension est composé de la manière montrée à la fig. 3a. Lorsque Vc est au niveau bas, le NT 42 est bloqué et le PT 54 est également bloqué par l'intermédiaire de l'inverseur 53, par contre, le PT 43, le PT 51, le PN 44, le PN 45 et le PN 50 sont à l'état passant, de sorte que du courant est délivré sur les voies de conduction respectives. Etant donné que le PT 43 a une tension de seuil quelque peu plus élevée et un cœfficient de conductance quelque peu plus bas, comparativement au NT 44, la tension de polarisation VB est quelque peu plus élevée que la tension de seuil du NT. Le NT 46, d'entrée inversée, et le NT 47, d'entrée non inversée, sont des 40 re les dites tensions de «sursaut» dans une mesure aussi éléments ayant les mêmes dimensions géométriques et les mêmes caractéristiques électriques. Le PT 48 et le PT 49, transistors de charge complémentaires, sont également des éléments présentant entre eux les mêmes dimensions géométriques et les mêmes caractéristiques électriques. Lorsque les potentiels sur les entrées  $V_I$  et  $V_{NI}$  sont plus hauts que les tensions de seuil de NT 46 et NT 47, le courant qui circule à travers le NT 45 est constant, quels que soient ces potentiels, et, de ce fait, le rapport des cœfficients de conductance pour PT 49 et 51 est double du rapport des cœfficients de conductance pour NT 45 et NT 50. Ainsi, en disposant de façon adjacente entre eux d'une part le PT 49 et le PT 51 et d'autre part le NT 45 et le NT 50, on obtient que les tensions de seuil des transistors de même polarité soient égales, et il est ainsi possible d'amener l'amplificateur opérationnel à amplifier seulement la différence de tension entre V<sub>I</sub> et V<sub>NI</sub>. Il est bon de déterminer les rapports des largeurs de canaux en égalisant les longueurs de canaux de PT 49 et PT 51 et de NT 45 et NT 50.

Si les cœfficients de conductance de NT 50 et de PT 51 sont rendus plus grands que ceux des transistors 45, 46, 47, 48 et 49, l'étage de sortie d'amplificateur comprenant le NT 50 et le PT 51 est à basse impédance et le point particulier de fréquence donnant un gain égal à 1 est très fortement supérieur au point de croisement de l'étage d'amplification différentielle comprenant les transistors 45, 46, 47, 48 et 49, de sorte que, le déplacement de phase étant inférieur à 180° au point de croisement, l'étage répéteur de tension 16 ne risque

pas d'osciller. De plus, si le cœfficient de conductance est plus grand, il est inévitablement nécessaire d'avoir une largeur de canal plus grande. Ainsi, en prenant toute la largeur du canal, la capacité globale (C<sub>1</sub>+C<sub>2</sub>)x (gain d'amplification de l'étage de sortie), comprenant la capacité de réaction  $\mathrm{C}_2$ qui s'établit de façon parasite entre le drain et l'électrode de commande du transistor 51, et la capacité C1 du film d'électrode de commande du transistor 51 qui adhère à celle-ci, et s'établit entre elle et le drain du transistor 49, atteint une va-10 leur relativement importante grâce à laquelle la caractéristique de fréquence est encore mieux stabilisée.

On peut expliquer cela au vu de la fig. 3b. Si la portion de superposition de l'électrode de commande et du drain du PT 51, représenté en tant que transistor 52 à la fig. 3b, prend une certaine extension supérieure au minimum représenté dans le cas de l'électrode 59 de la fig. 4a, la capacité C2 devient grande étant donné la grande largeur du canal. La capacité C<sub>1</sub> totalise la capacité C<sub>3</sub> entre l'électrode de commande et la source et la capacité C<sub>4</sub> entre l'électrode de com-20 mande et le substrat, capacités qui sont connectées en parallèle et sont considérées comme capacités entre l'électrode de commande et la source d'alimentation et qui sont relativement grandes du fait de la largeur du canal. Dans une tentative pour améliorer encore la stabilité à l'égard des oscilla-25 tions, la superposition de l'électrode de commande et du drain du transistor 52 pourrait encore être accrue, ce qui signifierait que la capacité de réaction serait encore augmentée, de façon arbitraire.

Il y a lieu de noter que les signes de références figurant à 30 la fig. 3b sont repris là où cela est possible sur la fig. 4a.

Un autre problème qui concerne l'amplificateur opérationnel représenté à la fig. 3a est celui de la tension «en sursaut» (offset voltage) qui se produit dans les étages différentiels. Ils sont théoriquement de l'ordre de quelques millivolts 35 et c'est seulement en prévoyant, pour le niveau bas du signal d'impulsion différentiel dans le circuit générateur d'impulsions 15, une durée d'impulsion d'une certaine importance que l'on peut minimiser l'afflux de courant de la source à courant constant 45 de l'amplificateur opérationnel et réduipoussée que possible, étant donné que la réponse de l'amplificateur opérationnel ne peut être abaissée que si la durée d'impulsion est élargie dans une certaine mesure. D'autre part, la caractéristique de température et la caractéristique 45 de tension des tensions «en sursaut» de l'amplificateur opérationnel de la fig. 3a sont véritablement très faibles et donc

Les résistances 17 et 18 peuvent être composées similairement à ce que montre la fig. 4b; plus précisément, en tant 50 que résistances CMOS, sous forme d'une couche incrustée P-, formée par diffusion ou implantation d'ions, d'une couche de type P ou de type N, établie par diffusion ou par implantation d'ions pour former une couche d'isolation source-drain, ou un silicium polycristallin. La fig. 4b illustre 55 le cas dans lequel la résistance est faite d'une couche encastrée P-. La résistance peut également être composée d'un élément MOS 71, comme le montre la fig. 4c, ou encore comme une diode 72, comme le montre la fig. 4d, le choix étant fait en fonction du procédé de fabrication. Dans la for-60 me d'exécution représentée à la fig. 2, Vst peut être déterminé seulement en fonction du rapport de résistance, et ce rapport n'a naturellement pas de caractéristique de température et de caractéristique de tension.

Comme on l'a mentionné, il y a là un troisième caractère 65 qui distingue particulièrement le circuit détecteur de tensions constituant une forme d'exécution particulière de l'invention, ce caractère consistant en l'adoption d'une conversion linéaire d'une différence de tension de seuil pour la tension

de référence, conversion linéaire qui correspond au rapport de deux résistances.

En d'autres termes, étant donné que l'on a

$$Vst = \frac{R_2}{R_1 + R_2} Vst_o,$$

on obtient  $Vst = Vst_0$  lorsque  $R_1$  vaut 0. Cela reviendrait au cas dans lequel les résistances 17 et 18 ne seraient pas présentes, ou également au cas où la tension Vst<sub>o</sub> apparaissant à la sortie des transistors NT 14 et PT 5 serait délivrée directement en tant que tension de sortie Vst. Compte tenu du fait que le comparateur 40 dans le cas de la présente forme d'exécution est à haute impédance d'entrée, par éléments MOS, comme le montre la fig. 3a, une sortie directe de ce type, sans étage répéteur de tension, serait également possible.

Accessoirement on note également que la tension d'une pile à l'oxyde d'argent, d'une pile au nickel-cadminum, d'une pile au mercure, etc. pourrait également être appliquée 20 péteur de tension (voltage follower) de sorte que la tension à l'entrée du comparateur 40 en tant que tension de référence Vst<sub>o</sub> ou Vst, ou que la chute de tension dans le sens avant dans une diode, ou encore la tension Zener dans une diode Zener, pourraient également être employées en tant que présentant certaines similitudes avec la valeur de seuil d'un élé-

ment MOS. Comme cela est bien connu, la caractéristique de température de la tension Zener évolue de façon opposée à la caractéristique de température de la chute de tension dans le sens passant d'une diode, et, pour cette raison, une diode 74 et une diode Zener 75 ont été mises en série dans l'exemple de source de tension de référence de la fig. 4e. Le transistor NT 73 effectue les commutations «en» et «hors» à la manière d'une résistance connectée en série avec la diode et la diode zener. Ainsi, la chute de tension dans le sens avant d'un 10 ensemble formé d'une diode Zener et d'une diode peut être utilisée en tant que tension de référence.

On va maintenant donner des explications concernant le circuit convertisseur de tension 2 (fig. 2). Il comprend un amplificateur opérationnel 19 constitué similairement à ce 15 qui est montré à la fig. 3a, pour l'amplificateur 16. Cet amplificateur opérationnel fonctionne lorsque  $\Phi_3$  est au niveau bas tandis que lorsque  $\Phi_3$  est au niveau élevé aucun courant ne peut circuler sur les voies de conduction du courant et les résistances 20, 21, 22, 23 et 24. L'élément 19 constitue un rédétectée Vdo est fournie à sa sortie, semblablement à ce que montre la fig. 3a, cette tension étant ensuite divisée par des résistances de haute valeur. Ainsi, si  $r_1 + r_2 + r_3 + r_4 = R$ , les tensions détectées sont sujettes à des conversions linéai-25 res, respectivement comme suit:

au point

$$c_1$$

,  $Vc_1 = \frac{r_1}{R+r}Vd_0$ , au point  $c_2$ ,  $Vc_2 = \frac{r_1+r_2}{R+r}Vd_0$ ,

au point

$$c_3$$

,  $Vc_3 = \frac{r_1 + r_2 + r_3}{R + r} Vd_0$ , au point  $c_4$ ,  $Vc_4 = \frac{r}{R + r} Vd_0$ .

Les résistances sujet de ces conversions linéaires sont également constituées comme le montre la fig. 4b, semblablement à ce qu'il en est des résistances 17 et 18. Sur cette figure, on voit un substrat de silicone N<sup>-</sup> 55, une couche d'incrustation (ou un îlot) P 56 étant formée conjointement avec la formation du substrat pour les transistors de type N. On voit, respectivement en 63, 66, 67, 68, 69 et 70, des couches de type P qui sont formées en même temps que la source et le drain des transistors de type P. L'îlot 63 est mis à la masse, par exemple par un câblage à l'aluminium. 67 correspond à  $c_1$ , 68 à  $c_2$ , 69 à  $c_3$  et 70 à  $c_4$ . La partie 66 est à connecter avec la sortie de l'amplificateur 19, par exemple par un câblage à l'aluminium. La résistance entre les points 63 et 67 correspond à la résistance r<sub>1</sub> 24, la résistance entre les points 67 et 68 correspond à la résistance r<sub>2</sub> 23, la résistance entre les points 68 et 69 correspond à la résistance r<sub>3</sub> 22, la résistance entre les points 69 et 70 correspond à la résistance r<sub>4</sub> 21, et la résistance entre les points 70 et 66 correspond à la résistance R 20. On voit encore en 64 un film isolant de champ, et en 65 le contact de l'aluminium et d'une couche de type P.

Un des avantages qu'il y a à constituer les résistances d'une façon uniforme par des couches incrustées, ou des îlots, P consiste dans le fait que le rapport des résistances n'a ainsi jamais de variation en fonction de la température ou en fonction de la tension. Un autre avantage réside en ce que les résistances sont ainsi déterminées de façon simple et précise, en correspondance avec leurs dimensions géométriques, seul le rapport pouvant poser en fait certains problèmes. Dans ce cas, il est bon de rendre uniforme la largeur des résistances et d'établir le rapport voulu sur la base de leur longueur, comme représenté à la fig. 4b.

On note que la raison pour laquelle on a choisi quatre points  $c_1$ ,  $c_2$ ,  $c_3$  et  $c_4$ , dans la forme d'exécution représentée, est une raison de simplicité du circuit de régulation dans lequel le choix entre ces quatre points peut être établi à l'aide de deux bits.

Le quatrième caractère qui distingue le circuit de détection de tension constituant une forme d'exécution particulièrement avantageuse de la présente invention consiste en ce 35 qu'un circuit convertisseur de la tension détectée convertit linéairement la tension à détecter, cette conversion linéaire étant déterminée par le rapport de résistances.

Par ailleurs, lorsque R vaut zéro, on a Vc<sub>4</sub> = Vd<sub>0</sub>, et la tension à détecter elle-même peut être appliquée par l'inter-40 médiaire de la porte de transmission 39.

Ainsi, la tension de référence susmentionnée et les tensions établies par conversion à partir de celle-ci deviennent, pour être détectées, des tensions de comparaison pour le comparateur.

On va expliquer maintenant la constitution et le fonctionnement du circuit de commande de régulation 4 qui comprend les moyens de commande d'ajustage, c'est-à-dire des moyens qui permettent de sélectionner, d'une façon directe ou par combinaison, différentes sorties préajustées, 50 afin, dans le cas particulier de la présente forme d'exécution qui constitue un circuit de détection de tension, de connecter la ou les sorties sélectionnées au circuit de comparaison 3 qui fournit les résultats de la détection de tension. Dans la forme d'exécution de la fig. 2, il s'agit de sélectionner une des qua-55 tre sorties C<sub>1</sub>-C<sub>4</sub> du circuit 2, convertisseur de la tension détectée Vdo. Avec deux bits appliqués aux entrées W1 et W2, il est possible de définir quatre états digitaux, I à IV, qui sont commandés par deux signaux b<sub>1</sub>, b<sub>2</sub> fournis par un circuit mémorisateur 25 qui emmagasine les ordres donnés sur les 60 entrées W1 et W2. Ces quatre états sont les suivants (0 désignant un niveau bas et 1 désignant un niveau haut):

I

$$(b_1, b_2) = (1, 1), Vd = Vc_1$$

II  $(b_1, b_2) = (1, 0), Vd = Vc_2$

III  $(b_1, b_2) = (0, 1), Vd = Vc_3$

IV  $(b_1, b_2) = (0, 0), Vd = Vc_4$

Vd représente l'information de sortie à la suite de la sélection, et Vc<sub>1</sub>, Vc<sub>2</sub>, Vc<sub>3</sub> et Vc<sub>4</sub> représentent les valeurs d'entrée dont l'une est sélectionnée.

9

Dans l'état «1», la porte ET INVERSE 28 reçoit deux niveaux «1» sur ses entrées et fournit donc un niveau «0» à sa sortie, lequel rend passante la porte de transmission 33, à l'aide d'un inverseur 32 pour le transistor de type T de cette porte de transmission 33. Celle-ci transfère la sortie  $C_1$  du circuit de tension de détection 2 sur une entrée du comparateur 40 dans le circuit de comparaison 3. Les trois autres portes ET INVERSE 29, 30, 31 ont toutes au moins une de leurs entrées au niveau «0», de sorte qu'elles fournissent touqué la porte de transmission, respectivement 35, 37, 39 qu'elles commandent. On note que les inverses des signaux b<sub>1</sub> et b<sub>2</sub>, nécessaires pour commander, au moins en partie, les portes 29, 30 et 31, sont obtenus à l'aide de deux inverseurs, respectivement 26 et 27.

Similairement, dans l'état II, c'est la porte ET INVERSE 29 qui agit pour rendre passante la porte de transmission 35, en partie à l'aide d'un inverseur 34, alors que les trois autres portes de transmission restent non passantes, de sorte que c'est le signal c2 du circuit 2 qui est transmis au circuit de comparaison 3. Dans l'état III, la porte ET INVERSE 31 commande l'ouverture de la porte de transmission 37, partiellement à l'aide d'un inverseur 36, et c'est le signal c3 du circuit 2 qui est transmis sur le circuit de comparaison 3, enfin, dans l'état IV, seule la porte de transmission 39 est rendue passante, en partie à l'aide d'un inverseur 38, par la porte ET INVERSE 31, les trois autres portes 28, 29 et 30 étant bloquées et fournissant à leur sortie un niveau «1» qui maintient non passantes les trois portes de transmission 33, 35 et 37. Dans ce dernier cas, c'est le signal c4 du circuit 2 qui est transféré à l'entrée du circuit de comparaison 3.

En vue de réaliser l'ajustement voulu à l'intérieur du circuit intégré, selon l'invention, le circuit de commande et de mémorisation 25 compris dans le circuit de commande de sélection 4 est constitué d'éléments de mémoire non volatile, par exemple de la manière illustrée par les figs 5a, 5b et 5c.

A la fig. 5a, qui représente le schéma du circuit 25, les transistors à effet de champ 76, 77, 81 et 82 sont des transistors FAMOS (field accelerat. MOS). Les électrodes de commande des éléments FAMOS n'ont pas d'injection d'électrons (ou le cas échéant de «trous» dans le cas des circuits à éléments FAMOS de polarité inverse), tant qu'ils n'ont pas reçu une ionisation particulière de mise en mémoire, et par conséquent, les points a1 et a2 présentent le niveau «0», amené par l'intermédiaire des transistors 79 et 84, respectivement, lorsque l'entrée de lecture Vc est au niveau haut, c'està-dire durant les impulsions du signal  $\Phi_3$ , puisque l'inverse de celui-ci  $\overline{\Phi}_3$  est appliqué à l'entrée du circuit 25, c'est-àdire sur la connexion Vc du circuit de la fig. 5a. Les sorties b<sub>1</sub> et b<sub>2</sub>, alimentées respectivement par l'intermédiaire de deux inverseurs 80, 85, présentent à ce moment-là deux niveaux «1», ce dont résultera, dans le circuit 4, fig. 2, la sélection de la sortie  $c_1$ ,  $Vd = Vc_1$ , correspondant à  $b_1$ ,  $b_2 = 1$ , 1. En dehors des impulsions, lorsque  $\Phi_3$  est au niveau haut et  $\overline{\Phi}_3$  au niveau bas, les transistors PT 78 et 83 sont rendus passants tandis que les transistors NT 79 et 84 sont bloqués, et aucun courant ne traverse les circuits représentés à la fig. 5a. Dans ce cas, les sorties b<sub>1</sub>, b<sub>2</sub> sont au niveau bas, mais cela ne tire pas à conséquence puisque les circuits 1, 2, 3 et 4 ne sont pas en fonction à ce moment-là. Les sorties du circuit 25 n'ont en fait de signification que durant les impulsions de niveau bas du signal  $\Phi_3$  (niveau haut pour son inverse  $\overline{\Phi}_3$ ).

On va voir maintenant comment ce circuit 25 établit les états I à IV précédemment mentionnés. Pour l'état I, on a b<sub>1</sub>, 65 talement soumis à l'injection.  $b_2 = 1$ , 1, c'est-à-dire  $a_1$ ,  $a_2 = 0$ , 0, ce qui est le cas lorsque la paire de transistors à électrode de commande commune 76, 77, et la paire de transistors à électrode de commande

commune 81, 82, sont non passants, c'est-à-dire sont exempts d'injection d'électrons sur leurs électrodes de commande. Pour établir l'état II,  $a_2$  doit être égal à 1 ( $b_2 = 0$ ) ce qui fait que les électrodes de commande des FAMOS 81 et 5 82 sont soumises à une injection d'électrons. Pour l'état III, a<sub>2</sub> doit redevenir zéro, tandis que a<sub>1</sub> doit avoir le niveau «1», et dans ce cas, des électrons sont à injecter dans l'électrode de commande des FAMOS 76 et 77. Enfin, pour l'état IV, a<sub>1</sub> et a<sub>2</sub> doivent avoir des niveaux 1, 1, pour fournir des niveaux tes un niveau «1» à leur sortie, et qu'elles laissent à l'état blo- 10 «0», «0» sur les sorties b<sub>1</sub> et b<sub>2</sub>, respectivement. Dans ce cas, tous les FAMOS, 76, 77, 81, 82 ont leur électrode de commande soumise à une injection d'électrons.

La fig. 5b montre la composition d'un FAMOS. Celui-ci comprend un substrat de silicium N<sup>-</sup> 55, des couches de 15 type P 57 et 58 pour constituer la source et le drain d'un transistor de type P, et des couches 87, 88 de type P pour former la source et le drain du transistor FAMOS. On a encore des couches 62 servant d'isolation et de contact avec le substrat, les films d'isolation de propreté d'électrode de comman-20 de 89, des films d'isolation supérieure 64 et des couches ou matières conductrices, par exemple d'aluminium, 65, pour le câblage des électrodes de commande, des sources, des drains, et du substrat. En 90, on a l'électrode de commande du transistor FAMOS, qui est flottante, conformément au mode de 25 fonctionnement de ce genre spécial de transistors à effet de champ. Ces électrodes de commande flottantes 90 sont composées de silicium polycristallin avec un dopage P ou un dopage N, ou encore sans dopage.

L'injection d'électrons dans les électrodes de commande 30 des FAMOS est produite en faisant agir un potentiel «d'avalanche» entre le substrat 55 (portions 62, 86) et l'îlot de drain 88, c'est-à-dire en provoquant une couche de déplétion (ligne en traits pointillés sur la figure) entre le substrat et le drain du FAMOS servant à l'enregistrement, l'injonction d'élec-35 trons se produisant alors dans les électrodes de commande par accélération du champ (comme cela est montré par des flèches à la fig. 5b). C'est la raison pour laquelle l'espace 92 entre l'isolation 86 et le drain 88 du FAMOS servant à l'écriture doit être plus large que l'espace 91 entre le drain 58 du 40 FAMOS servant à la lecture (mais qui est un transistor MOS ordinaire, à part le fait que son électrode de commande n'a pas de connexion extérieure), de façon que la tension d'avalanche sur la jonction PN entre le drain et le substrat du FA-MOS servant à l'écriture ne soit pas gênée par la tension de 45 claquage inverse de la jonction PN entre le drain et son isolation. Naturellement, il est possible d'adapter la longueur de l'espace 91 à celle de l'espace 92. En ce qui concerne l'électrode de commande flottante 90, un silicium polycristallin pour câblage en couches multiples peut être employé, de 50 même que, à l'inverse, le silicium polycristallin destiné à constituer l'électrode de commande flottante peut également être employé pour former un câblage multicouches. Sur la fig. 5a, les FAMOS 77 et 82 sont les FAMOS d'écriture sujets à injection, et l'on remarque que l'impédance des transis-55 tors MOS 79 et 84 doit être relativement élevée pour que, malgré la présence de ces derniers, le potentiel sur les points  $a_1$  et  $a_2$  puisse devenir élevé lorsque l'impulsion  $\Phi_3$  a lieu et que les transistors 79 et 84 sont passants. L'impédance de ceux-ci est naturellement suffisamment basse, et peut l'être 60 même si les transistors 77 et 82 ont les mêmes dimensions (même largeur de canal, même longueur de canal, même épaisseur de film isolant de l'électrode de commande) que les transistors 79 et 84, cette égalité étant toutefois seulement admissible pour autant que les transistors 77 et 82 soient to-

La fig. 5c représente en plan la configuration d'une partie de circuit intégré comprenant un élement FAMOS, en correspondance avec ce que la fig. 5b montre en coupe. Les conventions de représentation sont les mêmes à la fig. 5c qu'à la fig. 5b, c'est-à-dire que les hachures obliques représentent une couche de type N servant d'isolation et de contact avec le substrat, les parties restées en blanc représentent une couche de type P ou le substrat, la portion hachurée de façon représentant l'électrode de commande de l'élément FAMOS, faite par exemple de silicium polycristallin, tandis que les portions ombrées de points représentent les couches métalliques pour les connexions des électrodes de commande, sources, drains et substrats, ces couches métalliques étant par exemple de l'aluminium. Sur la fig. 5c, les endroits marqués d'un rectangle avec ses deux diagonales sont les endroits de contact entre la couche métallique et les couches de type P ou N. Dans le FAMOS 76 destiné à l'écriture, l'espace 92 entre le drain et l'isolation est établi d'une façon plus large que 15 (potentiel de masse), et si Vdo est plus petit que Vdo', ce nil'espace 91 entre le drain et l'isolation dans le FAMOS 78 servant à la lecture, en fait un transistor MOS ordinaire.

L'utilisation d'un élément de mémorisation non volatile tel qu'un élément FAMOS ou un composant équivalent dont le circuit de régulation en question présente des avantages du 20 tion de Vd soit faite à la valeur désirée de Vdo'. point de vue du procédé de fabrication, et ceci constitue un cinquième caractère qui distingue le circuit de détection de tension constituant une forme d'exécution de la présente invention, cet avantage se concrétisant dans le fait que l'ajustement peut être fait de façon directe à l'aide d'un testeur lorsque l'on teste le circuit intégré sous forme de plaquette (non encore enrobée), ce qui évite la nécessité d'un autre ajustement à effectuer encore sur ce circuit intégré, par exemple à l'état monté.

On va considérer maintenant le circuit de comparaison 3. 30 Celui-ci se compose d'un comparateur 40 qui entre effectivement en action lorsque le signal  $\Phi_3$  est au niveau bas, c'est-àdire durant les impulsions d'échantillonnage. Ce comparateur 40 est formé d'un amplificateur différentiel (amplificateur opérationnel) tel que celui qui est montré à la fig. 3a. Il compare les niveaux de tension présents sur une entrée inversée  $\hat{V}_I$  et sur une entrée non inversée  $V_{NI}$ . Dans le cas où  $V_I$ est plus grand que V<sub>NI</sub>, le niveau de sortie du comparateur Vo est au niveau bas (0), et dans le cas où V<sub>I</sub> est plus petit que V<sub>NI</sub>, la sortie Vo est au niveau haut (1).

La puissance de résolution du comparateur est déterminée par le gain en boucle ouverte de l'amplificateur tel qu'il est représenté à la fig. 3a. Comme ce gain est typiquement de l'ordre de 70 dB à 80 dB, des tensions présentant de très faibles différences, de l'ordre de 1/3000 à 1/10000 de la tension d'alimentation peuvent être comparées. Il n'y a pas de problème au sujet d'une éventuelle oscillation du comparateur et les capacités C1, C2 peuvent être faibles. Cela signifie que la construction des électrodes de commande correspondra à ce que l'on voit en 59 sur la fig. 4a plutôt qu'à ce que l'on voit en 52 sur la fig. 3b. Le rapport des cœfficients de conductance des transistors 45 et 50 peut également être d'un degré similaire. Le gain en boucle ouverte de l'amplificateur différentiel (amplificateur opérationnel) de la fig. 3a peut être plus élevé si la longueur du canal des transistors respectifs constituant les étages d'amplification est plus grande, ou si la concentration du substrat est plus élevée, ou encore si l'épaisseur du film d'électrode de commande est plus faible. Le principe appliqué dans la construction du circuit intégré pour obtenir un gain élevé est que la longueur de canal des transistors respectifs constituant l'amplificateur doit être grande. La longueur du canal des transistors pour l'amplificateur se distingue en ce qu'elle est plus grande que celle des transistors autres que ceux qui servent à l'amplificateur, même dans le circuit détecteur de tensions ou pour les transistors dans d'autres circuits intégrés ou d'autres parties de circuit intégré que le circuit de détection de tension dans l'appareil électronique équipé de cet amplificateur.

Dans la forme d'exécution décrite, la comparaison de tension a lieu entre la tension  $V_I = Vd$  et  $V_{NI} = Vst$ . Lorsque le circuit de commande de réglage 4 est dans l'état I,

$$Vd = \frac{r_1}{R+r}Vd_o$$

,  $Vst = \frac{R_2}{R_1+R_2}Vst_o$

On peut définir une tension Vdo' correspondant à une valeur corrigée de la tension de détection, pour tenir compte du fait que l'on compare des fractions des deux tensions. On a

10

$$Vd_{o'} = \frac{R_2}{R_1 + R_2} \times \frac{R + r}{r_1} Vst_o,$$

et cette valeur de Vdo' constitue une limite. Si Vdo est plus grand que Vdo', le niveau de sortie du comparateur sera bas veau sera élevé (V<sub>DD</sub>).

Inversement, les rapports  $R_2/R_1$ , ri/R+r (i=1, 2, ...), de même que la valeur Vsto (valant en bonne approximation, VTP-VGTP), devront être établis de façon telle que la détec-

Le sixième caractère qui distingue le circuit de détection de tension constituant une forme d'exécution particulièrement avantageuse de la présente invention consiste du reste en ce que la comparaison entre la tension de référence et la 25 tension convertie basée sur la tension détectée est réalisée à l'aide d'un comparateur, c'est-à-dire d'un amplificateur différentiel.

Enfin, le circuit 6 de conservation de l'information de sortie est constitué d'un flip-flop-verrou de type D, 41, dont le schéma est représenté à la fig. 6. Il s'agit d'un circuit mémorisateur dans lequel est mémorisée la tension de sortie Vcomp du comparateur 40, l'inscription se faisant lorsque  $\Phi_3$  est au niveau bas et le maintien de l'information continuant durant les périodes où Φ3 est au niveau haut. Vcomp 35 est de plus amplifié, pour fournir le signal de sortie Vh du circuit détecteur de tension, par les amplificateurs inverseurs du circuit de maintien, par exemple les transistors 96 et 97, ou 102 et 103 (fig. 6). On voit que c'est l'impulsion  $\Phi_3$ , qui fait fonctionner les circuits 1, 2, 3, 4 pour la détection de la 40 tension, qui constitue également l'impulsion cadencée (impulsion d'horloge) pour l'inscription de l'information dans le circuit de maintien 6. En fait, si le signal de sortie du circuit de maintien est requis d'une façon permanente, la caractéristique dynamique des circuits respectifs qui intervient lorsque 45 l'impulsion  $\Phi_3$  passe du niveau haut au niveau bas, c'està-dire les conditions du phénomène transitoire de saut, peuvent causer des perturbations. Dans ce cas, par exemple, un temps de retard to peut être pris en considération pour assurer que tous les circuits 1, 2, 3, 4 servant à la détection de 50 tension ont repris un état statique uniforme au moment où le circuit de maintien teste la sortie de l'amplificateur pour une nouvelle prise de l'information de sortie à mémoriser. Dans ce cas, ce temps de retard the est soustrait au début de l'impulsion  $\Phi_3$ , de façon que le circuit de maintien soit comman-55 dé par une impulsion  $\Phi_5$ , telle que montrée à la fig. 7c. L'impulsion  $\Phi_5$ , qui est une impulsion correspondant à l'impulsion  $\Phi_3$ , dont est soustrait, au début, un temps  $\tau$ b supérieur au temps nécessaire pour que tous les circuits aient assurément repris une situation statique, est obtenue en sous- $_{60}$  trayant au début de l'impulsion  $\Phi_{3}$  une demi-période du signal cadencé  $\Phi_4$ , également montrée à la fig. 7c. Cette soustraction d'impulsion est réalisée dans un circuit représenté à

VERSE 105. Par ailleurs, les phénomènes transitoires qui se produisent dans les circuits de l'agencement détecteur de tension et le circuit de maintien lorsque l'impulsion  $\Phi_3$  passe du niveau bas au niveau haut, c'est-à-dire à la fin de cette impulsion,

la fig. 7b, à l'aide d'un flip-flop 104 et d'une porte OU IN-

11 639 810 G

peuvent également provoquer quelques perturbations. Dans ce cas, le circuit de maintien sera commandé par une impulsion  $\Phi_6$  qui correspond à l'impulsion  $\Phi_5$  précédemment considérée, raccourcie à la fin d'un temps  $\tau a$  (ayant la durée d'une impulsion cadencée  $\Phi_4$ ). Ce signal impulsionnel  $\Phi_6$  est également représenté à la fig. 7c et il peut être obtenu en utilisant le circuit représenté à la fig. 7b, à l'aide d'un second flip-flop 106, d'une porte ET INVERSE 107, et d'un inverseur 108. Le circuit représenté à la fig. 7b est disposé dans le circuit générateur d'impulsions 5 de la fig. 2.

Bien que dans la forme d'exécution représentée à la fig. 2, l'ajustement soit effectué dans le circuit 2, cet ajustement pourrait également être fait dans le circuit 1. Il serait tout aussi possible d'ajuster Vst, par exemple en prévoyant les résistances 17 et 18 en lieu et place des résistances 20, 21, 22, 23 et 24 à la sortie de l'amplificateur 19, en fixant ainsi la valeur Vd à

$$Vd = \frac{R_2}{R_1 + R_2} Vd_o,$$

en même temps que, inversement les résistances 20, 21, 22, 23 et 24 seraient connectées en lieu et place des résistances 17 et 18, à la sortie de l'amplificateur 16 dans le circuit de tension de référence 1. A ce moment-là, la sélection à l'aide du circuit de commande de réglage 4 se ferait sur des fractions de la tension de référence et non pas sur des fractions de la tension de détection.

De toute façon, comme on l'a mentionné, le circuit intégré objet de l'invention se distingue par le fait que les ajustements sont effectués à l'intérieur du circuit intégré, d'une façon simple, avant son montage, en utilisant des éléments de mémoire non volatile en tant que moyens pratiques de réaliser ces ajustements.

Par ailleurs, les moyens pour ajuster le circuit intégré selon la présente invention peuvent permettre un ajustement automatique du circuit intégré.

En dépendance du degré d'exactitude avec lequel les réglages doivent être effectués, c'est-à-dire, dans le cas d'un circuit de détection de tension en dépendance de l'exactitude que doivent avoir les niveaux de tension pré-établis, il est également possible, naturellement, de ne pas prévoir d'ajustement. Dans ce cas, le circuit de la fig. 2 serait modifié par la suppression du circuit 4, une résistance fixe étant alors branchée sur la sortie de l'amplificateur 9 pour fournir une tension de sortie Vd représentant une fraction fixe de la tension détectée Vd<sub>0</sub>. Il suffit pour en arriver à cette forme d'exécution de rendre r<sub>2</sub>, r<sub>3</sub> et r<sub>4</sub> égaux à zéro, la fraction fournissant de façon appropriée la tension de sortie c<sub>1</sub>, ap-liquée directement, en tant que tension Vd sur l'entrée inversée du comparateur 40.

Comme on l'a mentionné, le circuit intégré équipé d'un circuit de détection de tension conforme à l'invention est caractérisé aussi par la cœxistence dans le circuit intégré d'autres circuits réalisant d'autres fonctions dans l'appareil électronique en question, l'intégration de tous les composants, du circuit détecteur de tension et des autres circuits, étant aisément réalisable.

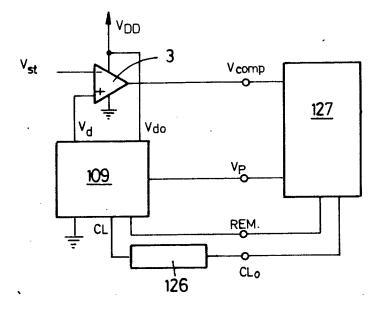

Le circuit intégré pour la détection de tension selon l'invention peut également permettre un système d'ajustage automatique des tensions établies comme niveau de détection. Ceci est illustré à la fig. 8 qui représente le schéma d'un circuit 109 comprenant à cet effet des éléments de mémoire non volatile 110–114, 115–119 (qui en l'occurrence sont constitués par des éléments FAMOS). Ce circuit comprend également des transistors de commande 120–124 pour commander la mise des éléments FAMOS à l'état passant ou à l'état bloqué, et il comprend encore un registre de décalage 125 qui permet de commander tour à tour chacun des élé-

ments FAMOS à l'aide d'une seule entrée, l'avancement pas à pas de ce registre à décalage 125 étant commandé par des impulsions d'horloge appliquées sur une entrée Cl de ce registre. Une connexion Vd du circuit est destinée à être connectée à l'entrée d'un comparateur, cette connexion subissant des variations de tension au fur et à mesure que des résistances r<sub>2</sub> - r<sub>n</sub> sont successivement court-circuitées après que l'élément FAMOS correspondant a été mis à l'état passant. Les éléments FAMOS sont, comme on l'a déjà vu, 10 d'une construction à électrode de commande double (une seule électrode de commande flottante pour deux éléments FAMOS appariés), et les éléments FAMOS forment donc des paires, par exemple 110 et 115, 111 et 116, etc. Une connexion Vp sert d'entrée d'enregistrement pour l'injection de charge dans les éléments FAMOS et des impulsions lui sont appliquées avec approximativement des tensions de 30 à 50.