(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4707295号

(P4707295)

(45) 発行日 平成23年6月22日(2011.6.22)

(24) 登録日 平成23年3月25日(2011.3.25)

(51) Int.Cl.

G 11 C 13/00 (2006.01)

F 1

G 11 C 13/00

Z

請求項の数 18 (全 14 頁)

(21) 出願番号 特願2001-543738 (P2001-543738)

(86) (22) 出願日 平成12年7月10日 (2000.7.10)

(65) 公表番号 特表2003-516602 (P2003-516602A)

(43) 公表日 平成15年5月13日 (2003.5.13)

(86) 國際出願番号 PCT/US2000/018805

(87) 國際公開番号 WO2001/043138

(87) 國際公開日 平成13年6月14日 (2001.6.14)

審査請求日 平成19年7月10日 (2007.7.10)

(31) 優先権主張番号 09/459,246

(32) 優先日 平成11年12月10日 (1999.12.10)

(33) 優先権主張国 米国(US)

(73) 特許権者 592130699

ザ リージェンツ オブ ザ ユニバーシティ オブ カリフォルニア

The Regents of The University of California

アメリカ合衆国 カリフォルニア州 94607 オークランド フランクリン ストリート 1111 トゥエルフス フロア

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100076691

弁理士 増井 忠式

最終頁に続く

(54) 【発明の名称】電気的アドレス可能な揮発性および不揮発性分子系スイッチング・デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

第1端子と、

第2端子と、

前記第1および第2端子の間に挿持された、[2]カテナン分子の単分子層と、

を備え、

前記単分子層が膜形成混合物から形成され、該膜形成混合物が、電気的に中立となるよう十分な量の対イオンを[2]カテナン分子とともに含む、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 2】

請求項1記載のデバイスにおいて、前記スイッチング・デバイスが揮発性分子スイッチング・デバイスである、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 3】

請求項2記載のデバイスにおいて、メモリ・セル、ルーティング回路、反転器、またはフィールド・プログラマブル・デバイス・アレイに含まれる、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 4】

請求項3記載のデバイスにおいて、前記メモリ・セル、ルーティング回路、反転器またはフィールド・プログラマブル・デバイス・アレイがダイオード挙動を示す、ソリッド・ステート分子スイッチング・デバイス。

10

20

## 【請求項 5】

請求項 1 記載のデバイスにおいて、前記スイッチング・デバイスが不揮発性分子スイッチング・デバイスである、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 6】

請求項 5 記載のデバイスにおいて、メモリ・セル、ルーティング回路、反転器、またはフィールド・プログラマブル・デバイス・アレイに含まれる、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 7】

請求項 6 記載のデバイスにおいて、前記メモリ・セル、ルーティング回路、反転器またはフィールド・プログラマブル・デバイス・アレイがダイオード挙動を示す、ソリッド・ステート分子スイッチング・デバイス。 10

## 【請求項 8】

請求項 1 記載のデバイスにおいて、前記 [ 2 ] カテナンが  $C_{70}H_{76}F_{24}N_4O_{10}P_4S_4$  である、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 9】

ソリッド・ステート分子スイッチング・デバイスの製造方法であって、2つの端子間に挟持された [ 2 ] カテナン分子の単分子層を形成するステップを備え、該単分子層形成ステップが、十分な量の対イオンを [ 2 ] カテナン分子と混合し、電気的に中立であり、前記 [ 2 ] カテナン分子の単分子層を形成する際に使用するのに適した膜形成混合物を得るステップを含む、製造方法。 20

## 【請求項 10】

請求項 9 記載の製造方法において、前記 [ 2 ] カテナンが  $C_{70}H_{76}F_{24}N_4O_{10}P_4S_4$  である、製造方法。

## 【請求項 11】

請求項 9 記載の製造方法において、前記対イオンを、両親媒性硫酸塩陰イオン、両親媒性カルボキシレート、および両親媒性ホスホリピド陰イオンから成るグループから選択する、製造方法。

## 【請求項 12】

請求項 9 記載の製造方法において、前記対イオンを、両親媒性硫酸塩陰イオン、両親媒性カルボキシレート、および両親媒性ホスホリピド陰イオンから成るグループから選択する、製造方法。 30

## 【請求項 13】

請求項 10 記載の製造方法において、前記対イオンが  $PF_6^-$  である、製造方法。

## 【請求項 14】

第 1 端子と、第 2 端子と、前記第 1 および第 2 端子間に挟持した [ 2 ] カテナン分子層とを備え、前記 [ 2 ] カテナン分子層を、請求項 9 の方法にしたがって製造した、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 15】

請求項 14 記載のデバイスにおいて、前記スイッチング・デバイスが揮発性分子スイッチング・デバイスである、ソリッド・ステート分子スイッチング・デバイス。 40

## 【請求項 16】

・ 請求項 15 記載のデバイスにおいて、メモリ・セル、ルーティング回路、反転器、またはフィールド・プログラマブル・デバイス・アレイに含まれる、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 17】

請求項 14 記載のデバイスにおいて、前記スイッチング・デバイスが不揮発性分子スイッチング・デバイスである、ソリッド・ステート分子スイッチング・デバイス。

## 【請求項 18】

請求項 17 記載のデバイスにおいて、メモリ・セル、ルーティング回路、反転器、またはフィールド・プログラマブル・デバイス・アレイに含まれる、ソリッド・ステート分子 50

スイッチング・デバイス。

【発明の詳細な説明】

【0001】

本発明は、米国陸軍によって裁定された契約第DABT63-99-3-0003号の下で政府支援によって行われた。

【0002】

(発明の背景)

1. 発明の分野

本発明は、一般的に、メモリ即ちデータ・ストレージ用に設計した電子デバイスに関する。また、これは、一般的に、電子信号のスイッチングおよびルーティング用に設計した電子デバイスにも関する。また、本発明は、一般的に、限界寸法をナノメートル単位で測定する電子デバイスに関し、更に特定すれば、構築ブロックとして用いより複雑な構造を形成する単純なデバイス、およびこのようなデバイスの形成方法に関する。

10

【0003】

2. 発明の分野

ランダム・アクセス・メモリ(RAM)は、電子ハードウェアの構成素子として増え重要なとなりつつあり、その用途は、2つだけあげるとすれば、スマート・クレジット・カードからコンピュータのストレージにまで及ぶ。ダイナミック・ランダム・アクセス・メモリ(DRAM)は、シリコン製造技術を基本としており、破壊的読み取りを特徴とする揮発性メモリである。これが意味するのは、メモリに常時電圧を供給する必要があり、さもないと情報が消えてしまうということである。更に、各メモリ・エレメントにはトランジスタが付随する。これが意味するのは、このようなメモリ・デバイスは、現世代のリソグラフィ技術によって可能である以上の密度では、製造できないということである。最後に、DRAMビットの状態を読み取ると、そのビットにおける情報を破壊してしまう。

20

【0004】

最近になって、強磁性体RAMと呼ばれるデバイス、即ち、Fe-RAMが多数の国によって開発された。Fe-RAMデバイスは、不揮発性メモリ・ビットであり、クロス・ポイント・メモリ・アレイ(米国特許第5,640,343号参照)として知られているものに組み込むことができる。このようなアレイの利点は、個々のFe-RAMデバイスがメモリ・ビット毎にトランジスタを必要とせず、代わりにn個のメモリ・ビットに対して $n^{1/2}$ 個程度のトランジスタがあればよいことである。しかしながら、Fe-RAMは、DRAMと同様に、破壊的読み取りを特徴とする。Fe-RAMデバイスは、電界を用いて強磁性体の磁気モーメントを変化させるとする原理に基づいている。ある物質では、この磁気モーメントを変化させると、強磁性体の電気抵抗にも小さな変化が生じる。微小ドメインでは、このスイッチング挙動はもはや作用しない。何故なら、物質のサイズが非常に小さくなると(即ち、30ナノメートル未満)、強磁性体はその強磁性特性を維持できないからである。最後に、Fe-RAMメモリ・エレメントにおける「1」および「0」状態間の差は、15%の抵抗変化である。これが意味するのは、比較的小さいFe-RAMのクロス・ポイント・メモリ・アレイ(1メガバイト未満)が構築可能であるということである。また、これは、Fe-RAMデバイスがメモリ・ビットとしてしか機能できないことも意味する。これらは真のスイッチとして機能することができない。

30

【0005】

最近になって、2つのクロス・ワイヤで構成され、その間に電気的にアドレス可能な分子種を挟持した電子デバイスが開発された。これらのデバイスは、製作が簡単で安価である。また、これらのデバイスは、非常に小さく作ることができ、その寸法は数ミクロンから数ナノメートル程度である。これらのデバイスは、クロスバー・スイッチ・アレイ、論理デバイス、メモリ・デバイス、ならびに通信および信号ルーティング・デバイスを生産するために用いることができる。クロス・ワイヤまたはクロスバー・デバイスは、以下の公開国際特許出願において開示されている。

40

【0006】

50

"Chemically Synthesized and Assembled Electronic Devices" ( 化学的に合成し組み立てた電子デバイス ) と題する米国特許出願第\_\_\_\_\_号に基づく PCT 番号\_\_\_\_\_ [PD-10981971-1] 、

"Molecular Wire Crossbar Interconnects for Signal Routing and Communications" ( 信号ルーティングおよび通信のための分子ワイヤ・クロスバー相互接続 ) と題する、米国特許出願第\_\_\_\_\_号に基づく PCT 番号\_\_\_\_\_ [PD-10981966-1] 、

"Molecular Wire Crossbar Memory" ( 分子ワイヤ・クロスバー・メモリ ) と題する、米国特許出願第\_\_\_\_\_号に基づく PCT 番号\_\_\_\_\_ [PD-10981968-1] 、 "Molecular Wire Crossbar Logic" ( 分子ワイヤ・クロスバー・ロジック ) と題する米国特許出願第\_\_\_\_\_号に基づく PCT 番号\_\_\_\_\_ [PD-10981969-1] 、 "Demultiplexer for a Molecular Wire Crossbar Network" ( 分子ワイヤ・クロスバー・ネットワーク用デマルチプレクサ ) と題する、米国特許出願第\_\_\_\_\_号に基づく PCT 番号\_\_\_\_\_ 10 、および

"Molecular Wire Transistors" ( 分子ワイヤ・トランジスタ ) と題する米国特許出願第\_\_\_\_\_号に基づく PCT 番号\_\_\_\_\_ [PD-10981967-1] 。

ここに列挙した公開の内容は、この言及により本願にも含まれるものとする。

( 発明の摘要 )

本発明によれば、ある [ 2 ] カテナンを用いて、ソリッド・ステート分子クロスバー・スイッチング・デバイスの作成に使用するのに特に適した薄膜を形成できることを発見した。 [ 2 ] カテナンを基本としたスイッチング・デバイスは、揮発性または不揮発性とすることができる、非破壊的読み出しを特徴とする。これらは、「 0 」および「 1 」状態間で大きな抵抗差を呈し、非常に小さな長さスケールでは消失するバルク物理現象 (bulk physical phenomena) を基本としない。 [ 2 ] カテナンを双安定電気的アドレス可能分子として採用し、クロス・ワイヤ間に挟持したデバイスは、メモリ・ビットまたはスイッチとして用いることができ、非常に小さい寸法でも動作し続ける。このようなデバイスは、先に引用した PCT 公開に記載されている様々な種類のデバイス全てを含む。

【 0 0 0 7 】

本発明は、ソリッド・ステート分子スイッチング・デバイスを対象とし、このスイッチング・デバイスは第 1 および第 2 端子を形成するクロス・ワイヤを含み、その間に [ 2 ] カテナン分子を挟持する。スイッチング・デバイスは、メモリ・セル、ルーティング回路、反転器または現場プログラム可能デバイスにおいて用いることができ、ダイオード挙動を呈することも、呈しないことも可能である。また、本発明は、膜形成混合物に対イオンを用いて、 [ 2 ] カテナン分子の 単分子層 を形成することを含む、デバイスの製造方法に関する。

【 0 0 0 8 】

本発明の前述のおよびその他の多くの特徴ならびに付随する利点は、以下の詳細な説明を添付図面と関連付けて参考することにより、より良く理解されよう。

【 0 0 0 9 】

( 発明の詳細な説明 )

定義

Mol-RAM は、ここで用いる場合、メモリ・セルの分子スイッチ系アレイを意味することとする。

【 0 0 1 0 】

メモリ・ビットは、ここで用いる場合、電気的にデバイスを調べることによって互いに区別することができる 2 つの状態 ( 「 0 」 または 「 1 」 ) で存在可能な物理デバイスを意味することとする。

【 0 0 1 1 】

スイッチは、ここで用いる場合、「開放」および「閉鎖」といような 2 つの状態間で切り換えることができ、2 つの状態間の差を電子的に調べることができる物理デバイスを意味することとする。スイッチの 2 つの状態間の差は、メモリ・ビットに対するよりも大きいのが通例である。例えば、スイッチの状態を判定するために測定する電気的特性がデバイ

10

20

30

30

40

50

スの抵抗である場合、メモリ・ビットは20%の抵抗変化によって特徴付けることができ、一方スイッチは200%の抵抗変化によって特徴付けることができる。スイッチはメモリ・ビットとして用いることができるが、メモリ・ビットは必ずしもスイッチとして有用ではない場合もある。

【0012】

自己組織化(self-assembled)は、ここで用いる場合、系の構成材料の同一性のために、ある幾何学的パターンを自然に採用する系を意味する。この系は、この構成を採用することによって、そのエネルギーにおいて少なくとも極小を達成する。

【0013】

単一構成可能は、ここで用いる場合、酸化または還元反応のように、非可逆的なプロセスによってスイッチがその状態を1回だけ変化できることを意味し、このようなスイッチは、例えば、プログラマブル・リード・オンリ・メモリ(PROM)の基礎となることができる。

10

【0014】

再構成可能は、ここで用いる場合、酸化または還元のように、可逆的なプロセスによってスイッチがその状態を多数回変化できることを意味する。言い換えると、スイッチは、ランダム・アクセス・メモリ(RAM)におけるメモリ・ビットのように多数回開閉することができる。

【0015】

酸化還元活性(redox active)は、ここで用いる場合、分子または分足接合を電子的に還元または酸化できることを意味し、分子または分子接合に電気的变化を追加したり、これらから除去できることを意味する。

20

【0016】

ミクロン・スケール寸法は、ここで用いる場合、サイズが1マイクロメートルないし数マイクロメートルの範囲にある寸法を意味する。

サブ・ミクロン・スケール寸法は、ここで用いる場合、1マイクロメートルから0.04マイクロメートルの範囲にある寸法を意味する。

【0017】

ナノメートル・スケール寸法は、ここで用いる場合、0.1ナノメートルから50ナノメートル(0.05マイクロメートル)の範囲にある寸法を意味する。

30

ミクロン・スケールおよびサブミクロン・スケール・ワイヤは、ここで用いる場合、1ないし10マイクロメートルの寸法を有する幅または直径、数十ナノメートルないし1マイクロメートルの範囲とすることができる高さ、および数マイクロメートル以上の長さを有する棒状または帯状導体を意味する。

【0018】

[2]カテナンは、ここで用いる場合、2つ以上の鎖交環から成り、その各々を別々の異なる分子として調合することができる、分子化合物を意味する。カテナンは、荷電することができ(これらは分子イオンであることを意味する)、この場合これらは逆電荷の対イオンと関連することが多い。

【0019】

好適な[2]カテナンは、 $[C_{70}H_{76}N_4O_{10}S_4]^{4+}$ である。[2]カテナンを製作する方法は公知である。例えば、M. Asakawa, P.R. Ashton, V. Balzani, A. Credi, C. Hamers, G. Mattersteig, M. Montalti, A. N. Shipway, N. Spencer, J.F. Stoddart, M.S. Tolley, M. Venturi, A.J.P. Whilte, およびD.J. Williams, "A chemically and electrochemically switchable [2] Catenane incorporating a tetrathiafulvalene unit" (テトラチアフルバレンを組み込んだ化学的および電気化学的にスイッチ可能な[2]カテナン)(Angewandte Chemie International Edition in English, vol. 37, p.333 (1990))を参照のこと。

40

【0020】

ヒステリシスは、ここで用いる場合、順方向電圧の軌跡(負から正への電圧)が、逆電圧

50

軌跡（正から負への電圧）とは異なる電流によって特徴付けられるような電流 - 電圧測定特性を意味する。 $V_{LH}$ は、ヒステリシス・ループの低電圧端を示し、 $V_{HH}$ は、電流ループの高電圧端を示す。 $V_{MH}$ は $V_{LH}$ および $V_{HH}$ 間のいずれかにある電圧値である。

#### 【0021】

揮発性は、ここで用いる場合、電位を印加しないと、格納されている情報を失うメモリ・セルを意味する。

不揮発性メモリは、ここで用いる場合、印加電位がなくても、格納されている情報を維持するメモリ・セルを意味する。

#### 【0022】

非破壊的読み取りは、ここで用いる場合、メモリ・ビットのステータスに影響を及ぼさず 10 に、セル内の情報を読み出すことができるようなメモリ・セルの動作を意味する。

#### 【0023】

メモリ・セルの分子スイッチ系アレイ (Mol - RAM) は、電気的にアドレス可能な分子スイッチのアレイであり、その各々は「1」または「0」を格納することができ、あるいは同様に「スイッチ閉鎖」状態または「スイッチ開放」状態にすることができる。各メモリ・セルは、トンネル接合 (TJ) エレメントであり、2つの導通ワイヤで構成され、その間に薄い分子層が挟持されている。種々の電極材料の使用によってデバイスにダイオードの挙動を組み入れ、一般滴な金属<sup>1</sup> - 絶縁体 - 金属<sup>2</sup> (M<sup>1</sup>IM<sup>2</sup>) ダイオードの変種を作成する。ここで、M<sup>1</sup>およびM<sup>2</sup>は異なる金属、または金属 - 絶縁体 - 半導体 (MIS) 20 ダイオードである。

#### 【0024】

前述のデバイスでは、絶縁体は分子層を含み、絶縁層の性質は、分子の電子的特性によって異なる。薄い分子層（例えば、1つの単分子層）は、荷電される酸化還元活性 [2] カテナン分子、およびそれらに対応する対イオンから成る。アレイ内の各メモリ・セルは、2本のワイヤのみで制御する。デバイスの動作は、分子接合の可逆酸化または還元に基づく。ある非常に特殊な分子接合の種類では、接合間に可変電圧を印加し、接合の電流または抵抗を測定することによって接合の応答を調べると、ヒステリシス・ループを測定することができる。

#### 【0025】

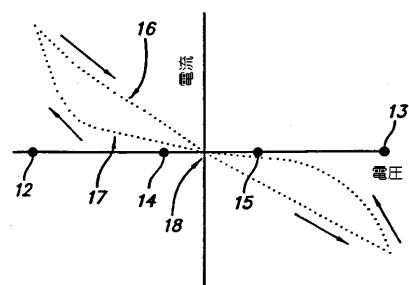

再構成可能なスイッチまたはメモリ・エレメントの基礎としてヒステリシス・ループを利用したデバイスの動作を図1に示す。低電圧(12)から高電圧(13)までデバイス間に可変電圧を印加すると、電流は1つの電圧依存経路(16)に追従することが認められる。しかしながら、高電圧(13)から低電圧(12)まで電圧を走査すると、電流は異なる電圧依存経路(17)を取ることが認められる。このように、2つの値(14および15)の間にある電圧をデバイスに印加すると、測定電流はデバイスの以前の履歴に依存する。図1における曲線では、ある低電圧(12)を印加することによって、高電流状態（「1」または「スイッチ閉鎖」状態）をデバイスに書き込むことができ、ある中間電圧(14および15の間)においてデバイスを読み取ることができる。ある高電圧(13)をデバイスに印加することにより、低電流状態（「0」または「スイッチ開放」状態）をデバイスに書き込むことができ、この状態も、ある中間電圧(14ないし15)において読み出すことができる。ヒステリシス・ループが0ボルト、0電流点(18)を交差すると、スイッチは「不揮発性」であると考えられる。範囲(14)ないし(15)以内のある電圧でデバイスの状態を調べてもデバイスの状態が変化しない場合、このステップは「非破壊的」読み取りと考えられる。 30 40

#### 【0026】

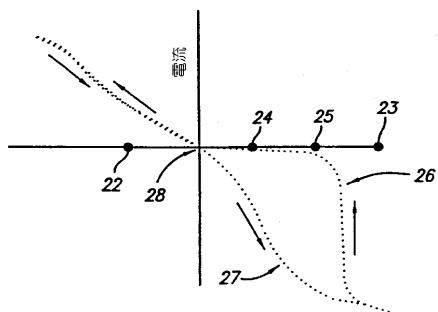

同様にメモリ・ストレージまたは再構成可能スイッチに有用な第2の種類のヒステリシス・ループを図2に示す。この場合、電流電圧軌跡ヒステリシス・ループは0ボルト、0電流点(28)からずれており、ヒステリシス・ループ(27、26)は、非ゼロ電圧を中心としている。しかしながら、デバイスの動作は同様である。デバイスに書き込むには、低(22)電圧または高(23)電圧のいずれかを印加する。前述の場合と同様、このデ 50

バイスの抵抗が低い場合、またはデバイスを流れる電流の大きさが大きい場合、デバイスは「1」即ち「閉鎖」状態にあると考えられる。逆に、デバイスの抵抗が大きい場合、またはデバイスを流れる電流の大きさが小さい場合、デバイスは「0」即ち「開放」状態にあると考えられる。範囲(24ないし25)以内の電圧で電流を監視することによってデバイスの状態を読み取る場合、この状態は以下のようにデバイスの履歴に依存する。以前に低電圧(22)でデバイスに書き込みを行っていた場合、ある中間電圧(24ないし25)において「高」状態が読み出される。ヒステリシス・ループ(23)の高電圧側の電圧でデバイスに書き込みを行った場合、ある中間電圧(24ないし25)において「低」状態が読み出される。

## 【0027】

10

ヒステリシス・ループ(16、17、26、27)は同様に見えるが、順および逆電圧走査の機能が図1および図2とは逆である、図1および図2の変形も可能である。ヒステリシス・ループ(26、27)が負電圧において現れる、図2の変形も可能である。

## 【0028】

図2に示すようなヒステリシス・ループを呈するデバイスは、電極材料を調節し、2つの電極間の化学ポテンシャル(フェルミ・エネルギーの差)が、「読み出し」ステップの電圧範囲(24ないし25)以内のある値に等しくなるようにすれば、不揮発性とすることができる。

## 【0029】

20

本発明の目的は、酸化還元活性分子から成る薄いソリッド・ステート電気化学セルにおいて、ヒステリシス電流-電圧曲線を生成することである。酸化還元活性である分子の殆どは、ヒステリシス電流電圧特性を呈さないので、ヒステリシスを分子内に「組み入れる」必要がある。1つの手法は、双安定分子を合成し、酸化/還元プロセスによって双方の状態にアクセス可能とし、エネルギー・バリアによって状態を分離することである。究極的に電流-電圧曲線にヒステリシスを与えるのは、このエネルギー・バリアである。分子が一旦酸化または還元してかなりの再編成を受けた場合、その再編成プロセスはエネルギーを必要とし、エネルギー・バリアの基礎を設けることができる。更に、デバイス製造プロセスは、分子または複数の分子への直接的な電気的アクセスを考慮しなければならない。最後に、分子形状の設計および/またはデバイス製造プロセスは、デバイス内部に十分な自由容積を確保し、分子が一旦酸化または還元したなら再編成できるように考慮しなければならない。

30

## 【0030】

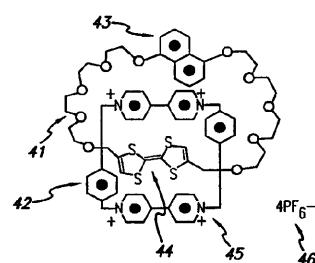

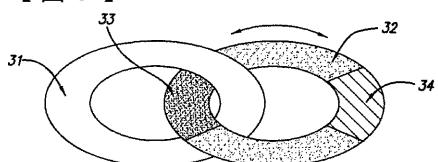

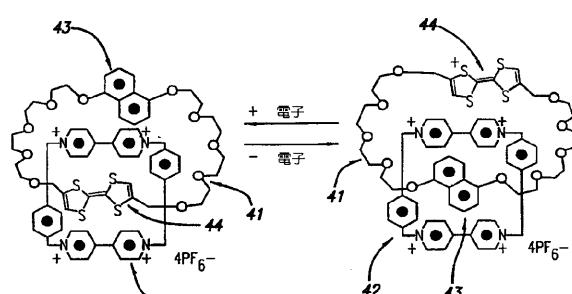

本発明によれば、前述の目的を達成するに当たり、[2]カテナンとして知られている一部類の分子を用いる。[2]カテナンをどのようにしてスイッチとして使用することができるかを、図3に概略的に示す。これは、[2]カテナンをシンボル化することを意図する。望ましければ、2つよりも多い環を有するカテナンを用いてもよい。しかしながら、[2]カテナンの使用が好ましい。このような[2]カテナンは、2つの鎖交環(31、32)から成る分子構造を有する。環の一方(32)は2つの化学部位(33、34)を有し、その各々は他方の環(31)に結合することができるので、カテナンは双安定となる。しかしながら、これらの結合部位(33、34)のどちらが実際に環(31)に結合するのかという問題は、酸化/還元プロセスによって判定することができる。例えば、環(32)上の部位(33)が環(31)に対して強い結合親和性を有するように、調合した分子を配向する。したがって、2つの環(31、33)は、図3に示すように、この相互作用を最大化するように配置する。電子を環(32)上の部位(33)から取り出すと、結合優位性(binding preference)が変化し、最も低いエネルギーの構成が環(31)内部に部位(34)を有するようにすることができる。2つの環(31、32)の一方は、この新たな構成に対応するために、回転しなければならない。この再編成は、分子スケールでは、比較的大きく、2つの幾何学的形状を分離するエネルギー・バリアの基礎を設けることができる。

40

## 【0031】

50

好適な [ 2 ] カテナン構造の一例を図 4 A に示す。この分子イオンの化学式は、 $[C_{70}H_{76}N_4O_{10}S_4]^{4+}$ である。分子は、 $P F_6^-$ のように典型的な対イオンを有する塩として調合するのが通例である。この場合、分子化合物の化学式は $C_{70}H_{76}F_{24}N_4O_{10}P_4S_4$ となる。この系は、2つのビピリジニウム単位 (45) を含む1つの環 (42) と、環の反対側にビフェニル (43) およびテトラチオルフルバレン (TTF : tetrathiofulvalene) (44) 構成材料を有する第2クラウン・エーテル環 (41) とから成る。これら2つの構成材料 (43、44) は、リンク (41) の2つの結合部位であり、これらは環 (42) 上のビピリジニウム単位 (45) に結合することができる。環 (42) は、正に荷電され、この場合複合体全体の電荷中立は、対イオンによって供給され、4つのヘキサフルオロホスフィン陰イオン ( $PF_6^-$ ) (46) である。

10

### 【0032】

この分子のスイッチング作用を図 4 B に示す。この分子を酸化させると、環 (41) 上の TT F 部位 (44) は正に荷電されていく。その結果、正に荷電した環 (42) と反発し、環 (41、42) の一方が回転して、環 (41) のビフェニル部位 (43) が環 (42) の内側となる。このリングの運動は、酸化還元化学に対するエネルギー・バリアを与える。このバリアは、カテナンの双安定性と結びついて、これらの分子化合物を組み込んだデバイスの電流電圧特性にヒステリシスが得られる。このスイッチング運動は、液相では既に実証されていたが、ソリッド・ステート・デバイスでは未だであった。(A. Masumi et al., "A Chemically and Electrochemically Switchable [2] Catenane Incorporating a Tetrathiafulvalene Unit," (テトラチアフルバレン単位を組み込んだ化学的および電気化学的にスイッチ可能な [2] カテナン) *Agnew Chem, Int. Ed.* 1998, 37, No. 3, pp. 333-337; V. Balzani et al., "The Switching of Pseudorotaxanes and Catenanes Incorporating a Tetrathiafulvalene Unit by Redox and Chemical Inputs" (酸化還元および化学入力による、テトラチアフルバレン単位を組み込んだ偽ロタキサンおよびカテナンのスイッチング) *Journal of Organic Chemistry* (印刷中) )。

20

### 【0033】

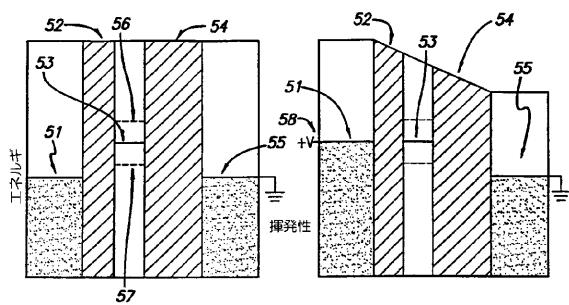

分子スイッチング・デバイスの揮発性または不揮発性メモリを提供する能力は、電極の性質によって異なる。図 5 (A) は、揮発性分子スイッチのエネルギー・レベル図の概略であり、一方図 5 (B) はスイッチング機構が分子の酸化に基づく不揮発性分子スイッチのエネルギー・レベル図である。揮発性メモリ (図 5 A) では、酸化分子 (53) のエネルギー・レベルは、ヒステリシス・ループの中央電圧にある。即ち、これは、スイッチの状態を読み取る電圧となる。ヒステリシス・ループの幅は、(56、57) によって決定される。これは、分子を再編成する際に必要な活性化エネルギーに関係がある。酸化分子 (53) のエネルギー・レベルは、分子のいずれの側でも、2つの電極 (51、55) の占有電子状態 (occupied electronic states) からエネルギー (トネリング) バリア (52、54) だけ離れている。

30

### 【0034】

ヒステリシス・ループ (56、57) のエネルギー範囲全体は、いずれの電極 (51、55) の電子状態よりも高いエネルギーにあるので、デバイスのヒステリシス・ループは、ある正の電圧を中心とする。したがって、ヒステリシス・ループにアクセスするには、正の電圧電圧バイアス (58) を電極 (51) に印加する。この電圧を除去すると、電極 (51) のエネルギー・レベルはヒステリシス・ループ (57) の最下位未満にまで低下し、スイッチの状態は失われる。電極 (51) を電圧 (58) に保持することによってのみ、スイッチを適当なレベルに保持することができる。したがって、メモリの状態は、バイアス (58) を除去すると、「蒸発」する。

40

### 【0035】

不揮発性分子スイッチのエネルギー・レベルを図 5 (B) に示す。この場合、2つの電極のエネルギー・レベルは同一ではない。何故なら、電極 (59) はここでは異なる物質で作られているからである。その結果、2つの電極 (59、55) 間の領域に静電界が発生し、ヒステリシス・ループ (56、57) はここでは電極 (59) のエネルギーを中心として対

50

称となる。したがって、正電圧を用いてヒステリシス・ループ(56)の高エネルギー側にアクセスし、負電圧を用いてヒステリシス・ループ(57)の低エネルギー側にアクセスする。電界を全く印加しない場合、メモリ・ビットの状態は不变であり、「蒸発」しない。

#### 【0036】

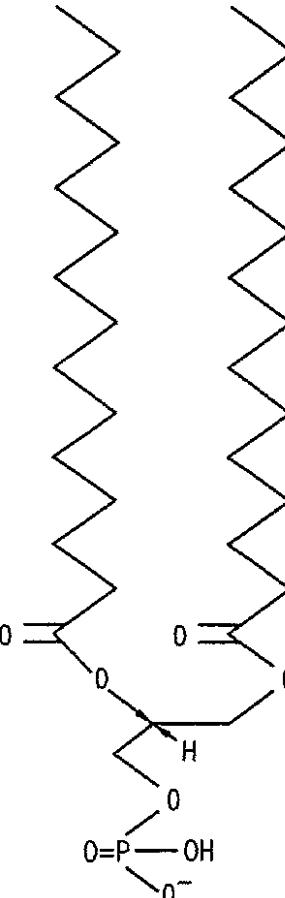

図4Aに示す[2]カテナンを、サンドイッチ構造に配した2端子デバイスに組み込むことによって、ソリッド・ステート双安定スイッチを作成した。[2]カテナンの薄膜を、水面上でラングミュア単分子層として調合し、ラングミュア・プロジェクト膜(Langmuir Blodgett film)として転写させた。[2]カテナンをラングミュア単分子層として調合するためには、これらの分子化合物を両親媒性にする必要があった。両親媒性は、空気/水界面において分子単分子層を形成する。[2]カテナンを両親媒性にするために、ヘキサフルオロホスフィン陰イオン(46)を、図6に示す炭化水素と置換した。このような置換カテナンは、高品質のラングミュア・プロジェクト膜を作ることが、以前から実証されていた。(C.L. Brown et al., "The Introduction of [2] Catenanes into Langmuir Films and Langmuir-Blodgett Multilayers - A Possible Strategy for Molecular Information Storage Materials" ([2]カテナンのラングミュア膜およびラングミュア・プロジェクト多層への導入 - 分子情報格納材料に可能な手法) Langmuir (印刷中))。

#### 【0037】

図6に示す対イオンは、好適な対イオンである。この場合に適した対イオンは、2つの要件を満たさなければならない。第1に、これらは[2]カテナンの電荷を調和し、電荷中立膜を調合できるようにしなければならない。第2に、これらは、カテナン/対イオンのラングミュア単分子層を形成することができるよう、両親媒性でなければならない。代替対イオンの具体例には、エイコサン酸( $\text{CH}_3(\text{CH}_2)_{18}\text{CO}_2^-$ )のような両親媒性カルボキシル陰イオン、( $\text{CH}_3(\text{CH}_2)_{n=8-20}\text{SO}_3^-$ )のような両親媒硫酸塩陰イオン、ここで用いるものに類似したその他の両親媒性ホスホリピド陰イオンが含まれるが、これらに限定される訳ではない。膜形成溶液に用いられるカテナンおよび対イオンの量、ならびに担体溶液自体を様々に変化させて、カテナン分子の単分子層を所望通りに形成することができる。

#### 【0038】

両親媒性分子のラングミュア単分子層の形成は、周知の技術である。例えば、review (Knobler, CM; Schwartz, DK. "Langmuir and self-assembled monolayers" (ラングミュアおよび自己組織化単分子層) (Current Opinion In Colloid & Interface Science, vol. 4, p.46-51, (1999))を参照のこと。イオン分子化合物のラングミュア単分子層を調合する際、多くの場合、更に複雑化を伴う可能性がある。例えば、イオン化合物では、陽イオンまたは陰イオンのいずれかがある特性水溶性を有することが多く、水溶性複合体からはラングミュア単分子層を形成することは不可能である。通常行うのは、いずれも著しい水溶性を呈しない分子複合体の陽イオンおよび陰イオン構成材料を具体的に設計または利用することである。このような非水溶性構成材料を識別することは必ずしも簡単な作業ではない。また、陽イオンおよび陰イオン双方を含む安定した溶液を調合する必要もあり、これらの溶液が長期安定性を呈しない場合もある。イオン両親媒性物質の優れた膜の調合を制御するパラメータは、サブフェーズのpH、サブフェーズのイオン強度、析出および転写温度、析出溶剤ならびに転写速度の制御を含む。

#### 【0039】

不揮発性および揮発性デバイス双方を製造した。手順Aを用いて揮発性スイッチング・デバイスのアレイ(タイプVデバイスと呼ぶ)を生産し、一方手順Bを用いて不揮発性スイッチング・デバイスのアレイ(タイプNVデバイスと呼ぶ)を生産した。

#### 【0040】

##### 手順A

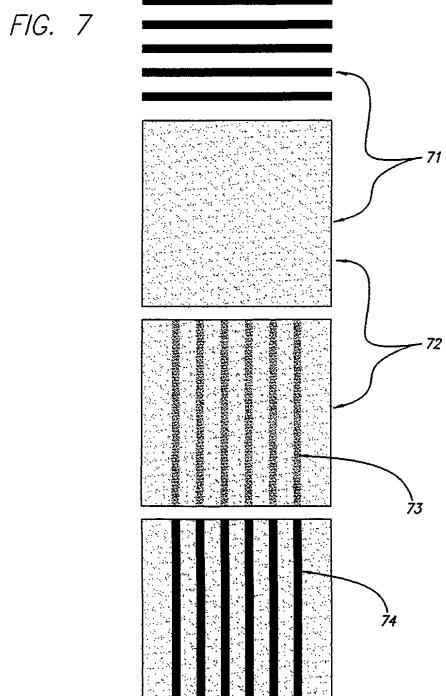

図7に示す手順にしたがってタイプVデバイスを製造した。ステップ1において、標準的なリソグラフィおよび製造手順を用いて、5マイクロメートル幅金属電極(71)をシリカ基板上に被着させた。金属電極は、厚さ0.1ナノメートルのアルミニウムを被覆した厚さ0.5マイクロメートルのチタン製の最下部電極から成る。ステップ2において、

10

20

30

40

50

対イオン(図6)を有する[2]カテナンの均一な单分子層を、ラングミュア・プロジェクト膜(72)として析出した。

【0041】

/ DMPA対イオンを有する[2]カテナンのラングミュア单分子層を両親媒性にするために、3:1クロロホルム：メタノール溶液内で、DMPAのナトリウム塩の2.4ミリモルの溶液を得る。別のフラスコにおいて、アセトニトリル溶液中で[2]カテナン<sup>4+</sup> / 4PF<sub>6</sub><sup>-</sup>複合体の0.8ミリモル溶液を調合する。0.5mLのDMPA溶液を[2]カテナン保存溶液と混合し、6:1 DMPA:[2]カテナン濃度を得る。これら2つの溶液を共に混合すると、時間と共に沈殿物がゆっくりと形成する。この沈殿物を回避するためには、調合後直ちにこの溶液を用いなければならない。マイクロシリンジを用いて、260cm<sup>2</sup>の表面積を特徴とし、18MegaOhm(超純)水で満たしたラングミュア・トラフに、約40マイクロリットルを滴状に追加する。30分待ち、单分子層 / サブフェーズを平衡させる。10cm<sup>2</sup>/分の割合で1ミリニュートン / メートルの表面圧力に单分子層を圧縮する。次いで、5cm<sup>2</sup>/分の割合で单分子層を14ミリニュートン / メートルの表面圧力に圧縮する。次いで、30ミリニュートン / メートルの表面圧力に達するまで、2cm<sup>2</sup>/分の割合で单分子層を圧縮する。この表面圧力は、大まかに[2]カテナン当たり87オングストローム<sup>2</sup>の面積に対応する。30分間单分子層を安定化させる。この時点で、垂直転写法(vertical transfer method)を用いて電極パターン化基板上に、ラングミュア・プロジェクト膜を調合する。これが意味するのは、パターン化基板を、1mm/分および一定表面圧力条件の下で、空気 / 水界面を通して上昇させることを意味する。測定した転写率(transfer ratio)は約1.1である。20

【0042】

ステップ3において、1組の上側Ti電極(73)(厚さ50ナノメートル、幅10マイクロメートル)を、第1組(71)に対して垂直に被着した。チタン金属は、有機分子上に蒸着すると、高品質の膜を形成することが以前から実証されている。ステップ4において、ステップ3において被着したチタン電極(73)の上に、アルミニウム電極(74)を直接被着した。最上部のアルミニウム電極(74)の1つおよび最下部のチタン電極(71)の1つを電気的に接触させることにより、個々のタイプVデバイスを指定した。

【0043】

得られたデバイスは、揮発性メモリ・セルの特性ヒステリシス・ループを呈し、メモリ・エレメントとしてまたはスイッチング・エレメントとして利用することができる。30

【0044】

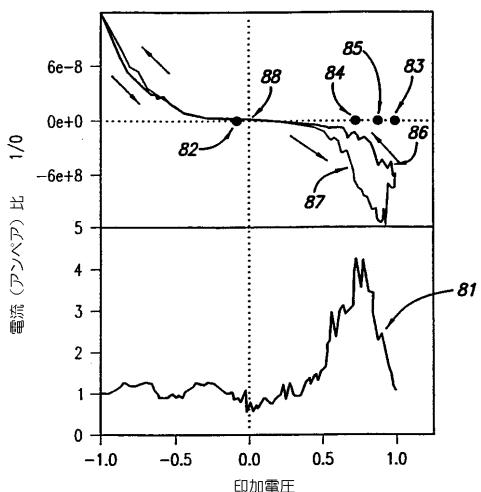

タイプVデバイスの1つの実際の動作を図8に示す。この場合、電流 / 電圧ヒステリシス・ループ(86、87)は、0電圧、0電流点(88)の高電圧側にある。スイッチが揮発性であると考えられるのは、このためである。ある電圧値(83)(例えば、+1V)でタイプVデバイスに書き込みを行うと、スイッチは「開放」即ち「0」状態となる。この状態は、ある中間電圧(例えば、83ないし84)(+0.65および+0.85ボルトの間)で読み出すことができる。ある低い電圧値(82)(例えば、0ボルト)でタイプVデバイスに書き込みを行うと、デバイスは「閉鎖」即ち「1」状態に移動する。この場合も、同じ中間電圧(83ないし84)で読み出すことができる。逆(86)および順方向(87)ヒステリシス曲線の比率を示し(81)、この比率から、この特定のデバイスが有用である電圧範囲がわかる。40

【0045】

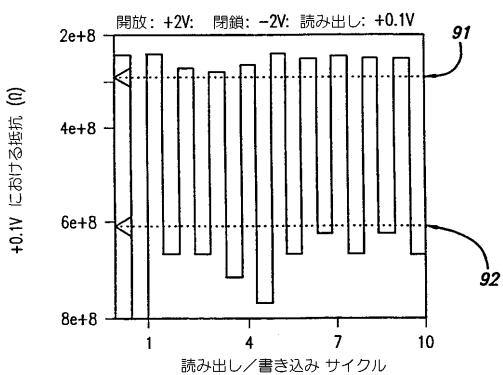

手順B

タイプNVデバイスは不揮発性スイッチであり、この場合は第1組の電極(71)をnドープ多結晶シリコンで作ったことを除いて、図7に示す製造手順にしたがって作った。これらの電極を空気に露出し、[2]カテナン(72)のラングミュア・プロジェクト分子单分子層を転写させる前に、酸素によるポリシリコン表面のパシベーションを行わせる。図9は、ヒステリシス・ループの代わりに、開放および閉鎖状態間におけるこれらのスイッチの1つの実際のサイクリングを示す。NVデバイスを、+2Vで「開放」即ち「0

10

20

30

40

50

」状態にセットし、-2Vで「閉鎖」即ち「1」状態にセットし、+0.1Vで読み出した。最下部電極(71)は半導体であり、最上部電極(73、74)は金属であるので、このデバイスは、分子スイッチング特性に加えて、ダイオード挙動が内蔵されている。このデバイスでは、読み出しが「非破壊的」であり、スイッチの状態を調べるという物理的作業によって、この状態が変化しないことを意味する。

#### 【0046】

別のデバイス例は、以下のようにして作った。

分子スイッチングにおいて補助する[2]カテナン(図4A)の必須(critical)構成材料は、一方の環(42)上で正に荷電したビピリジニウム単位(45)、および他方の環(41)上のテトラチアフルバレン化学基(44)である。他のデバイス例は、[2]カテナンに含まれる別の適当な化学基を置換することによって作ることができる。例えば、ビフェニル基(43)をフェニル基で置換した[2]カテナンも、スイッチ可能なカテナンとして機能する。この場合、[2]カテナン陽イオンの化学式は、 $[C_{66}H_{74}N_4O_{10}S_4]^{4+}$ である。このようなカテナンの液層スイッチングの証拠が報告されている(V. Valzani, A. Credi, G. mattersteig, O.A. Matthews, F.M. Raymo, J.F. Stoddart, M. Venturi, A.J.P. WhiteおよびD.J. Williams, "The switching of pseudorotaxanes and catenanes in incorporating a tetrathiafulvalene unit by redox and chemical inputs" (酸化還元および化学入力による、テトラチアフルバレン単位を組み込んだ偽ロタキサンおよびカテナンのスイッチング)(Journal of Organic Chemistry(印刷中、1999))。代わりの[2]カテナンは、ビフェニル基(43)を、テトラチアフルバレン単位以外の事実上他のいずれかの化学基で置換したものを含む。他の化学基は、エーテルまたはアルキル基というようなものを含むこともできる。また、ビピリジニウム単位(45)を含有するが、フェニル基の代わりにビフェニル、アルキル、またはその他の種々の基を利用してビピリジニウム単位を連結する[2]カテナンも、ソリッド・ステート・スイッチングまたは再構成可能メモリ・デバイスを作るのに適している。前述したような他の両親媒性対イオンで対イオン(図6)を置換した前述の[2]カテナンのいずれもが、ソリッド・ステート・スイッチングまたは再構成可能メモリ・デバイスとして機能する。

#### 【0047】

これら分子スイッチング・デバイスの必須電極構成材料は、スイッチング・デバイスの揮発性または不揮発性を制御可能とするような適切なフェルミ・レベルの電極を含む。pドープ・シリコンあるいはnまたはpドープ・ポリシリコンの電極が、不揮発性デバイスにおけるnドープ・ポリシリコン最下部電極(58)の代用品として適している。プラチナ、クロムおよびアルミニウムを含む種々の金属電極も、最下部または最上部電極のいずれにも代用することができる。しかしながら、これらの場合、分子スイッチング/メモリ・デバイスが揮発性かまたは不揮発性かを決定する際に、これらの電極のフェルミ・レベルを検討する必要がある。

#### 【0048】

以上、本発明の実施形態の一例について説明したが、開示内容は一例に過ぎず、本発明の範囲内において種々のその他の代替、改造および変更が可能であることは、当業者には認められよう。したがって、本発明は、上述の好適な実施形態に限定されるのではなく、特許請求の範囲によってのみ限定されるものとする。

#### 【図面の簡単な説明】

【図1】 図1は、不揮発性スイッチのヒステリシス・ループを示す電流対電圧図である。

【図2】 図2は、揮発性スイッチのヒステリシス・ループを示す電流対電圧図である。

【図3】 図3は、本発明によるデバイスに用いられる[2]カテナン分子の分子スイッチング機構の簡略図である。

【図4】 図4Aは、好適な[2]カテナンの一例の構造を示す。

図4Bは、[2]カテナンのスイッチング機構を分子レベルで示す。

【図5】 図5Aは、揮発性分子スイッチのエネルギー・レベル図である。

10

20

30

40

50

図 5 B は、不揮発性分子スイッチのエネルギー・レベル図である。

【図 6】 図 6 は、本発明によるデバイスを作成する際に用いられる膜を製作するときに用いられる好適な対イオンの一例を示す。

【図 7】 図 7 は、本発明による揮発性および不揮発性デバイスの製造工程の概略図を示す。

【図 8】 図 8 は、本発明による揮発性デバイスのヒステリシス・ループを示すグラフである。

【図 9】 図 9 は、本発明による不揮発性 [2] カテナン系分子スイッチの一例のサイクリングを示すグラフである。+ 2 V でデバイスに書き込みを行うことによってデバイスを「開放」即ち「0」状態に置く。- 2 V でデバイスに書き込みを行うことによって、デバイスを「閉鎖」即ち「1」状態に置く。+ 0.1 V でデバイスの読み出しを行う。このグラフは、デバイスを 2 つの状態間で巡回させたときのデバイスの抵抗を示す。

10

【図 1】

【図 4】

FIG. 4A

【図 2】

【図 3】

FIG. 3

FIG. 4B

【図5】

FIG. 5A

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

【図9】

---

フロントページの続き

(74)代理人 100075270

弁理士 小林 泰

(74)代理人 100080137

弁理士 千葉 昭男

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100120112

弁理士 中西 基晴

(72)発明者 ヒース, ジェームズ・リチャード

アメリカ合衆国カリフォルニア州 90405, サンタ・モニカ, ピア・アベニュー 2329

(72)発明者 コリアー, チャールズ・パトリック

アメリカ合衆国カリフォルニア州 90025, ロサンゼルス, カムデン・アベニュー 1624

アパートメント ナンバー 15

(72)発明者 マッターシュタイク, ギュンター

ドイツ連邦共和国バットネ・バイアイレンブルク, ヴィルデンハイナー・シュトラーセ 18

(72)発明者 ライモ, フランシスコ・エム

アメリカ合衆国カリフォルニア州 90024, ロサンゼルス, ミッドヴェール・アベニュー 6

10

(72)発明者 ストッダート, ジェームズ・フレイザー

アメリカ合衆国カリフォルニア州 90403, サンタ・モニカ, イエール・ストリート 1144

ナンバー 1

(72)発明者 ウォン, エリック

アメリカ合衆国カリフォルニア州 90036, ロサンゼルス, サウス・マンスフィールド・アベニュー 741, ナンバー 4

審査官 加藤 俊哉

(56)参考文献 特開平02-060166 (JP, A)

Vincenzo Balzani et al., Molecular Machines, Accounts of Chemical Research, American Chemical Society, 1998年 5月28日, VOL.31 NO.7, p.405-414

(58)調査した分野(Int.Cl., DB名)

G11C 13/00