(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7120792号**

**(P7120792)**

(45)発行日 令和4年8月17日(2022.8.17)

(24)登録日 令和4年8月8日(2022.8.8)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3233(2016.01) | F I | G 0 9 G | 3/3233       |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/20 6 4 2 K |

| H 0 4 N | 9/12 (2006.01)  |     | G 0 9 G | 3/20 6 4 1 P |

| H 0 1 L | 27/32 (2006.01) |     | G 0 9 G | 3/20 6 8 0 H |

| H 0 1 L | 51/50 (2006.01) |     | H 0 4 N | 9/12 B       |

請求項の数 9 (全19頁) 最終頁に続く

(21)出願番号

特願2018-75536(P2018-75536)

(22)出願日

平成30年4月10日(2018.4.10)

(65)公開番号

特開2019-184825(P2019-184825)

A)

(43)公開日

令和1年10月24日(2019.10.24)

審査請求日

令和3年3月30日(2021.3.30)

(73)特許権者

303018827

T i a n m a J a p a n 株式会社

神奈川県川崎市幸区鹿島田一丁目1番2

号

(73)特許権者

520272868

武漢天馬微電子有限公司

中華人民共和国武漢市東湖新技術開発区

流芳園横路8号

110001678

特許業務法人藤央特許事務所

松枝 洋二郎

神奈川県川崎市幸区鹿島田一丁目1番2

号 T i a n m a J a p a n 株式会社内

西島 篤宏

(74)代理人

(72)発明者

最終頁に続く

(54)【発明の名称】 表示装置

**(57)【特許請求の範囲】****【請求項1】**

表示装置であつて、

表示領域において、それぞれ第1方向に配列された複数の第1種画素からなる、複数の第1種画素ラインと、

前記表示領域において、それぞれ前記第1方向に配列された複数の第2種画素からなる、複数の第2種画素ラインと、

を含み、

前記複数の第1種画素ラインと前記複数の第2種画素ラインとは、前記第1方向に垂直な第2方向に交互に配列されており、

前記第1種画素は、前記第2方向に配列された第1赤副画素及び第1青副画素、並びに、前記第1赤副画素及び前記第1青副画素に対して前記第1方向と反対の側に配置され、かつ、前記第2方向において前記第1赤副画素及び前記第1青副画素の間に配置されている第1緑副画素、から構成され、

前記第2種画素は、前記第2方向に配列された第2赤副画素及び第2青副画素、並びに、前記第2赤副画素及び前記第2青副画素に対して前記第1方向の側に配置され、かつ、前記第2方向において前記第2赤副画素及び前記第2青副画素の間に配置されている第2緑副画素、から構成され、

前記複数の第1種画素ラインは、前記第1方向の反対側の端に配置されており、かつ、前記第2方向に配列されている画素ラインにおける前記第2方向の反対側の端に配置され

ている、複数の終端第1種画素を含み、

前記複数の第2種画素ラインは、前記第1方向の反対側の端に配置されており、かつ、前記第2方向に配列されている画素ラインにおける前記第2方向の反対側の端に配置されている、複数の終端第2種画素を含み、

前記複数の終端第1種画素それぞれの輝度は、同一の入力映像信号に対して、前記第1方向、前記第1方向の反対方向、前記第2方向、及び前記第2方向の反対方向の4方向において他の画素に囲まれている内部画素の輝度よりも小さく、

前記複数の終端第2種画素の輝度は、前記同一の入力映像信号に対して、前記複数の終端第1種画素の輝度よりも大きい、

表示装置。

10

#### 【請求項2】

請求項1に記載の表示装置であって、

前記複数の終端第1種画素それぞれの色度は、前記同一の入力映像信号に対して、前記内部画素の色度と同一である、

表示装置。

20

#### 【請求項3】

請求項1に記載の表示装置であって、

前記複数の終端第1種画素は、第1の終端第1種画素及び第2の終端第1種画素を含み、前記第1の終端第1種画素に対して前記第2方向の側において隣接している第2種画素は、前記第1方向の反対側において、第2種画素ラインの端に配置されており、

前記第2の終端第1種画素に対して前記第2方向において隣接している第2種画素は、前記第1方向の反対側に配置されている他の第2種画素に隣接し、

前記第1の終端第1種画素の輝度は、前記同一の入力映像信号に対して、前記第2の終端第1種画素の輝度よりも小さい、

表示装置。

20

#### 【請求項4】

請求項1に記載の表示装置であって、

前記複数の終端第2種画素の輝度は、前記同一の入力映像信号に対して、前記内部画素の輝度と同一である、

表示装置。

30

#### 【請求項5】

請求項1に記載の表示装置であって、

前記複数の終端第1種画素の両端の終端第1種画素に挟まれる終端第1種画素の縁副画素は、前記両端の終端第1種画素の縁副画素を結ぶ直線よりも外側に配置されている、

表示装置。

40

#### 【請求項6】

請求項5に記載の表示装置であって、

前記複数の終端第1種画素は、第1の終端第1種画素及び第2の終端第1種画素を含み、前記第1の終端第1種画素と、前記第1の終端第1種画素の両側の終端第1種画素それぞれとを結ぶ直線の間の角度は、前記第2の終端第1種画素と前記第2の終端第1種画素の両側の終端第1種画素それぞれとを結ぶ直線の間の角度よりも小さく、

前記第1の終端第1種画素の輝度は、前記同一の入力映像信号に対して、前記第2の終端第1種画素の輝度よりも小さい、

表示装置。

40

#### 【請求項7】

請求項1に記載の表示装置であって、

前記表示領域は、複数の終端第1種画素からなる第1グループと、前記第1グループと異なる複数の終端第1種画素からなる第2グループとを含み、

前記第1グループにおいて、両端の終端第1種画素に挟まれる終端第1種画素の縁副画素は、前記両端の終端第1種画素の縁副画素を結ぶ直線よりも外側に配置されており、

50

前記第2グループにおいて、両端の終端第1種画素に挟まれる終端第1種画素の縁副画素は、前記両端の終端第1種画素の縁副画素を結ぶ直線よりも内側に配置されており、前記同一の入力映像信号に対して、前記第1グループにおける最小輝度値は、前記第2グループにおける最小輝度値よりも小さい、表示装置。

**【請求項8】**

請求項1に記載の表示装置であって、

前記第1種画素及び前記第2種画素のそれぞれの輝度を制御する画素回路と、

前記画素回路それぞれの動作を制御する、制御装置をさらに含み、

前記制御装置は、前記複数の終端第1種画素の輝度を、前記同一の入力映像信号に対して、前記内部画素の輝度より小さくなるように、前記画素回路を制御する、表示装置。

10

**【請求項9】**

請求項1に記載の表示装置であって、

前記表示領域は、所定ピッチで配列された副画素からなる複数の副画素ラインで構成された領域であり、

前記複数の副画素ラインは、所定ピッチで配列されている、

表示装置。

**【発明の詳細な説明】**

**【技術分野】**

20

**【0001】**

本開示は、表示装置に関する。

**【背景技術】**

**【0002】**

カラー表示装置の表示領域は、一般に、表示パネルの基板上に配列された赤(R)、緑(G)、青(B)の副画素で構成されている。副画素の様々な配置(画素配置)が提案されおり、例えば、RGB Stripe配置や、デルタナブラ配置(単にデルタ配置とも呼ぶ)が知られている(例えば特許文献1)。

**【0003】**

近年、表示領域のコーナを曲線状に形成することで、表示領域のデザイン性を向上する製品が増加している。しかし、デルタナブラ配置では、曲線状のコーナ部(Rコーナ部とも呼ぶ)の刻み目が目立ちやすく、画質が低下する。

30

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【文献】特開2003-271088号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

したがって、デルタナ布拉配置の表示装置において、Rコーナ部における画質低下を抑制できる技術が望まれる。

40

**【課題を解決するための手段】**

**【0006】**

本開示の一態様の表示装置は、表示領域において、それぞれ第1方向に配列された複数の第1種画素からなる、複数の第1種画素ラインと、前記表示領域において、それぞれ前記第1方向に配列された複数の第2種画素からなる、複数の第2種画素ラインと、を含む。前記複数の第1種画素ラインと前記複数の第2種画素ラインとは、前記第1方向に垂直な第2方向に交互に配列されている。前記第1種画素は、前記第2方向に配列された第1赤副画素及び第1青副画素、並びに、前記第1赤副画素及び前記第1青副画素に対して前記第1方向と反対の側に配置され、かつ、前記第2方向において前記第1赤副画素及び前記第1青副画素を結ぶ直線よりも内側に配置されており、前記同一の入力映像信号に対して前記第1種画素及び前記第2種画素の輝度を制御する画素回路と、前記画素回路の動作を制御する、制御装置をさらに含み、前記制御装置は、前記複数の終端第1種画素の輝度を、前記同一の入力映像信号に対して、前記内部画素の輝度より小さくなるように、前記画素回路を制御する、表示装置。

50

記第1青副画素の間に配置されている第1緑副画素、から構成されている。前記第2種画素は、前記第2方向に配列された第2赤副画素及び第2青副画素、並びに、前記第2赤副画素及び前記第2青副画素に対して前記第1方向の側に配置され、かつ、前記第2方向において前記第2赤副画素及び前記第2青副画素の間に配置されている第2緑副画素、から構成されている。前記複数の第1種画素ラインは、前記第1の方向の反対側の端に配置されており、かつ、前記第2方向に配列されている画素ラインにおける前記第2方向の反対側の端に配置されている、複数の終端第1種画素を含む。前記複数の第2種画素ラインは、前記第1の方向の反対側の端に配置されており、かつ、前記第2方向に配列されている画素ラインにおける前記第2方向の反対側の端に配置されている、複数の終端第2種画素を含む。前記複数の終端第1種画素それぞれの輝度は、同一の入力映像信号に対して、前記第1方向、前記第1方向の反対方向、前記第2方向、及び前記第2方向の反対方向の4方向において他の画素に囲まれている内部画素の輝度よりも小さい。

#### 【発明の効果】

#### 【0007】

本開示の一態様によれば、デルタナプラ配置の表示装置において画質低下を抑制することができる。

#### 【図面の簡単な説明】

#### 【0008】

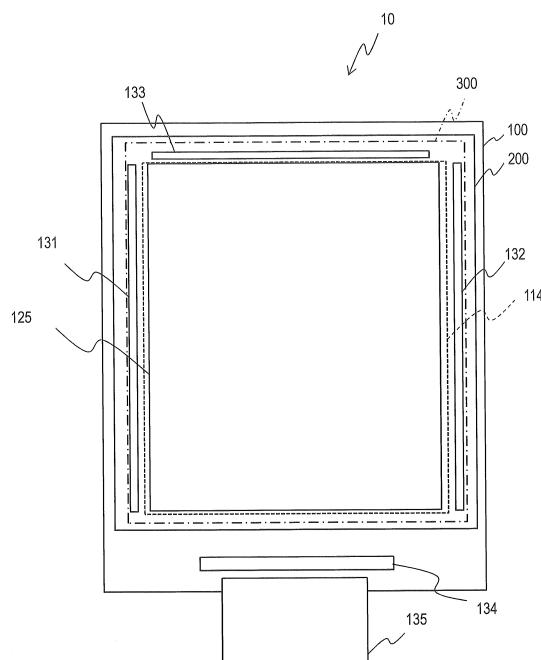

【図1】OLED表示装置の構成例を模式的に示す。

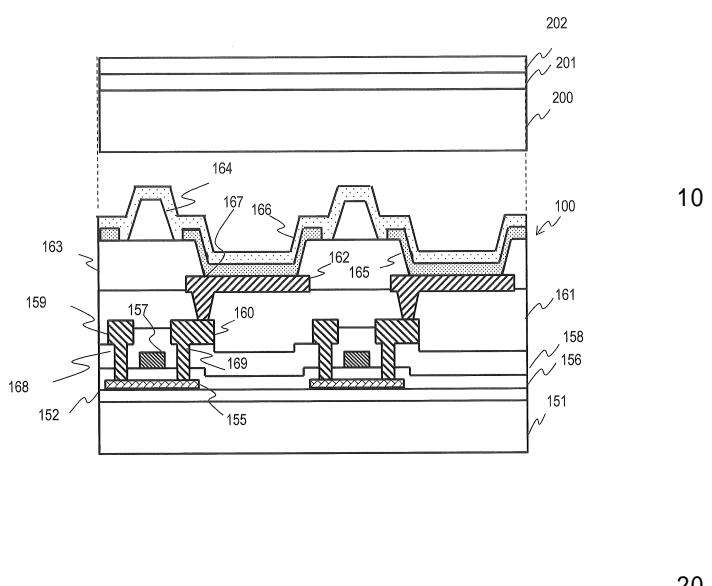

【図2】トップエミッション型の画素構造の例を示す。

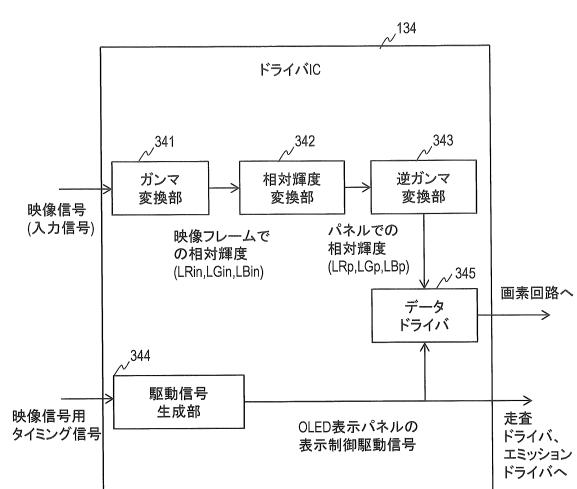

【図3A】ドライバICの論理要素を示す。

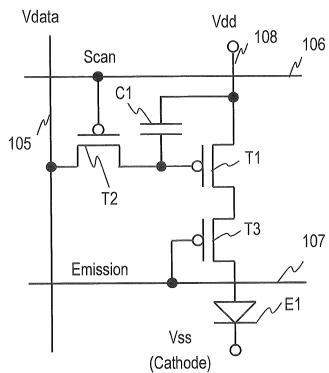

【図3B】画素回路の例を示す。

【図3C】画素回路の例を示す。

【図4】デルタナプラパネルにおける画素配置を示す。

【図5】図4に示す表示領域の部分に含まれる終端画素を示す。

【図6】凸状のRコーナ部における緑副画素外向き画素において、異なる輝度を与える例を示す。

【図7】緑副画素外向き終端画素と、隣接する緑副画素外向き終端画素との間の角度の例を示す。

【図8】表示領域の境界を含む一部の領域を模式的に示す。

【図9】凹状Rコーナ部における終端第1種画素及び終端第2種画素を示す。

【図10】凹状のRコーナ部における緑副画素外向き終端画素の位置関係を示す。

#### 【発明を実施するための形態】

#### 【0009】

以下、添付図面を参照して本開示の実施形態を説明する。本実施形態は本発明を実現するための一例に過ぎず、本開示の技術的範囲を限定するものではないことに注意すべきである。各図において共通の構成については同一の参照符号が付されている。

#### 【0010】

#### 【表示装置の構成】

図1を参照して、本実施形態に係る、表示装置の全体構成を説明する。なお、説明をわかりやすくするため、図示した物の寸法、形状については、誇張して記載している場合もある。以下において、表示装置の例として、OLED(Organic Light-Emitting Diode)表示装置を説明するが、本開示の特徴は、液晶表示装置や量子ドット表示装置等、OLED表示装置と異なる任意の種類の表示装置に適用することができる。

#### 【0011】

図1は、OLED表示装置10の構成例を模式的に示す。OLED表示装置10は、OLED表示パネルと制御装置とを含む。OLED表示パネルは、発光素子が形成されるTFT(Thin Film Transistor)基板100と、OLED素子を封止する封止基板200と、TFT基板100と封止基板200とを接合する接合部(ガラスフ

リットシール部) 300を含む。TFT基板100と封止基板200との間には、例えば、乾燥空気が封入されており、接合部300により封止されている。

#### 【0012】

TFT基板100の表示領域125の外側のカソード電極形成領域114の周囲に、走査ドライバ131、エミッションドライバ132、保護回路133、及びドライバIC134が配置されている。これらは、FPC(Flexible Printed Circuit)135を介して外部の機器と接続される。ドライバIC134は制御装置に含まれる。走査ドライバ131、エミッションドライバ132、及び保護回路133は、制御装置、又は、OLED表示パネル及び制御装置に含まれる。

#### 【0013】

走査ドライバ131はTFT基板100の走査線を駆動する。エミッションドライバ132は、エミッショントリニティ信号(制御信号)を駆動して、各副画素の発光期間を制御する。保護回路133は素子を静電気放電から保護する。ドライバIC134は、例えば、異方性導電フィルム(ACF:Anisotropic Conductive Film)を用いて実装される。

#### 【0014】

ドライバIC134は、走査ドライバ131及びエミッションドライバ132に電源及びタイミング信号(制御信号)を与え、さらに、データ線に映像データに対応する信号を与える。すなわち、ドライバIC134は、表示制御機能を有する。後述するように、ドライバIC134は、映像フレームの画素の相対輝度データを表示パネルの副画素の相対輝度データに変換する機能を有する。

#### 【0015】

図1において、左から右に延びる軸をX軸、上から下に延びる軸をY軸と呼ぶ。走査線はX軸に沿って延びてあり、表示領域125において、X軸に沿って配列された画素又は副画素を画素又は副画素の行と呼ぶ。表示領域125において、Y軸に沿って配列された画素又は副画素を画素列又は副画素の列と呼ぶ。

#### 【0016】

次に、OLED表示装置10の詳細構造について説明する。図2は、OLED表示装置10の断面構造の一部を模式的に示す。図2に示すように、OLED表示装置10は、TFT基板100と、TFT基板100と対向する封止構造部とを含む。ここで、封止構造部の一例は、可撓性又は不撓性の封止基板200である。封止構造部は、例えば、薄膜封止(TFE:Thin Film Encapsulation)構造であってもよい。

#### 【0017】

TFT基板100は、絶縁基板151と封止構造部との間に配置された、複数の下部電極(例えば、アノード電極162)と、1つの上部電極(例えば、カソード電極166)と、複数の有機発光層165とを含む。カソード電極166は、有機発光層165(有機発光膜165とも記す)からの光を封止構造部に向けて透過させる透明電極である。

#### 【0018】

1つのカソード電極166と1つのアノード電極162との間に、1つの有機発光層165が配置されている。複数のアノード電極162は、同一面上(例えば、平坦化膜161の上)に配置され、1つのアノード電極162の上に1つの有機発光層165が配置されている。

#### 【0019】

OLED表示装置10は、封止構造部に向かって立ち上がる複数のスペーサ164と、それぞれが複数のスイッチを含む複数の回路とを有する。複数の回路の各々は、絶縁基板151とアノード電極162との間に形成され、複数のアノード電極162の各々に供給する電流を制御する。

#### 【0020】

図2は、トップエミッショントリニティ型の画素構造の例を示す。トップエミッショントリニティ型の画素構造は、光が出射する側(図面上側)に、複数の画素に共通のカソード電極166が配置さ

10

20

30

40

50

れる。カソード電極 166 は、表示領域 125 の全面を完全に覆う形状を有する。本開示の特徴は、ボトムエミッション型の画素構造を有する OLED 表示装置にも適用できる。ボトムエミッション型の画素構造は、透明アノード電極と反射カソード電極を有し、 TFT 基板 100 を介して外部に光を出射する。

#### 【0021】

以下、OLED 表示装置 10 についてより詳しく説明する。TFT 基板 100 は、表示領域 125 内に配列された副画素、及び、表示領域 125 の周囲の配線領域に形成された配線を含む。配線は、画素回路と、配線領域に配置された回路 131、132、134 とを接続する。

#### 【0022】

本実施形態の表示領域 125 は、デルタナブラ配置された副画素で構成されている。デルタナ布拉配置の詳細は後述する。以下において、OLED 表示パネルを、デルタナ布拉パネルと呼ぶことがある。副画素は、赤 (R)、緑 (G)、又は青 (B) のいずれかの色を表示する発光領域である。以下に説明する例は、上記三色の組により画像を表示するが、OLED 表示装置 10 は、これと異なる三色の組により表示してもよい。

#### 【0023】

発光領域は、OLED 素子に含まれる。OLED 素子は、下部電極であるアノード電極、有機発光層、及び上部電極であるカソード電極を含んで構成される。すなわち、複数の OLED 素子は、1 つのカソード電極 166 と、複数のアノード電極 162 と、複数の有機発光層 165 により形成されている。

#### 【0024】

絶縁基板 151 は、例えばガラス又は樹脂で形成されており、不撓性又は可撓性基板である。なお、以下の説明において、絶縁基板 151 に近い側を下側、遠い側を上側と記す。ゲート絶縁膜 156 を介して、ゲート電極 157 が形成されている。ゲート電極 157 の層上に層間絶縁膜 158 が形成されている。

#### 【0025】

表示領域 125 内において、層間絶縁膜 158 上にソース電極 159、ドレイン電極 160 が形成されている。ソース電極 159、ドレイン電極 160 は、例えば、高融点金属又はその合金で形成される。ソース電極 159、ドレイン電極 160 は、層間絶縁膜 158 のコンタクトホールに形成されたコンタクト部 168、169 によって、チャネル部 155 に接続されている。

#### 【0026】

ソース電極 159、ドレイン電極 160 の上に、絶縁性の平坦化膜 161 が形成される。絶縁性の平坦化膜 161 の上に、アノード電極 162 が形成されている。アノード電極 162 は、平坦化膜 161 のコンタクトホールに形成されたコンタクト部によってドレイン電極 160 に接続されている。画素回路 (TFTs) は、アノード電極 162 の下側に形成されている。

#### 【0027】

アノード電極 162 の上に、OLED 素子を分離する絶縁性の画素定義層 (Pixel Defining Layer : PDL) 163 が形成されている。OLED 素子は、積層された、アノード電極 162、有機発光層 165、及びカソード電極 166 (の部分) で構成される。発光領域 OLED 素子は、画素定義層 163 の開口 167 に形成されている。

#### 【0028】

絶縁性のスペーサ 164 は、2 つのアノード電極 162 の間ににおける、画素定義層 163 の面上に形成されている。スペーサ 164 の頂面は画素定義層 163 の上面よりも高い (封止基板 200 に近い) 位置にあり、封止基板 200 が変形した場合に、封止基板 200 を支持して、OLED 素子と封止基板 200 との間隔を維持する。

#### 【0029】

アノード電極 162 の上に、有機発光層 165 が形成されている。有機発光層 165 は

10

20

30

40

50

、画素定義層 163 の開口 167 及びその周囲において、画素定義層 163 に付着している。有機発光層 165 の上にカソード電極 166 が形成されている。カソード電極 166 は、透明電極である。カソード電極 166 は、有機発光層 165 からの可視光の全て又は一部を透過させる。

#### 【0030】

画素定義層 163 の開口 167 に形成された、アノード電極 162、有機発光層 165 及びカソード電極 166 の積層膜が、OLED 素子を構成する。電流は画素定義層 163 の開口 167 のみに流れので、開口 167 において露出している有機発光層 165 の領域が、OLED 素子の発光領域（副画素）である。カソード電極 166 は、分離して形成されているアノード電極 162 及び有機発光層 165（OLED 素子）に共通である。なお、カソード電極 166 の上には、不図示のキャップ層が形成されてもよい。

10

#### 【0031】

封止基板 200 は、透明な絶縁基板であって、例えばガラス基板である。封止基板 200 の光出射面（前面）に、 $\sqrt{4}$  位相差板 201 と偏光板 202 とが配置され、外部から入射した光の反射を抑制する。

#### 【0032】

##### [ドライバICの構成]

図3Aは、ドライバIC 134の論理要素を示す。ドライバIC 134は、ガンマ変換部 341、相対輝度変換部 342、逆ガンマ変換部 343、駆動信号生成部 344、及びデータドライバ 345 を含む。

20

#### 【0033】

ドライバIC 134 は、不図示の主制御部から、映像信号及び映像信号用タイミング信号を受信する。映像信号は、連続する映像フレームのデータ（信号）を含む。ガンマ変換部 341 は、入力された映像信号に含まれる RGB 階調値（信号）を、RGB 相対輝度値に変換する。より具体的には、ガンマ変換部 341 は、各映像フレームの各画素の R 階調値、G 階調値、B 階調値を、R 相対輝度値、G 相対輝度値、B 相対輝度値（LRin、LGin、LBin）に変換する。画素の相対輝度値は、映像フレーム内で正規化された輝度値である。

#### 【0034】

相対輝度変換部 342 は、映像フレーム内の各画素の R、G、B 相対輝度値（LRin、LGin、LBin）を、OLED 表示パネルの副画素の R、G、B 相対輝度値（LRp、LGP、LBp）に変換する。副画素の相対輝度値は、OLED 表示パネルにおいて正規化された副画素の輝度値である。

30

#### 【0035】

なお、表示すべき画像データの画素数と表示パネルの画素数は必ずしも一致するとは限らず、レンダリング処理によって見かけ上の解像度を向上させることもできる。その場合には、レンダリング処理後に最終的に表示パネルの副画素に割り当てられた各画素の R、G、B 相対輝度値（LRin、LGin、LBin）に対して、上記処理を行い OLED 表示パネルの副画素の R、G、B 相対輝度値（LRp、LGP、LBp）に変換する。

40

#### 【0036】

後述するように、相対輝度変換部 342 は、特定のパネル画素を構成する副画素の相対輝度値を調整する。具体的には、相対輝度変換部 342 は、同一の入力信号に対して、特定画素の相対輝度値を他の画素の相対輝度値よりも小さくなるように決定する。なお、相対輝度変換部 342 と異なる機能部、例えば、ガンマ変換部 341 が、特定画素の輝度を調整する処理を行ってもよい。

#### 【0037】

逆ガンマ変換部 343 は、相対輝度変換部 342 による演算後の R 副画素、G 副画素、B 副画素の相対輝度値を、R 副画素、G 副画素、B 副画素の階調値に変換する。データドライバ 345 は、R 副画素、G 副画素、B 副画素の階調値に応じた駆動信号を、画素回路に送信する。

50

**【 0 0 3 8 】**

駆動信号生成部 344 は、入力された映像信号用タイミング信号を、OLED 表示パネルの表示制御用駆動信号に変換する。映像信号用タイミング信号は、データ転送レートを決定するドットクロック（ピクセルクロック）、水平同期信号、垂直同期信号、データイネーブル信号を含む。

**【 0 0 3 9 】**

駆動信号生成部 344 は、入力された映像信号用タイミング信号のドットクロック、データイネーブル信号、垂直同期信号、水平同期信号から、デルタナブラパネルのデータドライバ 345、走査ドライバ 131、及びエミッションドライバ 132 の制御信号（又は、パネルの駆動信号）を生成し、それらに出力する。

10

**【 0 0 4 0 】****[ 画素回路 ]**

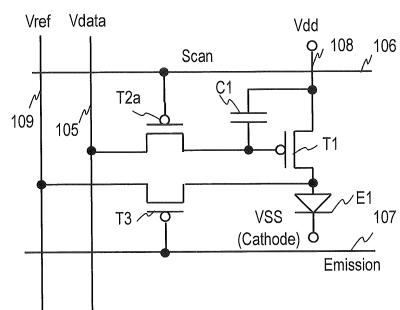

基板 100 上には、複数の副画素のアノード電極にそれぞれ供給する電流を制御する複数の画素回路が形成されている。図 3B は、画素回路の構成例を示す。各画素回路は、第 1 のトランジスタ T1 と、第 2 のトランジスタ T2 と、第 3 のトランジスタ T3 と、保持容量 C1 を含む。画素回路は、副画素である OLED 素子 E1 の発光を制御する。トランジスタは、TFT (Thin Film Transistor) である。以下、第 1 のトランジスタ T1 ~ 第 3 のトランジスタ T3 をそれぞれトランジスタ T1 ~ トランジスタ T3 と略記する。

**【 0 0 4 1 】**

トランジスタ T2 は副画素選択用のスイッチである。トランジスタ T2 は p チャネル型 TFT であり、ゲート端子は、走査線 106 に接続されている。ドレン端子は、データ線 105 に接続されている。ソース端子は、トランジスタ T1 のゲート端子に接続されている。

20

**【 0 0 4 2 】**

トランジスタ T1 は OLED 素子 E1 の駆動用のトランジスタ（駆動 TFT）である。トランジスタ T1 は p チャネル型 TFT であり、そのゲート端子は T2 のソース端子に接続されている。トランジスタ T1 のソース端子は電源線 108 (Vdd) に接続されている。ドレン端子は、トランジスタ T3 のソース端子に接続されている。トランジスタ T1 のゲート端子とソース端子との間に保持容量 C1 が形成されている。

30

**【 0 0 4 3 】**

トランジスタ T3 は、OLED 素子 E1 への駆動電流の供給と停止を制御するスイッチである。トランジスタ T3 は p チャネル型 TFT であり、ゲート端子はエミッショントリニティ制御線 107 に接続されている。トランジスタ T3 のソース端子はトランジスタ T1 のドレン端子に接続されている。ドレン端子は、OLED 素子 E1 に接続されている。

**【 0 0 4 4 】**

次に、画素回路の動作を説明する。走査ドライバ 131 が走査線 106 に選択パルスを出力し、トランジスタ T2 を開状態にする。データ線 105 を介してドライバ IIC 134 から供給されたデータ電圧は、保持容量 C1 に格納される。保持容量 C1 は、格納された電圧を、1 フレーム期間を通じて保持する。保持電圧によって、トランジスタ T1 のコンダクタンスがアナログ的に変化し、トランジスタ T1 は、発光調節に対応した順バイアス電流を OLED 素子 E1 に供給する。

40

**【 0 0 4 5 】**

トランジスタ T3 は、駆動電流の供給経路上に位置する。エミッションドライバ 132 は、エミッショントリニティ制御線 107 に制御信号を出力して、トランジスタ T3 開閉状態を制御する。トランジスタ T3 が開状態のとき、駆動電流が OLED 素子 E1 に供給される。トランジスタ T3 が閉状態のとき、この供給が停止される。トランジスタ T3 の開閉を制御することにより、1 フィールド周期内の点灯期間（デューティ比）を制御することができる。

**【 0 0 4 6 】**

50

図3Cは、画素回路の他の構成例を示す。図3Bの画素回路との相違は、トランジスタT2aと、トランジスタT3である。トランジスタT2aは、図3BのトランジスタT2の機能（副画素選択用のスイッチ）と同じ機能を有するスイッチである。

#### 【0047】

トランジスタT3は、様々な目的で使用することができる。トランジスタT3は、例えば、OLED素子E1間のリーク電流によるクロストークを抑制するために、一旦、OLED素子E1のアノード電極を黒信号レベル以下の十分低い電圧にリセットする目的で使用しても良い。

#### 【0048】

他にも、トランジスタT3は、トランジスタT1の特性を測定する目的で使用してもよい。例えば、トランジスタT1を飽和領域、スイッチングトランジスタT3を線形領域で動作するようにバイアス条件を選んで、電源線108(Vdd)から基準電圧供給線109(Vref)に流れる電流を測定すれば、トランジスタT1の電圧・電流変換特性を正確に測定することができる。副画素毎のトランジスタT1の電圧・電流変換特性の違いを補償するデータ信号を外部回路で生成すれば、均一性の高い表示画像を実現できる。

10

#### 【0049】

一方、トランジスタT1をオフ状態にしてトランジスタT3をリニア領域で動作させ、OLED素子E1を発光させる電圧を基準電圧供給線109から印加すれば、副画素毎のOLED素子E1の電圧・電流特性を正確に測定することができる。例えば、長時間の使用によってOLED素子E1が劣化した場合にも、その劣化量を補償するデータ信号を外部回路で生成すれば、長寿命化を実現できる。

20

#### 【0050】

図3B及び3Cの画素回路は例であって、画素回路は他の回路構成を有してもよい。図3B及び3Cの画素回路はpチャネル型TFTを使用しているが、画素回路はnチャネル型TFTを使用してもよい。

#### 【0051】

##### [デルタナプラパネルにおける画素配置]

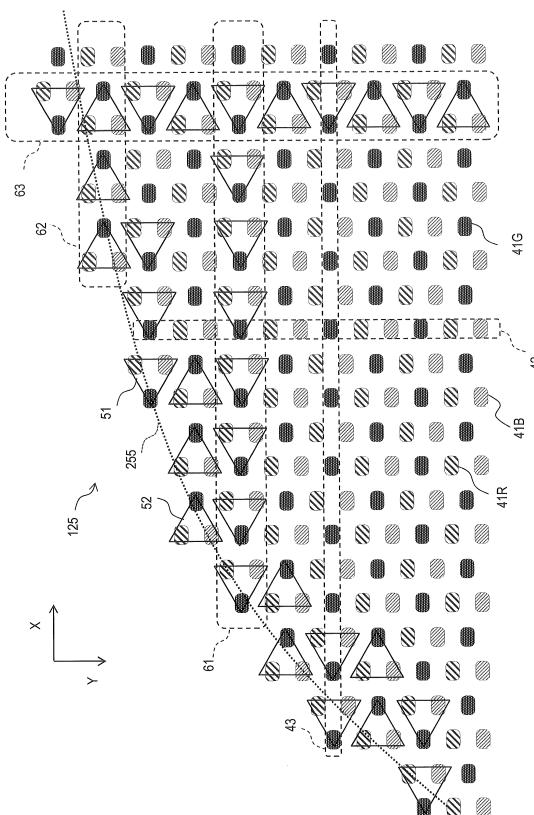

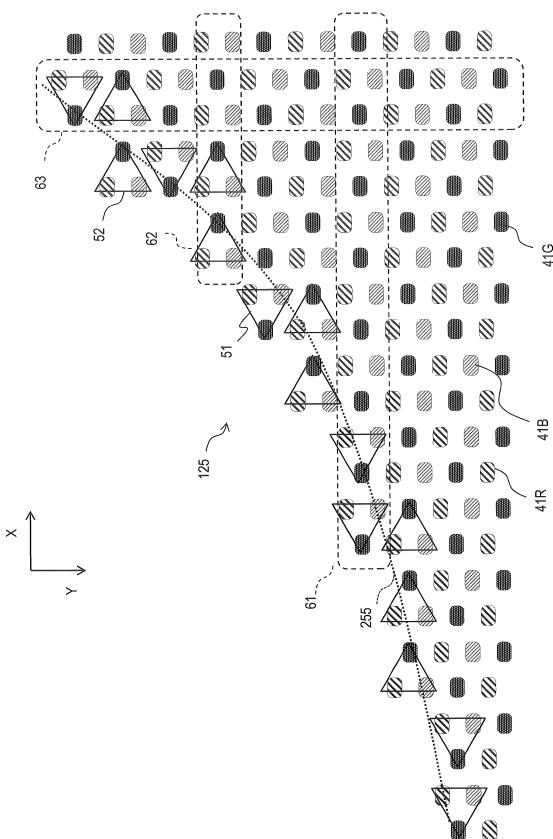

図4は、デルタナプラパネルにおける画素配置を示す。図4は、表示領域125の境界（表示領域125の端）を含む一部の領域を模式的に示す。図4は、凸状の曲線的な境界を示す部分を示す。曲線255は、表示領域125の設計上の仮想的な境界線を示す。曲線255に従って、表示領域125の端の画素及び副画素の配置が決定されている。以下において、凸状又は凹上の曲線的な境界を示す部分を、Rコーナ部とも呼ぶ。

30

#### 【0052】

表示領域125は、面内に配置されている、複数の赤副画素41R、複数の緑副画素41G、及び複数の青副画素41Bで構成されている。図4において、一つの赤副画素、一つの緑副画素、及び一つの青副画素が、例として、符号で指示されている。図4において、同一のハッチングの（丸い角の）四角は、同一色の副画素を示す。図4において、副画素の形状は四角であるが、副画素の形状は任意であって、例えば、六角形又は八角形であつてもよい。

#### 【0053】

表示領域125は、X方向に配列されている複数の副画素列42を含む。図4において、一つの副画素列が、例として、符号42で指示されている。副画素列42は、図4において、Y方向に配列されている副画素で構成されている。X方向（第1方向）は、図4において左から右に向かう方向であり、Y方向（第2方向）は、上から下に向かう方向である。X方向とY方向は、副画素が配置されている面内において垂直である。

40

#### 【0054】

副画素列42は、所定ピッチで交互に配列された赤副画素41R、緑副画素41G及び青副画素41Bで構成されている。図4の例において、赤副画素41R、青副画素41B、及び緑副画素41Gは、この順で配列されている。隣接する副画素列42の位置は、Y方向においてずれており、副画素列42の副画素は、Y方向において、隣接する副画素列

50

4 2 の他の二色の副画素の間にある。

**【 0 0 5 5 】**

図 4 の例において、隣接する副画素列 4 2 は半ピッチずれている。1 ピッチは、同一色の副画素の間の Y 方向における距離である。例えば、緑副画素は、Y 方向において、隣接副画素列 4 2 における赤副画素と青副画素の中央に位置している。

**【 0 0 5 6 】**

表示領域 1 2 5 は、Y 方向に配列されている複数の副画素行 4 3 を含む。図 4 において、一つの緑の副画素行が、例として、符号 4 3 で指示されている。副画素行 4 3 は、X 方向に所定ピッチで配列されている副画素で構成されている。図 4 の例において、各副画素行 4 3 は、同一色の副画素で構成されている。副画素行 4 3 は、他の 2 色の副画素行に Y 方向において挟まれている。

10

**【 0 0 5 7 】**

副画素行 4 3 の副画素は、X 方向において、隣接する副画素行 4 3 の隣接する二つの副画素の間に位置する。図 4 の例において、隣接する副画素行 4 3 は半ピッチずれている。1 ピッチは、副画素行 4 3 において隣接する副画素の間の距離である。副画素は、X 方向において、隣接する副画素行 4 3 の隣接する二つの副画素の中央に位置する。

**【 0 0 5 8 】**

なお、本実施形態においては、便宜的に、X 方向に延びる副画素ラインを副画素行、Y 方向に延びる副画素ラインを副画素列と呼びが、副画素行及び副画素列の方向は、これに限定されない。

20

**【 0 0 5 9 】**

表示領域 1 2 5 は、マトリックス状に配置されている、第 1 種画素 5 1 及び第 2 種画素 5 2 の、2 種類の画素を含む。図 4 において、一つの第 1 種画素のみが、例として、符号 5 1 で指示されている。また、一つの第 2 種画素のみが、例として、符号 5 2 で指示されている。第 1 種画素及び第 2 種画素の一方が、デルタナプラ配置におけるデルタ画素であり、もう一方がナプラ画素である。

**【 0 0 6 0 】**

図 4 において、いくつかの第 1 種画素 5 1 は、一つの頂点が左側にあり、二つの頂点が右側にある三角形で示されている。また、いくつかの第 2 種画素 5 2 は、一つの頂点が右側にあり、二つの頂点が左側にある三角形で示されている。図 4 における右側が X 方向の側であり、左側がその反対側である。なお、画素 5 1 が第 2 種画素と呼び、画素 5 2 を第 1 種画素と呼んでもよい。

30

**【 0 0 6 1 】**

第 1 種画素 5 1 及び第 2 種画素 5 2 は、それぞれ、一つ緑副画素 4 1 G と、当該緑副画素 4 1 G に隣接する副画素列 4 2 において、当該緑副画素 4 1 G に隣接する（最も近い）赤副画素 4 1 R 及び青副画素 4 1 B で構成されている。

**【 0 0 6 2 】**

第 1 種画素 5 1 において、赤副画素 4 1 R 及び青副画素 4 1 B は、同一の副画素列 4 2 において連続して配置されている。緑副画素 4 1 G が含まれる副画素列 4 2 は、赤副画素 4 1 R 及び青副画素 4 1 B が含まれる副画素列 4 2 、X 方向の反対側、つまり、図 4 における左側に隣接している。緑副画素 4 1 G は、Y 方向において、赤副画素 4 1 R と青副画素 4 1 B の間、より具体的には中央に位置している。

40

**【 0 0 6 3 】**

第 2 種画素 5 2 において、赤副画素 4 1 R 及び青副画素 4 1 B は、同一の副画素列 4 2 において連続して配置されている。緑副画素 4 1 G が含まれる副画素列 4 2 は、赤副画素 4 1 R 及び青副画素 4 1 B が含まれる副画素列 4 2 、X 方向の側、つまり、図 4 における右側に隣接している。緑副画素 4 1 G は、Y 方向において、赤副画素 4 1 R と青副画素 4 1 B の間、より具体的には中央に位置している。

**【 0 0 6 4 】**

表示領域 1 2 5 は、X 方向に延び、Y 方向に配列されている複数の画素行（X 方向延び

50

る画素ライン)を含む。複数の画素行は、第1種画素行61及び第2種画素行62の2種類の画素行で構成されている。図4において、一つの第1種画素行が、例として、符号61で指示されている。また、一つの第2種画素行が、例として、符号62で指示されている。

#### 【0065】

第1種画素行61は、X方向に配列された第1種画素51で構成されている。第2種画素行62は、X方向に配列された第2種画素52で構成されている。表示領域125において、第1種画素行61及び第2種画素行62は、Y方向において交互に配列されている。

#### 【0066】

表示領域125は、Y方向に延び、X方向に配列されている複数の画素列(Y方向延びる画素ライン)63を含む。図4において、一つの画素列が、例として、符号63で指示されている。各画素列は、Y方向に所定ピッチで交互に配列された、第1種画素51及び第2種画素52で構成されている。

#### 【0067】

図5は、図4に示す表示領域125の部分に含まれる終端画素を示す。終端画素は、画素行及び画素列双方の端に配置されている画素である。第1種画素の終端画素を、終端第1種画素と呼び、第2種画素の終端画素を、終端第2種画素と呼ぶ。また、画素行又は画素列の少なくとも一方の端に配置されている画素を境界画素と呼ぶ。終端画素は境界画素でもある。境界画素の位置は、境界線255に応じて決定されている。

#### 【0068】

図5は、終端第1種画素51A～51E、並びに、終端第2種画素52A、52B及び52Cを示す。例えば、第1種画素51Dは、第1種画素行61Aの左端に位置し、さらに、画素列63Bの上端に位置する。第2種画素52Aは、第2種画素行62Aの左端に位置し、さらに、画素列63Aの上端に位置する。なお、画素行又は画素列は、単一の画素で構成されていてもよい。当該单一画素は、その画素行又は画素列の端に配置されている。

#### 【0069】

終端画素は画素行及び画素列の端に位置しているため、画素行及び画素列それぞれに沿った2方向において表示領域の外部に露出している。図5の例において、終端第1種画素51A～51E、並びに、終端第2種画素52A、52B及び52Cは、画素行の左端(X方向の反対側の端)及び画素列の上端(Y方向の反対側の端)に配置されている。終端第1種画素51A～51E、並びに、終端第2種画素52A、52B及び52Cは、左側(X方向の反対側)及び上側(Y方向の反対側)において露出している。

#### 【0070】

終端第1種画素51A～51Eは、それらの緑副画素41Gの側において、露出している。一方、終端第2種画素52A、52B、52Cは、それらの緑副画素41Gと反対側(赤副画素41R及び青副画素41Bの側)において、露出している。言い換えれば、終端第1種画素51A～51Eの緑副画素41Gは、表示領域125の外側を向いており、終端第2種画素52A、52B、52Cの緑副画素41Gは、表示領域125の内側を向いている。

#### 【0071】

図5に示すように、終端第1種画素51A～51Eの重心から緑副画素41Gに向かうベクトルと、表示領域境界線255の上記重心に最も近い点の外側に向かう法線ベクトルとの間の角度は、鋭角である。反対に、終端第2種画素52A、52B及び52Cの重心から緑副画素41Gに向かうベクトルと、表示領域境界線255の上記重心に最も近い点の外側に向かう法線ベクトルとの間の角度は、鈍角である。

#### 【0072】

##### [輝度調整]

発明者の検討によれば、Rコーナ部において、終端画素の緑副画素が外向きである場合、その終端画素(の緑副画素)が視認されやすく、Rコーナ部における刻み目が目立ちや

10

20

30

40

50

すい。そこで、OLED表示装置10は、Rコーナ部において視認されやすい画素の輝度を相対的に低下させる。

#### 【0073】

つまり、OLED表示装置10は、同一の入力信号に対して、特定の終端画素の輝度を、他の画素の輝度よりも低くする。これにより、Rコーナ部における刻み目を目立ちにくくすることができる（スムージング処理）。

#### 【0074】

具体的には、OLED表示装置10は、終端第1種画素51A～51Eの輝度を、内部画素56の輝度よりも相対的に低くする。内部画素56は、周囲を他の画素に囲まれている画素であり、より具体的には、X方向、X方向の反対方向、Y方向及びY方向の反対方向の4方向において、他の画素に隣接している画素である。10

#### 【0075】

OLED表示装置10は、同一の入力映像信号に対して、終端第1種画素51A～51Eの輝度を内部画素56の輝度よりも低くする。なお、終端第1種画素51A～51Eの一部の輝度のみ、例えば、終端第1種画素51A～51Eにおいて終端第1種画素51A及び51Bのみを、内部画素56の輝度より低くしてもよい。

#### 【0076】

緑副画素外向き終端画素は、緑副画素内向き終端画素よりも視認されやすく、また、終端画素以外の境界画素よりも視認されやすい。OLED表示装置10は、例えば、同一の入力映像信号に対して、終端第1種画素51A～51Eの輝度を、終端第2種画素52A、52B、52Cの輝度よりも低くする。また、OLED表示装置10は、同一の入力映像信号に対して、終端第1種画素51A～51Eの輝度を、終端画素ではない境界画素の輝度よりも低くする。20

#### 【0077】

OLED表示装置10は、同一の入力映像信号に対して、緑副画素内向き終端画素の輝度を、内部画素及び終端画素ではない境界画素と同一にする。緑副画素内向き終端画素と内部画素及び終端画素ではない境界画素の視認性に大きな違いはないからである。緑副画素内向き終端画素の輝度は、内部画素及び/又は終端画素ではない境界画素の輝度よりも低くてもよい。

#### 【0078】

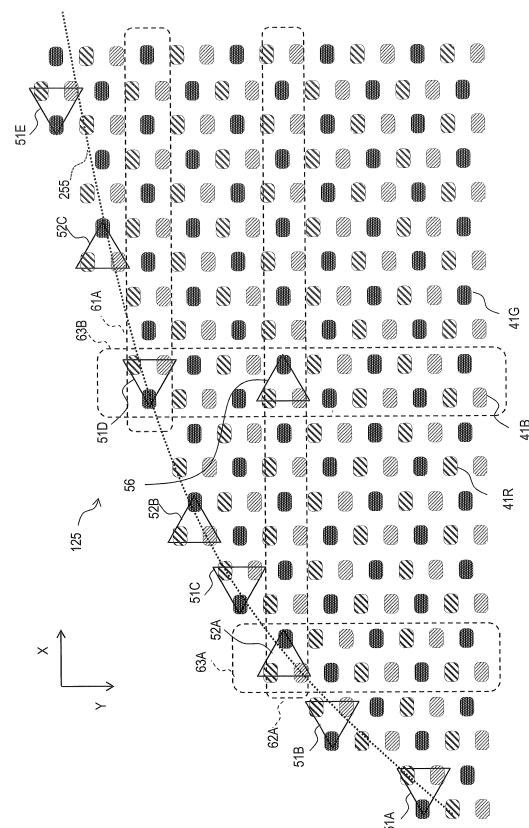

図5は、凸状のRコーナ部を示す。OLED表示装置10は、凸状のRコーナ部に含まれる緑副画素外向き画素において、異なる輝度を与えてよい。図6は、凸状のRコーナ部における緑副画素外向き画素において、異なる輝度を与える例を示す。30

#### 【0079】

図6に示すように、Rコーナ部は、X方向及びY方向における位置が異なる複数の終端画素を含む。図6の例において、終端第1種画素51A～51E及び終端第2種画素52A、52B、52Cの位置は、X方向及びY方向において異なる。さらに、凸状のRコーナ部において、終端第1種画素51A及び51Eの緑副画素41Gを結ぶ線256に対して、それらの間の終端第1種画素51B、51C、及び51Dの緑副画素41Gは、外側に配置されている。40

#### 【0080】

図6に示す例において、OLED表示装置10は、同一入力映像信号に対して、終端第1種画素51Bの輝度を、他の終端第1種画素51C、51D、51Eよりも小さくする。終端第1種画素51Bは、終端第1種画素51C、51D、51Eよりも視認されやすいからである。

#### 【0081】

終端第1種画素51Bは、下側、つまりY方向において、第2種画素53Aに隣接している。第2種画素53Aは、第2種画素行の端に配置されている境界画素であり、左側、つまり、X方向の反対側において、露出している（隣接第2種画素が存在しない）。

#### 【0082】

一方、例えば、終端第1種画素51Cは、Y方向(下側)において、第2種画素53Bに隣接している。第2種画素53Bの左側には、終端第2種画素52Aが存在している。つまり、第2種画素53Bは、X方向の反対側に配置されている終端第2種画素52Aに隣接している。他の終端第1種画素51D、51Eの左斜め下にも、第2種画素が配置されている。

#### 【0083】

例えば、相対輝度変換部342は、終端第1種画素51A～51Eの輝度Yのそれぞれに、所定の補正係数を掛けることで、他の画素よりも相対的に輝度を小さくすることができる。画素の輝度Y<sub>R</sub>、G、Bは、 $k \times (d / 255)$ で計算される。ここで、kは補正係数、dは階調レベル、そしてはガンマ値である。

10

#### 【0084】

一例において、終端第1種画素51A、51C、51Dの補正係数が2、終端第1種画素51Bの補正係数が3、終端第1種画素51Eの補正係数が1である。<sub>0</sub>(=1.0)><sub>1</sub>><sub>2</sub>><sub>3</sub>の関係が成立する。図6における他の境界画素の補正係数は<sub>0</sub>(=1.0)である。したがって、図6に示す画素において、終端第1種画素51B輝度が、同一入力信号に対して、最も小さい。

#### 【0085】

上記式から理解されるように、画素の輝度補正において色度は維持される。したがって、輝度補正により色変化を防止することができる。このように、緑副画素外向き終端画素のうち、より視認されやすい画素の輝度を相対的に低くすることで、画質の低下をより効果的に防ぐことができる。

20

#### 【0086】

緑副画素外向き終端画素の輝度補正係数kは、画素配置に応じて決定されている。一例において、輝度補正係数kは、緑副画素外向き終端画素における境界線255の曲率半径に応じて決定される。例えば、緑副画素外向き終端画素の重心から最も近い境界線255上の点が選択され、その点における境界線255の曲率半径が決定される。曲率半径が大きい程、小さい輝度補正係数kが与えられる。例えば、曲率半径の複数の範囲が定義され、範囲それぞれに輝度補正係数kが割り当てられる。

#### 【0087】

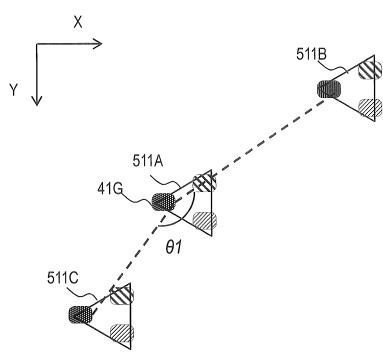

他の例において、緑副画素外向き終端画素の輝度補正係数kは、隣接する緑副画素外向き終端画素との間の角度に基づいて決定される。図7は、緑副画素外向き終端画素と、隣接する緑副画素外向き終端画素との間の角度の例を示す。終端第1種画素511Aは、隣接する終端第1種画素511B、511Cに挟まれている。

30

#### 【0088】

終端第1種画素511Aの所定位置と終端第1種画素511Bの所定位置とを結ぶ直線と、終端第1種画素511Aの所定位置と終端第1種画素511Cの所定位置とを結ぶ直線と、の間の内側角度、つまり表示領域側の角度は、<sub>1</sub>で表わされている。終端第1種画素511Aに割り当てる補正係数kは、角度<sub>1</sub>に基づいて決定される。角度<sub>1</sub>が小さい程、小さい補正係数kが割り当てられる。例えば、角度<sub>1</sub>の間の範囲が定義され、範囲それぞれに輝度補正係数kが割り当てられる。

40

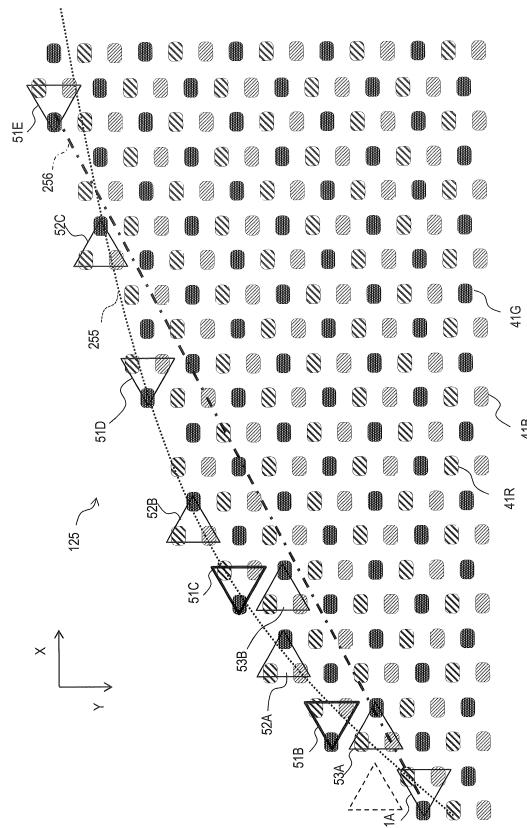

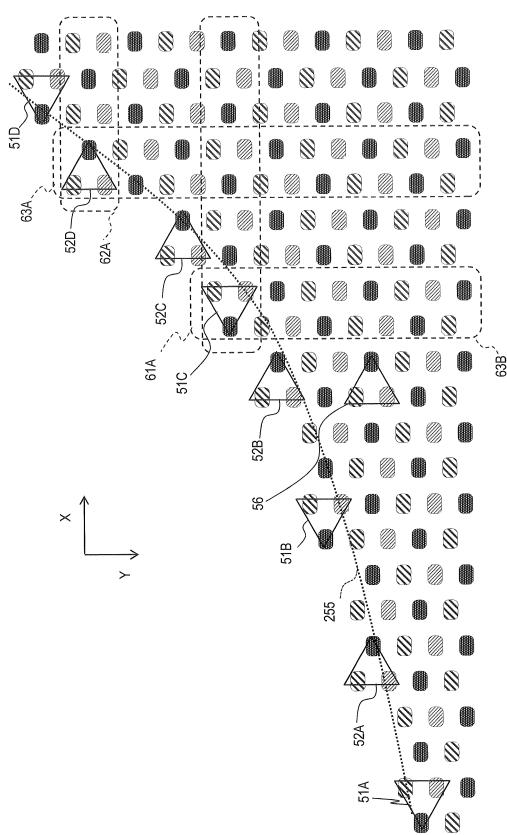

#### 【0089】

次に凹状のRコーナ部の例を説明する。図8は、デルタナプラパネルにおける画素配置の他の例を示す。図8は、表示領域125の境界(表示領域125の端)を含む一部の領域を模式的に示す。図8は、凹状の曲線的な境界255を示す部分を示す。

#### 【0090】

図8において、一つの第1種画素のみが、例として、符号51で指示されている。また、一つの第2種画素のみが、例として、符号52で指示されている。図8において、一つの第1種画素行が、例として、符号61で指示されている。また、一つの第2種画素行が、例として、符号62で指示されている。図8において、一つの画素列が、例として、符号63で指示されている。第1種画素、第2種画素、第1種画素行、第2種画素行及び画

50

素列に対して、図4を参照した説明が適用される。

#### 【0091】

図9は、凹状Rコーナ部における、終端第1種画素51A～51D、並びに、終端第2種画素52A～52Dを示す。例えば、第1種画素51Cは、第1種画素行61Aの左端に位置し、さらに、画素列63Bの上端に位置する。第2種画素52Dは、第2種画素行62Aの左端に位置し、さらに、画素列63Aの上端に位置する。

#### 【0092】

終端画素は画素行及び画素列の端に位置しているため、画素行及び画素列それぞれに沿った2方向において表示領域の外部に露出している。図9の例において、終端第1種画素51A～51D、並びに、終端第2種画素52A～52Dは、画素行の左端(X方向の反対側の端)及び画素列の上端(Y方向の反対側の端)に配置されている。終端第1種画素51A～51D、並びに、終端第2種画素52A～52Dは、左側(X方向の反対側)及び上側(Y方向の反対側)において露出している。

10

#### 【0093】

終端第1種画素51A～51Dは、それらの緑副画素41Gの側において、露出している。一方、終端第2種画素52A～52Dは、それらの緑副画素41Gと反対側(赤副画素41R及び青副画素41Bの側)において、露出している。言い換えれば、終端第1種画素51A～51Dの緑副画素41Gは、表示領域125の外側を向いており、終端第2種画素52A～52Dの緑副画素41Gは、表示領域125の内側を向いている。

20

#### 【0094】

図9に示すように、終端第1種画素51A～51Dの重心から緑副画素41Gに向かうベクトルと、表示領域境界線255の上記重心に最も近い点の外側に向かう法線ベクトルとの間の角度は、鋭角である。反対に、終端第2種画素52A～52Dの重心から緑副画素41Gに向かうベクトルと、表示領域境界線255の上記重心に最も近い点の外側に向かう法線ベクトルとの間の角度は、鈍角である。

20

#### 【0095】

OLED表示装置10は、同一の入力映像信号に対して、終端第1種画素51A～51Dの輝度を内部画素56の輝度よりも低くする。なお、終端第1種画素51A～51Dの一部の輝度のみを、内部画素56の輝度よりも低くしてもよい。OLED表示装置10は、例えば、同一の入力映像信号に対して、終端第1種画素51A～51Dの輝度を、終端第2種画素52A～52Dの輝度よりも低くする。また、OLED表示装置10は、同一の入力映像信号に対して、終端第1種画素51A～51Dの輝度を、終端画素ではない境界画素の輝度よりも低くする。

30

#### 【0096】

OLED表示装置10は、同一の入力映像信号に対して、終端第2種画素52A～52Dの輝度を、内部画素56及び終端画素ではない境界画素と同一にする。終端第2種画素52A～52Dの輝度は、内部画素56及び/又は終端画素ではない境界画素の輝度よりも低くてもよい。

30

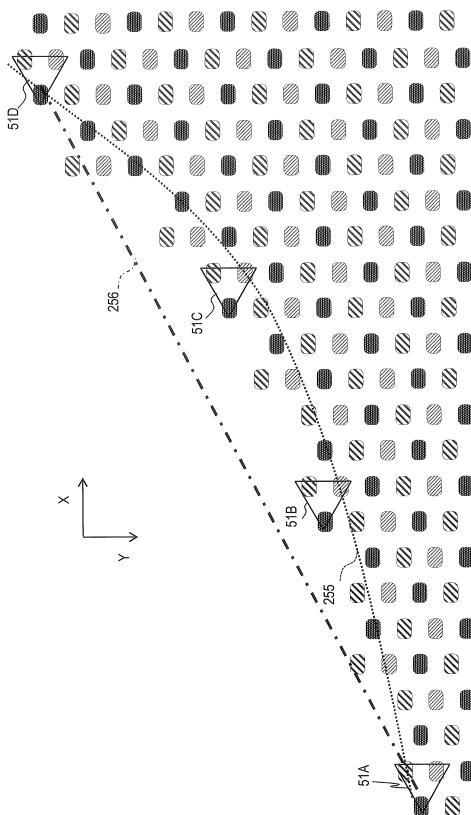

#### 【0097】

図9は、凹状のRコーナ部を示す。図10は、凹状のRコーナ部における緑副画素外向き終端画素の位置関係を示す。凹状のRコーナ部において、終端第1種画素51A及び51Dの緑副画素41Gを結ぶ線256に対して、それらの間の終端第1種画素51B及び51Cの緑副画素41Gは、内側に配置されている。

40

#### 【0098】

OLED表示装置10は、凹状のRコーナ部に含まれる緑副画素外向き画素において、異なる輝度を与えてよい。例えば、境界線255の曲率半径又は隣接緑副画素外向き終端画素との間の角度に応じて、緑副画素外向き終端画素に与える輝度補正率(補正後輝度/補正前輝度)を決定してもよい。

#### 【0099】

凹状Rコーナ部と凸状Rコーナ部の間で、緑副画素外向き終端画素に与える輝度補正率

50

が異なっていてもよい。具体的には、凸状 R コーナ部の緑副画素外向き終端画素の輝度を、凹状 R コーナ部の緑副画素外向き終端画素の輝度よりも小さくする。凸状 R コーナ部の緑副画素外向き終端画素の方が、視認されやすいからである。

#### 【 0 1 0 0 】

例えば、表示領域 1 2 5において、同一曲率半径における、凸状の R コーナ部内の緑副画素外向き終端画素の輝度補正率が、凹状の R コーナ部内の緑副画素外向き終端画素の輝度補正率以下である。例えば、表示領域 1 2 5は、輝度補正率が、同一曲率半径における凹状の R コーナ部内の緑副画素外向き終端画素の輝度補正率より小さい、凸状の R コーナ部内の緑副画素外向き終端画素を含んでもよい。

#### 【 0 1 0 1 】

例えば、表示領域 1 2 5において、同一入力映像信号に対し、凸状 R コーナ部の緑副画素外向き終端画素の最小輝度値を、凹状の R コーナ部に含まれる緑副画素外向き画素の最小輝度値よりも小さい。つまり、凸状 R コーナ部の緑副画素外向き終端画素の輝度補正率の最小値が、凹状の R コーナ部に含まれる緑副画素外向き画素の輝度補正率の最小値よりも小さい。

10

#### 【 0 1 0 2 】

または、同一入力映像信号に対して、全ての凸状 R コーナ部の緑副画素外向き終端画素の輝度の平均値は、全ての凹状の R コーナ部の緑副画素外向き終端画素の輝度の平均値よりも小さい。凸状 R コーナ部の緑副画素外向き終端画素の輝度補正率の平均値が、凹状の R コーナ部に含まれる緑副画素外向き画素の輝度補正率の平均値よりも小さい。

20

#### 【 0 1 0 3 】

以上のように、凹状の R コーナ部においても、緑副画素外向き終端画素の輝度を相対的に小さくすることで、表示品質の低下を抑制することができる。なお、本開示の輝度補正是、デルタナプラ画素配置の表示領域を含む、O L E D 表示装置と異なる任意の種類の表示装置に適用することができる。O L E D 表示装置は、副画素の発光素子への駆動電流により輝度を制御するが、液晶表示装置は、液晶に与える電圧により輝度（透過光）を制御する。

#### 【 0 1 0 4 】

以上、本発明の実施形態を説明したが、本発明が上記の実施形態に限定されるものではない。当業者であれば、上記の実施形態の各要素を、本発明の範囲において容易に変更、追加、変換することが可能である。ある実施形態の構成の一部を他の実施形態の構成に置き換えることが可能であり、ある実施形態の構成に他の実施形態の構成を加えることも可能である。

30

#### 【 符号の説明 】

#### 【 0 1 0 5 】

1 0 O L E D 表示装置、4 1 B 青副画素、4 1 G 緑副画素、4 1 R 赤副画素、4 2 副画素列、4 3 副画素行、5 1 第 1 種画素、5 2 第 2 種画素、5 6 内部画素、6 1 第 1 種画素行、6 2 第 2 種画素行、6 3 画素列、1 0 0 T F T 基板、1 1 4 カソード電極形成領域、1 2 5 表示領域、1 3 1 走査ドライバ、1 3 2 エミッションドライバ、1 3 3 保護回路、1 5 1 絶縁基板、1 5 2 表示領域、2 5 5 表示領域境界線、2 5 6 両端の緑副画素外向き終端画素を結ぶ直線、3 4 1 ガンマ変換部、3 4 2 相対輝度変換部、3 4 3 逆ガンマ変換部、3 4 4 駆動信号生成部、3 4 5 データドライバ、5 1 1 A - 5 1 1 C 緑副画素外向き終端画素

40

50

【図面】

【図 1】

【図 2】

【図 3 A】

【図 3 B】

40

30

10

20

50

【図 3 C】

【図 4】

10

20

30

40

【図 5】

【図 6】

50

【図 7】

【図 8】

10

20

【図 9】

【図 10】

30

40

50

---

フロントページの続き

(51)国際特許分類

|         |                 |         |       |

|---------|-----------------|---------|-------|

| H 0 5 B | 33/12 (2006.01) | F I     |       |

| G 0 9 F | 9/302(2006.01)  | H 0 1 L | 27/32 |

|         |                 | H 0 5 B | 33/14 |

|         |                 | H 0 5 B | 33/12 |

|         |                 | G 0 9 F | 9/302 |

(56)参考文献

特開2009-092981 (JP, A)

国際公開第2017/110721 (WO, A1)

特開2017-142368 (JP, A)

米国特許出願公開第2018/0063466 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

H 0 4 N 9 / 1 2

H 0 1 L 2 7 / 3 2

H 0 1 L 5 1 / 5 0

H 0 5 B 3 3 / 1 2

G 0 9 F 9 / 3 0 2