(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5562696号

(P5562696)

(45) 発行日 平成26年7月30日(2014.7.30)

(24) 登録日 平成26年6月20日(2014.6.20)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 613Z |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 618B |

| HO1L 27/12  | (2006.01) | HO1L 29/78 | 627D |

| HO1L 21/02  | (2006.01) | HO1L 27/12 | B    |

| HO1L 27/08  | (2006.01) | HO1L 27/08 | 331E |

請求項の数 2 (全 25 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2010-67633 (P2010-67633)    |

| (22) 出願日     | 平成22年3月24日 (2010.3.24)        |

| (65) 公開番号    | 特開2010-251729 (P2010-251729A) |

| (43) 公開日     | 平成22年11月4日 (2010.11.4)        |

| 審査請求日        | 平成25年3月5日 (2013.3.5)          |

| (31) 優先権主張番号 | 特願2009-78577 (P2009-78577)    |

| (32) 優先日     | 平成21年3月27日 (2009.3.27)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                     |

|-----------|---------------------|

| (73) 特許権者 | 000153878           |

|           | 株式会社半導体エネルギー研究所     |

|           | 神奈川県厚木市長谷398番地      |

| (72) 発明者  | 大沼 英人               |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

| 審査官       | 棚田 一也               |

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

炭化シリコン基板に第1のイオンを照射して、前記炭化シリコン基板中に第1の脆化領域を形成する工程と、

単結晶シリコン基板に第2のイオンを照射して、前記単結晶シリコン基板中に第2の脆化領域を形成する工程と、

第1の絶縁層を介して前記炭化シリコン基板と、第2の絶縁層を介して前記単結晶シリコン基板とに、ベース基板を貼り合わせる工程と、

前記第1の脆化領域において前記炭化シリコン基板を分離して、前記ベース基板上に前記第1の絶縁層を介して炭化シリコン層を形成する工程と、

前記第2の脆化領域において前記単結晶シリコン基板を分離して、前記ベース基板上に前記第2の絶縁層を介して単結晶シリコン層を形成する工程と、

前記炭化シリコン層を用いて、トランジスタ又はダイオードを形成する工程と、

前記単結晶シリコン層を用いて、トランジスタを形成する工程と、を有することを特徴とする半導体装置の作製方法。

## 【請求項 2】

請求項1において、

前記ベース基板はガラス基板であることを特徴とする半導体装置の作製方法。

## 【発明の詳細な説明】

## 【技術分野】

10

20

**【0001】**

本発明は、半導体装置及びその作製方法に関し、特に比較的大きな電力を制御する半導体装置に関する。

**【背景技術】****【0002】**

近年、集積回路を有する製品が様々な分野で多種多様に製品化され、集積回路の大規模化、多機能化が益々進んでいる。それに伴い、一つの半導体装置を構成する集積回路に、高速動作及び／又は低電圧動作が求められる回路（制御回路）が必要とされる一方で、他方では高電圧印加時の十分な信頼性（高耐圧）が求められる回路（パワー回路）が必要とされている。

10

**【0003】**

一般的に、集積回路を構成する素子は、シリコン基板を用いて形成されるが、近年、より高効率なパワー回路用の素子を作製するために、シリコンよりバンドギャップが大きい半導体基板を使用した素子が注目されている。例えば、炭化シリコン（SiC）を電力用の素子に用いることで、シリコンを用いた場合に比べ約10倍の絶縁破壊耐圧を持ち、インバータやコンバータなどの電力変換器として使用する場合に電力損失を大幅に低減できることから実用化が期待されている（例えば、特許文献1）。

**【0004】**

炭化シリコンを用いたデバイスを実用化するには、炭化シリコン基板の欠陥を低減する必要がある。一般的に、昇華再結晶法で形成される炭化シリコン基板は、マイクロパイプと呼ばれる中空貫通欠陥が形成されやすく、これがトランジスタの中に一つでも含まれると、トランジスタとして機能しなくなってしまうことが問題となっている。そのため、実用化されている単結晶シリコン基板のサイズが12インチであるのに対し、炭化シリコン基板のサイズは未だ3インチが主流である。したがって、炭化シリコン基板を用いてトランジスタ等の素子から構成される集積回路を作製する場合、集積回路の大面積化が困難となる。

20

**【0005】**

また、一般的に、集積回路を構成するそれぞれの回路（制御回路、パワー回路等）に必要な素子の特性はトレードオフの関係になりやすく、1枚の半導体基板を用いて集積回路の多機能化を図ることは困難である。

30

**【先行技術文献】****【特許文献】****【0006】**

【特許文献1】特開2003-229570号公報

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

本発明の一態様は、同一基板上に設けられる集積回路の多機能化を図ることを目的のーとする。又は、本発明の一態様は、炭化シリコン基板を用いて集積回路を形成する場合であっても、集積回路の大面積化を図ることを目的のーとする。

40

**【課題を解決するための手段】****【0008】**

本発明の一態様は、同一基板上に第1の絶縁層を介して設けられた炭化シリコン層を有する素子と、第2の絶縁層を介して設けられたシリコン層を有する素子を設け、回路の多機能化を図るものである。

**【0009】**

また、本発明の一態様は、基板上に第1の絶縁層を介して設けられた島状の炭化シリコン層と、炭化シリコン層上に設けられた第1のゲート絶縁層と、第1のゲート絶縁層上に設けられ且つ炭化シリコン層と重畠する第1の導電層とを有する第1のトランジスタと、基板上に第2の絶縁層を介して設けられた島状の単結晶シリコン層と、単結晶シリコン層上

50

に設けられた第2のゲート絶縁層と、第2のゲート絶縁層上に設けられ且つ単結晶シリコン層と重畳する第2の導電層とを有する第2のトランジスタを具備し、第1のトランジスタと第2のトランジスタが電気的に接続された半導体装置を提供する。

#### 【0010】

この場合、第1のトランジスタが有する炭化シリコン層と、第2のトランジスタが有するシリコン層は、バンドギャップと絶縁破壊電界とデバイスにした際の移動度が異なるため、第1のトランジスタと第2のトランジスタをそれぞれ用いることにより、特性の異なる回路を作製することができる。

#### 【0011】

また、第1のトランジスタと第2のトランジスタをそれぞれ特性の異なる回路に適用する場合には、第1のゲート絶縁層の膜厚を第2のゲート絶縁層の膜厚より厚くすることが好み。また、炭化シリコン層の膜厚を単結晶シリコン層の膜厚より厚く設けることができる。

10

#### 【0012】

この場合、第1のトランジスタを高い耐圧を必要とするパワー回路として機能させ、第2のトランジスタを高速動作及び／又は低電圧動作する制御回路として機能させることができる。

#### 【0013】

また、本発明の一態様は、基板上に第1の絶縁層を介して設けられた第1の電極層と、第1の電極層上に設けられた島状の炭化シリコン層と、炭化シリコン層上に設けられた第2の電極層とを有するダイオードと、基板上に第2の絶縁層を介して設けられた単結晶シリコン層と、単結晶シリコン層上に設けられたゲート絶縁層と、ゲート絶縁層上に設けられ且つ単結晶シリコン層と重畳する導電層とを有するトランジスタを具備する半導体装置を提供する。

20

#### 【0014】

また、本発明の一態様は、基板上に第1の絶縁層を介して設けられた島状の炭化シリコン層と、炭化シリコン層に設けられたp型を示す不純物領域及びn型を示す不純物領域と、p型を示す不純物領域に電気的に接続された第1の電極層と、n型を示す不純物領域に電気的に接続された第2の電極層とを有するダイオードと、基板上に第2の絶縁層を介して設けられた単結晶シリコン層と、単結晶シリコン層上に設けられたゲート絶縁層と、ゲート絶縁層上に設けられ且つ単結晶シリコン層と重畳する導電層とを有するトランジスタを具備する半導体装置を提供する。

30

#### 【0015】

また、本発明の一態様は、炭化シリコン基板に第1のイオンを照射することにより炭化シリコン基板中に第1の脆化領域を形成する工程と、単結晶シリコン基板に第2のイオンを照射することにより単結晶シリコン基板中に第2の脆化領域を形成する工程と、第1の絶縁層を介して炭化シリコン基板とベース基板とを貼り合わせる工程と、第2の絶縁層を介して単結晶シリコン基板とベース基板とを貼り合わせる工程と、第1の脆化領域において炭化シリコン基板を分離して、ベース基板上に第1の絶縁層を介して炭化シリコン層を形成する工程と、第2の脆化領域において単結晶シリコン基板を分離して、ベース基板上に第2の絶縁層を介して単結晶シリコン層を形成する工程と、炭化シリコン層をチャネル層とする第1のトランジスタ及び単結晶シリコン層をチャネル層とする第2のトランジスタを形成する工程とを有する半導体装置の作製方法を提供する。

40

#### 【0016】

また、本発明の一態様は、炭化シリコン基板上に導電層を形成する工程と、炭化シリコン基板に第1のイオンを照射することにより炭化シリコン基板中に第1の脆化領域を形成する工程と、単結晶シリコン基板に第2のイオンを照射することにより単結晶シリコン基板中に第2の脆化領域を形成する工程と、導電層及び第1の絶縁層を介して炭化シリコン基板とベース基板とを貼り合わせる工程と、第2の絶縁層を介して単結晶シリコン基板とベース基板とを貼り合わせる工程と、第1の脆化領域において炭化シリコン基板を分離して

50

、ベース基板上に導電層及び第1の絶縁層を介して炭化シリコン層を形成する工程と、第2の脆化領域において単結晶シリコン基板を分離して、ベース基板上に第2の絶縁層を介して単結晶シリコン層を形成する工程と、炭化シリコン層を有するダイオード及び単結晶シリコン層をチャネル層とするトランジスタを形成する工程とを有する半導体装置の作製方法を提供する。

#### 【0017】

また、本明細書で示すトランジスタの構成は、様々な形態をとることができ、特定の構成に限定されない。例えば、ゲート電極が2個以上のマルチゲート構造を適用することができる。マルチゲート構造にすると、チャネル領域が直列に接続されるため、複数のトランジスタが直列に接続された構成となる。マルチゲート構造により、オフ電流の低減、トランジスタの耐圧向上（信頼性の向上）を図ることができる。あるいは、マルチゲート構造により、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、電圧・電流特性の傾きをフラットにすることができます。電圧・電流特性の傾きがフラットである特性を利用すると、理想的な電流源回路や、非常に高い抵抗値をもつ能動負荷を実現することが出来る。その結果、特性のよい差動回路やカレントミラー回路を実現することが出来る。

#### 【0018】

別の例として、チャネルの上下にゲート電極が配置されている構造を適用することができる。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値の増加を図ることができる。また、チャネルの上下にゲート電極が配置されている構造にすることにより、空乏層ができやすくなるため、S値の改善を図ることができる。なお、チャネルの上下にゲート電極が配置される構成にすることにより、複数のトランジスタが並列に接続されたような構成となる。

#### 【0019】

チャネル領域の上にゲート電極が配置されている構造、チャネル領域の下にゲート電極が配置されている構造、正スタガ構造、逆スタガ構造、チャネル領域を複数の領域に分けた構造、チャネル領域を並列に接続した構造、またはチャネル領域が直列に接続する構成も適用できる。さらに、チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なっている構造も適用できる。チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なる構造にすることによって、チャネル領域の一部に電荷が溜まることにより動作が不安定になることを防ぐことができる。あるいは、LDD領域を設けた構造を適用できる。LDD領域を設けることにより、オフ電流の低減、又はトランジスタの耐圧向上（信頼性の向上）を図ることができる。あるいは、LDD領域を設けることにより、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、電圧・電流特性の傾きがフラットな特性にすることができます。

#### 【0020】

本明細書中において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法（RBS：Rutherford Backscattering Spectrometry）及び水素前方散乱法（HFS：Hydrogen Forward Scattering）を用いて測定した場合に、濃度範囲として酸素が50～70原子%、窒素が0.5～15原子%、シリコンが25～35原子%、水素が0.1～10原子%の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS及びHFSを用いて測定した場合に、濃度範囲として酸素が5～30原子%、窒素が20～55原子%、シリコンが25～35原子%、水素が10～30原子%の範囲で含まれるものという。ただし、酸化窒化シリコン又は窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

#### 【0021】

本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を

10

20

30

40

50

指し、表示装置、半導体回路および電子機器は全て半導体装置に含まれる。

【発明の効果】

【0022】

本発明の一態様によれば、同一基板上に形成された炭化シリコン層とシリコン層を用いて、高耐圧を有する素子から構成される回路と、高速動作及び／又は低電圧動作する素子から形成される回路を設けるため、集積回路の多機能化を図ることができる。

【0023】

又は、本発明の一態様によれば、同一基板に炭化シリコン基板とシリコン基板を貼り合わせて一部を残して分離することにより、同一基板上に炭化シリコン層とシリコン層を形成することができる。したがって、炭化シリコン基板を用いる場合であっても、炭化シリコン基板のサイズに限定されず集積回路の大面積化を図ることができる。10

【図面の簡単な説明】

【0024】

【図1】半導体装置の構成の一例を示す図。

【図2】半導体装置の構成の一例を示す図。

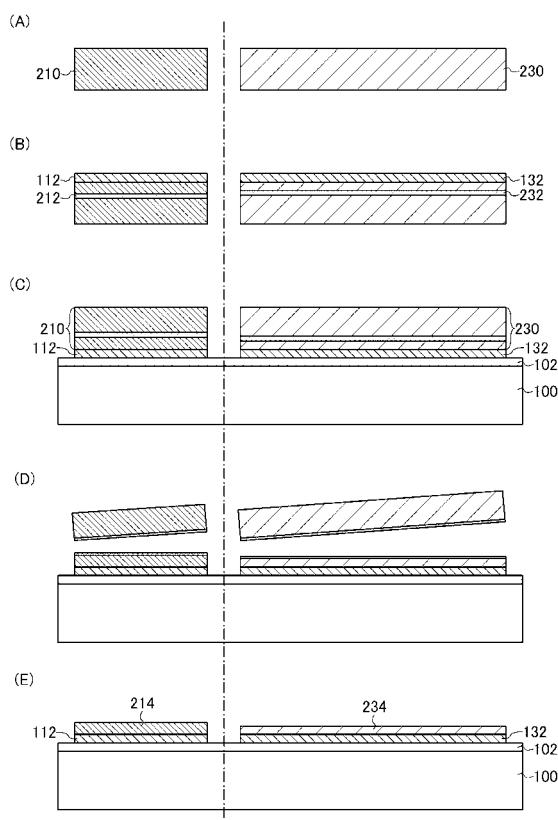

【図3】半導体装置の作製方法の一例を示す図。

【図4】半導体装置の作製方法の一例を示す図。

【図5】半導体装置の作製方法の一例を示す図。

【図6】半導体装置の作製方法の一例を示す図。

【図7】半導体装置の作製方法の一例を示す図。

【図8】半導体装置の作製方法の一例を示す図。

【図9】半導体装置の構成の一例を示す図。

【図10】半導体装置の作製方法の一例を示す図。

【図11】半導体装置の作製方法の一例を示す図。

【図12】半導体装置の作製方法の一例を示す図。

【図13】半導体装置の構成の一例を示す図。

【発明を実施するための形態】

【0025】

以下に、本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下に示す実施の形態の記載内容に限定されず、発明の趣旨から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者にとって自明である。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。また、異なる実施の形態に係る構成は、適宜組み合わせて実施することができる。また、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を用い、その繰り返しの説明は省略する。30

【0026】

(実施の形態1)

本実施の形態では、半導体装置の構成の一例について、図面を参照して説明する。

【0027】

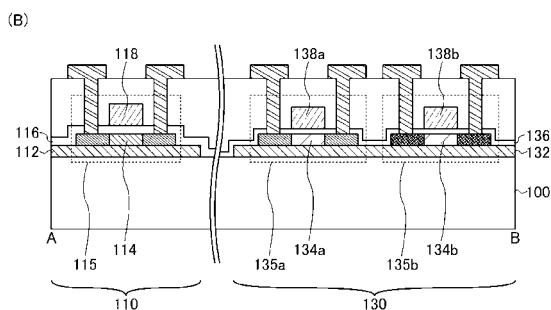

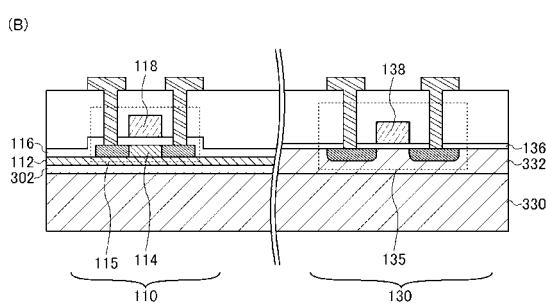

はじめに、本実施の形態で示す半導体装置について図1を用いて説明する。図1(A)は、半導体装置の平面図であり、図1(B)は、図1(A)におけるA-B間の断面の模式図を示している。40

【0028】

本実施の形態で示す半導体装置は、基板100上に、高い耐圧(高耐圧)を有する素子から構成される第1の回路群110と、高速動作及び／又は低電圧動作する素子から構成される第2の回路群130を有する構成とすることができる(図1(A)参照)。なお、本実施の形態では、半導体装置が第1の回路群110と第2の回路群130を有する集積回路から構成される場合を示すが、これに限られず、他の回路群を集積回路に加えた構成とすることができる。

【0029】

10

20

30

40

50

第1の回路群110は、シリコンよりバンドギャップが大きい半導体（例えば、炭化シリコン層）を有する素子で形成することができる。図1では、第1の回路群110に、炭化シリコン層114をチャネル層とするトランジスタ115を設ける場合を示している。この場合、半導体装置において、トランジスタ115を、高い耐圧を必要とするパワー回路として機能させることができる。

#### 【0030】

トランジスタ115は、炭化シリコン層114をチャネル層とするのであれば特定の構造に限定されない。一例として、トランジスタ115を、基板100上に絶縁層112を介して設けられた島状の炭化シリコン層114と、炭化シリコン層114上に設けられた絶縁層116と、絶縁層116上に設けられ且つ炭化シリコン層114と重畠する導電層118とを有する構成とすることができます（図1（B）参照）。この場合、トランジスタ115において、絶縁層116はゲート絶縁層として機能し、導電層118はゲート電極として機能する。

10

#### 【0031】

第2の回路群130は、シリコンを有する素子で形成することができる。図1では、第2の回路群130に、シリコン層134aをチャネル層とするトランジスタ135a及びシリコン層134bをチャネル層とするトランジスタ135bを設ける場合を示している。この場合、半導体装置において、トランジスタ135a及びトランジスタ135bを高速動作及び／又は低電圧動作する制御回路として機能させることができます。

#### 【0032】

20

トランジスタ135a、トランジスタ135bは、それぞれシリコン層134a、シリコン層134bをチャネル層とするのであれば特定の構造に限定されない。一例として、トランジスタ135aを、基板100上に絶縁層132を介して設けられた島状のシリコン層134aと、シリコン層134a上に設けられた絶縁層136と、絶縁層136上に設けられた導電層138aとを有する構成とすることができます。また、トランジスタ135bを、基板100上に絶縁層132を介して設けられた島状のシリコン層134bと、シリコン層134b上に設けられた絶縁層136と、絶縁層136上に設けられた導電層138bとを有する構成とすることができます（図1（B）参照）。この場合、トランジスタ135a、135bにおいて、絶縁層136はゲート絶縁層として機能し、導電層138a、138bはゲート電極として機能する。

30

#### 【0033】

なお、図1では、トランジスタ115、トランジスタ135aをn型で設け、トランジスタ135bをp型で設けた場合を示しているが、これに限られない。トランジスタ115をp型で設けてもよいし、第1の回路群110にn型とp型のトランジスタを設けてもよい。また、トランジスタ135a、135bの双方をn型又はp型で設けてもよい。ここで、n型又はp型とは、トランジスタの動作状態のチャネルがn型又はp型であることを指す。

#### 【0034】

図1において、同一の基板（ここでは、基板100）上に設けられた第1の回路群110に設けられた素子（ここでは、トランジスタ115）と、第2の回路群130に設けられた素子（ここでは、トランジスタ135a、トランジスタ135b）とを電気的に接続した構成とすることができます。電気的な接続は、それぞれのトランジスタのソース配線又はドレイン配線を用いて行うことができる。

40

#### 【0035】

また、図1（B）に示すように、絶縁層136の膜厚を絶縁層116の膜厚より薄く設けることができる。この場合、第1の回路群110に設けられたトランジスタ115の耐圧を向上させ、第2の回路群130に設けられたトランジスタ135a、135bの高速動作及び／又は低消費電力化を行うことができ、集積回路の高効率化を図ることができる。

#### 【0036】

もちろん、炭化シリコン層114を用いることにより、トランジスタ115の耐圧を向上

50

できる場合には、絶縁層 136 と絶縁層 116 を同一の材料を用いて同等の膜厚で形成してもよい。この場合、絶縁層 116 と絶縁層 136 を同時に形成することができるため、作製工程を簡略化すると共に低コスト化を図ることができる。

#### 【0037】

図 1 に示すように、同一の基板 100 上に、炭化シリコン層をチャネル層とするトランジスタ（ここでは、トランジスタ 115）と、シリコン層をチャネル層とするトランジスタ（ここでは、トランジスタ 135a、135b）とを設けることにより、集積回路の多機能化を図ることができる。

#### 【0038】

また、同一の基板 100 上に、炭化シリコン層を有する素子から構成されるパワー回路と、シリコン層を有する素子から構成される制御回路を設けることにより、異なる半導体基板上に制御回路とパワー回路を作製して電気的に接続させる場合と比較して、半導体装置の小型化を図ることができる。

#### 【0039】

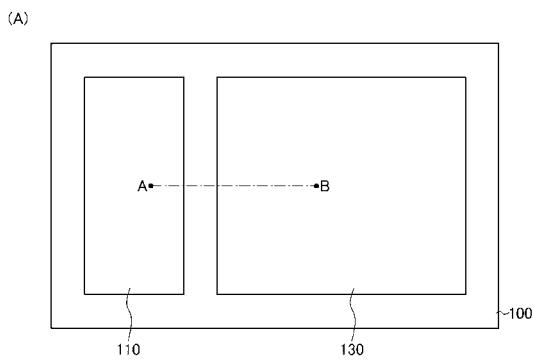

また、図 1 に示す構造において、高耐圧化の観点からは、第 1 の回路群 110 を構成するトランジスタ 115 のチャネル層（ここでは、炭化シリコン層 114）の膜厚を、第 2 の回路群 130 を構成するトランジスタ 135a、135b のシリコン層 134a、134b の膜厚より厚くなるように設けることが好ましい（図 2（A）参照）。

#### 【0040】

また、チャネル層を厚くすることにより、埋め込みチャネル型トランジスタの形成が容易になり、さらにオン電流を増加させることができる。

#### 【0041】

なお、本実施の形態で示す半導体装置において、第 1 の回路群 110、第 2 の回路群 130 に設ける素子はトランジスタに限られない。例えば、第 1 の回路群 110 にダイオード 120 を設けた構成とができる（図 2（B）参照）。

#### 【0042】

ダイオード 120 は、炭化シリコン層 114 を有するのであれば特定の構造に限定されない。一例として、ダイオード 120 を、基板 100 上に絶縁層 112 を介して設けられた第 1 の電極層 121 と、第 1 の電極層 121 上に設けられた炭化シリコン層 114 と、炭化シリコン層 114 上に設けられた第 2 の電極層 122 とを有する構成とができる。

#### 【0043】

この場合、ダイオード 120 において、第 1 の電極層 121 を炭化シリコン層 114 とオーミック接続した電極として機能させ、第 2 の電極層 122 を炭化シリコン層 114 とショットキー接合を形成する電極として機能させることができる。

#### 【0044】

なお、図 2（B）では、ダイオード 120 として、炭化シリコン層 114 と第 2 の電極層 122 の接触する領域におけるショットキー接合を利用したショットキーバリアダイオードを用いる場合を示したが、これに限られない。ダイオード 120 として、P N 接合ダイオードを用いてもよい。

#### 【0045】

このように、同一の基板 100 上に、炭化シリコン層を有するダイオード（ここでは、ダイオード 120）と、シリコン層をチャネル層とするトランジスタ（ここでは、トランジスタ 135a、135b）を設けることにより、同一基板上で回路の多機能化を図ることができる。

#### 【0046】

（実施の形態 2）

本実施の形態では、上記実施の形態 1 で示した半導体装置の作製方法の一例について、図面を参照して説明する。

#### 【0047】

10

20

30

40

50

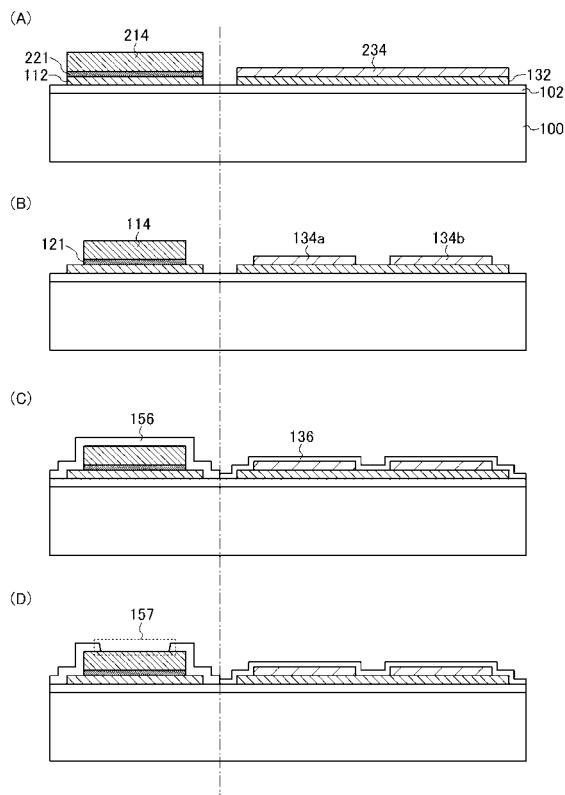

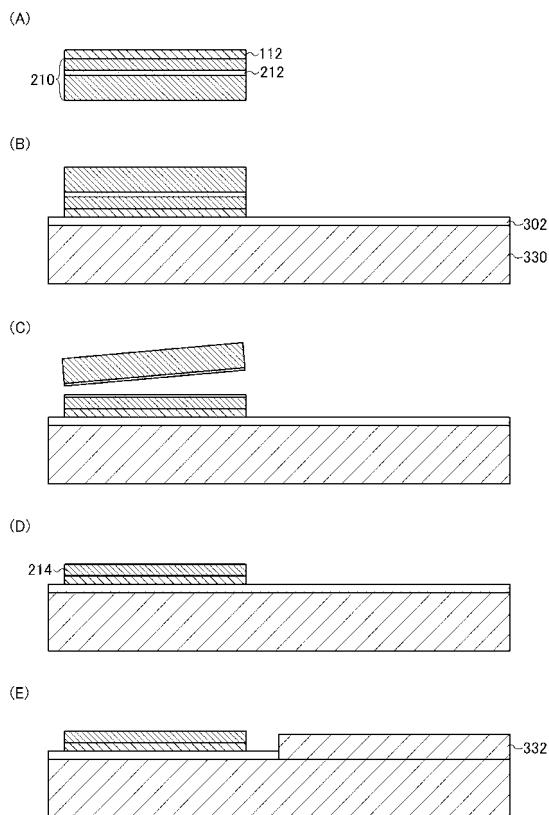

はじめに、絶縁層上にバンドギャップが異なる複数の半導体層を有する基板の作製方法について図3を参照して説明する。

#### 【0048】

まず、バンドギャップが異なる半導体基板を準備する。ここでは、炭化シリコン基板210と、シリコン基板230を準備する(図3(A)参照)。

#### 【0049】

炭化シリコン基板210は、市販の単結晶炭化シリコン基板を用いることができる。市販の単結晶炭化シリコン基板としては、直径3インチ(75mm)サイズの円形のものが代表的である。なお、炭化シリコン基板210の形状は円形に限らず、矩形状等に加工して用いることも可能である。また、炭化シリコン基板210に代えて、GaN基板等を用いてもよい。他にも、シリコン基板上に炭化シリコン層が設けられた基板を用いてもよい。シリコン基板上の炭化シリコン層は、シリコン基板への炭化処理、シリコン基板上への炭化シリコンのエピタキシャル成長により形成することができる。

#### 【0050】

シリコン基板230は、市販の単結晶シリコン基板を用いることができる。市販の単結晶シリコン基板としては、直径5インチ(125mm)、直径6インチ(150mm)、直径8インチ(200mm)、直径12インチ(300mm)、直径16インチ(400mm)サイズの円形のものが代表的である。なお、シリコン基板230の形状は円形に限らず、矩形状等に加工して用いることも可能である。

#### 【0051】

次に、炭化シリコン基板210上に絶縁層112を形成すると共に、炭化シリコン基板210の表面から所定の深さに結晶構造が損傷された脆化領域212を形成する。同様に、シリコン基板230上に絶縁層132を形成すると共に、シリコン基板230の表面から所定の深さに結晶構造が損傷された脆化領域232を形成する(図3(B)参照)。

#### 【0052】

絶縁層112、絶縁層132は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜等の絶縁層を用いて、単層又は積層させて形成することができる。これらの膜は、熱酸化法、CVD法又はスパッタリング法等を用いて形成することができる。

#### 【0053】

CVD法を用いて絶縁層112、絶縁層132を形成する場合には、テトラエトキシシラン(略称;TEOS:化学式Si(OCH<sub>3</sub>)<sub>4</sub>)等の有機シランを用いて作製される酸化シリコン膜を用いることにより、絶縁層112、絶縁層132の表面を平坦化することができる。

#### 【0054】

熱酸化処理を用いて絶縁層112、絶縁層132を形成する場合には、酸化性雰囲気中にハロゲン(フッ素、塩素等)を添加して行うことができる。

#### 【0055】

また、絶縁層112、絶縁層132として同じ材料を用いてもよい。例えば、絶縁層112及び絶縁層132として、熱酸化法により形成された酸化シリコン膜を用いることができる。この場合、炭化シリコン基板210とシリコン基板230を絶縁層112、絶縁層132を介してベース基板と貼り合わせる際に、同様の条件で貼り合わせを行うことが可能となる。

#### 【0056】

脆化領域212は、イオンを炭化シリコン基板210に添加することで形成することができる。例えば、イオン注入法又はイオンドーピング法を用いて、運動エネルギーを有する水素イオンを炭化シリコン基板210に照射することで、炭化シリコン基板210の所定の深さの領域に水素イオンと、水素イオンに起因する欠陥とが導入され、脆化領域212を形成することができる。また、脆化領域232も同様に形成することができる。

#### 【0057】

10

20

30

40

50

イオンを添加する領域の深さを制御することにより、後に分離される炭化シリコン層の膜厚、シリコン層の膜厚を制御することができる。また、炭化シリコン基板 210、シリコン基板 230 を加熱しながらイオンを添加してもよい。

#### 【0058】

炭化シリコン基板 210、シリコン基板 230 に添加する水素イオンとしては、 $H^+$ 、 $H_2^+$ 、 $H_3^+$  のうちいずれか一種類又は複数種類を用いることができる。また、炭化シリコン基板 210、シリコン基板 230 に添加するイオンは、水素イオンに限られず、他のイオン（例えば、ヘリウムイオン等）を用いてもよい。

#### 【0059】

図3(B)において、脆化領域 212、脆化領域 232 は、絶縁層 112、絶縁層 132 を設ける前に形成してもよいし、絶縁層 112、絶縁層 132 を設けた後に形成してもよい。なお、イオンの添加に伴う炭化シリコン基板 210、シリコン基板 230 の表面の損傷を低減する観点からは、絶縁層 112、絶縁層 132 を設けた後に脆化領域 212、脆化領域 232 を形成することが好ましい。10

#### 【0060】

次に、ベース基板 100 を準備し、炭化シリコン基板 210、シリコン基板 230 をそれぞれ絶縁層 112、絶縁層 132 を介してベース基板 100 に貼り合わせる（図3(C) 参照）。

#### 【0061】

ベース基板 100 としては、ガラス基板、セラミック基板、石英基板やサファイア基板等の絶縁体である基板、シリコン等の半導体である基板、金属やステンレスなどの導電体である基板などを用いることもできる。また、本実施の形態の作製工程における処理温度に耐えうるのであればベース基板 100 としてプラスチック基板を用いてもよい。20

#### 【0062】

また、ベース基板 100 の表面に絶縁層を形成してもよい。絶縁層を構成する材料としては、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコン、酸化ゲルマニウム、窒化ゲルマニウム、酸化窒化ゲルマニウム、窒化酸化ゲルマニウムなどの、珪素またはゲルマニウムを組成に含む絶縁材料を用いることができる。また、酸化アルミニウム、酸化タンタル、酸化ハフニウムなどの金属の酸化物、窒化アルミニウムなどの金属の窒化物、酸化窒化アルミニウムなどの金属の酸化窒化物、窒化酸化アルミニウムなどの金属の窒化酸化物を用いることもできる。30

#### 【0063】

ここでは、表面に絶縁層 102 が形成されたベース基板 100 を用いる場合を示している。そのため、ベース基板 100 と炭化シリコン基板 210 の貼り合わせでは絶縁層 112 と絶縁層 102 が接触し、ベース基板 100 とシリコン基板 230 の貼り合わせでは絶縁層 132 と絶縁層 102 が接触する。

#### 【0064】

次に、脆化領域 212 において炭化シリコン基板 210 を分離すると共に、脆化領域 232 においてシリコン基板 230 を分離する（図3(D) 参照）。

#### 【0065】

その結果、ベース基板 100 上に、絶縁層 112（及び絶縁層 102）を介して設けられた炭化シリコン層 214 と、絶縁層 132（及び絶縁層 102）を介して設けられたシリコン層 234 を有する基板（ハイブリッドSOI基板）が得られる（図3(E) 参照）。40

#### 【0066】

図3(D)において、炭化シリコン基板 210、シリコン基板 230 を分離する前に熱処理を行うことが好ましい。熱処理を行うことで、温度上昇によって脆化領域 212、脆化領域 232 に形成されている微小な孔に体積変化が起こり、脆化領域 212、脆化領域 232 に亀裂が生じるので、容易に脆化領域 212、脆化領域 232 に沿って炭化シリコン基板 210、シリコン基板 230 を分離することができる。

#### 【0067】

熱処理は、拡散炉、抵抗加熱炉などの加熱炉、RTA（瞬間熱アニール、Rapid Thermal Anneal）装置、マイクロ波加熱装置などを用いることができる。例えば、RTA装置を用いる場合、加熱温度550以上730以下、処理時間0.5分以上60分以内で行うことができる。また、ここで熱処理の温度は、ベース基板100の歪み点を越えない温度で行えばよい。

#### 【0068】

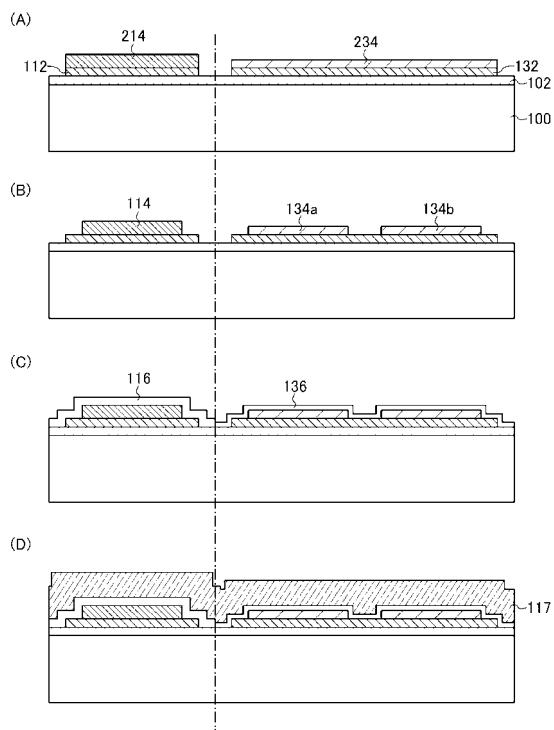

次に、図3の工程で得られた基板を用いた半導体装置の作製方法の一例について図面を参照して説明する。

#### 【0069】

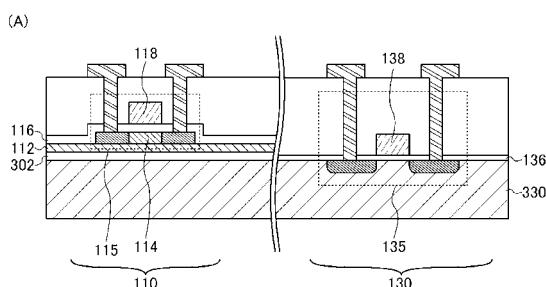

まず、ベース基板100上に絶縁層112を介して設けられた炭化シリコン層214と、絶縁層132を介して設けられたシリコン層234を有する基板を準備する（図4（A）参照）。なお、図4（A）は、図3（E）に対応している。

#### 【0070】

また、ここでは、炭化シリコン層214の膜厚をシリコン層234の膜厚より大きくする場合を示すが、これに限られない。

#### 【0071】

次に、炭化シリコン層214をエッティングして素子分離を行い、島状の炭化シリコン層114を形成する。また、シリコン層234をエッティングして素子分離を行い、島状のシリコン層134a、134bを形成する（図4（B）参照）。

#### 【0072】

炭化シリコン層214、シリコン層234のエッティングを行う前に、TFTのしきい値電圧を制御するために、ホウ素、アルミニウム、ガリウムなどのp型不純物元素、またはリン、ヒ素などのn型不純物元素を炭化シリコン層214、シリコン層234の一方又は両方に添加してもよい。例えば、nチャネル型TFTが形成される領域にホウ素、アルミニウム、ガリウム等のp型不純物元素を添加し、pチャネル型TFTが形成される領域にリン、ヒ素等のn型不純物元素を添加する。

#### 【0073】

次に、炭化シリコン層114上に絶縁層116を形成し、シリコン層134a、134b上に絶縁層136を形成する（図4（C）参照）。絶縁層116は、炭化シリコン層114をチャネル層とするトランジスタのゲート絶縁層として機能し、絶縁層136は、シリコン層134a、134bをチャネル層とするトランジスタのゲート絶縁層として機能する。

#### 【0074】

絶縁層116、絶縁層136は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、酸化ハフニウム膜、酸化アルミニウム膜、酸化タンタル膜等の絶縁層を用いて、単層又は積層させて形成することができる。これらの膜は、CVD法、スパッタリング法等を用いて形成することができる。

#### 【0075】

また、プラズマ処理により炭化シリコン層114、シリコン層134a、134bの表面を酸化又は窒化させて絶縁層116、絶縁層136を形成してもよい。

#### 【0076】

プラズマ処理は、例えば、ヘリウム、アルゴン、クリプトン、キセノンなどの希ガスと、酸素、酸化窒素、アンモニア、窒素、水素などガスの混合ガスを用いて行う。この場合、プラズマの励起をマイクロ波の導入により行うことで、低電子温度で高密度のプラズマを生成することができる。このような高密度のプラズマで生成された酸素ラジカル（OHラジカルを含む場合もある）や窒素ラジカル（NHラジカルを含む場合もある）によって、炭化シリコン層114、シリコン層134a、134bの表面を酸化または窒化することにより、1nm以上20nm以下、望ましくは2nm以上10nm以下の絶縁層を形成することができる。

#### 【0077】

10

20

30

40

50

上述したプラズマ処理による炭化シリコン層 114、シリコン層 134a、134b の酸化または窒化は固相反応であるため、絶縁層 116 と炭化シリコン層 114 の界面準位密度、絶縁層 136 とシリコン層 134a、134b の界面準位密度をきわめて低くすることができる。また、プラズマ処理により炭化シリコン層 114、シリコン層 134a、134b を直接酸化または窒化することで、形成される絶縁層の厚さのばらつきを抑えることが出来る。

#### 【0078】

また、炭化シリコン層 114、シリコン層 134a、134b を熱酸化させることで、絶縁層 116、絶縁層 136 を形成してもよい。熱酸化を用いる場合には、ベース基板 100 として、耐熱性の高い基板を用いることが好ましい。

10

#### 【0079】

本実施の形態では、炭化シリコン層 114 上に形成される絶縁層 116 の膜厚を、シリコン層 134a、134b 上に形成される絶縁層 136 の膜厚より厚く形成する場合を示している。もちろん、絶縁層 116 と絶縁層 136 を同一の材料を用いて設けてもよい。

#### 【0080】

次に、絶縁層 116、絶縁層 136 上に導電層 117 を形成する（図 4（D）参照）。

#### 【0081】

導電層 117 は、タンタル（Ta）、タンゲステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ニオブ（Nb）等の材料を用いて、単層又は積層させて形成することができる。また、上記金属を主成分とする合金材料を用いてもよいし、上記金属を含む化合物を用いても良い。又は、半導体に導電性を付与する不純物元素をドーピングした多結晶珪素等の半導体材料を用いて形成してもよい。これらの材料は、CVD 法、スパッタリング法等を用いて形成することができる。

20

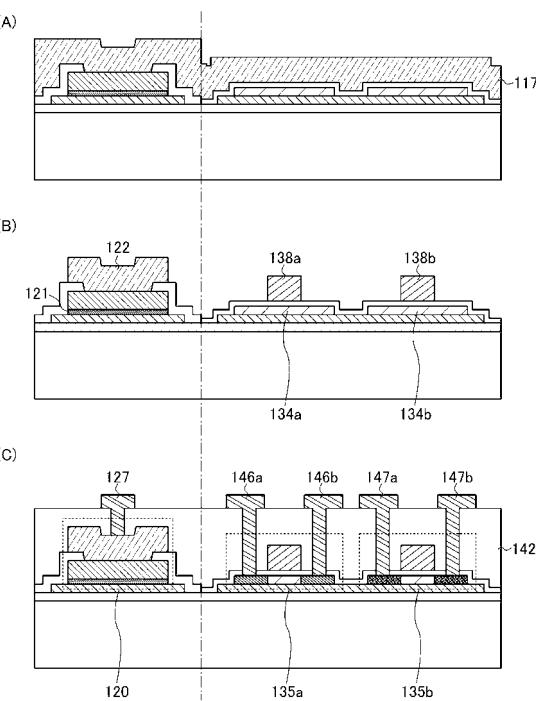

#### 【0082】

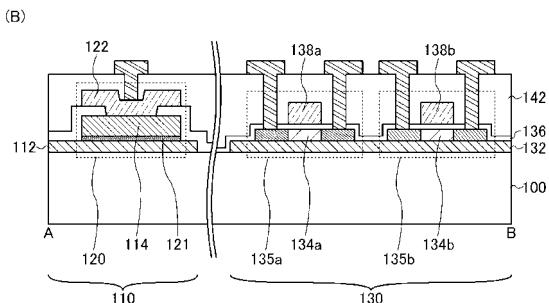

次に、導電層 117 をエッチングして、導電層 118、導電層 138a、導電層 138b を形成する（図 5（A）参照）。

#### 【0083】

導電層 118 は、炭化シリコン層 114 をチャネル層とするトランジスタのゲート電極として機能する。導電層 138a は、シリコン層 134a をチャネル層とするトランジスタのゲート電極として機能し、導電層 138b は、シリコン層 134b をチャネル層とするトランジスタのゲート電極として機能する。

30

#### 【0084】

次に、炭化シリコン層 114、シリコン層 134a、134b に不純物元素を添加することにより、炭化シリコン層 114 に不純物領域 124b、124c を形成し、シリコン層 134a に不純物領域 144b、144c を形成し、シリコン層 134b に不純物領域 145b、145c を形成する（図 5（B）参照）。

#### 【0085】

不純物領域 124b、124c は、トランジスタ 115 のソース領域又はドレイン領域として機能し、不純物領域 124b と不純物領域 124c の間にチャネル形成領域 124a が形成される。また、不純物領域 144b、144c は、トランジスタ 135a のソース領域又はドレイン領域として機能し、不純物領域 144b と不純物領域 144c の間にチャネル形成領域 144a が形成される。また、不純物領域 145b、145c は、トランジスタ 135b のソース領域又はドレイン領域として機能し、不純物領域 145b と不純物領域 145c の間にチャネル形成領域 145a が形成される。

40

#### 【0086】

不純物元素としては、ホウ素、アルミニウム、ガリウム等の p 型を付与する不純物元素、又はリン、ヒ素等の n 型を付与する不純物元素を添加すればよい。

#### 【0087】

ここでは、一例として、炭化シリコン層 114、シリコン層 134a に n 型を付与する不純物元素（例えば、リン）を添加し、シリコン層 134b に p 型を付与する不純物元素（

50

例えば、ホウ素)を添加する場合を示している。

**【0088】**

なお、不純物元素を添加した後、不純物領域の活性化(及び結晶性の回復)のための加熱処理を行うことが好ましい。

**【0089】**

一般的に、炭化シリコンにおいては、結晶中の不純物の拡散係数が低いことから、炭化シリコン層に形成された不純物領域の活性化のためにはシリコン層に形成された不純物領域の活性化と比較して高温(1500以上)の熱処理が必要となる。そのため、本実施の形態では、炭化シリコン層114に設けられた不純物領域124b、124cの活性化としてレーザー光を用いることが好ましい。具体的なレーザーの種類としては、KrFエキシマレーザー(波長248nm)、ArFエキシマレーザー(波長193nm)などを用いることができる。10

**【0090】**

例えば、300～700の熱処理を行った後、炭化シリコン層114にレーザー光を照射する。この場合、熱処理を行うことにより、シリコン層134a、134bに形成された不純物領域(ここでは、不純物領域144b、144c、不純物領域145b、145c)の活性化を行い、レーザー光の照射により炭化シリコン層114に形成された不純物領域(ここでは、不純物領域124b、124c)の活性化を行うことができる。また、炭化シリコン層114にレーザー光を照射した後に、300～700の熱処理を行ってもよい。熱処理を行なながらレーザー光を照射することにより、レーザー光の吸収率が高まるので、効果的である。20

**【0091】**

このように、同一基板上に設けられた炭化シリコン層とシリコン層を用いてトランジスタを作製する場合であっても、熱処理とレーザー光の照射を組み合わせて行うことにより、シリコン層に設けられた不純物領域と炭化シリコン層に設けられた不純物領域の活性化を十分に行うことができる。

**【0092】**

また、熱処理とレーザー光の照射を組み合わせて、シリコン層に設けられた不純物領域と炭化シリコン層に設けられた不純物領域の活性化を行うことにより、活性化の熱処理を低温で行なうことが可能となる。その結果、ベース基板100として耐熱性が低い基板を用いることができる。また、レーザー光の照射を全面に行なうのではなく、炭化シリコン層114の形成領域に選択的に照射することによって、スループットを向上することができる。30

**【0093】**

レーザー光の照射において、ベース基板100としてガラスやプラスチック等の透光性を有する基板を用いる場合には、ベース基板100の裏面(トランジスタが形成される面と反対側の面)側からレーザー光を照射することにより、炭化シリコン層114の活性化を行うことができる。

**【0094】**

なお、ベース基板100として、耐熱性を有する基板(シリコン基板、石英基板、金属基板等)を用いる場合には、不純物領域の活性化における熱処理を400～1200(一例として、800)でおこなってもよい。40

**【0095】**

また、図5(B)に示すトランジスタ115、135a、135bの構造において、LD(DLightly Doped Drain)領域として機能する低濃度不純物領域を設けてもよい。例えば、チャネル形成領域124aと不純物領域124b、124cとの間に当該不純物領域124b、124cより低濃度の不純物元素が含まれる領域を設けてもよい。また、チャネル形成領域144aと不純物領域144b、144cとの間に低濃度不純物領域を設けてもよいし、チャネル形成領域145aと不純物領域145b、145cとの間に低濃度不純物領域を設けてもよい。

**【0096】**

次に、トランジスタ 115、135a、135b を覆うように絶縁層 142 を形成した後、当該絶縁層 142 上に、トランジスタ 115 のソース電極又はドレイン電極として機能する導電層 126a、126b、トランジスタ 135a のソース電極又はドレイン電極として機能する導電層 146a、146b、トランジスタ 135b のソース電極又はドレイン電極として機能する導電層 147a、147b を形成する（図 5（C）参照）。

#### 【0097】

絶縁層 142 としては、酸化シリコン、酸化窒化シリコン等の無機絶縁材料、又はポリイミド、アクリルなどの有機絶縁材料を用いて形成することができる。また、絶縁層 142 は、単層構造としてもよいし、複数の絶縁層を積層させて積層構造としてもよい。

#### 【0098】

導電層 126a、126b、導電層 146a、146b、導電層 147a、147b としては、スパッタ法や真空蒸着法等を用いて、アルミニウム（Al）、銅（Cu）、チタン（Ti）、タンタル（Ta）、タンゲステン（W）、モリブデン（Mo）、クロム（Cr）、ネオジム（Nd）、スカンジウム（Sc）から選ばれた元素を含む金属、上述の元素を成分とする合金又は上述の元素を成分とする窒化物等からなる材料を用いて、単層又は積層させて形成することができる。

#### 【0099】

本実施の形態で示した作製工程を用いることにより、炭化シリコン層をチャネル層とするトランジスタと、シリコン層をチャネル層とするトランジスタを同一基板上に有する半導体装置を作製することができる。

10

20

#### 【0100】

本実施の形態で示すように、同一基板上に炭化シリコン基板とシリコン基板を貼り合わせて一部を残して分離することにより、同一基板上に炭化シリコン層を有する素子とシリコン層を有する素子から構成される集積回路を形成することができる。このように、炭化シリコン基板を用いて集積回路を形成する場合であっても、他の基板上に炭化シリコン基板の一部を分離して炭化シリコン層を形成することにより、炭化シリコン基板のサイズに影響されずに集積回路の高集積化または大規模化を図ることができる。

#### 【0101】

また、炭化シリコン基板の一部を分離して炭化シリコン層が形成される基板上に、シリコン基板の一部を分離してシリコン層を設け、当該炭化シリコン層とシリコン層を有する基板を用いて素子を形成することによって、集積回路の高集積化または大規模化と共に多機能化を図ることができる。

30

#### 【0102】

また、同一基板上に炭化シリコン基板とシリコン基板を貼り合わせて一部を残して分離することにより、同一基板上に炭化シリコン層とシリコン層を形成することにより、炭化シリコン層を有するトランジスタとシリコン層を有するトランジスタを同一のプロセスで作製することが可能となり、作製工程を簡略化することができる。

#### 【0103】

また、炭化シリコン層を有するトランジスタと、シリコン層を有するトランジスタにおいて、ゲート電極として機能する導電層、ソース電極又はドレイン電極として機能する導電層、層間絶縁膜として機能する絶縁層等を同一のプロセスで設けることにより、作製工程を簡略化すると共に低コスト化を図ることができる。

40

#### 【0104】

なお、本実施の形態では、ベース基板 100 に炭化シリコン基板 210 とシリコン基板 230 を貼り合わせて分離することにより、ベース基板 100 上に炭化シリコン層 214 とシリコン層 234 を形成した後にトランジスタ等の素子を形成する場合をしめしたが、これに限られない。

#### 【0105】

例えば、ベース基板 100 上に炭化シリコン層 214 のみ形成し、当該炭化シリコン層 214 を用いて素子を形成した後にベース基板 100 にシリコン基板 230 を貼り合わせて

50

もよい。また、ベース基板 100 上にシリコン層 234 のみ形成し、当該シリコン層 234 を用いて素子を形成した後にベース基板 100 に炭化シリコン基板 210 を貼り合わせてもよい。つまり、ベース基板 100 への炭化シリコン基板 210 の貼り合わせとシリコン基板 230 の貼り合わせは同時に行わなくてもよい。また、炭化シリコン層 214 とシリコン層 234 は、同一平面上に形成しなくてもよい。

#### 【0106】

また、本実施の形態では、ベース基板 100 上にそれぞれ 1 枚ずつ炭化シリコン基板とシリコン基板を貼り合わせる場合を示したが、これに限られない。例えば、ベース基板 100 に炭化シリコン基板を複数枚貼り合わせてもよい。

#### 【0107】

##### (実施の形態 3)

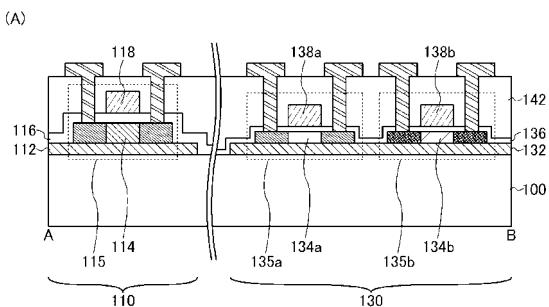

本実施の形態では、上記実施の形態 1 で示した半導体装置の作製方法の一例について、図面を参照して説明する。具体的には、上記図 2 (B) に示した半導体装置の作製方法の一例について説明する。

#### 【0108】

また、本実施の形態で示す作製工程（適用できる材料等）は多くの部分で上記実施の形態 2 と共に通している。したがって、以下においては、重複する部分の説明は省略し、異なる点について詳細に説明する。

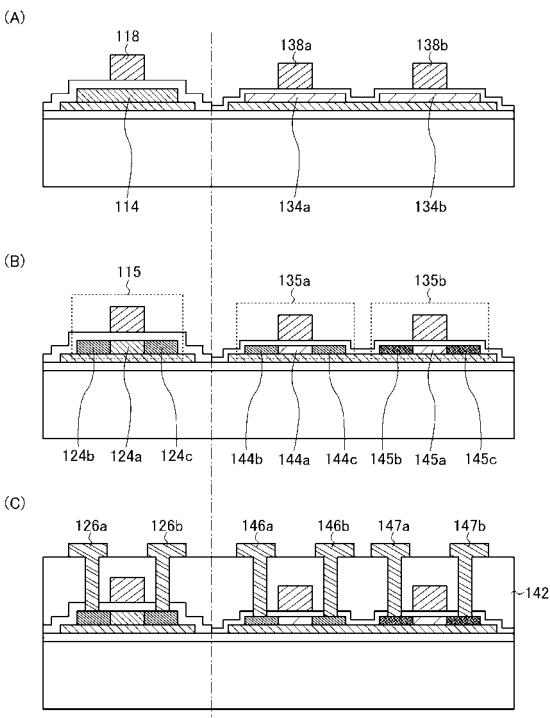

#### 【0109】

はじめに、絶縁層上にバンドギャップが異なる複数の半導体層を有する基板の作製方法について図 6 を参照して説明する。

#### 【0110】

まず、バンドギャップが異なる半導体基板を準備する。ここでは、炭化シリコン基板 210 と、シリコン基板 230 を準備し、炭化シリコン基板 210 上に導電層 221 を形成する。（図 6 (A) 参照）。炭化シリコン基板 210 としては、P 型基板又はN型基板を用いることができる。

#### 【0111】

導電層 221 としては、ニッケル (Ni)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al)、白金 (Pt) から選ばれた元素を含む金属又は上述の元素を成分とする合金からなる材料を用いて、単層又は積層させて形成することができる。

#### 【0112】

なお、炭化シリコン基板 210 とこれらの材料からなる導電層をオーミック接続させる場合には、導電層 221 を形成した後、熱処理（一例として、900 ~ 1000）を行うことが好ましい。また、あらかじめ炭化シリコン基板 210 の表面に不純物元素を添加してもよい。

#### 【0113】

次に、導電層 221 上に絶縁層 112 を形成すると共に、炭化シリコン基板 210 の所定の深さに結晶構造が損傷された脆化領域 212 を形成する。同様に、シリコン基板 230 上に絶縁層 132 を形成すると共に、シリコン基板 230 の所定の深さに結晶構造が損傷された脆化領域 232 を形成する（図 6 (B) 参照）。

#### 【0114】

次に、ベース基板 100 を準備し、炭化シリコン基板 210、シリコン基板 230 をそれぞれ絶縁層 112、絶縁層 132 を介してベース基板 100 に貼り合わせる（図 6 (C) 参照）。

#### 【0115】

ここでは、絶縁層 102 が形成されたベース基板 100 を用いる場合を示している。そのため、ベース基板 100 と炭化シリコン基板 210 の貼り合わせでは絶縁層 112 と絶縁層 102 が接触し、ベース基板 100 とシリコン基板 230 の貼り合わせでは絶縁層 132 と絶縁層 102 が接触する。

#### 【0116】

10

20

30

40

50

次に、脆化領域 212において炭化シリコン基板 210を分離すると共に、脆化領域 232においてシリコン基板 230を分離する(図6(D)参照)。

#### 【0117】

その結果、ベース基板 100上に、絶縁層 112(及び絶縁層 102)と導電層 221を介して設けられた炭化シリコン層 214と、絶縁層 132(及び絶縁層 102)を介して設けられたシリコン層 234を有する基板(ハイブリッドSOI基板)が得られる(図6(E)参照)。

#### 【0118】

次に、図6の工程で得られた基板を用いた半導体装置の作製方法の一例について図面を参考して説明する。

10

#### 【0119】

まず、ベース基板 100上に絶縁層 112を介して設けられた炭化シリコン層 214と、絶縁層 132を介して設けられたシリコン層 234を有する基板を準備する(図7(A)参照)。なお、図7(A)は、図6(E)に対応している。

#### 【0120】

また、本実施の形態では、炭化シリコン層 214の膜厚をシリコン層 234の膜厚より大きくする場合について示すが、これに限られない。

#### 【0121】

次に、炭化シリコン層 214をエッチングして素子分離を行い、島状の炭化シリコン層 114を形成する。また、シリコン層 234をエッチングして素子分離を行い、島状のシリコン層 134a、134bを形成する。また、導電層 221をエッチングすることにより、第1の電極層 121を形成する(図7(B)参照)。第1の電極層 121は、炭化シリコン層 114を有するダイオードにおいて、電極として機能する。

20

#### 【0122】

炭化シリコン層 214、シリコン層 234のエッチングを行う前に、TFTのしきい値電圧を制御するために、ホウ素、アルミニウム、ガリウムなどのp型不純物元素、またはリン、ヒ素などのn型不純物元素をシリコン層 234に添加してもよい。例えば、nチャネル型 TFTが形成される領域にホウ素、アルミニウム、ガリウム等のp型不純物元素を添加し、pチャネル型 TFTが形成される領域にリン、ヒ素等のn型不純物元素を添加する。また、炭化シリコン層 214にも、不純物元素を添加してもよい。

30

#### 【0123】

次に、炭化シリコン層 114上に絶縁層 156を形成し、シリコン層 134a、134b上に絶縁層 136を形成する(図7(C)参照)。

#### 【0124】

絶縁層 156は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、酸化ハフニウム膜、酸化アルミニウム膜、酸化タンタル膜等の絶縁膜を用いて、単層又は積層させて形成することができる。これらの膜は、CVD法、スパッタリング法等を用いて形成することができる。

#### 【0125】

また、プラズマ処理により炭化シリコン層 114の表面を酸化又は窒化させて酸化膜又は窒化膜を形成した後、当該酸化膜又は窒化膜上にCVD法やスパッタリング法等により形成した絶縁層を形成することにより絶縁層 156を形成してもよい。

40

#### 【0126】

また、炭化シリコン層 114を熱酸化させることで、絶縁層 156を形成してもよい。熱酸化を用いる場合には、ベース基板 100として、耐熱性の高い基板を用いることが好ましい。

#### 【0127】

次に、絶縁層 156をエッチングすることにより、炭化シリコン層 114を露出させる開口部 157を形成する(図7(D)参照)。

#### 【0128】

50

次に、絶縁層 156、絶縁層 136 上に導電層 117 を形成する（図 8（A）参照）。導電層 117 は、開口部 157 において炭化シリコン層 114 と接して形成される。

#### 【0129】

次に、導電層 117 をエッティングして、第 2 の電極層 122、導電層 138a、導電層 138b を形成する（図 8（B）参照）。第 1 の電極層 121 は、炭化シリコン層 114 を有するダイオードにおいて、電極として機能する。また、炭化シリコン層 114 と第 2 の電極層 122 との接触面でショットキー接合が形成される。

#### 【0130】

ここでは、第 2 の電極層 122、導電層 138a、導電層 138b を同一の導電層 117 を用いて形成する場合を示したが、これに限られない。第 2 の電極層 122 を、導電層 138a 及び導電層 138b と異なる材料で設けてもよい。第 2 の電極層 122 は、炭化シリコン層 114 との接触面でショットキー接合が形成されやすい材料を用いることが好ましく、一例として、金（Au）、白金（Pt）、ニッケル（Ni）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）を用いて、第 2 の電極層 122 を形成することが好ましい。もちろん、これらの材料を用いて導電層 117 を形成してもよい。

10

#### 【0131】

その後、シリコン層 134a、134b に不純物元素を添加して不純物領域を形成し、トランジスタ 135a のソース電極又はドレイン電極として機能する導電層 146a、146b を形成し、トランジスタ 135b のソース電極又はドレイン電極として機能する導電層 147a、147b を形成する。また、導電層 146a、146b、導電層 147a、147b と同時に、ダイオード 120 の第 2 の電極層 122 と接続する導電層 127 を形成してもよい（図 8（C）参照）。

20

#### 【0132】

導電層 127 は、配線として機能する。また、ダイオード 120 と、トランジスタ 135a 及び / 又はトランジスタ 135b とを電気的に接続する場合には、導電層 127 を用いればよい。

#### 【0133】

なお、オーミック接合を形成する炭化シリコンの接触面近傍には、炭化シリコンに n 型導電性を有するためのドーピングを行っても良い。ドーパントとして、N や P を用いることができる。ドーパントの添加は、イオン注入やイオンドーピングや熱拡散を用いることができる。ドーパント添加のタイミングは、導電層 221 とオーミック接合を形成する場合は脆化領域形成前後でもよいし、電極層 122 とオーミック接合を形成する場合は、炭化シリコン分離後から導電層 127 形成前または電極層 122 形成前に行うとよい。

30

#### 【0134】

本実施の形態で示した作製工程を用いることにより、炭化シリコン層を有するダイオードと、シリコン層をチャネル層とするトランジスタを同一基板上に有する半導体装置を作製することができる。

#### 【0135】

##### （実施の形態 4）

本実施の形態では、上記実施の形態 1 と異なる半導体装置の構成及びその作製方法について、図面を参照して説明する。具体的には、上記図 2（B）のダイオードを PN 接合ダイオードとする場合について説明する。また、本実施の形態で示す構成及び作製工程（適用できる材料等）は多くの部分で上記実施の形態と共通している。したがって、以下においては、重複する部分の説明は省略し、異なる点について詳細に説明する。

40

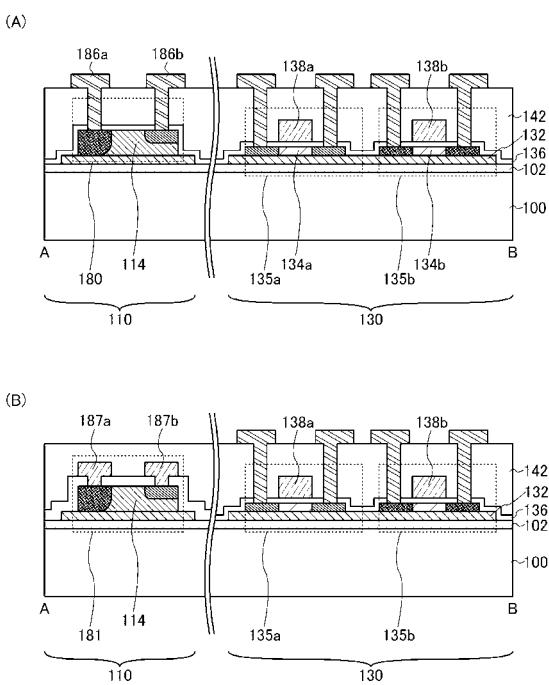

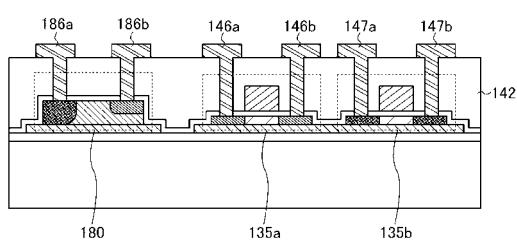

#### 【0136】

図 9（A）において、ダイオード 180 は、基板 100 上に絶縁層 112 を介して設けられた炭化シリコン層 114 と、炭化シリコン層 114 に電気的に接続された第 1 の電極層 186a 及び第 2 の電極層 186b とを有している。炭化シリコン層 114 には、n 型を示す不純物領域と p 型を示す不純物領域が形成されており、第 1 の電極層 186a と第 2 の電極層 186b は、それぞれいずれかの不純物領域に電気的に接続されている。

50

**【0137】**

また、ダイオード180と、トランジスタ135a及び/又はトランジスタ135bは電気的に接続した構成とすることができます。

**【0138】**

なお、図9(A)及び図9(B)に示す第2の回路群130において、2層の絶縁層(絶縁層102、絶縁層132)を介してトランジスタ135a、135bを設ける構成を示しているが、図1に示すように、1層の絶縁層(絶縁層102)を介してトランジスタ135a、135bを設ける構成としてもよい。

**【0139】**

次に、図9(A)に示す半導体装置の作製方法に関して図面を参照して説明する。

10

**【0140】**

まず、ベース基板100上に絶縁層112を介して設けられた炭化シリコン層214と、絶縁層132を介して設けられたシリコン層234を有する基板を準備した後、炭化シリコン層214をエッチングして島状の炭化シリコン層114を形成すると共に、シリコン層234をエッチングして素子分離を行い、島状のシリコン層134a、134bを形成する(図10(A)参照)。

**【0141】**

なお、ベース基板100上に絶縁層112を介して設けられた炭化シリコン層214と、絶縁層132を介して設けられたシリコン層234を有する基板の作製方法は、上記図3で示した作製方法を用いることができる。

20

**【0142】**

なお、炭化シリコン層214、シリコン層234のエッチングを行う前に、TFTのしきい値電圧を制御するために、ホウ素、アルミニウム、ガリウムなどのp型不純物元素、またはリン、ヒ素などのn型不純物元素をシリコン層234に添加してもよい。また、炭化シリコン層214にも、不純物元素を添加してもよい。本実施の形態では、炭化シリコン層にリンを添加することにより、低濃度のn型とする。ただし、これに限られない。

**【0143】**

次に、炭化シリコン層114、シリコン層134a、134b上に絶縁層136を形成する(図10(B)参照)。

**【0144】**

30

次に、シリコン層134aの上方に導電層138aを形成し、シリコン層134bの上方に導電層138bを形成する(図10(C)参照)。

**【0145】**

次に、炭化シリコン層114、シリコン層134a、134bに不純物元素を添加することにより、炭化シリコン層114、シリコン層134a、134b内に不純物領域を形成する(図10(D)参照)。

**【0146】**

ここでは、炭化シリコン層114にp型の不純物領域183、n型の不純物領域184を形成し、シリコン層134aにn型の不純物領域144b、144cを形成し、シリコン層134bにp型の不純物領域145b、145cを形成する。

40

**【0147】**

また、本実施の形態では、炭化シリコン層114において、p型の不純物領域183とn型の不純物領域184の間に、n型の不純物領域184より不純物元素の濃度が低い低濃度n型不純物領域182が形成されている。

**【0148】**

また、炭化シリコン層114のp型の不純物領域183と、シリコン層134bのp型の不純物領域145b、145cを同一の工程で形成することができる。また、炭化シリコン層114のn型の不純物領域184と、シリコン層134aのn型の不純物領域144b、144cを同一の工程で形成することができる。この場合、工程を簡略化することができる。

50

**【0149】**

なお、炭化シリコン層114、シリコン層134a、134bに不純物元素を添加した後、不純物領域の活性化（及び結晶性の回復）のための加熱処理を行うことが好ましい。不純物領域の活性化方法は、上記実施の形態2で示した方法と同様に行うことができる。

**【0150】**

次に、絶縁層136、導電層138a、138bを覆うように絶縁層142を形成した後、当該絶縁層142上に、ダイオードの電極（アノード又はカソード）として機能する第1の電極層186a、第2の電極層186b、トランジスタ135aのソース電極又はドレイン電極として機能する導電層146a、146b、トランジスタ135bのソース電極又はドレイン電極として機能する導電層147a、147bを形成する（図11参照）10。

**【0151】**

ここでは、第1の電極層186aが炭化シリコン層114に形成されたp型の不純物領域183に電気的に接続され、第2の電極層186bが炭化シリコン層114に形成されたn型の不純物領域184に電気的に接続される場合を示している。

**【0152】**

本実施の形態で示した作製工程を用いることにより、炭化シリコン層を有するPN接合ダイオードと、シリコン層をチャネル層とするトランジスタを同一基板上に有する半導体装置を作製することができる。20

**【0153】**

なお、図10～図11で説明した作製工程では、ダイオード180の第1の電極層186a、第2の電極層186bを、トランジスタ135a、135bのソース電極、ドレイン電極と同一の工程（材料）で形成する場合を示したが、これに限られない。例えば、図9（B）に示すように、ダイオード181の第1の電極層187a、第2の電極層187bをトランジスタ135a、135bのゲート電極として機能する導電層138a、138bと同一の工程（材料）で作製してもよい。20

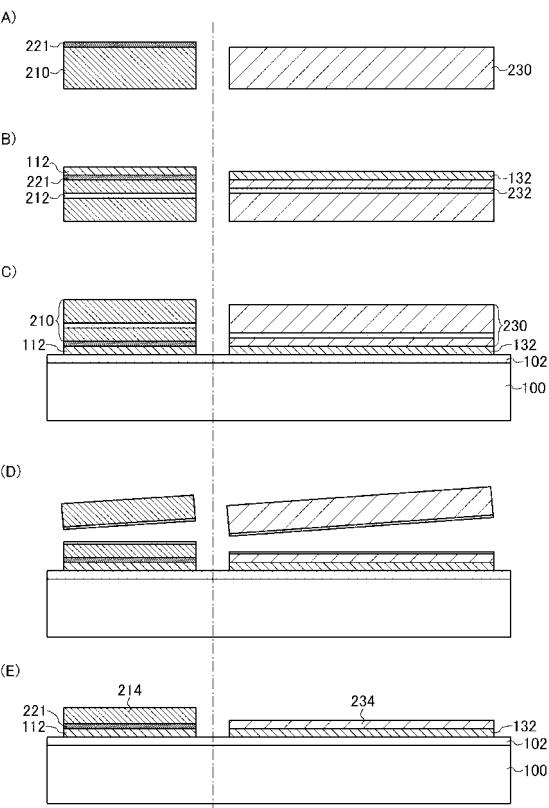

**【0154】****（実施の形態5）**

本実施の形態では、上記実施の形態と異なる半導体装置の構成及びその作製方法について、図面を参照して説明する。具体的には、シリコン基板に当該シリコン基板よりバンドギャップが大きい半導体基板を貼り合わせて設ける場合について説明する。30

**【0155】**

また、本実施の形態で示す構成及び作製工程（適用できる材料等）は多くの部分で上記実施の形態と共通している。したがって、以下においては、重複する部分の説明は省略し、異なる点について詳細に説明する。

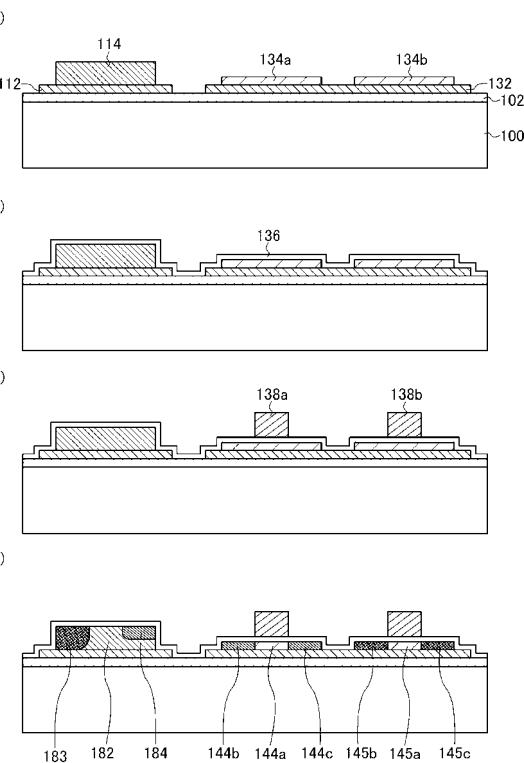

**【0156】**

まず、表面から所定の深さに脆化領域212を有し、且つ表面に絶縁層112が設けられた炭化シリコン基板210を準備する（図12（A）参照）。

**【0157】**

次に、シリコン基板330を準備し、炭化シリコン基板210を、絶縁層112を介してシリコン基板330に貼り合わせる（図12（B）参照）。40

**【0158】**

シリコン基板330は、市販の単結晶シリコン基板を用いることができる。市販の単結晶シリコン基板としては、直径5インチ（125mm）、直径6インチ（150mm）、直径8インチ（200mm）、直径12インチ（300mm）、直径16インチ（400mm）サイズの円形のものが代表的である。なお、シリコン基板330の形状は円形に限らず、矩形状等に加工して用いることも可能である。

**【0159】**

また、シリコン基板330の表面に絶縁層を形成してもよい。ここでは、シリコン基板330上に絶縁層302を形成し、絶縁層112の表面と絶縁層302の表面を貼り合わせ50

る場合を示している。

**【 0 1 6 0 】**

絶縁層 302 は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜等の絶縁膜を用いて、単層又は積層させて形成することができる。これらの膜は、熱酸化法、CVD 法又はスパッタリング法等を用いて形成することができる。

**【 0 1 6 1 】**

次に、脆化領域 212 において炭化シリコン基板 210 を分離する（図 12（C）参照）。

**【 0 1 6 2 】**

その結果、シリコン基板 330 上の一部の領域に、絶縁層 302 及び絶縁層 112 を介して設けられた炭化シリコン層 214 を有する基板が得られる（図 12（D）参照）。 10

**【 0 1 6 3 】**

なお、シリコン基板 330 上の炭化シリコン層 214 が設けられていない領域にシリコン層 332 を設けてもよい（図 12（E）参照）。

**【 0 1 6 4 】**

シリコン層 332 は、シリコン基板 330 上に設けられた絶縁層 302 の一部をエッチングした後、露出したシリコン基板 330 上にエピタキシャル成長させることにより形成することができる。

**【 0 1 6 5 】**

次に、図 12 の工程で得られた基板を用いて形成した半導体装置の一例に関して図 13 を参照して説明する。 20

**【 0 1 6 6 】**

図 12（D）で得られた基板上に、高い耐圧（高耐圧）を有する素子から構成される第 1 の回路群 110 と、高速動作や低電圧動作する素子から構成される第 2 の回路群 130 を設けることができる。図 13（A）は、図 12（D）で得られた基板上に、高い耐圧（高耐圧）を有する素子から構成される第 1 の回路群 110 の一部と、高速動作や低電圧動作する素子から構成される第 2 の回路群 130 の一部を設ける場合を示している。

**【 0 1 6 7 】**

第 1 の回路群 110 は、炭化シリコン層 114 をチャネル層として用いるトランジスタ 115 を設けた構成とすることができる。 30

**【 0 1 6 8 】**

第 2 の回路群 130 は、シリコン基板 330 をチャネル層として用いるトランジスタ 135 を設けた構成とすることができる。ここでは、シリコン基板 330 上に設けられた絶縁層 302 の一部をエッチングした後、当該露出したシリコン基板上に絶縁層 136 を介して導電層 138 を設ける場合を示している。絶縁層 136 は、トランジスタ 135 においてゲート絶縁層として機能し、導電層 138 はゲート電極として機能する。

**【 0 1 6 9 】**

図 13（B）は、図 12（E）で得られた基板上に、高い耐圧（高耐圧）を有する素子から構成される第 1 の回路群 110 と、高速動作や低電圧動作する素子から構成される第 2 の回路群 130 を設ける場合を示している。 40

**【 0 1 7 0 】**

第 1 の回路群 110 は、炭化シリコン層 114 をチャネル層として用いるトランジスタ 115 を設けた構成とすることができる。

**【 0 1 7 1 】**

第 2 の回路群 130 は、シリコン基板 330 上に形成されたシリコン層 332 をチャネル層として用いるトランジスタ 135 を設けた構成とすることができる。

**【 0 1 7 2 】**

なお、図 13 において、トランジスタ 115、トランジスタ 135 の構成は、様々な形態をとることができ、特定の構成に限定されない。また、トランジスタ 115 に代えて、炭化シリコン層 114 を用いたダイオードを設けてもよい。 50

## 【符号の説明】

## 【0173】

|         |          |    |

|---------|----------|----|

| 1 0 0   | 基板       |    |

| 1 0 2   | 絶縁層      |    |

| 1 1 0   | 回路群      |    |

| 1 1 2   | 絶縁層      |    |

| 1 1 3   | 絶縁層      |    |

| 1 1 4   | 炭化シリコン層  |    |

| 1 1 5   | トランジスタ   |    |

| 1 1 6   | 絶縁層      | 10 |

| 1 1 7   | 導電層      |    |

| 1 1 8   | 導電層      |    |

| 1 2 0   | ダイオード    |    |

| 1 2 1   | 電極層      |    |

| 1 2 2   | 電極層      |    |

| 1 2 7   | 導電層      |    |

| 1 3 0   | 回路群      |    |

| 1 3 2   | 絶縁層      |    |

| 1 3 5   | トランジスタ   |    |

| 1 3 6   | 絶縁層      | 20 |

| 1 3 8   | 導電層      |    |

| 1 4 2   | 絶縁層      |    |

| 1 5 6   | 絶縁層      |    |

| 1 5 7   | 開口部      |    |

| 1 8 0   | ダイオード    |    |

| 1 8 1   | ダイオード    |    |

| 1 8 2   | 不純物領域    |    |

| 1 8 3   | 不純物領域    |    |

| 1 8 4   | 不純物領域    |    |

| 2 1 0   | 炭化シリコン基板 | 30 |

| 2 1 2   | 脆化領域     |    |

| 2 1 4   | 炭化シリコン層  |    |

| 2 2 1   | 導電層      |    |

| 2 3 0   | シリコン基板   |    |

| 2 3 2   | 脆化領域     |    |

| 2 3 4   | シリコン層    |    |

| 3 3 0   | シリコン基板   |    |

| 3 3 2   | シリコン層    |    |

| 3 0 2   | 絶縁層      |    |

| 1 2 4 a | チャネル形成領域 | 40 |

| 1 2 4 b | 不純物領域    |    |

| 1 2 4 c | 不純物領域    |    |

| 1 2 6 a | 導電層      |    |

| 1 3 4 a | シリコン層    |    |

| 1 3 4 b | シリコン層    |    |

| 1 3 5 a | トランジスタ   |    |

| 1 3 5 b | トランジスタ   |    |

| 1 3 8 a | 導電層      |    |

| 1 3 8 b | 導電層      |    |

| 1 4 4 a | チャネル形成領域 | 50 |

|         |          |

|---------|----------|

| 1 4 4 b | 不純物領域    |

| 1 4 4 c | 不純物領域    |

| 1 4 5 a | チャネル形成領域 |

| 1 4 5 b | 不純物領域    |

| 1 4 5 c | 不純物領域    |

| 1 4 6 a | 導電層      |

| 1 4 7 a | 導電層      |

| 1 8 6 a | 電極層      |

| 1 8 6 b | 電極層      |

| 1 8 7 a | 電極層      |

| 1 8 7 b | 電極層      |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

| (51)Int.Cl.              | F I               |

|--------------------------|-------------------|

| H 01 L 21/8234 (2006.01) | H 01 L 27/08 102C |

| H 01 L 27/088 (2006.01)  | H 01 L 27/06 102A |

| H 01 L 27/06 (2006.01)   | H 01 L 29/91 F    |

| H 01 L 29/868 (2006.01)  | H 01 L 29/91 L    |

| H 01 L 29/861 (2006.01)  |                   |

(56)参考文献 特開2006-041516(JP,A)

特開2001-267573(JP,A)

特表2005-531153(JP,A)

国際公開第2007/061563(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 786

H 01 L 21 / 02

H 01 L 21 / 336

H 01 L 21 / 8234

H 01 L 27 / 06

H 01 L 27 / 08

H 01 L 27 / 088

H 01 L 27 / 12

H 01 L 29 / 861

H 01 L 29 / 868