(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-123459

(P2017-123459A)

(43) 公開日 平成29年7月13日(2017.7.13)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H05K 3/46</b> (2006.01)  | H05K 3/46  | L 5 E 3 1 6 |

| <b>H05K 1/14</b> (2006.01)  | H05K 3/46  | B 5 E 3 4 4 |

| <b>H01L 23/12</b> (2006.01) | H05K 1/14  | B           |

| <b>H01L 25/00</b> (2006.01) | H01L 23/12 | N           |

|                             | H01L 25/00 | B           |

審査請求 未請求 請求項の数 16 O L (全 13 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2016-240411 (P2016-240411) |

| (22) 出願日     | 平成28年12月12日 (2016.12.12)     |

| (31) 優先権主張番号 | 10-2016-0002884              |

| (32) 優先日     | 平成28年1月8日 (2016.1.8)         |

| (33) 優先権主張国  | 韓国 (KR)                      |

| (31) 優先権主張番号 | 10-2016-0048927              |

| (32) 優先日     | 平成28年4月21日 (2016.4.21)       |

| (33) 優先権主張国  | 韓国 (KR)                      |

|          |                                                                                            |

|----------|--------------------------------------------------------------------------------------------|

| (71) 出願人 | 594023722<br>サムソン エレクトローメカニックス カンパニーリミテッド。<br>大韓民国、キョンギード、スウォンーシ、ヨントング、(マエタンドン) マエヨン-ロ 150 |

| (74) 代理人 | 110000877<br>龍華国際特許業務法人                                                                    |

| (72) 発明者 | ヨン-ホ バエク<br>大韓民国、キョンギード、スウォンーシ、ヨントング、(マエタンドン) マエヨン-ロ 150 サムソン エレクトローメカニックス カンパニーリミテッド、内    |

最終頁に続く

(54) 【発明の名称】プリント回路基板

## (57) 【要約】 (修正有)

【課題】高多層の構造や大きいサイズの基板においても、収率を確保し、リードタイムが長くならず、また、多層のビア構造、精密な整合度及び優れた電気特性が得られるプリント回路基板を提供する。

【解決手段】貫通ホールが形成されたコア部材155と、貫通ホールに配置されたサブ回路基板100と、コア部材及びサブ回路基板の両面に積層された第1絶縁層180と、貫通ホールの内壁155aとサブ回路基板との間に充填された絶縁材185と、を含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

貫通ホールが形成されたコア部材と、

前記貫通ホールに配置されたサブ回路基板と、

前記コア部材及び前記サブ回路基板の両面に積層された第1絶縁層と、

前記貫通ホールの内壁と前記サブ回路基板との間に充填された絶縁材と、

を含むプリント回路基板。

**【請求項 2】**

前記コア部材を貫通するピアをさらに含む請求項1に記載のプリント回路基板。

**【請求項 3】**

前記サブ回路基板は、少なくとも一層の回路層と第2絶縁層とを含む請求項1または請求項2に記載のプリント回路基板。

**【請求項 4】**

前記絶縁材は、前記第2絶縁層とは異なる材質からなる請求項3に記載のプリント回路基板。

**【請求項 5】**

前記絶縁材は、前記第1絶縁層の絶縁物質の一部が充填されて形成された請求項4に記載のプリント回路基板。

**【請求項 6】**

前記第1絶縁層は、纖維補強材をさらに含む請求項1から請求項5のいずれか1項に記載のプリント回路基板。

**【請求項 7】**

前記サブ回路基板は、コアレス構造を有する請求項1から請求項6のいずれか1項に記載のプリント回路基板。

**【請求項 8】**

前記サブ回路基板は、纖維補強材を備えた補強層をさらに含む請求項1から請求項7のいずれか1項に記載のプリント回路基板。

**【請求項 9】**

前記サブ回路基板は、高密度回路を備え、

前記コア部材及び/または前記第1絶縁層に形成され、前記高密度回路よりも密度の低い低密度回路をさらに含む請求項1から請求項8のいずれか1項に記載のプリント回路基板。

**【請求項 10】**

前記高密度回路は、互いに対称に積層されたスタックピア(stack via)を含む請求項9に記載のプリント回路基板。

**【請求項 11】**

前記低密度回路と前記高密度回路とを接続させるピアまたはソルダーバンプをさらに含む請求項9または請求項10に記載のプリント回路基板。

**【請求項 12】**

前記高密度回路における回路層の間隔は、前記低密度回路における回路層の間隔よりも狭い請求項9から請求項11のいずれか1項に記載のプリント回路基板。

**【請求項 13】**

前記高密度回路の幅は、前記低密度回路の幅よりも狭い請求項9から請求項12のいずれか1項に記載のプリント回路基板。

**【請求項 14】**

前記高密度回路に接続され、前記第1絶縁層に埋め込まれる電子素子をさらに含む請求項9から請求項13のいずれか1項に記載のプリント回路基板。

**【請求項 15】**

前記第1絶縁層に形成された接続パッドと、前記高密度回路を前記接続パッドに接続させる回路パターンを備えた外層回路とをさらに含む請求項9から請求項14のいずれか1

10

20

30

40

50

項に記載のプリント回路基板。

【請求項 1 6】

前記コア部材及び前記サブ回路基板に積層される多層の低密度回路層をさらに含む請求項 9 から請求項 1 5 のいずれか 1 項に記載のプリント回路基板。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、プリント回路基板に関する。

【背景技術】

【0 0 0 2】

近年、コンピューター産業の発達に伴って、より高性能を有し、より低コストで生産できる集積回路（ダイ、die）に関する技術が発達している。これにより、ダイが実装される様々なプリント回路基板に関する技術も開発されている。

特に、サーバに使用されている基板は、高多層の構造や大きいサイズのために、収率を確保しにくく、長いリードタイムが必要となる。また、サーバ基板は、多層のビア構造、精密な整合度及び優れた電気特性が要求されるという困難性があった。

【先行技術文献】

【特許文献】

【0 0 0 3】

【特許文献 1】アメリカ登録公告第 8 7 5 4 5 1 4 号公報

20

【発明の概要】

【課題を解決するための手段】

【0 0 0 4】

本発明の一側面によれば、貫通ホールが形成されたコア部材と、貫通ホールに配置されたサブ回路基板と、コア部材及びサブ回路基板の両面に積層された第 1 絶縁層と、貫通ホールの内壁とサブ回路基板との間に充填された絶縁材と、を含むプリント回路基板が提供される。

【図面の簡単な説明】

【0 0 0 5】

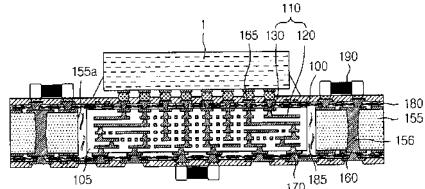

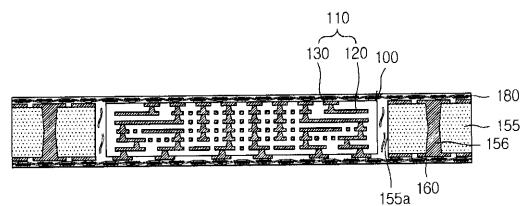

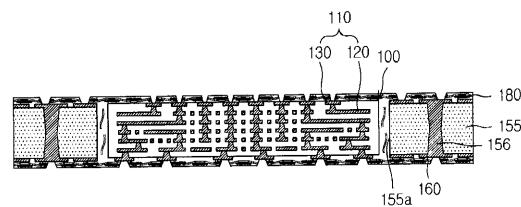

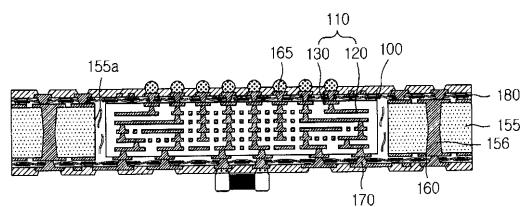

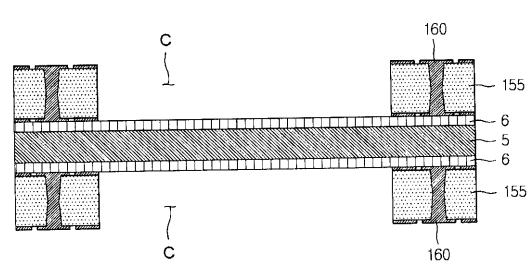

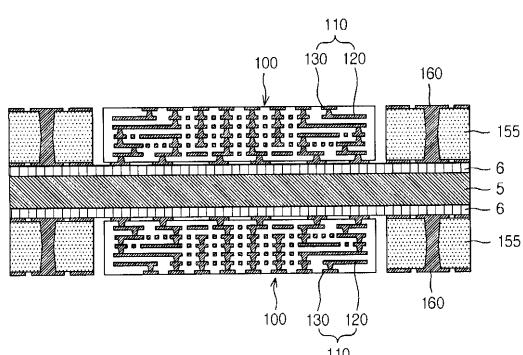

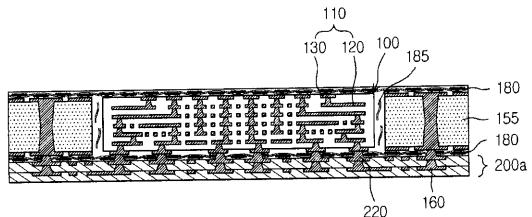

【図 1】本発明の第 1 実施例に係るプリント回路基板を示す図である。

30

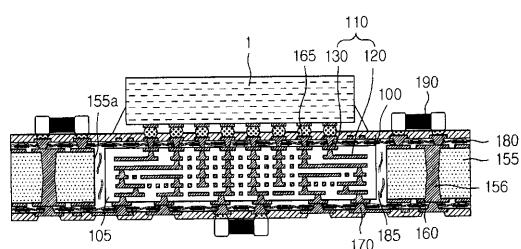

【図 2】本発明に係るプリント回路基板の高密度回路におけるビア構造を例示する図である。

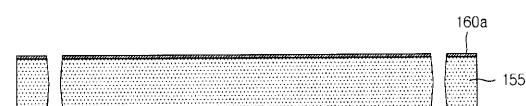

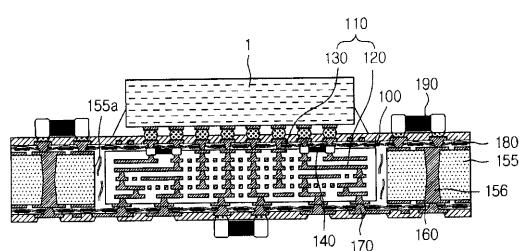

【図 3】本発明の第 1 実施例に係るプリント回路基板の製造方法の一工程を示す図である。

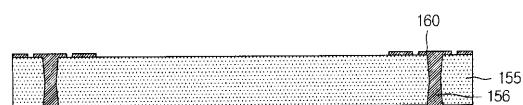

【図 4】図 3 に示す工程の次の工程を示す図である。

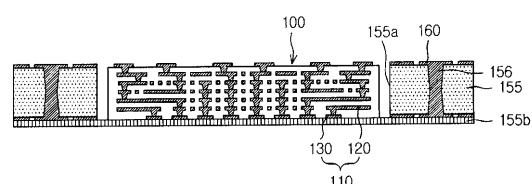

【図 5】図 4 に示す工程の次の工程を示す図である。

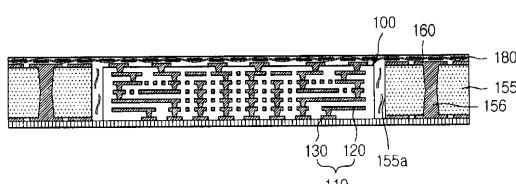

【図 6】図 5 に示す工程の次の工程を示す図である。

【図 7】図 6 に示す工程の次の工程を示す図である。

【図 8】図 7 に示す工程の次の工程を示す図である。

【図 9】図 8 に示す工程の次の工程を示す図である。

40

【図 1 0】図 9 に示す工程の次の工程を示す図である。

【図 1 1】図 1 0 に示す工程の次の工程を示す図である。

【図 1 2】図 1 1 に示す工程の次の工程を示す図である。

【図 1 3】図 1 2 に示す工程の次の工程を示す図である。

【図 1 4】図 1 3 に示す工程の次の工程を示す図である。

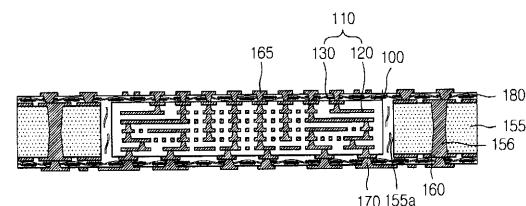

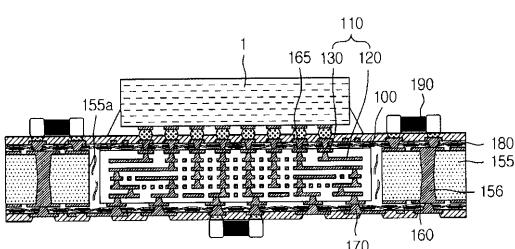

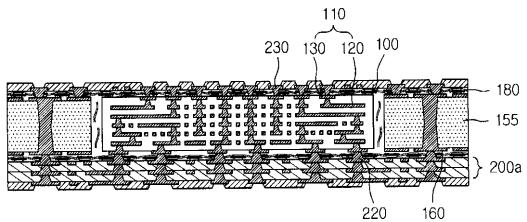

【図 1 5】本発明の第 2 実施例に係るプリント回路基板を示す図である。

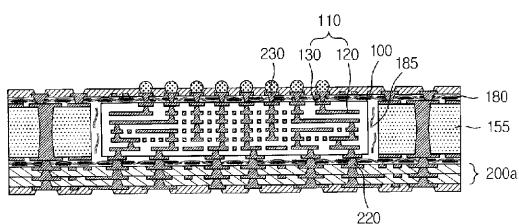

【図 1 6】本発明の第 3 実施例に係るプリント回路基板を示す図である。

【図 1 7】本発明の第 3 実施例に係るプリント回路基板の製造方法の一工程を示す図である。

【図 1 8】図 1 7 に示す工程の次の工程を示す図である。

50

【図19】図18に示す工程の次の工程を示す図である。

【図20】図19に示す工程の次の工程を示す図である。

【図21】図20に示す工程の次の工程を示す図である。

【図22】図21に示す工程の次の工程を示す図である。

【図23】図22に示す工程の次の工程を示す図である。

【図24】図23に示す工程の次の工程を示す図である。

【図25】図24に示す工程の次の工程を示す図である。

【発明を実施するための形態】

【0006】

本発明に係るプリント回路基板の実施例を添付図面に基づいて詳細に説明し、添付図面に基づいて説明するに当たって、同一または対応する構成要素には同一の図面符号を付し、これに対する重複説明を省略する。

また、本明細書において、「第1」、「第2」などの用語は、同一または相応する構成要素を区別するための識別記号に過ぎず、同一または相応する構成要素が第1、第2などの用語により限定されない。

また、「結合」とは、各構成要素間の接触関係において、各構成要素の間に物理的に直接接触する場合のみを意味するものではなく、他の構成が各構成要素の間に介在され、その他の構成に構成要素がそれぞれ接触している場合まで包括する概念として使用する。

【0007】

図1は、本発明の第1実施例に係るプリント回路基板を示す図である。図1を参照すると、本発明の一実施例に係るプリント回路基板は、サブ回路基板100と、コア部材155と、第1絶縁層180と、絶縁材185と、を含む。

【0008】

サブ回路基板100は、プリント回路基板に内蔵されるまた一つの回路基板であって、少なくとも一層の回路層と回路層の間を絶縁させる第2絶縁層とを含むことができる。サブ回路基板100は、プリント回路基板における他の領域では処理しない特定の機能を行うことができる。例えば、サブ回路基板100は、プリント回路基板に実装されるダイ(die)1と電気的に接続して電気的信号の伝達などの機能を行うことができる。

【0009】

ここで、ダイ1は、集積回路であって、ダイ1と接続するためには、小さな空間に非常に密集した回路が必要となる。つまり、サブ回路基板100は、微細な回路パターン120からなる高密度回路110を備えることができる。

【0010】

サブ回路基板100において、高密度回路110の幅及び回路の間の間隔は、後述する低密度回路160の幅及び回路の間の間隔に比べて、狭く形成される。

【0011】

また、高密度回路110は、サブ回路基板100が内蔵された後に外層に形成される外層回路165よりも微細に形成することができる。例えば、高密度回路110は、半導体工程等で形成され、低密度回路160は、SAP工程(Semi-Additive Process)、M-SAP工程(Modified Semi-Additive Process)またはテンティング(tenting)工程等の基板工程により形成することができる。または、高密度回路110を、基板工程中の相対的に精密なSAP工程により形成し、低密度回路160を、相対的に、より精密でない基板工程であるM-SAP工程またはテンティング工程などにより形成することができる。

【0012】

サブ回路基板100は、コアレス(coreless)構造、すなわち、別の補強部材を中心部に有しない構造であってもよい。例えば、サブ回路基板100は、中心部に補強部材なしで微細な回路パターン120と、これを絶縁させる第2絶縁層を順に積層して形成することができる。このとき、コアレス構造のサブ回路基板100の歪み(warpage)を防止するために、サブ回路基板100に繊維補強材を備えた補強層を追加するこ

10

20

30

40

50

とができる。例えば、微細な回路パターン 120 と第 2 絶縁層とでビルドアップされた回路層にプリプレグ層をさらに積層してもよい。

【0013】

サブ回路基板 100 は、ダイ 1 と直接接続されるように、一面にパッド 130 が形成され、パッド 130 とダイ 1 を直接結合することができる。このとき、サブ回路基板 100 の一面は、プリント回路基板の外層となることができる。

【0014】

また、サブ回路基板 100 の一面上に付加的に外層が形成され、外層には、ダイ 1 と高密度回路 110 とを接続させる外層回路 165 を形成することができる。

【0015】

図 1 に示すように、外層回路 165 は、ダイ 1 との接続のためのパッドを含み、高密度回路 110 のパッド 130 と接続することができる。外層回路 165 は、微細な高密度回路 110 が直接ソルダーリングされることで、損傷を防止することができる。

【0016】

一方、外層回路 165 は、高密度回路 110 をファンアウト (fan-out) させるファンアウト回路パターンを含むことができる。具体的に、サブ回路基板 100 において稠密に形成された高密度回路 110 は、ファンアウト回路パターンを介して低密度回路基板領域の外層に広く分散させることができる。

【0017】

ファンアウト回路パターンは、ダイ 1 の規格に合わせてプリント回路基板の外層に形成されたパッドを含むことができる。これにより、高密度回路 110 は、ダイ 1 の規格の影響を受けずに自由に設計できるので、高密度回路 110 の設計自由度を高めることができる。

【0018】

サブ回路基板 100 は、高密度回路 110 に接続され、第 1 絶縁層 180 に埋め込まれる第 1 電子素子 140 を含むことができる。例えば、サブ回路基板 100 の外層に能動素子及び受動素子等の第 1 電子素子 140 を搭載することができる。図 15 に示すように、サブ回路基板 100 の上面にキャパシタ等の受動素子を搭載することができる。特に、ダイサイドキャパシタ (die side capacitor) 等のように、従来のプリント回路基板の外層に搭載される電子素子もサブ回路基板 100 に搭載されることで、プリント回路基板に内蔵することができる。

【0019】

また、サブ回路基板 100 は、ダイ 1 の機能を支援するように、マイクロ電子装置 / システムのルーティング及び電力伝達機能を有する第 1 電子素子 140 を搭載することができる。

【0020】

サブ回路基板 100 において、高密度回路 110 は、互いに対称に積層されたスタックビア (stack via) 125a、125b を含むことができる。サブ回路基板 100 の歪みを低減するために、高密度回路 110 のビアは、中心部分を基準として両側に対称となるように積層されるビア構造を有することができる。

【0021】

図 2 は、本発明に係るプリント回路基板の高密度回路 110 におけるビア構造を例示する図である。

図 2 を参照すると、初期において幾つかの層を一方に積層し、その後、残りの層を両方に分けて連続して積層し、互いに対称なスタックビアの構造 125a、125b を形成することができる。

【0022】

コア部材 155 は、プリント回路基板の中心部層であり、第 1 絶縁層 180 とともにサブ回路基板 100 の歪み (warpage) を防止する役割を担う。このため、コア部材 155 は、サブ回路基板 100 及び第 1 絶縁層 180 よりも剛性の高い材質で形成され、

コア部材 155 には、貫通ホールが形成されて、サブ回路基板 100 を内部に配置することができる。

【0023】

例えば、コア部材 155 は、絶縁樹脂内にガラス繊維または炭素繊維等の補強部材が含浸された絶縁基板であってもよく、金属材質のメタルコアをコア部材 155 として使用できる等、その材質は様々に変更可能である。

【0024】

また、コア部材 155 は、貫通するビア 156 をさらに含むことができる。コア部材 155 のビア 156 は、コア部材 155 の両側を電気的に接続させる。

【0025】

図 1 を参照すると、コア部材 155 の上面及び下面に形成された低密度回路 160 は、ビア 156 を介して接続されることができる。

【0026】

本実施例のように、コア部材 155 にサブ回路基板 100 を内蔵する構造を有すると、サブ回路基板 100 が内蔵される領域においては、厚いコア構造を削除することができる。これにより、少なくともサブ回路基板 100 が内蔵される領域においては、コア部材 155 を貫通して形成されるビア 156 を省略することができる。コア部材 155 を貫通するビア 156 は、加工上の問題のために微細な間隔で形成することに制約がある。このため、コア部材 155 を貫通するビア 156 を省略し、サブ回路基板 100 のスタックビアが、コア部材 155 におけるビア 156 としての役割を担うようにすると、ビアの間のピッチを微細化することができる。また、コア構造が削除されることにより、コアの上面/下面の 2 層の回路層を低減することができる。ビアの間隔を低減し、コアの上面/下面の回路層を低減することにより、回路ルーティング (routing) の距離を低減させ、基板全体の層数及びサイズを低減することができる。また、コア部材 155 のビア 156 と、これに接続するビアとをスタックビアで代替することにより、コア部材 155 のビア 156 と、これに接続するビアとの CTE (熱膨脹係数) 差による応力発生の問題を防止することができる。

【0027】

第 1 絶縁層 180 は、コア部材 155 及びサブ回路基板 100 の両面に積層され、コア部材 155 の貫通ホールに配置されたサブ回路基板 100 の両面とコア部材 155 とを結合させることができる。

【0028】

図 1 を参照すると、コア部材 155 がプリント回路基板の中心部層として用いられ、コア部材 155 の中心部分に形成された貫通ホールにサブ回路基板 100 を配置することができる。そして、第 1 絶縁層 180 により、コア部材 155 とサブ回路基板 100 とを結合することができる。例えば、コア部材 155 は、四角フレームの形状を有し、サブ回路基板 100 は、四角フレームの内部に配置されて内蔵される構造とすることができる。そして、両面に積層された第 1 絶縁層 180 により、コア部材 155 は、内蔵されたサブ回路基板 100 を押さえる構造を有し、サブ回路基板 100 の歪みを防止することができる。

【0029】

また、第 1 絶縁層 180 は、ガラス繊維 (Glass cloth) 等の繊維補強材を含むことができる。例えば、第 1 絶縁層 180 は、プリプレグを積層して形成することができる。ガラス繊維等の繊維補強材が含まれた第 1 絶縁層 180 は、サブ回路基板 100 及びコア部材 155 を一体にすると、サブ回路基板 100 の剛性をさらに補強することができる。

【0030】

絶縁材 185 は、貫通ホールの内壁 155a とサブ回路基板 100 との間に充填され、サブ回路基板 100 の側面をコア部材 155 に結合することができる。

【0031】

10

20

30

40

50

図1を参照すると、コア部材155の貫通ホールにサブ回路基板100が配置され、貫通ホールの内壁155aとサブ回路基板100との間にはギャップが形成される。絶縁材185は、このギャップを充填するとともにコア部材155とサブ回路基板100とを結合することができる。これにより、絶縁材185は、コア部材155がサブ回路基板100の側面を押さえる構造を有することになり、サブ回路基板100の歪みを防止することができる。

#### 【0032】

絶縁材185は、サブ回路基板100の第2絶縁層105とは異なる材質からなることができる。例えば、第1絶縁層180の絶縁物質の一部が充填されて形成されてもよい。このとき、第1絶縁層180が繊維補強材を含む場合は、絶縁材185も同じく繊維補強材を含むことができる。また、第1絶縁層180を積層する前に、貫通ホールの内壁155aとサブ回路基板100との間に、別の物質を充填して絶縁材185を形成することも可能である。

10

#### 【0033】

コア部材155及び第1絶縁層180で構成された領域には、高密度回路110に比べて密度の低い低密度回路160を形成することができる。プリント回路基板において、特別な用途のために高密度回路110を必要とする部分以外の他の部分には高密度回路を構成する必要は少ない。よって、当該他の部分には、収率が高く、コストの低い低密度回路を形成することが好ましい。

20

#### 【0034】

例えば、コア部材155または第1絶縁層180のうちの少なくともいずれか1つには、内部または外部に低密度回路160を形成することができる。これにより、コア部材155、第1絶縁層180及び低密度回路160は、一体で低密度回路基板領域を形成することができ、全体的には、低密度回路基板領域が高密度回路110を備えたサブ回路基板100を内蔵する構造を有することができる。

#### 【0035】

サブ回路基板100は、低密度回路基板領域に比べて高密度の回路層を有するため、層間隔が低密度回路基板領域における層間隔よりも狭く形成される。例えば、低密度回路基板領域のうちの1つの絶縁層に、複数層のサブ回路基板100を内蔵することができる。内蔵されたサブ回路基板100は、低密度回路基板領域の外層により覆われることができる。

30

#### 【0036】

また、低密度回路基板領域は、サーバ基板のフォームファクタ(form factor)に合わせて形成することが可能である。フォームファクタとは、サーバ基板等の特定の用途を有する回路基板の大きさ、構成及び物理的な配列のことをいい、ハードウェアを構成する標準となる。本発明のプリント回路基板は、低密度回路基板領域がフォームファクタに対応して形成され、サブ回路基板100は、自由に形成することができる。例えば、フォームファクタに対応する領域である低密度回路基板領域は、規格に従うレイアウトを有し、フォームファクタの以外の領域であるサブ回路基板100は、様々なサイズや形態に製作することができる。

40

#### 【0037】

一方、低密度回路基板領域には、ダイ1サイドの部品実装空間を確保する。低密度回路基板領域には、ダイ1サイドのキャパシタ(die side capacitor)等の、サーバ基板の外層に搭載される第2電子素子190を搭載することができる。また、低密度回路基板領域には、グラウンド(GND)が形成されてもよく、グラウンドは、ビアを介してサブ回路基板100に接続することができる。

#### 【0038】

低密度回路基板領域は、低密度回路160とサブ回路基板100の高密度回路110とを接続させるビア170またはソルダーバンプをさらに含むことができる。低密度回路基板領域の低密度回路160は、サブ回路基板100側を向いたパッド及びこれに接続する

50

回路パターンを備えることができる。図1を参照すると、ビア170を介して、低密度回路160と高密度回路110とは、上下に直接接続することができる。これにより、信号を伝達する回路のルーティング距離が低減し、電気的信頼性を高めることができる。

【0039】

図3から図14は、本発明の第1実施例に係るプリント回路基板の製造方法を示す図である。本発明の第1実施例に係るプリント回路基板の製造方法では、コア部材155を備えた低密度回路基板領域にサブ回路基板100を結合させて内蔵する方法が例示される。

【0040】

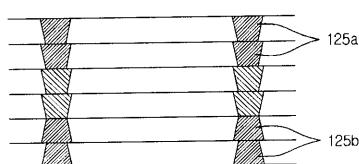

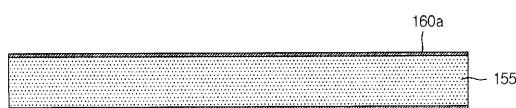

図3から図5を参照すると、金属層160aが形成されたコア部材155を準備し、コア部材155を貫通するビア156を含む低密度回路160の一部を形成することができる。このとき、サブ回路基板100が収容される部分の金属層160aを予め除去してもよい。

【0041】

図6を参照すると、コア部材155を加工して貫通ホールCを形成することができる。

【0042】

図7を参照すると、高密度回路110が備えられたサブ回路基板100を準備し、サブ回路基板100を貫通ホールCの内部に配置することができる。サブ回路基板100を固定するために、コア部材155の一面には接着テープ155bが付着されてもよい。

【0043】

図8を参照すると、コア部材155の他面に第1絶縁層180を積層し、絶縁材185を充填してサブ回路基板100を内蔵(encapsulation)することができる。第1絶縁層180の絶縁物質の一部が、貫通ホールの内壁155aとサブ回路基板100との間のギャップに充填されて絶縁材185が形成されることもできる。このとき、第1絶縁層180は、ガラス繊維等の繊維補強材を含むことができる。

【0044】

図9を参照すると、コア部材155の一面から接着テープ155bを除去し、コア部材155の一面にも第1絶縁層180を積層することができる。これにより、サブ回路基板100の両面は、第1絶縁層180によりコア部材155と強く結合され、歪みを防止することができる。

【0045】

図10及び図11を参照すると、サブ回路基板100の一面と接続する外層回路165を形成することができる。また、サブ回路基板100の他面には、ビア170及びビア170と接続する低密度回路160を形成することができる。図12を参照すると、プリント回路基板の外層にソルダーレジスト層をさらに形成することができる。

【0046】

図13を参照すると、ソルダーレジスト層のオープニングを介してプリント回路基板の一面に露出した外層回路165にソルダーバンプを形成することができ、他面には第2電子素子190を実装することができる。

【0047】

図14を参照すると、プリント回路基板の一面にダイ1を実装し、ソルダーバンプにより外層回路165に接続されることができる。

【0048】

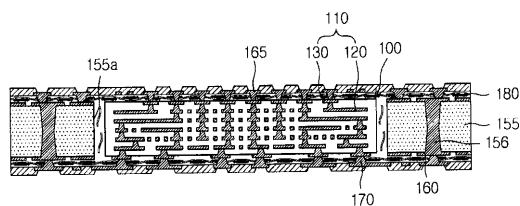

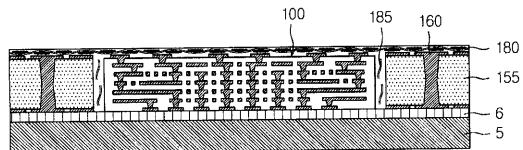

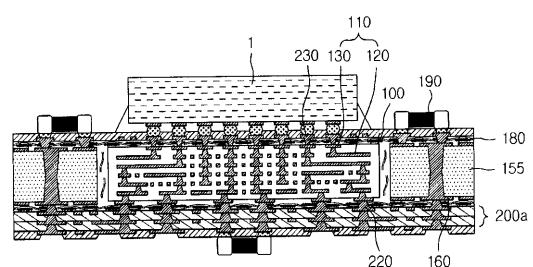

図16は、本発明の第3実施例に係るプリント回路基板を示す図である。

図16を参照すると、本発明の第3実施例に係るプリント回路基板は、サブ回路基板100の他面に積層される多層の低密度回路層200aをさらに含む構造を有する。つまり、上述した第1実施例に係るプリント回路基板を上部基板とし、多層の低密度回路層200aを下部基板として加えられた構造を有することができる。

【0049】

多層の低密度回路層200aは、サブ回路基板100の内蔵された上部基板を支持するように接続される。多層の低密度回路層200aの回路は、ビア220を介してサブ回路

基板 100 及び上部基板の低密度回路に接続される。多層の低密度回路層 200a には、サブ回路基板 100 よりも厚い回路及び絶縁層が形成されるので、サブ回路基板 100 を内蔵する上部基板よりは高い剛性を有することができる。これにより、多層の低密度回路層 200a は、サブ回路基板 100 及び上部基板の歪みを防止する役割を担うことができる。

#### 【0050】

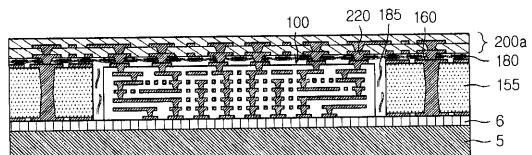

図 17 から図 25 は、本発明の第 3 実施例に係るプリント回路基板の製造方法を示す図である。本発明の第 3 実施例に係るプリント回路基板の製造方法は、コア部材 155 と多層の低密度回路層 200a とが備えられた低密度回路基板 200 にサブ回路基板 100 を結合させて内蔵する方法を例示する。

10

#### 【0051】

図 17 及び図 18 を参照すると、キャリア 5 を準備し、キャリア 5 の両面に接着層 6 を形成することができる。図 19 を参照すると、キャリア 5 の両面に、貫通ホール C 及び低密度回路 160 の一部が形成されたコア部材 155 を付着することができる。

#### 【0052】

図 20 を参照すると、高密度回路 110 が備えられたサブ回路基板 100 を準備し、サブ回路基板 100 を貫通ホール C の内部に配置することができる。このとき、本実施例におけるサブ回路基板 100 は、上述した第 1 実施例のサブ回路基板 100 が逆になった形態に配置される。つまり、ダイ 1 と接続されるサブ回路基板 100 の一面が、キャリア 5 を向くように配置される。

20

#### 【0053】

図 21 を参照すると、コア部材 155 の他面に第 1 絶縁層 180 を積層し、絶縁材 185 を充填してサブ回路基板 100 を内蔵することができる。また、繊維補強材を含む第 1 絶縁層 180 をサブ回路基板 100 及びコア部材 155 に積層して、サブ回路基板 100 をコア部材 155 に、より強く結合させることができる。

#### 【0054】

図 22 を参照すると、キャリア 5 の両面に形成された 2 つの上部基板のそれぞれに、多層の低密度回路層 200a をさらに形成することができる。このとき、サブ回路基板 100 の他面には、低密度回路層 200a に接続されるビア 220 を形成することができる。また、歪みを防止するために、多層の低密度回路層 200a に繊維補強材が含まれた絶縁層を適用することができる。

30

#### 【0055】

図 23 及び図 24 を参照すると、キャリア 5 を分離した後に、サブ回路基板 100 の一面に接続する外層回路 230 を形成することができる。また、プリント回路基板の外層にソルダーレジスト層をさらに形成することができる。

#### 【0056】

図 25 を参照すると、ソルダーレジスト層のオープニングを介してプリント回路基板の一面に露出した外層回路にダイ 1 を実装することができ、他面には第 2 電子素子 190 を実装することができる。

40

#### 【0057】

以上のように、本発明の一実施例について説明したが、当該技術分野で通常の知識を有する者であれば特許請求の範囲に記載された本発明の思想から逸脱しない範囲内で、構成要素の付加、変更、削除または追加などにより本発明を多様に修正及び変更することができ、これも本発明の権利範囲内に含まれるものといえよう。

#### 【符号の説明】

#### 【0058】

|     |        |

|-----|--------|

| 1   | ダイ     |

| 5   | キャリア   |

| 100 | サブ回路基板 |

| 110 | 高密度回路  |

50

|               |          |

|---------------|----------|

| 1 4 0         | 第 1 電子素子 |

| 1 5 5         | コア部材     |

| 1 6 0         | 低密度回路    |

| 1 6 5 、 2 3 0 | 外層回路     |

| 1 8 0         | 第 1 絶縁層  |

| 1 8 5         | 絶縁材      |

| 1 9 0         | 第 2 電子素子 |

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

【図21】

【図22】

【図23】

【図24】

【図25】

---

フロントページの続き

(72)発明者 ジュン - ヒュン チョ

大韓民国、キヨンギ - ド、スウォン - シ、ヨントン - グ、(マエタン - ドン)マエヨン - ロ 15

0 サムソン エレクトロ - メカニックス カンパニーリミテッド. 内

(72)発明者 セウン - ヨ クク

大韓民国、キヨンギ - ド、スウォン - シ、ヨントン - グ、(マエタン - ドン)マエヨン - ロ 15

0 サムソン エレクトロ - メカニックス カンパニーリミテッド. 内

F ターム(参考) 5E316 AA04 AA15 AA22 AA43 CC04 CC08 CC31 DD02 DD23 DD24

DD32 DD33 EE31 EE43 FF04 FF13 FF14 FF28 GG26 GG28

HH07 HH31 JJ02

5E344 AA05 BB02 BB06 BB10 CC03 CD34 DD01 EE21 EE30