# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(11) 공개번호 10-2009-0072394 (43) 공개일자 2009년07월02일

주식회사 하이닉스반도체

(51) Int. Cl.

*G11C* 11/4093 (2006.01) *G11C* 11/4091 (2006.01) *G11C* 11/408 (2006.01)

(21) 출원번호

10-2007-0140489

(22) 출원일자

2007년12월28일

심사청구일자

2007년12월28일

2007년12월28일

(72) 발명자

(71) 출원인

장지은

경기 용인시 죽전동 우미1차 303-2002

경기 이천시 부발읍 아미리 산136-1

(74) 대리인

특허법인 신성

전체 청구항 수 : 총 21 항

#### (54) 반도체 메모리장치의 리드 제어장치 및 방법

#### (57) 요 약

본 발명은 반도체 메모리장치에서 리드 동작시에 입출력센스앰프(IOSA)를 동작시키는 제어신호의 타이밍을 제어하는 리드 제어장치 및 방법에 관한 것이다. 본 발명은, 리드 동작시에 컬럼 어드레스의 펄스 폭을 검출하고, 검출된 신호를 이용해서 입출력센스엠프 제어신호를 발생시키도록 제어하는 것을 특징으로 한다. 따라서 본 발명은 컬럼 어드레스의 펄스폭을 검출하기 위한 구성과, 상기 펄스폭이 검출된 후 이를 이용하여 입출력센스엠프의 제어신호를 발생하기 위한 구성 등을 포함하여 이루어진다. 이와 같은 본 발명의 특징 및 구성에 따르면, 모든 스큐에서 컬럼 어드레스 펄스신호의 펄스 폭이 변하더라도 입출력센스 엠프의 제어신호가 상기 컬럼 어드레스 펄스신호의 펄스 폭 변화량에 기초하여 변화하므로서, 입출력센스엠프의 오동작을 방지하는 효과를 얻는다.

#### 대 표 도 - 도8

## 특허청구의 범위

#### 청구항 1

컬럼 커맨드를 입력하고, 컬럼 어드레스 인에이블신호를 발생하는 컬럼 어드레스 인에이블 신호 발생수단; 및 상기 컬럼 어드레스 인에이블신호의 펄스폭을 검출하고, 검출된 신호에 기초하여 입출력센스엠프의 제어신호를 생성하는 입출력센스엠프 제어신호 생성수단을 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드 제어장 치.

#### 청구항 2

제 1 항에 있어서,

상기 입출력센스엠프 제어신호 생성수단에서 생성된 입출력센스엠프 제어신호를 기결정된 일정량만큼 지연시키는 지연수단을 더 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장치.

## 청구항 3

제 1 항에 있어서,

상기 입출력센스엠프 제어신호 생성수단은, 컬럼 어드레스의 펄스폭을 검출하기 위한 검출부와;

상기 펄스폭이 검출된 후 이를 이용하여 입출력센스엠프의 제어신호를 발생하기 위한 펄스 발생부를 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드 제어장치.

### 청구항 4

제 3 항에 있어서,

상기 펄스 검출부는, 컬럼 어드레스 인에이블신호와, 상기 컬럼 어드레스 인에이블신호를 반전시키고 일정시간 지연시킨 신호를 노아 연산하는 노아연산기;

상기 노아연산기의 출력을 반전시키는 인버터를 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장 치.

#### 청구항 5

제 4 항에 있어서,

상기 펄스 검출부는, 상기 컬럼 어드레스 인에이블 신호를 일정시간 지연시킨 만큼의 펄스폭을 갖고, 상기 컬럼 어드레스 인에이블 신호의 폴링 에지에서 로우 펄스를 발생하도록 제어하는 것을 특징으로 하는 반 도체 메모리장치의 리드제어장치.

## 청구항 6

제 3 항에 있어서,

상기 펄스 발생부는, 검출된 펄스폭 만큼 지연 후에 입출력센스엠프 제어신호를 발생하는 것을 특징으로 하는 반도체 메모리장치의 리드 제어장치.

## 청구항 7

제 6 항에 있어서,

상기 펼스 발생부는, 컬럼 어드레스 인에이블 신호의 폴링 에지에서 발생된 로우 펼스를 이용해서 입출력센스 엠프 제어신호의 펼스폭을 생성하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장치.

## 청구항 8

제 7 항에 있어서,

상기 펄스 발생부는, 컬럼 어드레스 인에이블 신호의 폴링 에지에서 발생된 로우 펄스를 래치시키는 래치;

상기 로우 펄스를 기결정된 시정수만큼 지연시키고, 상기 래치에 제공되는 지연부;

상기 래치의 출력과 상기 지연부의 출력으로부터 입출력센스엠프의 제어신호를 발생하는 연산기를 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장치.

#### 청구항 9

제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 컬럼 커맨드는, 리드 커맨드인 것을 특징으로 하는 반도체 메모리장치의 리드 제어장법.

#### 청구항 10

컬럼 어드레스를 입력하고, 상기 컬럼 어드레스 인에이블신호에 제어되어 컬럼 어드레스 신호를 디코딩하는 컬럼 어드레스 신호 발생수단;

컬럼 커맨드를 입력하고, 컬럼 어드레스 인에이블신호를 발생하는 컬럼 어드레스 인에이블 신호 발생수단;

상기 컬럼 어드레스 인에이블신호의 펄스폭을 검출하고, 검출된 신호에 기초하여 입출력센스엠프의 제어신호를 생성하는 입출력센스엠프 제어신호 생성수단을 포함하여 구성되고,

상기 컬럼 어드레스신호에 의해 비트라인의 데이터가 로컬데이터라인으로 전송되고, 로컬데이터라인의 데이터가 상기 입출력센스엠프의 제어신호에 의해 인에이블된 입출력센스엠프에서 증폭되어 글로벌라인으로 전송되도록 제어하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장치.

#### 청구항 11

제 10 항에 있어서,

상기 입출력센스엠프 제어신호 생성수단에서 생성된 입출력센스엠프 제어신호를 기결정된 일정량만큼 지연시키는 지연수단을 더 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장치.

#### 청구항 12

제 10 항에 있어서,

상기 입출력센스엠프 제어신호 생성수단은, 컬럼 어드레스의 펄스폭을 검출하기 위한 검출부와;

상기 펄스폭이 검출된 후 이를 이용하여 입출력센스엠프의 제어신호를 발생하기 위한 펄스 발생부를 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드 제어장치.

#### 청구항 13

제 12항에 있어서,

상기 필스 검출부는, 컬럼 어드레스 인에이블신호와, 상기 컬럼 어드레스 인에이블신호를 반전시키고 일정시간 지연시킨 신호를 노아 연산하는 노아연산기;

상기 노아연산기의 출력을 반전시키는 인버터를 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장 치.

## 청구항 14

제 13항에 있어서,

상기 펄스 검출부는, 상기 컬럼 어드레스 인에이블 신호를 일정시간 지연시킨 만큼의 펄스폭을 갖고, 상기 컬럼 어드레스 인에이블 신호의 폴링 에지에서 로우 펄스를 발생하도록 제어하는 것을 특징으로 하는 반 도체 메모리장치의 리드제어장치.

## 청구항 15

제 12 항에 있어서.

상기 펄스 발생부는, 검출된 펄스폭 만큼 지연 후에 입출력센스엠프 제어신호를 발생하는 것을 특징으

로 하는 반도체 메모리장치의 리드 제어장치.

#### 청구항 16

제 15 항에 있어서,

상기 펼스 발생부는, 컬럼 어드레스 인에이블 신호의 폴링 에지에서 발생된 로우 펼스를 이용해서 입출력센스 엠프 제어신호의 펄스폭을 생성하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장치.

#### 청구항 17

제 16 항에 있어서,

상기 펄스 발생부는, 컬럼 어드레스 인에이블 신호의 폴링 에지에서 발생된 로우 펄스를 래치시키는 래치;

상기 로우 펄스를 기결정된 시정수만큼 지연시키고, 상기 래치에 제공되는 지연부;

상기 래치의 출력과 상기 지연부의 출력으로부터 입출력센스엠프의 제어신호를 발생하는 연산기를 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드제어장치.

#### 청구항 18

제 10 항 내지 제 17 항 중 어느 한 항에 있어서,

상기 컬럼 커맨드는, 리드 커맨드인 것을 특징으로 하는 반도체 메모리장치의 리드 제어장법.

#### 청구항 19

컬럼 어드레스를 입력하고, 상기 컬럼 어드레스 인에이블신호에 제어되어 컬럼 어드레스 신호를 디코딩하는 컬럼 어드레스 신호 디코딩 단계;

컬럼 커맨드를 입력하고, 컬럼 어드레스 인에이블신호를 발생하는 컬럼 어드레스 인에이블 신호 발생 단계;

상기 컬럼 어드레스 인에이블신호의 펄스폭을 검출하고, 검출된 신호에 기초하여 입출력센스엠프의 제어신호를 생성하는 입출력센스엠프 제어신호 생성 단계;

상기 컬럼 어드레스신호에 의해 비트라인의 데이터가 로컬데이터라인으로 전송되는 제 1 전송단계;

상기 로컬데이터라인의 데이터가 상기 입출력센스엠프의 제어신호에 의해 인에이블된 입출력센스엠프에서 증폭되어 글로벌라인으로 전송되도록 제어하는 제 2 전송단계를 포함하는 것을 특징으로 하는 반도체 메모리장치의리드제어방법.

## 청구항 20

제 19 항에 있어서,

상기 입출력센스엠프 제어신호 생성단계는, 상기 컬럼 어드레스 인에이블 신호를 일정시간 지연시킨 만큼의 필 스폭을 갖고, 상기 컬럼 어드레스 인에이블 신호의 폴링 에지에서 로우 펄스를 발생하도록 제어하는 펄스폭 검 출 단계;

상기 컬럼 어드레스 인에이블 신호의 폴링 에지에서 발생된 로우 펄스를 이용해서 입출력센스엠프 제어신호의 펄스폭을 생성하는 펄스 생성 단계를 포함하는 것을 특징으로 하는 반도체 메모리장치의 리드제어방법.

#### 청구항 21

제 19항 또는 제 20 항에 있어서,

상기 컬럼 커맨드는, 리드 커맨드인 것을 특징으로 하는 반도체 메모리장치의 리드 제어장법.

## 명 세 서

## 발명의 상세한 설명

## 기술분야

본 발명은 반도체 메모리장치에 관한 것으로, 더욱 상세하게는 리드 동작시에 입출력센스앰프(IOSA)를 동작시키는 제어신호의 타이밍을 제어하는 리드 제어장치 및 방법에 관한 것이다.

## 배경기술

- VAM을 비롯한 반도체 메모리장치는, 데이터를 저장하기 위한 단위 메모리 셀의 집합체인 메모리 셀 어레이와, 원하는 데이터 입출력 동작을 제어하기 위한 주변회로로 구성된다.

- <3> 메모리 셀 어레이는 흔히 워드라인으로 불리우는 다수의 로우(ROW)와 흔히 비트라인으로 불리우는 다수의 컬럼(Column)으로 이루어진 매트릭스 형태를 이루고 있다. 각각의 로우와 컬럼에는 소정의 어드레스가 할당되 어 있으며, 특정 로우를 지정하기 위해서 로우 어드레스가, 특정 컬럼을 지정하기 위해서 컬럼 어드레스가 사용된다.

- <4> 로우 어드레스와 컬럼 어드레스는 커맨드와 함께 외부로부터 인가된 어드레스 신호를 디코딩하여 생성하며, 특히 리드/라이트 동작시 컬럼 어드레스에 의해 정해진 특정 비트라인에 대응하는 컬럼 선택신호의 활성화 구간을 정의하기 위하여 커맨드 신호를 받아 생성된 컬럼 어드레스 인에이블 신호가 사용된다.

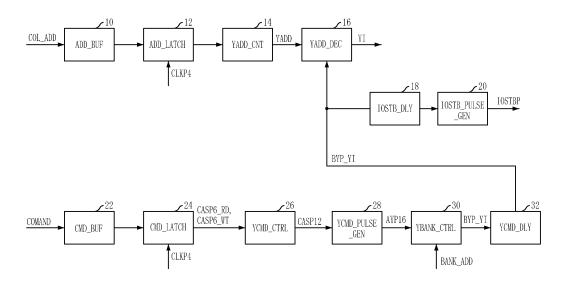

- <5> 도 1은 일반적인 동기식 반도체 메모리장치의 컬럼 경로와 함께, 입출력센스엠프(IOSA)를 동작시-키는 제어신호인 IOSTBp를 발생시키기 위한 블록도이다.

- <6> 도시하고 있는 바와 같이, 컬럼 경로에는 N+1 비트의 어드레스신호(COL\_ADD)를 버퍼링하기 위한 어드레스 버퍼(Add\_buf; 10), 어드레스 버퍼(10)의 출력신호를 내부 클럭(CLKp4)으로 래치하기 위한 어드레스 래치(ADD\_Latch; 12), 어드레스 래치(12)의 출력신호를 카운팅하여 순차적인 어드레싱을 가능하게 하는 컬럼 어드레스 카운터(Yadd\_CNT; 14), 칼럼 어드레스 인에이블 신호(BYP Yi)에 응답하여 컬럼 어드레스 카운터(1 4)의 출력신호를 디코딩하여 컬럼 어드레스 신호(Yi)를 생성하기 위한 컬럼 어드레스 디코더(Yadd\_dec; 16)을 포함하여 구성된다.

- <7> 또한, 전술한 바와 같이 컬럼 어드레스 인에이블 신호(BYP Yi)는 커맨드 신호를 받아 생성되는데, /RAS,/CAS,/WE 등의 커맨드신호(COMAND)를 버퍼링하기 위한 커맨드 버퍼(CMN\_buf;22), 커맨드 버퍼(22)의 출력신호를 내부 클럭(CLKp4)으로 래치하기 위한 커맨드 래치(CMD\_latch; 24), 커맨드 래치(24)의 출력신호를 디코딩하여 내부 커맨드 신호를 생성하기 위한 커맨드 디코더(YCMD\_CTRL;26) 및 상기 커맨드 디코더(26)로부터 출력된 내부 커맨드 신호를 입력받아 컬럼 어드레스 인에이블 신호(BYP\_Yi)를 생성하기 위한 컬럼 어드레스 인에이블 신호 생성기가 커맨드의 경로를 형성한다. 상기 컬럼 어드레스 인에이블 신호 생성기의 구성은, 상기 커맨드 디코더(26)로부터 생성된 신호를 내부 필스를 적용하여 필스 폭(pulse width)을 결정하는 필스 발생기(YCMD\_PULSE\_GEN; 28), 상기 필스 발생기(28)에서 발생된 AYP16 신호가 각각의 뱅크로 뿌려지게 되고, 뱅크에서는 뱅크 어드레스(Bank\_add)와 만나 해당 뱅크만을 동작시키는 뱅크 제어부(YBANK\_CTRL;30), 상기 뱅크제어부(30)에서 출력되는 컬럼 어드레스 인에이블 신호(BYP\_Yi)가 상기 컬럼 어드레스 신호(Yi)와 만나도록 준비시키는 지연부(YCMD\_DLY; 32)로 구성된다. 따라서 상기 컬럼 어드레스 인에이블 신호(BYP\_Yi)가 컬럼 어드레스 디코더(16)에서 컬럼 어드레스신호(Yi)를 인에이블시키게 된다.

- 전편, 상기와 같은 과정을 통해서 생성된 컬럼 어드레스 인에이블 신호(BYP\_Yi)는, 리드 동작시에 IOSA 동작제어를 위한 IOSTBp 신호를 발생시키기 위해 이용되어진다. 즉, 도시하고 있는 바와 같이 상기 컬럼 어드레스 인에이블 신호(BYP\_Yi)가 지연부(IOSTB\_DLY; 18)에서 일정시간 지연된 후에 펄스 발생기(IOSTB\_PULSE\_GEN; 20)에서 펄스 폭을 재 조정하여 IOSTBp신호가 발생되어진다.

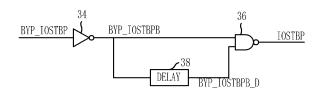

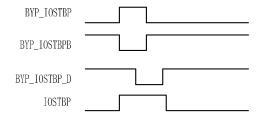

- <9> 도 2는 종래 리드 제어장치에서 펄스 발생기(20)의 상세 구성도를 도시하고 있고, 도 3은 펄스 발생기(20)의 타이밍도를 도시하고 있다.

- <10> 종래 반도체 메모리장치의 리드 제어장치의 동작과정을 살펴보면, 외부에서 리드 커맨드와 컬럼 어드레스가 입력되면, 커맨드는 커맨드 버퍼와 커맨드 래치(22,24)를 거쳐서 읽기 또는 쓰기 동작시에 인에이블, 즉 하이레벨 펄스를 발생시키는 신호(Casp6\_rd, Casp6\_wt)를 발생한다.

- <11> 컬럼 어드레스 신호(Yi)가 발생되야 하는 경우는, 리드/라이트 두 경우이다. 따라서 라이트 커맨드가 입력되었을 때, 커맨드 디코딩이 이루어져서 Casp6\_wt와 Casp12를 만들고, 이 신호가 내부 펄스 발생기(28)에서 펄스폭이 결정되어 AYP16신호를 발생한다. 상기 AYP16 신호는 각각의 뱅크로 뿌려지게 되고, 이때 뱅크

제어부(30)에서 해당 뱅크만이 동작되도록 제어하는 신호(BYP\_Yi)를 발생한다. 이렇게 발생된 BYP\_Yi 신호는 지연부(32)에서 커맨드와 어드레스가 만날 준비를 한다.

- <12> 그리고 리드 커맨드시 함께 입력된 컬럼 어드레스는, 어드레스버퍼(10), 어드레스 래치(12), 그리고 카운터(14)를 거쳐 컬럼 어드레스 디코더(16)에 입력된다. 상기 컬럼 어드레스 디코더(16)는, 상기 지연부(32)에서 제공되는 컬럼 어드레스 인에이블신호(BYP\_Yi)에 제어되어 컬럼 어드레스 신호(Yi)를 인에이블 시킨다.

- <13> 한편, 컬럼 어드레스 디코더(16)에서 컬럼 어드레스 신호(Yi)가 출력될 때, 비트라인(bit)/비트라인바(bitb)에 실려있던 데이터가 SIO 라인/SIOB 라인을 거쳐서 LIO 라인/LIOB 라인까지 전달되어진다. 이후 다시 LIO 라인/LIOB 라인에 전달된 데이터는 IOSA에서 증폭되어 GIO 라인/GIOB 라인으로 전달되어진다.

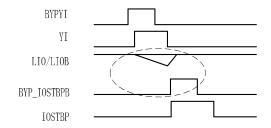

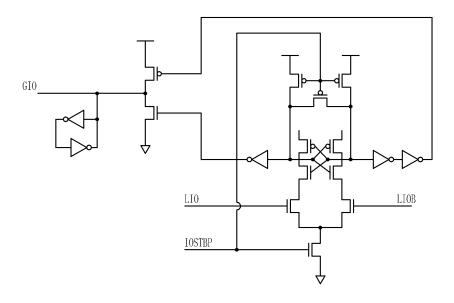

- <14> 도 4 내지 도 6은 컬럼 어드레스 신호(Yi)가 인에이블될 때, LIO 라인/ LIOB 라인에 데이터가 실리는 과정에 따른 동작 타이밍도를 나타내고 있다. 그리고 도 7을 참조하면, 상기 LIO 라인/ LIOB 라인에 실린 데이터가 IOSA에서 증폭되어진 후, GIO 라인/GIOB 라인에 실리기 위한 입출력센스엠프(IOSA)의 회로도를 나타낸다.

- <15> 즉, IOSA 제어신호인 IOSTBp 신호가 인에이블되면, 에지 트리거(edge trigger)인 IOSA가 LIO 라인/ LIOB 라인에 실린 데이터를 감지해서 충분하게 로우 또는 하이상태로 증폭하게 되고, 이 증폭된 신호가 GIO 라인/GIOB 라인에 실리게 된다.

- <16> 여기서 상기 IOSA를 인에이블시키기 위한 IOSTBp 신호는, 도 2에 도시하고 있는 바와 같이, 컬럼 어드레스 인에이블 신호(BYP\_Yi)가 지연부(38)에서 일정시간 지연된 후 펄스 폭을 재 조정하여 발생되어진다.

- <17> 이와 같이 종래 리드 제어장치에서 컬럼 어드레스 신호(Yi), 컬럼 어드레스 인에이블 신호(BYP\_Yi), 그리고 IOSA 제어신호(IOSTBp)는, 각각의 라인에 실린 데이터의 전달을 제어하게 되는데, 스큐(Skew)가 다름으로 인해서 동작상의 오류를 발생시키는 문제점을 야기시킨다.

- <18> 다시 말해서, 단순히 컬럼 어드레스 신호(Yi)의 인에이블 타이밍 후에 LIO 라인/ LIOB 라인 신호가 적당히 증폭되었을 때라고 생각되는 시점까지 많은 양의 지연회로를 사용하여 지연시킨 후에 IOSA 제어신호(IOSTBp)가인에이블 되어진다. 이때 많은 양의 지연회로를 사용하기 위해서는 어쩔 수 없이 많은 단수의 트랜지스터를 거치게 되고, 공급전압(VDD) 또는 트랜지스터의 특성에 따라서 많은 양의 스큐가 발생되어진다.

- <19> 여기서 LIO 라인/ LIOB 라인 신호를 증폭하는 델타(Delta) 량은 컬럼 어드레스 신호(Yi)의 펄스 폭에 의해 좌우된다. 따라서 공급전원이나 트랜지스터의 특성에 따라서 컬럼 어드레스 신호(Yi)의 펄스 폭이 변하는 양과 IOSA 제어신호(IOSTBp)를 만드는 딜레이 양이 다르게 된다면 도 5 또는 도 6과 같이 실패를 발생하게 된다.

- <20> 즉, 도 5에서와 같이 로우 공급전원에서 컬럼 어드레스 신호(Yi)의 펄스 폭이 늘어나는 양보다 IOSA 제어신호(IOSTBp)가 증가하는 양이 더 커서 LIO 라인/ LIOB 라인 신호가 프리차지(Precharge) 되고 있는 상태를 스트로브(strobe) 하는 경우가 발생될 수 있다. 또한, 도 6에서와 같이, 하이 공급전원에서 컬럼 어드레스 신호(Yi)의 펄스 폭이 줄어드는 양보다 IOSA 제어신호(IOSTBp)가 줄어드는 양이 더 작아서 실패를 발생할 수 있다. 따라서 컬럼 어드레스 신호(Yi)의 라이징 에지에서부터 많은 양의 지연회로를 사용하여 IOSA 제어신호(IOSTBp)를 생성하기 위해서는 모든 스큐에 안전하게 동작하도록 하기 위하여 많은 마진(Margin)을 가져가게 되고, 결과적으로 타이밍의 보틀-넥(Bottle-Neck) 현상을 야기시키는 문제점이 있다.

## 발명의 내용

## 해결 하고자하는 과제

- <21> 따라서 상기 문제점을 해결하기 위한 본 발명의 목적은 리드 동작시에 입출력센스앰프(IOSA)를 동작시키는 제어신호의 타이밍을 적절히 제어 가능한 반도체 메모리장치의 리드 제어장치 및 방법을 제공함에 있다.

- <22> 본 발명의 다른 목적은 리드 동작시에 입출력센스엠프를 동작시키기 위한 제어신호가 컬럼 어드레스의 변화에 연동해서 발생할 수 있도록 제어 가능한 반도체 메모리장치의 리드 제어장치 및 방법을 제공함에 있다.

## 과제 해결수단

<23> 상기 목적을 달성하기 위한 본 발명에 따른 반도체 메모리장치의 리드제어장치 및 방법은, 리드 동작시에 컬럼 어드레스의 펄스 폭을 검출하고, 입출력센스엠프 제어신호를 발생시키도록 제어하는 것을 특징으로 한다.

- <24> 따라서 본 발명의 제 1 실시예에 따른 반도체 메모리장치의 리드제어장치는, 컬럼 커맨드를 입력하고, 컬럼 어드레스 인에이블신호를 발생하는 컬럼 어드레스 인에이블 신호 발생수단; 및 상기 컬럼 어드레스 인에이블신호의 필스폭을 검출하고, 검출된 신호에 기초하여 입출력센스엠프의 제어신호를 생성하는 입출력센스엠프 제어신호 생성수단을 포함하여 제공된다.

- <25>

- 또한 본 발명의 제 2 실시예에 따른 반도체 메모리장치의 리드제어장치는, 컬럼 어드레스를 입력하고, 상기 컬럼 어드레스 인에이블신호에 제어되어 컬럼 어드레스 신호를 디코딩하는 컬럼 어드레스 신호 발생수단; 컬럼 커맨드를 입력하고, 컬럼 어드레스 인에이블신호를 발생하는 컬럼 어드레스 인에이블 신호 발생수단; 상기 컬럼 어드레스 인에이블신호의 펄스폭을 검출하고, 검출된 신호에 기초하여 입출력센스엠프의 제어신호를 생성 하는 입출력센스엠프 제어신호 생성수단을 포함하여 구성되고, 상기 컬럼 어드레스신호에 의해 비트라인의 데이 터가 로컬데이터라인으로 전송되고, 로컬데이터라인의 데이터가 상기 입출력센스엠프의 제어신호에 의해 인에이 블된 입출력센스엠프에서 증폭되어 글로벌라인으로 전송되도록 제어한다.

- <27> 그리고 본 발명의 실시예에 따른 반도체 메모리장치의 리드제어방법은, 컬럼 어드레스를 입력하고, 상기 컬럼 어드레스 인에이블신호에 제어되어 컬럼 어드레스 신호를 디코딩하는 컬럼 어드레스 신호 디코딩 단계; 컬럼 커맨드를 입력하고, 컬럼 어드레스 인에이블신호를 발생하는 컬럼 어드레스 인에이블 신호 발생 단계; 상기 컬럼 어드레스 인에이블신호의 펄스폭을 검출하고, 검출된 신호에 기초하여 입출력센스엠프의 제어신호를 생성하는 입출력센스엠프 제어신호 생성 단계; 상기 컬럼 어드레스신호에 의해 비트라인의 데이터가 로컬데이터라인으로 전송되는 제 1 전송단계; 상기 로컬데이터라인의 데이터가 상기 입출력센스엠프의 제어신호에 의해 인에이블된 입출력센스엠프에서 증폭되어 글로벌라인으로 전송되도록 제어하는 제 2 전송단계를 포함하는 것을 특징으로 한다.

#### 直 과

<28> 본 발명은 리드 동작시에 컬럼 어드레스의 펄스 폭을 검출하고, 검출된 신호를 이용해서 입출력센스엠프 제어 신호를 발생시키도록 제어하는 것을 특징으로 하고, 컬럼 어드레스의 펄스폭을 검출하기 위한 구성과, 상기 펄 스폭이 검출된 후 이를 이용하여 입출력센스엠프의 제어신호를 발생하기 위한 구성 등을 포함하여 이루어진다. 이와 같은 본 발명의 특징 및 구성에 따르면, 모든 스큐에서 컬럼 어드레스 펄스신호의 펄스 폭이 변하더라도 입출력센스 엠프의 제어신호가 상기 컬럼 어드레스 펄스신호의 펄스 폭 변화량에 기초하여 변화하므로서, 입출 력센스엠프의 오동작을 방지하는 효과를 얻는다.

## 발명의 실시를 위한 구체적인 내용

- <29> 이하 첨부한 도면을 참조하여 본 발명에 따른 반도체 메모리장치의 리드제어장치 및 방법에 대해서 자세하게 살펴보기로 한다.

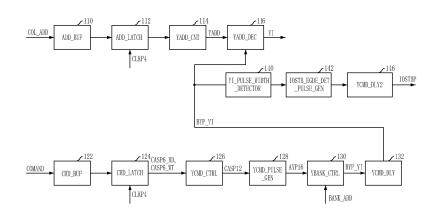

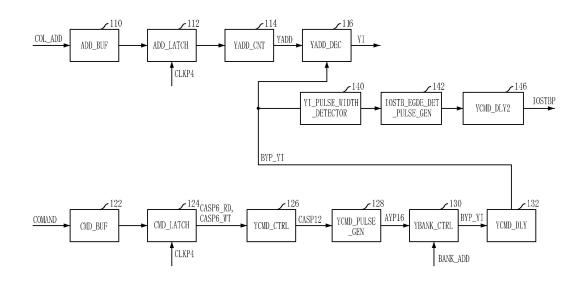

- <30> 도 8은 본 발명에 따른 반도체 메모리장치의 리드제어장치의 블록도를 도시하고 있다.

- <31> 데이터 입출력 패드와 메모리 셀 영역 사이의 데이터 전송을 위한 입출력 데이터라인인 글로벌데이터라인(GIO)과, 메모리 셀 영역 내에서 출력되는 비트라인감지증폭기의 출력을 전송받는 로컬데이터라인(LIO) 사이에 데이터 전송을 위한 회로가 필요하다. 이를 위해서 리드 동작시에 LIO라인에 실린 데이터를 GIO라인으로 전송하기 위하여 도 7에 도시하고 있는 입출력센스엠프(IOSA)를 사용한다. 이때 사용되는 컬럼 어드레스신호 및 컬럼 어드레스 인에이블신호, 그리고 입출력센스엠프 제어신호 등을 발생시키기 위한 회로가 리드제어장치의 구성이다.

- <32> 도시하고 있는 바와 같이, 컬럼 경로에는 N+1 비트의 어드레스신호(COL\_ADD)를 버퍼링하기 위한 어드레스 버퍼(Add\_buf; 110), 어드레스 버퍼(110)의 출력신호를 내부 클럭(CLKp4)으로 래치하기 위한 어드레스 래치(ADD\_Latch; 112), 어드레스 래치(112)의 출력신호를 카운팅하여 순차적인 어드레싱을 가능하게 하는 컬 럼 어드레스 카운터(Yadd\_CNT; 114), 칼럼 어드레스 인에이블 신호(BYP Yi)에 응답하여 컬럼 어드레스 카운터(114)의 출력신호를 디코딩하여 컬럼 어드레스 신호(Yi)를 생성하기 위한 컬럼 어드레스 디코더(Yadd\_dec; 116)을 포함하여 구성된다.

- <33> 또한, 전술한 바와 같이 컬럼 어드레스 인에이블 신호(BYP Yi)는 커맨드 신호를 받아 생성되는데, /RAS,/CAS,/WE 등의 커맨드신호(COMAND)를 버퍼링하기 위한 커맨드 버퍼(CMN\_buf ;122), 커맨드 버퍼(122)의

출력신호를 내부 클럭(CLKp4)으로 래치하기 위한 커맨드 래치(CMD\_latch; 124), 커맨드 래치(124)의 출력신호를 디코딩하여 내부 커맨드 신호를 생성하기 위한 커맨드 디코더(YCMD\_CTRL; 126) 및 상기 커맨드 디코더(126)로부터 출력된 내부 커맨드 신호를 입력받아 컬럼 어드레스 인에이블 신호(BYP\_Yi)를 생성하기 위한 컬럼 어드레스 인에이블 신호 생성기가 커맨드의 경로를 형성한다. 상기 컬럼 어드레스 인에이블 신호 생성기의 구성은, 상기 커맨드 디코더(126)로부터 생성된 신호를 내부 펄스를 적용하여 펄스 폭(pulse width)을 결정하는 펄스 발생기(YCMD\_PULSE\_GEN; 128), 상기 펄스 발생기(128)에서 발생된 AYP16 신호가 각각의 뱅크로 뿌려지게되고, 뱅크에서는 뱅크 어드레스(Bank\_add)와 만나 해당 뱅크만을 동작시키는 뱅크 제어부(YBANK\_CTRL; 130), 상기 뱅크 제어부(130)에서 출력되는 컬럼 어드레스 인에이블 신호(BYP\_Yi)가 상기 컬럼 어드레스 신호(Yi)와만나도록 준비시키는 지연부(YCMD\_DLY; 132)로 구성된다. 따라서 상기 컬럼 어드레스 인에이블 신호(BYP\_Yi)가 된다.

- <34> 한편, 상기와 같은 과정을 통해서 생성된 컬럼 어드레스 인에이블 신호(BYP\_Yi)는, 리드 동작시에 IOSA 동작 제어를 위한 IOSTBp 신호를 발생시키기 위해 이용되어진다. 즉, 도시하고 있는 바와 같이 상기 컬럼 어드레스 인에이블 신호(BYP\_Yi)가 컬럼 어드레스 펼스 검출기(Yi\_PULSE\_WIDTH\_DETECTOR:140)에 입력되어, 컬럼 어드레스 펄스 폭이 검출되고, 상기 컬럼 어드레스 펄스 검출기(140)에서 펄스 폭이 검출되어진 다. 그리고 상기 컬럼 어드레스 펄스 검출기(140)에서 검출된 신호에 기초해서 IOSA 제어신호 펄스 발생기(IOSTB\_EGDE\_DET\_PULSE\_GEN:142)에서 IOSA 제어신호인 IOSTBp의 펄스가 조정되어 발생된다. 상기 IOSA 제어신호 펄스 발생기(142)에서 발생된 IOSA 제어신호는 소정의 지연회로(YCMD\_DLY2; 146)를 거쳐서 발생되어 진다.

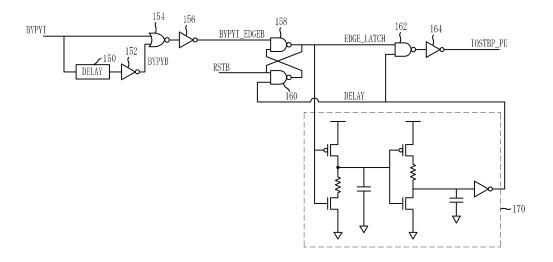

- <35> 도 9는 본 발명의 리드 제어장치에서 컬럼 어드레스 펄스 검출기(140)와, IOSA 제어신호 펄스 발생기(IOSTB\_EGDE\_DET\_PULSE\_GEN :142)의 상세 구성도를 도시하고 있다.

- <36> 컬럼 어드레스 필스 검출기(140)는, 지연부(132)에서 발생된 컬럼 어드레스 인에이블신호(BYP YI)를 입력하고, 소정시간 지연시키는 지연소자(150)와, 상기 지연소자(150)에서 소정시간 지연 된 신호를 인버팅시키는 인버터(152), 그리고 상기 인버터(152)에서 반전된 신호와 상기 컬럼 어드레스 인에이블신호를 노아 연산하는 노아연산기(154); 상기 노아 연산기(154)의 출력을 다시 반전시키는 인버터(156)로 포함된다.

- <37> 그리고 IOSA 제어신호 펄스 발생기(142)는, 상기 컬럼 어드레스 펄스 검출기(140)에서 검출되는 신호를 래치시키는 래치부(158,160), 상기 래치부(158,160)의 출력을 이용하여 PMOS 트랜지스터 및 NMOS 트랜지스터 등을 이용하여 소정량 지연시키는 지연부(170), 그리고 상기 래치부의 출력과 지연부(170)의 출력을 낸드 연산하는 낸 드 연산기(162), 그리고 상기 낸드 연산기(162)의 출력을 반전하는 인버터(164)를 포함한다.

- <38> 상기와 같은 구성으로 이루어진 본 발명에 따른 반도체 메모리장치의 리드제어장치의 동작과정을 살펴보면 다음과 같다.

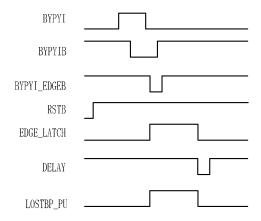

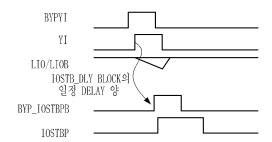

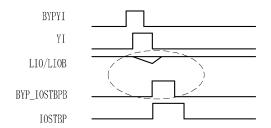

- <39> 도 10은 본 발명에 따른 리드제어장치의 동작 타이밍도를 도시하고 있다.

- <40> 반도체 메모리장치의 리드 제어장치의 동작과정을 살펴보면, 외부에서 리드 커맨드와 컬럼 어드레스가 입력되면, 커맨드는 커맨드 버퍼와 커맨드 래치(122,124)를 거쳐서 읽기 또는 쓰기 동작시에 인에이블, 즉 하이레벨 펄스를 발생시키는 신호(Casp6\_rd, Casp6\_wt)를 발생한다.

- <41> 컬럼 어드레스 신호(Yi)가 발생되야 하는 경우는, 리드/라이트 두 경우이다. 따라서 라이트 커맨드가 입력되었을 때, 커맨드 디코딩이 이루어져서 Casp6\_wt와 Casp12를 만들고, 이 신호가 내부 펄스 발생기(128)에서 펄스폭이 결정되어 AYP16신호를 발생한다. 상기 AYP16 신호는 각각의 뱅크로 뿌려지게 되고, 이때 뱅크제어부(130)에서 해당 뱅크만이 동작되도록 제어하는 신호(BYP\_Yi)를 발생한다. 이렇게 발생된 BYP\_Yi 신호는지연부(312)에서 커맨드와 어드레스가 만날 준비를 한다.

- <42> 그리고 리드 커맨드시 함께 입력된 컬럼 어드레스는, 어드레스버퍼(110), 어드레스 래치(112), 그리고 카운터(114)를 거쳐 컬럼 어드레스 디코더(116)에 입력된다. 상기 컬럼 어드레스 디코더(116)는, 상기 지연부(132)에서 제공되는 컬럼 어드레스 인에이블신호(BYP\_Yi)에 제어되어 컬럼 어드레스 신호(Yi)를 인에이 블시킨다.

- <43> 한편, 컬럼 어드레스 디코더(116)에서 컬럼 어드레스 신호(Yi)가 출력될 때, 비트라인(bit)/비트라인바(bitb)에 실려있던 데이터가 SIO 라인/SIOB 라인을 거쳐서 LIO 라인/ LIOB 라인까지 전달되어진다. 이후 다시 LIO라인/LIOB라인에 전달된 데이터는 IOSA에서 증폭되어 GIO라인/GIOB라인으로 전달되어진다.

- <44> 따라서 도 10은 LIO 라인/ LIOB 라인에 실린 데이터가 IOSA에서 증폭되어진 후, GIO 라인/GIOB 라인에 실리게 되는 과정의 동작 타이밍도를 나타낸다.

- <45> 즉, IOSA 제어신호인 IOSTBp 신호가 인에이블되면, 에지 트리거(edge trigger)인 IOSA가 LIO 라인/ LIOB 라인에 실린 데이터를 감지해서 충분하게 로우 또는 하이상태로 증폭하게 되고, 이 증폭된 신호가 GIO 라인/GIOB라인에 실리게 된다.

- <46> 여기서 상기 IOSA를 인에이블시키기 위한 IOSTBp 신호는, 도 10에 도시하고 있는 바와 같이, 컬럼 어드레스 인에이블 신호(BYP\_Yi)의 펄스폭을 컬럼 어드레스 펄스 검출기(140)에서 우선 검출한다. 따라서 컬럼 어드레스 펄스 검출기(140)는, 컬럼 어드레스 인에이블 신호(BYP\_Yi)와, 이를 소정량 지연하여 반전시킨 신호(BYPYb)를 연산해서, 컬럼 어드레스 인에이블신호의 폴링 에지가 검출되어지는 펄스 폭을 검출한다(BUPYI\_edgeb). 즉, 상기 컬럼 어드레스 펄스 검출기(140)는, 상기 컬럼 어드레스 인에이블 신호를 일정시간 지연시킨 만큼의 펄스폭을 갖고, 상기 컬럼 어드레스 인에이블 신호의 폴링 에지에서 로우 펄스를 발생하도록 제어하는 것을 특징으로 한다.

- <47> 그 다음 IOSA 제어신호 펄스 발생기(142)는, 상기 검출된 컬럼 어드레스 인에이블신호의 펄스폭을 이용해서, 신호를 래치시키고, 래치된 값과 소정만큼 지연된 값을 연산하여 IOSA 제어를 위한 신호를 발생한다. 이때, 래치(158,160)는, 컬럼 어드레스 인에이블 신호의 폴링 에지에서 발생된 로우 펄스를 이용해서 신호를 발생한다. 그리고 상기 래치(158,160)의 펄스 폭은, 상기 래치에 로우신호를 제공하는 지연부(170)에 의해 결정된다. 즉, 상기 지연부(170)에서 상기 로우 펄스를 기결정된 시정수만큼 지연시키는 값에 의해 결정된다. 그리고 상기 래치의 출력과 상기 지연부의 출력이 앤드 연산되어져서 입출력센스엠프의 제어신호를 발생한다.

- <48> 따라서 상기 IOSA 제어신호인 IOSTBp PU는 컬럼 어드레스 인에이블신호의 펄스폭을 검출한 후에 상기 검출된 값을 이용하여 발생되어진다. 즉, 상기 IOSA 제어신호 펄스 발생기(142)는, 컬럼 어드레스 인에이블 신호의 폴링 에지에서 발생된 로우 펄스를 이용해서 입출력센스엠프 제어신호의 펄스폭을 생성하는 것을 특징으로 한다. 그러므로 회로 소자의 스큐로 인하여 발생될 수 있는 상기 컬럼 어드레스 인에이블신호의 펄스 폭 변화가 그대로 적용된 IOSA 제어신호가 발생될 수 있는 것이다.

- <49> 이상 전술한 본 발명의 바람직한 실시예는, 예시의 목적을 위해 개시된 것으로, 리드 동작시에 입출력센스앰프(IOSA)를 동작시키는 제어신호의 타이밍을 제어하는 경우에 적용한다. 따라서 본 발명은 당업 자라면 이하 첨부된 특허청구범위에 개시된 본 발명의 기술적 사상과 그 기술적 범위 내에서 또 다른 다양한 실시예들을 개량, 변경, 대체 또는 부가 등이 가능할 것이다.

## 도면의 간단한 설명

- <50> 도 1은 종래 기술에 따른 반도체 메모리장치의 리드제어장치의 블록도.

- <51> 도 2는 종래 입출력센스엠프의 제어신호를 발생하는 발생기의 상세 구성도.

- <52> 도 3 내지 도 6은 종래 입출력센스엠프의 제어신호의 동작 타이밍도,

- <53> 도 7은 일반적인 입출력센스엠프의 회로도,

- <54> 도 8은 본 발명에 따른 반도체 메모리장치의 리드제어장치의 블록도,

- <55> 도 9는 본 발명에 따른 리드제어장치에서 입출력센스엠프의 제어신호를 발생하는 발생기의 상세 구성도.

- <56> 도 10은 본 발명에 따른 입출력센스엠프의 제어신호의 동작 타이밍도.

- <57> \* 도면의 주요 부분에 대한 부호의 설명 \*

- <58> 110 : 컬럼 어드레스 버퍼 112 : 컬럼 어드레스 래치

- <59> 114 : 컬럼 어드레스 카운터 116 : 컬럼 어드레스 디코더

- <60> 122 : 커맨드 버퍼 124 : 커맨드 래치

- <61> 126 : 커맨드 디코더 130 : 뱅크 제어부

- <62> 132,146 : 지연부 140 : 컬럼 어드레스 펄스폭 검출기

- <63> 128 : 컬럼 어드레스 인에이블 펄스 발생기

## <64> 142 : 입출력센스엠프 펄스 발생기

## 도면

## 도면1

# 도면2

# 도면4

# 도면5

# 도면7

# 도면9