(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-65304

(P2009-65304A)

(43) 公開日 平成21年3月26日(2009.3.26)

(51) Int.Cl.

HO3K 17/687 (2006.01)

F 1

HO3K 17/687

G

テーマコード(参考)

5 J O S S

審査請求 未請求 請求項の数 7 O L (全 13 頁)

(21) 出願番号

特願2007-229643 (P2007-229643)

(22) 出願日

平成19年9月5日 (2007.9.5)

(71) 出願人 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100097445

弁理士 岩橋 文雄

(74) 代理人 100109667

弁理士 内藤 浩樹

(74) 代理人 100109151

弁理士 永野 大介

(72) 発明者 谷内 寛直

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72) 発明者 按田 義治

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

最終頁に続く

(54) 【発明の名称】高周波スイッチ装置

## (57) 【要約】

【課題】トランジスタのオン状態において基板バイアス効果による電流駆動能力の低下を抑制し、低挿入損失、低信号歪を備えた高周波スイッチスイッチ装置を提供する。

【解決手段】スイッチトランジスタ106のソース・ドレインはそれぞれDCカット用の容量110, 111を介して高周波信号の入出力端子101, 102に接続され、スイッチトランジスタ106のゲートには抵抗107を介して第2のDC端子104が接続、固定電位が印加され、ソース・ドレインは抵抗108, 109を介して第1のDC端子103が接続、スイッチトランジスタの制御電位が印加される。また、スイッチトランジスタの基板には、第3のDC端子105が接続され、固定電位が印加される。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

高周波信号の入力、出力端子と、第1、第2、第3の端子と、1ないし複数であるN個のスイッチトランジスタと、スイッチトランジスタと同数の第1の抵抗と、スイッチトランジスタより1個多い第2の抵抗、および第1、第2の容量を備え、

N個のスイッチトランジスタのゲートは、それぞれに対応した第1の抵抗を介して、第2の端子に接続され、

N個のスイッチトランジスタの基板は、第3の端子に接続され、

N個のスイッチトランジスタのソース・ドレインはn番目のスイッチトランジスタのドレンとn+1番目のスイッチトランジスタのソースが接続し、この接続したノードは、それぞれ対応した第2の抵抗を介して、第1の端子に接続され、

1番目のスイッチトランジスタのソースは、第1の容量と対応した第2の抵抗に接続され、第1の容量は高周波信号の入力端子に、対応した第2の抵抗は第1の端子にそれぞれ接続され、

N番目のスイッチトランジスタのドレンは、第2の容量と対応した第2の抵抗に接続され、第2の容量は高周波信号の入力端子に、対応した第2の抵抗は第1の端子にそれぞれ接続され、

第1の端子には第1の固定電位が印加され、

第2の端子にはスイッチトランジスタの制御電位が印加され、

第3の端子には第2の固定電位が印加されることを特徴とする、

高周波スイッチ装置。

**【請求項 2】**

高周波信号の入力、出力端子と、第1、第2、第3の端子と、1ないし複数であるN個のスイッチトランジスタと、スイッチトランジスタと同数の第1の抵抗と、スイッチトランジスタより1個多い第2の抵抗、および第1、第2の容量を備え、

N個のスイッチトランジスタのゲートは、それぞれに対応した第1の抵抗を介して、第2の端子に接続され、

N個のスイッチトランジスタの基板は、第3の端子に接続され、

N個のスイッチトランジスタのソース・ドレンはn番目のスイッチトランジスタのドレンとn+1番目のスイッチトランジスタのソースが接続し、この接続したノードは、それぞれ対応した第2の抵抗を介して、第1の端子に接続され、

1番目のスイッチトランジスタのソースは、第1の容量を介して高周波信号の入力端子に、対応した第2の抵抗を介して第1の端子に接続され、

N番目のスイッチトランジスタのドレンは、第2の容量を介して高周波信号の入力端子に、対応した第2の抵抗を介して第1の端子に接続され、

第1の端子と第3の端子にはスイッチトランジスタの制御電位が印加され、

第2の端子には第1の固定電位が印加されていることを特徴とする、

高周波スイッチ装置。

**【請求項 3】**

請求項1ないし請求項2に記載の高周波スイッチ装置において、特にスイッチトランジスタにデプレッションモードのn型FETを用いることを特徴とする、

高周波スイッチ装置。

**【請求項 4】**

請求項1ないし請求項3のいずれかに記載の高周波スイッチ装置において、スイッチトランジスタを形成する半導体層構造において、チャネル層より深い半導体層に伝導キャリアと逆の電荷を持つキャリアを生成する半導体層を備えるスイッチトランジスタを用いることを特徴とする、

高周波スイッチ装置。

**【請求項 5】**

請求項1ないし請求項4のいずれかに記載の高周波スイッチ装置において、スイッチトランジスタ

10

20

30

40

50

ンジスタの制御電位に、グランド電位と任意の正電位を印加してスイッチトランジスタのオン・オフないしオフ・オンを制御することを特徴とする、

高周波スイッチ装置。

【請求項 6】

請求項 5 に記載の高周波スイッチ装置において、スイッチトランジスタに印加されるハイレベル電位は第 2 の固定電位と同電位であることを特徴とする、

高周波スイッチ装置。

【請求項 7】

請求項 1 および、請求項 3 ないし請求項 6 のいずれかに記載の高周波スイッチ装置において、第 1 固定電位および第 2 の固定電位はそれぞれ、グランド電位であることを特徴とする、

高周波スイッチ装置。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、送受信信号の通過周波数帯域と送受信経路を切り替える高周波スイッチ装置に関する。

【背景技術】

【0002】

携帯電話に代表される無線通信システムでは、通信方式の切替および送受信の切替のため、アンテナと送受信装置とを接続、遮断する高周波スイッチ装置が用いられている。

20

【0003】

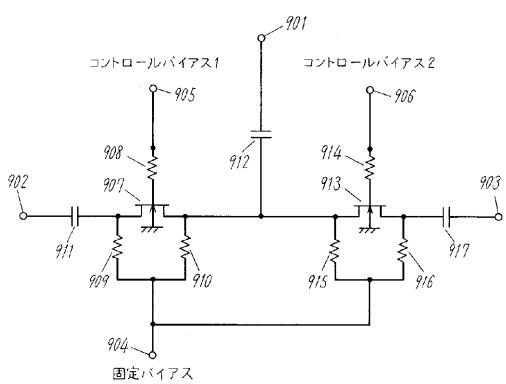

図 9 に一般的な高周波スイッチ装置である S P D T (Single-Pole Double-Throw) スイッチの回路図を示す。図 9 の高周波スイッチでは、第 1 のスイッチトランジスタ 907 のソース・ドレインはそれぞれ容量 912、911 を介して第 1 の R F 端子 901 と第 2 の R F 端子 902 に接続されており、第 2 のスイッチトランジスタ 913 のソース・ドレインはそれぞれ容量 912、917 を介して第 1 の R F 端子 901 と第 3 の R F 端子 903 に接続されている。

【0004】

第 1 の D C 端子 905 にハイ・ローレベルの電位 V 1 を印加して第 1 のスイッチトランジスタ 907 をオン、オフさせることで、第 1 と第 2 の R F 端子間の高周波信号の接続、遮断を制御している。同様に、第 2 の D C 端子 906 にハイ・ローレベルの電位 V 2 を印加することで、第 1 と第 3 の R F 端子間の高周波信号の接続、遮断を制御している。このとき第 1 および第 2 のスイッチトランジスタの基板電位はパッケージのダイパッドを介して接地されている。

30

【0005】

第 1、第 2 のスイッチトランジスタ 907、913 のそれぞれオン、オフは、第 1、第 2 の D C 端子 905、906 に印加された電位と第 3 の D C 端子 904 に印加された固定電位 V 3 との電位差により制御される。スイッチトランジスタがオン状態の場合、スイッチトランジスタのインピーダンスは、負荷インピーダンスに対して十分低く高周波信号の電圧振幅 V A によるスイッチトランジスタのバイアス状態への影響は小さい。

40

【0006】

スイッチトランジスタのオフ状態の場合、高周波信号の電圧振幅 V A により、スイッチトランジスタのソースおよびドレイン電圧は  $V_3 \pm V_A$  の範囲で変動する。このため、スイッチトランジスタをオフ状態に安定させるには、第 1、第 2 の D C 端子にそれぞれ印加されるローレベルでの電圧  $V_{1L}$ 、 $V_{2L}$  および第 3 の D C 端子に印加される固定電圧  $V_3$  は、スイッチトランジスタのゲート閾値電圧に、高周波信号の電圧振幅  $V_A$  をマージン考慮した、 $V_{1L} - V_3 < V_{th} - V_A$  ( $V_{2L} - V_3 < V_{th} - V_A$ ) で設計する必要がある。

【0007】

50

40

50

そのため、スイッチトランジスタをオフさせるためには、第1、第2のコントロール端子のローレベル電位V1、V2を低い電位に、固定電位V3を高い電位で設計する必要がある。第1、第2のDC端子に負電位を印加するには電源回路が複雑かつ大規模化するため、ローレベル電位V1L、V2Lをグランド電位とし、V3を十分高い電位とする電位条件が一般に用いられている。このとき、スイッチトランジスタの基板は接地されているため、基板・ソース間にはスイッチトランジスタのオン、オフに係わらず、-V3の電位差があり、実効的に負の基板バイアスが印加された状態となる。

#### 【0008】

なお、この出願の発明に関する先行技術文献情報としては、例えば、特許文献1が知られている。

10

#### 【特許文献1】特開2004-320439号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

上記のバイアス条件で動作するスイッチトランジスタの動作における負の基板バイアスの影響について述べる。

#### 【0010】

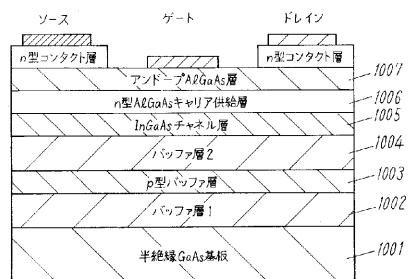

図10にスイッチトランジスタとして用いられる、ガリウム砒素電界効果トランジスタ(GaAs FET)の断面構造の例を示す。半絶縁基板1001上に、アンドープバッファ層1002、p型バッファ層1003、アンドープバッファ層1004、チャネル層1005、n型キャリア供給層1006、アンドープバリア層1007の順に半導体層が形成されている。

20

#### 【0011】

GaAs-FETのオフ状態において、ドレイン・ソース間を、バッファ層および基板を介した微小なドレンリーク電流が流れ、高周波スイッチ装置のアイソレーション特性の劣化および、信号歪みの要因となる。そこで、チャネルの伝導キャリアと異なる電荷を供給する半導体層をバッファ層に形成し、伝導キャリアに対してエネルギーレベルを高くすることで、バッファ層、基板に入る伝導キャリアを抑制し、ドレンリーク電流を抑制する。図10の断面構造例では、p型バッファ層1003がドレンリーク電流低減を目的とした半導体層である。

30

#### 【0012】

前述したように、スイッチトランジスタのソース・ドレインには第3のDC端子よりV3が印加され、スイッチトランジスタの基板はパッケージのダイパッドを介して接地されるため、スイッチトランジスタの基板・ソースには実効的に負の基板バイアス-V3が印加される。

#### 【0013】

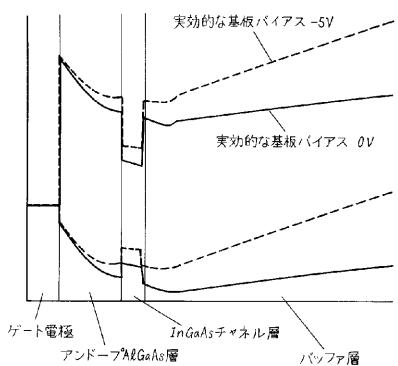

図7は、図10のGaAs-FETの断面A-A'において実効的な基板バイアス0Vおよび-5V印加された状態におけるコンダクションバンド、バレンスバンドをそれぞれ示す。この図から、基板バイアス-5Vにおけるコンダクションバンドは0Vにおけるそれに対して、チャネル層を含めたバンド全体が持ち上がっていることがわかる。

40

#### 【0014】

結果、ゲート閾値電圧のシフトが発生、スイッチ素子の電流駆動能力が低下し、高周波信号損失の増加、信号歪の増加となる。特に、p型半導体層をバッファ層に有する半導体層構造の場合、チャネル層に比較的近いp型半導体層に電界が集中、それに引っ張られる形でチャネル層のポテンシャルが持ち上がるためスイッチトランジスタの電流駆動能力の低下は大きくなる。

#### 【0015】

つまり、従来の高周波スイッチ装置における、スイッチトランジスタのソース、ドレンに固定電位を印加し、ゲートにハイレベルもしくはローレベルの制御電位を印加する制御方法では、スイッチトランジスタのオフ状態におけるアイソレーション、信号歪み特性

50

と、スイッチ素子のオン状態における挿入損失、信号歪み特性にトレードオフの関係を有する。

#### 【0016】

本発明は、このような従来の高周波スイッチ装置におけるトレードオフの関係を鑑みてなされたものであり、その目的はスイッチトランジスタのオン状態において基板バイアス効果による電流駆動能力の低下を抑制し、スイッチトランジスタのオン状態、オフ状態における高周波特性のトレードオフを解消するものである。

#### 【課題を解決するための手段】

#### 【0017】

第1の発明の高周波スイッチ装置は、高周波信号の入力、出力端子と、第1、第2、第3の端子と、1ないし複数であるN個のスイッチトランジスタと、スイッチトランジスタと同数の第1の抵抗と、スイッチトランジスタより1個多い第2の抵抗、および第1、第2の容量を備え、

10

N個のスイッチトランジスタのゲートは、それぞれに対応した第1の抵抗を介して、第2の端子に接続され、

N個のスイッチトランジスタの基板は、第3の端子に接続され、

N個のスイッチトランジスタのソース・ドレインはn番目のスイッチトランジスタのドレインとn+1番目のスイッチトランジスタのソースが接続し、この接続したノードは、

それぞれ対応した第2の抵抗を介して、第1の端子に接続され、

1番目のスイッチトランジスタのソースは、第1の容量と対応した第2の抵抗に接続され、第1の容量は高周波信号の入力端子に、対応した第2の抵抗は第1の端子にそれぞれ接続され、

20

N番目のスイッチトランジスタのドレインは、第2の容量と対応した第2の抵抗に接続され、第2の容量は高周波信号の入力端子に、対応した第2の抵抗は第1の端子にそれぞれ接続され、

第1の端子には第1の固定電位が印加され、

第2の端子にはスイッチトランジスタの制御電位が印加され、

第3の端子には一定の電位が印加されることを特徴とする、

高周波スイッチ装置である。

#### 【0018】

第2の発明の高周波スイッチ装置は、高周波信号の入力、出力端子と、第1、第2、第3の端子と、1ないし複数であるN個のスイッチトランジスタと、スイッチトランジスタと同数の第1の抵抗と、スイッチトランジスタより1個多い第2の抵抗、および第1、第2の容量を備え、

30

N個のスイッチトランジスタのゲートは、それぞれに対応した第1の抵抗を介して、第2の端子に接続され、

N個のスイッチトランジスタの基板は、第3の端子に接続され、

N個のスイッチトランジスタのソース・ドレインはn番目のスイッチトランジスタのドレインとn+1番目のスイッチトランジスタのソースが接続し、この接続したノードは、それぞれ対応した第2の抵抗を介して、第1の端子に接続され、

40

1番目のスイッチトランジスタのソースは、第1の容量を介して高周波信号の入力端子に、対応した第2の抵抗を介して第1の端子に接続され、

N番目のスイッチトランジスタのドレインは、第2の容量を介して高周波信号の入力端子に、対応した第2の抵抗を介して第1の端子に接続され、

第1の端子と第3の端子にはスイッチトランジスタの制御電位が印加され、

第2の端子には第1の固定電位が印加されていることを特徴とする、

高周波スイッチ装置である。

#### 【0019】

第3の発明は、第1ないし第2の発明の高周波スイッチ装置において、特にスイッチトランジスタにデプレッションモードのn型FETを用いることを特徴とする、

50

高周波スイッチ装置である。

【0020】

第4の発明は、第1ないし第3の発明の高周波スイッチ装置において、スイッチトランジスタを形成する半導体層構造において、チャネル層より深い半導体層に伝導キャリアと逆の電荷を持つキャリアを生成する半導体層を備えるエピタキシャル構造上に形成されたスイッチトランジスタを用いることを特徴とする。

高周波スイッチ装置である。

【0021】

第5の発明は、第1ないし第4の発明の高周波スイッチ装置において、スイッチトランジスタの制御電位に、グランド電位と任意の正電位を印加してスイッチトランジスタのオン・オフないしオフ・オンを制御することを特徴とする。

高周波スイッチ装置である。

【0022】

第6の発明は、第5の発明の高周波スイッチ装置において、スイッチトランジスタに印加されるハイレベル電位は第2の固定電位と同電位であることを特徴とする。

高周波スイッチ装置である。

【0023】

第7の発明は、第1および、第3ないし第6の発明のいずれかの高周波スイッチ装置において、第1固定電位および第2の固定電位はそれぞれ、グランド電位であることを特徴とする。

高周波スイッチ装置である。

【発明の効果】

【0024】

本発明によれば、スイッチトランジスタのオン状態、オフ状態における高周波特性のトレードオフを解消し、低損失、高アイソレーション、低信号歪みの高周波スイッチ装置を提供することができる。

【発明を実施するための最良の形態】

【0025】

(実施の形態1)

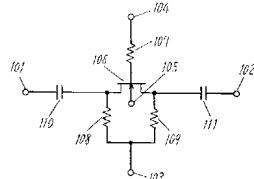

図1に本発明の第1の実施の形態を示す。

【0026】

スイッチトランジスタ106のソース・ドレインはそれぞれDCカット用の容量110, 111を介して高周波信号の入出力端子101, 102に接続されている。また、スイッチトランジスタ106のゲートには抵抗107を介して第2のDC端子104が接続され、固定電位が印加されている。また、ソース・ドレインは抵抗108, 109を介して第1のDC端子103が接続され、スイッチトランジスタの制御電位が印加される。また、スイッチトランジスタの基板には、第3のDC端子105が接続され、固定電位が印加されている。

【0027】

このとき、スイッチトランジスタ106のゲート閾値電圧をVth、第1のDC端子103に印加されるローレベル電位をVL、ハイレベル電位を VH、第2のDC端子104に印加される固定電位をVGG、第3のDC端子105に印加される電位をVBBとすると、 $V_{GG} - V_L > V_{th}$ となるVLが印加されたとき、スイッチトランジスタはオン状態となる。尚、 $V_{th}$ に対して $V_{GG} - V_L$ を大きくすることで、スイッチトランジスタのドレン電流を上げ、低挿入損失、低信号歪とすることができます。また、 $V_{GG} - V_H < V_{th}$ となるVHが印加されたとき、スイッチトランジスタはオフ状態となる。

【0028】

従来の高周波スイッチ装置の場合、ソース・ドレインに高い固定電位を印加し、基板を接地した状態で動作させるため、前述したように実効的に負の基板バイアスが印加された状態となるため、チャネルのコンダクションバンドが持ち上がり、同一のゲート電位にお

10

20

30

40

50

いて生成されるキャリア密度は、オン、オフ状態に係わらず低くなる。

#### 【0029】

これに対し、本発明の第1の実施の形態ではスイッチトランジスタがオンの場合、スイッチトランジスタ106のソース電位はVL、基板電位はVBBとなり、実効的な基板バイアスはVBB-VLと任意のバイアス状態で動作させることが可能となる。また、ソース・ドレインのローレベル電位VLと基板電位VBBを等しい電位としてすることで、基板バイアスを0Vとし、基板バイアスによるキャリア密度の低減を効果を排除することが可能となる。また、VBB > VLとして設計することで、キャリア密度を高くし、低挿入損失、低信号歪を実現することも可能である。

#### 【0030】

また、スイッチトランジスタがオフの場合、スイッチトランジスタ106のソース電位はVH、基板電位はVBBとなり、実効的な基板バイアスはVBB-VHと任意のバイアス状態で動作させることが可能となる。このとき、VHを十分高い電位として負の基板バイアス効果を大きくし、チャネル層におけるキャリアの空乏化により、アイソレーションの向上が可能である。

#### 【0031】

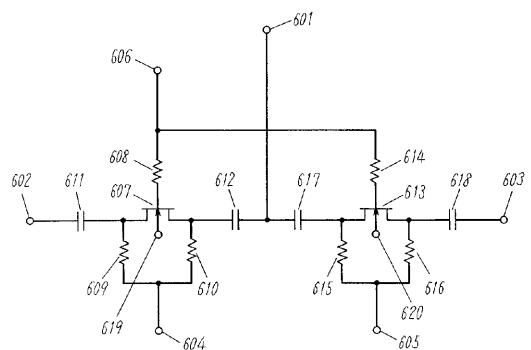

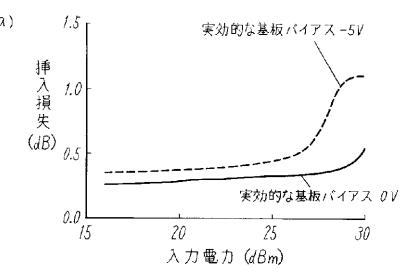

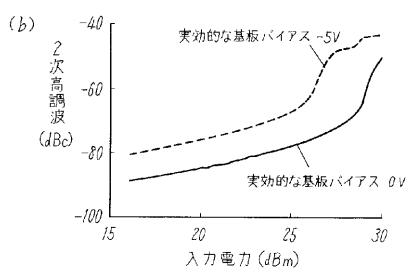

図8に、図9に示す従来構成のSPDTスイッチ装置と、図6に示す本発明の第1の実施の形態の高周波スイッチ装置を用いたSPDTスイッチ装置における挿入損失と2次高調波の特性比較を示す。図6、図9それぞれ同じGaaSデプレッションモードFETをスイッチトランジスタとして用いた。スイッチトランジスタの閾値Vthは-0.5V，ゲート幅は600μmである。

#### 【0032】

図9の高周波スイッチ装置は、第1のDC端子905にハイレベル電位5Vが印加され、第2のDC端子906にローレベル電位0Vが印加され、第3の端子904に固定電位5Vが印加され、それぞれのスイッチトランジスタの基板は接地されている。このとき、第1のスイッチトランジスタ907はオン状態、第2のスイッチトランジスタ913はオフ状態となり、第1のRF端子901と第2のRF端子902が導通状態となる。

#### 【0033】

図6の高周波スイッチ装置では、第1のDC端子604にローレベル電位0Vが印加され、第2のDC端子605にハイレベル電位5Vが印加され、第3のDC端子606には固定電位0Vが印加され、第4、第5のDC端子619、620にはそれぞれ固定電位0Vが印加される。このとき、第1のスイッチトランジスタ607はオン状態、第2のスイッチトランジスタ613はオフ状態となり、第1のRF端子601と第2のRF端子602が導通状態となる。

#### 【0034】

図8(a)に図9に示す従来の高周波スイッチ装置と図6に示す本発明の第1の実施の形態の高周波スイッチ装置を用いたSPDTスイッチ、それぞれの第1のRF端子と第2のRF端子間の挿入損失を示す。従来の高周波スイッチに対して、第1の実施の形態を用いたSPDTスイッチの方が、入力電力25dBm以下において、入力電力に依らず、0.1~0.2dB低いことがわかる。これは、従来の高周波スイッチでは実効的な負の基板バイアス効果によるキャリア減少によりオン抵抗が増加していたが、第1の実施の形態により負の基板バイアスを0として、キャリアの減少とオン抵抗の増加を抑えたため、挿入損失を低減できた。

#### 【0035】

また、従来例の高周波スイッチ装置において、入力電力27dBm付近より挿入損失の増加が見られるのに対して、本発明の第1の実施の形態を用いたSPDTでは、入力電力30dBmまで挿入損失の増加が見られない。これは、従来例の高周波スイッチ装置では負の基板バイアス効果によるキャリア密度の低下のため、低いドレイン・ソース電圧でチャネルがピンチオフし、電流が飽和するためである。本発明の第1の実施の形態では、負の基板バイアスが0であるため、キャリア密度の低下がなく、より高いドレイン・ソース

電圧で線形動作するため、より大きい電力を低損失で導通させることが可能である。

【0036】

図8(b)に図9に示す従来の高周波スイッチ装置と図6に示す本発明の第1の実施の形態の高周波スイッチ装置を用いたSPDTスイッチ、それについて、第1のRF端子から入力したRF信号に対する、第2のRF端子での出力信号の2次高調波を示す。広い入力電力に対して10dB程度の信号歪が低い。これは、挿入損失における議論同様、本発明の第1の実施の形態では、負の基板バイアスが0であるため、キャリア密度の低下がなく、より高いドレイン・ソース電圧で線形動作するため、従来の高周波スイッチ装置に比べて線形性が良いためである。

【0037】

尚、本発明の第1の実施の形態の高周波スイッチ装置による特性改善についてn型のデプレッショングートモードFETをスイッチトランジスタに用いたSPDTスイッチ装置で説明したが、エンハンスマードFETをスイッチトランジスタに用いたスイッチ装置においても同様の効果は得られる。しかし、エンハンスマードFETを用いた高周波スイッチ装置もオフ状態で許容するRF信号の電圧振幅を大きくするためにソース電位を高く設定する場合に限られ、デプレッショングートモードに比べてゲート閾値の高い分、低いドレイン、ソース電位で動作するため、デプレッショングートFETをスイッチトランジスタに用いた場合に比べて効果は低い。

【0038】

また、チャネル層より深い半導体層に伝導キャリアと逆のキャリアを生成するドープ層があるエピ構造を備えたFETをスイッチトランジスタに場合、実効的な負の基板バイアスによるコンダクタンスバンドの持ち上がりは、伝導キャリアと逆のキャリアを生成するドープ層で大きく持ち上がるため、第1の実施の形態の実施による負の基板バイアスの効果低減による、低挿入損失、低信号歪化の効果は大きく、特に、伝導キャリアと逆のキャリアを生成するドープ層がチャネル層に対して1000nm以下と近接して存在する場合は低挿入損失、低信号歪化の効果は大きい。

【0039】

尚、図6の第1の実施の形態を用いたSPDTスイッチの動作について、第1のDC端子604に印加されるローレベル電位、第3のDC端子606に印加される固定電位、第4のDC端子619に印加される固定電位を、それぞれ0Vとして説明をしたが、第1のスイッチトランジスタ607がオンの状態において、第1のDC端子604を介してスイッチトランジスタのソース・ドレインに印加される電位と、第3のDC端子606を介して、スイッチトランジスタのソース・ドレインに印加される電位と、第4のDC端子619を介して基板に印加される電位差、つまり負の基板バイアスを低減する電位条件であれば任意のバイアス条件で動作させることができる。

【0040】

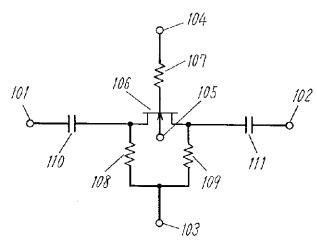

図2に本発明の第2の実施の形態を示す。

【0041】

スイッチトランジスタ205のソース・ドレインはそれぞれDCカット用の容量209, 210を介して高周波信号の入出力端子201, 202に接続されている。また、スイッチトランジスタ205のゲートには抵抗206を介して第2のDC端子204が接続され、スイッチトランジスタの制御電位が印加される。また、ソース・ドレインは抵抗207, 208を介して第1のDC端子203が接続され、固定電位が印加される。また、スイッチトランジスタの基板には第2のDC端子と同電位が印加される。

【0042】

このとき、スイッチトランジスタ205のゲート閾値電圧をV<sub>th</sub>、第2のDC端子204に印加されるローレベル電位をV<sub>L</sub>、ハイレベル電位をV<sub>H</sub>、第1のDC端子203に印加される固定電位をV<sub>DD</sub>、第3のDC端子に印加される電位をV<sub>BB</sub>とすると、V<sub>H</sub> - V<sub>DD</sub> > V<sub>th</sub>となるV<sub>H</sub>が印加されたとき、スイッチトランジスタはオン状態となる。尚、V<sub>th</sub>に対してV<sub>H</sub> - V<sub>DD</sub>を大きくすることで、スイッチトランジスタのド

10

20

30

40

50

レイン電流を上げることができ、低挿入損失、低信号歪化をすることができる。

【0043】

従来の高周波スイッチ装置の場合、第1の端子を介してスイッチトランジスタのソース・ドレインに電位VDDを印加した場合、実効的な負の基板バイアス-VDDが印加されるため、前述したようにチャネルのキャリア密度は減少し、挿入損失、信号歪が大きくなる。これに対して、本発明の第2の実施の形態では、第2のDC端子からスイッチトランジスタのゲート電位と同電位を基板電位として印加するため、実効的な負の基板バイアスはVH-VDDに抑えることができる。

【0044】

また、デプレッションモードFETをスイッチトランジスタに用いた場合、第2のDC端子から印加されるハイレベル電位は、第1の端子に印加される固定電位VDDと同電位で設計することが多いため、スイッチトランジスタがオン状態において、実効的な基板バイアスは0になり、効果が大きい。

【0045】

さらに第1の実施の形態で説明したように、チャネル層より深い半導体層に伝導キャリアと逆のキャリアを生成するドープ層があるエピ構造を備えたFETをスイッチトランジスタに場合、実効的な負の基板バイアスによるコンダクタンスバンドの持ち上がりは大きいため、低挿入損失、低信号歪化の改善効果は大きい。

【0046】

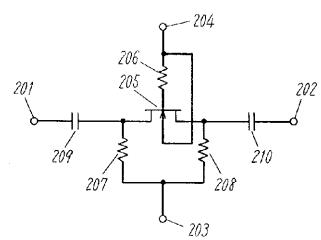

図3に本発明の第3の実施の形態を示す。

【0047】

スイッチトランジスタ305のソース・ドレインはそれぞれDCカット用の容量309, 310を介して高周波信号の入出力端子301, 302に接続されている。また、スイッチトランジスタ305のゲートは抵抗306を介して接地され、ソース・ドレインは抵抗307、308を介して第1のDC端子303が接続され、ハイレベルもしくは、ローレベルの制御電位が印加される。また、スイッチトランジスタの基板は接地される。

【0048】

スイッチの動作および、効果は第1の実施の形態と同様である。スイッチトランジスタのゲート、基板電位を接地する事で、印加電圧の変動、ノイズ等の影響を低減することができ、動作の安定性を向上することができる。また、スイッチトランジスタの基板を設置するため、基板電位を印加する構造およびダイパッドに任意の電位を印加する構造を必要としない利点がある。

【0049】

また、スイッチトランジスタにエンハンスマードFETを用いる場合は、第1のDC端子に印加するローレベル電位は負電位となり負電源を必要とするが、デプレッションモードFETを用いる場合は、負電位を必要としないため、正電源のみで動作が可能である。

【0050】

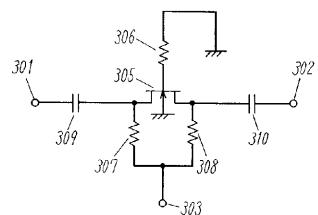

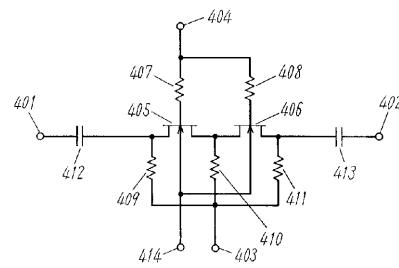

図4に本発明の第4の実施の形態を示す。

【0051】

第1、第2のスイッチトランジスタ405、406のソース・ドレインの一方は互いに接続し、他方はそれぞれDCカット用の容量412, 413を介して高周波信号の入出力端子401, 402に接続されている。第1、第2のスイッチトランジスタ405、406のゲートは抵抗407、408を介して第2のDC端子404に接続され、固定電位が印加されている。第1、第2のスイッチトランジスタ405、406のソース・ドレインは抵抗409、410、411を介して第1のDC端子403に接続され、ハイレベルもしくは、ローレベルの制御電位が印加される。第1、第2のスイッチトランジスタ405、406の基板は第3のDC端子414に接続され、固定電位が印加される。

【0052】

スイッチの動作および、効果は第1の実施の形態と同様である。一般にトランジスタを用いた高周波スイッチにおいて、アイソレーションの向上および、オフ時の許容電圧振幅

10

20

30

40

50

の向上を目的として、複数のスイッチトランジスタを R F 端子間に直列に接続する。本発明は複数のスイッチトランジスタを直列に接続した場合にも用いることが可能である。

**【0053】**

また、第4の実施の形態は、第2、第3の実施の形態の高周波スイッチについても適用可能である。

**【0054】**

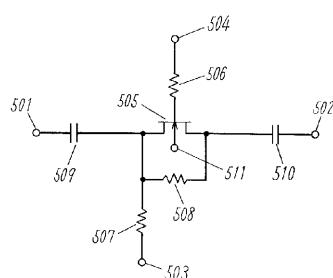

図5に本発明の第5の実施の形態を示す。

**【0055】**

スイッチトランジスタ505のソース・ドレインはそれぞれDCカット用の容量509, 510を介して高周波信号の入出力端子501, 502に接続されている。また、スイッチトランジスタ505のゲートには抵抗506を介して第2のDC端子504が接続され、固定電位が印加されている。また、ソースは抵抗507を介して第1のDC端子503が接続され、スイッチトランジスタの制御電位が印加される。ドレインは抵抗508を介してソースに接続されている。また、スイッチトランジスタの基板には、第3のDC端子511が接続され、固定電位が印加されている。

10

**【0056】**

スイッチの動作および、効果は第1の実施の形態と同様である。スイッチトランジスタのソース・ドレインに接続する抵抗はスイッチトランジスタ1個の場合で2個、スイッチトランジスタN個の場合、N+1個必要となるが、すべて同じ抵抗値である必要はないので、図5のようなレイアウトのスイッチ装置でも同様の効果が得られる。

20

**【0057】**

また、第5の実施の形態における、スイッチトランジスタのソース・ドレインに接続する抵抗のレイアウトは、第2、第3の実施の形態の高周波スイッチについても適用可能である。

**【0058】**

以上、スイッチトランジスタの基板電位の印加手段については、エピ上に電極を形成する、ダイパッドに電位を印加する等、半導体装置で一般に用いられている基板電位印加手段を用いることができる。

**【産業上の利用可能性】**

**【0059】**

本発明の高周波スイッチ装置は、携帯電話などの無線システムにおいて、特に低挿入損失、低信号歪を要求される高周波信号のスイッチング装置に用いることができる。

30

**【図面の簡単な説明】**

**【0060】**

【図1】本発明の高周波スイッチ装置の第1の実施の形態の回路図

【図2】本発明の高周波スイッチ装置の第2の実施の形態の回路図

【図3】本発明の高周波スイッチ装置の第3の実施の形態の回路図

【図4】本発明の高周波スイッチ装置の第4の実施の形態の回路図

【図5】本発明の高周波スイッチ装置の第5の実施の形態の回路図

【図6】本発明の高周波スイッチ装置の第1の実施の形態を用いたS P D Tスイッチ装置の回路図

40

【図7】基板バイアス効果の有無によるバンド図の比較を示す図

【図8】図6と図9のS P D Tスイッチ装置の挿入損失および2次高調波特性の比較を示す図

【図9】従来の高周波スイッチ装置により形成したS P D Tスイッチ装置の回路図

【図10】一般にスイッチトランジスタに用いられるG a A s - H F E Tの断面図

**【符号の説明】**

**【0061】**

101 入出力端子

102 入出力端子

50

- 1 0 3 第 1 の D C 端子

1 0 4 第 2 の D C 端子

1 0 5 第 3 の D C 端子

1 0 6 スイッチトランジスタ

1 0 7 第 1 の 抵抗

1 0 8 , 1 0 9 第 2 の 抵抗

1 1 0 , 1 1 1 D C カット容量

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図 8】

【図 7】

【図 9】

【図 10】

---

フロントページの続き

(72)発明者 河野 広明

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ター&ム(参考) 5J055 AX05 BX17 CX03 CX24 DX12 EX07 EY01 EY10 EY21 EZ12

FX05 FX12 FX32 GX01