#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization International Bureau

#

#### (43) International Publication Date 4 February 2010 (04.02.2010)

# (10) International Publication Number WO 2010/014116 A1

- (51) International Patent Classification: *H02M 3/155* (2006.01)

- (21) International Application Number:

PCT/US2008/075127

(22) International Filing Date:

3 September 2008 (03.09.2008)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/137,741 1 August 2008 (01.08.2008) US 12/202,110 29 August 2008 (29.08.2008) US

(71) Applicant (for all designated States except US): TIGO ENERGY, INC. [US/US]; 170 Knowles Drive, Suite 203, Los Gatos, California 95032 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): AVRUTSKY, Mordechay [IL/IL]; 20 Arbel Street, 44851 Alphai Menashe (IL). AVRUTSKY, Idan [IL/IL]; 20 Arbel Street, 44851 Alphai Menashe (IL). HADAR, Ron [IL/US]; 10337 Tula Lane, Cupertino, California 95014

- (US). **ARDITI, Shmuel** [US/US]; 104 Las Uvas, Los Gatos, California 95032 (US).

- (74) Agent: WARD, John P.; Greenberg Traurig, LLP, 2450 Colorado Avenue, Suite 400 East, Santa Monica, California 90404 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI

[Continued on next page]

#### (54) Title: STEP-UP CONVERTER SYSTEMS AND METHODS

# FIG. 1

(57) Abstract: Methods and systems with a step-up converter are provided based on a boost converter. In one aspect, a step-up converter includes: a boost converter having a first inductor; a second inductor paired on a core with the first inductor; and a rectifier circuit coupled with the second inductor to generate a direct current output.

(BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, Published: NE, SN, TD, TG).

— with international search report (Art. 21(3))

#### STEP-UP CONVERTER SYSTEMS AND METHODS

#### FIELD OF THE TECHNOLOGY

[0001] At least some embodiments disclosed herein relate to voltage conversion in general and, more particularly but not limited to, voltage conversion for direct current energy sources, such as solar panels, fuel cells, etc.

#### **RELATED APPLICATIONS**

[0002] The present application claims priority to provisional U.S. Patent Application Serial No. 61/137,741, filed on August 1, 2008 and entitled "Method and System of New Topology for Enhanced Ultra-Low-Cost, High-Efficiency, DC-to-DC Step-up Converter," and U.S. Utility Application No. 12/202,110 filed August 29, 2008 and entitled "Step-Up Converter Systems and Methods" the disclosures of which are hereby incorporated herein by reference.

### **BACKGROUND**

[0003] Solar panels and other kinds of energy sources produce variable voltages, which, depending on the type of panel, may range anywhere from 10 to 60 volts (and to 70 volts in some instances). It is known to the inventors that there are efforts to combine solar panels with a high-voltage bus (e.g., in the 200 to 600 volt range), which may be implemented via step-up converters that have an output voltage larger than its input voltage.

[0004] A discussion of some current DC-to-DC converter topologies can be found on the web site http://www.boostbuck.com/, which includes discussions of boost-buck switching converter, Cuk Converter, Coupled Inductor Cuk Converter, and Integrated Magnetics Cuk Converter. Other topologies for direct current voltage conversion include boost converter, buck converter, flyback converter, etc.

[0005] A boost converter typically includes at least two switches, such as a diode and a transistor, and at least one energy storage element, such as an inductor. The transistor is used to periodically connect the energy source directly to the energy storage element to store energy into the energy storage element; and the energy storage element causes the converter to output a voltage higher than its input DC voltage. Filters made of capacitors

can be added to the output of the converter to reduce changes in its output voltage. The diode prevents the electric current in the output from flowing backwards.

[0006] However, one of the problems with existing direct current to direct current (DC-to-DC) converters is that in some cases their low efficiency may erase a good part of the gains made by using a high-voltage bus.

[0007] What is needed is an ultra-high-efficiency, DC-to-DC step-up converter that allows voltages to be transformed for a high-voltage bus typically in the 100 to 600 volt range, and that at the same time uses a very few low-cost components.

#### SUMMARY OF THE DESCRIPTION

[0008] Methods and systems with a step-up converter based on a boost converter are described herein. Some embodiments are summarized in this section. In one aspect, a step-up converter includes: a boost converter having a first inductor; a second inductor paired on a core with the first inductor; and a rectifier circuit coupled with the second inductor to generate a direct current output.

[0009] In one embodiment, the rectifier circuit includes a half bridge rectifier circuit. The half bridge rectifier circuit may include a first diode and a first capacitor connected to the second inductor to form a loop to allow electric current to go through the inductor in a first direction; and a second diode and a second capacitor connected to the second inductor to from a loop to allow electric current to go through the inductor in a second direction.

[0010] In one embodiment, the boost converter provides a first portion of a voltage output of the step-up converter; and the rectifier circuit provides a second portion of the voltage output of the step-up converter. The first portion and the second portion of the voltage output of the step-up convert are proportional to a ratio between the first inductor and the second inductor.

[0011] In one embodiment, the boost converter further includes a transistor to implement a switch in the boost converter; the voltage output of the step-up converter is higher than 100 volts; and the transistor has a breakdown voltage lower than 100 volts. In one embodiment, the breakdown voltage of the transistor is lower than 75 volts.

[0012] In one embodiment, the between drain source connection in the transistor is less than ten milliohms when the transistor is in a saturated on mode; and the output voltage of the boost converter is no more than 50 volts.

[0013] In one embodiment, the boost converter further comprises a transistor to implement a switch in the boost converter and a microprocessor coupled to the transistor to control the switch. The microprocessor may be configured to control the switch to adjust an output voltage of the step-up converter.

[0014] In one embodiment, the input to output voltage ratio of the step-up converter is higher than 1:8.

[0015] In one embodiment, outputs of the boost converter and the rectifier circuit are connected in serial.

[0016] In another aspect, a solar panel includes: at least one solar cell to generate a direct current input; a boost converter having a first inductor, the boost converter to receive the direct current input from the at least one solar cell and to generate a first portion of a direct current output; a second inductor paired on a core with the first inductor; and a rectifier circuit coupled with the second inductor to generate a second portion of the direct current output.

[0017] In one embodiment, the direct current output has a voltage no less than 200 volts; and the boost converter operates under 100 volts.

[0018] In another aspect, an energy system includes: a plurality of direct current energy sources; a voltage bus; and at least one step-up converter coupled between the direct current energy sources and the voltage bus, the step-up converter comprising a boost converter having a first inductor, a second inductor paired on a core with the first inductor, a half bridge rectifier circuit coupled with the second inductor, outputs of boost converter and the half bridge rectifier circuit being connected in serial to power the voltage bus.

[0019] In one embodiment, the voltage bus has a voltage equal to or above 200 volts; and the boost converter operates under 50 volts. The energy sources may include solar panels; and the boost converter may include a trench transistor having less than ten milliohms in resistance between drain source when the transistor is in on mode.

[0020] The disclosure includes methods and apparatuses which perform these methods, including data processing systems which perform these methods, and computer readable media containing instructions which when executed on data processing systems cause the systems to perform these methods.

[0021] Other features will be apparent from the accompanying drawings and from the detailed description which follows.

# BRIEF DESCRIPTION OF THE DRAWINGS

[0022] The embodiments are illustrated by way of example and not limitation in the figures of the accompanying drawings in which like references indicate similar elements.

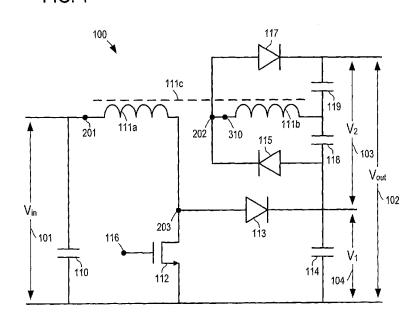

[0023] Figure 1 shows a converter according to one embodiment.

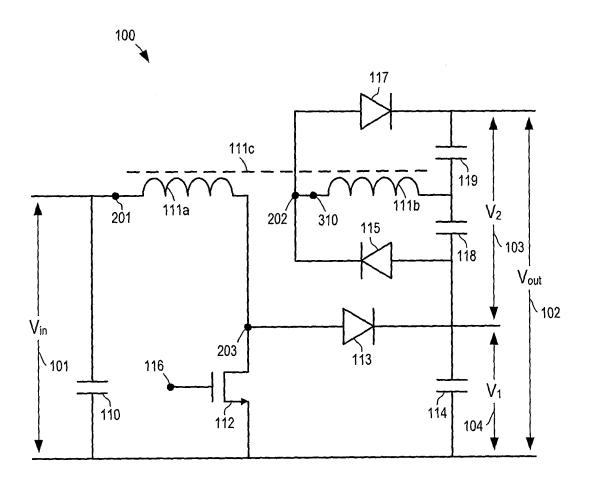

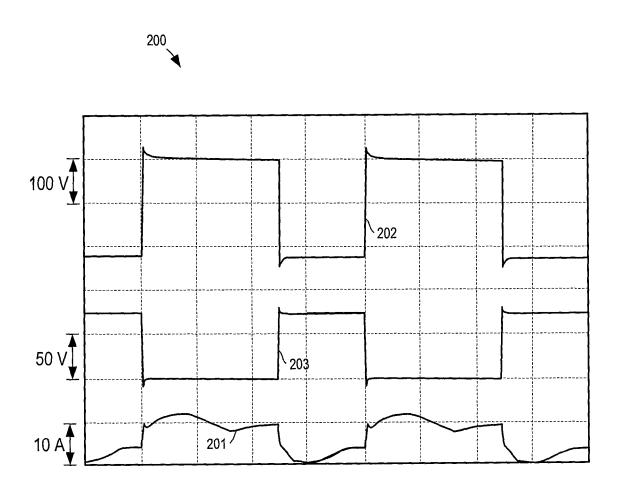

[0024] Figures 2 – 3 illustrate waveforms in various locations in the converter illustrated in Figure 1.

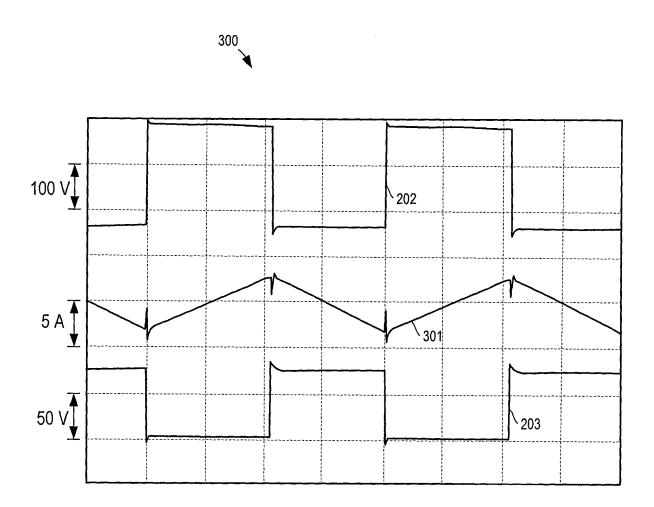

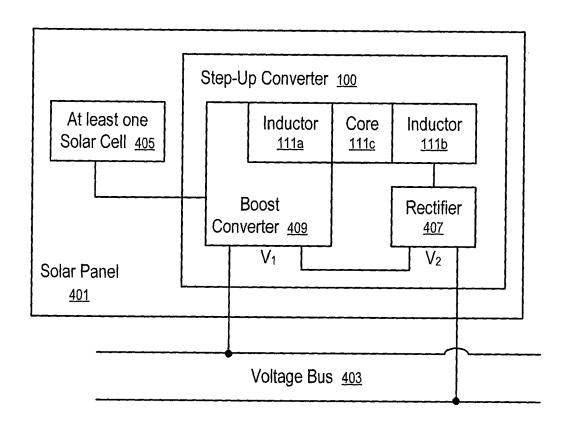

[0025] Figure 4 shows an energy system according to one embodiment.

#### **DETAILED DESCRIPTION**

[0026] The following description and drawings are illustrative and are not to be construed as limiting. Numerous specific details are described to provide a thorough understanding. However, in certain instances, well known or conventional details are not described in order to avoid obscuring the description. References to one or an embodiment in the present disclosure are not necessarily references to the same embodiment; and, such references mean at least one.

[0027] Figure 1 shows a converter according to one embodiment. As opposed to other technologies, such as the boostbuck or other similar technologies, the converter 100 illustrated in Figure 1 has significant advantages, which will be discussed below.

[0028] In Figure 1, the step-up converter 100 includes a boost converter section, including an inductor 111a, a transistor 112, and a diode 113. The booster converter section applies a regular, typical boost converter approach to generate the voltage 104,  $V_1$ , which is higher than the input voltage 101,  $V_{in}$ , of the step-up converter.

[0029] In the boost converter section, the transistor 112 is controlled by the control voltage 116 to periodically connect the inductor 111a to the input voltage  $V_{in}$  to store energy into the inductor and to disconnect the inductor 111a from the input voltage  $V_{in}$  to release energy and thus power the output. When the transistor 112 is in on mode, energy is stored into the inductor 111a to increase the electric current in the inductor 111a; when the transistor 112 is in off mode, energy is released from the inductor 111a to direct the electric current to the output via the diode 113. The diode 113 is used to create a rectified output voltage  $V_1$ .

[0030] In Figure 1, capacitors 110 and 114 are used as filters in the input and output portions of the boost converter section to reduce voltage changes.

[0031] In one embodiment, the voltage V1 of the output of the booster converter section is typically kept at 50 volts or below, allowing the use of a very highly efficient transistor 112 that has low resistance between drain source connection when the transistor 112 is in saturated on mode (i.e., low RDS-on), such as trench transistors.

[0032] In the 50-volt or below operational range, the transistor 112 may typically have a breakdown voltage of 75V-100V and very few milliohms of RDS-on (resistance between drain source connection when the transistor is running in saturated on mode). This low ratio between breakdown voltage and operation voltage is due in large part to

the clean waveforms produced by the design of the converter 100 and the resulting low spikes or ringing associated with it.

[0033] However, the boost converter section alone, having a very typical design, may result in lots of noise on the output voltage  $V_1$  and also in some cases considerable noise on the input voltage  $V_{\rm in}$ .

[0034] Further, to produce an output voltage above 50 volts using the booster converter section along, a high-voltage type of transistor would be used to implement the transistor 112. However, high-voltage transistors are expensive and have high RDS-on.

[0035] Once the breakdown voltage of the transistor 112 voltage exceeds 100 volts, the RDS-on is in the high 10s or even 100s of milliohms, affecting the efficiency dramatically. For example, when the power to be converted is in the high 10s or low 100s of watts, the electric currents can exceed 10 amps. Increasing the RDS-on from a few milliohms to a few hundred milliohms can therefore increase losses by 10 times or more for the converter.

[0036] Further, high voltage peaks require additional components, such as snubbing networks, diodes, and other components to protect the circuitry and reduce noise, all of which result in additional energy losses in the circuitry.

[0037] In Figure 1, another inductor 111b is connected to a half bridge rectifier circuit to generate another rectified output voltage  $V_2$ . The inductor 111a and the inductor 111b are paired on the same core 111c, which has a slight air gap in one embodiment, to transfer energy via inductive coupling. The half bridge rectifier circuit includes diodes 115 and 117 and capacitors 118 and 119 to provide a multiplier voltage from the energy drawn from the inductor 111b.

[0038] In Figure 1, the capacitor 118, the diode 115, and the inductor 111b are used to form a path for electric current flowing in one direction in the inductor 111b and drive a voltage output; and the diode 117, the capacitor 119 and the inductor 111b are used to form another path for electric current flowing in another direction in the inductor 111b.

[0039] In Figure 1, the rectified output voltages  $V_1$  and  $V_2$  are connected in serial to provide the output voltage  $V_{out}$  of the convert.

[0040] In one embodiment, the inductor 111b has a 1:n ratio to inductor 111a, resulting in a second boost voltage 103,  $V_2$ , which has the same 1:n ratio to the first boost voltage 103,  $V_1$ , which was the nominal output voltage. Since the two inductors 111a and 111b are coupled, electric current is taken out of the core 111c both during conduction and during flyback of the transistor 112 (when the transistor 112 is switched off),

resulting in much less ripple on the output voltage and in much better use of the flux capabilities of core 111c.

[0041] The converter 100 can be used as a highly reliable, low-cost add-on to solar panels and other energy sources, such as water- or wind-generators, fuel cells, etc.

[0042] Although Figure 1 illustrates the use of a half bridge rectifier circuit to generate a direct current output from the inductor 111b, other types of known rectifier circuits can also be used.

[0043] Figures 2-3 illustrate waveforms at various locations in the converter illustrated in Figure 1.

[0044] The input current at the point 201 in **Figure 1**, after the input filter capacitor 110 and before the inductor 111a, is illustrated as the waveform 201 in **Figure 2**. The drain voltage on the transistor 112 at the point 203 in **Figure 1** is illustrated as the waveform 203 in **Figures 2** and 3. The output rectifier voltage across diode 115 at the point 202 in **Figure 1** is illustrated as the waveform 202 in **Figures 2** and 3.

[0045] In Figure 3, the electric current measured at the points 201 and 310 in Figure 1 are combined and illustrated as one waveform 301, which shows the core current adjusted for the ratio of inductor 111b and 111a, coupled with core 111c. The waveform 301 of electric current can be measured using an n-factor current probe at the point 310 in Figure 1 and the standard current probe at the point 201 in Figure 1, thus allowing compensation for the higher voltage of 111b.

[0046] In the example illustrated in **Figure 2**, the nominal input voltage  $V_{in}$  is 30 volts; the nominal output voltage  $V_{out}$  is 300 volts; the nominal output power is 180 watts.

In many cases, a simple square wave may be used, because the output voltage is very stable and it does not necessarily require regulation. However, in some cases the control circuitry (not shown in **Figure 1**) for supplying the control voltage 116 is not merely a simple square wave; rather, it may have a fine tuning adjustment to fine tune the output voltage 102, according to certain load situations. For example, negative impedance may be desired in some cases to make the bus more stable; or, current fallback for short circuits situations, etc., may also be desired and may be added using known control technologies for control circuitry (not shown in **Figure 1**) that supplies the control voltage 116. Control voltage 116 could be even controlled by a simple microprocessor, because the square wave frequency may be relatively low. The frequency mainly

depends on the inductor flux capabilities, etc. Since the circuit illustrated in **Figure 2** has very few components, the diode 113 and transistor 112 are low-voltage components, and the switching speed is relatively slow, no expensive components are needed. Thus, the converter 100 permits building a circuitry very inexpensively and integrating it easily into a solar panel or other device designed for field use.

[0048] In one aspect, for example, the input voltage or voltage range is defined to calculate the turn ratio. In the case of the exemplary embodiment discussed above, the input voltage would be 16 to 50 volts. Then a suitable boost-voltage  $V_1$  measured at the cathode of diode 113 is selected. This selection is affected by such considerations as component ratings, duty cycle, input voltage range, etc. In this example, 100V components allow  $V_1$  to reach safely 75V. This approach also achieves a duty cycle of approximately 50 percent for best transformer operation. In this example, the duty cycle would be approximately 53 percent at 35V. The turn ratio N may then be determined according to the desired output voltage  $V_{out}$ . It can be calculated based on  $V_{out} = V_1/(N+1)$ . In this example with N=3 it follows that  $V_{out}=V_1+3$   $V_1$ . If  $V_1$  is 75V, then  $V_{out}=300$ V.

[0049] As illustrated in Fig. 3, the inductor total current is identical to that of a regular boost converter. Current changes  $\Delta I$  calculation is chosen such that peak inductor current is lower than  $1.5 \times I$  on average ( $\Delta I < I_{avg}$ ). Average current  $I_{avg} = P_{in}(max)/V_{in}(min)$ , where  $P_{in}(max)$  is the maximum input power (e.g., 200W/30V=6.7A). In this example,  $\Delta I \approx 6Ap$ -p. At  $\Delta I = 6A$ , the inductivity of the transformer  $L \approx 60\mu H$ . Further  $L=T_{on}\times V_{in}/\Delta I=12\mu S\times 30/6=60\mu H$ , which may be calculated in an iterative cycle, that means  $\Delta I$ , inductor value and final number of turns number of turns per layer and outputs location on the transformer may not come at first iteration. In one embodiment, the core 111c has 1mm gap. For example, one can use an air gap instead but to make it simpler, it is easier to specify the shelf air gap.

**[0050]** Peak current =  $I_{in}(avg) + 0.5 \Delta I = 6.7A + 3A < 10A$ . For these conditions AL of  $400nH/T^2$  a potcore with  $42 \times 29$  mm dimensions can be chosen. A sandwich construction of layers is recommended for performance. In one embodiment, the following arrangement is used: three sets of primary 13T, secondary 13T, with all primary windings in parallel connection and all secondary in serial connection. In one embodiment, primary is 38#x60 litz wire; and secondary is 38#x40 litz wire.

[0051] The forward boost versus regular boost has additional current during ON, and the inductor discharge reflected to the input filter is smaller by 1/N than regular boost. Therefore the RMS ripple current behaves according to  $\sqrt{D.C} \times I_{in}(average)$ . Capacitors can be chosen according to this requirement. In this example,  $3 \times 10 \mu F/100 V$  are used. For example, in a worst case we assume all ripple current flows through input filter capacitor and capacitor rated to handle this current. Therefore,  $I_{rms} = \sqrt{\Delta 0.6 \times 6.7} \approx 5.2 A$ ; each cap can handle 3A RMS.

[0052] As a result of the high voltage output, current is comparably low and  $I_{out}(rms) < I_{out}(av)$ . In this example,  $2\mu F$  per "branch" covers the filtering needs. Additional capacitance and filtering may be needed as a result of the application.

[0053] The advantages of the circuit as illustrated in Figure 1 are numerous. The switching transistor 112 can be implemented by low voltage (100V), similar to a transistor based on trench technology. The diode 113 can be implemented by a 100V Schottky diode. The operation duty cycle can be set around 50 percent, allowing stable control operation versus a conventional boost performing the same function and other topologies. Wave forms are well clamped, avoiding energy losses and the need for snubbers and stress that cause reliability loss. Switching losses are minimal (about quarter in comparison to regular boost). Over all part count is small; and the circuit works with average mode control and a wide input voltage range.

[0054] In some cases, the current waveform is not ramp, so peak current mode can not work only voltage mode or average current mode. Peak pulse current limit can function but as protection only. Because it is a boost type the converter 100 can have large input voltage range.

[0055] The converter 100 has various applications, including middle power rating for conversion of Photovoltaic (PV) voltage to bus voltage (e.g., 200V), or any topology that needs a conversion ratio of input to output higher then 1:8. Another application is a situation where input current is limited (e.g., as in Photovoltaic modules), or other cases that may need serial current limit protection.

**Figure 4** shows an energy system according to one embodiment. In **Figure 4**, the system includes at least one solar panel 401 connected to a voltage bus 403 that has a voltage above 100 volt (e.g., at 200V). At least one solar cell 405 and a step-up converter 100 are integrated on the solar panel. The solar cell 405 is connected to the boost converter 409, which has a first inductor 111a to generate a first voltage  $V_1$ . The first

inductor 111a and a second inductor 111b are inductively coupled via the core 111c. The rectifier 407 is coupled to the second inductor 111b to generate a second voltage  $V_2$ . The first voltage  $V_1$  generated from the booster converter 409 and the second voltage  $V_2$  generated from the rectifier 407 are connected in serial to power the voltage bus 403.

[0057] In one embodiment, the booster converter 409 is implemented using a trench transistor 112, a Schottky diode 113 and the inductor 111, as illustrated in **Figure 1**.

[0058] In one embodiment, the rectifier 407 is implemented using a half bridge rectifier having diodes 115 and 117 and capacitors 118 and 119, as illustrated in **Figure 1**.

[0059] In one embodiment, the booster converter 409 further includes filters, such as those implemented using capacitors 110 and 114 as illustrated in **Figure 1**.

**[0060]** In the foregoing specification, the disclosure has been described with reference to specific exemplary embodiments thereof. It will be evident that various modifications may be made thereto without departing from the broader spirit and scope as set forth in the following claims. The specification and drawings are, accordingly, to be regarded in an illustrative sense rather than a restrictive sense.

# **CLAIMS**

What is claimed is:

- 1. A step-up converter, comprising:

- a boost converter having a first inductor;

- a second inductor paired on a core with the first inductor; and

- a rectifier circuit coupled with the second inductor to generate a direct current output.

- 2. The step-up converter of claim 1, wherein the rectifier circuit comprises a half bridge rectifier circuit.

- 3. The step-up converter of claim 2, wherein the half bridge rectifier circuit comprises:

- a first diode and a first capacitor connected to the second inductor to form a loop to allow electric current to go through the inductor in a first direction; and a second diode and a second capacitor connected to the second inductor to from a loop to allow electric current to go through the inductor in a second direction.

- 4. The step-up converter of claim 1, wherein the boost converter provides a first portion of a voltage output of the step-up converter; and the rectifier circuit provides a second portion of the voltage output of the step-up converter.

- 5. The step-up converter of claim 4, wherein the first portion and the second portion of the voltage output of the step-up convert are proportional to a ratio between the first inductor and the second inductor.

- 6. The step-up converter of claim 1, wherein the boost converter further comprises a transistor to implement a switch in the boost converter, the voltage output of the step-up converter being higher than 100 volts, and the transistor having a breakdown voltage lower than 100 volts.

7. The step-up converter of claim 6, wherein the breakdown voltage of the transistor is lower than 75 volts.

- 8. The step-up converter of claim 6, wherein resistance between drain source connection in the transistor is less than ten milliohms when the transistor is in a saturated on mode.

- 9. The step-up converter of claim 6, wherein an output voltage of the boost converter is no more than 50 volts.

- 10. The step-up converter of claim 1, wherein the boost converter further comprises a transistor to implement a switch in the boost converter and a microprocessor coupled to the transistor to control the switch.

- 11. The step-up converter of claim 1, wherein the microprocessor is configured to control the switch to adjust an output voltage of the step-up converter.

- 12. The step-up converter of claim 1, wherein input to output voltage ratio of the step-up converter is higher than 1:8.

- 13. The step-up converter of claim 1, wherein outputs of the boost converter and the rectifier circuit are connected in serial.

- 14. A solar panel, comprising:

- at least one solar cell to generate a direct current input;

- a boost converter having a first inductor, the boost converter to receive the direct current input from the at least one solar cell and to generate a first portion of a direct current output;

- a second inductor paired on a core with the first inductor; and

- a rectifier circuit coupled with the second inductor to generate a second portion of the direct current output.

15. The solar panel of claim 14, wherein the direct current output has a voltage no less than 200 volts.

- 16. The solar panel of claim 15, wherein the boost converter operates under 100 volts.

- 17. An energy system, comprising:

- a plurality of direct current energy sources;

- a voltage bus; and

- at least one step-up converter coupled between the direct current energy sources and the voltage bus, the step-up converter comprising a boost converter having a first inductor, a second inductor paired on a core with the first inductor, a half bridge rectifier circuit coupled with the second inductor, outputs of boost converter and the half bridge rectifier circuit being connected in serial to power the voltage bus.

- 18. The system of claim 17, wherein the voltage bus has a voltage equal to or above 200 volts; and the boost converter operates under 50 volts.

- 19. The system of claim 17, wherein the energy sources comprise solar panels.

- 20. The system of claim 17, wherein the boost converter includes a trench transistor having less than ten milliohms in resistance between drain source when the transistor is on.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

International application No. **PCT/US2008/075127**

#### A. CLASSIFICATION OF SUBJECT MATTER

#### H02M 3/155(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC G05F 1/10, G05F 1/652, H02M 3/155, H02M 3/28, H02J 7/35, H01L 31/042, H02K 7/18

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Korean Utility models and applications for Utility models since 1975

Japanese Utility models and applications for Utility models since 1975

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) e-KIPASS(KIPO internal) "boost", "converter", "multiplier", "coupled inductor", "half bridge", " rectifier"

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                       | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | Ju-Won Back et. al., "High Boost Converter using Voltage Multiplier" 2005 IEEE Conference, IECON 05, pp. 567-572, Nov. 2005.                                                                                             | 1-20                  |

| x         | US 6175219 B1 (Sony Corp) 16 Jan. 2001 see the abstract, claims 1-2, figures 1-4                                                                                                                                         | 1, 4-16               |

| A         | KR 10-2008-0065817 A (Konkuk University) 15 Jul. 2008 see the abstract, claims 1-4, detailed description of the invention, figures 1-5 (English version is a valiable on K-PION: http://kposd.kipo.go.kr:8088/up/kpion/) | 1-20                  |

| A         | US 2006/0185727 A1 (ISG Technology LLC) 24 Aug. 2006 see the abstract, claims 1-14, figures 1-11                                                                                                                         | 1-20                  |

| $\boxtimes$ | Further | documents | are listed | in the | continuation | of $\operatorname{Box}$ | C |

|-------------|---------|-----------|------------|--------|--------------|-------------------------|---|

|-------------|---------|-----------|------------|--------|--------------|-------------------------|---|

See patent family annex.

- \* Special categories of cited documents:

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- "&" document member of the same patent family

Date of the actual completion of the international search

28 APRIL 2009 (28.04.2009)

Date of mailing of the international search report

28 APRIL 2009 (28.04.2009)

Name and mailing address of the ISA/KR

Korean Intellectual Property Office Government Complex-Daejeon, 139 Seonsa-ro, Seogu, Daejeon 302-701, Republic of Korea

Facsimile No. 82-42-472-7140

Authorized officer

BAE, Jin Yong

Telephone No. 82-42-481-8503

# INTERNATIONAL SEARCH REPORT

International application No.

PCT/US2008/075127

| C (Continua | tion). DOCUMENTS CONSIDERED TO BE RELEVANT                                                  |                       |

|-------------|---------------------------------------------------------------------------------------------|-----------------------|

| Category*   | Citation of document, with indication, where appropriate, of the relevant passages          | Relevant to claim No. |

| A           | US 2005/0275386 A1 (PowerLynx A/S) 15 Dec. 2005 see the abstract, claims 1-23, figures 1-12 | 1-20                  |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

|             |                                                                                             |                       |

# INTERNATIONAL SEARCH REPORT

International application No.

| Information on patent family members   |                  |                                   | PCT/US2008/075127        |  |

|----------------------------------------|------------------|-----------------------------------|--------------------------|--|

| Patent document cited in search report | Publication date | Patent family member(s)           | Publication date         |  |

| US 6175219 B1                          | 16.01.2001       | JP 2000-078836 A<br>JP 4010060 B2 | 14.03.2000<br>14.09.2007 |  |

| KR 10-2008-0065817 A                   | 15.07.2008       | KR 10-0859495 B1                  | 22.09.2008               |  |

| US 2006-0185727 A1                     | 24.08.2006       | NONE                              |                          |  |

| US 2005-0275386 A1                     | 15.12.2005       | EP 1525656 A1<br>US 7339287 B2    | 27.04.2005<br>04.03.2008 |  |

|                                        |                  |                                   |                          |  |

|                                        |                  |                                   |                          |  |

|                                        |                  |                                   |                          |  |