(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-100673

(P2016-100673A)

(43) 公開日 平成28年5月30日(2016.5.30)

(51) Int.Cl.

H04J 3/00 (2006.01)

H04L 12/931 (2013.01)

F 1

H04J 3/00

H04L 12/931

U

テーマコード(参考)

5K028

5K030

審査請求 未請求 請求項の数 4 O L (全 22 頁)

(21) 出願番号

特願2014-234402 (P2014-234402)

(22) 出願日

平成26年11月19日 (2014.11.19)

(71) 出願人 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100092978

弁理士 真田 有

(74) 代理人 100112678

弁理士 山本 雅久

(72) 発明者 河原 英剛

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 巻島 博道

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

最終頁に続く

(54) 【発明の名称】 伝送装置

## (57) 【要約】

【課題】オーバヘッド処理を実現するハードウェア規模を削減できるようにする。

【解決手段】伝送装置 20 は、オーバヘッド情報を有する異なるレートの信号が階層的に多重された信号を受信処理する受信処理部 211, 213, 231, 233, 234 と、前記異なるレートの信号のオーバヘッド情報を探各レートに共通で処理する共通オーバヘッド処理部 24 と、を備える。

【選択図】図 6

**【特許請求の範囲】****【請求項 1】**

オーバヘッド情報を有する異なるレートの信号が階層的に多重された信号を受信処理する受信処理部と、

前記異なるレートの信号のオーバヘッド情報を各レートに共通で処理する共通オーバヘッド処理部と、を備えた、伝送装置。

**【請求項 2】**

前記共通オーバヘッド処理部は、

前記オーバヘッド情報を処理するオーバヘッド処理回路と、

前記オーバヘッド処理回路で処理するオーバヘッド情報を前記レートに応じてスケジューリングするスケジューラと、を備えた、請求項 1 に記載の伝送装置。 10

**【請求項 3】**

前記スケジューラは、

前記レートの高い信号のオーバヘッド情報が前記レートの低い信号のオーバヘッド情報よりも優先して前記オーバヘッド処理回路で処理されるように前記スケジューリングを行なう、請求項 2 に記載の伝送装置。

**【請求項 4】**

前記共通オーバヘッド処理部は、

前記スケジューラによるスケジューリングに応じて、前記オーバヘッド処理回路と前記伝送装置の装置制御部との間の制御通信をスケジューリングするインターフェースを備えた、請求項 2 又は 3 に記載の伝送装置。 20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、伝送装置に関する。

**【背景技術】****【0002】**

光伝送技術の一例として、OTN (Optical Transport Network) 伝送技術がある。OTN 伝送技術においては、例えば、LO - ODU 信号と称される複数の低速信号を、HO - ODU 信号（又は、OTN 信号）と呼ばれる、より高速な信号に多重（「マッピング」と称してもよい。）して伝送する。 30

**【0003】**

HO - ODU 信号の受信側は、受信した HO - ODU 信号に多重されている複数の LO - ODU 信号を分離（「デマッピング」と称してもよい。）する。なお、「LO - ODU」は、「Low Order - Optical Data Unit」の略称であり、「HO - ODU」は、「High Order - Optical Data Unit」の略称である。

**【0004】**

なお、HO - ODU 信号は、「高速信号」、「高次信号」あるいは「上位レイヤ信号」と称してもよく、LO - ODU 信号は、「低速信号」、「低次信号」あるいは「下位レイヤ信号」と称してもよい。 40

**【先行技術文献】****【特許文献】****【0005】****【特許文献 1】国際公開第 2008 / 035769 号****【発明の概要】****【発明が解決しようとする課題】****【0006】**

OTN 信号の受信処理の一例として、オーバヘッド（OH）情報の処理（終端、監視、変更等）がある。OTN 信号には、多種多様なレートの信号を階層的にマッピングすることが可能であり、個々の信号に OH 情報が付加される。 50

**【0007】**

そのため、例えばOTN信号の容量が増加して、OTN信号にマッピング可能な信号の種類（「レイヤ」と称してもよい。）が増えると、処理対象のOH情報も増える。処理対象のOH情報は、OTN信号そのものの容量増加に限らず、例えば、伝送装置においてOTN信号の入力ポート数が増えて、処理対象のOTN信号数が増えることによっても増加する。

**【0008】**

OH処理をポート及びレイヤの別に個別的に実施すると、OH処理に関わるハードウェアリソースの消費量が増加する。そのため、OH処理を実現するハードウェア規模が増大し、電力消費量も増大してしまうおそれがある。

10

**【0009】**

1つの側面では、本発明の目的の1つは、伝送装置において、オーバヘッド処理を実現するハードウェア規模を削減できるようにすることにある。

**【課題を解決するための手段】****【0010】**

1つの側面において、伝送装置は、オーバヘッド情報を有する異なるレートの信号が階層的に多重された信号を受信処理する受信処理部と、前記異なるレートの信号のオーバヘッド情報を各レートに共通で処理する共通オーバヘッド処理部と、を備える。

**【発明の効果】****【0011】**

1つの側面として、オーバヘッド処理を実現するハードウェア規模を削減できる。

20

**【図面の簡単な説明】****【0012】**

【図1】一実施形態に係る通信システム（「通信ネットワーク」と称してもよい。）の構成例を示す図である。

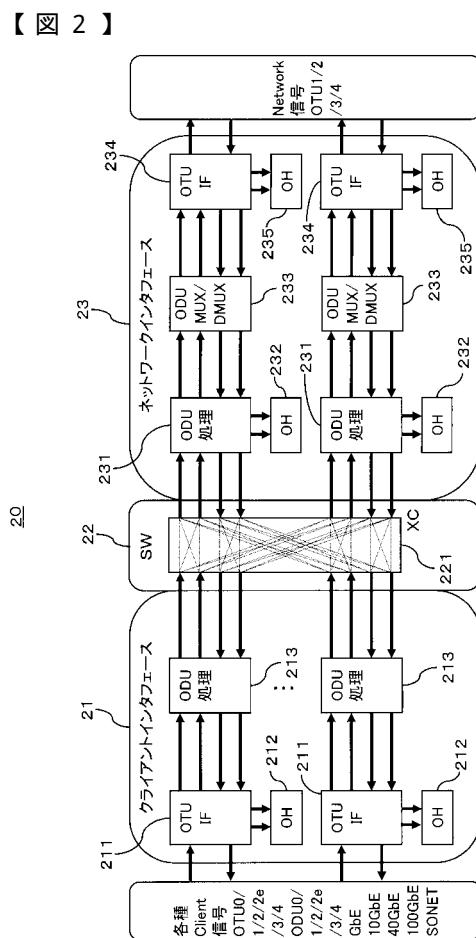

【図2】図1に例示するADM(Add-Drop Multiplexer)の構成例を示すブロック図である。

30

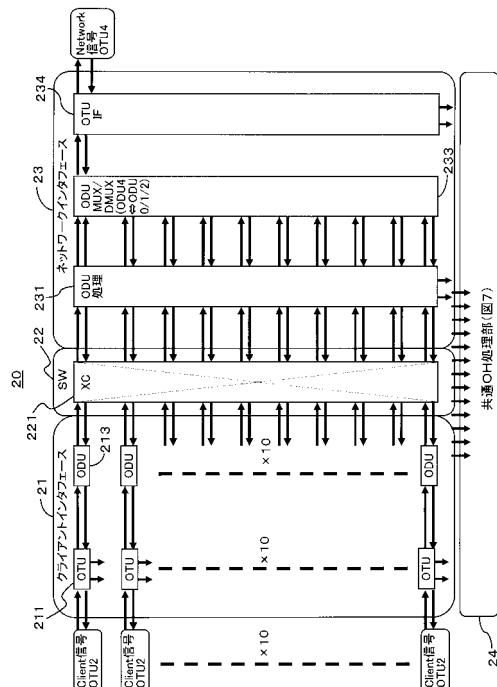

【図3】図1に例示するADMの構成例を示すブロック図である。

【図4】図1に例示するADMの構成例を示すブロック図である。

【図5】図2～図4に例示するオーバヘッド(OH)処理部とH/Sインターフェースとの接続例を示す図である。

【図6】図1に例示するADMの構成例を示すブロック図である。

【図7】図6に例示する共通OH処理部の構成例を示すブロック図である。

【図8】図7に例示するOH処理スケジューラの入出力ポート接続例を示すブロック図である。

【図9】図7及び図8に例示するOH処理スケジューラの動作例を説明するタイミングチャートである。

【図10】図7及び図8に例示するOH処理スケジューラの動作例を説明するフローチャートである。

40

【図11】図7に例示するOH処理回路と共通H/Sインターフェースとの接続例を示すブロック図である。

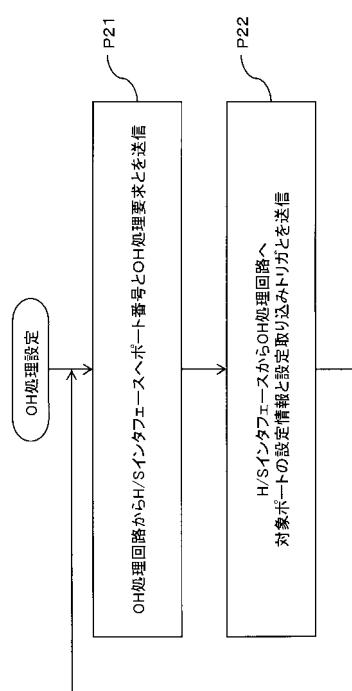

【図12】図11に例示するOH処理回路及び共通H/Sインターフェースの動作例を説明するフローチャートである。

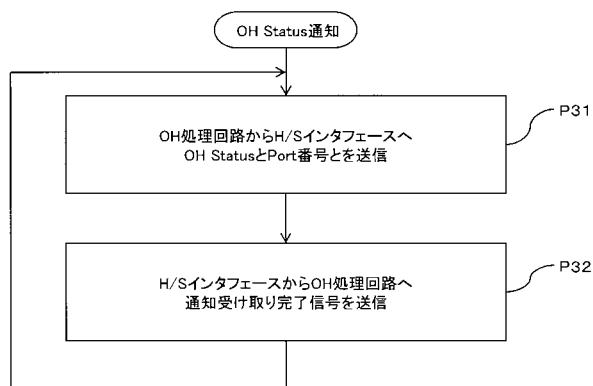

【図13】図11に例示するOH処理回路及び共通H/Sインターフェースの動作例を説明するフローチャートである。

**【発明を実施するための形態】****【0013】**

以下、図面を参照して本発明の実施の形態を説明する。ただし、以下に説明する実施形態は、あくまでも例示であり、以下に明示しない種々の変形や技術の適用を排除する意図はない。また、以下に説明する各種の例示的態様は、適宜に組み合わせて実施しても構わ

50

ない。なお、以下の実施形態で用いる図面において、同一符号を付した部分は、特に断らない限り、同一若しくは同様の部分を表す。

#### 【0014】

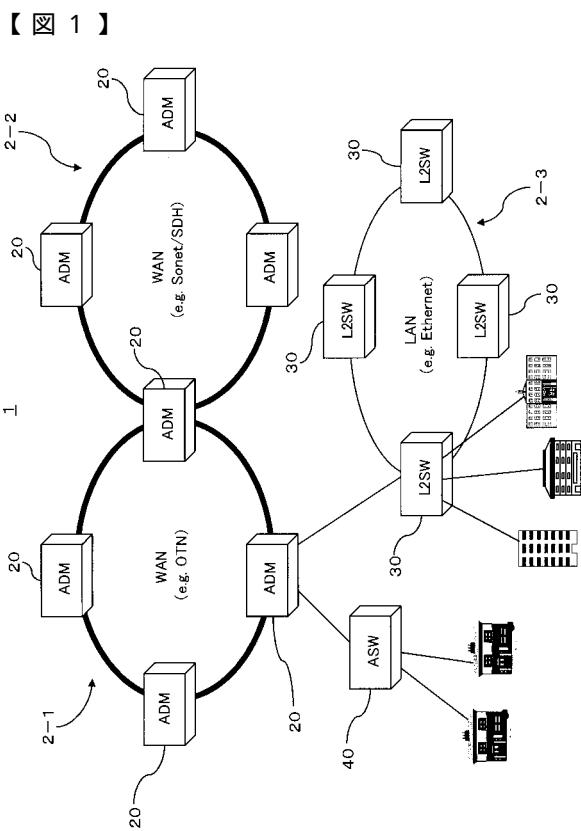

図1は、一実施形態に係る通信システム（「通信ネットワーク」と称してもよい。）の構成例を示す図である。図1に示す通信システム1は、例示的に、OTN伝送をサポートするネットワーク2-1と、SONET（又はSDH）伝送をサポートするネットワーク2-2と、イーサネットフレームの伝送をサポートするイーサネット2-3と、を備える。

#### 【0015】

ネットワーク2-1は、OTN2-1と称してもよく、ネットワーク2-2は、SONET/SDHネットワーク2-2と称してもよい。図1に例示するように、いずれのネットワーク2-1及び2-2も、WAN（Wide Area Network）であってよい。また、イーサネット2-3は、LAN（Local Area Network）であってよい。

10

#### 【0016】

なお、「OTN」は、「Optical Transport Network」の略称である。「SONET」は、「Synchronous Optical Network」の略称であり、「SDH」は、「Synchronous Digital Hierarchy」の略称である。SONETとSDHとは互換性のある伝送方式である。「イーサネット」は、登録商標である。

#### 【0017】

ネットワーク2-1及び2-2のそれぞれは、ネットワークエレメント（NE）の一例として、1又は複数のADM20を備えてよい。NEの一例であるADM20は、「伝送装置」、「ノード」、「局」等と称されてもよい。また、ネットワーク2-3は、NEの一例として、1又は複数のレイヤ2スイッチ（L2SW）30を備えてよい。L2SWは、「ルータ」と称されてもよい。

20

#### 【0018】

図1の例では、ネットワーク2-1～2-3のそれぞれにおいて、NEがリング状の伝送路を介して相互に接続されることにより、リングネットワーク2-1～2-3が形成されている。ただし、ネットワーク2-1～2-3の形態（「トポロジー」と称してもよい。）は、リングネットワークに限られない。例えば、ネットワーク2-1～2-3のいずれかが、メッシュネットワークであってもよい。

30

#### 【0019】

図1に例示するように、いずれかのADM20を介してネットワーク2-1及び2-2が相互通信可能に接続されてよい。また、OTN2-1における他のいずれかのADM20を介してOTN2-1とイーサネット2-3とが相互通信可能に接続されてよい。例えば、OTN2-1のADM20と、イーサネット2-3のレイヤ2スイッチ30と、が通信可能に接続されてよい。

#### 【0020】

ネットワーク2-1及び2-2同士を接続するADM20、並びに、ネットワーク2-1及び2-3同士を接続するADM20は、いずれも「ゲートウェイ（GW）ノード」あるいは単に「ゲートウェイ（GW）」と称されてもよい。したがって、GWとしてのADM20を便宜的に「GW-ADM20」と表記することがある。

40

#### 【0021】

ネットワーク2-1及び2-3同士を接続するGW-ADM20に着目すると、GW-ADM20は、イーサネット2-3（レイヤ2スイッチ30）から受信される信号をOTN2-1の信号に複数多重（「マッピング」）することが可能である。

#### 【0022】

イーサネット2-3から受信される信号は、LO-ODU信号であってよい。LO-ODU信号のペイロードに、イーサネット信号がマッピングされている。LO-ODU信号は、より高速なHO-ODU信号のペイロードにマッピングされる。HO-ODU信号は、OTN信号のペイロードにマッピングされてOTN2-1に伝送される。HO-ODU

50

信号は、第1の信号の一例であり、LO-ODU信号は、第2の信号の一例である。

【0023】

HO-ODU信号のペイロードは、「トリビュータリスロット(TS)」と呼ばれるスロットに分割されてよく、TSの単位でLO-ODU信号をHO-ODU信号のペイロードにマッピング可能である。

【0024】

「トリビュータリ」は、HO-ODU信号からデマッピングされたLO-ODU信号の送信先(別言すると、HO-ODU信号にマッピングされるLO-ODU信号の送信元)に相当すると捉えてよい。例えば、イーサネット2-3は、OTN1の「トリビュータリネットワーク」に相当すると捉えてよい。「OTN1」は、「トリビュータリネットワーク」に対する「コアネットワーク」に相当すると捉えてよい。10

【0025】

「トリビュータリネットワーク」は、「クライアントネットワーク」と称されてもよく、「クライアントネットワーク」を伝送される信号を「クライアント信号」と称してもよい。そのため、HO-ODU信号のTSにマッピングされる「LO-ODU信号」は、「クライアント信号」と称してもよいし「トリビュータリ信号」と称してもよい。

【0026】

一方、コアネットワークを伝送される信号、例えば、LO-ODU信号がマッピングされたHO-ODU信号(OTU信号)は、「ネットワーク信号」と称してよい。「OTU」は、「Optical channel Transport Unit」の略称である。ただし、OTU信号が「クライアント信号」に相当することもある。20

【0027】

OTN1のトリビュータリネットワークに相当し得るのは、イーサネット2-3に限られない。SONET/SDHネットワーク2-2が、「トリビュータリネットワーク」に相当してもよい。また、例えば図1中に示すように、複数の通信路(「パス」あるいは「チャネル」と称してもよい。)を集約(「アグリゲート」と称してよい。)するアグリゲートスイッチ(ASW)40が、OTN1のADM20に通信可能に接続されてもよい。この場合、AGW40によってアグリゲートされた通信路が「トリビュータリネットワーク」に相当すると捉えてよい。30

【0028】

一方、GW-ADM20は、OTN信号のペイロード(HO-ODU信号)にマッピングされているLO-ODU信号をデマッピングしてイーサネット2-3(レイヤ2スイッチ)へ伝送することが可能である。

【0029】

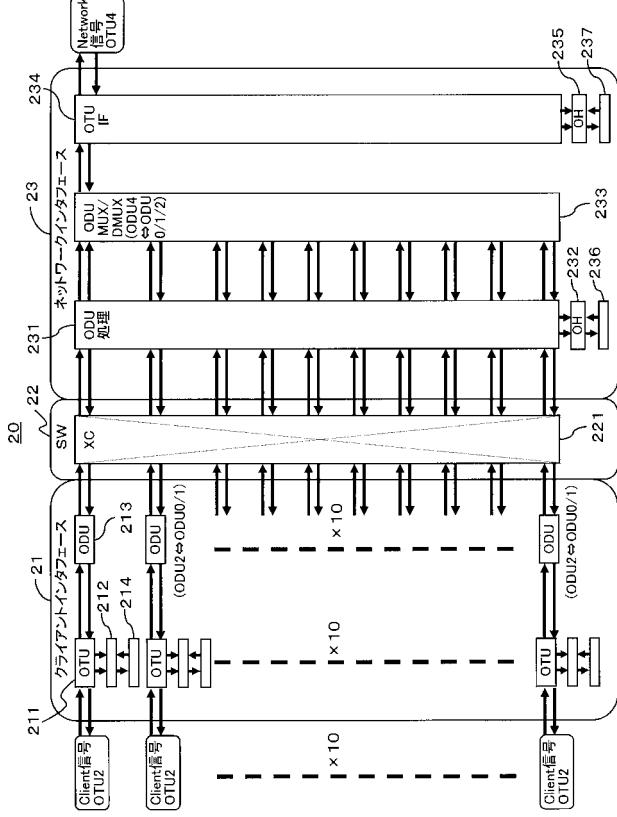

図2に、GW-ADM20の構成例を示す。図2に示すGW-ADM20は、例示的に、クライアントインターフェース21と、スイッチ(SW)22と、ネットワークインターフェース23と、を備える。

【0030】

クライアントインターフェース21は、例示的に、複数種類のクライアント信号の信号処理をサポートする。クライアント信号の非限定的な一例は、OTUk(Optical channel Transport Unit k)信号、ODUk(Optical channel Data Unit k)信号、イーサネット信号、SONETのOC信号、SDHのSTM信号等である。なお、「OC」は、「Optical Carrier」の略称であり、「STM」は、「Synchronous Transport Module」の略称である。40

【0031】

クライアントインターフェース21は、トリビュータリネットワークとの間で送受信されるOTUk信号を処理する。

【0032】

OTUk信号に、ODU信号がマッピングされる。当該ODU信号に更に別のODU信号がマッピングされる場合に、後者の「別のODU信号」が「LO-ODU信号」と称さ50

れる。一方、当該 L O - O D U 信号がマッピングされる前者の O D U 信号が、「 H O - O D U 信号」と称される。

#### 【 0 0 3 3 】

O T U k 信号（又は O D U k 信号）の「 k 」は、当該信号の容量（又は、ビットレート）によって異なる値（「次数」と称してもよい。）をとる。例えば、 $k = 0, 1, 2, 3, 4$  等である。「 k 」の値が「レイヤ」を表すと捉えてよい。

#### 【 0 0 3 4 】

$k = 0$  の O T U 0 信号（又は O D U 0 ）は、約 1 . 0 G b p s の容量を有し、例えば、1 G b p s イーサネットの信号伝送に用いることができる。

#### 【 0 0 3 5 】

$k = 1$  の O T U 1 信号（又は O D U 1 信号）は、約 2 . 4 G b p s の容量を有し、S O N E T の O C - 4 8 ( S D H の S T M - 1 6 ) の信号伝送に用いることができる。

10

#### 【 0 0 3 6 】

$k = 2$  の O T U 2 信号（又は O D U 2 信号）は、約 1 0 G b p s の容量を有し、例えば、O C - 1 9 2 ( S T M - 6 4 ) や 1 0 G b p s イーサネットの信号伝送に用いることができる。

#### 【 0 0 3 7 】

$k = 3$  の O T U 3 信号（又は O D U 3 信号）は、約 4 0 G b p s の容量を有し、例えば、O C - 7 6 8 ( S T M - 2 5 6 ) や 4 0 G b p s イーサネットの信号伝送に用いることができる。

20

#### 【 0 0 3 8 】

$k = 4$  の O T U 4 信号（又は O D U 4 信号）は、約 1 0 0 G b p s の容量を有し、例えば、1 0 0 G b p s イーサネットの信号伝送に用いることができる。

#### 【 0 0 3 9 】

なお、O T U 2 信号の容量を拡張した O T U 2 e 信号や、O T U 3 信号の容量を拡張した O T U 3 e 信号等もある。

#### 【 0 0 4 0 】

「 k 」の値を区別しなくてよい場合、O T U k 信号は、「 k 」を省略して単に「 O T N 信号」と表記されてよい。O D U k 信号についても、「 k 」の値を区別しなくてよい場合、「 k 」を省略して単に「 O D U 信号」と表記されてよい。

30

#### 【 0 0 4 1 】

このように、O T U 信号は、多種多様なプロトコル（「レイヤ」と称してもよい。）のクライアント信号が、より高速な信号に階層的にマッピング（「カプセル化」と称してもよい。）されることで生成される。

#### 【 0 0 4 2 】

したがって、クライアント信号のプロトコルやレートの相違を意識せずに、各種クライアント信号をO T U 信号にてトランスペアレン特にネットワーク間を伝送することが可能になる。

#### 【 0 0 4 3 】

そのため、クライアントインターフェース 2 1 1 は、図 1 に例示するように、N 個（N は 1 以上の整数）の O T U インタフェース（I F ）2 1 1 と、N 個のオーバヘッド（O H ）処理部 2 1 2 と、N 個の O D U 処理部 2 1 3 と、を備える。

40

#### 【 0 0 4 4 】

O T U インタフェース 2 1 1 は、クライアントネットワークから受信した O T U 信号を処理する。また、O T N インタフェース 2 1 1 は、クライアントネットワークへ送信する O T U 信号を生成する。

#### 【 0 0 4 5 】

O T U インタフェース 2 1 1 は、クライアントネットワークからの受信系に着目すると、例えば、クライアントネットワークから受信した O T U 信号のフレーム同期をとり、O H を終端して O H 情報を O H 処理部 2 1 2 に送信する。なお、「 O H 情報」は、「 O H デ

50

ータ」あるいは「O H バイト」と称してもよいし、単に「O H」と称してもよい。

【0046】

その一方で、OTUインターフェース211は、受信OTU信号に付加されているFEC(Forward Error Correction)符号を終端してODU信号に変換しODU処理部213へ送信する。

【0047】

当該ODU信号がHO-ODU信号であれば、ペイロードに1又は複数のLO-ODU信号が多重されているので、ODU処理部213にてLO-ODU信号の分離処理が施される。

【0048】

一方、クライアントネットワークへの送信系に着目すると、OTUインターフェース211は、ODU処理部213から受信したODU信号をOTU信号にマッピングしO Hを付加してクライアントネットワークへ送信する。

【0049】

O H処理部212は、例示的に、OTU信号についてのO Hの生成や監視等のO H処理を行なう。

【0050】

ODU処理部213は、OTUインターフェース211から受信したODU信号を処理する。また、ODU処理部213は、スイッチ22から受信したODU信号を処理する。ODU信号の処理には、例示的に、ODU信号のフレーム信号化や、ODU信号の多重分離処理が含まれてよい。

【0051】

例えば、クライアントネットワークからの受信系に着目すると、ODU処理部213は、HO-ODU信号に多重(マッピング)されているLO-ODU信号を分離(デマッピング)することが可能である。また、コアネットワークへの送信系に着目すると、ODU処理部213は、1又は複数のLO-ODU信号をHO-ODU信号に多重(マッピング)することが可能である。

【0052】

例示的に、OTU1信号(図3参照)であれば、ODU1信号を1多重又はODU0信号を最大2多重することが可能である。OTU2信号(図4参照)であれば、ODU1信号を最大4多重又はODU0信号を最大8多重することが可能である。

【0053】

スイッチ22は、例示的に、クライアントインターフェース21とネットワークインターフェース23との間で送受信される信号をLO-ODU信号の単位でクロスコネクト(XC)する。

【0054】

そのため、スイッチ22は、例示的に、クロスコネクト(XC)スイッチ221を備える。XCスイッチ221は、例えば、複数のセレクタを用いて実現できる。

【0055】

ネットワークインターフェース23は、コアネットワークとの間で送受信されるOTUk信号を処理する。

【0056】

そのため、ネットワークインターフェース23は、例示的に、それぞれN個の、ODU処理部231と、O H処理部232と、ODU多重分離部(ODU MUX/DMUX)233と、OTUインターフェース(IF)234と、O H処理部235と、を備える。

【0057】

ODU処理部231は、例示的に、XCスイッチ221から受信したODU信号と、XCスイッチ221へ送信するODU信号と、を処理する。

【0058】

当該ODU信号処理には、例えば、XCスイッチ221から受信したコアネットワーク

10

20

30

40

50

宛のODU信号に、OH処理部232で生成されたOHを付加する処理が含まれてよい。また、当該ODU信号処理には、ODU多重分離部233から受信したクライアントネットワーク宛のODU信号のOHを終端してOH情報をOH処理部232へ送信する処理が含まれてよい。

#### 【0059】

OH処理部232は、ODU信号についてのOHの生成や監視等のOH処理を行なう。

#### 【0060】

ODU多重分離部233は、コアネットワークへの送信系に着目すると、ODU処理部231で処理されたODU信号を、コアネットワークへのOTU信号の容量に応じた数だけ多重して、OTUインターフェース234へ送信する。また、ODU多重分離部233は、コアネットワークからの受信系に着目すると、OTUインターフェース234から受信したOTN信号にマッピングされているODU信号を分離してODU処理部231へ送信する。

10

#### 【0061】

例示的に、OTU2信号(図3参照)であれば、ODU1信号を最大4多重又はODU0信号を最大8多重することが可能である。OTU4信号(図4参照)であれば、ODU2信号を最大10多重、又は、ODU1信号を最大40多重、又は、ODU0信号を最大80多重することが可能である。

#### 【0062】

OTNインターフェース234は、コアネットワークへの送信系に着目すると、ODU多重分離部233から受信した多重化ODU信号をOTU信号にマッピングしOH処理部235で生成されたOHを付加してコアネットワークへ送信する。

20

#### 【0063】

その一方で、コアネットワークからの受信系に着目すると、OTNインターフェース234は、コアネットワークから受信したOTN信号のフレーム同期をとり、OHを終端してOH情報をOH処理部235に送信する。また、OTUインターフェース234は、受信OTU信号に付加されているFEC符号を終端してODU信号に変換しODU多重分離部233へ送信する。

#### 【0064】

ところで、上述したOH処理(例示的に、OHの監視)は、処理対象の信号のポート及びレイヤが異なれば、それぞれの信号について実施される。そのため、図2の例では、異なる箇所にOH処理部212, 232及び235が備えられる。

30

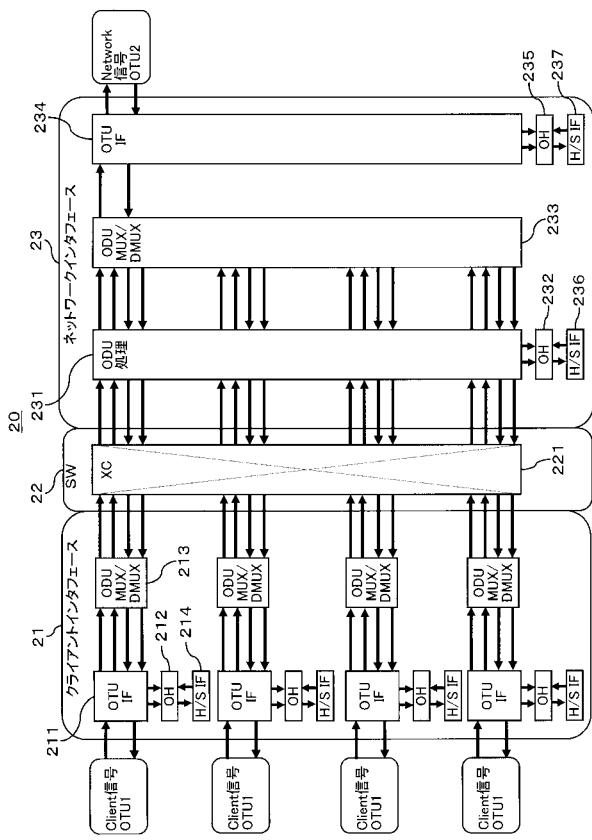

#### 【0065】

より具体的な例を図3に示す。図3には、ADM20に、クライアント信号であるOTU1信号の入力ポートが4ポート備えられ、コアネットワークへのOTU2信号の出力ポートが1ポート備えられた例を示している。

#### 【0066】

この場合、OTU1信号×4ポート分のOH処理部212と、ODU信号向けのOH処理部232と、OTU信号向けのOH処理部235と、がADM20に備えられる。なお、図3において、符号214, 236及び237は、OH処理部211, 232及び235のそれぞれに対応して設けられたハード/ソフト(H/S)インターフェースを示す。

40

#### 【0067】

H/Sインターフェース214, 236及び237は、それぞれ、例示的に、対応するOH処理部212, 232及び235と、図示を省略した装置制御部との間で送受信される信号をインターフェースする。当該信号には、設定、要求、通知等の各種信号が含まれてよい。

#### 【0068】

各種信号は、「制御信号」と総称してよい。「制御信号」による通信は、「制御通信」あるいは「制御アクセス」と称してよい。「制御通信」あるいは「制御アクセス」に用いられる配線が、個々のH/Sインターフェース214, 236及び237と、装置制御部と

50

の間に設けられる。

【0069】

装置制御部は、例示的に、CPU(Central Processing Unit)やDSP(Digital Signal Processor)等の演算能力を備えたプロセッサデバイスを用いて構成されてよく、ADM20の全体的な動作を統括的に制御する。

【0070】

当該制御は、例示的に、プロセッサデバイスがメモリに記憶されたプログラム(「ソフトウェア」と称してもよい。)やデータ等を適宜に読み取って動作することで実現されてよい。ソフトウェアによって実現される制御に、上述した制御通信が含まれてよい。

【0071】

なお、以下において、「OH処理部」と「H/Sインターフェース」とを、OH処理に関わる回路の一例として便宜的に「OH回路」と総称することがある。

【0072】

図3に例示したように、OH回路をポートやレイヤの単位で具備する構成であれば、ポートの増設やレイヤの追加に対して、OH回路の複製によって容易に対応できる。その一方で、ポートやレイヤの増設に比例して、ADM20の装置規模や消費電力が増大していくおそれがある。

【0073】

例えば図4に示すように、ADM20に、クライアント信号の一例であるOTU2信号の入力(受信)ポートが10ポート分備えられ、ネットワーク信号の一例であるOTU4信号の出力ポートが1ポート分備えられる場合を想定する。

【0074】

この場合、1ポートあたりのOTU2信号には、ODU0信号を最大8多重できるので、 $(OTU2 \times 10\text{ポート}) + (ODU0 \times 10\text{ポート} \times 8\text{多重}) + (OTU4 \times 1\text{ポート}) = 91\text{箇所}$ にOH回路を設けることになる。

【0075】

ADM20でサポートしようとするポート数やレイヤの信号容量が更に増えれば、OH回路の数も更に増える。これでは、ADM20の装置規模や消費電力が許容できないほど増大し、例えば、ADM20の装置設計に大きな影響を与えててしまう。

【0076】

そこで、本実施形態では、ポート毎及びレイヤ毎のOH回路を共通化(「集中化」と称してもよい。)して、ポートやレイヤの数に依存しないOH処理が可能なアーキテクチャをADM20において実現する。これによって、ADM20の装置規模や消費電力の低減を図る。

【0077】

ただし、OH処理を単純に共通化して各ポート及び各レイヤの信号のOH処理を単純な先着順で処理してしまうと、OH処理が所定の時間内に終了できないおそれがある。所定の時間は、例示的に、複数のODU信号がマッピングされる、コアネットワーク宛のOTU信号の1フレーム時間に相当してよい。

【0078】

例えば、OTU信号のOH処理(例えば、OH監視)は、OTU信号の1フレームに1回の周期での監視でよいので、OTU信号が複数のポートにそれぞれ入力されても、同じレートで入力されていれば、先着順にOH処理を行なえばよい。

【0079】

しかし、異なるレイヤの信号についてOH処理を行なう場合、単純な先着順処理では、上位レイヤの信号の1フレーム時間内に下位レイヤの信号のOH処理が終了しないために、上位レイヤの信号のOH処理が行なえず、OH処理が破綻するおそれがある。

【0080】

例えば図4に示したように、10ポート分のOTU2信号にそれぞれ最大8多重されているODU0信号( $ODU0 \times 10 \times 8$ )をOTU4信号にマッピングして伝送する場合

10

20

30

40

50

を想定する。

【0081】

この場合に、下位レイヤの80本のODU0信号のOH処理を、先着順処理によって上位レイヤのOTU4信号のOH処理に優先すると、OTU4信号の1フレーム時間内にODU0信号のOH処理が終了しないおそれがある。

【0082】

例えば、OH処理の動作クロック（「システムクロック」と称してもよい。）が164MHz（6.1ns）であり、OTU4（又はODU4）信号の1フレーム時間（周期）が1.168μsであると仮定する。

【0083】

ここで、OH処理に3クロック以上の時間がかかるとすると、 $80 \times 3$ （クロック）×6.1（ns）=1.46μs以上の処理時間がかかる。そのため、80本のODU0信号のOH処理をOTU4信号のOH処理に優先すると、1.168μsというOTU4信号の1フレーム周期内にODU信号のOH処理が終了しない。別言すると、ODU信号のOH処理が完了しない途中の状態で、次のOTU4信号のフレーム周期が到来してしまう。

【0084】

なお、参考として、以下の表1に各レイヤの信号の1フレーム周期を例示する。

【表1】

各レイヤの信号のフレーム周期の一例

| レイヤ         | 1フレーム周期 (μs) |

|-------------|--------------|

| OTU4 (ODU4) | 1.168        |

| OTU3 (ODU3) | 3.305        |

| OTU2 (ODU2) | 12.191       |

| OTU1 (ODU1) | 48.971       |

| OTU0 (ODU0) | 98.354       |

【0085】

そこで、本実施形態では、或る優先度（「優先順位」と称してもよい。）に従って各ポート及び各レイヤのOH処理をスケジューリングする。ADM20において当該スケジューリングを行なう回路又は部分を、「OH処理スケジューラ」と称してよい。優先度は、例示的に、信号のレイヤ（別言すると、レート）によって決定されてよい。詳細については後述する。

【0086】

また、OH処理の共通化に伴い、既述のH/Sインターフェースも共通化できる。ただし、単純な共通化では、制御信号ラインが共通化したH/Sインターフェース（「共通H/Sインターフェース」と称してよい。）に集中して配線混雑が生じるおそれがある。

【0087】

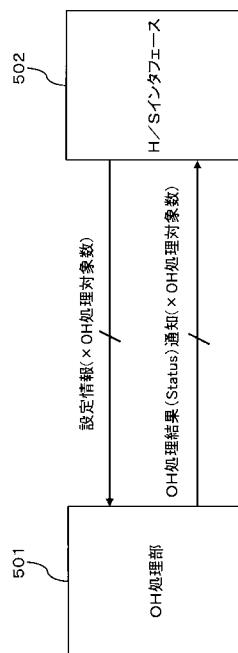

図5に、図4に例示した構成におけるOH処理部とH/Sインターフェースとの間の制御信号の接続例を示す。図5に例示するように、OH処理部501とH/Sインターフェース502との間は、ポート及びレイヤの数に応じた数の設定信号ライン及び通知信号ラインによって接続される。

【0088】

なお、図5のOH処理部501は、図4の各OH処理部212, 232及び235をまとめたブロックに相当すると捉えてよい。また、図5のH/Sインターフェース502は、図4の個別のH/Sインターフェース214, 236及び237をまとめたブロックに相当すると捉えてよい。設定信号ライン及び通知信号ラインは、いずれも制御信号ラインの一例である。

10

20

30

40

50

**【0089】**

設定信号ラインは、例えば、装置制御部からのOH処理の設定情報をOH処理部501へ伝送する。通知信号ラインは、例えば、OH処理部501でのOH監視結果（「OHステータス」と称してよい。）を装置制御部に通知する。

**【0090】**

ここで、OH処理の設定とOHステータスの通知とは、ポート及びレイヤ毎のOHが対象になる。そのため、図4の例では、(OTU2×10ポート)+(ODU0×10ポート×8多重)+(OTU4×1ポート)=91本の設定信号ライン及び通知信号ラインのセットが、図5のOH処理部501とH/Sインターフェース502との間に配線される。ポート数やレイヤ数が増えれば更に配線数は増える。

10

**【0091】**

このように多数の配線を、共通化したH/Sインターフェース（「共通H/Sインターフェース」と称してよい。）に単純に接続しようとすると、配線混雑が生じる。配線混雑が生じると、共通化した回路を集積回路に集積化しようとした場合に、物理的な設計に制約が生じるおそれがある。なお、集積回路の一例としては、LSI（Large Scale Integration）や、FPGA（Field Programmable Gate Array）、ASIC（Application Specific Integrated Circuit）等が挙げられる。

**【0092】**

そこで、本実施形態では、既述のOH処理スケジューラと共通H/Sインターフェースとの間で送受信される制御信号数を削減する。これにより、OH処理スケジューラと共通H/Sインターフェースとの間の制御信号ライン数を削減して、配線混雑を回避あるいは低減できるようとする。

20

**【0093】**

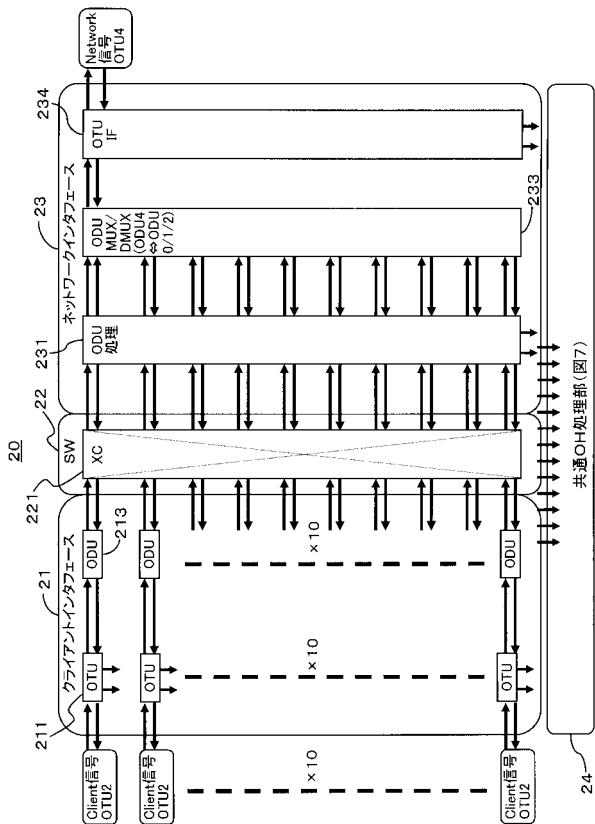

図6に、一実施形態にかかるADM20の構成例を示す。図6に示すADM20の構成は、図4に例示した構成におけるOH回路を、共通OH処理部24に集約して共通化した構成に相当する。そのため、図6に例示するクライアントインターフェース21及びネットワークインターフェース23において、OH回路は削除されている。

**【0094】**

代替的に、クライアントインターフェース21においてOTU信号向けのOH回路がそれぞれ接続されていた各OTUインターフェース211と、共通OH処理部24と、が通信可能に接続される。また、ネットワークインターフェース23においてODU信号向け及びOTU信号向けのOH回路がそれぞれ接続されていたODU処理部231及びOTUインターフェース234と、共通OH処理部24と、が、それぞれ通信可能に接続される。

30

**【0095】**

なお、図6において、OTUインターフェース211, 234、ODU処理部213, 231、及び、ODU多重分離部233は、クライアントネットワークからコアネットワークへ伝送される信号の受信処理部に相当すると捉えてよい。受信処理部は、OH情報を有する異なるレートの信号が階層的に多重された信号を受信処理する。

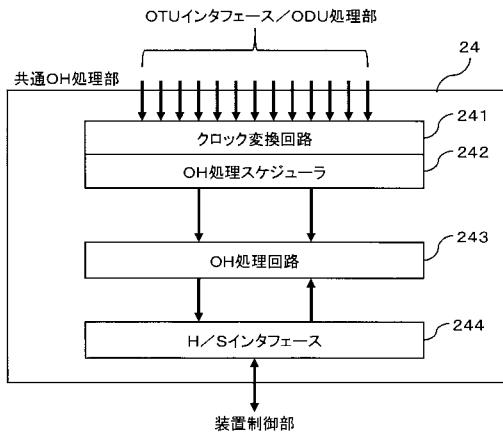

**【0096】**

共通OH処理部24は、図7に例示するように、クロック変換回路241と、OH処理スケジューラ242と、OH処理回路243と、共通H/Sインターフェース244と、を備える。

40

**【0097】**

クロック変換回路241は、各ポートや各レイヤで異なるクロックソースを使用していた場合に、信号処理クロックを各ポート及び各レイヤに共通のクロック（例えば、システムクロック）に変換（「載せ替え」と称してもよい。）する。これにより、各ポート及び各レイヤの信号のOH処理を共通のシステムクロックに従って処理できる。

**【0098】**

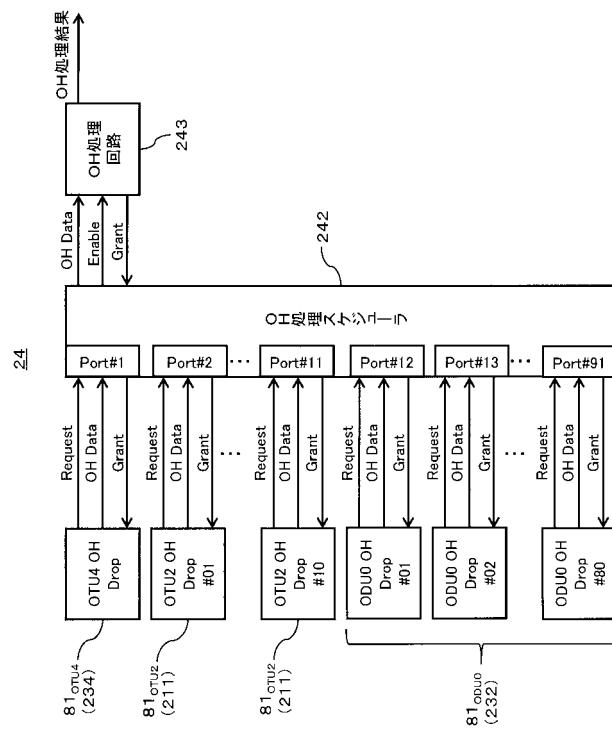

OH処理スケジューラ242は、例示的に、各ポート及び各レイヤの信号レートに応じた優先度に従って、OH処理をスケジューリングする。図8に、OH処理対象の信号が、

50

(OTU2×10ポート) + (ODU0×10ポート×8多重) + (OTU4×1ポート)

)= 91本存在する場合の、OH処理スケジューラ242の構成例を示す。

#### 【0099】

図8に例示するように、OH処理スケジューラ242は、OH処理対象の信号数に応じた数の入出力ポート#1～#91を有する。

#### 【0100】

入出力ポート#1には、例示的に、OTU4信号のOHを分離(ドロップ)するOTU4-OHドロップ回路81<sub>OTU4</sub>が接続される。OTU4-OHドロップ回路81<sub>OTU4</sub>は、例示的に、ネットワークインターフェース23においてOTU4信号を処理するOTUインターフェース234に備えられる。

10

#### 【0101】

入出力ポート#2～#11の10ポートには、それぞれ、OTU信号のOHをドロップする10個(#01～#10)のOTU2-OHドロップ回路81<sub>OTU2</sub>が接続される。OTU2-OHドロップ回路81<sub>OTU2</sub>は、例示的に、クライアントインターフェース21においてOTU2信号を処理する10ポート分のOTUインターフェース211のそれぞれに備えられる。

#### 【0102】

残り80ポート分の入出力ポート#12～#91には、それぞれ、ODU0信号のOHをドロップする80個(#01～#80)のODU0-OHドロップ回路81<sub>ODU0</sub>が接続される。ODU0-OHドロップ回路81<sub>ODU0</sub>は、ネットワークインターフェース23において最大80本のODU0信号を処理するODU処理部231に備えられる。

20

#### 【0103】

なお、上記の各OHドロップ回路81<sub>OTU4</sub>、81<sub>OTU2</sub>及び81<sub>ODU0</sub>を区別しなくてよい場合は、単に「OHドロップ回路81」と表記する。

#### 【0104】

OHドロップ回路81は、それぞれが接続された、OH処理スケジューラ242の入出力ポート#j(j=1～91のいずれか)を介してOH処理に関わる通信を行なう。例えば、OHドロップ回路81は、ドロップしたOHのデータを当該OHの処理要求と共にOH処理スケジューラ242へ送信する。

30

#### 【0105】

OH処理スケジューラ242は、複数のOH処理要求を同じタイミングで受信すると、より優先度の高いレイヤの信号のOHデータがOH処理回路243にて優先して処理されるように、OH処理のスケジューリングを行なう。優先度は、例えば、OTU4>OTU2>ODU0である。

#### 【0106】

なお、OH処理スケジューラ242は、どの入出力ポート#jにどのレイヤのOHドロップ回路81が接続されているかを管理しており、OH処理要求を受信した入出力ポート#jのポート番号を基に、当該OH処理要求のレイヤを識別できる。同じレイヤのOH処理要求が競合した場合は、入出力ポート#jのポート番号を基に、優先するOH処理要求を決定してよい。

40

#### 【0107】

例えば、図8の例では、入出力ポート#jのポート番号の昇順に優先度を設定してよい。すなわち、ポート#1>ポート#2>・・・>ポート#90>ポート#91に優先度を設定してよい。ただし、図8の例とは逆に、ポート番号が大きい入出力ポート#jほど上位レイヤのOHドロップ回路81が接続される場合には、入出力ポート#jのポート番号の降順に優先度を設定してよい。

#### 【0108】

別言すると、ポート番号の昇順又は降順で、より上位のレイヤ(又は、より下位のレイヤ)のOHドロップ回路81を入出力ポート#jに接続しておくことで、ポート番号に基づくレイヤの識別、管理、優先度の管理が容易になる。

50

## 【0109】

もっとも、入出力ポート#jに接続されるOHドロップ回路81のレイヤと、当該入出力ポート#jのポート番号との対応関係が、OH処理スケジューラ242にて、管理されれば、レイヤ(優先度)の識別は可能である。

## 【0110】

OH処理スケジューラ242は、OH処理要求のスケジューリング結果に従って、OHデータを、順次、OH処理回路243に、OH処理のイネーブル信号と共に送信する。

## 【0111】

OH処理回路243は、OH処理スケジューラ242から、イネーブル信号と共にOHデータを受信すると、受信したOHデータの処理(例えば、OHステータスの監視)を行なう。OHデータの処理結果は、例えば、共通H/Sインターフェース244を通じて装置制御部に通知される。10

## 【0112】

OH処理回路243は、OH処理が正常に終了すると、その旨を示す応答(例えば、グラント)をOH処理スケジューラ242に返信する。

## 【0113】

OH処理スケジューラ242は、OH処理回路243からグラントを受信すると、対応するOHドロップ回路81にグラントを送信してOH処理が正常に終了したことを通知する。

## 【0114】

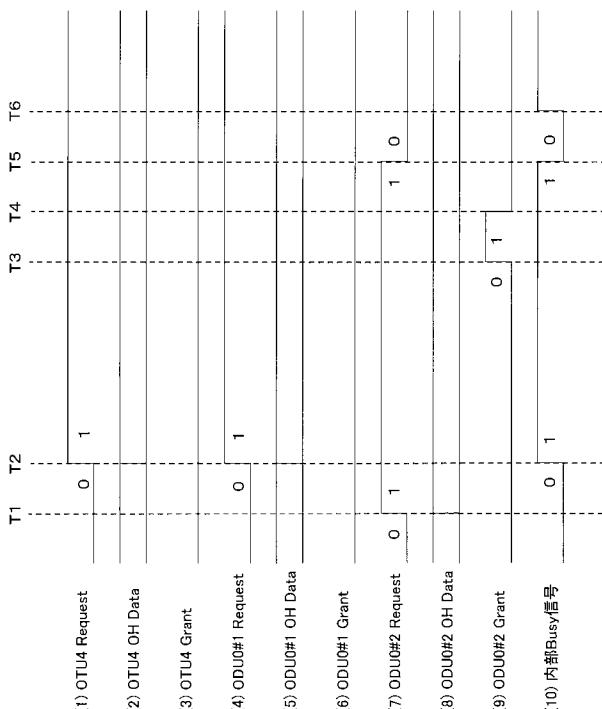

図9に、OH処理スケジューラ242(以下「スケジューラ242」と略称することがある。)の動作例を示す。図9には、まずODU0信号のOH処理要求が先着順で受け付けられ、その後に、OTU4信号のOH処理要求とODU0信号のOH処理要求とが競合した場合について例示している。20

## 【0115】

OH処理スケジューラ242は、図9の(10)に例示する内部ビジー信号が「1」となっている場合、新たなOH処理要求は受け付けない。

## 【0116】

内部ビジー信号は、いずれかのレイヤのOH処理がOH処理回路243にて開始(イネーブル)されると「0」から「1」に遷移する。いずれのレイヤのOH処理も正常に終了してディゼーブル状態になると、内部ビジー信号は、「1」から「0」に遷移する。内部ビジー信号は、「フラグ情報」と称してもよい。30

## 【0117】

図9の(7)及び(8)に例示するように、時刻T1で、図8の入出力ポート#13に接続されたODU0-OHドロップ回路#02からOH処理要求(ODU#2 Request)がOHデータ(ODU#2 OH Data)と共にスケジューラ242に送信されたとする。

## 【0118】

時刻T1では、図9の(10)に例示する内部ビジー信号が「0」であるので、スケジューラ242は、当該OH処理要求(ODU#2 Request)を受け付けて、受信したOHデータ(ODU#2 OH Data)をOH処理回路243へイネーブル信号と共に送信する。40

## 【0119】

ODU0信号のOH処理要求(ODU#2 Request)の受け付けに応じて、スケジューラ242は、図9の(10)に例示するように、例えば時刻T2において内部ビジー信号を「1」に変更する。

## 【0120】

ここで、図9の(1)及び(2)に例示するように、時刻T2において、図8の入出力ポート#1に接続されたOTU4-OHドロップ回路81 OTU4からOH処理要求(OTU4 Request)がOHデータと共にスケジューラ242に送信されたとする。

## 【0121】

また、同時刻T2において、図9の(4)及び(5)に例示するように、図8の入出力

10

20

30

40

50

ポート # 1 2 に接続された O D U 0 - O H ドロップ回路 # 0 1 から O H 処理要求 ( ODU0#1 Request ) が O H データと共にスケジューラ 2 4 2 に送信されたとする。

#### 【 0 1 2 2 】

しかし、スケジューラ 2 4 2 は、時刻 T 2 において、内部イネーブル信号が「 1 」になっているので、O T U 4 信号及び O D U 0 信号のいずれについての O H 処理要求 ( OTU4 Request , ODU0#1 Request ) も受け付けない。

#### 【 0 1 2 3 】

一方、時刻 T 1 で O H 処理要求 ( ODU#2 Request ) が受け付けられた O H データ ( ODU#2 OH Data ) の処理が O H 処理回路 2 4 3 にて正常に終了し、図 9 の ( 9 ) に例示するように、時刻 T 3 - T 4 の間、O H 処理回路 2 4 3 がグラントを送信したとする。 10

#### 【 0 1 2 4 】

スケジューラ 2 4 2 は、当該グラン트を受信すると、O H 処理要求 ( ODU#2 Request ) の送信元 O D U 0 - O H ドロップ回路 # 0 2 へグラントを送信する。O D U 0 - O H ドロップ回路 # 0 2 は、スケジューラ 2 4 2 からのグラントの受信に応じて、図 9 の ( 7 ) に例示するように、例えば時刻 T 5 で O H 処理要求 ( ODU#2 Request ) をディゼーブルする。

#### 【 0 1 2 5 】

当該ディゼーブルに応じて、スケジューラ 2 4 2 は、図 9 の ( 1 0 ) に例示するように、内部ビジー信号を「 1 」から「 0 」に変更する。内部ビジー信号が「 0 」になった時刻 T 5 以降、スケジューラ 2 4 2 は、O H 処理要求を受け付け可能な状態となる。 20

#### 【 0 1 2 6 】

ここで、図 9 の ( 1 ) 及び ( 4 ) に例示するように、時刻 T 2 以降、O T U 4 信号及び O D U 0 信号についての O H 処理要求 ( OTU4 Request , ODU0#1 Request ) が競合的にイネーブル状態となっている。

#### 【 0 1 2 7 】

スケジューラ 2 4 2 は、上位レイヤの信号である O T U 4 信号の O H 処理を優先させるため、O T U 4 - O H ドロップ回路 8 1 \_ O T U 4 からの O H 処理要求 ( OTU4 Request ) を受け付けて、O H データ ( OTU4 OH Data ) を O H 処理回路 2 4 3 へ送信する。

#### 【 0 1 2 8 】

O T U 4 信号の O H 処理要求 ( OTU4 Request ) の受け付けに応じて、スケジューラ 2 4 2 は、図 9 の ( 1 0 ) に例示するように、例えば時刻 T 6 において内部ビジー信号を「 0 」から「 1 」に変更する。 30

#### 【 0 1 2 9 】

その後、O T U 4 信号の O H 処理が正常に終了し、O H 処理回路 2 3 4 からグラン트が受信されれば、スケジューラ 2 4 2 は、内部ビジー信号を「 1 」から「 0 」に変更する。この時点で、O D U 信号よりも上位レイヤの O T U 4 信号の新たな O H 処理要求が受信されていなければ、スケジューラ 2 4 2 は、時刻 T 5 で選択しなかった下位レイヤ ( O D U 0 信号 ) の O H 処理要求 ( ODU0#1 Request ) を受け付ける。

#### 【 0 1 3 0 】

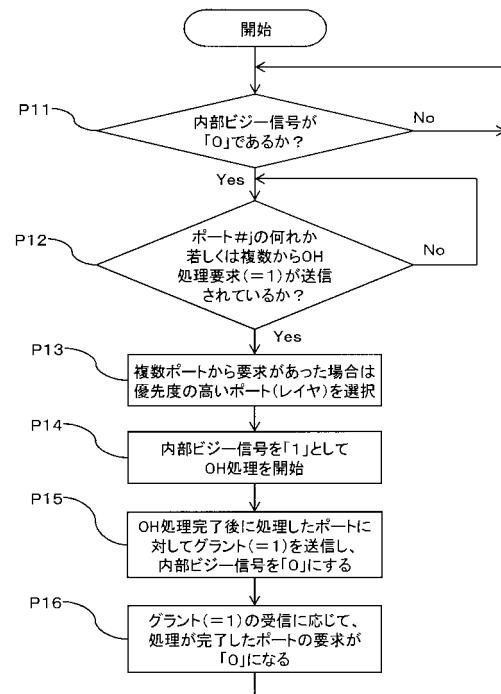

次に、図 1 0 に、上述したスケジューラ 2 4 2 の動作例をフローチャートにて示す。図 1 0 に例示するように、スケジューラ 2 4 2 は、内部ビジー信号が「 0 」であるか否かをチェック ( 「 監視 」 と称してもよい。 ) する ( 処理 P 1 1 ) 。 40

#### 【 0 1 3 1 】

チェックの結果、内部ビジー信号が「 1 」であれば ( 処理 P 1 1 で N o の場合 ) 、スケジューラ 2 4 2 は、既にいずれかのレイヤの O H 処理が開始されていると判断して、新たな O H 処理要求が受信されても受け付けない。

#### 【 0 1 3 2 】

一方、内部ビジー信号が「 0 」であれば ( 処理 P 1 1 で Y e s の場合 ) 、スケジューラ 2 4 2 は、入出力ポート # j のいずれか若しくは複数において O H 処理要求 ( 「 1 」 ) が受信されているか否かをチェックする ( 処理 P 1 2 ) 。 50

**【0133】**

チェックの結果、入出力ポート# j のいずれにおいても O H 处理要求が受信されていなければ（処理 P 1 2 で N o の場合）、O H 处理要求の監視を継続する。

**【0134】**

入出力ポート# j のいずれかで O H 处理要求が受信されており（処理 P 1 2 で Y e s の場合）、複数の O H 处理要求が競合していなければ、スケジューラ 2 4 2 は、当該 O H 处理要求を受け付ける。複数の O H 处理要求が競合していれば、優先度の高い入出力ポート# j で受信されている O H 处理要求を受け付ける（処理 P 1 3）。

**【0135】**

O H 处理要求の受け付けに応じて、スケジューラ 2 4 2 は、内部ビジー信号を「 1 」に設定し、O H 处理回路 2 4 3 にイネーブル信号と共に O H データを送信して O H 处理を開始する（処理 P 1 4）。

10

**【0136】**

その後、スケジューラ 2 4 2 は、O H 处理回路 2 4 3 による O H 处理が正常に終了して O H 处理回路 2 4 3 からグラントが受信されると、O H 处理要求を受け付けた入出力ポート# j から O H ドロップ回路 8 1 へグラント（「 1 」）を発行する。また、スケジューラ 2 4 2 は、内部ビジー信号を「 0 」に設定する（処理 P 1 5）。

**【0137】**

O H ドロップ回路 8 1 は、スケジューラ 2 4 2 からグラント（「 1 」）を受信することによって、O H 处理要求を「 0 」に設定（ディゼーブル）する（処理 P 1 6）。

20

**【0138】**

以上のようにして、スケジューラ 2 4 2 は、各入出力ポート# j を通じて受信される O H 处理要求を上位レイヤの O H 处理が優先されるようにスケジューリングする。これにより、O H 处理回路 2 4 3 が共通化されていても、例えば、上位レイヤの信号の 1 フレーム周期内に下位レイヤの信号の O H 处理を完了することができるようになる。したがって、O H 处理の共通化に伴う破綻を回避できる。

**【0139】**

なお、スケジューラ 2 4 2 による共通 O H 处理の最大許容能力は、A D M 2 0 が処理対象とする最上位レイヤの信号レート（別言すると、1 フレーム時間）に応じて決まる。非限定的な一例として、O H 处理の動作クロック（システムクロック）が 1 7 0 [ M H z ] であり、O H 处理回路 2 4 3 での O H 处理に 7 クロック分の時間がかかると仮定する。すなわち、O H 处理回路 2 4 3 において、( 1 / 1 7 0 [ M H z ] ) × 7 [ クロック ] × 1 0 0 0 4 1 . 1 7 6 [ n s ] の処理時間がかかると仮定する。

30

**【0140】**

現状の I T U - T G . 7 0 9 規格では、O T U 4 信号が最上位レイヤ、すなわち、最高レートの信号であり、前記の表 1 に例示したように、1 フレーム時間は 1 . 1 6 8 [ μ s ] = 1 1 6 8 [ n s ] である。なお、I T U - T は、「 International Telecommunication Union Telecommunication Standardization Sector 」の略称である。

**【0141】**

したがって、O T U 4 信号の 1 フレーム時間内に処理可能な O H 处理数は、1 1 7 6 [ n s ] ÷ 4 1 . 1 7 6 [ n s ] = 2 8 . 3 となる。つまり、最大で約 2 8 個分の O T U 4 信号に対する O H 处理を、スケジューラ 2 4 2 及び O H 处理回路 2 4 3 によって処理できる。

40

**【0142】**

（ O H 处理回路 2 4 3 と共通 H / S インタフェース 2 4 4 との間の接続例 ）

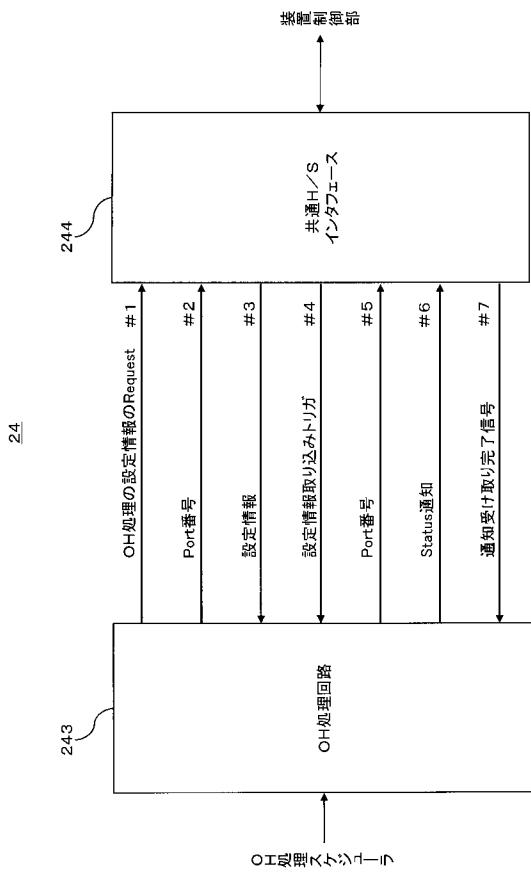

次に、図 1 1 ~ 図 1 3 を参照して、図 7 に例示した、O H 处理回路 2 4 3 と共通 H / S インタフェース 2 4 4 との間の接続例及び制御通信例について説明する。

**【0143】**

図 1 1 に例示するように、O H 处理回路 2 4 3 と共通 H / S インタフェース 2 4 4 との間は、例えば 7 種類の信号ライン # 1 ~ # 7 にて接続される。なお、以下において、「共

50

通H/Sインターフェース244」は、「共通インターフェース244」と略称することがある。

【0144】

O H処理回路243は、第1の信号ライン#1を通じて、既述の装置制御部宛にO H処理の設定情報を要求（「O H設定要求」と称してよい。）する。併せて、O H処理回路243は、当該O H設定要求がどのポート番号についての要求であるかを装置制御部が識別できるように、O H設定要求元のポート番号を第2の信号ライン#2にて、共通H/Sインターフェース244に送信する（図12の処理P21）。

【0145】

なお、「ポート番号」は、例えば図8に示したスケジューラ242の入出力ポート番号#jに相当する。したがって、ポート番号#jは、既述のように、O H処理対象の信号のレイヤを識別する情報の一例に相当すると捉えてよい。

10

【0146】

共通インターフェース244は、第1及び第2の信号ライン#1及び#2を通じてそれ受信したO H設定要求及びポート番号#jのセットを装置制御部へ送信する。

【0147】

装置制御部は、共通インターフェース244からO H設定要求とポート番号#jとのセットを受信すると、ポート番号#jに対するO H設定要求であることを識別し、識別したポート番号#j向けのO H処理の設定情報を共通インターフェース244へ送信する。

20

【0148】

共通インターフェース244は、装置制御部から受信した設定情報を、第3の信号ライン#3を通じて、O H処理回路243に与える。その際、共通インターフェース244は、当該設定情報をO H処理回路243に取り込ませる（別言すると、設定を反映させる）ためのトリガ信号を、第4の信号ライン#4を通じて、O H処理回路243に与えてよい（図12の処理P22）。

【0149】

設定情報を受信したO H処理回路243は、当該設定情報に従って、対象ポート番号#j（レイヤ）のO H処理（例示的に、監視）を実施し、処理結果（例示的に、O Hステータス）を、第6の信号ライン#6を通じて共通インターフェース244へ通知する。併せて、O H処理回路243は、当該O Hステータスがどのポート番号#jについてのO H処理結果であるかを示すために、ポート番号#jを第5の信号ライン#5にて共通インターフェース244に送信する（図13の処理P31）。

30

【0150】

共通インターフェース244は、第5及び第6の信号ライン#5及び#6を通じてそれ受信したポート番号#j及びO Hステータスのセットを装置制御部へ送信する。当該ポート番号#j及びO Hステータスのセットの受信に応じて、共通インターフェース244は、第7の信号ライン#7にて、通知受け取り完了信号をO H処理回路243に送信してよい（図13の処理P32）。

【0151】

装置制御部は、共通インターフェース244からポート番号#jとO Hステータスとのセットを受信すると、当該ポート番号#jについてのO Hステータスに応じた処理を実施する。

40

【0152】

上述した第1～第7の信号ライン#1～#7は、O H処理回路24と装置制御部との間の制御通信（あるいは制御アクセス）に用いられる制御信号ラインの一例である。

【0153】

ここで、上述したO H処理の設定情報やO Hステータスは、システムクロック毎に送受信される必要はなく、スケジューラ242にてスケジューリングされたO H処理のタイミングにて送受信されれば足りる。

【0154】

50

別言すると、O H処理回路243に対するO H処理の設定や、装置制御部に対するO Hステータスの通知を含む制御通信も、O H処理のスケジューリングに応じてスケジューリングされる。したがって、ADM20のポートや信号のレート(レイヤ)別に制御信号ラインを配線しなくてよく、H/Sインターフェース244を共通化した際の配線混雑を回避できる。

#### 【0155】

以上のように、上述した実施形態によれば、スケジューラ242によって、信号のレート(あるいはレイヤ)に応じたO H処理のスケジューリングを行なうので、異なるレートの信号のO H処理を共通のO H処理回路243にて処理できる。

#### 【0156】

したがって、図2～図4に例示したように異なるポート及び異なるレイヤの別にO H回路を設けなくてよく、O H処理に関わるハードウェアリソースの消費量(別言すると、規模)を削減できる。また、ハードウェア規模の削減に応じて、電力消費量も削減できる。

#### 【0157】

例えば、図4の例では91箇所に設けられていたO H回路を、図6及び図7の例では、共通O H処理部24(O H処理回路243)の1箇所に共通化できる。したがって、O H処理スケジューラ242の追加分を考慮しても、50%程度のハードウェア規模及び消費電力の削減効果を見込める。

#### 【0158】

また、ADM20が処理対象とする信号容量が増大してレイヤの数(種類)が増えたとしても、レイヤ数に依存しないで、各レイヤのO H処理をO H処理回路243にて共通処理できる。したがって、ADM20が処理対象とする信号容量の増加に対しても、容易に、また、柔軟に対応することができる。

#### 【0159】

更に、スケジューラ242は、異なるレイヤのO H処理が競合する場合には、より上位レイヤの信号(別言すると、より信号レートの高い信号)のO H処理ほど下位レイヤの信号に優先してスケジューリングできる。したがって、O H処理の共通化に伴う破綻を回避できる。

#### 【符号の説明】

#### 【0160】

1 通信システム(通信ネットワーク)

2 - 1 ネットワーク(OTN)

2 - 2 ネットワーク(SONET/SDHネットワーク)

2 - 3 イーサネット

20 ADM

21 クライアントインターフェース

211 OTUインターフェース(IF)

212, 232, 235 オーバヘッド(OH)処理部

213 N個のODU処理部

214, 236, 237 ハード/ソフト(H/S)インターフェース

22 スイッチ(SW)

221 クロスコネクト(XC)スイッチ

23 ネットワークインターフェース

231 ODU処理部

233 ODU多重分離部(ODU MUX/DMUX)

234 OTUインターフェース(IF)

24 共通オーバヘッド(OH)処理部

241 クロック変換回路

242 O H処理スケジューラ

243 O H処理回路

10

20

30

40

50

2 4 4 共通 H / S インタフェース

3 0 レイヤ 2 スイッチ ( L 2 S W )

4 0 アグリゲートスイッチ ( A S W )

8 1 o T U 4 O T U 4 - O H ドロップ回路

8 1 o T U 2 O T U 2 - O H ドロップ回路

8 1 o D U 0 O D U 0 - O H ドロップ回路

5 0 1 O H 処理部

5 0 2 H / S インタフェース

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

---

フロントページの続き

(72)発明者 北島 広之

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 尾花 裕治

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 堀田 真吾

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 小田嶋 渉

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

F ターム(参考) 5K028 AA08 BB01 MM12 MM14

5K030 GA05 HA08 HB25 HD01 JA01 JL03 KX18 LE05