(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5284401号

(P5284401)

(45) 発行日 平成25年9月11日(2013.9.11)

(24) 登録日 平成25年6月7日(2013.6.7)

(51) Int.Cl.

G06F 1/32 (2006.01)

F 1

G06F 1/00 332Z

請求項の数 8 (全 22 頁)

(21) 出願番号 特願2011-65704 (P2011-65704)

(22) 出願日 平成23年3月24日 (2011.3.24)

(65) 公開番号 特開2012-203518 (P2012-203518A)

(43) 公開日 平成24年10月22日 (2012.10.22)

審査請求日 平成23年9月16日 (2011.9.16)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100089118

弁理士 酒井 宏明

(74) 代理人 100112656

弁理士 宮田 英毅

(72) 発明者 春木 洋美

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 藤崎 浩一

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】動作切替装置およびプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

1 または複数の処理を実行可能な処理装置が前記処理を実行していないアイドル状態を検出する状態検出部と、

割り込み処理の種別を示す割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを記憶する第4記憶部と、

前記割り込み種別と、当該割り込み種別に対応する割り込み待ち時間とを記憶する第5記憶部と、

前記状態検出部で前記アイドル状態が検出されたとき、前記第4記憶部に記憶された情報と、前記第5記憶部に記憶された情報に基づいて、現在時刻から、次の前記割り込み処理が開始されるまでの時間長を示す待ち時間を算出する算出部と、

前記算出部で算出された前記待ち時間に応じて、前記処理装置の動作モードを決定する決定部と、を備える、

ことを特徴とする動作切替装置。

## 【請求項 2】

前記決定部は、前記算出部で算出された前記待ち時間が所定の時間長を超える場合は、前記動作モードを、前記処理装置の動作が一時的に停止して節電状態となる第1モードに決定する一方、前記待ち時間が前記所定の時間長以下の場合は、前記動作モードを、前記処理装置が前記アイドル状態を維持する第2モードに決定する、

ことを特徴とする請求項1に記載の動作切替装置。

## 【請求項 3】

前記決定部が、前記動作モードを前記第1モードに決定したときに、前記処理装置の動作を一時的に停止して節電状態にする一時停止部と、

前記割り込み処理が開始されるときに、前記一時停止部により節電状態にされた前記処理装置の動作を再開させて前記第1モードを解除する再開部と、

割り込み待ちが発生したときに、当該割り込み待ちになった前記割り込み種別と、当該割り込み待ちが発生した時刻とを前記第4記憶部に登録する一方、割り込み処理が開始されるときに、割り込み待ちが解除される前記割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを、前記第4記憶部から削除する登録削除部と、を備える、

ことを特徴とする請求項1または2に記載の動作切替装置。

10

## 【請求項 4】

前記割り込み種別で特定される割り込み処理が開始される時刻と、当該割り込み処理の割り込み待ちが発生した時刻とから、割り込み待ち時間を求め、その求めた割り込み待ち時間を用いて、前記第5記憶部に記憶された前記割り込み待ち時間を更新する更新部をさらに備える、

ことを特徴とする請求項1乃至3のうちの何れか1項に記載の動作切替装置。

## 【請求項 5】

前記決定部が、前記動作モードを前記第2モードに決定したときに、前記処理装置の前記アイドル状態を維持する維持部をさらに備える、

ことを特徴とする請求項1に記載の動作切替装置。

20

## 【請求項 6】

前記処理装置の動作が一時的に停止して節電状態になったときから動作を再開するまでの間における前記処理装置の特性を示す特性情報に応じて、前記所定の時間長を変更する変更部をさらに備える、

ことを特徴とする請求項2に記載の動作切替装置。

## 【請求項 7】

前記特性情報は前記処理装置の消費電力である、

ことを特徴とする請求項6に記載の動作切替装置。

## 【請求項 8】

1または複数の処理を実行可能な処理装置が前記処理を実行していないアイドル状態を検出する手順と、

30

前記アイドル状態検出部で前記アイドル状態が検出されたとき、割り込み処理の種別を示す割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを記憶する第4記憶部に記憶された情報と、前記割り込み種別と、当該割り込み種別に対応する割り込み待ち時間とを記憶する第5記憶部に記憶された情報に基づいて、次の前記割り込み処理が開始されるまでの時間長を示す待ち時間を算出する手順と、

前記算出部で算出された前記待ち時間に応じて、前記処理装置の動作モードを決定する手順と、をコンピュータに実行させるためのプログラム。

## 【発明の詳細な説明】

## 【技術分野】

40

## 【0001】

本発明の実施形態は、動作切替装置およびプログラムに関する。

## 【背景技術】

## 【0002】

従来、1または複数の処理を実行可能な処理装置（例えばマイクロプロセッサ）の消費電力を低減する技術が知られている。例えば、電源電圧や周波数を下げて消費電力を低減するDVS（Dynamic Voltage Frequency Scaling）と呼ばれる技術や、電力を必要としている部分にだけ電力を供給するパワーティング技術などが挙げられる。

## 【0003】

パワーティング技術の例として、プロセッサ内を複数のクロックドメインに分割し

50

、各クロックドメイン内で電力を供給するか否かを決定する技術がある。また、プロセッサ内の演算器単位で電力を供給するか否かを決定する細粒度パワーゲーティング技術がある。

【0004】

また、マイクロプロセッサの消費電力を低減する別の手法として、プロセッサ全体を一時的に停止させて節電状態（スリープ状態）にする技術がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009-64456号公報

10

【非特許文献】

【0006】

【非特許文献1】砂田 徹也著“細粒度パワーゲーティングを制御するOSの資源管理方式”、情報処理学会研究報告、Vol.2010-OS-114 No.8, 2010

【非特許文献2】Intel: Intel Core2 Duo Processors and Intel Core2 Extreme Processors for Platforms Based on Mobile Intel 965 Express Chipset Family Datasheet, In Proceedings of the 40th Annual IEEE/ACM International Symposium on Microarchitecture Pages: 183-196 Year of Publication:2007

【発明の概要】

【発明が解決しようとする課題】

20

【0007】

しかしながら、従来の技術では、マイクロプロセッサなどの処理装置の消費電力を効率的に低減することは困難であるという問題がある。本発明が解決しようとする課題は、処理装置の消費電力を効率的に低減可能な動作切替装置およびプログラムを提供することである。

【課題を解決するための手段】

【0008】

実施形態の動作切替装置は、1または複数の処理を実行可能な処理装置が前記処理を実行していないアイドル状態を検出する状態検出部と、割り込み処理の種別を示す割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを記憶する第4記憶部と、前記割り込み種別と、当該割り込み種別に対応する割り込み待ち時間とを記憶する第5記憶部と、前記状態検出部で前記アイドル状態が検出されたとき、前記第4記憶部に記憶された情報と、前記第5記憶部に記憶された情報に基づいて、現在時刻から、次の前記割り込み処理が開始されるまでの時間長を示す待ち時間を算出する算出部と、前記算出部で算出された前記待ち時間に応じて、前記処理装置の動作モードを決定する決定部と、を備えることを特徴とする。

30

【0009】

また、実施形態のプログラムは、1または複数の処理を実行可能な処理装置が前記処理を実行していないアイドル状態を検出する手順と、前記アイドル状態検出部で前記アイドル状態が検出されたとき、割り込み処理の種別を示す割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを記憶する第4記憶部に記憶された情報と、前記割り込み種別と、当該割り込み種別に対応する割り込み待ち時間とを記憶する第5記憶部に記憶された情報に基づいて、次の前記割り込み処理が開始されるまでの時間長を示す待ち時間を算出する手順と、前記算出部で算出された前記待ち時間に応じて、前記処理装置の動作モードを決定する手順と、をコンピュータに実行させるためのプログラムである。

40

【図面の簡単な説明】

【0010】

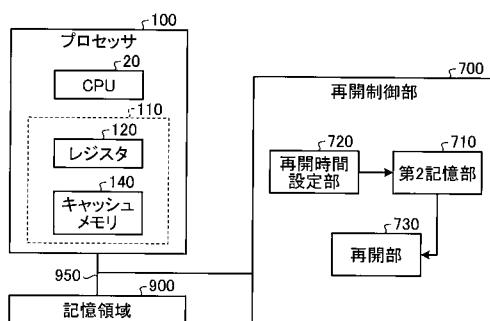

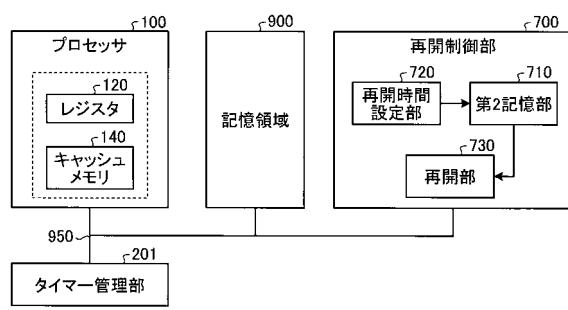

【図1】第1実施形態のターゲットシステムのブロック図。

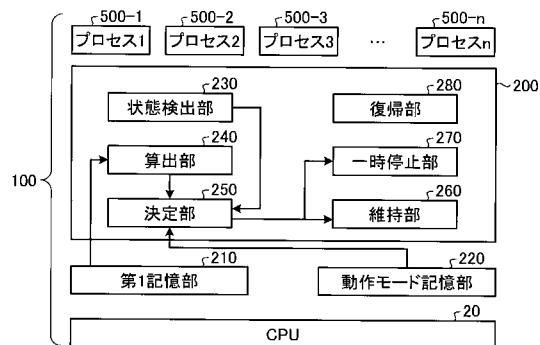

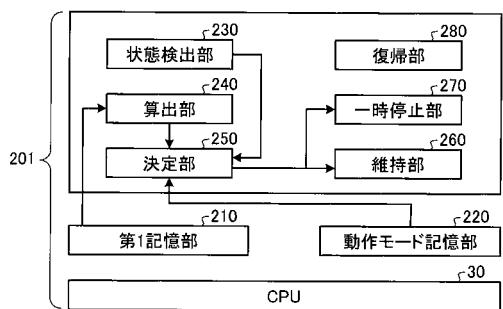

【図2】第1実施形態のプロセッサのブロック図。

【図3】動作モード記憶部に記憶される情報の一例を示す図。

50

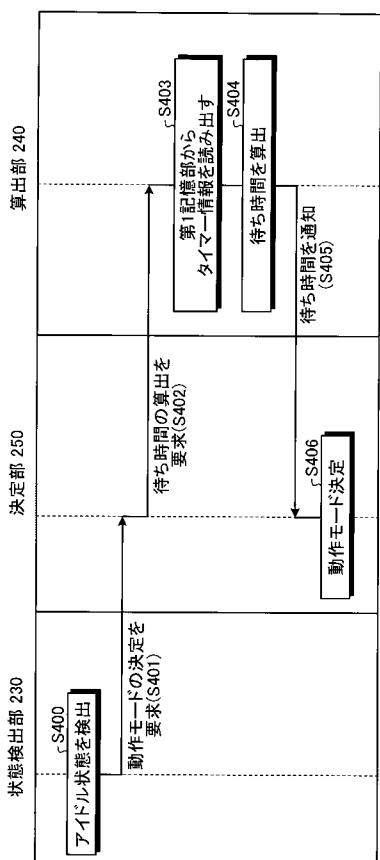

【図4】第1実施形態のターゲットシステムの動作手順を示すシーケンス図。

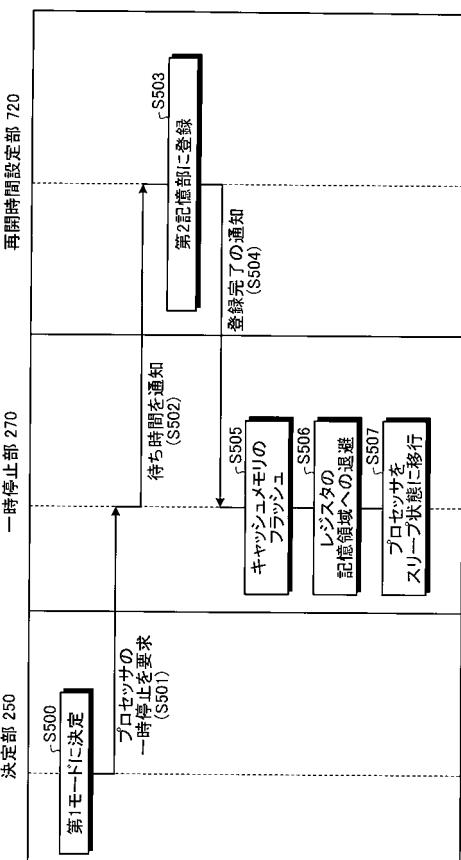

【図5】第1実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図6】第1実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図7】第2実施形態のターゲットシステムのブロック図。

【図8】第2実施形態のプロセッサのブロック図。

【図9】第4記憶部に記憶される情報の一例を示す図。

【図10】第5記憶部に記憶される情報の一例を示す図。

【図11】第2実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図12】第2実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図13】第2実施形態のターゲットシステムの動作手順を示すシーケンス図。

10

【図14】第2実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図15】第2実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図16】第3実施形態のターゲットシステムのブロック図。

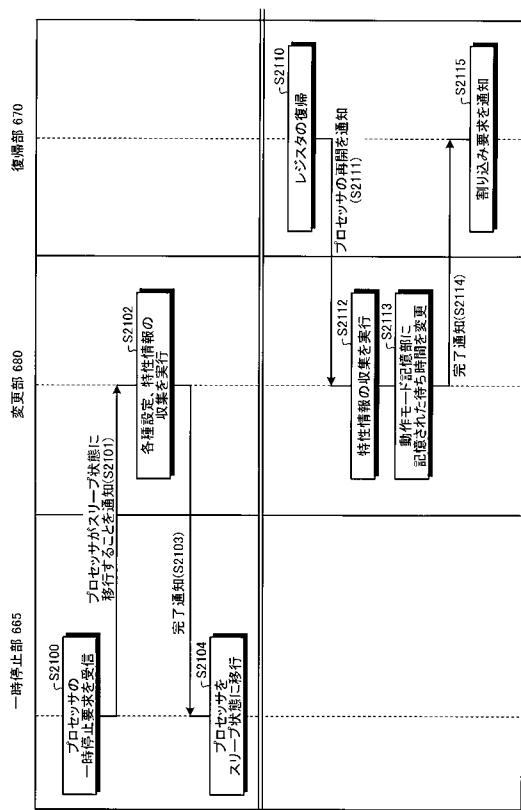

【図17】第3実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図18】第4実施形態のターゲットシステムのブロック図。

【図19】第4実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図20】第5実施形態のターゲットシステムのブロック図。

【図21】第4実施形態のターゲットシステムの動作手順を示すシーケンス図。

【図22】動作モード記憶部に記憶される情報の変形例を示す図。

【図23】変形例のターゲットシステムのブロック図。

20

【図24】変形例のターゲットシステムのブロック図。

【発明を実施するための形態】

【0011】

(第1実施形態)

図1は、本実施形態のターゲットシステムの概略構成の一例を示すブロック図である。図1に示すように、ターゲットシステムは、プロセッサ100と、再開制御部700と、記憶領域900と、を備え、それぞれがバス950で相互に接続されている。プロセッサ100は、1または複数の処理を実行可能な処理装置である。図1に示すように、プロセッサ100は、CPU20と第3記憶部110とを有する。より具体的には、第3記憶部110は、各種のデータが記憶されるレジスタ120と、使用頻度の高いデータなどが記憶されるキャッシュメモリ140とを含む。本実施形態では、レジスタ120およびキャッシュメモリ140の各々は揮発性のメモリで構成される。

30

【0012】

再開制御部700は、後述の節電状態(スリープ状態)にされたプロセッサ100の動作を再開させるための手段である。図1に示すように、再開制御部700は、第2記憶部710と、再開時間設定部720と、再開部730とを有する。第2記憶部710は、後述の待ち時間を記憶する。再開時間設定部720は、プロセッサ100から通知された待ち時間を第2記憶部710に設定する。再開部730は、第2記憶部710に記憶された待ち時間に到達したことを検出すると、プロセッサ100の動作を再開させる。これらの詳細な動作については後述する。

40

【0013】

記憶領域900は、電源OFFした後で再度電源ONした場合に、その内部データを復元できる。これを実現する記憶領域として、例えば不揮発性メモリと呼ばれるものがあり、MRAM(Magnetic Random Access Memory)やFeRAM(Ferroelectric Random Access Memory)で構成することができる。また、不揮発性メモリに限らず、通常のDRAM(Dynamic Random Access Memory)であっても電源ON時に内部データを復元させる機構を持つものもこれに該当する。

【0014】

図2は、プロセッサ100に搭載されたCPU20が、基本ソフトウェアであるOS(operating system)200を実行することにより実現される機能の構成と、プロセッサ1

50

00が備えるハードウェアとを示すブロック図である。ここでは、プロセッサ100上で単一のOS200が動作し、OS200上で1または複数のプロセス(500-1~500-n)が動作すると捉えることができる。また、図2においては、プロセッサ100が備えるハードウェアとプロセッサ100上で動作するOS200、OS200上で動作する1または複数のプロセスをプロセッサ100が含む表現としている。

#### 【0015】

図2に示すように、プロセッサ100が備えるハードウェアには、CPU20と、第1記憶部210と、動作モード記憶部220とが含まれる。第1記憶部210は、タイマー情報を記憶する。タイマー情報には、設定時刻と、当該設定時刻に実行する処理とが含まれる。動作モード記憶部220は、後述の待ち時間と、設定すべき動作モードとの関係を記憶する。この詳細な内容については後述する。

10

#### 【0016】

図2に示すように、OS200は、状態検出部230と、算出部240と、決定部250と、維持部260と、一時停止部270と、復帰部280とを有する。状態検出部230は、アイドル状態を検出可能である。アイドル状態とは、プロセッサ100が何れの処理も実行していない状態を指す。

#### 【0017】

算出部240は、状態検出部230によってアイドル状態が検出されたとき、第1記憶部210に記憶されたタイマー情報を用いて、次の処理が開始されるまでの時間長を示す待ち時間を求める。より具体的には、算出部240は、第1記憶部210に記憶されたタイマー情報から、次の処理が開始される時刻を求め、その求めた時刻と現在時刻との差分の時間長を、待ち時間として求める。

20

#### 【0018】

決定部250は、算出部240から上述の待ち時間を取得し、その取得した待ち時間に応じて、プロセッサ100の動作モードを決定する。より具体的には、決定部250は、算出部240から取得した待ち時間と、動作モード記憶部220に記憶されたデータとから、プロセッサ100の動作モードを決定する。さらに詳述すると以下のとおりである。図3は、動作モード記憶部220に記憶される情報の一例を示す図である。図3に示すように、動作モード記憶部220は、待ち時間と、設定すべき動作モードとの関係を記憶する。決定部250は、待ち時間がt1を越える場合は、プロセッサ100の動作モードを、プロセッサの動作が一時的に停止して節電状態(スリープ状態)となる第1モードに決定する。一方、待ち時間がt1以下の場合は、決定部250は、プロセッサ100がアイドル状態を維持する第2モードに決定する。

30

#### 【0019】

維持部260は、プロセッサ100の動作モードが第2モードのときに、アイドル状態を維持するためのタスク(アイドルタスクと呼ぶ)を実行する。一時停止部270は、決定部250によって、プロセッサ100の動作モードが第1モードに決定されたときに、レジスタ120およびキャッシュメモリ140に記憶されたデータを記憶領域900に退避させ、プロセッサ100の動作を一時的に停止して節電状態(スリープ状態)にする。復帰部280は、スリープ状態にされていたプロセッサ100が動作を再開するときに、記憶領域900に退避されていたデータを、レジスタ120へ復帰させる。詳細な内容については後述する。

40

#### 【0020】

図4は、プロセッサ100のアイドル状態が検出されてから、プロセッサ100の動作モードが決定されるまでの手順の一例を示すシーケンス図である。図4に示すように、まず状態検出部230が、プロセッサ100のアイドル状態を検出し(S400)、決定部250に対して動作モードの決定を要求する(S401)。次に、決定部250は、算出部240に対して、待ち時間の算出を要求する(S402)。

#### 【0021】

次に、算出部240は、第1記憶部210に記憶されたタイマー情報を読み出す(ステ

50

ップS403)。次に、算出部240は、読み出したタイマー情報から、次の処理が実行される時刻を抽出し、その抽出した時刻と現在時刻との差分の時間長を待ち時間として算出する(S404)。そして、算出部240は、その算出した待ち時間を決定部250へ通知する(S405)。

【0022】

次に、決定部250は、算出部240から取得した待ち時間と、動作モード記憶部220に記憶されたデータとから、動作モードを決定する(S406)。

【0023】

図5は、プロセッサ100の動作モードが第1モードに決定されてから、プロセッサ100がスリープ状態にされるまでの手順の一例を示すシーケンス図である。図5に示すように、決定部250は、プロセッサ100の動作モードを第1モードに決定したとき(S500)、一時停止部270に対して、プロセッサ100の動作の一時停止を要求する(S501)。本実施形態では、決定部250は、プロセッサ100の一時停止の要求と併せて、算出部240から取得した待ち時間を、一時停止部270へ通知する。

10

【0024】

次に、一時停止部270は、決定部250から通知された待ち時間を再開時間設定部720へ通知する(S502)。次に、再開時間設定部720は、一時停止部270から通知された待ち時間を第2記憶部710に登録する(S503)。次に、再開時間設定部720は、待ち時間の登録が完了したことを一時停止部270へ通知する(S504)。

20

【0025】

次に、一時停止部270は、キャッシングメモリ140に格納されたデータを記憶領域900へフラッシュする(S505)。フラッシュされた(送り出された)データは記憶領域900に書き込まれる。次に、一時停止部270は、レジスタ120に格納されたデータを記憶領域900へ退避する(S506)。次に、一時停止部270は、プロセッサ100の動作を一時的に停止して節電状態(スリープ状態)に移行させる(S507)。

【0026】

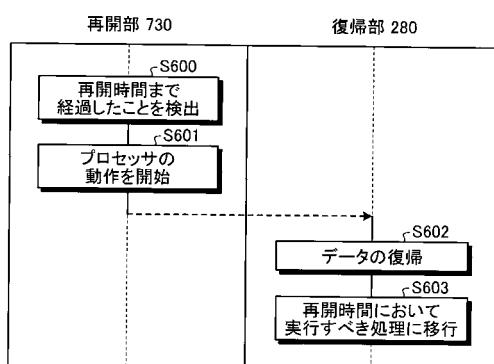

図6は、再開時間に到達してプロセッサ100の動作が再開されるまでの手順の一例を示すシーケンス図である。図6に示すように、再開部730は、再開時間に到達したことを検出したときに(S600)、プロセッサ100の動作を再開させて第1モードを解除する(S601)。

30

【0027】

次に、復帰部280は、一時停止部270によって記憶領域900に退避されていたデータを、レジスタ120へ復帰させる(スップS602)。そして、再開時間において実行すべき処理に移行する(S603)。

【0028】

以上に説明したように、本実施形態では、タイマー情報から求められた待ち時間に応じて、プロセッサ100の動作モードを決定する。より具体的には、待ち時間が所定の時間長(t1)を超える場合は、プロセッサ100をスリープ状態にする一方、待ち時間が所定の時間長以下の場合は、アイドル状態を維持するので、プロセッサ100の消費電力を効率的に低減できる。

40

【0029】

ここで、プロセッサ100をスリープ状態に移行させて消費電力を低減する方法は、プロセッサ100の消費電力を低減できる一方で、プロセッサ100を一時的に停止させるための処理等によるオーバーヘッドが大きい、当該処理(例えばレジスタの退避および復帰やキャッシングメモリのフラッシュなどの処理)やそれによる影響(キャッシングメモリのフラッシュによるメモリアクセス増加等)で発生する消費電力も無視できない。このため、プロセッサ100がアイドル状態に移行してから、次の処理が実行されるまでの時間長(待ち時間)の値によっては、プロセッサ100をスリープ状態に移行させると発生する消費電力の方が、プロセッサ100をスリープ状態に移行させることによって低減できる消費電力よりも大きい場合がある。

50

## 【0030】

本実施形態では、上述の待ち時間が所定の時間長を超えるときのみに、プロセッサ100をスリープ状態に移行させてるので、効率的に消費電力を低減できるという利点がある。なお、本実施形態では、プロセッサ100のみを、プロセッサ100の動作モードを切り替え可能な動作切替装置として捉えることができるし、プロセッサ100と再開制御部700とを動作切替装置として捉えることもできる。

## 【0031】

## (第2実施形態)

本実施形態では、プロセッサ100がアイドル状態になってから、最も早い割り込み処理が開始されるまでの時間長を待ち時間として算出する点で第1実施形態と異なる。以下、具体的な内容を説明する。なお、第1実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

## 【0032】

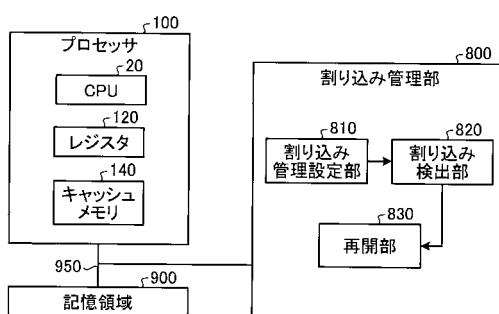

図7は、本実施形態のターゲットシステムの概略構成の一例を示すブロック図である。図7に示すように、ターゲットシステムは、プロセッサ100と、割り込み管理部800と、記憶領域900と、を備え、それぞれがバス950で相互に接続されている。割り込み管理部800は、プロセッサ100が節電状態(スリープ状態)になっている場合に、プロセッサ100の代わりに割り込みを管理する手段である。図7に示すように、割り込み管理部800は、割り込み管理設定部810と、割り込み検出部820と、再開部830とを有する。

10

## 【0033】

割り込み管理設定部810は、決定部250によってプロセッサ100の動作モードが第1モードに決定されたときに、割り込み検出部820に対して、プロセッサ100がスリープ状態に移行することを通知する。割り込み検出部820は、割り込み処理の発生を検出する。再開部830は、割り込み検出部820で割り込み処理の発生が検出されたときに、スリープ状態のプロセッサ100の動作を再開させる。割り込み検出部820は、割り込みを検出すると、プロセッサ100がスリープ状態のときには、再開部830に対して後述の再開要求を通知する。再開部830は、割り込み検出部820から再開要求が通知されたときに、スリープ状態のプロセッサ100の動作を再開させる。

20

## 【0034】

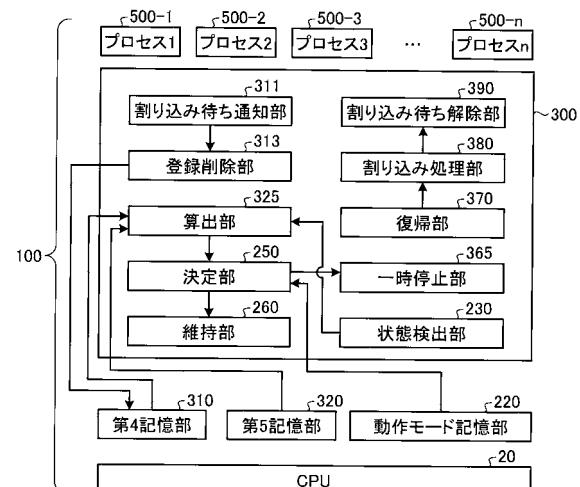

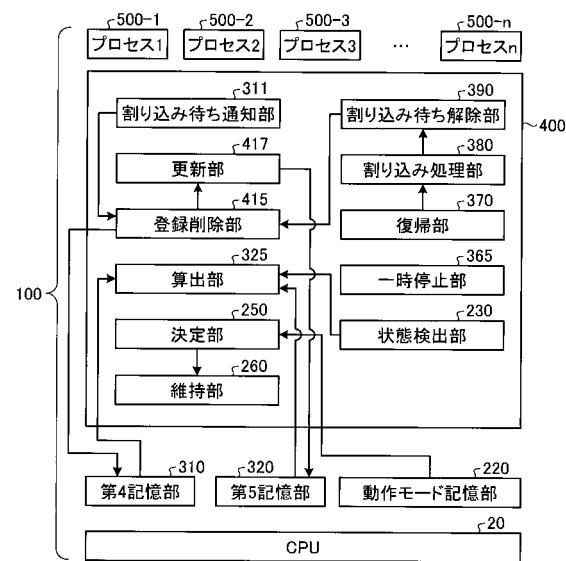

図8は、プロセッサ100に搭載されたCPU20が、OS300を実行することにより実現される機能の構成と、プロセッサ100が備えるハードウェアとを示すブロック図である。図8に示すように、プロセッサ100が備えるハードウェアには、CPU20と、第4記憶部310と、第5記憶部320と、動作モード記憶部220とが含まれる。また、図8においては、プロセッサ100が備えるハードウェアとプロセッサ100上で動作するOS300、OS300上で動作する1または複数のプロセスをプロセッサ100が含む表現としている。

30

## 【0035】

第4記憶部310は、割り込み待ち情報を記憶する。割り込み待ち情報には、割り込み処理の種別を示す割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とが含まれる。図9は、第4記憶部310に記憶された割り込み待ち情報の一例を示す図である。図9の例では、割り込み種別は、デバイス読み出しとキーボード入力の2種類である。また、デバイス読み出しの割り込み待ちが発生した時刻はT\_aであり、キーボード入力の割り込み待ちが発生した時刻はT\_bである。

40

## 【0036】

図8に示す第5記憶部320は、割り込み種別と、当該割り込み種別に対応する割り込み待ち時間とを記憶する。各割り込み種別に対応する割り込み待ち時間は、予め計算等によって求められた予測値である。図10は、第5記憶部320に記憶された情報の一例を示す図である。図10の例では、デバイス読み出しに対応する割り込み待ち時間はT3に設定される。また、キーボード入力に対応する割り込み待ち時間はT4に設定される。さ

50

らに、マウス入力に対応する割り込み待ち時間は T 5 に設定される。

【 0 0 3 7 】

再び図 8 に戻って説明を続ける。図 8 に示すように、O S 3 0 0 は、割り込み待ち通知部 3 1 1 と、登録削除部 3 1 3 と、算出部 3 2 5 と、決定部 2 5 0 と、維持部 2 6 0 と、状態検出部 2 3 0 と、一時停止部 3 6 5 と、復帰部 3 7 0 と、割り込み処理部 3 8 0 と、割り込み待ち解除部 3 9 0 とを有する。割り込み待ち通知部 3 1 1 は、割り込み待ちが発生したときに、当該割り込み待ちとなった割り込み種別を、登録削除部 3 1 3 へ通知する。登録削除部 3 1 3 は、割り込み待ち通知部 3 1 1 から通知された割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを第 4 記憶部 3 1 0 に登録する。一方、登録削除部 3 1 3 は、割り込み処理が開始されるときに、割り込み待ちが解除された割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを第 4 記憶部 3 1 0 から削除する。詳細な内容については後述する。

10

【 0 0 3 8 】

算出部 3 2 5 は、状態検出部 2 3 0 によってアイドル状態が検出されたとき、第 4 記憶部 3 1 0 に記憶された割り込み待ち情報と、第 5 記憶部 3 2 0 に記憶された情報とに基づいて、現在時刻から、次の割り込み処理が開始されるまでの時間長を待ち時間として算出する。詳細な内容については後述する。

【 0 0 3 9 】

一時停止部 3 6 5 は、決定部 2 5 0 によって、プロセッサ 1 0 0 の動作モードが第 1 モードに決定されたときに、レジスタ 1 2 0 およびキャッシュメモリ 1 4 0 に記憶されたデータを記憶領域 9 0 0 に退避させ、プロセッサ 1 0 0 の動作を一時的に停止して節電状態（スリープ状態）にする。復帰部 3 7 0 は、スリープ状態にされていたプロセッサ 1 0 0 が動作を再開するときに、記憶領域 9 0 0 に退避されていたデータを、レジスタ 1 2 0 へ復帰させる。

20

【 0 0 4 0 】

割り込み処理部 3 8 0 は、割り込み管理部 8 0 0 から、割り込み処理の発生を通知する割り込み通知を受信したときに、割り込み処理を開始する。また、割り込み処理部 3 8 0 は、割り込み管理部 8 0 0 からの割り込み通知を受信したときに、当該割り込み通知で特定される割り込み種別を、割り込み待ち解除部 3 9 0 へ通知する。割り込み待ち解除部 3 9 0 は、割り込み処理部 3 8 0 から通知された割り込み種別の割り込み待ちを解除する要求を、登録削除部 3 1 3 へ通知する。

30

【 0 0 4 1 】

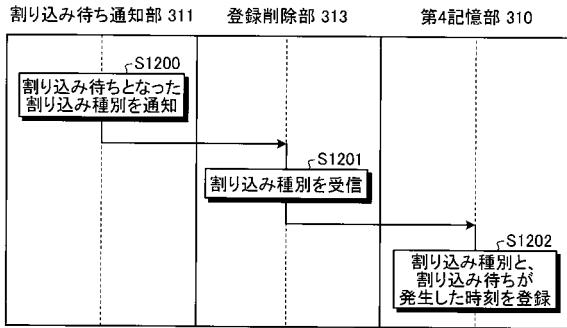

図 1 1 は、割り込み待ちが発生したときのプロセッサ 1 0 0 の動作手順の一例を示すシーケンス図である。本実施形態では、デバイスが割り込み待ちの状態になると、当該デバイスの割り込み待ちが発生したことを示す情報が、デバイスドライバ等から割り込み待ち通知部 3 1 1 へ通知される。図 1 1 に示すように、割り込み待ちが発生すると、割り込み待ち通知部 3 1 1 は、当該割り込み待ちとなった割り込み種別を登録削除部 3 1 3 へ通知する（ステップ S 1 2 0 0）。登録削除部 3 1 3 は、割り込み待ち通知部 3 1 1 から通知された割り込み種別を受信したときに（S 1 2 0 1）、その受信した割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを第 4 記憶部 3 1 0 に登録する（S 1 2 0 2）。

40

【 0 0 4 2 】

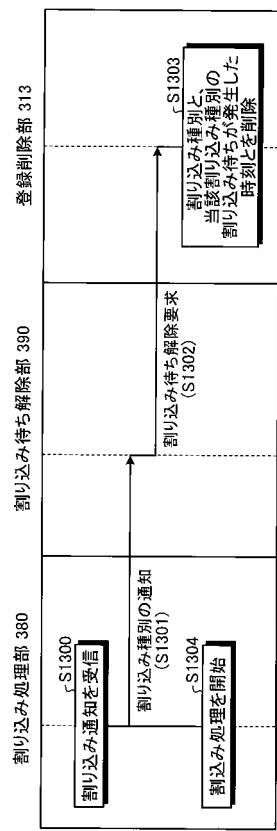

図 1 2 は、割り込み処理が発生したときのプロセッサ 1 0 0 の動作手順の一例を示すシーケンス図である。図 1 2 に示すように、割り込み処理部 3 8 0 は、割り込み管理部 8 0 0 からの割り込み通知を受信したときに（S 1 3 0 0）、当該割り込み通知で特定される割り込み種別を、割り込み待ち解除部 3 9 0 へ送信する（S 1 3 0 1）とともに、当該割り込み通知で特定される割り込み処理を開始する（S 1 3 0 4）。

【 0 0 4 3 】

割り込み待ち解除部 3 9 0 は、割り込み処理部 3 8 0 から通知された割り込み種別の割り込み待ちを解除することを要求する割り込み待ち解除要求を、登録削除部 3 1 3 へ通知

50

する（S1302）。登録削除部313は、割り込み待ち解除部390から割り込み待ちの解除を要求された割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを、第4記憶部310から削除する（S1303）。このように、第4記憶部310には、割り込み待ちが発生したときには、当該割り込み待ちとなった割り込み種別と、当該割り込み待ちが発生した時刻とが登録される一方、割り込み待ちが解除されたときには、割り込み待ちが解除される割り込み種別と、当該割り込み待ちが発生した時刻とが削除される。これにより、現在の割り込み待ちの状況を適切に管理することができる。

#### 【0044】

図13は、プロセッサ100のアイドル状態が検出されてから、プロセッサ100の動作モードが決定されるまでの手順の一例を示すシーケンス図である。図13に示すように、まず状態検出部230が、プロセッサ100のアイドル状態を検出し（ステップS1400）、決定部250に対して、動作モードの決定を要求する（S1401）。次に、決定部250は、算出部325に対して、次の割り込み処理が発生するまでの時間長を示す待ち時間の算出を要求する（S1402）。

10

#### 【0045】

次に、算出部325は、第4記憶部310に記憶された割り込み待ち情報を取得する（S1403）。次に、算出部325は、現在割り込み待ちになっている割り込み種別に対応する割り込み待ち時間を第5記憶部320から取得する（S1404）。次に、算出部325は、第4記憶部310から取得した割り込み待ち情報をと、第5記憶部320から取得した割り込み待ち時間とから、待ち時間を算出する（S1405）。

20

#### 【0046】

ここで、算出部325による待ち時間の算出方法の具体例を説明する。例えば、現在、デバイス読み出しとキーボード入力の割り込み待ちであって、キーボード入力の割り込み待ちの発生時刻T\_bの方が、デバイス読み出しの割り込み待ちの発生時刻T\_aよりも先であり、かつ、キーボード入力に対応する割り込み待ち時間T4の方が、デバイス読み出しに対応する割り込み待ち時間T3よりも短い場合を想定する。この場合、キーボード入力の方がデバイス読み出しそれよりも先に実行されるので、次の割り込み処理は、キーボード入力となり、上述の時刻T\_bから時間長T4が経過した時点で、当該キーボード入力が実行される。このようにして、次の割り込み処理であるキーボード入力が開始される時刻を特定することができるので、算出部325は、現在時刻から、キーボード入力が開始される時刻までの時間長を待ち時間として算出する。そして、算出部325は、算出した待ち時間を決定部250へ通知する（S1406）。

30

#### 【0047】

次に、決定部250は、算出部325から取得した待ち時間と、動作モード記憶部220に記憶されたデータとから、動作モードを決定する（S1407）。動作モードの決定方法は、上述の第1実施形態と同じである。

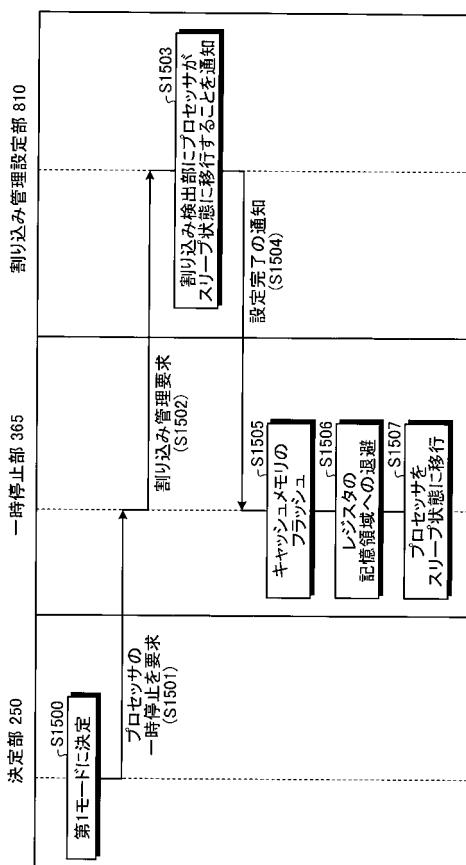

#### 【0048】

図14は、プロセッサ100の動作モードが第1モードに決定されてから、プロセッサ100がスリープ状態にされるまでの手順の一例を示すシーケンス図である。図14に示すように、決定部250は、プロセッサ100の動作モードを第1モードに決定したとき（ステップS1500）、一時停止部365に対して、プロセッサ100の動作の一時停止を要求する（S1501）。

40

#### 【0049】

次に、一時停止部365は、割り込み管理設定部810に対して、割り込み管理を要求する（S1502）。割り込み管理を要求された割り込み管理設定部810は、割り込み検出部820に対して、プロセッサ100がスリープ状態に移行することを通知する（S1503）。次に、割り込み管理設定部810は、一時停止部365に対して、設定完了を通知する（S1504）。

#### 【0050】

次に、一時停止部365は、キャッシングメモリ140に格納されたデータを記憶領域9

50

00へフラッシュする(S1505)。フラッシュされたデータは記憶領域900に書き込まれる。次に、一時停止部365は、レジスタ120に格納されたデータを記憶領域900へ退避する(ステップS1506)。次に、一時停止部365は、プロセッサ100をスリープ状態に移行させる(S1507)。

#### 【0051】

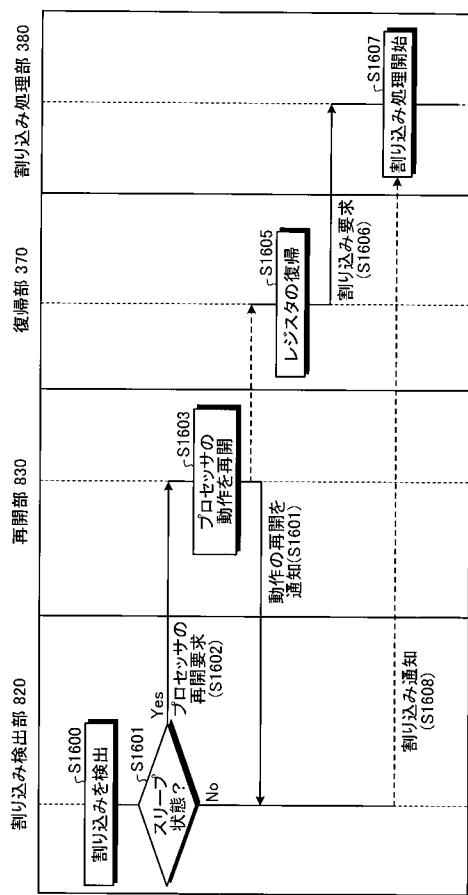

図15は、割り込みが検出されてから、当該割り込み処理が開始されるまでの手順の一例を示すシーケンス図である。図15に示すように、割り込み検出部820は、割り込みを検出したときに(S1600)、プロセッサ100がスリープ状態であるか否かを判断する(S1601)。例えば割り込み管理設定部810からプロセッサ100がスリープ状態に移行することを通知されていた場合は、割り込み検出部820は、プロセッサ100がスリープ状態であると判断し、プロセッサ100の動作の再開を要求する再開要求を再開部830に対して通知する(S1602)。一方、割り込み検出部820は、プロセッサ100がスリープ状態でないと判断した場合は、割り込み処理部380に対して割り込み通知を送信する(S1608)。

#### 【0052】

図15に示すように、再開部830は、割り込み検出部820から、プロセッサ100の再開要求が通知されたときに、プロセッサ100の動作を再開させて第1モードを解除する(S1603)。そして、再開部830は、割り込み検出部820に対して、プロセッサ100の動作を再開させたことを通知する(S1604)。当該通知を受けた割り込み検出部820は、割り込み処理部380に対して割り込み通知を送信する(S1608)。

#### 【0053】

プロセッサ100の動作が再開されると、復帰部370は、一時停止部365によって記憶領域900に退避されていたデータを、レジスタ120へ復帰させる(ステップS1605)。そして、復帰部370は、割り込み処理部380に対して、割り込みの実行を要求する割り込み要求を通知する(S1606)。当該割り込み要求が通知された割り込み処理部380は、割り込み検出部820から割り込み通知を受信したときに、当該割り込み通知で特定される割り込み処理を開始する(S1607)。

#### 【0054】

以上に説明したように、本実施形態では、プロセッサ100がアイドル状態になってから、最も早い割り込み処理(次の割り込み処理)が開始されるまでの時間長を待ち時間として算出し、その算出した待ち時間に応じて、プロセッサ100の動作モードを決定する。この構成であっても、上述の第1実施形態と同様に、プロセッサ100の消費電力を効率的に低減できる。なお、上述の実施形態では、プロセッサ100のみを動作切替装置として捉えることができるし、プロセッサ100と割り込み管理部800とを動作切替装置として捉えることもできる。

#### 【0055】

##### (第3実施形態)

上述の第2実施形態では、第5記憶部320に記憶された割り込み待ち時間の値は固定値であったが、第3実施形態では、第5記憶部320に記憶された割り込み待ち時間の値が可変に設定される。以下、具体的な内容を説明する。なお、第2実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

#### 【0056】

図16は、プロセッサ100に搭載されたCPU20が、OS400を実行することにより実現される機能の構成と、プロセッサ100が備えるハードウェアとを示すブロック図である。図16に示すように、OS400は、割り込み待ち通知部311と、更新部417と、登録削除部415と、算出部325と、決定部250と、維持部260と、状態検出部230と、一時停止部365と、復帰部370と、割り込み処理部380と、割り込み待ち解除部390とを有する。また、図16においては、プロセッサ100が備えるハードウェアとプロセッサ100上で動作するOS400、OS400上で動作する1ま

たは複数のプロセスをプロセッサ 100 が含む表現としている。

【0057】

登録削除部 415 は、上述の第 2 実施形態で説明した機能に加えて、割り込み待ち解除部 390 から割り込み待ち解除要求が通知されたときに、割り込み待ち解除が要求された割り込み種別の割り込み待ちが発生した時刻を、第 4 記憶部 310 から読み出す。そして、登録削除部 415 は、その読み出した時刻と、割り込み待ち解除が要求された割り込み種別とを更新部 417 へ通知する。

【0058】

更新部 417 は、登録削除部 415 から通知された時刻（登録削除部 415 から通知された割り込み種別で特定される割り込みの割り込み待ちが発生した時刻）と、現在時刻（割り込み処理が開始される時刻に相当）とから、割り込み待ちが継続した時間（割り込み待ち時間）を算出する。より具体的には、更新部 417 は、登録削除部 415 から通知された時刻と、現在時刻との差分の時間長を割り込み待ち時間として算出する。そして、更新部 417 は、算出した割り込み待ち時間を用いて第 5 記憶部 320 に記憶された割り込み待ち時間を更新する。より具体的には、更新部 417 は、第 5 記憶部 320 に記憶された割り込み待ち時間のうち、登録削除部 415 から通知された割り込み種別に対応する割り込み待ち時間の値を、算出した割り込み待ち時間の値に更新する。

【0059】

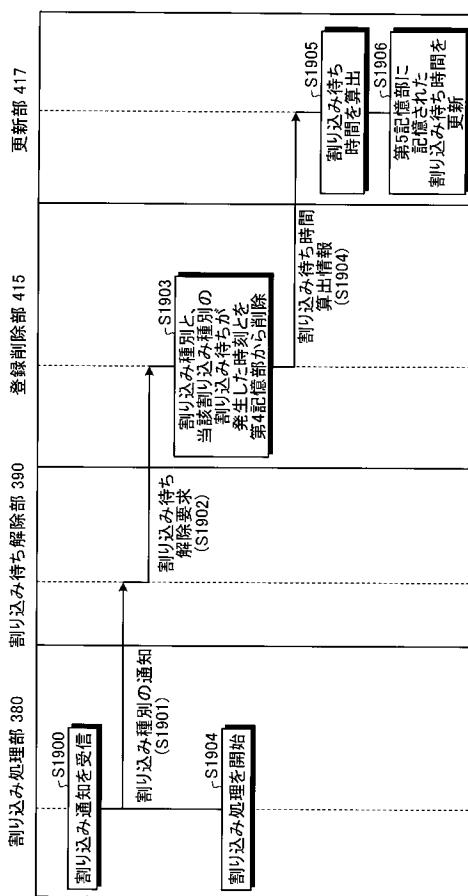

図 17 は、割り込み処理部 380 が上述の割り込み通知を受信してから、更新部 417 による更新が行われるまでの手順の一例を示すシーケンス図である。図 17 に示すように、割り込み処理部 380 は、割り込み管理部 800 からの割り込み通知を受信したときに（S1900）、割り込み待ちが解除される割り込み種別を、割り込み待ち解除部 390 へ通知する（S1901）とともに、当該割り込み通知で特定される割り込み処理を開始する（S1904）。

【0060】

割り込み待ち解除部 390 は、割り込み処理部 380 から通知された割り込み種別の割り込み待ちの解除を要求する割り込み待ち解除要求を、登録削除部 415 へ通知する（S1902）。次に、登録削除部 415 は、割り込み待ち解除部 390 から割り込み待ちの解除を要求された割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを、第 4 記憶部 310 から削除する（S1903）とともに、割り込み待ちの解除が要求された割り込み種別と、当該割り込み種別の割り込み待ちが発生した時刻とを、割り込み待ち時間の算出に用いられる割り込み待ち時間算出情報として更新部 417 へ通知する（S1904）。

【0061】

更新部 417 は、登録削除部 415 から通知された割り込み待ち時間情報に基づいて、割り込み待ち時間を算出する（S1905）。割り込み待ち時間の算出方法については上述したとおりであるので、詳細な説明は省略する。次に、更新部 417 は、算出した割り込み待ち時間を用いて、第 5 記憶部 320 に記憶された割り込み待ち時間を更新する（S1906）。更新方法は、上述したとおりであるので、詳細な説明は省略する。

【0062】

以上に説明したように、本実施形態では、更新部 417 によって最新の割り込み待ち時間が算出されるたびに、第 5 記憶部 320 に記憶された割り込み待ち時間の値が更新されるので、第 5 記憶部 320 に記憶された割り込み待ち時間の値を、現在のターゲットシステムにとって最適な値に近づけることができる。

【0063】

（第 4 実施形態）

上述の第 1 実施形態では、動作モード記憶部 220 に記憶された、動作モードの移行条件を示す待ち時間の値は固定値であったが、第 4 実施形態では、動作モード記憶部 220 に記憶された待ち時間の値が可変に設定される。以下、具体的な内容を説明する。なお、第 1 実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

10

20

30

40

50

## 【0064】

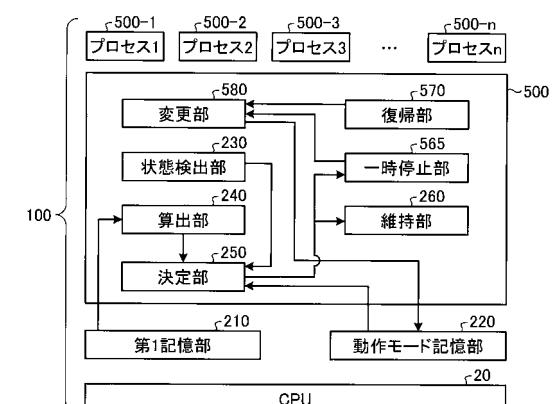

図18は、プロセッサ100に搭載されたCPU20が、OS500を実行することにより実現される機能の構成と、プロセッサ100が備えるハードウェアとを示すブロック図である。図18に示すように、OS500は、変更部580と、状態検出部230と、算出部240と、決定部250と、維持部260と、一時停止部565と、復帰部570とを有する。また、図18においては、プロセッサ100が備えるハードウェアとプロセッサ100上で動作するOS500、OS500上で動作する1または複数のプロセスをプロセッサ100が含む表現としている。

## 【0065】

一時停止部565は、上述の第1実施形態で説明した機能に加えて、決定部250から、プロセッサ100の動作の一時停止を要求されたときに、プロセッサ100がスリープ状態に移行することを変更部580に通知する。復帰部570は、上述の第1実施形態で説明した機能に加えて、一時停止部565によって記憶領域900に退避されていたデータを、レジスタ120へ復帰させたときに、プロセッサ100の動作の再開を変更部580へ通知する。

10

## 【0066】

変更部580は、プロセッサ100がスリープ状態になったときから動作を再開するまでの間におけるプロセッサ100の特性を示す特性情報に応じて、動作モード記憶部220に記憶された待ち時間の値を変更する。ここでは、特性情報としてプロセッサ100の消費電力が採用されている。ただし、これに限らず、特性情報の種類は任意である。例えばプロセッサ100の温度情報やキャッシュのヒット率などを特性情報として採用することもできる。要するに、特性情報は、動作モード記憶部220に記憶された待ち時間の変更に必要な情報であればよい。

20

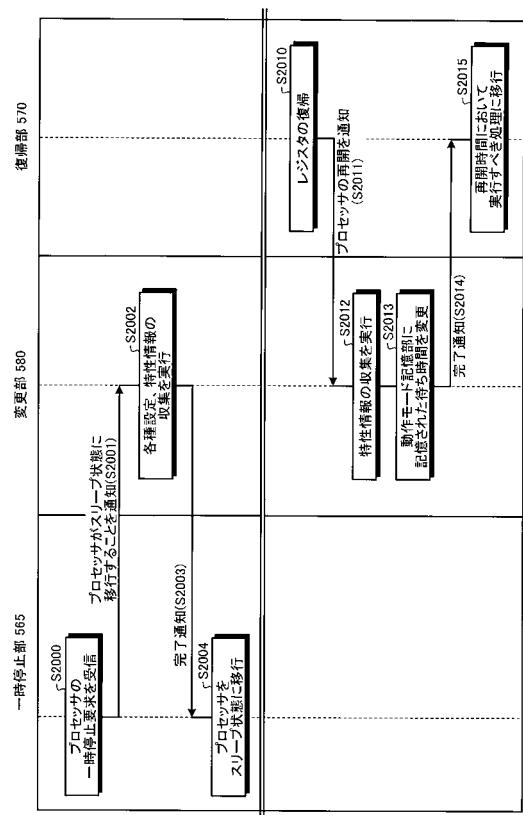

## 【0067】

図19は、プロセッサ100の一時停止が要求されてから、動作モード記憶部220に記憶された待ち時間が変更されるまでの手順の一例を示すシーケンス図である。図19に示すように、一時停止部565は、決定部250から、プロセッサ100の動作の一時停止要求を受信したときに(S2000)、プロセッサ100がスリープ状態に移行することを変更部580へ通知する(S2001)。

## 【0068】

30

次に、変更部580は、動作モード記憶部220に記憶された待ち時間の変更に必要な各種設定や特性情報の収集を行う(S2002)。例えば変更部580は、特定期間におけるプロセッサ100の消費電力を計測可能な計測装置をリセットし、その計測装置に対して、プロセッサ100がスリープ状態に移行した時点からの消費電力を計算させる。そして、変更部580は、一時停止部565に対して、各種設定および特性情報の収集の実行が完了したことを通知する(S2003)。一時停止部565は、変更部580からの完了通知を受けたときに、プロセッサ100の動作を一時的に停止して節電状態(スリープ状態)に移行させる(S2004)。

## 【0069】

40

その後、上述したように、再開時間に到達して、再開部730がプロセッサ100の動作を再開させたとき、復帰部570は、一時停止部565によって記憶領域900に退避されていたデータを、レジスタ120へ復帰させる(ステップS2010)。次に、復帰部570は、変更部580に対して、プロセッサ100の動作が再開されたことを通知する(S2011)。

## 【0070】

変更部580は、復帰部570から、プロセッサ100の動作の再開を通知されたときに、特性情報の収集を実行する(S2012)。例えば変更部580は、上述の計測装置から、プロセッサ100がスリープ状態に移行した時点から現在に至るまでの消費電力を取得することができる。

## 【0071】

50

次に、変更部 580 は、これまでに収集した特性情報に基づいて、動作モード記憶部 220 に記憶された待ち時間を変更する (S2013)。例えば待ち時間が  $t_y (> t_1)$  の場合に、当該  $t_y$  にわたってプロセッサ 100 がスリープ状態に維持されたときの消費電力  $W_2$  が、待ち時間  $t_1$  にわたってプロセッサ 100 がアイドル状態に維持されていたときの消費電力  $W_1$  を大きく下回った場合には、動作モードの移行条件を示す待ち時間の値を  $t_1$  より小さくすることが好みしい。

#### 【0072】

動作モード記憶部 220 に記憶された待ち時間の変更が完了すると、変更部 580 は、待ち時間の変更が完了したことを復帰部 570 へ通知する (S2014)。復帰部 570 は、変更部 580 から当該完了通知を受けたときに、再開時間において実行すべき処理に 10 移行する (S2015)。

#### 【0073】

以上に説明したように、本実施形態では、プロセッサ 100 がスリープ状態になったときから動作を再開するまでの間におけるプロセッサ 100 の消費電力（特性情報の一例）に応じて、動作モード記憶部 220 に記憶された待ち時間の値が可変に設定されるので、動作モード記憶部 220 に記憶された待ち時間の値を、現在のターゲットシステムにとつて最適な値に近づけることができる。

#### 【0074】

##### （第 5 実施形態）

上述の第 2 実施形態では、動作モード記憶部 220 に記憶された、動作モードの移行条件を示す待ち時間の値は固定値であったが、第 5 実施形態では、第 4 実施形態と同様に、動作モード記憶部 220 に記憶された待ち時間の値が可変に設定される。以下、具体的な内容を説明する。なお、第 2 実施形態および第 4 実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。 20

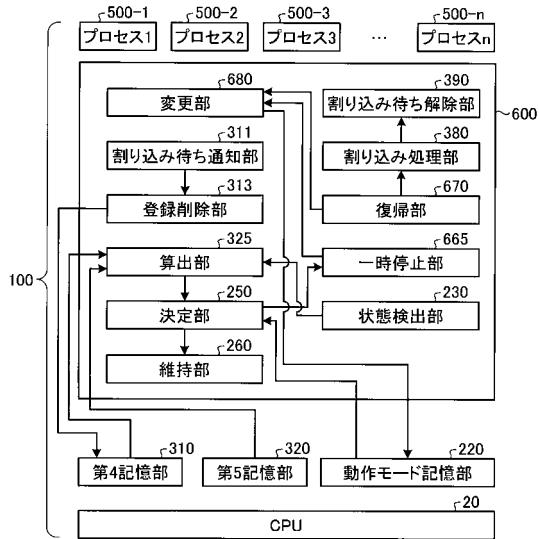

#### 【0075】

図 20 は、プロセッサ 100 に搭載された CPU 20 が、OS600 を実行することにより実現される機能の構成と、プロセッサ 100 が備えるハードウェアとを示すブロック図である。図 20 に示すように、OS600 は、変更部 680 と、割り込み待ち通知部 311 と、登録削除部 313 と、算出部 325 と、決定部 250 と、維持部 260 と、状態検出部 230 と、一時停止部 665 と、復帰部 670 と、割り込み処理部 380 と、割り込み待ち解除部 390 とを有する。また、図 20 においては、プロセッサ 100 が備えるハードウェアとプロセッサ 100 上で動作する OS600、OS600 上で動作する 1 または複数のプロセスをプロセッサ 100 が含む表現としている。 30

#### 【0076】

一時停止部 665 は、上述の第 2 実施形態で説明した機能に加えて、決定部 250 から、プロセッサ 100 の動作の一時停止を要求されたときに、プロセッサ 100 がスリープ状態に移行することを変更部 680 に通知する。復帰部 670 は、上述の第 2 実施形態で説明した機能に加えて、一時停止部 665 によって記憶領域 900 に退避されていたデータを、レジスタ 120 へ復帰させたときに、プロセッサ 100 の動作の再開を変更部 680 へ通知する。 40

#### 【0077】

変更部 680 は、プロセッサ 100 がスリープ状態になったときから動作を再開するまでの間におけるプロセッサ 100 の特性を示す特性情報に応じて、動作モード記憶部 220 に記憶された待ち時間の値を変更する。ここでは、第 4 実施形態と同様、特性情報としてプロセッサ 100 の消費電力が採用されている。

#### 【0078】

図 21 は、プロセッサ 100 の一時停止が要求されてから、動作モード記憶部 220 に記憶された待ち時間が変更されるまでの手順の一例を示すシーケンス図である。図 21 に示すように、一時停止部 665 は、決定部 250 から、プロセッサ 100 の動作の一時停止要求を受信したときに (S2100)、プロセッサ 100 がスリープ状態に移行するこ 50

とを変更部 680 へ通知する (S2101)。

【0079】

次に、変更部 680 は、動作モード記憶部 220 に記憶された待ち時間の変更に必要な各種設定や特性情報の収集を行う (S2102)。この内容は上述の第4実施形態と同じである。次に、変更部 580 は、一時停止部 665 に対して、各種設定および特性情報の収集の実行が完了したことを通知する (S2103)。一時停止部 665 は、変更部 680 からの完了通知を受けたときに、プロセッサ 100 の動作を一時的に停止して節電状態 (スリープ状態) に移行させる (S2104)。

【0080】

その後、上述したように、割り込み検出部 820 が割り込みを検出して、再開部 830 がプロセッサ 100 の動作を再開させたとき、復帰部 670 は、一時停止部 665 によって記憶領域 900 に退避されていたデータを、レジスタ 120 へ復帰させる (ステップ S2110)。次に、復帰部 670 は、変更部 680 に対して、プロセッサ 100 の動作が再開されたことを通知する (S2111)。

【0081】

変更部 680 は、復帰部 670 から、プロセッサ 100 の動作の再開を通知されたときに、特性情報の収集を実行する (S2112)。この内容は上述の第4実施形態と同じである。

【0082】

次に、変更部 680 は、これまでに収集した特性情報に基づいて、動作モード記憶部 220 に記憶された待ち時間を変更する (S2113)。この内容は上述の第4実施形態と同じである。動作モード記憶部 220 に記憶された待ち時間の変更が完了すると、変更部 680 は、待ち時間の変更が完了したことを復帰部 670 へ通知する (S2114)。復帰部 670 は、変更部 680 から当該通知を受けたときに、割り込み処理部 380 に対して割り込み要求を通知する (S2115)。

【0083】

本実施形態においても、上述の第4実施形態と同様に、プロセッサ 100 がスリープ状態になったときから動作を再開するまでの間におけるプロセッサ 100 の消費電力に応じて、動作モード記憶部 220 に記憶された待ち時間の値が可変に設定されるので、動作モード記憶部 220 に記憶された待ち時間の値を、現在のターゲットシステムにとって最適な値に近づけることができる。

【0084】

(変形例)

以上、本発明の実施形態を説明したが、上述の各実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。例えば上述の各実施形態では、タイマー情報や割り込み予測から待ち時間を算出しているが、本発明はこれに限定されるものではない。要するに、本発明は、プロセッサ 100 のアイドル状態が検出されたとき、次の処理が開始されるまでの時間長を示す待ち時間を算出し、その算出した待ち時間に応じて動作モードを決定するものであればよい。

【0085】

また、例えば上述の動作モード記憶部 220 に記憶される動作モードの移行条件は任意である。例えば図 22 に示すように、決定部 250 は、待ち時間が  $t_2$  以下の場合は、プロセッサ 100 の動作モードを上述の第2モードに決定し、待ち時間が  $t_2$  を超えて  $t_3$  未満の場合は、プロセッサ 100 の動作モードを、DVF S による周波数制御が行われる第3モードに決定し、待ち時間が  $t_3$  以上の場合は、プロセッサ 100 の動作モードを上述の第1モードに決定することもできる。図 22 の例も、決定部 250 は、待ち時間が所定の時間長 (ここでは  $t_2$  ) を越える場合は、プロセッサ 100 の動作モードを第1モードに変更する。

10

20

30

40

50

ドに決定する一方、待ち時間が所定の時間長以下の場合は、プロセッサ100の動作モードを第2モードに決定するという概念に含まれる。

#### 【0086】

また、上述の各実施形態では、プロセッサ100は、それぞれが揮発性のメモリで構成されるレジスタ120およびキャッシュメモリ140を有しているが、これに限らず、例えばプロセッサ100が、キャッシュメモリ140を有しない構成であってもよい。この構成であれば、キャッシュメモリ140に記憶されたデータのフラッシュ処理を省略できる。また、レジスタ120やキャッシュメモリ140が不揮発性のメモリで構成されてもよい。この構成であれば、レジスタ120やキャッシュメモリ140に記憶されたデータの退避処理および復帰処理を省略できる。

10

#### 【0087】

さらに、上述したOS(200, 300, 400, 500, 600)の機能の少なくとも一部が、プロセッサ100以外のハードウェアで実現される構成であってもよい。例えば図23に示すように、第1実施形態のOS200の機能が、プロセッサ100とは別のハードウェアであるタイマー管理部201で実現することもできる。

#### 【0088】

図24は、タイマー管理部201のCPU30が、プログラムを実行することにより実現される機能の構成と、タイマー管理部201が備えるハードウェアとを示すブロック図である。図24に示すように、タイマー管理部201が備えるハードウェアには、CPU30と、第1記憶部210と、動作モード記憶部220とが含まれる。また、図24に示すように、CPU30がプログラムを実行することにより実現される機能は、状態検出部230、算出部240、決定部250、維持部260、一時停止部270および復帰部280である。図23および図24の例では、タイマー管理部201を動作切替装置として捉えることができる。また、図24においては、タイマー管理部201が備えるハードウェアとタイマー管理部201上で動作するOS、OS上で動作する1または複数のプロセスをタイマー管理部201が含む表現としている。

20

#### 【0089】

なお、図23および図24の例に限らず、例えばOS200の一部の機能のみがプロセッサ100とは別のハードウェアで実現され、他の機能はOS200上で実現されてもよい。他の実施形態(第2実施形態～第5実施形態)についても同様である。

30

#### 【符号の説明】

##### 【0090】

- 100 プロセッサ

- 110 第3記憶部

- 120 レジスタ

- 140 キャッシュメモリ

- 201 タイマー管理部

- 210 第1記憶部

- 220 動作モード記憶部

- 230 状態検出部

- 240 算出部

- 250 決定部

- 260 維持部

- 270 一時停止部

- 280 復帰部

- 310 第4記憶部

- 311 割り込み待ち通知部

- 313 登録削除部

- 320 第5記憶部

- 325 算出部

40

50

|       |           |    |

|-------|-----------|----|

| 3 6 5 | 一時停止部     |    |

| 3 7 0 | 復帰部       |    |

| 3 8 0 | 割り込み処理部   |    |

| 3 9 0 | 割り込み待ち解除部 |    |

| 4 1 5 | 登録削除部     |    |

| 4 1 7 | 更新部       |    |

| 5 0 0 | バス        |    |

| 5 6 5 | 一時停止部     |    |

| 5 7 0 | 復帰部       |    |

| 5 8 0 | 変更部       | 10 |

| 6 6 5 | 一時停止部     |    |

| 6 7 0 | 復帰部       |    |

| 6 8 0 | 変更部       |    |

| 7 0 0 | 再開制御部     |    |

| 7 1 0 | 第2記憶部     |    |

| 7 2 0 | 再開時間設定部   |    |

| 7 3 0 | 再開部       |    |

| 8 0 0 | 割り込み管理部   |    |

| 8 1 0 | 割り込み管理設定部 |    |

| 8 2 0 | 割り込み検出部   | 20 |

| 8 3 0 | 再開部       |    |

| 9 0 0 | 記憶領域      |    |

【図1】

【図3】

| 待ち時間 | 動作モード |

|------|-------|

| 0~t1 | 第2モード |

| t1~  | 第1モード |

【図2】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

| 割り込み種別   | 発生時間 |

|----------|------|

| デバイス読み出し | T_a  |

| キーボード入力  | T_b  |

【図10】

| 割り込み種別   | 割り込み待ち時間 |

|----------|----------|

| デバイス読み出し | T3       |

| キーボード入力  | T4       |

| マウス入力    | T5       |

【図12】

【図11】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

| 待ち時間  | 動作モード |

|-------|-------|

| 0~t2  | 第2モード |

| t2~t3 | 第3モード |

| t3~   | 第1モード |

【図23】

【図24】

---

フロントページの続き

(72)発明者 白井 智

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 尊家 昌也

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 柴田 章博

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 木村 哲郎

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 金井 達徳

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 外山 春彦

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 猪瀬 隆広

(56)参考文献 特開2010-113641(JP, A)

特許第4644747(JP, B2)

特開2003-029886(JP, A)

特開平03-171217(JP, A)

特開2008-243220(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 26 - 1 / 32 ,

G 06 F 9 / 46 , 9 / 48 , 9 / 50 - 9 / 52 , 9 / 54