(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4839349号

(P4839349)

(45) 発行日 平成23年12月21日(2011.12.21)

(24) 登録日 平成23年10月7日(2011.10.7)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G09G 3/20 (2006.01)

G09G 3/20 612P

G02F 1/133 (2006.01)

G09G 3/20 612K

G09G 3/20 631B

G09G 3/20 633Z

請求項の数 7 (全 23 頁) 最終頁に続く

(21) 出願番号

特願2008-177589 (P2008-177589)

(22) 出願日

平成20年7月8日(2008.7.8)

(62) 分割の表示

特願2006-206029 (P2006-206029)

の分割

原出願日

平成14年12月26日(2002.12.26)

(65) 公開番号

特開2009-3457 (P2009-3457A)

(43) 公開日

平成21年1月8日(2009.1.8)

審査請求日

平成20年7月8日(2008.7.8)

(31) 優先権主張番号

特願2001-397307 (P2001-397307)

(32) 優先日

平成13年12月27日(2001.12.27)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100093506

弁理士 小野寺 洋二

(72) 発明者 坂巻 五郎

東京都小平市上水本町五丁目20番1号

株式会社日立製作所

半導体グループ内

(72) 発明者 大山 尚

千葉県茂原市早野3681番地

日立デバイスエンジニアリング株式会社内

最終頁に続く

(54) 【発明の名称】表示システム

(57) 【特許請求の範囲】

【請求項 1】

表示パネルと、

上記表示パネルに結合され、半導体チップに形成された表示駆動制御装置とを含む表示システムであって、

上記表示駆動制御装置は、

上記表示システムの外部から供給されるべき動画データと、

上記表示システムの外部から供給されるべき垂直同期信号と、

上記表示システムの外部から供給されるべき水平同期信号と、

上記表示システムの外部から供給されるべきドットクロックとを受けるようにされた動画インターフェースと、 10

内部動作クロック信号が発生されるクロック発生回路と、

上記表示システムの外部から供給されるべき静止画データを受けるようにされたシステムインターフェースと、

上記表示パネルに表示される画像データを格納するメモリと、

上記メモリに結合され、上記メモリから読み出された画像データにしたがって、上記表示パネルへ駆動信号を供給する駆動回路と、

上記メモリから上記画像データを読み出す際、上記内部動作クロック信号に従い読み出しを可能とする第1状態と、上記垂直同期信号、上記水平同期信号及び上記ドットクロックに従い読み出しを可能とする第2状態とのいずれか一方を、上記表示システムの外部 20

から設定可能な第1レジスタと、

上記画像データを上記メモリへ書き込む際、上記システムインターフェースへ供給された上記静止画データを上記メモリへ書き込みを可能とする第1状態と、上記動画インターフェースへ供給された上記動画データを上記メモリへ書き込みを可能とする第2状態とのいずれか一方を、上記表示システムの外部から設定可能な第2レジスタと、を有し、

上記第1レジスタが上記第1状態とされ、かつ、上記第2レジスタが上記第1状態とされた場合、上記静止画データが上記メモリに書き込まれると共に表示され、

上記第1レジスタが上記第2状態とされ、かつ、上記第2レジスタが上記第2状態とされた場合、上記動画データが上記メモリに書き込まれると共に表示され、

上記第1レジスタが上記第2状態とされ、かつ、上記第2レジスタが上記第1状態とされた場合、動画表示中に上記メモリ内の静止画エリアが上記静止画データによって書き換えられる表示システム。 10

#### 【請求項2】

請求項1において、

上記表示駆動制御装置は、上記動画インターフェースに結合され、上記表示システムの外部からイネーブル信号を受けるようにされ、

上記イネーブル信号は、活性状態と非活性状態とを有し、

上記データ端子を介して上記動画インターフェースへ供給された上記動画データは、上記イネーブル信号の上記活性状態に従って上記メモリへ書き込まれる表示システム。 20

#### 【請求項3】

請求項1又は2において、

上記表示駆動制御装置は、さらに、上記メモリにおいて、上記動画インターフェースへ供給された上記動画データが書き込まれる領域の先頭アドレスと最終アドレスとを、上記表示システムの外部から指定可能な第3レジスタを有する表示システム。 20

#### 【請求項4】

請求項2又は3において、

上記第1レジスタ、上記第2レジスタ及び上記第3レジスタは、上記システムインターフェースから設定される表示システム。

#### 【請求項5】

請求項2又は3又は4において、

上記表示駆動制御装置の上記システムインターフェースには、さらに、チップセレクト信号、レジスタセレクト信号及びライト信号が供給される表示システム。 30

#### 【請求項6】

請求項5において、

上記第1レジスタは、2ビットで構成され、

上記第1レジスタの上記第1状態は、00とされ、

上記第1レジスタの上記第2状態は、01とされ、

上記第2レジスタの上記第1状態は、0とされ、

上記第2レジスタの上記第2状態は、1とされる表示システム。 40

#### 【請求項7】

請求項1において、

上記表示システムは、携帯電話機の表示システムとされる表示システム。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、表示装置の画像表示モードを制御するための表示駆動制御技術に係り、特に液晶表示装置や有機EL表示装置、他のドットマトリクス型表示装置に静止画や動画

を表示する表示装置の画像表示モードを制御する表示システムに関する。

### 【背景技術】

#### 【0002】

通常、ドットマトリクス型表示装置は、二次元にマトリクス配列された多数の画素を有する表示パネルと、この表示パネルに画像信号を供給して静止画や動画を表示させるための表示制御回路から構成される。この種の表示装置としては、液晶表示装置、有機EL表示装置、プラズマ表示装置、あるいは電界放出型表示装置等が知られている。ここでは、表示装置の典型である液晶表示装置と、この液晶表示装置を表示部に用いた携帯電話機を例として、その画像表示システムの概要を説明する。

10

#### 【0003】

近年、携帯電話機の表示画面に動画像（以下、単に動画とも言う）を表示する要求が高まっている。しかし、従来の携帯電話機は主としてテキストを含めた静止画像（以下、単に静止画とも言う）表示を行うことを目的としているため、その駆動制御回路には静止画・テキスト・システム・I/O・インターフェース回路のみを具備し、動画対応のインターフェース回路は内蔵されていない。そのため、従来の駆動制御回路では動画の表示は可能であるが、スムーズに観察される高画質での動画の表示を行うことは難しい。なお、以下では、インターフェース回路を単にインターフェースと称する。

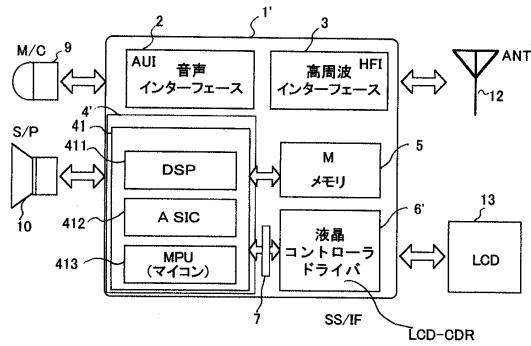

#### 【0004】

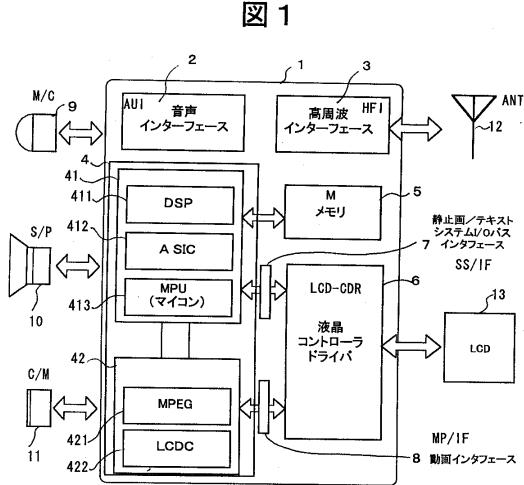

図21は本発明前に発明者によって検討された表示駆動制御回路および表示装置の一例である動画対応のインターフェースを持たない携帯電話機の駆動回路システム構成の一例を説明するブロック図である。この駆動制御回路システム1'は音声インターフェース(AUI)2、高周波インターフェース(HFI)3、画像プロセッサ4'、メモリ5および表示駆動制御回路である液晶コントローラ・ドライバ(LCD-CDR)6'、静止画・テキスト・システム・I/Oバス・インターフェース(SS/IF)7等で構成される。なお、参照符号9はマイクロフォン(M/C)、10はスピーカ(S/P)、12はアンテナ(ANT)、13は液晶パネル(液晶ディスプレイ：LCD)である。

20

#### 【0005】

画像プロセッサ4'はデジタル・シグナル・プロセッサ(DSP)411とASIC412およびマイコンMPUを有するベースバンド・プロセッサ41で構成される。音声インターフェース(AUI)2はマイクロフォン9からの音声入力の取込みとスピーカ10への音声の出力を制御する。

30

#### 【0006】

液晶パネル13への表示は、メモリ5から画像データを読みだし、マイコンMPU413で必要な処理を行って静止画・テキスト・システム・I/Oバス・インターフェースSS/IF7を使用して液晶コントローラ・ドライバ(LCD-CDR)6'内の表示RAMへ書き込まれる。動画表示モードでは、1秒間に10~15画面(フレーム)が書換えられる。このシステムでは、80系インターフェースに代表されるシステム・I/Oバスが使用される。以下、静止画・テキスト・システム・I/Oバス・インターフェース(SS/IF)7をシステム・インターフェース7と略記することもある。

40

#### 【0007】

液晶コントローラ・ドライバ(LCD-CDR)6'での表示動作は、当該ドライバ内の内蔵クロックで動作する。このため、画像データの書き込みと表示動作は全く非同期に行われる。

### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0008】

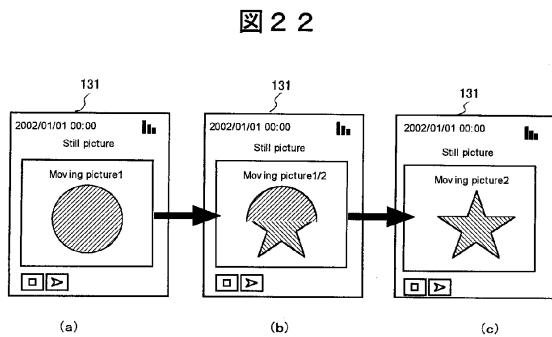

図22は図21に示したシステムでの動画像表示時の画面更新の動作例を模式的に示す説明図である。図22は携帯電話機の表示画面を示し、静止画像(Still picture)表示領域の中に動画像(Motion picture)表示を行う様子を示す

50

。この図面表示は以降の図面でも同様である。液晶コントローラ・ドライバ（LCD-C DR）6'内の表示RAMへの画像データの書き込みは、表示動作とは全く無関係に行われる。上記したように、画像データの書き込みと液晶パネルLCDでの表示のための当該画像データの読み出しが無関係（非同期）に行われるため、図22の（a）に示した動画1（Moving picture 1）から同（c）の動画2（Moving picture 2）への画面更新は、図22の（b）に示したように当該画面の途中から行われる場合がある。

#### 【0009】

画面の途中から動画の更新が行われた場合、動画1（Moving picture 1）と動画2（Moving picture 2）が同一表示内に併存して更新が行われる。このため、図22の（b）のように表示中の動画1と動画2の境界が目立ち、それが画面のチラツキとなって視認される場合があり、表示品質の観点からは好ましいものではない。このように、静止画・テキスト・システム・I/Oバス・インターフェースSS/IFのみでは動画の表示を高品質で行なうことが困難である。動画の表示のためには、表示動作に同期して画像データの書き込みを行う必要がある。

10

#### 【0010】

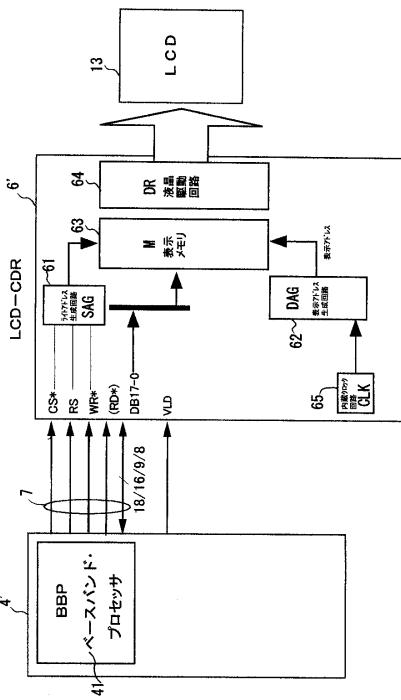

図23は図21に示されるシステムでの液晶コントローラ・ドライバとその周辺回路の構成例を説明するブロック図である。液晶コントローラ・ドライバ（LCD-CDR）6'は、書き込みアドレス生成回路61、表示アドレス生成回路62、RAMで構成したビットマップ画像メモリである表示メモリ（M）63、液晶駆動回路（DR）64、内蔵クロック発生回路（CLK）65を有する。画像プロセッサ4'のベースバンド・プロセッサ41からの表示データ（DB17-0）はシステム・インターフェース（SS/IF）7から内蔵の表示メモリMに書き込まれる。

20

#### 【0011】

このときの書き込みアドレスは、書き込みアドレス生成回路（SAG）61でシステム・インターフェース信号CS（チップセレクト）、RS（レジスタセレクト）WR（ライト）の各信号により生成される。表示動作での表示データの読み出しへは、表示アドレス生成回路（DAG）で生成される表示アドレスに従い表示メモリ（M）63より読み出される。表示アドレス生成は内蔵クロック発生回路（CLK）65で生成されるクロックに同期して行われる。この内蔵クロックによる動作とシステム・インターフェース（SS/IF）7による動作は、全く無関係（非同期）に行われる。

30

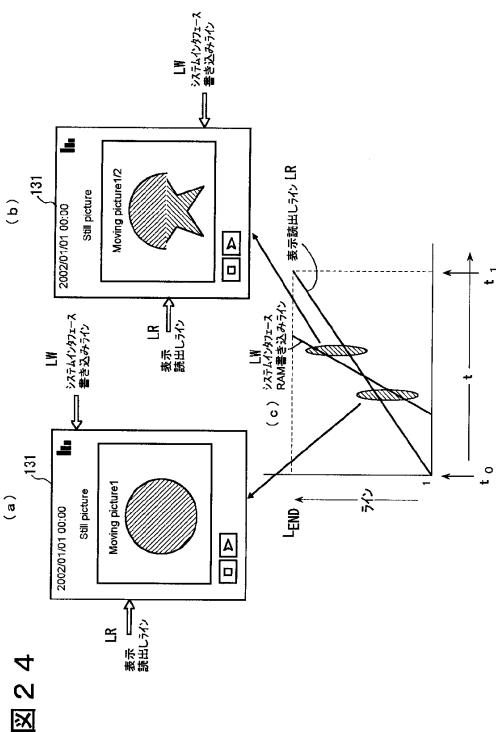

#### 【0012】

図24は図23に示したシステムの液晶コントローラ・ドライバを用いた携帯電話機の画面における動画像の画面更新の様子を説明する模式図である。表示動作による表示読み出しライン（走査線：画素選択ライン）LRは、内蔵クロックに従って一定速度で順次先頭から読み出される。システム・インターフェース（SS/IF）7からの表示データのメモリMへの書き込みは、表示動作に無関係に行われる。このため、システム・インターフェース（SS/IF）7による書き込みラインLWが、表示動作による表示読み出しラインLRを追い越す場合が起こる。すなわち、表示書き込みラインLWと表示読み出しラインLRとが交差する場合がある。

40

#### 【0013】

書き込みラインと読み出しラインとが図24の（c）に示したように交差すると、同図（a）の動画表示状態から同図（b）の動画表示状態に表示が変化するときに、この交差するラインで表示にチラツキが発生する。1秒間に60フレームの画面表示において、毎秒15コマの動画表示を行うと、4フレームに1回の画面更新が必要である。この場合、1秒間に4回の画面更新が起こり、毎秒4回のチラツキが発生することになる。この画面チラツキはこの種の表示装置における解決すべき課題の一つとなっていた。

#### 【0014】

また、上記のような画面チラツキを回避するための構成を液晶コントローラ・ドライバに付加すると、表示装置の消費電力が増加し、特に携帯電話機のような携帯端末では好ま

50

しいものではない。本発明の目的は、動画表示時に画面チラツキがなく、かつ高画質の動画表示機能を付加したことによる電力消費を抑制して低消費電力化した表示システムとの表示システムを用いた携帯電話装置を提供することにある。

【課題を解決するための手段】

【0015】

上記目的を達成するために、本発明は、第2機能とされる静止画モードにおけるシステム・インターフェースに加えて第1機能とされる動画対応のインターフェースを用い、さらに必要な期間のみ動画対応のインターフェースを動作させるように静止画インターフェース（システム・インターフェース）との切り換えを行うことによって低消費電力化した点に特徴を有する。本発明による表示駆動制御装置の構成例の概要を記述すれば、下記のとおりである。10

【0016】

(1)、静止画・テキスト・システム・I/Oバス・インターフェースと、画像データ処理装置からの動画像データを入力する外部表示インターフェースと、少なくとも1フレーム分の画像データ格納領域をもつ画像表示メモリと、表示装置に表示データを供給する表示駆動回路とを備えた。

【0017】

(2)、(1)において、前記静止画・テキスト・システム・I/Oバス・インターフェースと外部表示インターフェースの表示データを前記画像表示メモリの書き込みと読み出しに選択接続する表示動作切り換えレジスタとメモリアクセス切り換えレジスタとを備えた。20

【0018】

(3)、(1)において、動画像の垂直同期信号入力端子を備え、前記画像表示メモリへの動画表示データの書き込みと読み出しのタイミングを前記垂直同期信号入力端子から入力する垂直同期信号により制御する。

【0019】

(4)、(1)乃至(3)において、前記表示装置の画面に前記動画像を表示する領域を指定するイネーブル信号入力端子を備えた。

【0020】

(5)、(1)乃至(3)において、前記表示装置の画面の前記静止画像を表示する領域内の静止画像の一部を更新する領域を指定するイネーブル信号入力端子を備えた。30

【0021】

(6)、動画データが転送される第1ポートと静止画データが転送され第2ポートとを備えた。

【0022】

(7)、表示パネルに供給されるべき画像データを格納するメモリと、前記メモリに格納される前記画像データとしての動画データが転送される第1ポートと、前記メモリに格納される前記画像データとしての静止画データが転送される第2ポートとを備えた。40

【0023】

(8)、表示パネルの画面に供給されるべき画像データを格納するメモリと、前記メモリに格納される前記画像データとして動画データが転送される第1ポートと、前記画面の先頭を示す信号が供給される外部信号端子とを備え、

前記外部端子に供給された前記信号に同期して、前記動画データの転送を開始するようにした。

【0024】

(9)、(8)において、前記メモリに格納される前記画像データとして静止画データが転送される第2ポートをさらに備えた。

【0025】

(10)、表示パネルの画面に供給されるべき画像データを格納するメモリと、前記メモリに格納される前記画像データとして動画データが転送される第1ポートと、前記画面の先頭を示す信号が供給される外部信号端子とを備え、50

りに格納される前記画像データとして動画データが転送されるポートと、前記動画データを前記メモリの所望の領域へ書き込むことを指示する信号を受ける外部端子とを備えた。

#### 【0026】

(11)、表示パネルに供給されるべき画像データを格納するメモリと、前記メモリに格納される上記画像データとして動画データが転送される第1ポートと、前記メモリに格納される前記画像データとして静止画データが転送され第2ポートと、前記メモリへの前記画像データの書き込みに、前記第1ポートに供給された前記動画データと前記第2ポートに供給された静止画データとの一方を指定するための第1制御レジスタを備えた。

#### 【0027】

(12)、内部動作クロックを発生するクロック生成回路と、表示パネルに供給されるべき画像データを格納するメモリと、前記メモリに格納される前記画像データとして動画データが同期信号に同期して転送される第1ポートと、前記メモリに格納される前記画像データとして静止画データが転送される第2ポートと、前記メモリからの前記画像データの読み出し動作を制御する第1制御レジスタとを有し、10

前記第2ポートに供給された前記静止画データを、前記内部動作クロックに同期して前記メモリに書き込み可能とし、

前記第1制御レジスタが、前記メモリからの前記画像データの読み出しに、前記同期信号に同期した読み出し動作と前記内部クロック信号に同期した読み出し動作の一方を指定するようにした。20

#### 【0028】

上記構成とした本発明の表示駆動制御装置によれば、高品質の動画像を表示することができると共に、動画インターフェースと静止画インターフェースを表示内容（動画モード／静止画モード）に応じて切り換えることにより、低消費電力化を実現できる。

#### 【発明の効果】

#### 【0029】

本発明によれば、動画表示時の更新画面をフレームに同期させて行うため、更新途中の表示のチラツキがなく、また動画表示時の表示データの転送データ数を低減できるため、本発明の表示駆動制御装置を用いたシステム全体での消費電力の低減が可能である。

#### 【0030】

また、静止画・テキスト・システム・I/Oバス・インターフェースと、画像データ処理装置からの動画像データを入力する外部表示インターフェースの切り換えと画像表示メモリのアクセスを独立して制御するように構成したことにより、表示内容に合わせた表示モードを選択できる。30

#### 【0031】

さらに、動画表示モードと静止画表示モードで対応するインターフェースを切り換えることで、それぞれのインターフェースの機能を有効に活用できることでもシステム全体での消費電力の低減が可能である。

#### 【発明を実施するための最良の形態】

#### 【0032】

以下、本発明の実施の形態について、実施例の図面を参照して詳細に説明する。40

#### 【実施例1】

#### 【0033】

図1は本発明の一実施例の全体構成の説明図であり、本発明による表示駆動制御装置の一例である第1機能とされる動画対応のインターフェース（すなわち、動画データが転送される第1ポートを含む）を有する携帯電話機の駆動回路システム構成の一実施例を説明するブロック図である。この駆動制御装置1は図20に示したものと同様の音声インターフェース(AUI)2、高周波インターフェース(HFI)3、画像データ処理装置である画像プロセッサ4、画像表示メモリであるメモリ5および表示駆動制御回路である液晶コントローラ・ドライバ(LCD-CDR)6、第2機能とされる静止画・テキスト・システム・I/Oバス・インターフェース(SSIF)7（すなわち、静止画データが転50

送される第2ポートを含む)等で構成される。

#### 【0034】

メモリ5は少なくとも画像1フレーム分の表示データを格納するフレームメモリ(ビットマップメモリ)であり、以下ではグラフィックRAMとも称する。また、実施例の説明でも、静止画・テキスト・システム・I/Oバス・インターフェース(SS/IF)7をシステム・インターフェース7、あるいは動画インターフェースとして説明する場合もある。

#### 【0035】

そして、画像プロセッサ4には、デジタル・シグナル・プロセッサ(DSP)411とASIC412およびマイコンMPUを有するベースバンド・プロセッサ41に加えて、動画対応プロセッサ(MPEG)421と液晶表示コントローラ(LCDC)422を有するアプリケーション・プロセッサ(APP)42を備えている。なお、参照符号9はマイクロフォン(M/C9、10はスピーカ(S/P)、11はビデオカメラ(C/M)、12はアンテナ(ANT)、13は液晶パネル(液晶ディスプレイ:LCD)である。ASIC412はその他の携帯電話システム構成上必要な周辺回路機能を有する。また、画像プロセッサ4は、単結晶シリコンの様な1つの半導体基板(チップ)に形成されても良いし、ベースハンドプロセッサ41及びアプリケーション・プロセッサ42のそれぞれが1つの半導体基板(チップ)に形成されても良い。

10

#### 【0036】

前記した図21に示された携帯電話機システムにおいて一般的に具備されるベースバンド・プロセッサBBPでは動画処理能力が不足する。このベースバンド・プロセッサBBPの他にアプリケーション・プロセッサ(APP)と称するサブMPUが知られている。図1におけるアプリケーション・プロセッサ(APP)42には、MPEG動画処理などを行うためにMPEGプロセッサ(MPRG)421が内蔵される。また、アプリケーション・プロセッサ(APP)42は動画インターフェース(MP/IF)8で液晶コントローラ・ドライバ(LCD-CDR)6に画像データを転送する。静止画表示データやテキスト表示データは、図21に示されたシステムと同様にシステム・インターフェース(SS/IF)7を介して液晶コントローラ・ドライバ(LCD-CDR)6に転送される。

20

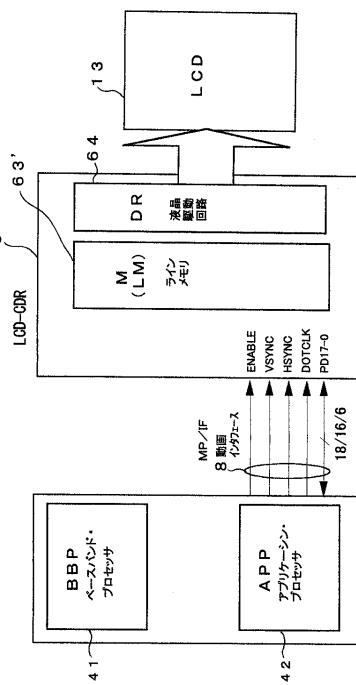

#### 【0037】

30

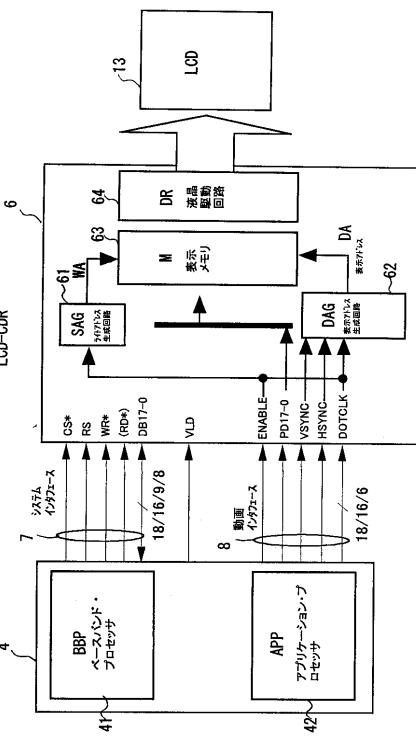

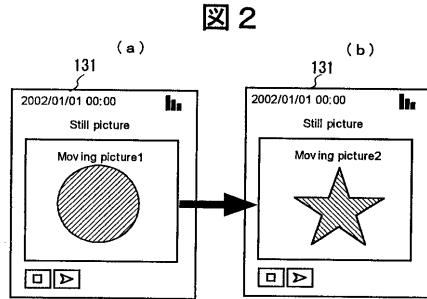

図2は本発明の表示駆動制御装置の一実施例を用いた携帯電話機の表示画面における動画像の画面更新の様子を説明する模式図である。動画インターフェースMP/IF8では、表示動作に必要な同期信号(垂直同期信号VSYNC、水平同期信号HSYNC、ドットクロックDOTCLK)により表示動作を行い、表示動作に同期して後述する表示データ信号(例えば、18ビット:PD17-PD0、以下PD17-0のように表記する)、データイネーブル信号(ENABLE)により表示データを液晶コントローラ・ドライバ(LCD-CDR)6の表示メモリ(内蔵RAM:M)63に書き込む。これにより、図2の(a)の画面表示から同(b)の画面表示への画面の更新は当該画面の先頭から行われ、画面の途中からの切り替えは起こらない。

#### 【0038】

40

図3は本発明による液晶コントローラ・ドライバの回路構成とその関連回路を動画インターフェースを用いた動画表示動作について説明するブロック図である。図中、図1と同一参照符号は同一機能部分に対応する。液晶コントローラ・ドライバ(LCD-CDR)6は、例えば、単結晶シリコンの様な1つの半導体基板(チップ)に公知のCMOS製造プロセスによって形成されており、ライトアドレス生成回路(SAG)61、表示アドレス生成回路(DAG)62、表示メモリ(M)63、および液晶駆動回路(DR)64を有している。表示データの書き込みは、データバス(PD17-0)から行われる。この時の書き込みアドレスWAは動画インターフェース信号(VSYNC, HSYNC, DOTCLK, ENABLE)の内のドットクロックDOTCLK及びイネーブル信号ENABLEに基づいてライトアドレス生成回路(SAG)61で生成される。

50

## 【0039】

すなわち、ライトアドレス生成回路（SAG）61は、イネーブル信号ENABLEのアクティブルレベルにしたがって上記ドットクロックDOTCLKをカウントするカウンタを有し、上記カウンタの出力が書き込みアドレスWAとされる。尚、上記イネーブル信号ENABLEは、動画表示エリアの先頭でアクティブルレベルとされ、動画表示エリアの最後で非アクティブルレベルとされる。上記ライトアドレス生成回路61のカウンタは上記イネーブル信号ENABLEのアクティブルレベルでその値がリセットされ、ドットクロックDOTCLKのカウント動作を開始する。

## 【0040】

動画表示エリアが図2に示されるように、表示パネルの中央部分に表示される場合、表示メモリの動画エリアに対応する部分の先頭アドレスと最後アドレスとを格納するレジスタが液晶コントローラ・ドライバ6に設けられる。この場合、ライトアドレス発生回路61内のカウンタの出力は、上記先頭アドレスを加算されてライトアドレスとされることになる。

10

## 【0041】

表示データは、動画インターフェース信号に基づいて表示アドレス生成回路（DAG）62から生成される表示アドレスDAに従って内蔵のメモリ（M）63から読み出されて液晶駆動回路（DR）64に与えられる。表示アドレス生成回路62は、VSYNC及びHSYNCのアクティブルレベルで初期化されるとともに、ドットクロックを計数するカウンタを有し、上記カウンタの出力が表示アドレスDAとされる。すなわち、表示データの書き込みアドレスWAと読み出しアドレスDAは、共に動画インターフェース信号を基準として生成される。

20

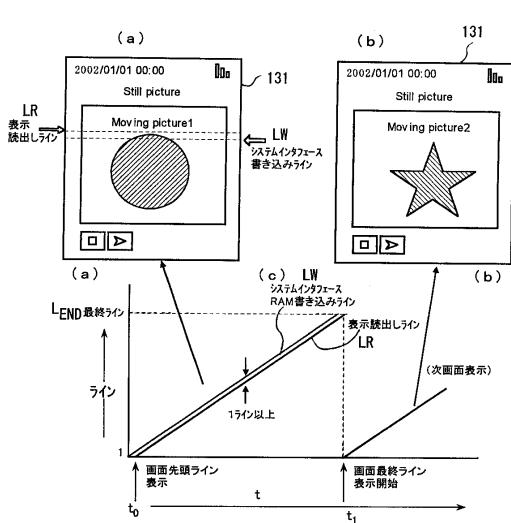

## 【0042】

図4は本発明の表示駆動制御システムの一実施例を用いた携帯電話機の表示画面における動画像の画面更新の様子を動画インターフェースでの表示動作として説明する模式図である。システム・インターフェース（SS/IF）7からの表示データの書き込みは、図3における動画インターフェース（MP/IF）8からのドットクロックDOTCLK及びイネーブル信号ENABLEに従って表示メモリ（M）63に書き込まれる。

## 【0043】

表示データは、動画インターフェース信号（VSYNC, HSYNC, DOTCLK）に従って読み出される。画像データの書き込みと表示読み出しは同一の信号を基準として動作するため、同一の一定速度で行われる。図4の（a）におけるLRは表示データの読み出しライン、LWは表示データの書き込みラインを示す。また、図4の（c）におけるENDは最終ラインを示す。

30

## 【0044】

そして、時間t0は画面先頭ライン表示時点、時間t1は画面最終ライン表示開始時点を示す。これにより、表示データの書き込みと表示読み出しは、1画面表示中に互いに追い越すことはないため、前記図23で説明したような動画1と動画2の境界がなく、画面のチラツキが発生することがない。書き込みアドレスと表示読み出しアドレスは、1ライン以上の間隔が常に保たれていればよい。

40

## 【0045】

尚、図4において、同じ時間に表示されるメモリへの書き込み動作と読み出し動作が発生している様に見えるものの、実際は1動作サイクルにおいて前半に書き込み動作が行われ、後半に読み出し動作が行われていると理解されたい。ただし、表示メモリ63がライトポートとリードポートとを有する2ポートメモリの場合、書き込み動作と読み出し動作とを同時に行うこととは可能である。

## 【0046】

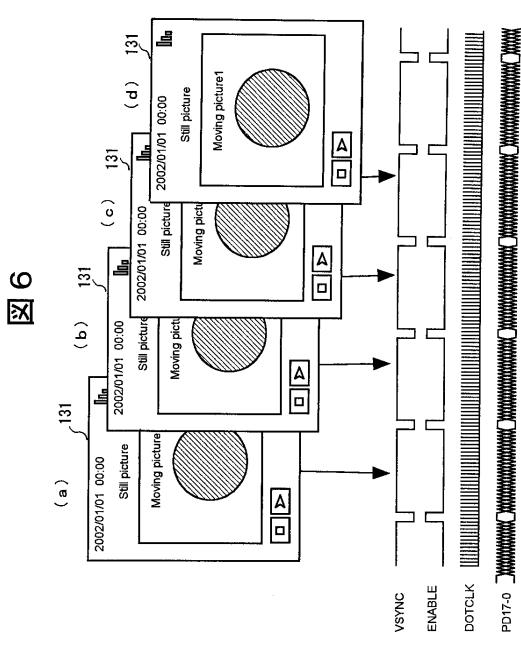

次に、静止画表示モードについて説明する。図5は本発明の実施例の効果を比較して説明するための動画インターフェースと内蔵メモリを有しない液晶コントローラ・ドライバの構成とその動作の説明図である。また、図6は図5の液晶コントローラ・ドライバによ

50

る静止画表示の様子を説明する模式図である。この液晶コントローラ・ドライバ（LCD-CDR）6はメモリMとしてラインメモリ（LM）63'を有している。

#### 【0047】

この構成では、ピットマップメモリのようなRAMメモリを持たないため、静止画表示モードでも、図6の（a）、（b）、・・・に示したように常時同一画面データを液晶コントローラ・ドライバ（LCD-CDR）6に転送し続けなければならない。そのため、データ転送による電力を要旨、消費電力の低減は難しい。また、動画表示には転送データが1画面ずつ異なるため、表示動作に同期して書き込める本発明の回路（図3参照）が有効である。

#### 【0048】

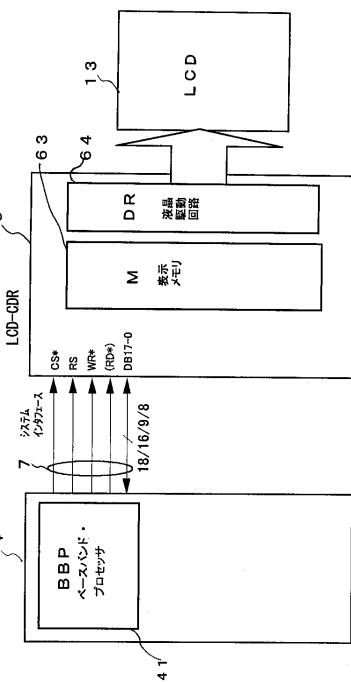

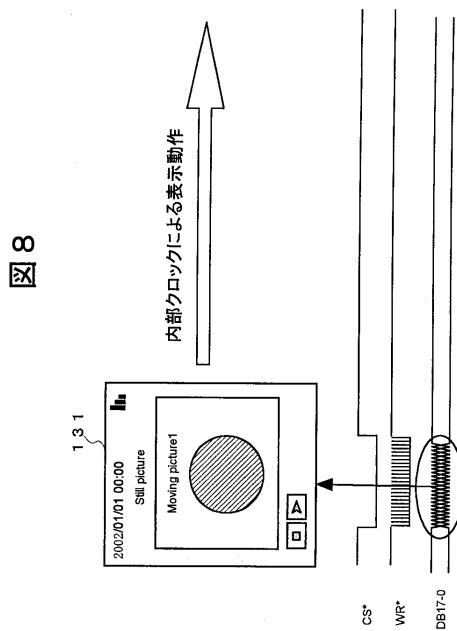

図7は本発明の実施例の効果を比較して説明するためのシステム・インターフェースと内蔵メモリによるデータ転送を行う液晶コントローラ・ドライバの構成とその動作の説明図である。また、図8は図7の液晶コントローラ・ドライバによる静止画表示の様子を説明する模式図である。図7に示した構成では、内蔵メモリ（M）63として図3と同様のRAMメモリであるピットマップメモリ（M）63を表示メモリとして内蔵している。

#### 【0049】

図8に示したように、この内蔵のメモリ（M）63に1画面分の画像データを書き込んだ後は、内蔵クロックにより当該メモリ（M）63のデータを読み出すために静止画データを再度転送する必要がない。このため、データ転送における消費電力を低減できる。この考え方に基づいて、本発明の実施例では、静止画の表示モードでは図7の構成部分を使用し、動画表示モードでは図5に示した構成を機能させるようにしたものである。この静止画表示モードと動画表示モードの切り換えには、後述するレジスタを設け、このレジスタの状態に従ってモード切り換えを行うようとする。

#### 【0050】

図9は本発明の構成を図7の構成および図5の構成と比較して示すメリットとデメリットの説明図である。図9の（1）、すなわちシステム・インターフェースのみと表示メモリ（RAM）を備えた構成では、表示メモリ（RAM）を内蔵したことにより、静止画表示モード、動画表示モードの何れの画像表示モードでも表示データの転送量を最小限にすることができる。しかし、前記図20～図23で説明したような表示画面のチラツキが発生する。

#### 【0051】

図9の（2）の構成、すなわち動画インターフェースとラインメモリを備えた構成では、チラツキの無い画面表示が可能であるが、静止画表示を含めて常時データの転送を必要とするために消費電力が増加し、低消費電力化は難しい。これらに対し、図9の（3）に示した内蔵メモリと動画インターフェースを設け、かつ静止画表示モードと動画表示モードとを切り換えるようにした本発明の実施例の構成によれば、表示画面にチラツキの無い動画更新が可能で、かつ最小限のデータ転送により低消費電力化を実現できる。

#### 【0052】

次に、本発明による動画インターフェースとシステム・インターフェースにおける動画表示と静止画表示の各表示モードの切り換えを実現するための具体的なシステム構成およびその動作を説明する。

#### 【0053】

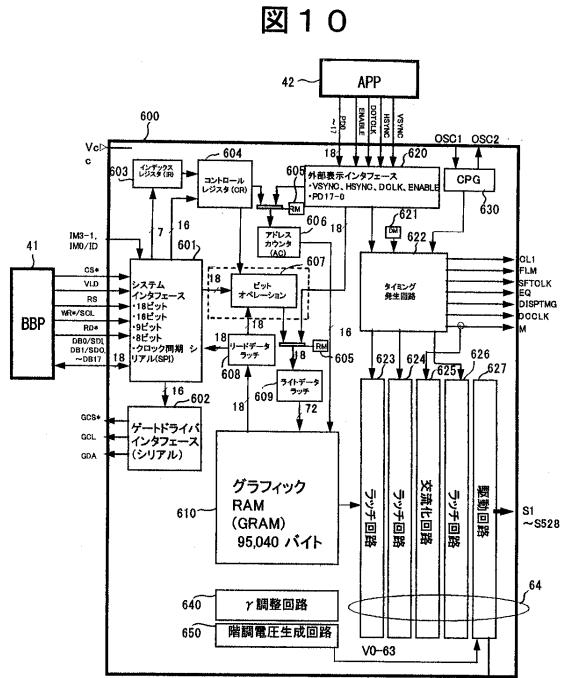

図10は本発明の表示駆動制御装置を構成する液晶コントローラ・ドライバを具体化したドライバチップの回路構成の説明図である。このドライバチップ600への静止画データ、テキストデータ等はベースバンド・プロセッサ41からシステム・インターフェース601に書き込まれ、内部のアドレスカウンタ（AC）606の示すアドレスのメモリすなわちグラフィックRAM（GRAM）610に表示データとして書き込まれる。この表示動作は次のとおりである。すなわち、内部クロック生成回路（CPG）630で生成したクロック信号に基づいてタイミング発生回路622は表示動作に必要なタイミング、表示アドレスを発生する。

## 【0054】

このタイミング、表示アドレスでグラフィックRAM(GRAM)610から表示データを読み出し、液晶表示に必要な電圧レベルに変換して液晶パネルに送出する。動画表示モードと静止画表示モードの切り換えは、表示動作切り換えレジスタ(DM)621、RAMアクセス切り換えレジスタ(RM)605により行う。

## 【0055】

動画表示モードでは、動画表示データ(PD17-0)、垂直同期信号VSYNC、水平同期信号HSYNC、ドットクロックDOTCLK、データタイネーブル信号ENABLEがアプリケーション・プロセッサ42から外部表示インターフェース620に入力する。表示動作切り換えレジスタ(DM)621によりタイミング発生回路622内でのタイミングを内蔵クロック基準から同期信号(VSYNC、HSYNC)に切り換え、必要なタイミング信号を生成する。尚、タイミング発生回路622は、図3で示される表示アドレス生成回路が含まれるが、図面の複雑さを避けるため記載されていない。10

## 【0056】

また、RAMアクセス切り換えレジスタ(RM)605によりライトアドレスカウンタ(AC)606の動作をドットクロックDOTCLK、データタイネーブル信号ENABLEより発生する信号に切り換える。そして、グラフィックRAM(GRAM)610へのデータバスを表示データ(PD17-0)へ切り換える。これにより、表示動作、RAMアクセス動作は、システム・インターフェース601と内部クロック生成回路(CPG)630から動画インターフェースである外部表示インターフェースモジュール620に切り換えられる。20

## 【0057】

なお、図10において、参照符号602はゲートドライバ・インターフェース(シリアル)、603はインデックスレジスタ(IR)、604はコントロールレジスタ(CR)、607はビット単位の演算処理を行うビットオペレーション回路、608は読み出し(リード)データラッチ回路、609は書き込み(ライト)データラッチ回路である。また、参照符号623、624、626はラッチ回路、625は交流化回路、627は駆動回路で、表示駆動回路(ここでは液晶駆動回路)64を構成する。そして、640はガンマ( )調整回路、650は階調電圧生成回路であり、液晶パネルへの表示データ処理回路を構成する。なお、ビットオペレーション回路607はビット単位の演算処理、及びビット単位の並び換え操作を行うものであるため、本機能を必要としない場合は省略できる。30

## 【0058】

次に、システム・インターフェースとアプリケーション・インターフェースの切り換えレジスタの詳細について説明する。表1は図10で説明したRAMアクセス切り換えレジスタ(RM)605のモード設定状態を示す。なお、表1では、このレジスタをRAMアクセスモードレジスタと表記している。

## 【0059】

## 【表1】

表140

| RM | RAMアクセスを行う<br>インターフェース     |

|----|----------------------------|

| 0  | システムインターフェース/VSYNCインターフェース |

| 1  | RGBインターフェース                |

## 【0060】

また、表2は同じく図10で説明した表示動作切り換えレジスタ(DM)605のモード設定状態を示す。なお、表2では、このレジスタを表示動作モードレジスタと表記している。50

ド設定状態を示す。なお、表2では、このレジスタを表示動作モードレジスタと表記している。

【0061】

【表2】

表2

| DM1 | DM0 | 表示動作を行うインターフェース |

|-----|-----|-----------------|

| 0   | 0   | 内部クロック動作        |

| 0   | 1   | RGBインターフェース     |

| 1   | 0   | VSYNCインターフェース   |

| 1   | 1   | 設定禁止            |

10

【0062】

そして、表3はRAMアクセス切り換えレジスタ(RM)と表示動作切り換えレジスタ(DM)の組み合わせ設定による各種の表示動作モードの状態の説明図である。

20

【表3】

表3

| 表示状態             | 動作モード          | RAMアクセス設定(RM)      | 表示動作モード(DM1-0)          |

|------------------|----------------|--------------------|-------------------------|

| 静止画表示            | 内部クロック動作のみ     | システムインターフェース(RM=0) | 内部クロック動作(DM1-0=00)      |

| 動画表示             | RGBインターフェース(1) | RGBインターフェース(RM=1)  | RGBインターフェース(DM1-0=01)   |

| 動画表示中の静止画エリア書き換え | RGBインターフェース(2) | システムインターフェース(RM=0) | RGBインターフェース(DM1-0=01)   |

| 動画表示             | VSYNCインターフェース  | システムインターフェース(RM=0) | VSYNCインターフェース(DM1-0=10) |

30

【0063】

表1に示したように、RAMアクセス切り換えレジスタ(RM)は内蔵した表示メモリ(グラフィックRAM)GRAMへのアクセスを行うインターフェースの切り換えを設定する。このRAMアクセス切り換えレジスタ(RMレジスタ)の設定を「RMの設定状態」で説明すると、「RM=0」のときはシステム・インターフェースのみからメモリGRAMへの表示データの書き込みが可能となる。また、「RM=1」のときはアプリケーション・インターフェース(動画インターフェース、表1のRGBインターフェース)のみからメモリGRAMへの書き込みが可能となる。

40

【0064】

表2に示した表示動作切り換えレジスタ(DMレジスタ)は2ビットの設定であり、表示動作モードを切り換える。このDMレジスタの設定を「DMの設定状態」で説明する。「DM=00」のときは内蔵クロックによる表示動作が行われる。また、「DM=01」のときは動画インターフェース(RGBインターフェース)により表示動作が行われる。

50

また、「 $DM = 10$ 」のときは $VSYNC$ インターフェースによる表示動作となり、 $RGB$ インターフェース時の $VSYNC$ 信号のみと内蔵ブロックにより表示動作が行われる。なお、「 $DM = 11$ 」の設定は禁止される。

#### 【0065】

このように、インターフェースの切り換えをRAMアクセス切り換えレジスタと表示動作切り換えレジスタとの2つのレジスタ（RAMレジスタ、DMレジスタ）を用いて独立に制御する。表3に纏めて表記したように、2つのレジスタの設定状態で表示動作を切り換えることで種々の表示モードで動作可能となる。なお、表3では、「DMの設定状態」を( $DM1 - 0 = 00$ )のように表記してある。

#### 【0066】

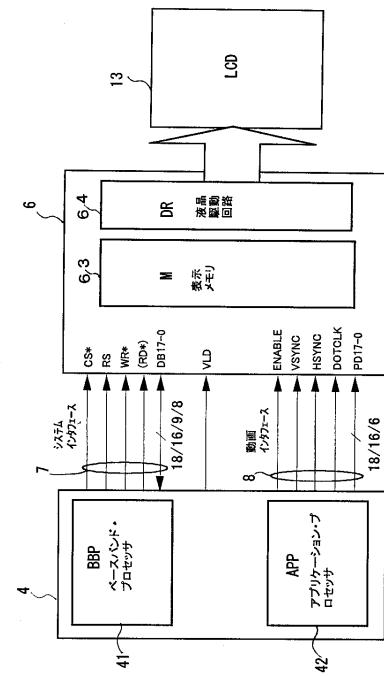

図11はシステム・インターフェースとアプリケーション・インターフェースを備えて内蔵メモリによるデータ転送を行う液晶コントローラ・ドライバの実施例の構成とその動作の説明図である。また、図12は図11の液晶コントローラ・ドライバによる静止画表示の様子を説明する模式図である。本実施例では、静止画データ等を入力するシステム・インターフェース（ベースバンド・インターフェース）41、動画インターフェースであるアプリケーション・インターフェース42は共に、そのデータは表示メモリである内蔵RAMメモリ（表示メモリM）63に格納される。

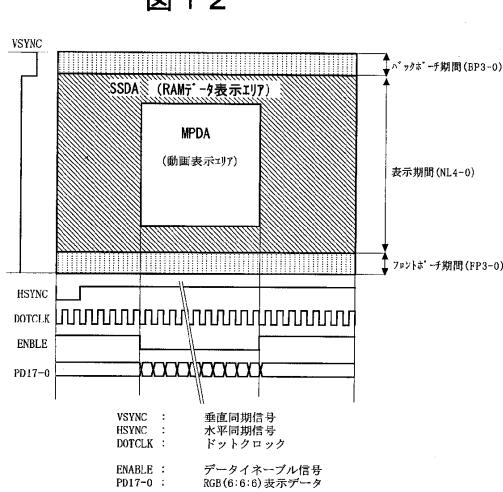

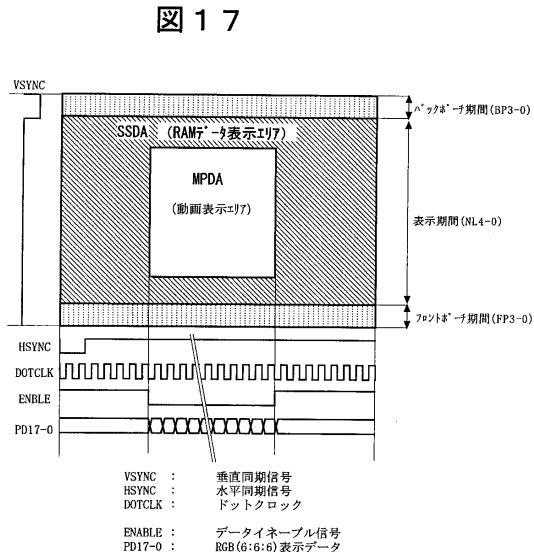

#### 【0067】

垂直同期信号 $VSYNC$ は表示動作の画面先頭を示すタイミング信号、水平同期信号 $Hsync$ は表示動作のライン周期を示すタイミング信号、ドットクロック $DOTCLK$ は画素単位のクロックで動画インターフェースすなわちアプリケーション・インターフェース（APP）42による表示動作の基準クロックとなる。また、このドットクロック $DOTCLK$ は表示メモリ（M）63の書き込み信号ともなる。アプリケーション・プロセッサ42はこのドットクロック $DOTCLK$ に同期して画像データを転送する。なお、イネーブル信号 $ENABLE$ は、各画素データが有効であることを示す信号である。このイネーブル信号 $ENABLE$ が有効のときのみ転送データが表示メモリ（M）63に書き込まれる。

#### 【0068】

すなわち、図12に示したように、画面のRAMデータ表示エリア（静止画表示領域）SSDA内のイネーブル信号 $ENABLE$ が有効とされた領域である動画表示領域MPDAに動画表示データPD17-0が表示される。なお、画面の上下にはバックポーチ期間（BPP3-0）とフロントポーチ期間（FP3-0）が設けてあり、その間に表示期間（NL4-0）が設けられている。

#### 【0069】

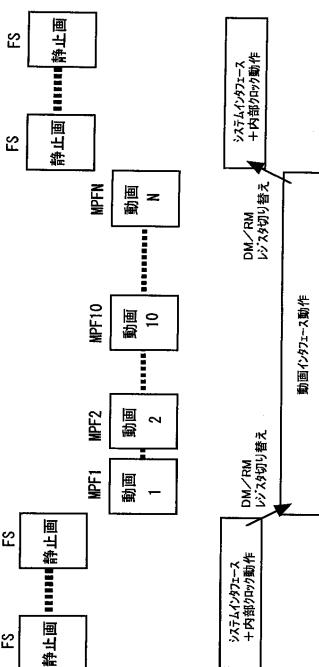

図13はシステム・インターフェースとアプリケーション・インターフェースの切り換え動作を表示画面の状態で示した説明図である。システム・インターフェースの動作で静止画FSが表示され、アプリケーション・インターフェースの動作で動画MP1, MP2, ..., MP10, ..., MPNが表示される様子を示している。携帯電話機では、動画表示を行う時間は表示を行う時間からすると少ないはずである。このため、大多数を占める静止画表示時は「システム・インターフェース+内部クロックによる表示」により低消費電力での動作となる。

#### 【0070】

そして、動画表示を行う際のみ、前記したように各レジスタ（RM、DM）を切り換えてアプリケーション・インターフェース（動画インターフェース）を有効にする。これにより、データの転送電力を使用するインターフェースの使用期間を最小限にし、システム全体での電力消費の低減化を図ることができる。なお、レジスタの設定を含め、本システムのインストラクション設定はシステム・インターフェースのみから可能としている。しかし、別経由でのインストラクション設定を行うようにしてもよい。

#### 【実施例2】

#### 【0071】

10

20

30

40

50

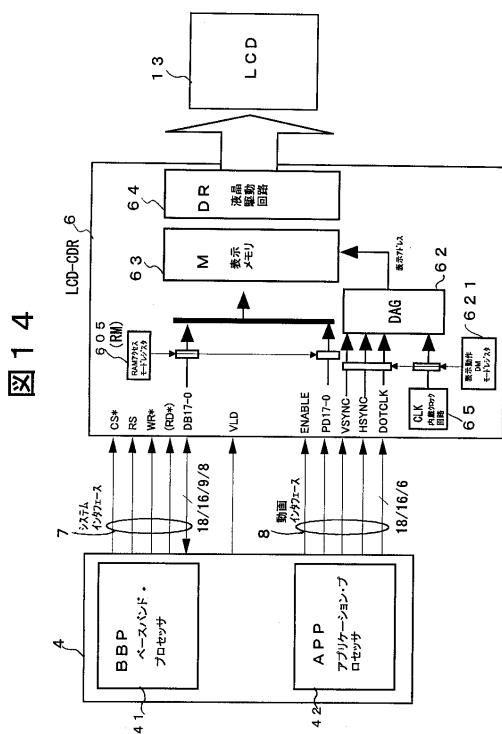

図14は本発明の実施例2の説明図であり、動画バッファリング動作を実行する回路構成を説明するためのブロック図である。前記図5と図6で説明した画像表示システムでは、動画表示時（アプリケーション・インターフェースの使用時）は表示データをラインメモリに逐次格納して表示が行われる。そのため、表示データを常時転送し続ける必要がある。本実施例では、動画インターフェース（アプリケーション・インターフェース（APP）42）の使用時も表示データを全てRAMメモリ（M）63に格納し、格納された表示データを、動画インターフェース（63）により入力する同期信号（VSYNC, HSYNC, DOTCLK）に従って読み出して液晶パネルに出力し、これを表示する。内蔵のRAMメモリ（M）63へのアクセス切り換えをアクセスモードレジスタ（RMレジスタ）605で行う。

10

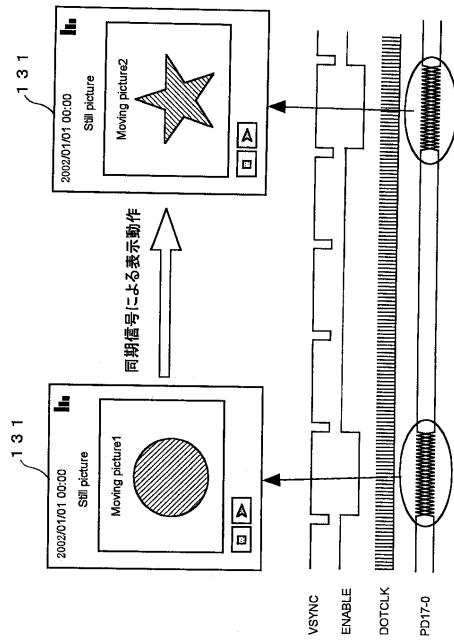

#### 【0072】

図15は図14の回路構成による動画バッファリング動作における動画データの転送の様子を説明する説明する模式図である。前記図5で説明したようなラインメモリのみを用いる動画表示では、動画データを常時転送しなければならない。現状の携帯電話機のシステムでは、動画表示時の1秒間のコマ（フレーム）数は10～15である。このため、1秒間の表示フレーム数を60フレームとすると画面更新は4フレームに一回行われることになる。すなわち、4フレーム期間は同じ画面を表示している。

#### 【0073】

現状の携帯電話機での動画を図5、図6で説明した構成で行うと、4フレームの同一画面表示期間にわたってデータ転送を行なわなければならないため、データ転送により消費電力が増加する。本実施例では、動画データを全て内蔵のRAMメモリに格納する動画バッファリングを行うようにしたため、画面の更新時のみデータ転送を行い、内蔵のメモリの表示データを更新することになる。その後の同一画面の表示期間は、システム側からのデータ転送を行わずにメモリに格納された表示データを読み出して表示する。これにより、動画データの転送回数が、上記例の動画15フレーム/秒、フレーム周波数60Hzにおいて、従来に比較して1/4に削減される。

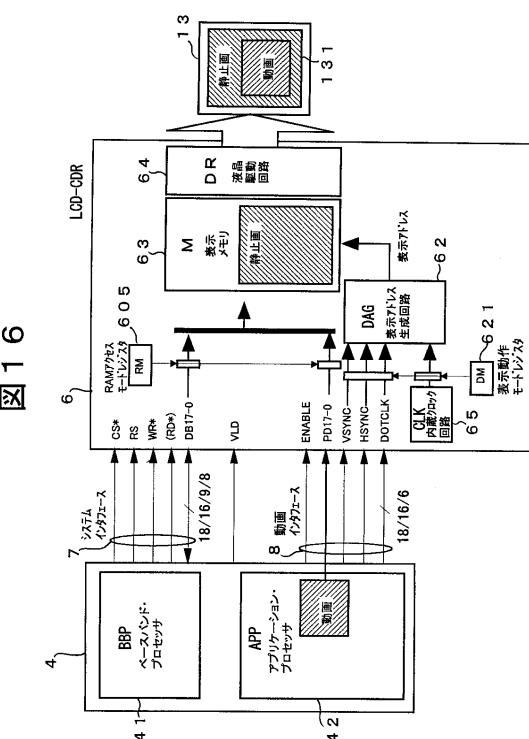

20

#### 【0074】

本発明は、上記説明したような画面のRAMデータ表示エリア（静止画表示領域）SSDAの内に動画表示領域MPDAをはめ込む際の動画データ表示領域の選択した領域のみに当該動画データを転送することもできる。図16は本発明による動画転送を実現する回路構成の一実施例を説明するブロック図である。また、図17は図16の液晶コントローラ・ドライバによる選択領域のみへの静止画表示の様子を説明する模式図である。

30

#### 【0075】

動画バッファリングを用いない場合、液晶パネルの一部分を使用して動画表示を行う際に動画表示領域MPDA以外の静止画表示領域SSDAも含めて動画インターフェースから表示データを常時転送する必要があった。このため、データ転送数が増し、消費電力が増加する。本実施例の選択領域転送方式では、動画インターフェースから転送する表示データは、動画表示領域MPDAの表示データのみを転送可能である。

#### 【0076】

選択領域転送方式では、事前に表示メモリへ静止画データを書き込んで置き、ENABLE信号にて指示された表示メモリの部分にのみ動画インターフェースから表示データを書き込む。これにより、表示メモリ上で静止画と動画が合成され、表示動作時に同時に読み出されて液晶パネル13に表示がなされる。このように、本実施例によれば、選択的に動画表示領域を指定することができ、動画領域分に相当する最小限のデータ転送で動画表示が可能となり、データ転送時の消費電力を低減することができる。なお、以上は携帯電話機の表示装置に限るものではなく、パソコンやディスプレイモニターなどの大サイズの表示装置についても同様に適用できる。

40

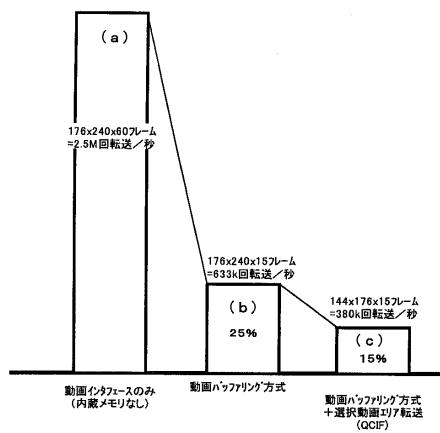

#### 【0077】

図18は本発明の効果を説明するための前記各データ転送方式の動画データ転送数の比較説明図である。なお、図18は、液晶パネルサイズが176×240ドット、動画サイ

50

ズがQ C I F サイズ ( $144 \times 176$  ドット)、動画コマ数が 15 フレーム / 秒 (fps)、フレーム周波数が 60 Hz の液晶表示装置で比較したものである。図 18 から分かるように、(a) 動画インターフェースのみの場合 (内蔵メモリ無し) では  $176 \times 240 \times 60$  フレーム = 2.5 M 回転送 / 秒、(b) 動画バッファリング方式では  $176 \times 240 \times 15$  フレーム = 633 k 回転送 / 秒、(c) 動画バッファリング方式 + 選択動画領域転送方式では  $144 \times 176 \times 15$  フレーム = 380 k 回転送 / 秒となる。

#### 【0078】

したがって、データ転送量は、(b) 動画バッファリング方式は (a) 動画インターフェースのみの場合に対して約 25 % の低減、(c) 動画バッファリング方式 + 選択動画領域転送方式は (a) 動画インターフェースのみの場合に対して約 15 % の低減が可能となる。10

#### 【実施例 3】

#### 【0079】

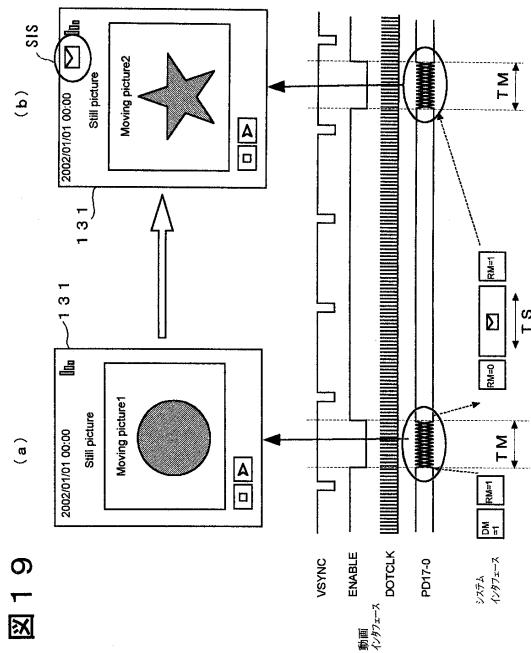

図 19 は本発明の実施例 3 の説明図であり、動画表示中の静止画領域の表示書き換え方式を説明する模式図である。図 10 で具体的に説明したように、本発明の液晶コントローラ・ドライバは静止画インターフェースと動画インターフェースの切り替えをレジスタで行い、また、図 14 以降で説明したような動画バッファリングが可能であることから、動画表示中の静止画領域の表示書き換えを行うこともできる。

#### 【0080】

図 19 に示したように、表示画面に動画を表示しているときにも、携帯電話機におけるようなアイコンマーク (時計、電波状況) 等を更新する必要がある。ここでは、画面の静止画表示領域にメール着信表示 SIS を表示させる場合を例として示す。動画バッファリング方式による表示データの書き換えは、画面更新時となる。この他の期間は表示動作のみを行う。前記したように、静止画表示モードと動画表示モードはレジスタ (表示動作切り換えレジスタ (DM)、RAM アクセス切り換えレジスタ (RM)) で行う。さらに、この切り換えは、表示動作とメモリへのアクセスのそれぞれを独立して切り換えが可能である。20

#### 【0081】

このため、本実施例では、図 19 の動作波形に示したように、動画表示の画面更新時以外の期間に、RAM アクセスのみ RAM アクセス切り換えレジスタ (RM) を「=0」としてシステム・インターフェースに切り替え、静止画表示領域の表示データを更新する。この静止画表示領域の更新期間 TS が終了した時点で当該 RAM アクセス切り換えレジスタ (RM) を「=1」とする。この静止画表示領域の更新期間 TS には、表示動作切り換えレジスタ (DM) を「=1」として動画インターフェースから表示を継続する。これにより、動画表示中においても静止画表示領域の更新が可能となり、より柔軟な表示形態を実現できる。30

#### 【0082】

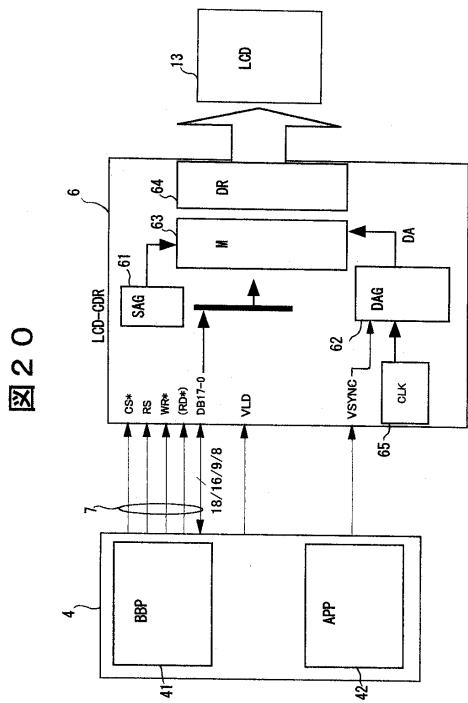

図 20 は本発明の実施例 4 の説明図であり、表 2 及び表 3 の VSYNC インターフェースを採用した場合の液晶コントローラ・ドライバとその周辺回路の構成例を説明するブロック図である。そして、メモリ (M) の書き込みを制御するライトアドレス生成回路 (SAG) は、システム・インターフェース 7 から制御し、メモリ (M) の読み出しを制御する表示アドレス生成回路 (DAG) のアドレスの生成タイミングをアプリケーション・プロセッサ 42 から垂直同期信号 VSYNC で制御するようにした。40

#### 【0083】

この場合、表示アドレス生成回路 (DAG) は、VSYNC アクティブルレベルでリセットされ、内蔵クロック回路 CLK から発生されたクロック信号を計数するカウンタを有し、このカウンタの出力が表示アドレス DA として利用される。この構成の場合、従来システムをほとんど変更することなく、動画データを表示することが可能となる。尚、システム・インターフェース 7 側からの動画データの書き込み速度は、内蔵クロック発生回路 CLK からのクロック信号に基づく表示動作よりも十分高速に行われる必要性がある。他の50

構成と動作は図 3 で説明したものと同様である。

【 0 0 8 4 】

本実施例の構成において、表示メモリ (M) に対してアプリケーション・プロセッサ 42 からの垂直同期信号 VSYNC で書き込まれた表示データの読み出しの開始時点を制御することにより、画像表示を画面の走査タイミングに同期させることができ、画面の途中から画像更新がなされることはない。したがって、画面更新中での画面のチラツキは発生しない。

【 0 0 8 5 】

なお、以上、本発明を実施例により説明したが、本発明は上記実施例の構成に限定されるものではなく、本発明の技術思想を逸脱することなく、種々の変形が可能であることは言うまでもない。

10

【図面の簡単な説明】

【 0 0 8 6 】

【図 1】本発明の実施例 1 の全体構成の説明図である。

【図 2】本発明の表示駆動制御装置の実施例 1 の構成を用いた携帯電話機の表示画面における動画像の画面更新の様子を説明する模式図である。

【図 3】本発明による液晶コントローラ・ドライバの回路構成とその関連回路を説明するブロック図である。

【図 4】本発明の表示駆動制御装置の実施例 1 の構成を用いた携帯電話機の表示画面における動画像の画面更新の様子を動画インターフェースでの表示動作として説明する模式図である。

20

【図 5】本発明の実施例の効果を比較して説明するための動画インターフェースと内蔵メモリを有しない液晶コントローラ・ドライバの構成とその動作の説明図である。

【図 6】図 5 の液晶コントローラ・ドライバによる静止画表示の様子を説明する模式図である。

【図 7】本発明の実施例の効果を比較して説明するためのシステム・インターフェースと内蔵メモリによるデータ転送を行う液晶コントローラ・ドライバの構成とその動作の説明図である。

【図 8】図 7 の液晶コントローラ・ドライバによる静止画表示の様子を説明する模式図である。

30

【図 9】本発明の構成を図 7 の構成および図 5 の構成と比較して示すメリットとデメリットの説明図である。

【図 10】本発明の液晶コントローラ・ドライバを具体化したドライバチップの回路構成の説明図である。

【図 11】システム・インターフェースとアプリケーション・インターフェースを備えて内蔵メモリによるデータ転送を行う液晶コントローラ・ドライバの実施例の構成とその動作の説明図である。

【図 12】図 11 の液晶コントローラ・ドライバによる静止画表示の様子を説明する模式図である。

【図 13】システム・インターフェースとアプリケーション・インターフェースの切り換え動作を表示画面の状態で示した説明図である。

40

【図 14】本発明の実施例 2 の説明図である。

【図 15】図 14 の回路構成による動画バッファリング動作における動画データの転送の様子を説明する説明図である。

【図 16】本発明による動画転送を実現する回路構成の一実施例を説明するブロック図である。

【図 17】図 16 の液晶コントローラ・ドライバによる選択領域のみへの静止画表示の様子を説明する模式図である。

【図 18】本発明の効果を説明するための前記各データ転送方式の動画データ転送数の比較説明図である。

50

【図19】本発明の実施例3の説明図である。

【図20】本発明のさらに実施例4の説明図である。

【図21】本発明前に本発明者によって検討された表示駆動制御装置の一例である動画対応のインターフェースを持たない携帯電話機の駆動回路装置のシステム構成の一例を説明するブロック図である。

【図22】図21に示したシステム構成での動画像表示時の画面更新の動作例を模式的に示す説明図である。

【図23】図21に示したシステム構成での液晶コントローラ・ドライバとその周辺回路の構成例を説明するブロック図である。

【図24】図23に示したシステム構成での液晶コントローラ・ドライバを用いた携帯電話機の画面における動画像の画面更新の様子を説明する模式図である。 10

【符号の説明】

【0087】

1 . . . 駆動制御回路装置、2 . . . 音声インターフェース( A U I ) 3 . . . 高周波インターフェース( H F I )、4 . . . 画像データ処理装置である画像プロセッサ、4 1 . . . マイコン M P U を有するベースバンド・プロセッサ、4 1 1 . . . デジタル・シグナル・プロセッサ( D S P )、4 1 2 . . . A S I C 、4 2 . . . アプリケーション・プロセッサ( A P P )、4 2 1 . . . 動画対応プロセッサ( M P E G )、4 2 2 . . . 液晶表示コントローラ( L C D C )、5 . . . 画像表示メモリ、6 . . . 表示駆動制御回路である液晶コントローラ・ドライバ( L C D - C D R )、7 . . . 静止画・テキスト・システム・I / Oバス・インターフェース( S S / I F )、動画インターフェース( M P / I F )、9 . . . マイクロフォン( M / C )、1 0 . . . スピーカ( S / P )、1 1 . . . ビデオカメラ( C / M )、1 2 . . . アンテナ( A N T )、1 3 . . . 液晶パネル( 液晶ディスプレイ: L C D )、6 2 1 . . . 表示動作切り換えレジスタ( D M )、6 0 5 . . . R A M アクセス切り換えレジスタ( R M )。 20

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

| メソッド                                  | 特徴                                                          |

|---------------------------------------|-------------------------------------------------------------|

| (1) 図7の構成のみ<br>(スピーカー端子のみ<br>(表示メモリ有) | 静止画：転送データ量小<br>消費電力小<br>動画：画面更新時にチラッキが無い<br>消費電力小           |

| (2) 図5の構成のみ<br>(ライセンスモリのみ)            | 静止画：転送データ量大<br>消費電力大<br>動画：画面更新時にチラッキが無い<br>消費電力大           |

| (3) 本発明の構成                            | 静止画：転送データ量小<br>消費電力小<br>動画：画面更新時にチラッキなし<br>転送データ量小<br>消費電力小 |

【図10】

【図11】

【図12】

【図13】

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

【図23】

【図24】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 6 0 V |

| G 0 2 F | 1/133 | 5 0 5   |

| G 0 9 G | 3/20  | 6 8 0 S |

| G 0 9 G | 3/20  | 6 6 0 U |

| G 0 9 G | 3/20  | 6 1 2 L |

(72)発明者 太田 茂

東京都小平市上水本町五丁目20番1号

ー プ内

株式会社日立製作所 半導体グル

(72)発明者 田邊 圭

東京都小平市上水本町五丁目20番1号

ー プ内

株式会社日立製作所 半導体グル

審査官 堀部 修平

(56)参考文献 特開2001-222249 (JP, A)

特開2000-066654 (JP, A)

特開平10-111671 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |           |   |         |

|---------|-----------|---|---------|

| G 0 9 G | 3 / 0 0   | - | 3 / 3 8 |

| G 0 2 F | 1 / 1 3 3 |   |         |