#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

#### (19) World Intellectual Property Organization

International Bureau

#

(10) International Publication Number WO 2012/122521 A2

#### (43) International Publication Date 13 September 2012 (13.09.2012)

(51) International Patent Classification: *G11C 7/10* (2006.01) *G11C 7/06* (2006.01)

(21) International Application Number:

PCT/US2012/028599

(22) International Filing Date:

9 March 2012 (09.03.2012)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

| 61/451,031 | 9 March 2011 (09.03.2011)  | US |

|------------|----------------------------|----|

| 61/452,845 | 15 March 2011 (15.03.2011) | US |

| 61/476,098 | 15 April 2011 (15.04.2011) | US |

| 61/483,544 | 6 May 2011 (06.05.2011)    | US |

- (72) Inventor; and

- (71) Applicant: SHEPPARD, Douglas, P. [US/US]; 324 Inverness Drive, Trophy Club, TX 76262 (US).

- (74) Agent: CARSTENS, David, W.; Carstens & Cahoon, LLP, P.O.Box 802334, Dallas, TX 75380 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

(54) Title: MEMORY CELL SYSTEM AND METHOD

(57) Abstract: A memory cell system/method incorporating reduced transistor counts and/or improved design-for-manufacturability (DFM) is disclosed. The system/method incorporates cross-coupled feedthru (3410) / feedback (3420) amplifiers to implement memory cell state memory, wherein the feedback amplifier incorporates a multi-state output drive capability (3423) allowing the memory cell to be read/written using only one access device (3430) connected to the output (3412) of the feedthru (3410) amplifier. The multi-state output drive capability (3423) modulates the feedback amplifier (3420) drive strength to enable reading/writing of the feedthru amplifier (3410) state with greatly reduced memory cell input fan-in requirements. The invention anticipates replacement of traditional DP/8T/6T/4T memory cell structures with corresponding 6T/6T/5T/3T memory cell configurations, resulting in a 16% - 25% transistor reduction depending on memory array application context.

### PATENT APPLICATION INVENTORS

A citizen of the United StatesSPECIFICATION

5

### **TITLE OF INVENTION**

#### MEMORY CELL SYSTEM AND METHOD

### **CROSS REFERENCE TO RELATED APPLICATIONS**

Applicant claims benefit pursuant to 35 U.S.C. § 119 and hereby incorporates by reference Provisional Patent Application for "IMPROVED MEMORY CELL", serial number 61/451,031, docket ASHEP.0102P, filed electronically with the USPTO on 3/9/2011.

Applicant claims benefit pursuant to 35 U.S.C. § 119

15 and hereby incorporates by reference Provisional Patent

Application for "MEMORY CELL", serial number 61/452,845,

docket ASHEP.0103P, filed electronically with the USPTO on

3/15/2011.

Applicant claims benefit pursuant to 35 U.S.C. § 119

20 and hereby incorporates by reference Provisional Patent

Application for "5T SINGLE PORT SRAM UTILIZING EASY-WRITE

WITH IMPROVED NOISE MARGIN", serial number 61/476,098,

docket ASHEP.0104P, filed electronically with the USPTO on

4/15/2011.

25 Applicant claims benefit pursuant to 35 U.S.C. § 119 and hereby incorporates by reference Provisional Patent

Application for "METHOD FOR WRITING AND READING A MEMORY WITH ENHANCED DFM", serial number 61/483,544, docket ASHEP.0105P, filed electronically with the USPTO on 5/6/2011.

### PARTIAL WAIVER OF COPYRIGHT

All of the material in this patent application is subject to copyright protection under the copyright laws of the United States and of other countries. As of the first effective filing date of the present application, this material is protected as unpublished material.

However, permission to copy this material is hereby granted to the extent that the copyright owner has no objection to the facsimile reproduction by anyone of the patent documentation or patent disclosure, as it appears in the United States Patent and Trademark Office patent file or records, but otherwise reserves all copyright rights whatsoever.

#### STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH

#### OR DEVELOPMENT

20 Not Applicable

5

10

15

### REFERENCE TO A MICROFICHE APPENDIX

Not Applicable

#### **FIELD OF THE INVENTION**

The present invention generally relates to memory cell systems and methods. While not limitive of the invention teachings, the present invention may in some circumstances

SUBSTITUTE SHEET (RULE 26)

be advantageously applied to areas including but not limited to U.S. Patent Classifications 365/149; 365/154; 365/156; 365/203; 365/189.05; 365/189.04; 326/49; 327/199; 327/51; 365/230.06; 307/290.

#### PRIOR ART AND BACKGROUND OF THE INVENTION

5

10

15

20

25

30

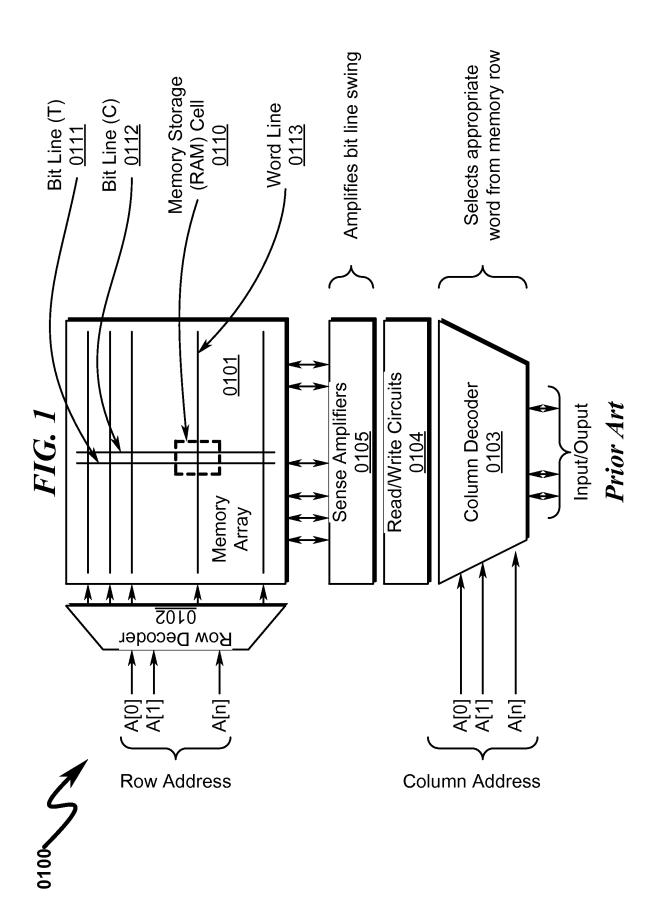

### **Memory Array Architecture Overview (0100)**

The current architecture used to configure large memory arrays is generally illustrated in FIG. 1 (0100), wherein the memory array (0101) is addressed by a multi-bit row address (0102) and column address (0103) decoders. circuits are used in conjunction with read/write circuits (0104) and sense amplifiers (0105) to read/write the contents of a memory cell (0110) contained within the memory array (0101). Within this context the individual memory cells (0110) are accessed via bit lines (true (0111) and well (0112)) as as a word line Activation of the true/complement bit lines (0111, 0112) in conjunction with the appropriate word select line (0113) individually addresses the memory cell (0110) within a particular row and permits read/write access particular memory cell (0110).

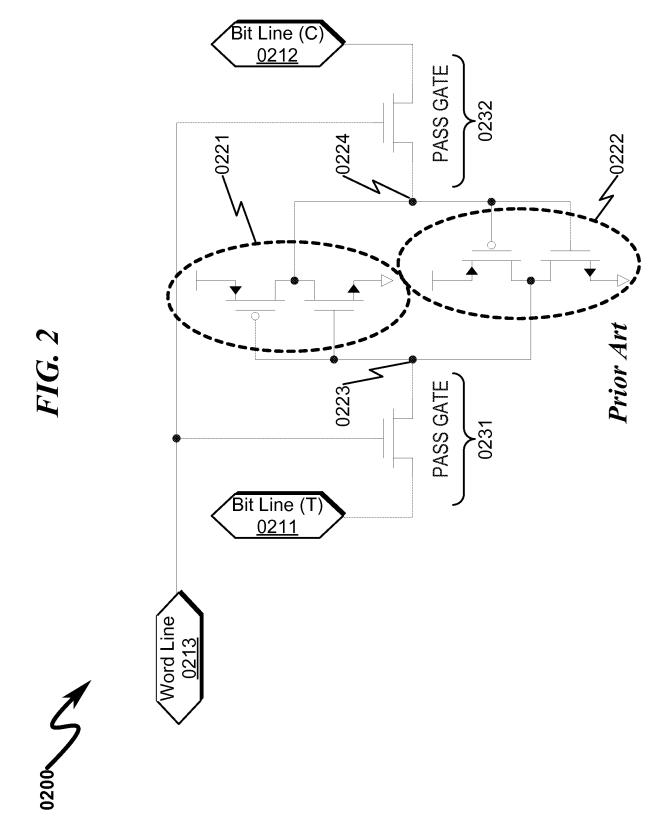

## Static 6T Memory Cell Architecture Overview (0200)

Within the memory array architecture of FIG. 1 (0100), the individual memory cells (0110) have traditionally taken the form of a pair of cross-coupled CMOS inverters (0221, 0222) as generally depicted in FIG. 2 (0200) in the implementation of fully static memory (SRAM) arrays. These cross-coupled inverters (0221, 0222) are accessed for read/write by a bit lines (true (0211) and complement (0212)) as well as a word line (0213). The bit lines (0211,

0212) access the cross-coupled inverter memory cell (0221, 0222) via respective pass gates (0231, 0232) that operate in conjunction with the bit lines (0211, 0212) and word line (0213).

This architecture is commonly referred to as a "6T cell" architecture as it requires six active transistors for its implementation.

10

15

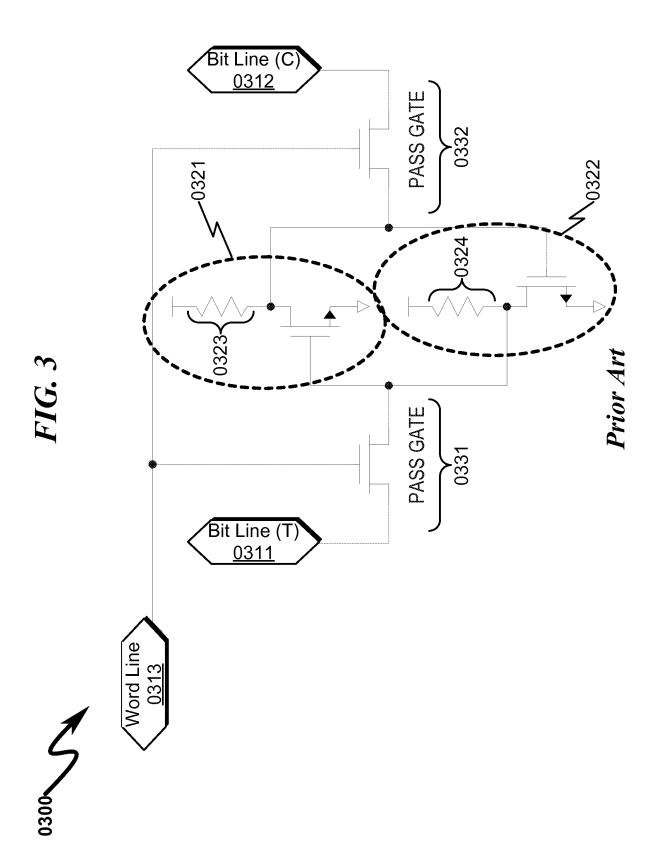

## Non-Static 4T Memory Cell Architecture Overview (0300)

Within the memory array architecture of FIG. 1 (0100), the individual memory cells (0110) may also take the form of a pair of cross-coupled NMOS inverters (0321, 0322) as generally depicted in FIG. 3 (0300) in the implementation of non-static memory arrays. These cross-coupled inverters (0321, 0322) are accessed for read/write by a bit lines (true (0311) and complement (0312)) as well as a word line (0313). The bit lines (0311, 0312) access the cross-coupled inverter memory cell (0321, 0322) via respective pass gates (0331, 0332) that operate in conjunction with the bit lines (0311, 0312) and word line (0313).

20 The major difference in this architecture as compared with that of FIG. 2 (0200) is that high value resistors (0323, 0324) operate as loads to their respective N-channel transistors within the inverters (0321, 0322). These high value resistors may be implemented with polysilicon, depletion transistors, modified ion implantation profiles, 25 fabrication methodologies common semiconductor industry. While this memory cell is not fully static and does consume power in the idle state, it can achieve a manufacturing area advantage over some fully static designs as depicted in FIG. 2 (0200). 30

This architecture is commonly referred to as a "4T cell" architecture as it requires four active transistors for its implementation.

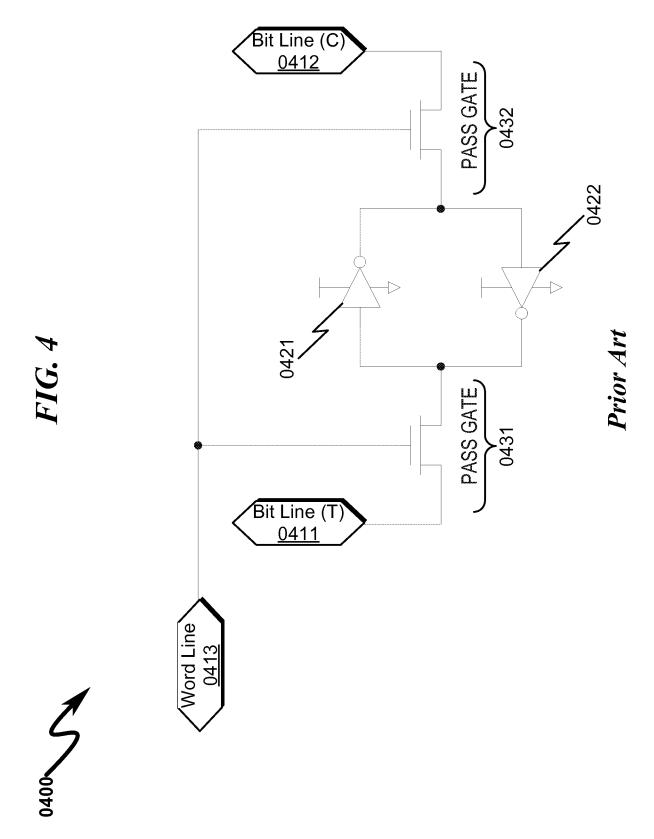

### **Generalized Memory Cell Architecture Overview (0400)**

5

10

15

20

25

30

The combination of memory array architecture in FIG. 1 (0100) and memory cell architecture in FIG. 2 (0200) and FIG. 3 (0300) can be more fully generalized as depicted in FIG. 4 (0400) to characterize the prior art. Here it can be seen that the feedthru (0221, 0321) and feedback (0222, 0322) inverters have been abstracted as generalized inverters (0421, 0422) with appropriate power supply connections depicted. Note that in some abstractions the power supply (VDD/VCC) and reference ground (VSS/GND) connections may be omitted and assumed as included by the context of the schematic.

This memory cell abstraction can be applied to a variety of other static/non-static memory cell configurations that implement other functions such as dual-port (DP) memories, FIFOs, and the like.

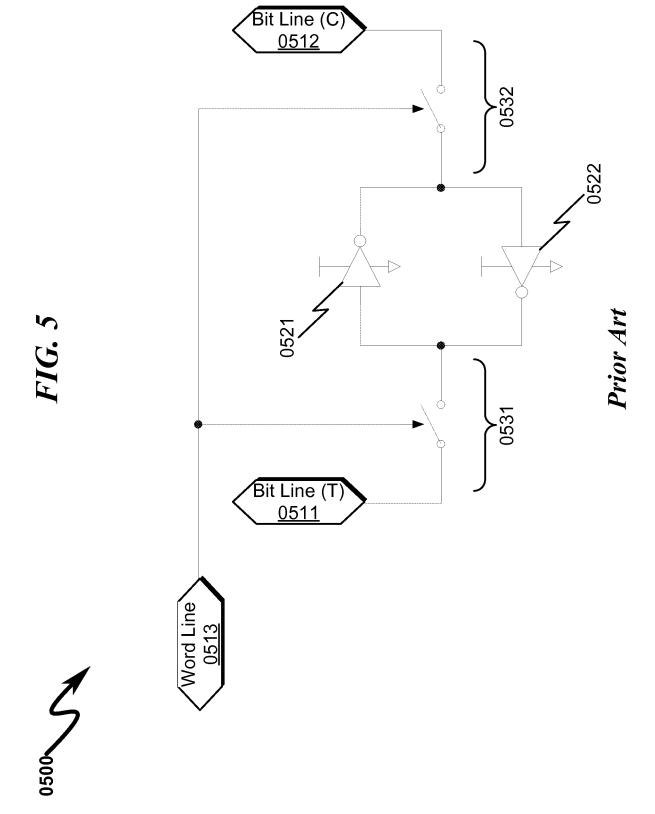

# **Memory Cell Abstraction (0500)**

The generalized memory cell architecture of FIG. 4 (0400) may be further abstracted as indicated in FIG. 5 (0500) wherein the pass gates (0231, 0232, 0331, 0332, 0431, 0432) are replaced by generalized switches (0531, 0532).

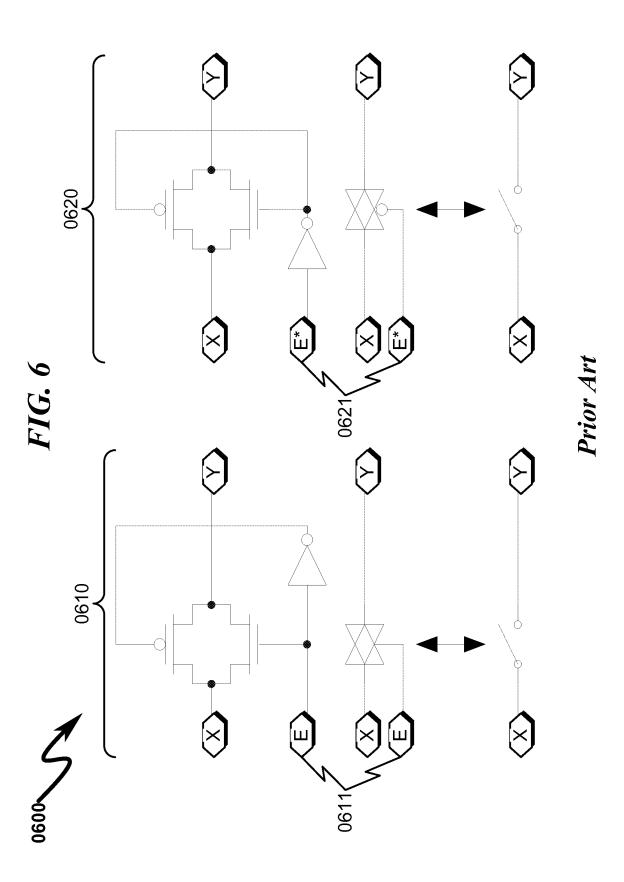

# **Switch Abstraction (0600)**

The replacement of pass gates (0231, 0232, 0331, 0332, 0431, 0432) by switches (0531, 0532) as abstracted in FIG. 5 (0500) may also take the form of traditional transmission gates (0610, 0620) with associated control inputs (0611, 0621) as generally illustrated in FIG. 6 (0600). Within

this context the switching functionality is more robust than that allowed by traditional single transistor pass gates (0231, 0232, 0331, 0332, 0431, 0432) at the expense of a four-fold increase in the overall transistor count. While this approach is not generally practical for large memory arrays, it can have application in some state memory logic functions as detailed below.

### **Ancillary Memory Cell Applications**

While memory arrays and their associated cells have been traditionally associated with architectures depicted in FIG. 1 (0100) and FIG. 2 (0200), other forms have been used in some circumstances.

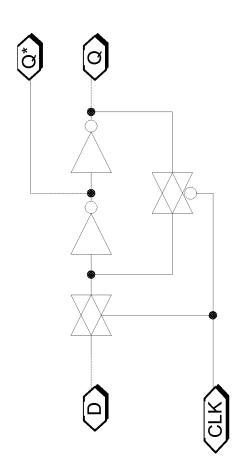

### Transparent Latch (0700)

FIG. 7 (0700) illustrated a traditional transparent digital latch configuration in which the cross-coupled inverters are switched using transmission gates in response to a latching clock signal (CLK). This topology provides for state memory context to be achieved, albeit at a greatly increased transistor count.

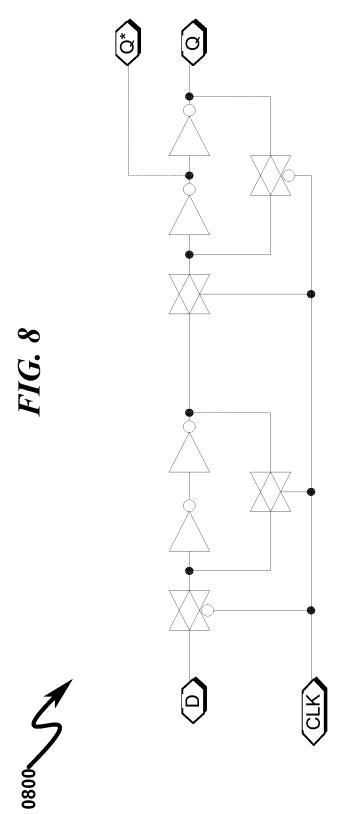

#### 20 **D-Flip-Flop (0800)**

25

30

As generally illustrated in FIG. 8 (0800), the transparent latch of FIG. 7 (0700) may be augmented to implement a traditional D-flip-flop having state memory dictated by input clock (CLK) transitions to the device. These two types of state memories are just examples of many variations on a theme that are taught by the prior art.

# **Background Context Suitable for Invention Application**

While the present invention may have significant advantages in the application to static and non-static memory array designs, the previously discussed background context has been presented solely to indicate that the

present invention as described herein may be applied to a wide variety of contexts in which "state memory" is required within the overall design. Thus, while the present invention has wide application in the design of large memory arrays, as indicated above it is not strictly limited to this particular application.

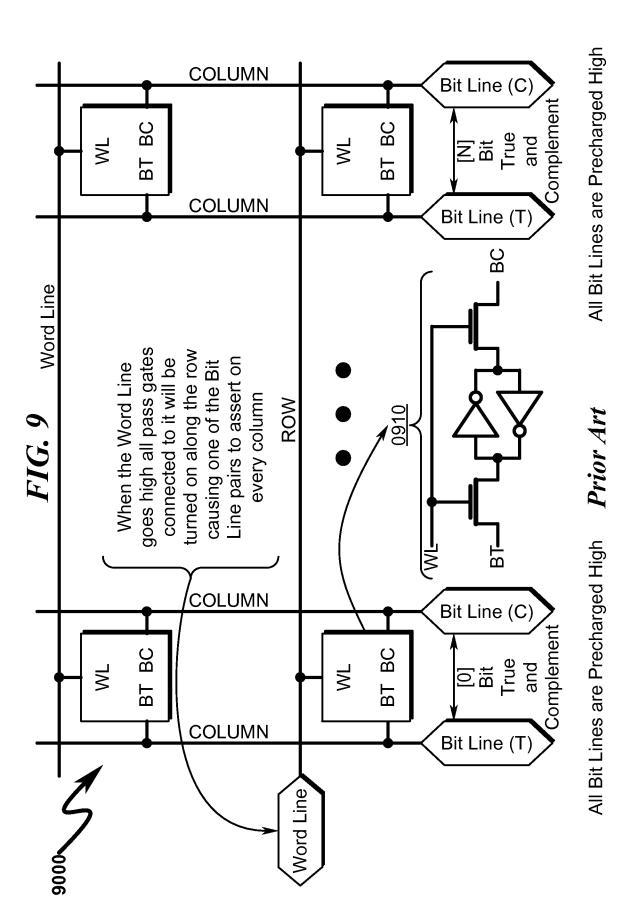

# **Memory Array Design Context (0900)**

The memory array as depicted in FIG. 1 (0100) typically consists of columns of Bit Lines (0111, 0112) and rows of Word Lines (0113). A row of the array is accessed by taking one of the Word Lines (0113) high while all others are low. Taking the Word Line (0113) high turns on the pass gates of every memory cell (0110) on that row which in turn will pass the internal state of the memory cell latch to the Bit Lines (0111, 0112). The state of the true side is passed to its own bit true (BT) Bit Line (0111), and the compliment side is passed to its own bit compliment (BC) side (0112). All Bit Lines (0111, 0112) are initially pre-charged high, and all Word Lines (0113) are initially low.

10

15

This structure is illustrated in more detail by the system block diagram of FIG. 9 (0900) wherein the memory cell (0910) has been generalized to comprise a Bit Line (T) (BT), Bit Line (C) (BC), and a Word Line (WL).

### Overview Of Prior Art Memory Array Design Challenges

25 The traditional 6T (six transistor) SRAM memory cell generally illustrated in FIG. 2 (0200) has always had to deal with conflicting requirements of being easy to write to an opposite state and yet not be susceptible to flipping during a read. This is called READ DISTURB which occurs 30 when accessing the sensitive internal latch of the memory cell causes it to lose its stored data. This tradeoff of

write-ability vs. read is one of the reasons that the traditional 6T memory cell requires two (2) pass gates (PG) (0231, 0232) as illustrated in FIG. 2 (0200). A conflicting design requirement is often fabrication area, as a major requirement of the memory cell is for it to be as small as possible. Generally speaking, the fewer transistors required by the memory cell the smaller the overall physical size of the memory cell.

5

The design and production of the SRAM has always required that the noise margin of the memory cell (also 10 referred to as the "bit cell") be designed around. Reading the memory cell caused the sensitive internal nodes of the latch (0223, 0224) to be coupled to the highly capacitive Bit Lines (0211, 0212) through the pass gates (PG) (0231, 0232) thus exposing the cell to the possibility of being 15 disturbed. Thus, any time the memory cell is accessed (pass gate (0231, 0232) turned on) it is in danger. Throughout the history of the SRAM, designers have tried to design around this problem which gets increasingly worse as the process technology continues to shrink and the transistor 20 variation relative to each other increases. In fact, it has become severe enough that some current memory cell designs actually have to use more than six transistors per memory cell.

What is commonly called READ DISTURB actually occurs during a write as well as during a read - any time that the memory cell is accessed. Conventional memory archtectures access every memory cell along a given Word Line (0213), with each Word Line potentially having many (128, 256, 512, 30 1024, ...) attached memory cells.

The READ DISTURB issue is further exasperated due the requirement that during a write the cell must be able to

flip from an opposite state to the desired state to be written. By assuring that the cell can be written, the design is often in conflict with a requirement that the design to be intolerant to READ DISTURB. One design requirement is typically traded off against the other when using the traditional approach.

### **READ DISTURB**

The possibility of the cell being flipped by exposing its low side to the pre-charged high Bit Line when the shared Word Line along a given row is taken high is called READ DISTURB. The 6 transistors in the memory cell should be as small as possible to reduce the area of the overall memory since it can have millions of memory cells. Very small transistors within the memory cell means that they have very weak drive which can be overcome by the highly capacitive Bit Lines and pull the internal state of the cell in the opposite direction causing it to lose the state that is stored in it.

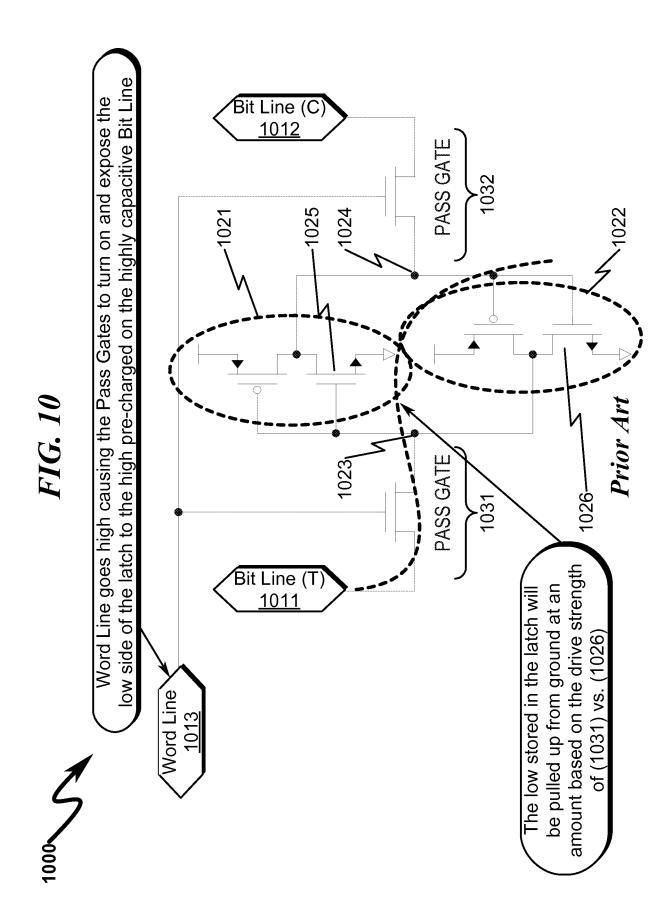

#### Memory Cell Read Disturb (1000)

10

15

25

The architecture of a memory cell undergoing READ DISTURB is generally illustrated in FIG. 10 (1000).

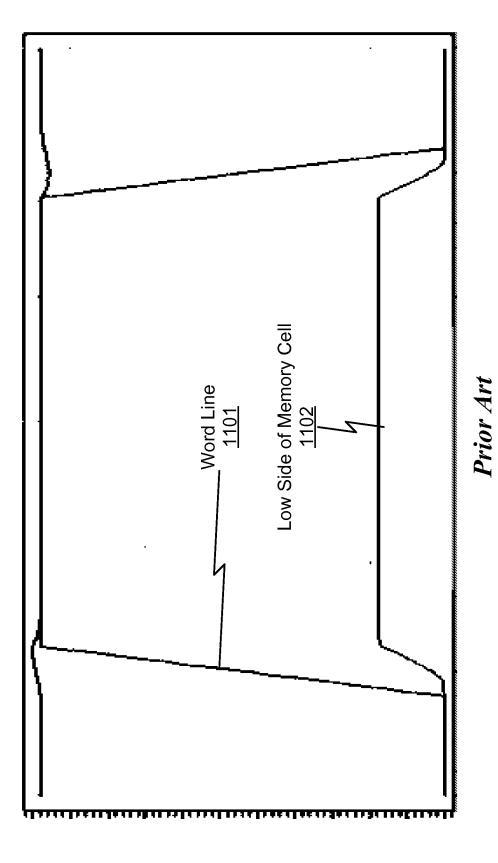

#### Internal Memory Cell Voltages (1100)

The internal memory cell voltages for a memory cell undergoing READ DISTURB are generally illustrated in FIG. 11 (1100), wherein activation of the Word Line (1101) results in a low side kickup voltage spike (1102) at the memory cell. Note that this voltage spike (1102) occurs for ALL memory cells in the row addressed by the Word Line.

The only way to increase the memory cell margin to READ 30 DISTURB is to adjust the drive strength between the pass gate (PG) (1131) and the pull down (PD) (1126) such that the

low side of the cell can't be pulled up so high that it causes the cell to flip. As the drive strength of the pull down (1126) is increased relative to the pass gate (1131) the ability to keep a low on the low side of the memory cell increases thereby increasing the noise margin of the memory cell. The relationship of the pull down (1126) drive strength vs. the pass gate (1131) drive strength is called the BETA RATIO ( $\beta_R$ ) and is defined as follows:

$$eta_{R} = rac{I_{PD}}{I_{PG}} = rac{\left(rac{W_{PD}}{L_{PD}}

ight)}{\left(rac{W_{PG}}{L_{PG}}

ight)}$$

10 Where W and L are the effective transistor gate width and length respectively for the pull-down (PD) and pass-gate (PG) devices.

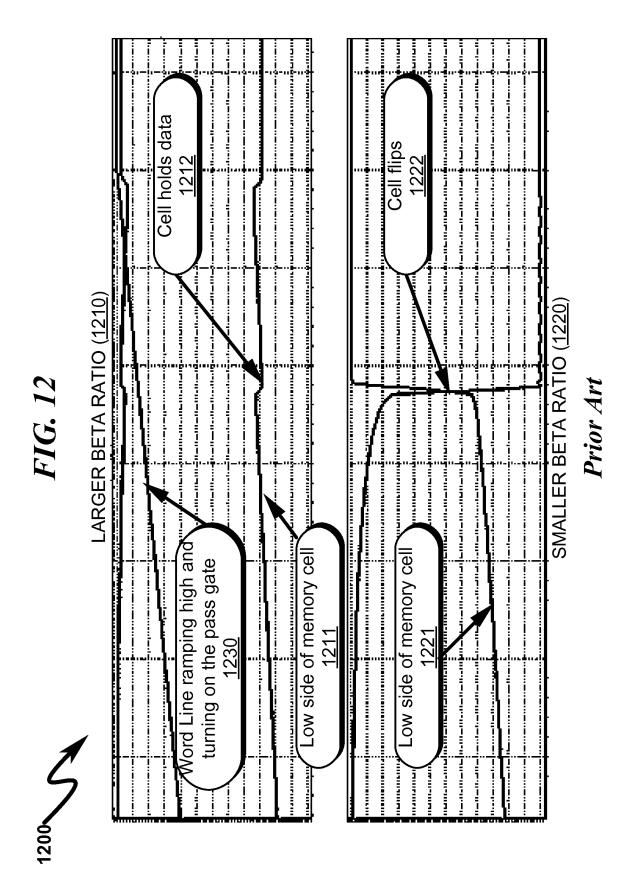

### Read Disturb BETA RATIO Sensitivity (1200)

5

15

20

25

The READ DISTURB behavior as a function of BETA RATIO can be best illustrated by the waveforms depicted in FIG. 12 (1200), wherein a larger BETA RATIO (1210) configuration is compared to a smaller BETA RATIO (1220) configuration. In both situations the Word Line (1230) is ramped from low-to-high and the depicted waveforms indicate a larger BETA RATIO configuration (1210) maintains the memory cell bit state (1212) while the smaller BETA RATIO configuration (1220) trips the memory cell bit state (1222). This memory cell sensitivity to BETA RATIO often results in larger memory cell array size to accommodate additional transistor sizing required by this design requirement for stable memory cell state in response to READ DISTURB behavior.

### Writing the Memory Cell (1300)

The traditional 6T memory cell is written to the opposite state by pulling the high side of the latch low — it cannot be written by pulling the low side high because of it needing to be protected against READ DISTURB. It is limited by how high it can eventually pull which is the supply voltage (VDD) minus a N-channel threshold voltage (VTN) or (VDD — VTN). Also, the BETA RATIO is increased to assure that no READ DISTURB occurs, and the low side of the latch cannot be pulled high enough to cause the cell to flip when a write to the opposite state is required. Therefore, a write of the memory cell to the opposite state can only occur by pulling the high side of the latch low. It is this requirement that requires that both the true and compliment sides of the latch be accessed by a bit true (BT) Bit Line and a bit compliment (BC) Bit Line, respectively.

5

10

15

20

25

30

An efficient array design will usually have many columns on a given row that will far exceed the number of Bits Per Word (BPW) that is on the output of the memory example a memory array may As an configuration that requires 1 BPW, but 512 columns may be configured on each row. Thus, when a write cycle is initiated the 1 bit to be written will be forced onto the decoded column to write just that single memory cell location, but 512 memory cells are accessed on the addressed row (pass gates turned on) at one time. This means that on the selected Word Line 511 memory cells are being read while the 1 decoded column for which the write is occurring. Thus, the 511 memory cells that are not being written are exposed to READ DISTURB even though a write is occurring.

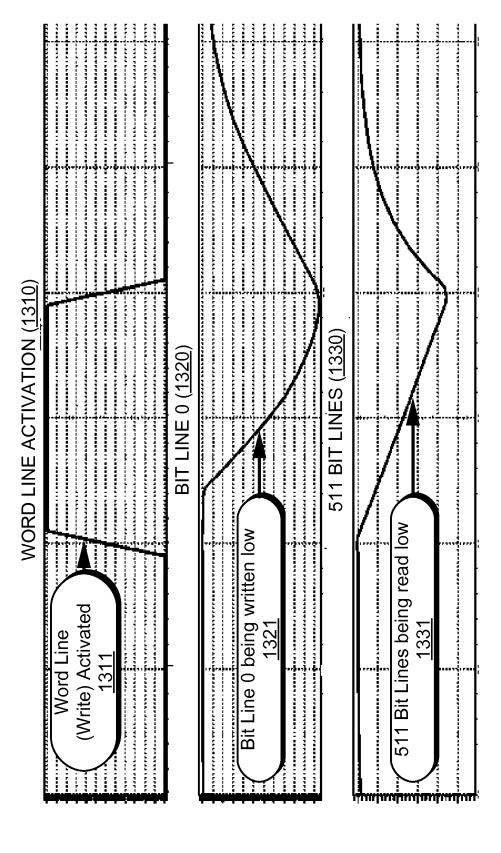

This behavior can be best illustrated by viewing the signal waveforms of FIG. 13 (1300), wherein the Word Line

(write) activation pulse (1310) is illustrated along with the corresponding Bit Line 0 output (1320) and the loading effect on the remaining unaddressed 511 Bit Lines (1330). As can be seen by this illustration, the read loading effect on the unwritten 511 bit lines (1330) is significant and accounts for the real possibility of READ DISTURB among the other memory cells within the memory array.

The dynamic switching associated with this behavior can also result in significant dynamic power consumption, since every column has a voltage swing on either the BT or BC Bit Adding this dynamic power consumption with the usually rail-to-rail voltage swing on the Bit Lines being written can result in the write cycle consuming more power than the read cycle in the memory array. Note that the number of Bit Lines being written is dependent on the number of Bits Per Word (BPW). Thus, if there are many bits per word such as 16, 32 or 64 BPW this would equate to a significant amount of dynamic power consumption within the This dynamic power consumption represents a memory array. significant barrier to low power consumption in modern 8/16/32/64-bit processors that incorporate embedded memory as well as conventional large capacity externally addressed memory systems.

# **Prior Art Switched VDD/VSS Memory Cells**

Several attempts have been disclosed by the prior art that attempt to reduce the overall memory cell area by eliminating one of the Pass Gates that are used to access the memory cell. Two of these approaches will now be discussed.

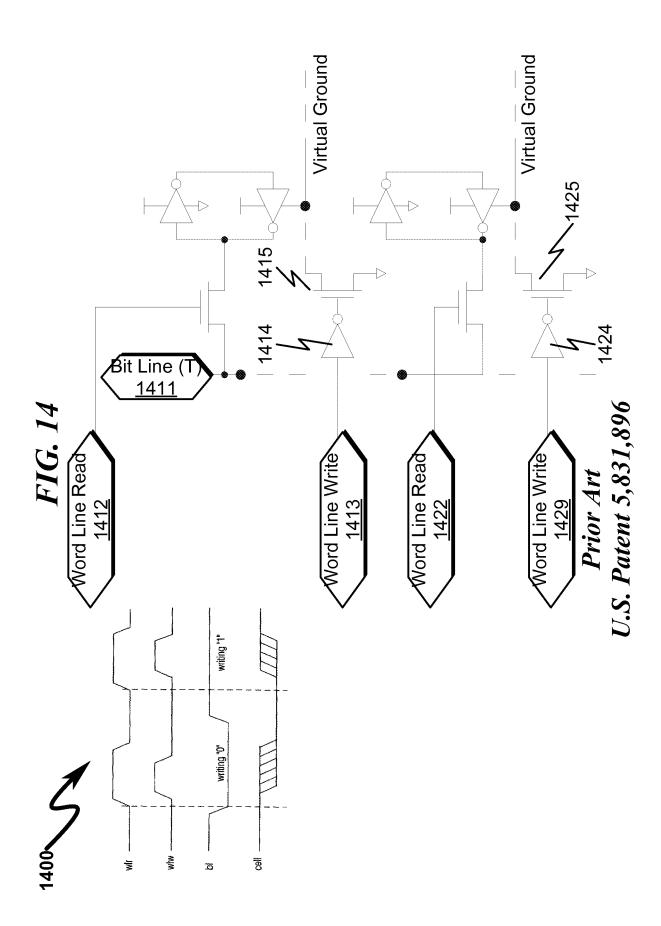

#### 30 *U.S. Patent 5.831.896 (1400)*

5

10

15

20

As generally illustrated in FIG. 14 (1400), this U.S. patent discloses a cross-coupled inverter pair that has VSS

switched on the feedback inverter in conjunction with separate WORD LINE READ (1412, 1422) and WORD LINE WRITE (1413, 1423) control signals. This memory architecture enables the entire word row during a write and/or read operation and while the VSS switching (1415, 1425) permits easier writing of the memory cell, it also subjects the entire row to READ DISTURB during the process of a read operation.

Sharing virtual ground during a write can create a condition where it could be difficult to write a high into one of the memory cells within the same group. This condition can occur based on what is being written and what was previously stored in the memory cells as generally illustrated in FIG. 14 (1400).

15 The lack of Bit True (BT) and Bit Complement (BC) Bit Lines in this design can also result in poorer noise immunity than traditional 6T memory cell designs, as the sensed Bit Line voltage in this design is referenced to digital VSS ground, which can contain significant noise.

20 This is in contrast to traditional 6T designs in which the BT/BC signal lines may be differentially sensed irrespective of VDD/VSS noise.

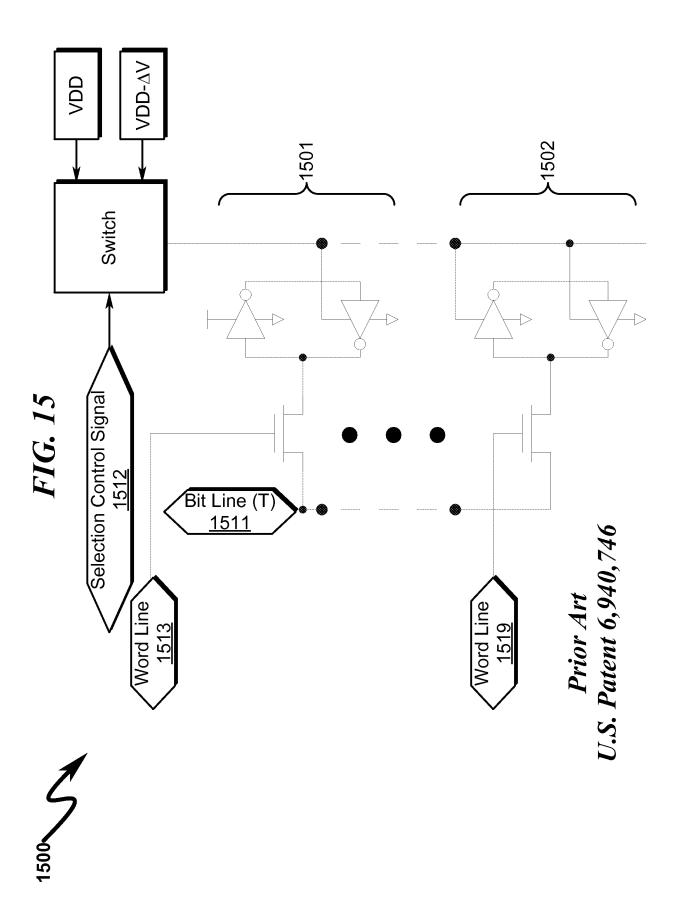

#### U.S. Patent 6.940.746 - VDD Switching (1500)

10

25

30

As generally illustrated in FIG. 15 (1500), this patent discloses VDD switching in FIG. 15 (1500) of the feedback inverter within the memory cell (1501, 1502). The approach taken by this patent disclosure is to reduce the feedback inverter strength by reducing its VDD strength and thus permitting the pass gate to be driven by the Bit Line (1511) to write the memory cell (1501, 1502). This is typically accomplished by switching the VDD line to an alternate voltage during write cycles.

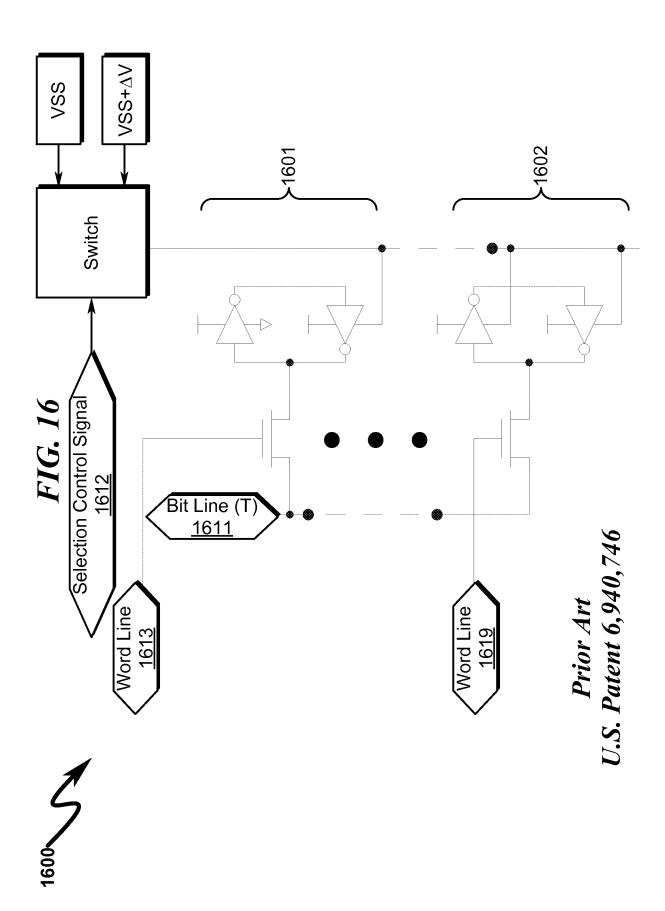

### U.S. Patent 6.940.746 - VSS Switching (1600)

This patent discloses VSS switching in FIG. 16 (1600) of the feedback inverter within the memory cell (1601, 1602). The approach taken by this patent disclosure is to reduce the feedback inverter strength by reducing its VSS strength and thus permitting the pass gate to be driven by the Bit Line (1611) to write the memory cell (1601, 1602). This is typically accomplished by switching the VSS lines to an alternate voltage during write cycles.

#### 10 **U.S. Patent 6.940.746 – READ DISTURB**

5

15

20

25

30

These VDD/VSS switching architecture still suffer from READ DISTURB issues in that during read cycles the Bit Line drags down all the memory cells in a given selected Word Line with the potential of flipping the memory cells to an indeterminate state. This drawback requires that this architecture undergo similar BETA RATIO tradeoffs as discussed previously.

### **Conflicts Between Read and Write**

As can be seen from the above discussion, it important for a memory cell to be stable during a read and during a write cycle, but this presents writeable conflicting constraint on the memory cell. These opposing requirements have always presented the designer manufacturer with having to make tradeoffs with the hope that there would be enough noise margin that will make it possible to produce a yieldable memory that is reliable over the variation in the manufacturing process as well as the variation in conditions such as temperature and voltage. fact it has become more difficult to continue to reduce the voltage of the memory cell (VDD) as much as can be done with logic circuits, because this also makes it difficult for the memory cell to stay stable.

This problem has gotten substantially worse as the transistors continue to shrink with each new reduction in feature sizes of the process. The new generation of submicron processes have problems with transistors characteristics not matching - even when they are in the same memory cell right next to each other. This can have a big effect on the BETA RATIO of the memory cell, because the threshold voltage (VT) of the Pull Down can be different than the threshold voltage (VT) of the Pass Gate. There can be other variations as well that can shift the drive strength of either the pull down or pass gate in different directions, and again this variation is getting much more difficult to deal with in the newer fabrication processes causing the semiconductor industry to have to seek other solutions in order to be able to have a reliable and yieldable memory.

10

15

20

25

From the above discussion it is evident that there is a clear need to improve writing and reading a memory that is easy to write without trading off the opposing requirement to protect against READ DISTURB, thereby improving Design For Manufacturability (DFM). In addition to improving write and read reliability it is important that the resulting physical size of the memory cell/array not be increased to achieve these goals, with a long-felt industry need to make the overall memory cell/array even smaller than existing prior art designs.

### **Deficiencies in the Prior Art**

The prior art as detailed above suffers from the following deficiencies:

• The prior art SRAM memory cells suffer from poor Design For Manufacturability (DFM) in that they are prone to

yield and other failures due to variations in the transistor manufacturing and fabrication process.

• The prior art 5T memory cell architectures rely on parallel connection of bit lines to a given memory cell, resulting in poor READ DISTURB performance.

5

10

15

- The prior art tradeoffs with respect to the sizing of pass gates and pulldown devices within a given memory cell often result in unwanted and inefficient transistor sizing tradeoffs that increase memory cell sizing requirements for a given memory array.

- The prior art implementations of 6T memory cells and their associated arrays are particularly prone to yield/performance problems associated with variations in manufacturing process and/or supply voltage variations.

- The prior art implementations of 6T memory cells suffers from poor static power consumption with submicron geometries in part due to pass gate leakage currents associated with each memory cell.

- The prior art implementations of 6T memory cells suffers from poor dynamic power consumption with submicron geometries in part due to bit line capacitance associated with each memory cell.

While some of the prior art may teach some solutions to 25 several of these problems, the core issues of reducing the area of memory cells while improving design for manufacturability have not been addressed by the prior art.

### **OBJECTIVES OF THE INVENTION**

Accordingly, the objectives of the present invention are (among others) to circumvent the deficiencies in the prior art and affect the following objectives:

- 5 (1) Provide for a memory cell system and method that minimizes memory cell area.

- (2) Provide for a memory cell system and method that reduces or eliminates the stability of the memory cell as a function of BETA RATIO.

- 10 (3) Provide for a memory cell system and method that permits mass erasure of a memory array in response to a predetermined event.

- (4) Provide for a memory cell system and method that reduces the number of transistors required to implement a memory array.

- (5) Provide for a memory cell system and method that increases the design for manufacturability (DFM) of the memory cell and associated memory arrays using the memory cell.

- 20 (6) Provide for a memory cell system and method that permits smaller geometry transistors to be used to construct the memory cell.

- (7) Provide for a memory cell system and method that permits a reduction of static power consumed by a memory array by minimizing the number of Bit Line Pass Gates associated with a given memory cell.

- (8) Provide for a memory cell system and method that permits a reduction of dynamic power consumed by a memory array by minimizing the number of Bit Lines associated with a given memory cell.

15

25

30

(9) Provide for a memory cell system and method that permits a reduction of dynamic power consumed by a memory array by utilizing a single Bit Line to access a given memory cell.

While these objectives should not be understood to limit the teachings of the present invention, in general these objectives are achieved in part or in whole by the disclosed invention that is discussed in the following sections. One skilled in the art will no doubt be able to select aspects of the present invention as disclosed to affect any combination of the objectives described above.

5

10

15

20

25

30

### **BRIEF SUMMARY OF THE INVENTION**

A memory cell system/method incorporating a reduced transistor count and/or improved design-for-manufacturability (DFM) is disclosed. The system/method incorporates cross-coupled feedthru/feedback amplifiers to implement the state memory component of the memory cell, wherein the feedback amplifier incorporates a multi-state output drive capability allowing the memory cell to be set/reset using only one access device connected to the input of the feedthru amplifier.

The multi-state output drive capability modulates the feedback amplifier drive strength to enable setting/resetting of the feedthru amplifier state with greatly reduced memory cell input fan-in requirements.

The invention anticipates the replacement of traditional 8T/6T/4T memory cell structures with corresponding 6T/5T/3T memory cell configurations, resulting in an overall transistor reduction ranging from 16% - 25% depending on memory array application context.

The disclosed memory cell is typically incorporated into memory arrays in which the memory cells may be written with or without the use of pass gates within the Word Line selectors and also in some circumstance written using a multiple step MULTI-WRITE procedure.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

5

10

For a fuller understanding of the advantages provided by the invention, reference should be made to the following detailed description together with the accompanying drawings wherein:

- FIG. 1 illustrates a prior art memory array architecture system block diagram;

- FIG. 2 illustrates a prior art static memory cell architecture compatible with the memory array architecture of FIG. 1;

- FIG. 3 illustrates a prior art non-static memory cell architecture compatible with the memory array architecture of FIG. 1;

- FIG. 4 illustrates a generalization of memory cell architectures compatible with the memory array architecture of FIG. 1:

- FIG. 5 illustrates a memory cell abstraction as applied to memory cell architectures of FIG. 2;

- FIG. 6 illustrates a switch abstraction as applied to 25 memory cell architectures of FIG. 2;

- FIG. 7 illustrates a traditional prior art transparent latch memory cell circuit topology;

- FIG. 8 illustrates a traditional prior art D-flip-flop memory cell circuit topology;

FIG. 9 illustrates a prior art memory array depicting interconnection of memory cells with Bit Lines and Word Lines;

- FIG. 10 illustrates a prior art 6T memory cell 5 depicting READ DISTURB behavior;

- FIG. 11 illustrates internal memory cell waveforms of a 6T memory cell undergoing READ DISTURB behavior;

- FIG. 12 illustrates the effect of varying BETA RATIOs within a 6T memory cell undergoing READ DISTURB behavior;

- FIG. 13 illustrates a 1 Bit-Per-Word (BPW) memory cell write cycle with Bit Line 0 written low while all other 511 Bit Lines undergoing READ DISTURB behavior as they are being pulled low as if being read;

- FIG. 14 illustrates a 5T memory cell incorporating single-ended / double-ended VDD switching as taught by U.S. Patent 5,831,896;

- FIG. 15 illustrates a 5T memory cell incorporating single-ended / double-ended VSS switching as taught by U.S. Patent 6,940,746;

- FIG. 16 illustrates 5T memory cell incorporating single-ended VSS switching as taught by U.S. Patent 5,831,896;

- FIG. 17 illustrates an exemplary system block diagram of various preferred subcircuits associated with the present invention:

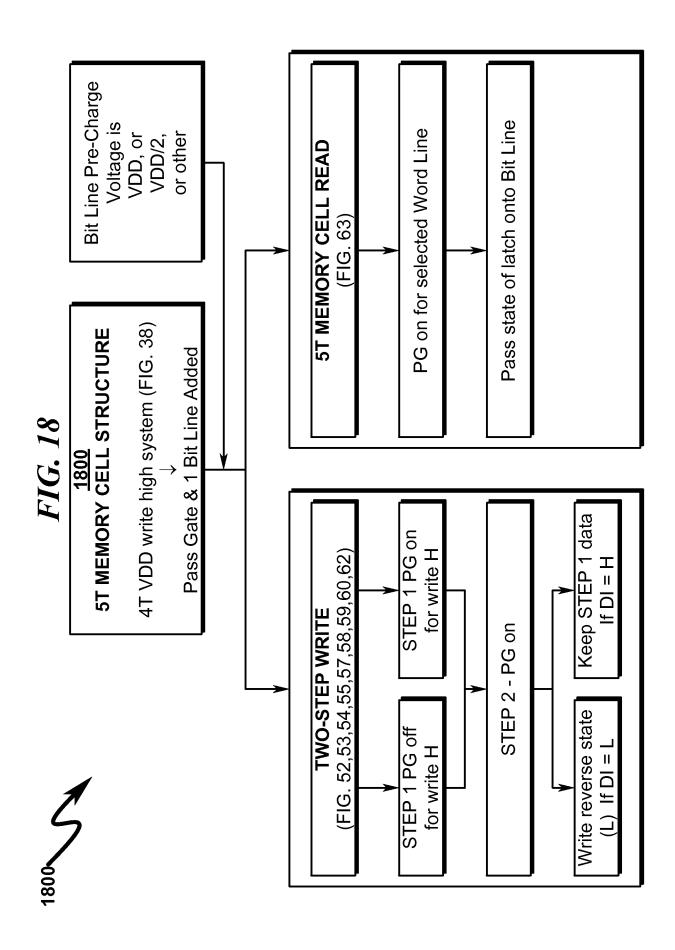

- FIG. 18 illustrates a block diagram of an exemplary 5T memory cell structure useful in some preferred embodiments of the present invention;

FIG. 19 illustrates a block diagram of an exemplary 5T memory cell group useful in some preferred embodiments of the present invention;

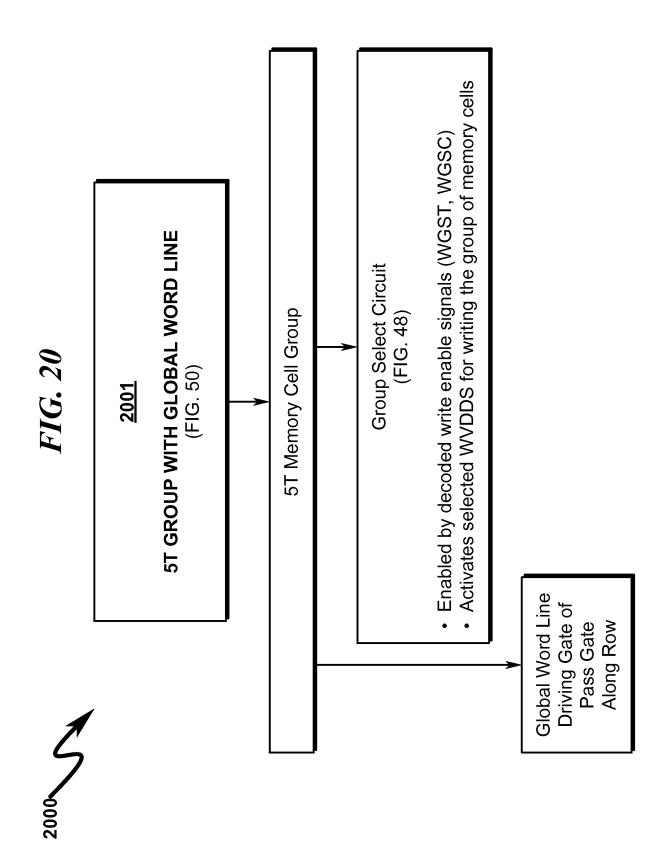

- FIG. 20 illustrates a block diagram of an exemplary 5T group with global word line useful in some preferred embodiments of the present invention;

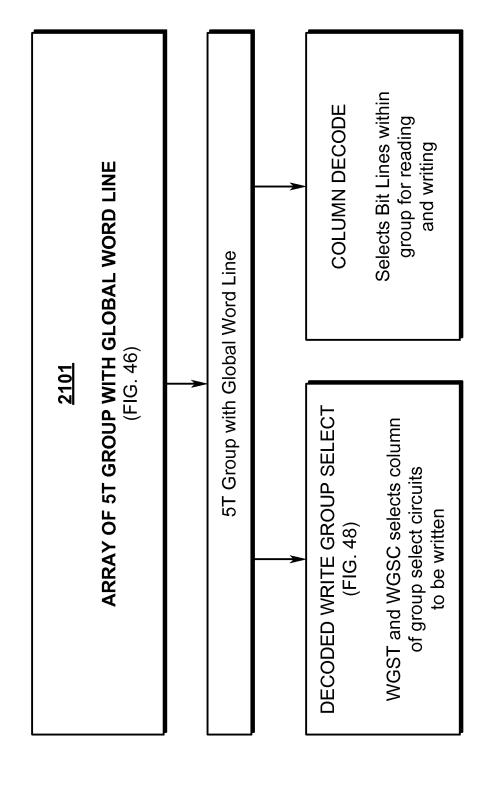

- FIG. 21 illustrates a block diagram of an exemplary array of 5T groups with global word line useful in some preferred embodiments of the present invention;

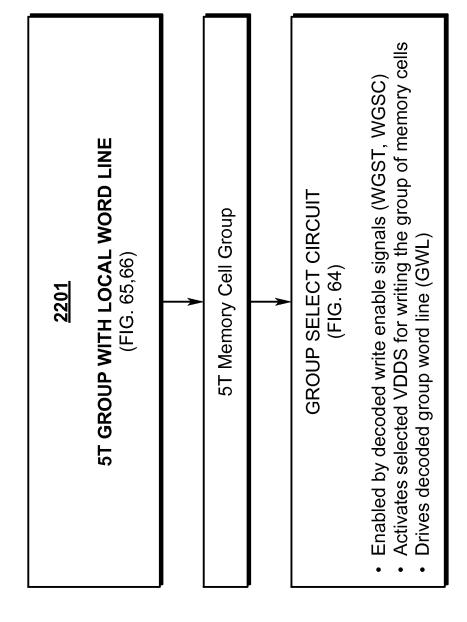

- 10 FIG. 22 illustrates a block diagram of an exemplary 5T group with local word line useful in some preferred embodiments of the present invention;

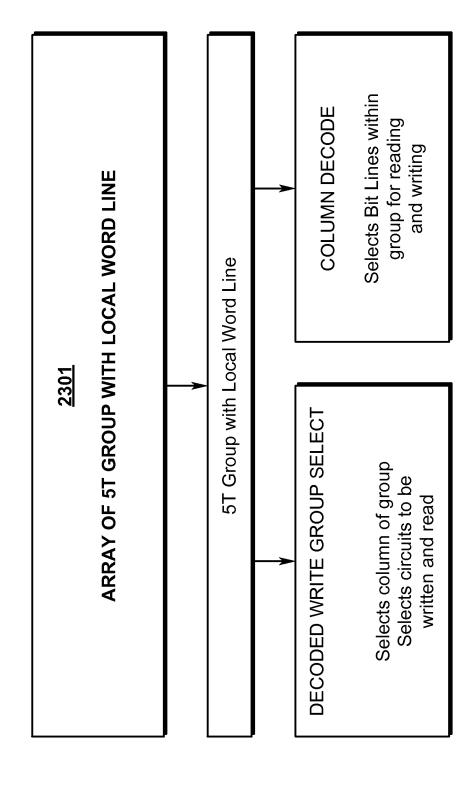

- FIG. 23 illustrates a block diagram of an exemplary array of 5T groups with local word line useful in some preferred embodiments of the present invention;

15

- FIG. 24 illustrates a block diagram of an exemplary array of 5T write and read memory cells without interspersed groups useful in some preferred embodiments of the present invention:

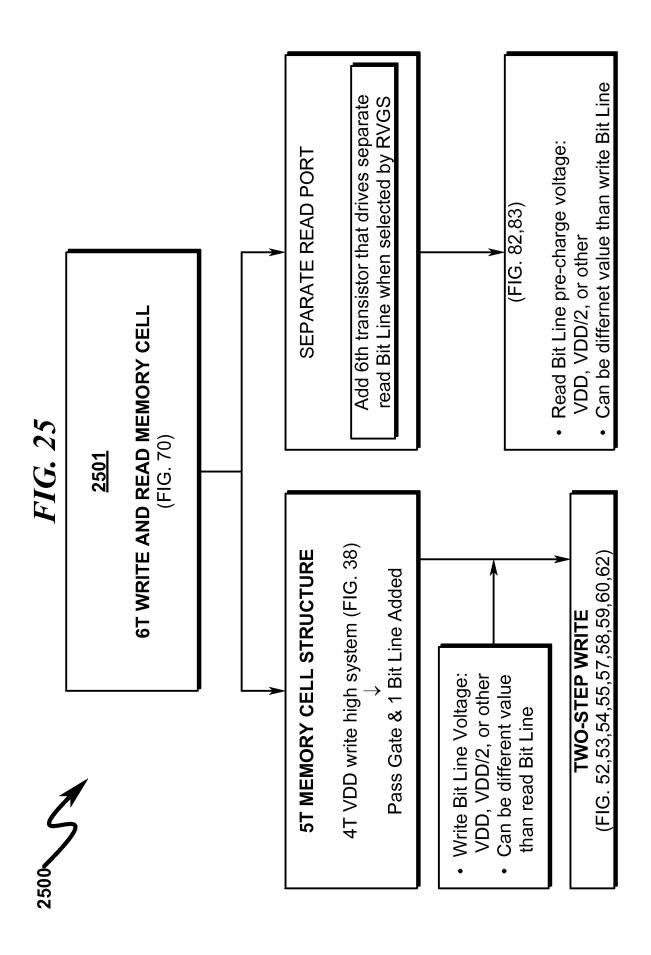

- FIG. 25 illustrates a block diagram of an exemplary 6T write and read memory cell useful in some preferred embodiments of the present invention;

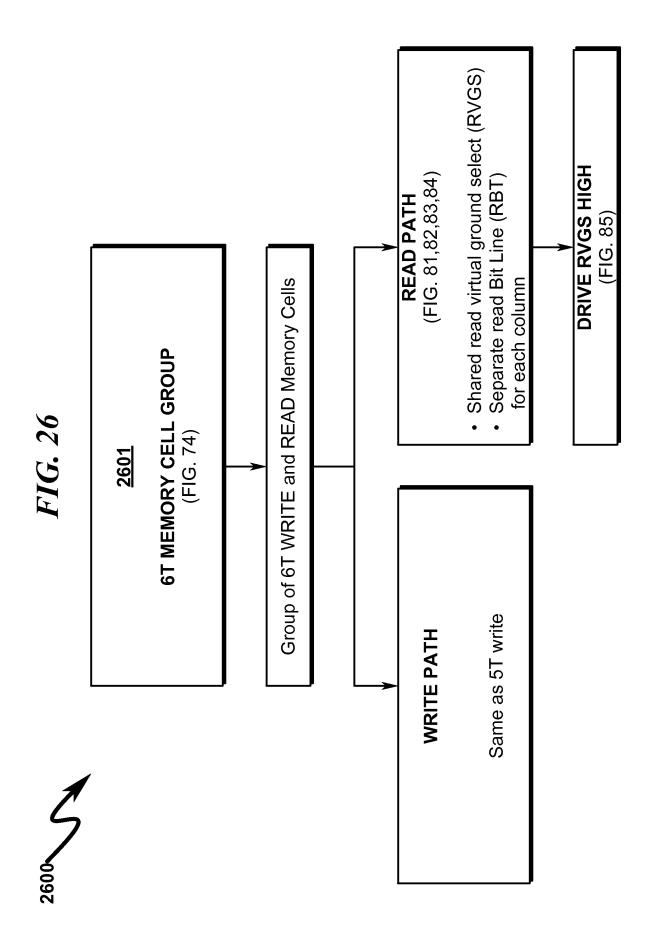

- FIG. 26 illustrates a block diagram of an exemplary 6T memory cell group useful in some preferred embodiments of the present invention;

- FIG. 27 illustrates a block diagram of an exemplary 6T group with global word line useful in some preferred embodiments of the present invention;

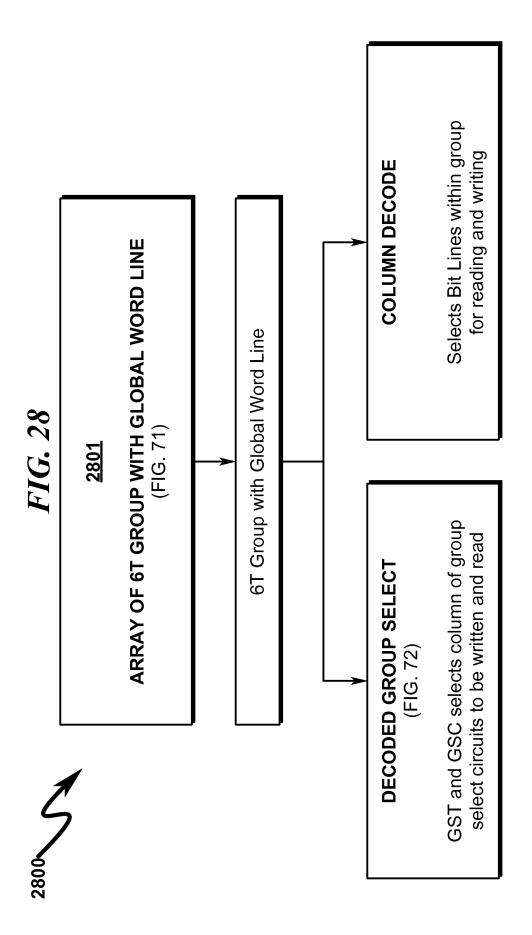

FIG. 28 illustrates a block diagram of an exemplary array of 6T groups with global word line useful in some preferred embodiments of the present invention;

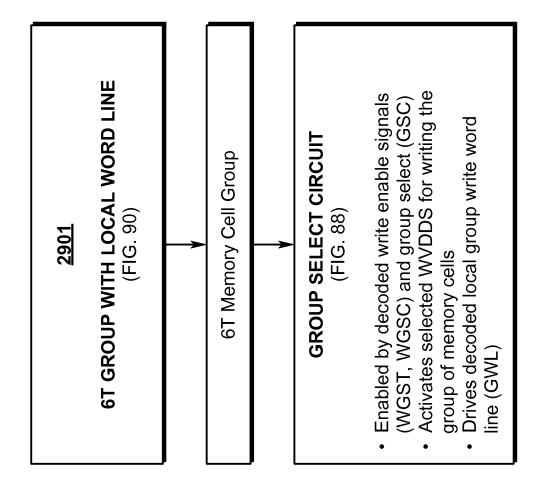

- FIG. 29 illustrates a block diagram of an exemplary 6T group with local word line useful in some preferred embodiments of the present invention;

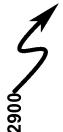

- FIG. 30 illustrates a block diagram of an exemplary array of 6T groups with local word line useful in some preferred embodiments of the present invention;

- 10 FIG. 31 illustrates a block diagram of an exemplary array of 6T write and read memory cells without interspersed groups useful in some preferred embodiments of the present invention;

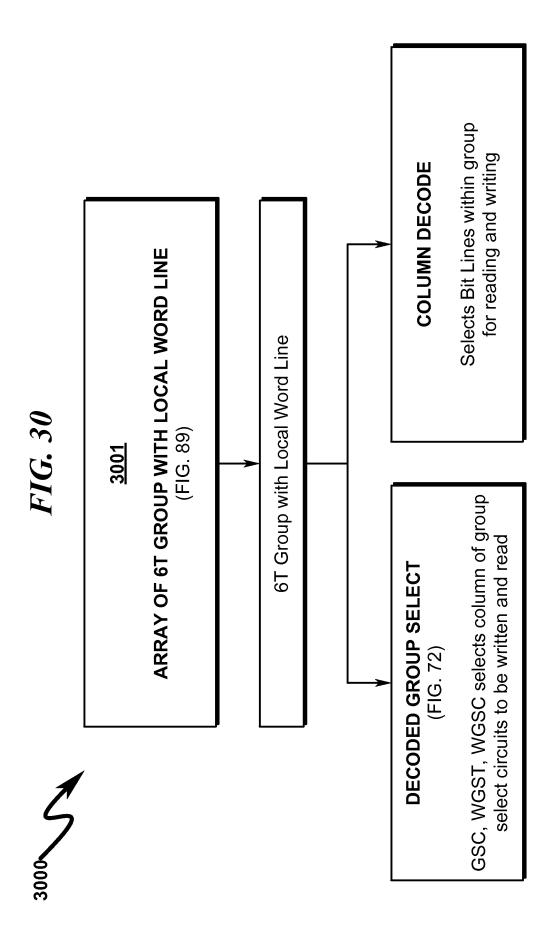

- FIG. 32 illustrates a block diagram of an exemplary 7T memory cell group useful in some preferred embodiments of the present invention;

- FIG. 33 illustrates a block diagram of an exemplary array of 6T dual port based on group with local word line useful in some preferred embodiments of the present invention;

20

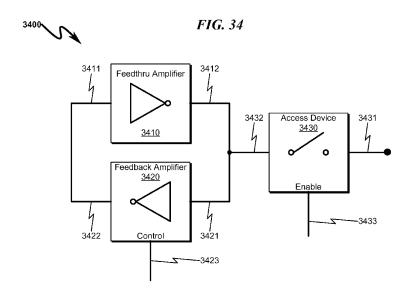

- FIG. 34 illustrates a block diagram of an exemplary high level overview of the memory cell structure used within the present invention;

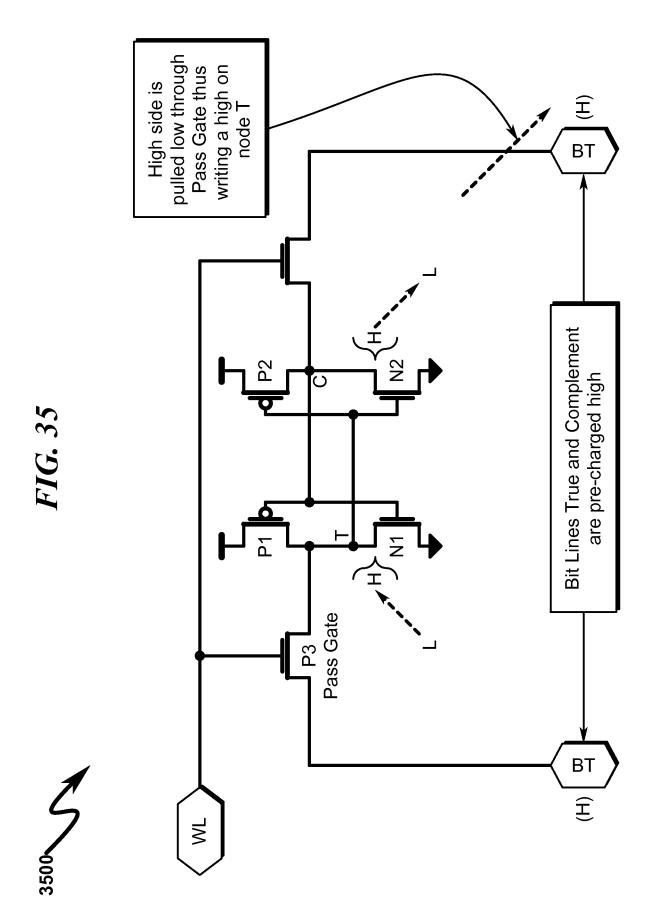

- FIG. 35 illustrates writing a high against a stored low in the traditional 6T memory cell requires access to high side:

- FIG. 36 illustrates an internal cross coupled latch of memory cell and interface circuitry;

- FIG. 37 illustrates driving VDD low forces a high on 30 node T of the latch;

FIG. 38 illustrates a transistor level schematic of the memory latch with a switched VDD configuration;

- FIG. 39 illustrates an embodiment of writing a high against a stored low;

- FIG. 40 illustrates a 5T memory cell utilizing switched VDD with a single pass gate;

- FIG. 41 illustrates driving ground high forces a low on node T of the latch;

- FIG. 42 illustrates a transistor level schematic of latch utilizing switched ground;

- FIG. 43 illustrates 5T SRAM memory cell (bit cell) with single-sided access and switched VDD to second inverter;

- FIG. 44 illustrates writing a high when previous stored state was low;

- FIG. 45 illustrates writing a high when previous stored state was high;

- FIG. 46 illustrates an array of 5T memory cell with global word lines;

- FIG. 47 illustrates group select decoder creates write 20 VDD switch;

- FIG. 48 illustrates transistor implementation of the group select circuit for creating WVDSS;

- FIG. 49 illustrates internal transistors from array in FIG. 46;

- 25 FIG. 50 illustrates schematic of single group of 5T memory cells;

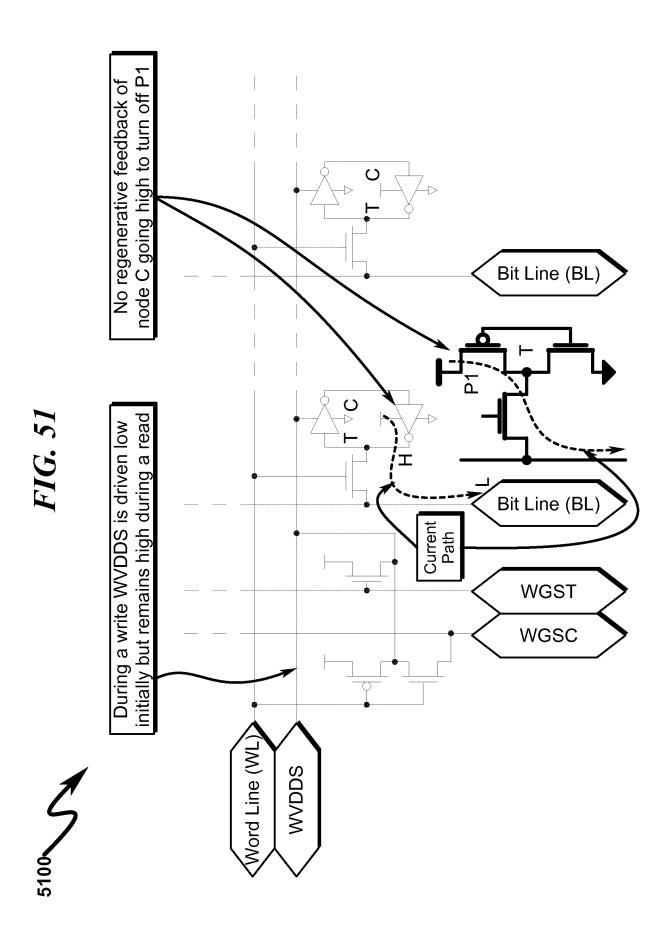

- FIG. 51 illustrates current path if the bit line is driven low while WVDDS is driven low;

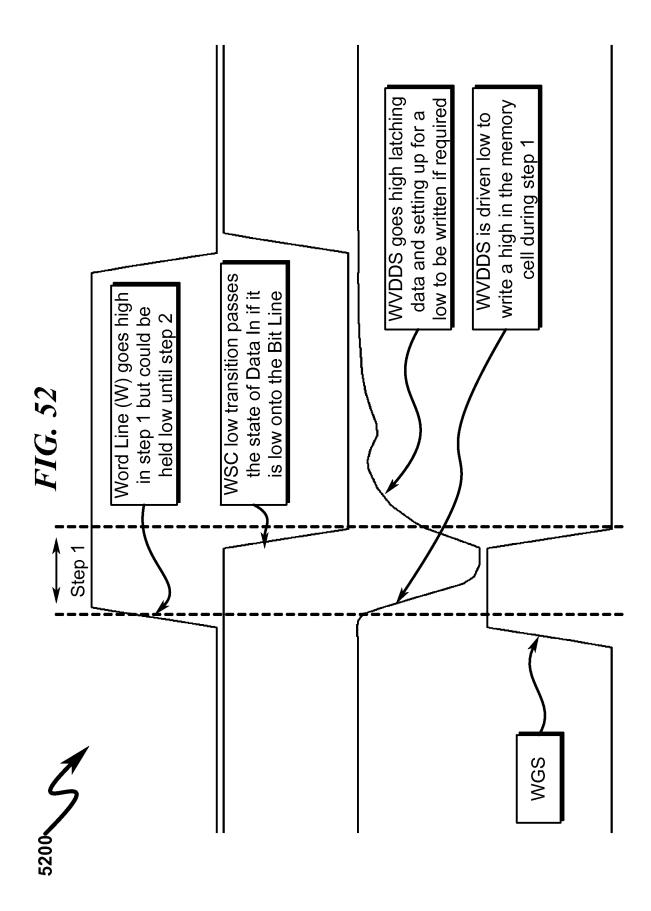

FIG. 52 illustrates waveforms demonstrating a TWO-STEP-WRITE with bit line pre-charged at VDD/2 which is used for a read:

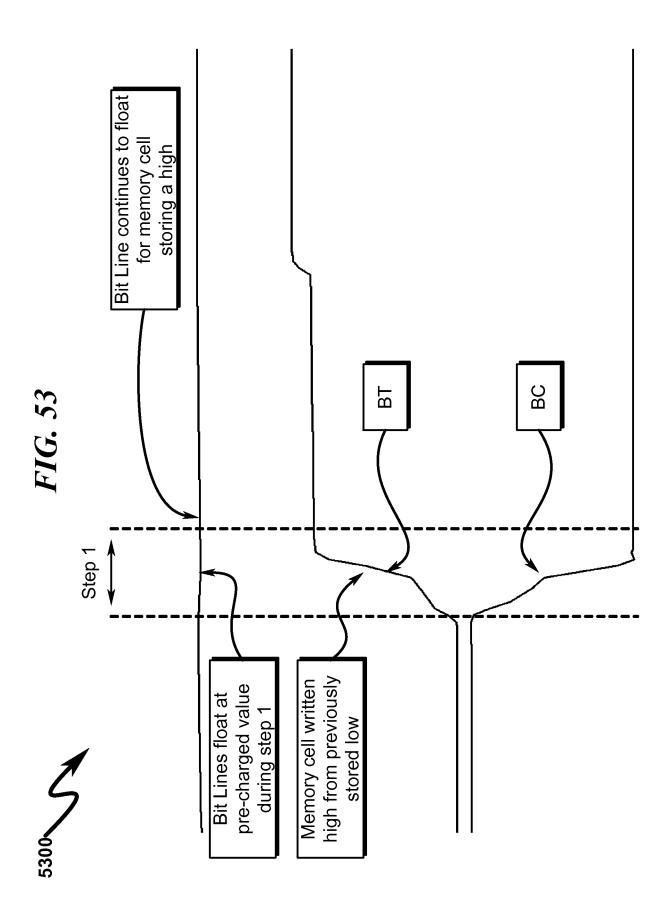

- FIG. 53 illustrates waveforms demonstrating a TWO-STEP-5 WRITE with bit line pre-charged at VDD/2 which is used for a read;

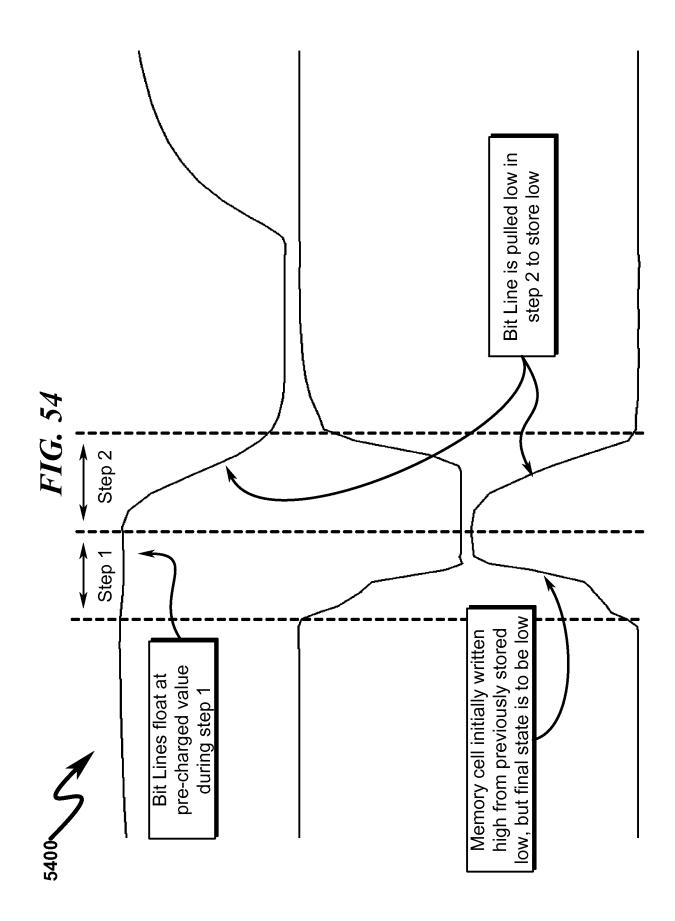

- FIG. 54 illustrates waveforms demonstrating a TWO-STEP-WRITE with bit line pre-charged at VDD/2 which is used for a read;

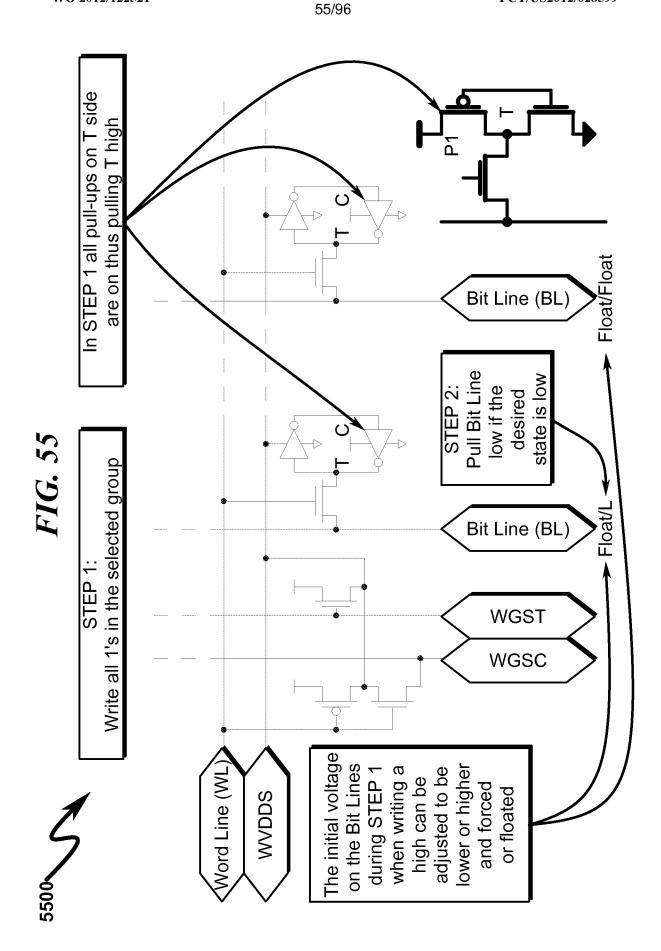

- 10 FIG. 55 illustrates an exemplary schematic circuit diagram of a single group demonstrating a TWO-STEP-WRITE with bit lines pre-charged to VDD/2;

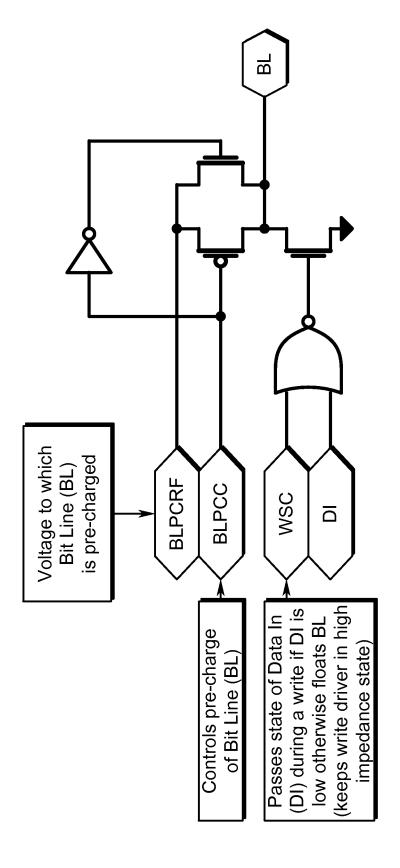

- FIG. 56 illustrates an exemplary schematic circuit diagram that controls pre-charge of bit lines and passing data in (if low) onto bit lines during a write;

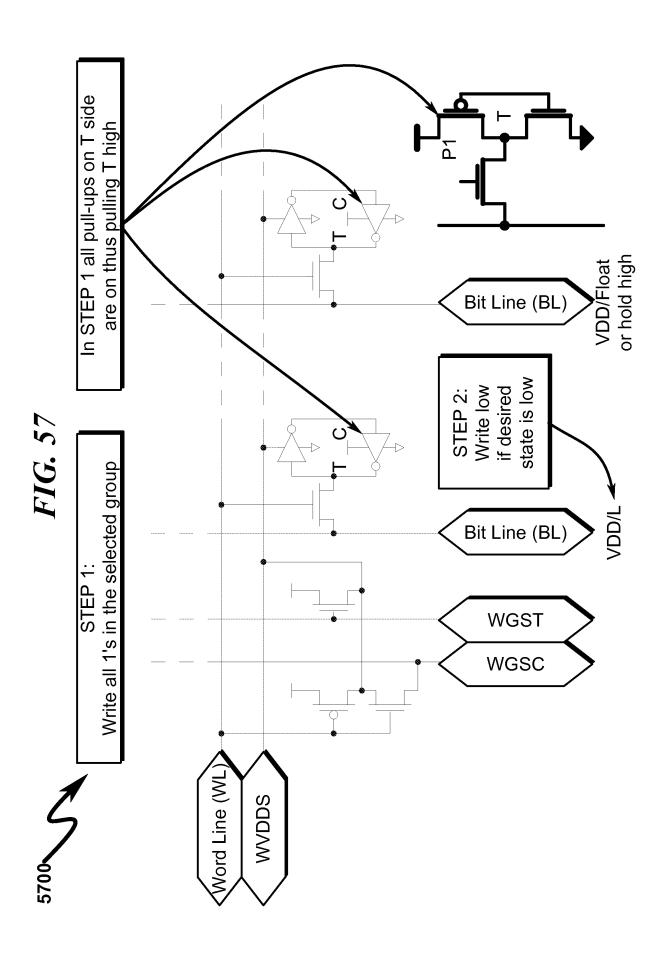

- FIG. 57 illustrates an exemplary schematic circuit diagram of a single group demonstrating a TWO-STEP-WRITE with bit lines held at VDD during step 1

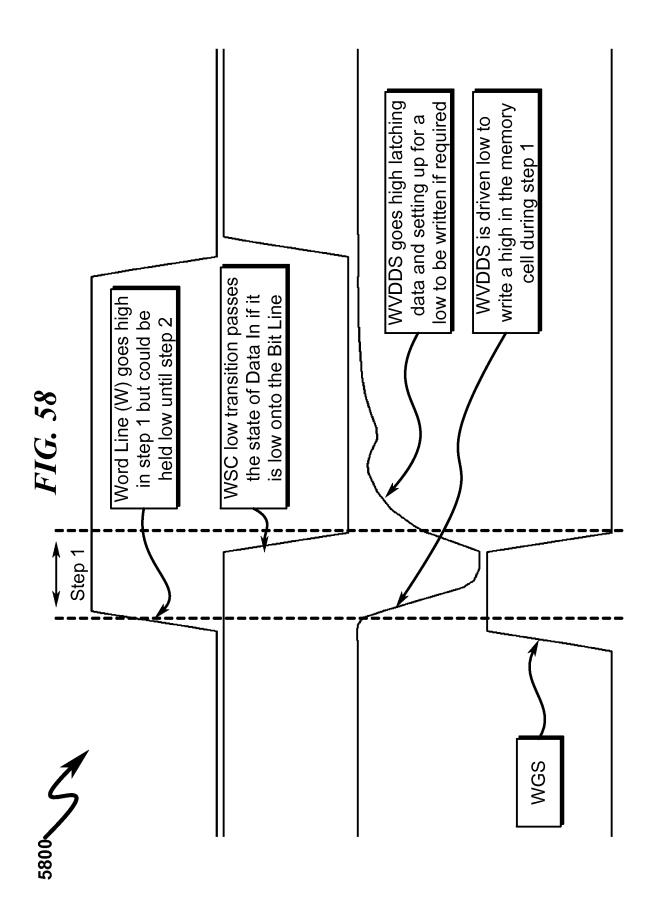

- FIG. 58 illustrates waveforms demonstrating a TWO-STEP-20 WRITE with bit line held at VDD during step 1 of writing a high;

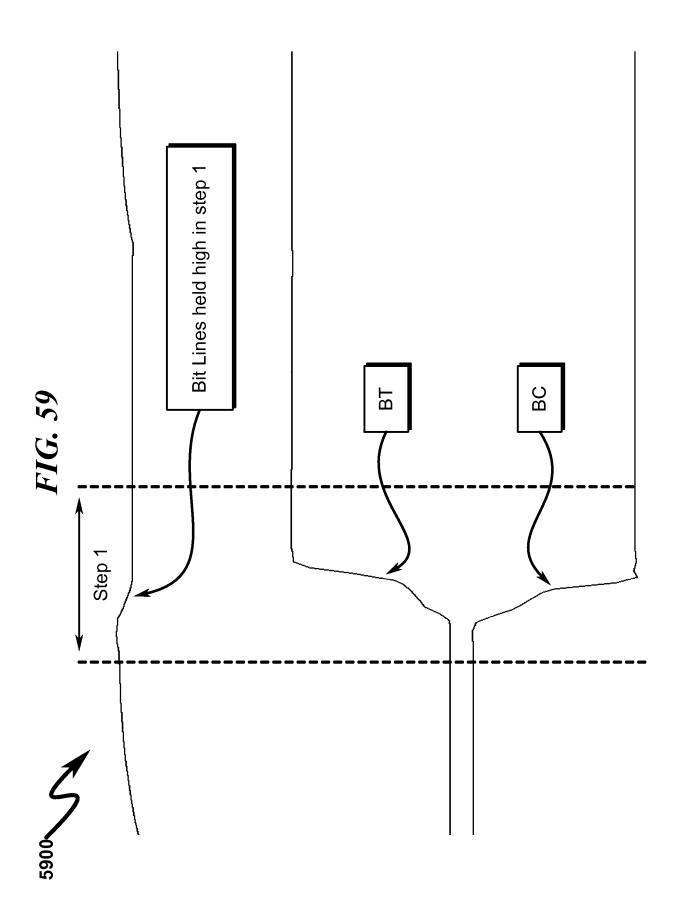

- FIG. 59 illustrates waveforms demonstrating a TWO-STEP-WRITE with bit line held at VDD during step 1 of writing a high;

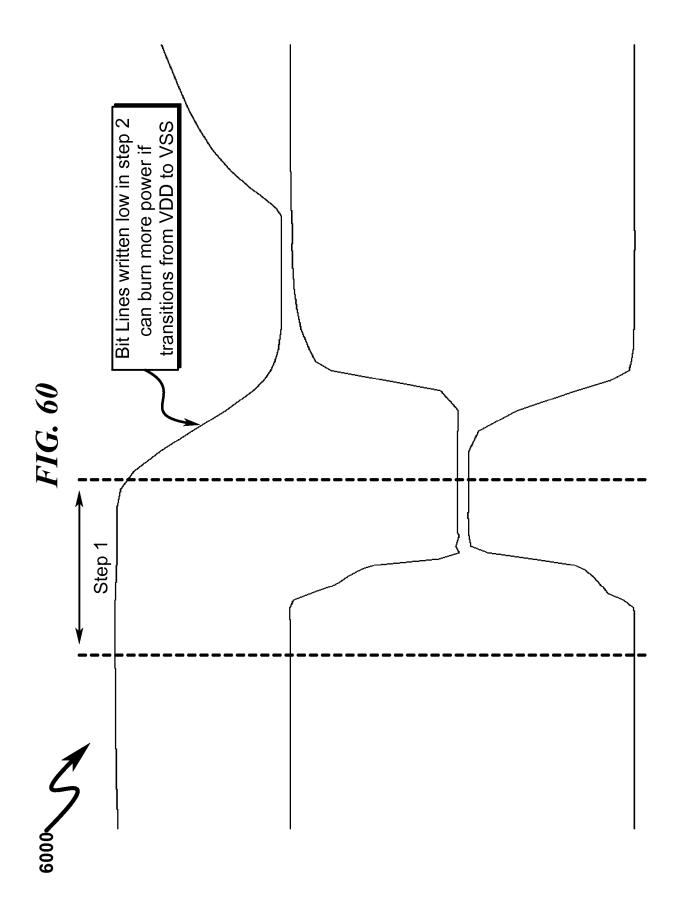

- FIG. 60 illustrates waveforms demonstrating a TWO-STEP-WRITE with bit line held at VDD during step 1 of writing a high;

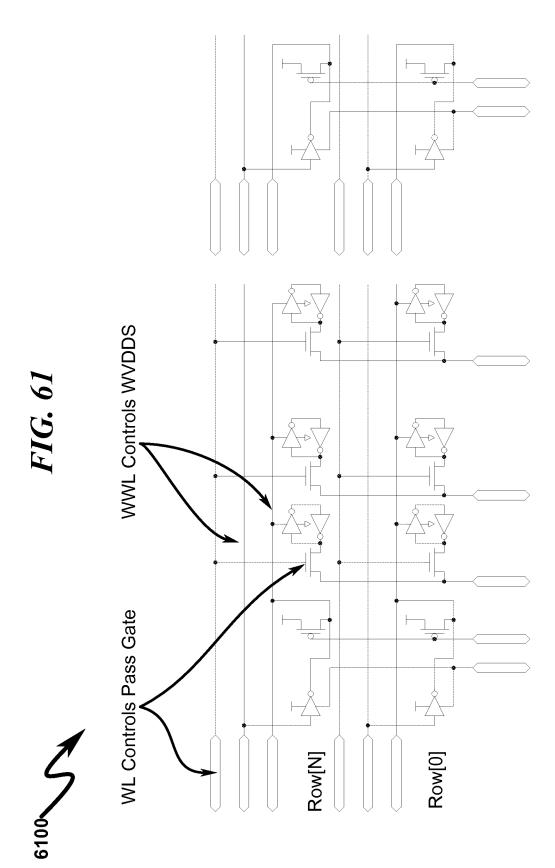

- FIG. 61 illustrates an exemplary schematic circuit diagram embodiment with separate word line control for pass 30 gate;

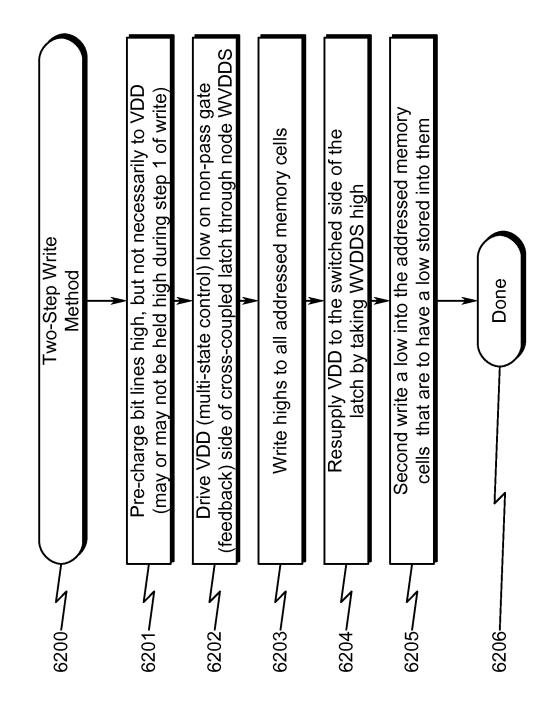

FIG. 62 illustrates an exemplary method flowchart detailing a TWO-STEP-WRITE for writing the 5T memory cell;

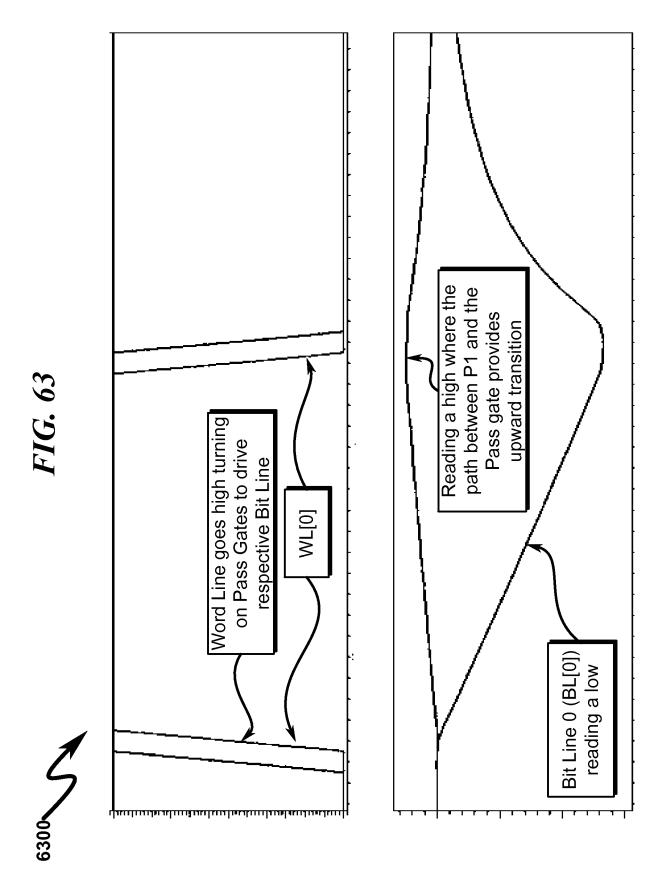

- FIG. 63 illustrates signal waveforms associated with a one-sided read of a bit line that is pre-charged to VDD/2;

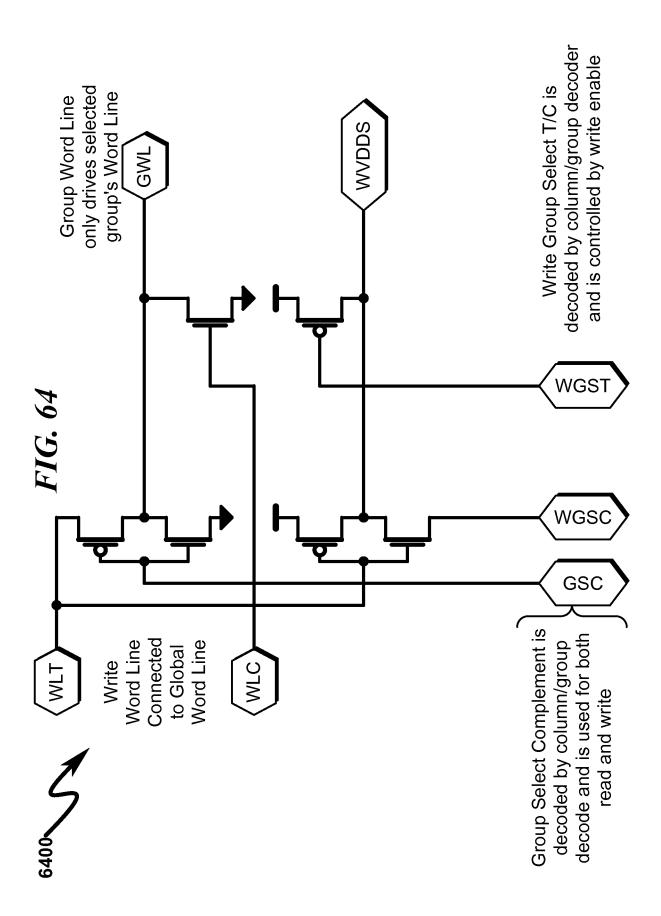

- FIG. 64 illustrates an exemplary schematic circuit diagram of a group select circuit used in group word line embodiment;

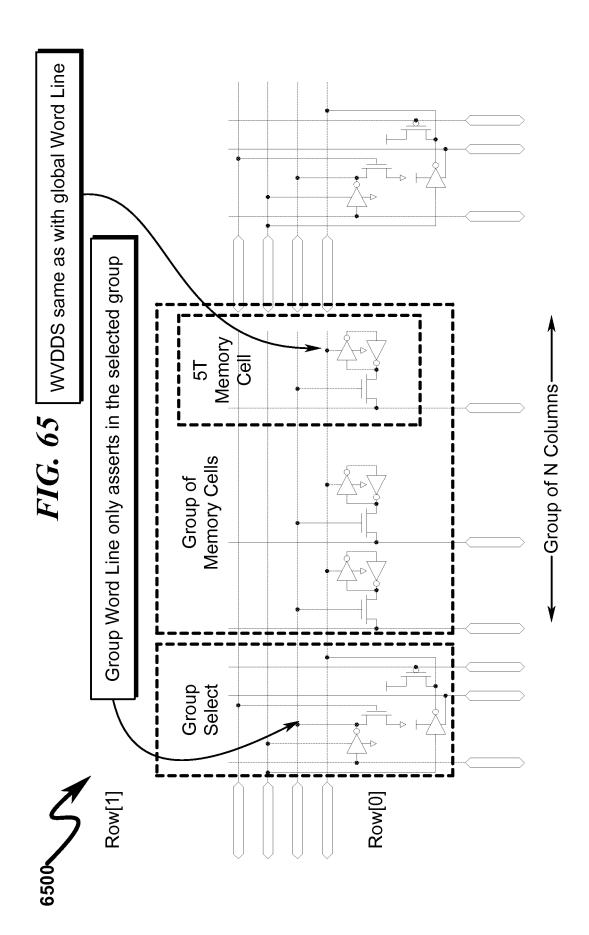

- FIG. 65 illustrates an exemplary schematic circuit diagram of a transistor level 5T array with local group word lines accessing a single group of memory cells;

10

15

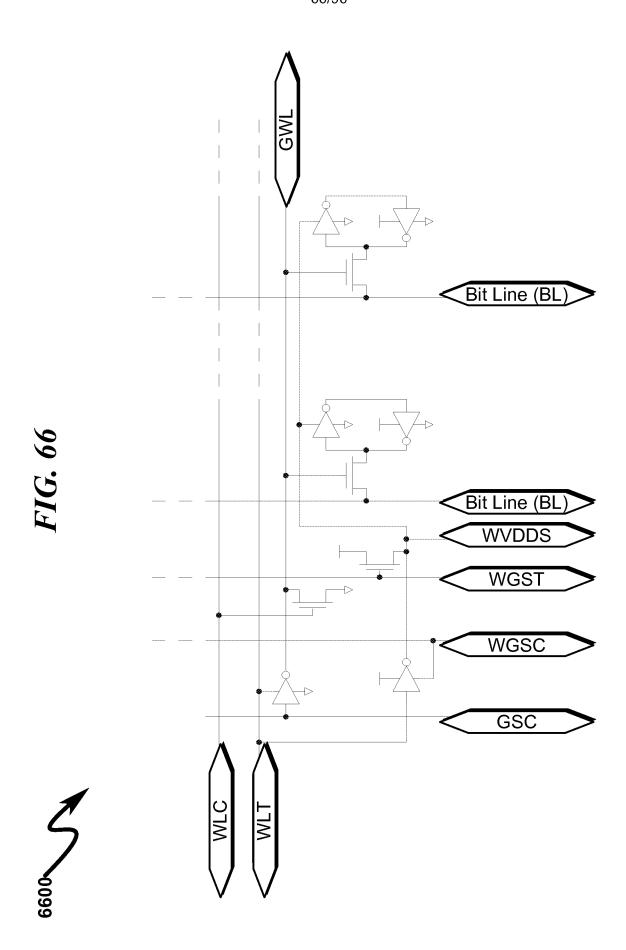

- FIG. 66 illustrates an exemplary schematic circuit diagram of a single group with local group word line;

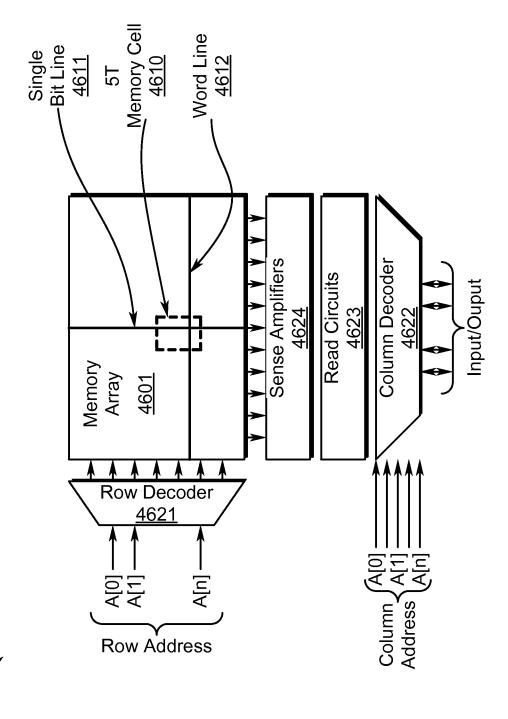

- FIG. 67 illustrates a general block diagram of a single port SRAM utilizing the 5T memory cell with single bit line per memory cell;

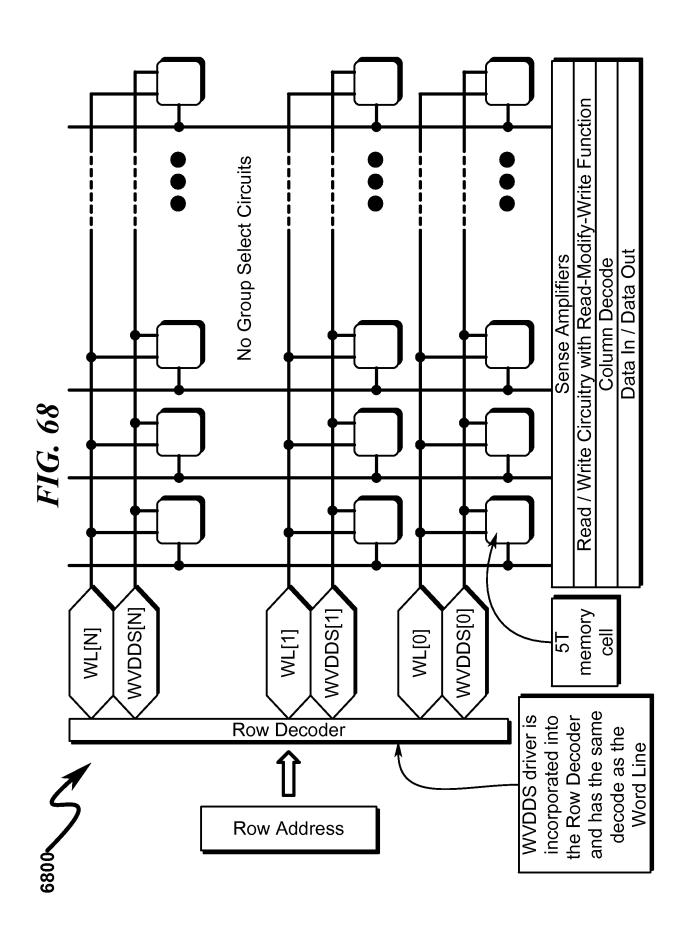

- FIG. 68 illustrates a block diagram of single memory array without group select interspersed;

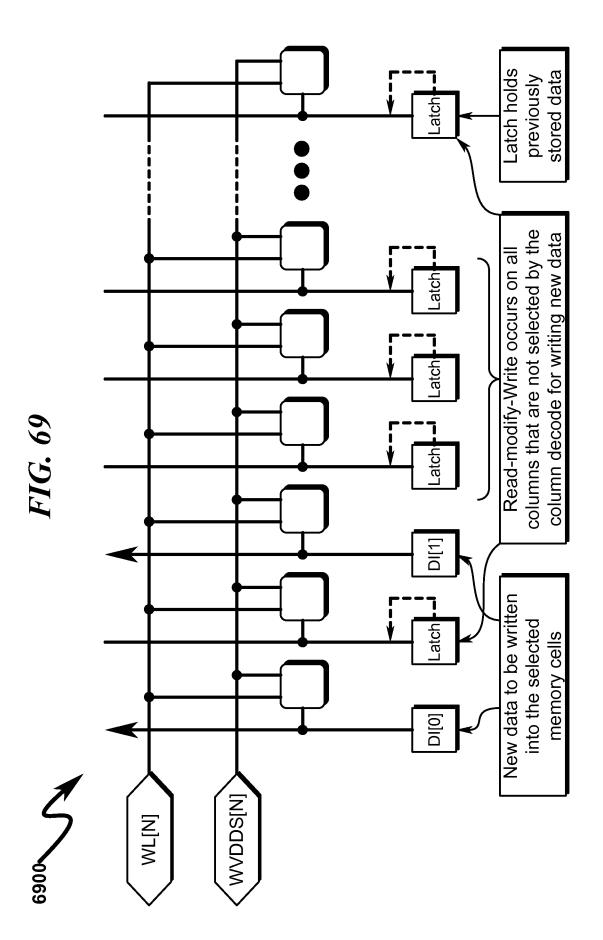

- FIG. 69 illustrates example of read-modify-write for a two BPW configuration;

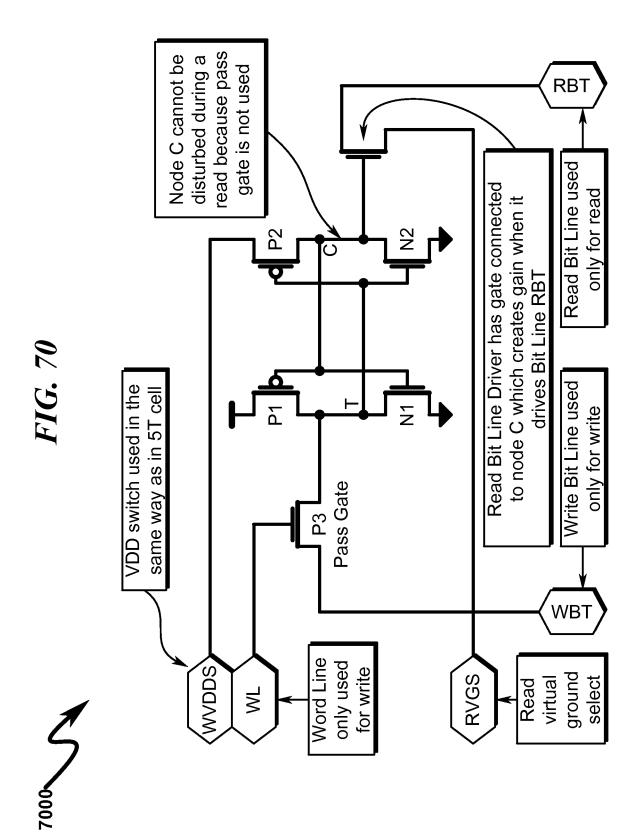

- FIG. 70 illustrates a 6T DFM SRAM memory cell with separate single-sided read and write ports;

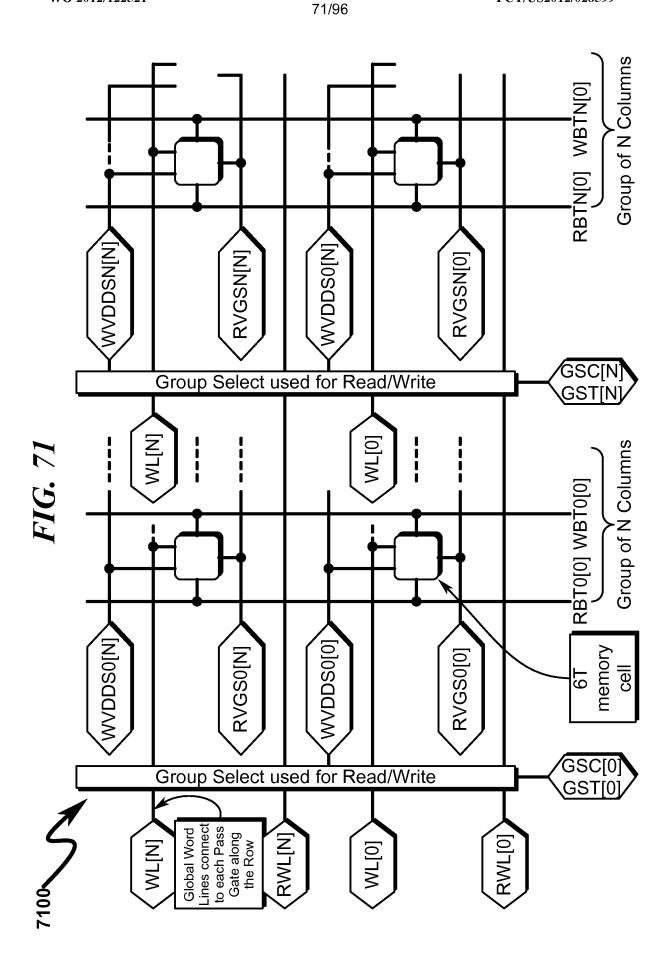

- FIG. 71 illustrates an exemplary array of 6T DFM memory cells with global word lines;

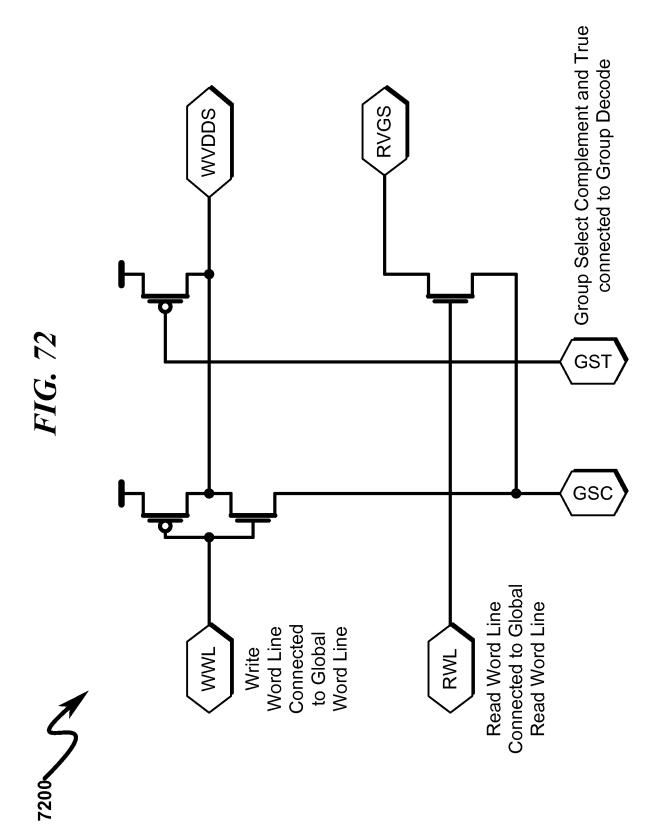

- FIG. 72 illustrates an exemplary schematic circuit diagram of a group select circuit that creates write VDD switch and read virtual ground select;

- FIG. 73 illustrates internal transistors from array in FIG. 71;

- FIG. 74 illustrates Single Group of 6T DFM Memory 30 Cells;

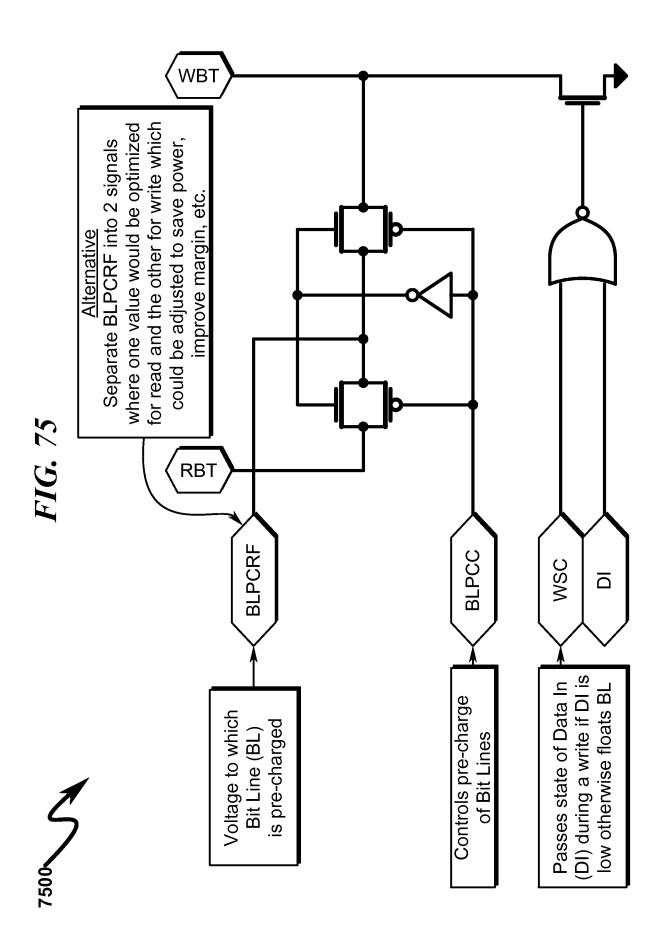

FIG. 75 illustrates circuit that controls pre-charge of bit lines and passing data in (if low) onto bit lines during a write;

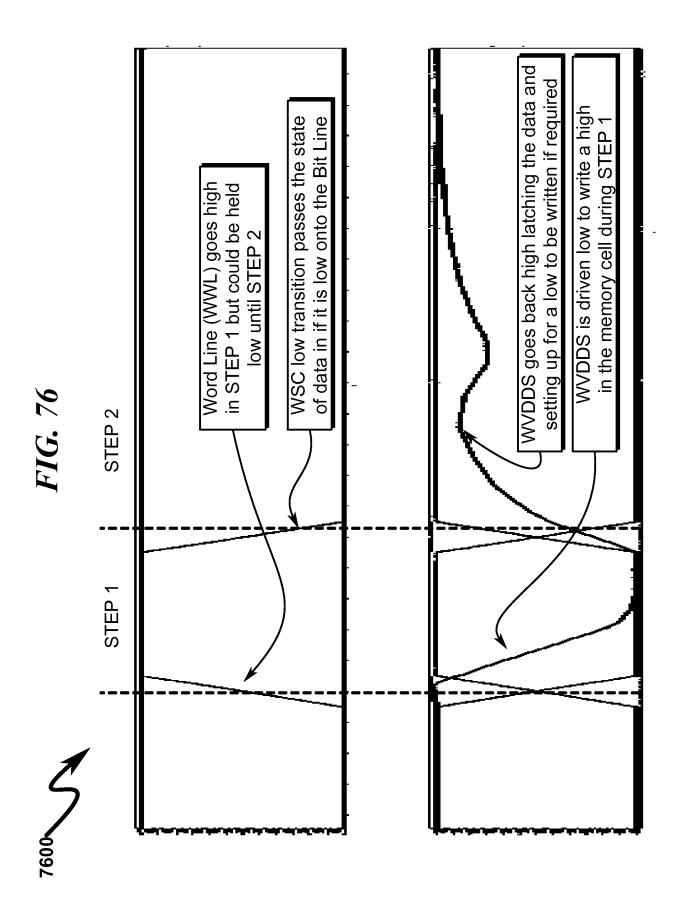

- FIG. 76 illustrates exemplary TWO-STEP MULTI-WRITE 5 signal waveforms and timing;

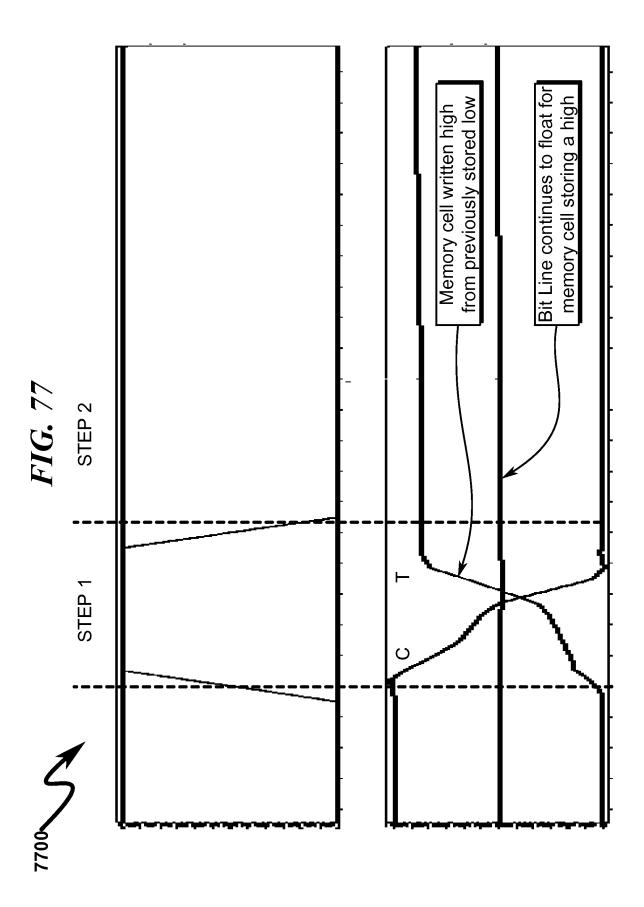

- FIG. 77 illustrates exemplary TWO-STEP MULTI-WRITE signal waveforms and timing;

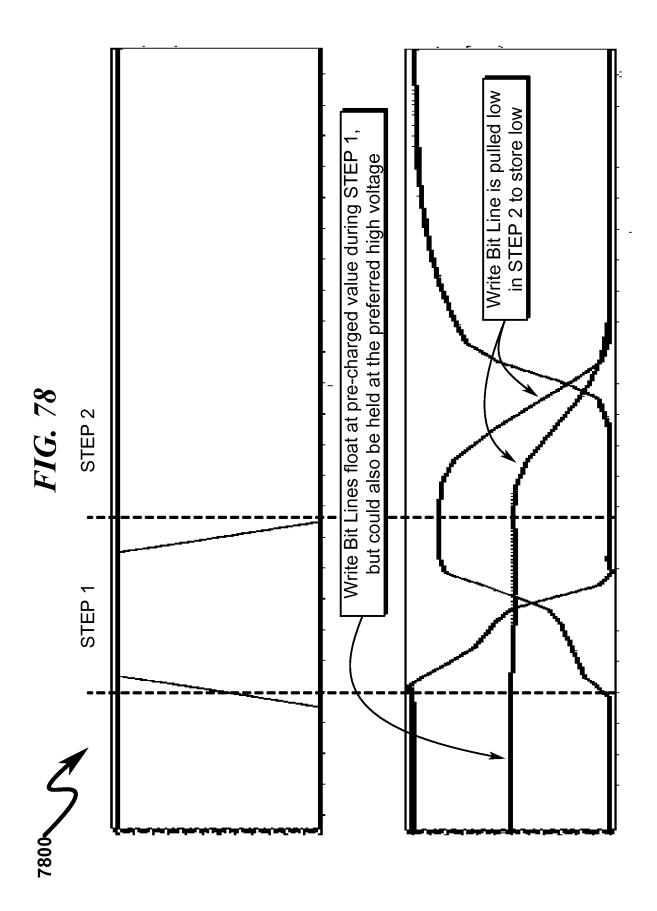

- FIG. 78 illustrates exemplary TWO-STEP MULTI-WRITE signal waveforms and timing;

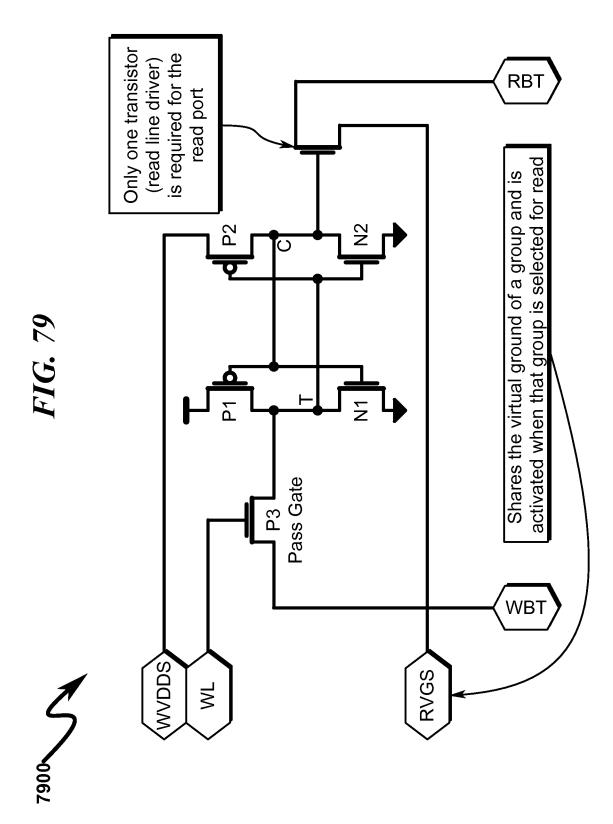

- 10 FIG. 79 illustrates an exemplary schematic circuit diagram of a 6T DFM memory cell read port embodiment;

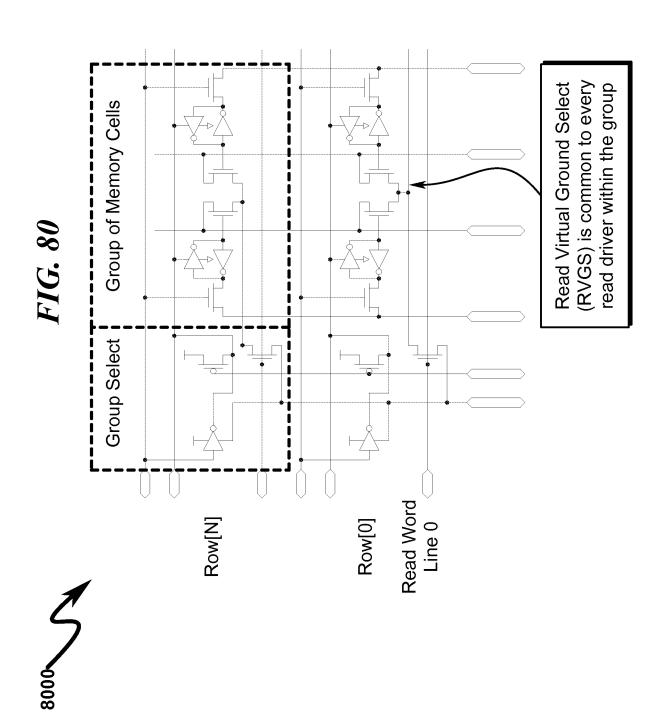

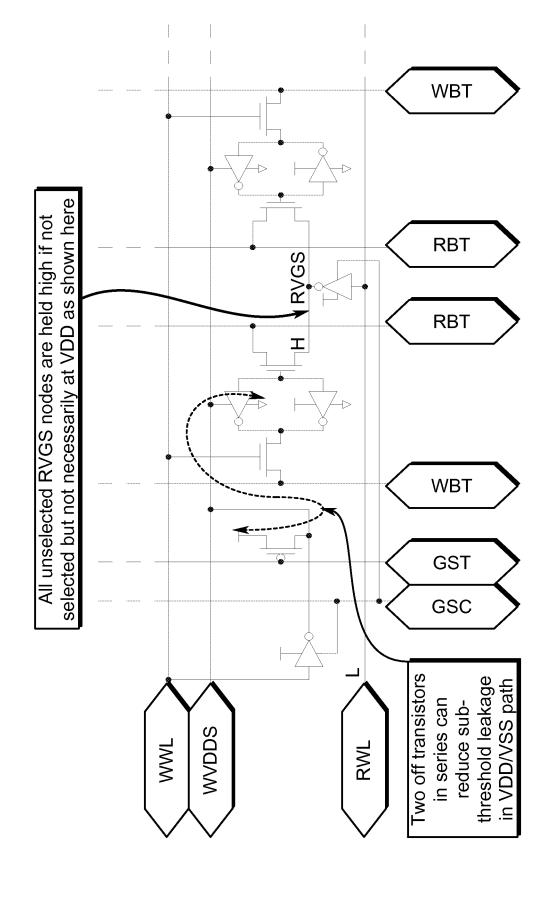

- FIG. 80 illustrates an exemplary schematic circuit diagram of a read virtual ground select (RVGS) implementation;

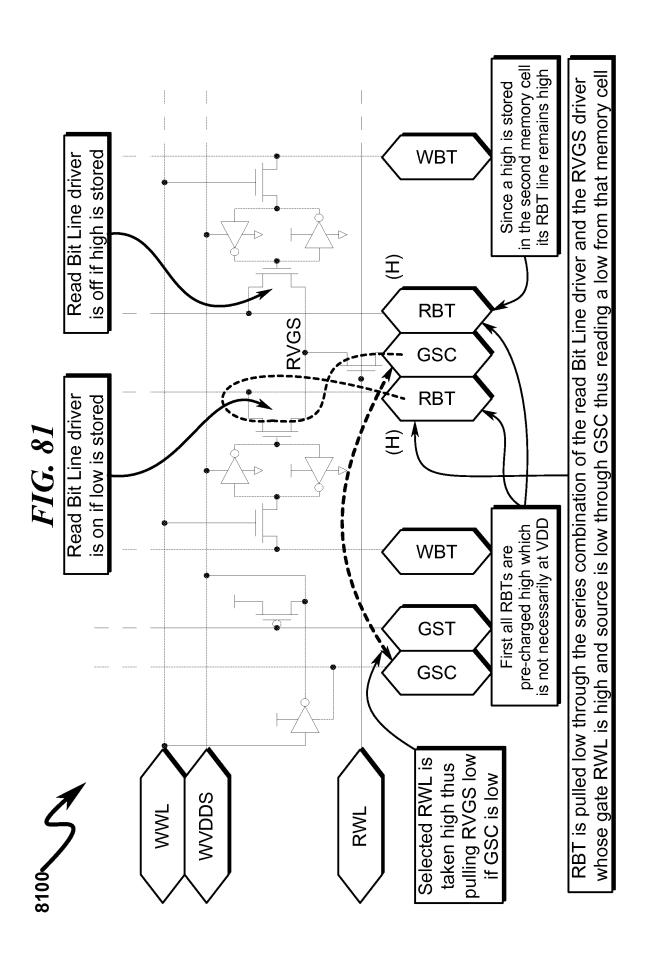

- FIG. 81 illustrates reading a low from the first memory cell and a high from the second memory cell within the selected group;

- FIG. 82 illustrates an exemplary signal timing diagram of reading a low and a high where the value of high is VDD;

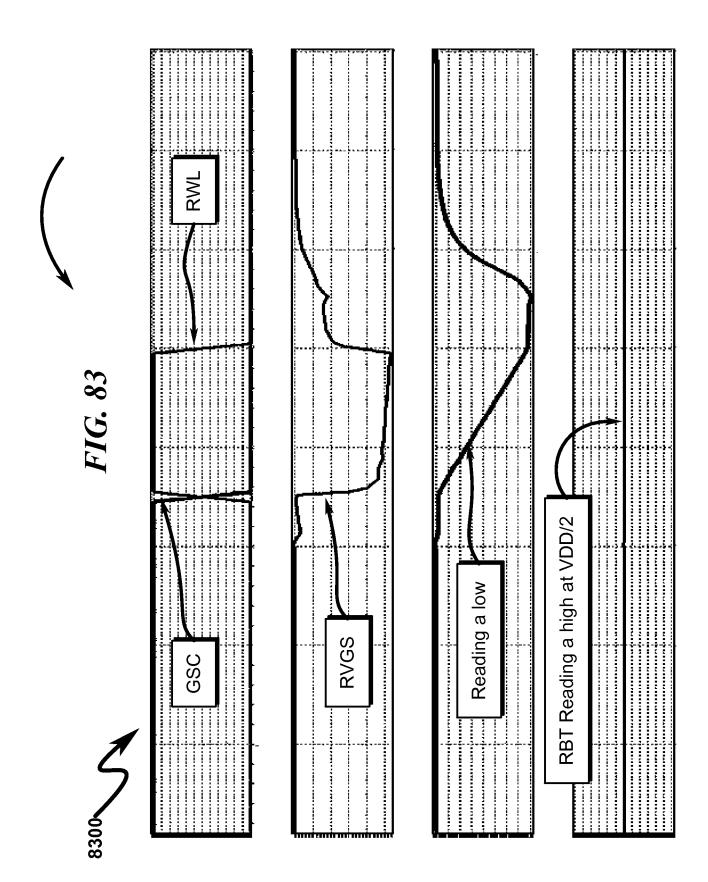

- FIG. 83 illustrates an exemplary signal timing diagram of reading a low and a high where the value of high is VDD/2;

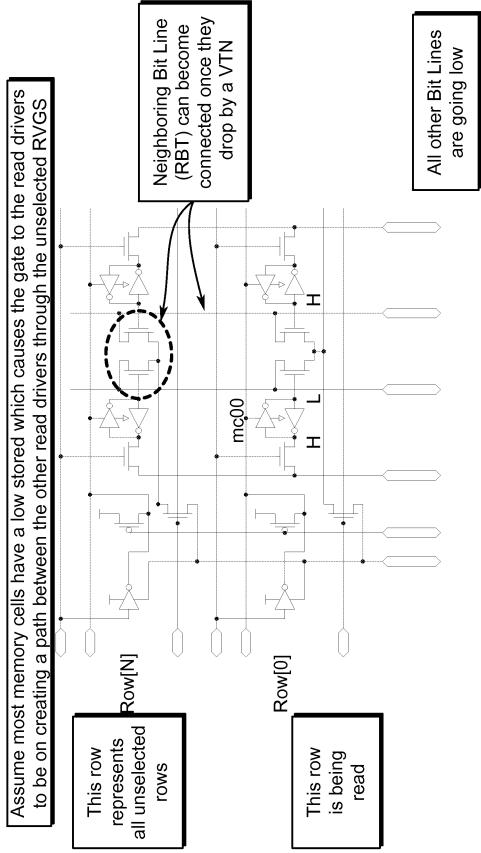

- FIG. 84 illustrates clamping path through other read drivers on other rows but on same columns within group;

- 25 FIG. 85 illustrates P-channel pull-up added to RVGS driver to hold RVGS high when unselected;

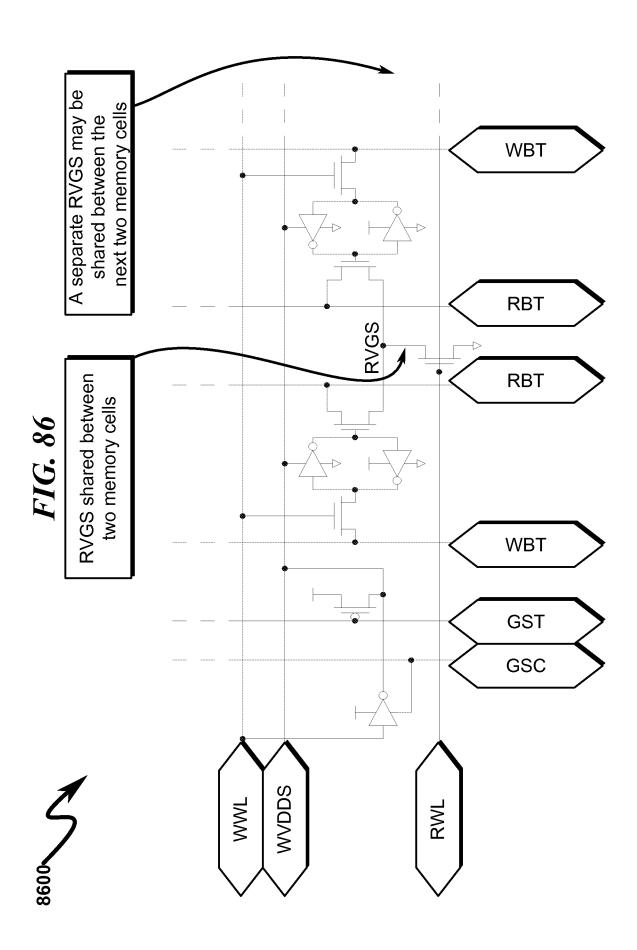

- FIG. 86 illustrates an exemplary schematic circuit diagram of a single group showing a variation of how RVGS is shared with only two neighboring memory cells;

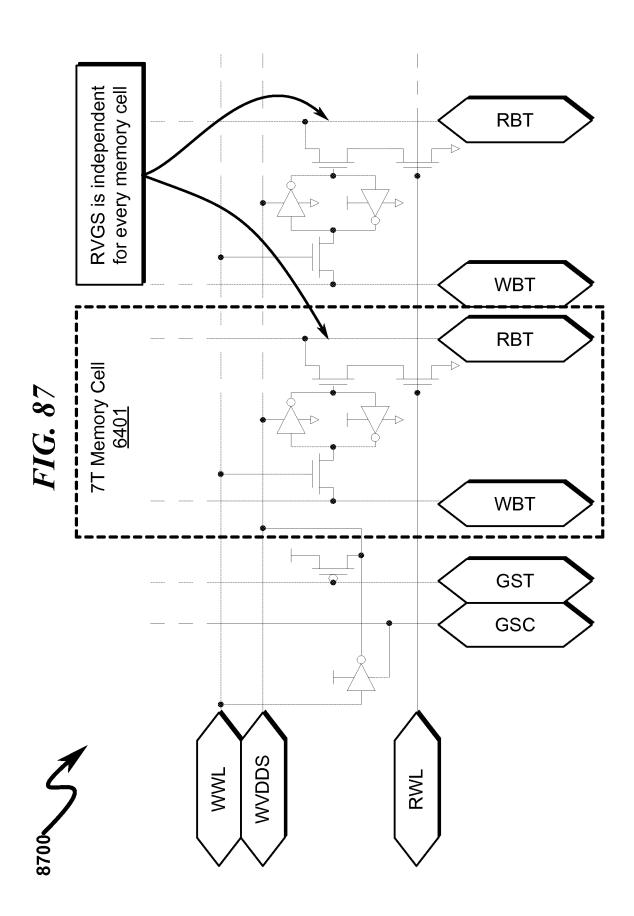

FIG. 87 illustrates an exemplary schematic circuit diagram of a group of 7T memory cells where the RVGS driver is not shared but is included in every memory cell;

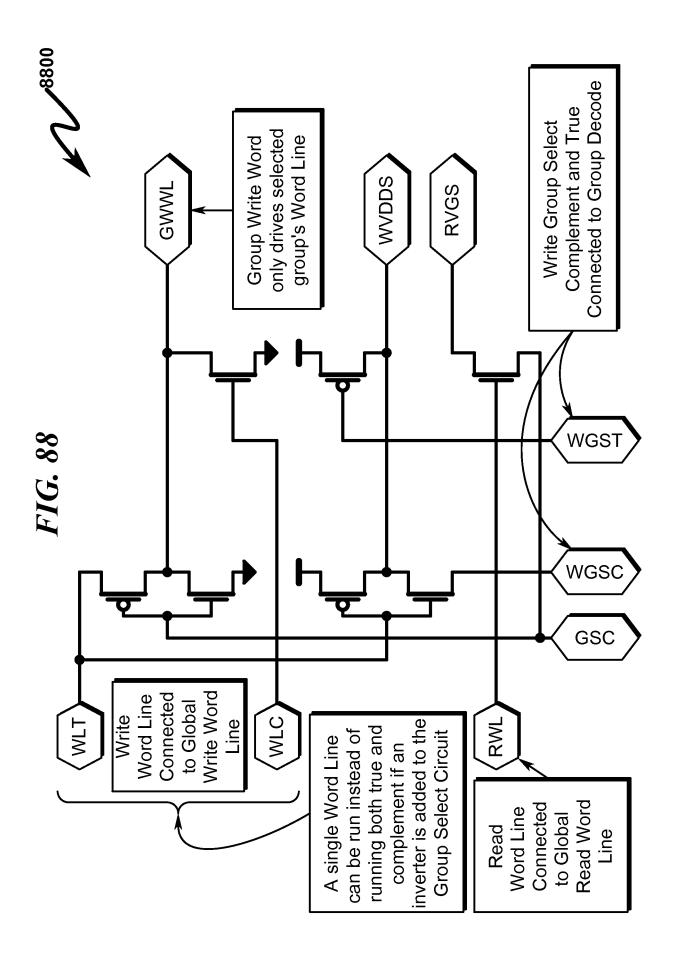

- FIG. 88 illustrates an exemplary schematic circuit diagram depicting an exemplary group select decoder creating a group write word line, VDD select, and read virtual ground select;

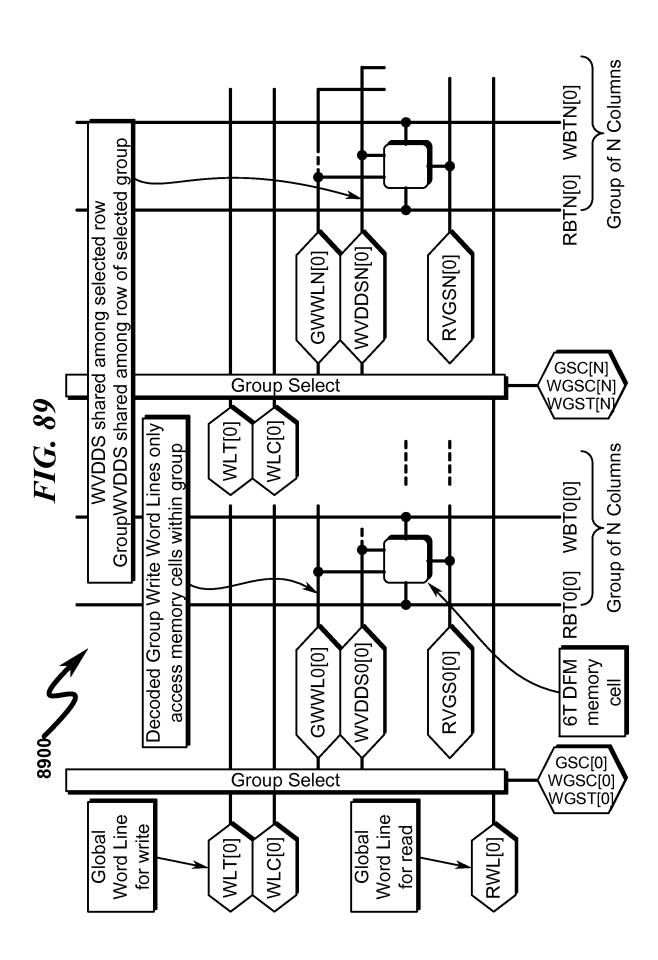

- FIG. 89 illustrates array of 6T DFM memory cells with decoded group word lines accessing a group of memory cells;

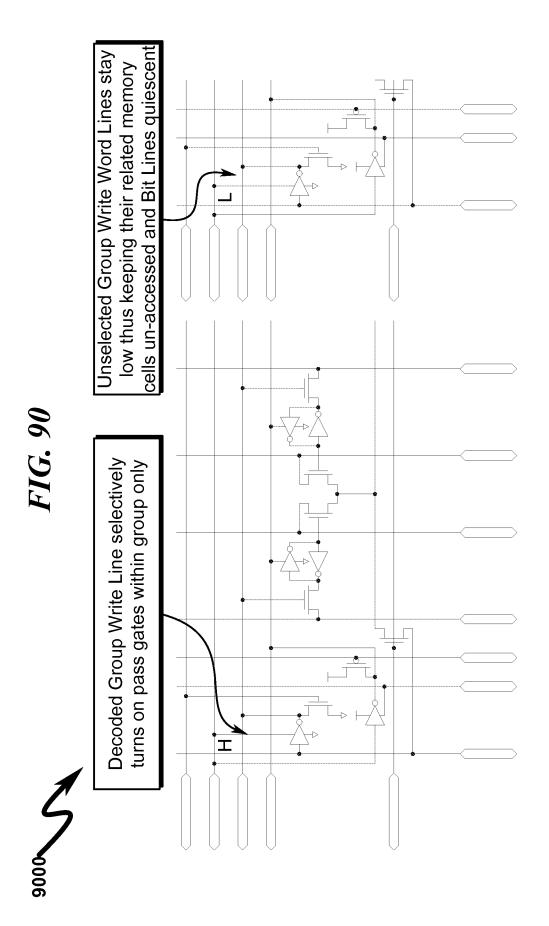

- 10 FIG. 90 illustrates an exemplary transistor level schematic circuit diagram of a group write word line approach;

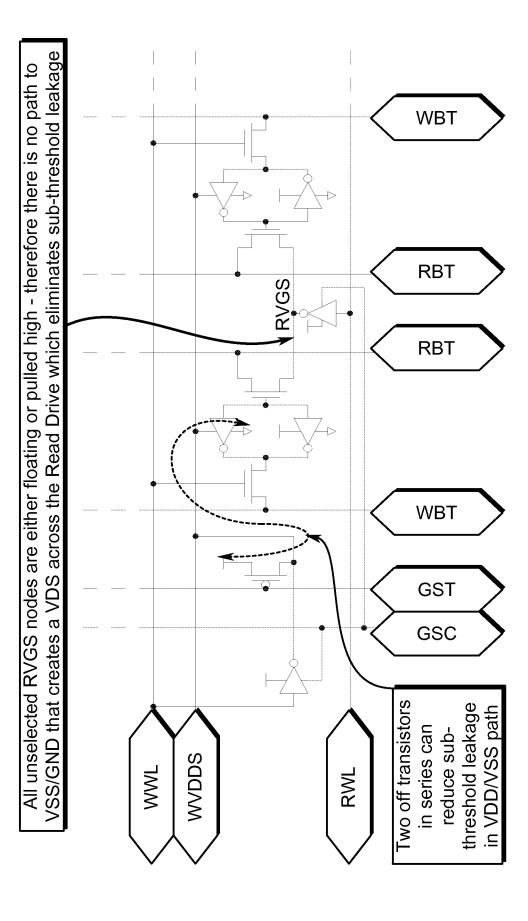

- FIG. 91 illustrates example of reduction of subthreshold conduction leakage of unelected groups;

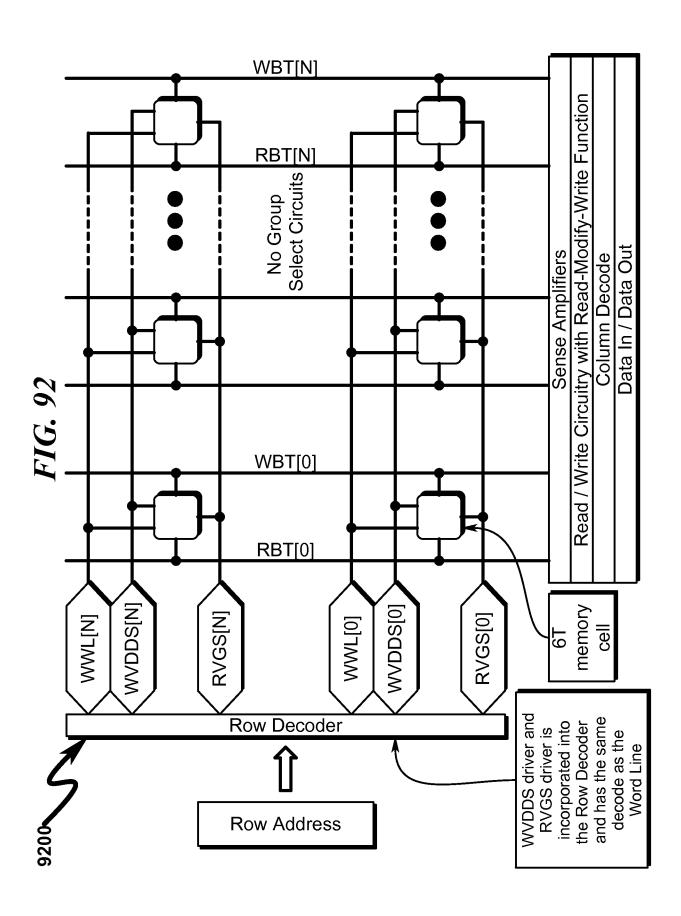

- 15 FIG. 92 illustrates block diagram of single array without group select circuit interspersed;

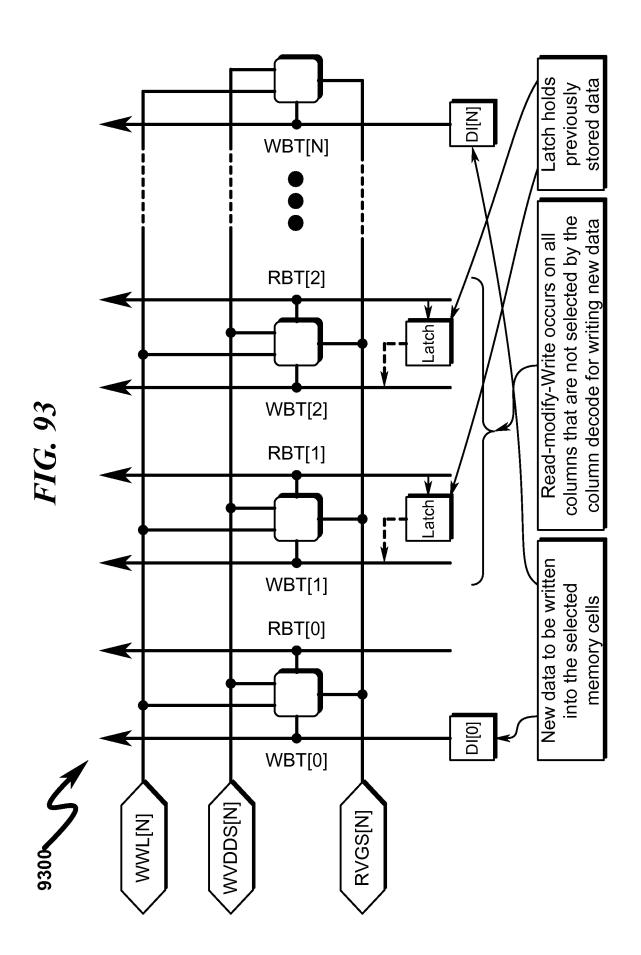

- FIG. 93 illustrates example of read-modify-write for a two BPW configuration;

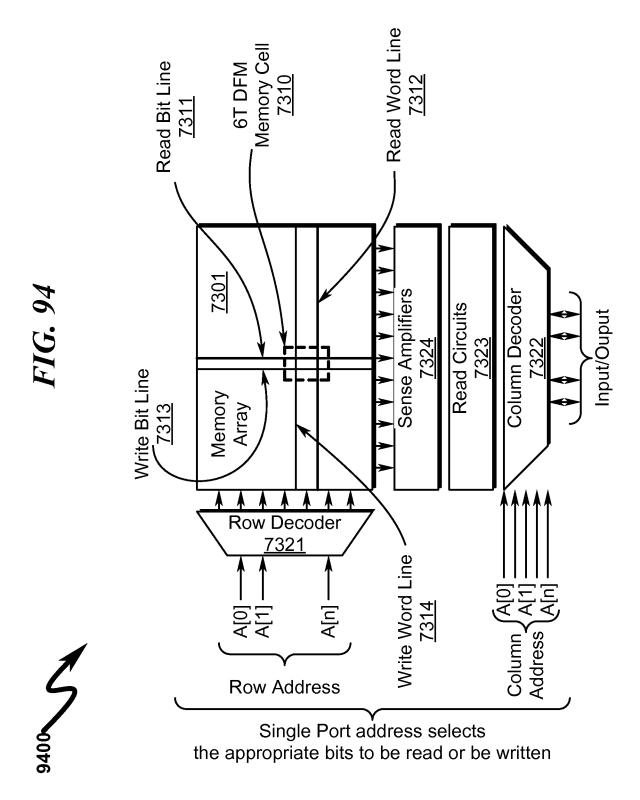

- FIG. 94 illustrates block diagram of a 6T DFM single 20 port SRAM;

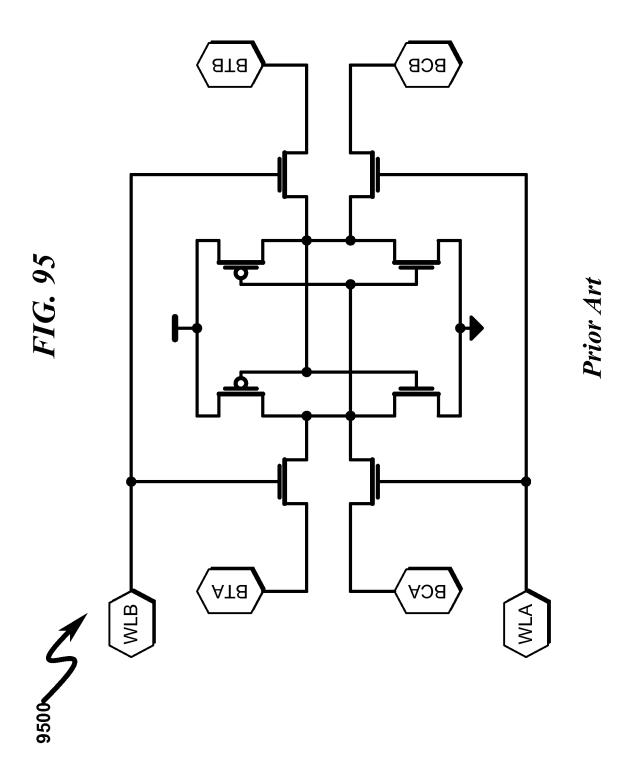

- FIG. 95 illustrates conventional 8T dual port memory cell;

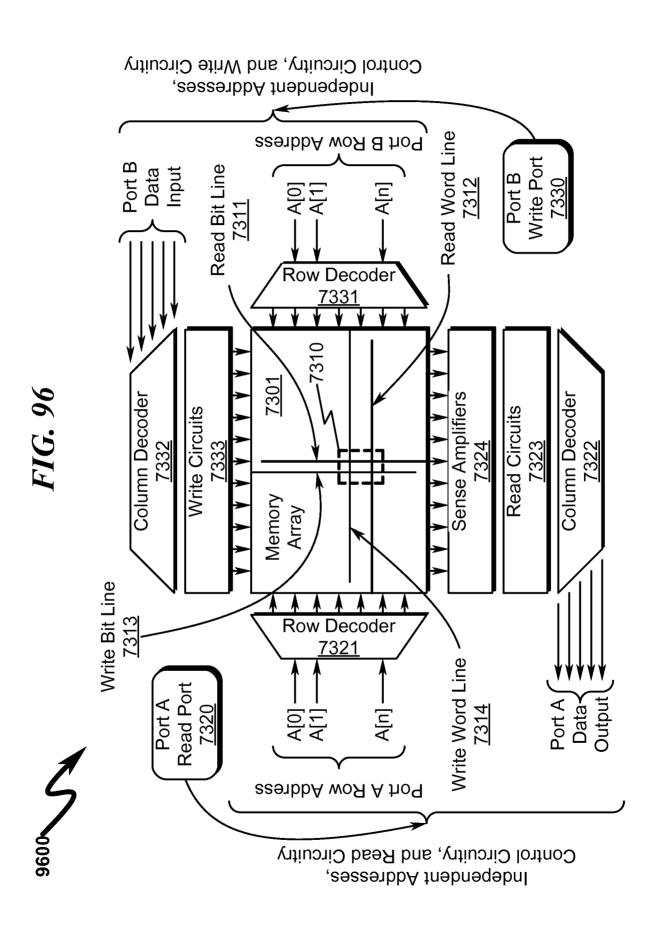

- FIG. 96 illustrates block diagram of dual port SRAM utilizing same 6T DFM memory cell.

### DESCRIPTION OF THE PRESENTLY PREFERRED EXEMPLARY

25

### **EMBODIMENTS**

While this invention is susceptible of embodiment in many different forms, there is illustrated in the drawings

and will herein be described in detailed preferred embodiment of the invention with the understanding that the present disclosure is to be considered as an exemplification of the principles of the invention and is not intended to limit the broad aspect of the invention to the embodiment illustrated.

5

10

15

30

The numerous innovative teachings of the present application will be described with particular reference to the presently preferred embodiment, wherein these innovative teachings are advantageously applied to the particular problems of a MEMORY CELL SYSTEM AND METHOD. However, it should be understood that this embodiment is only one example of the many advantageous uses of the innovative teachings herein. In general, statements made in the specification of the present application do not necessarily limit any of the various claimed inventions. Moreover, some statements may apply to some inventive features but not to others.

### **Amplifier Not Limitive**

The present invention anticipates a wide variety of 20 in which disclosed application environments the Within this context, the system/method may operate. feedthru and feedback amplifiers that constitute the memory cell storage methodology may take many forms, some of which may include inverting and non-inverting amplifiers. 25 traditional CMOS static memory systems utilize cross-coupled inverting amplifiers to achieve two stable states within the memory cell, the present invention may also be implemented using non-inverting amplifiers in some embodiments.

### **Multi-State Output Drive Control Not Limitive**

The present invention utilizes a feedback amplifier that incorporates a multi-state output drive control feature

enabling selective enablement of the current sourcing/sinking capability of the feedback amplifier output circuitry. This selective enablement of output sourcing/sinking drive capability may take many forms, but is generally anticipated to encompass a wider implementation range than traditional "tri-state" drive control circuitry. For example, the output drive modulation is specifically anticipated to include one or more of the following capabilities:

• Removing current sourcing capability from the feedback amplifier (i.e. switching or disconnecting the power supply source to the amplifier);

15

30

- Removing current sinking capability from the feedback amplifier (i.e. switching or disconnecting the power supply ground to the amplifier);

- Modulating the threshold voltage for a PMOS transistor associated with the current sourcing capability of the feedback amplifier to limit the current sourcing capability of the feedback amplifier;

- Modulating the threshold voltage for a NMOS transistor associated with the current sinking capability of the feedback amplifier to limit the current sinking capability of the feedback amplifier;

One skilled in the art will recognize that these techniques may be used individually or may be combined together in some preferred embodiments.

### **Logic Levels Not Limitive**

The present invention places no restriction on the sense of logic levels within the context of the present invention. Thus, logic "true/false" and/or "1/0" levels may be represented by high/low voltage levels or low/high logic

levels without loss of generality. Furthermore, representative memory state conditions may be represented equally well by voltage levels and/or current levels and/or charge levels without loss of generality. Within the context of this disclosure, it will be assumed that the normal convention of a logic zero (0) ("false") being represented by a low voltage and a logic one (1) ("true") being represented by a higher voltage will be used within document as a framework of discussion with the understanding that these conventions are not limitive of the scope of the claimed invention.

### **Complementary Devices Not Limitive**

10

15

20

25

30

The present invention may utilize a variety of devices that have complementary functional forms. For example, CMOS devices may be implemented using N-channel and P-channel devices, BJTs may be implemented using NPN and PNP devices, etc. The present invention specifically anticipates that any implementation described and claimed herein may also be implemented using complementary technologies without loss of generality. Furthermore, the present invention specifically anticipates that complementary elements crossing technology boundaries may be combined to form claimed elements within some present invention embodiments. Thus, for example, the present invention anticipates the combination of MOS and bipolar technologies (BiCMOS) to be utilized in some preferred embodiments of the present invention.

# **Inverting Amplifier Implementation Not Limitive**

The present invention anticipates a wide variety of implementations, some incorporating cross-coupled inverting feedthru/feedback amplifiers. The present invention makes no limitation on the implementation of these inverting amplifiers. For example, the use of conventional CMOS

inverters is anticipated when implementing fully static 5T/6T memory cell designs as detailed herein. Additionally, non-static 3T/4T memory cell designs may also be implemented using NMOS technology, wherein the inverter loads are configured using high value resistors, depletion mode loads, and the like. The present invention anticipates in some embodiments these fully-static/non-static methodologies may integrated or mixed within a given memory cell. Additionally, while the use of single-ended amplifiers is thought to be optimal in many preferred embodiments of the the invention may be implemented using differential and/or double-ended amplifier designs.

10

15

20

25

30

One skilled in the art will recognize that the above teachings may also be applied to a wide variety of complementary fabrication processes as well as scenarios that are outside the realm of conventional MOS manufacturing processes.

# **4T/3T Memory Cell Optimization**

The present invention permits an area space reduction within the context of traditional 4T memory cells. Since the present invention permits elimination of the traditional pass gate associated with the output of the feedthru amplifier, the total transistor count associated with the memory cell is reduced from 4 (one input pass gate, two transistors associated with the cross-coupled inverters, two load resistors, and an output pass gate) to 3 (one input pass gate, two transistors associated with the cross-coupled inverters, two load resistors). This represents a 25% reduction in overall transistor area consumed by the present invention 3T memory cell in this application environment.

### **6T/5T Memory Cell Optimization**

The present invention permits an area space reduction within the context of traditional 6T memory cells. Since the present invention permits elimination of the traditional pass gate associated with the output of the feedthru amplifier, the total transistor count associated with the memory cell is reduced from 6 (one input pass gate, four transistors associated with the cross-coupled inverters, and an output pass gate) to 5 (one input pass gate, four transistors associated with the cross-coupled inverters). This represents a 16% reduction in overall transistor area consumed by the present invention 5T memory cell in this application environment.

5

10

30

### **8T/6T Memory Cell Optimization**

The present invention permits an area space reduction within the context of traditional 8T dual port memory cells. Since the present invention permits elimination of the traditional pass gate associated with the output of the feedthru amplifier, the total transistor count associated with the memory cell is reduced from 8 (two input pass gates, four transistors associated with the cross-coupled inverters, and two output pass gates) to 6 (two input pass gates, four transistors associated with the cross-coupled inverters). This represents a 25% reduction in overall transistor area consumed by the present invention 8T memory cell in this application environment.

# **MULTI-WRITE Not Limitive**

The present invention describes a variety of methodologies in which the present invention memory cell embodiments may be written. These techniques will be generally described by the term "MULTI-WRITE" to indicate these memory cell write capabilities. This may include but

is not limited to the use of one-step writes, two-step writes, multi-step writes, writes using VDD switching, writes using VSS switching, or any combination of the above techniques. Thus, the term MULTI-WRITE should be given its broadest possible interpretation within this definition scope.

### **Power Supply Polarity Not Limitive**

The present invention describes a variety of methodologies in which the present invention memory cell embodiments utilize power supply sources indicated by VDD/VCC and VSS/GND. One skilled in the art will recognize that power supply polarity may be generalized within the context of the disclosed invention to include other nomenclature and other polarities, as well as multiple power supplies having multiple voltage values. The present invention specifically anticipates this generalization within the scope of the claimed invention and the claims definitions herein.

10

15

# **Electrical Reversal Not Limitive**

20 present invention describes a variety The methodologies in which the present invention memory cell embodiments utilize various means to switch VDD/VCC and VSS/GND to the feedback amplifier in a cross-coupled amplifier configuration in order to maintain a stable memory 25 Within this context the term "electric reversal" or "electrical reversal" or "electrically reversed" will be used to mean a change in the designated signal from VSS-to-VDD or from VDD-to-VSS, as appropriate within the context. While one skilled in the art will recognize that power supply polarity may be generalized within the context of the 30 disclosed invention to include other nomenclature and other polarities, the general scope of this term is used to

indicate a logic reversal of the designated signal. The present invention specifically anticipates that this generalization within the scope of the claimed invention will include voltage swings that are not fully rail-to-rail, but which may include partial transitions to fractions of the VDD/VCC voltage.

### **System SubCircuit Overview**

The present invention relates generally to memory systems and specifically memory arrays. The disclosed invention may be constructed in a wide variety of ways using a wide variety of both circuit fabrication techniques as well as the use of a wide variety of subcircuits in combination. To better understand the architectural scope of the present invention it is instructive to review block diagrams of how these subcircuit elements are arranged and how they may be combined to form various embodiments of the invention. A brief discussion of the various subcircuits that may comprise the present invention in its various embodiments follows.

#### 20 System Subcircuit Overview (1700)

10

15

FIG. 17 (1700) illustrates an exemplary system block diagram of various preferred major embodiment subcircuits associated with the present invention.

#### 5T Memory Cell Structure (1800)

25 FIG. 18 (1800) illustrates a block diagram of an exemplary 5T memory cell structure.

#### 5T Memory Cell Group (1900)

FIG. 19 (1900) illustrates a block diagram of an exemplary 5T memory cell group.

### 5T Group With Global Word Line (2000)

FIG. 20 (2000) illustrates a block diagram of an exemplary 5T group with global word line.

### Array Of 5T Groups With Global Word Line (2100)

5 FIG. 21 (2100) illustrates a block diagram of an exemplary array of 5T groups with global word line.

### 5T Group With Local Word Line (2200)

FIG. 22 (2200) illustrates a block diagram of an exemplary 5T group with local word line.

#### 10 Array Of 5T Groups With Local Word Line (2300)

FIG. 23 (2300) illustrates a block diagram of an exemplary array of 5T groups with local word line.

#### Array of 5T Write and Read Memory Cells w/o Interspersed Groups (2400)

FIG. 24 (**2400**) illustrates a block diagram of an exemplary array of 5T write and read memory cells without interspersed groups.

#### 6T Write and Read Memory Cell (2500)

FIG. 25 (2500) illustrates a block diagram of an exemplary 6T write and read memory cell.

#### 20 6T Memory Cell Group (2600)

FIG. 26 (2600) illustrates a block diagram of an exemplary 6T memory cell group.

#### 6T Group With Global Word Line (2700)

FIG. 27 (2700) illustrates a block diagram of an 25 exemplary 6T group with global word line.

### Array of 6T Groups With Global Word Line (2800)

FIG. 28 (2800) illustrates a block diagram of an exemplary array of 6T groups with global word line.

#### 6T Group With Local Word Line (2900)

FIG. 29 (2900) illustrates a block diagram of an exemplary 6T group with local word line.

#### Array of 6T Groups With Local Word Line (3000)

5 FIG. 30 (3000) illustrates a block diagram of an exemplary array of 6T groups with local word line.

#### Array of 6T Write And Read Memory Cells (3100)

FIG. 31 (3100) illustrates a block diagram of an exemplary array of 6T write and read memory cells without interspersed groups.

#### 7T Memory Cell Group (3200)

10

FIG. 32 (3200) illustrates a block diagram of an exemplary 7T memory cell group.

#### Array of 6T Dual Port Based On Group With Local Word Line (3300)

15 FIG. 33 (3300) illustrates a block diagram of an exemplary array of 6T dual port based on group with local word line.

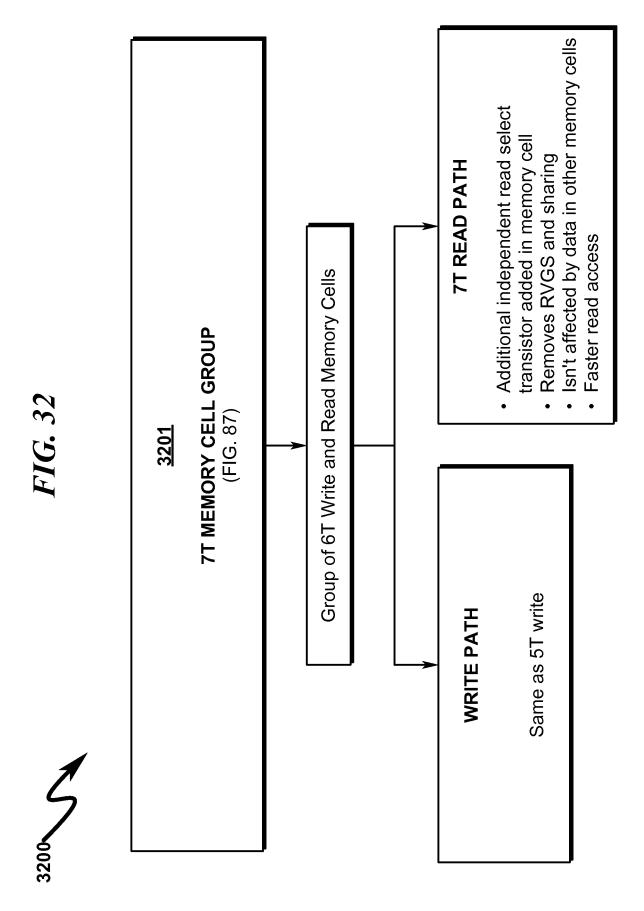

## **System Memory Cell Overview (3400)**

The present invention system may be broadly described as depicted in FIG. 34 (3400). In this broad system block diagram, the present invention incorporates a feedthru amplifier (3410) having input (3411) and output terminals (3412); a feedback amplifier (3420) having input (3421), output (3422), and control (3423) terminals; and an access device (3430) having input (3431), output (3432), and enable (3433) terminals.

Note that this configuration generally differs from the prior art in that the access device (3430) is connected to the output of the feedthru amplifier (3410) rather than the

output of the feedback amplifier (3420). Additionally, the operation of the control input (3423) on the feedback amplifier (3420) in the present invention differs from the prior art in that this control input (3423) is used to force a write to the memory cell by virtue of its influence on the drive strength of the feedback amplifier Specifically, the control input (3423) in the present invention is typically used to control or drive the power supply (VDD/VCC or VSS/GND) reversed electrical state, forcing a change in the state of the memory cell during a write operation. Thus, in contrast to the prior art, the control port (3423) is used to WRITE the state of the memory cell, not aid the access device (3430) in setting the state of the memory cell. This modified write operation may be used in conjunction with a TWO-STEP-WRITE sequence to permit read/write access to the memory cell without the drawbacks typically associated with READ DISTURB in conventional prior art designs.

## **MULTI-WRITE Embodiment**

#### 20 Traditional Latch Write-1 Challenges (3500)

5

10

15

30

As mentioned in the Background Section, writing a "1" in the traditional 6T memory cell is difficult and requires a second Pass Gate to always have the ability to pull the high side low as shown in FIG. 35 (3500).

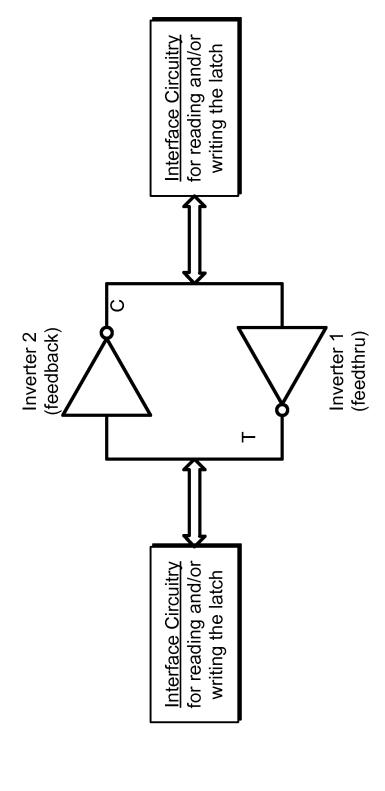

#### 25 Cross-Coupled Latch Overview (3600)

A fundamental characteristic is the ability to easily write a high ("1) or low ("0") into the cross coupled latch that makes up many different types of memory cells. A logic schematic of the cross coupled latch without the pass gates is illustrated in FIG. 36 (3600).

Reading and writing the memory cell latch traditionally been achieved through additional circuitry that either passes the state of the latch out to be read or forces a high or a low onto the internal nodes of the latch (true (T), complement (C)) to the desired state of either a high or a low. An important embodiment is the ability to accomplish writing the more difficult state, such as a high in this case, even with weak interface circuitry, without requiring any involvement by the Interface Circuitry or in another embodiment minor assistance. This means that the issues with the N-channel Pass Gate losing drive as it pulls up and the conflicting need for it to have weak drive relative to the Pull Down to prevent READ DISTURB are eliminated. Writing the more difficult state is achieved by switching the power to the inverter to the opposite voltage such as, driving VDD to Ground or driving Ground to VDD on one of the two inverters in the latch then returning it back to the supply power voltage.

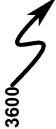

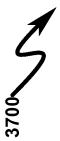

#### Generalized Latch Write (3700)

20 Writing a high in the latch through switching VDD low is generally illustrated in FIG. 37 (3700).

#### Latch Write Detail (3800)

10

15

30

FIG. 38 (3800) illustrates a detailed implementation of the VDD latch write.

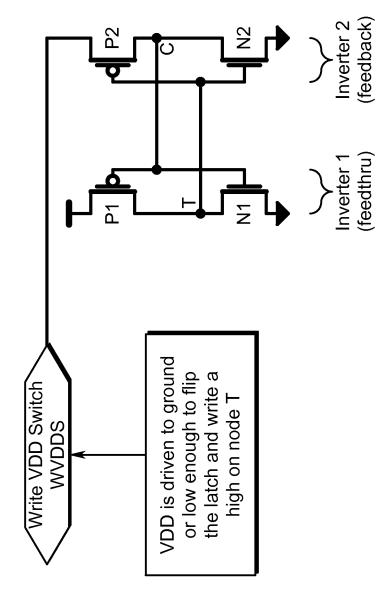

#### 25 <u>Switched VDD Latch Overcomes Latch Writing Difficulty (3900)</u>

The difficulty in writing a high in the traditional 6T memory cell shown in FIG. 18 (1800) is eliminated with the switched VDD embodiment generally illustrated in FIG. 39 (3900). This configuration eliminates the need to have a second Pass Gate that accesses the high side thus allowing for a single-sided write and removes the conflicting

constraints of READ DISTURB vs. write-ability thereby, improving DFM.

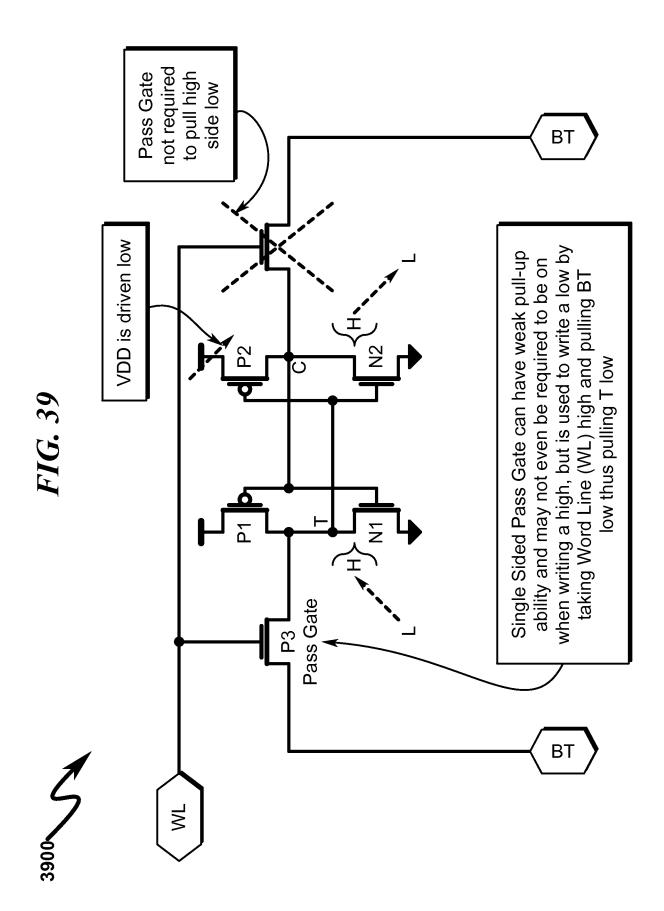

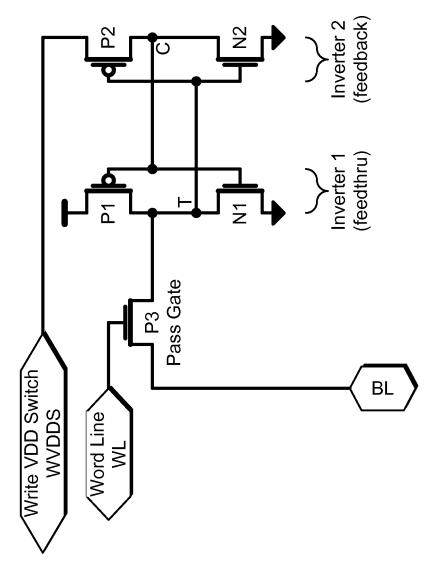

#### Exemplary 5T Memory Cell With VDD Write (4000)

5

10

15

As mentioned previously, writing a low is easy, because the N-channel has full drive strength (VGS = VDD) and therefore, can pull low against the P-channel device P1. P1 can also be sized to have less drive than the Pass Gate to aid in writing a low. The embodiment of the 5T memory cell is illustrated in FIG. 40 (4000) and is discussed in a later section.

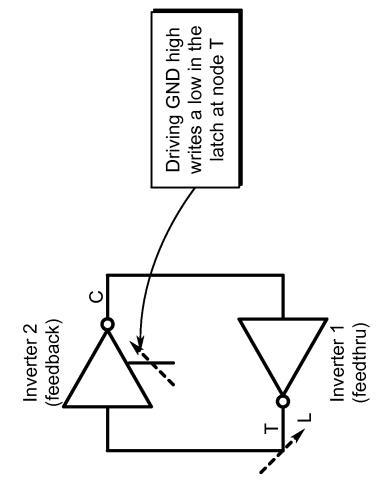

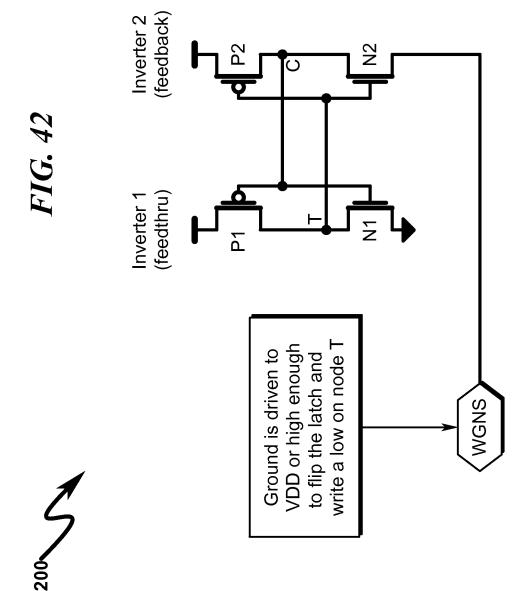

#### Exemplary 5T Memory Cell With VSS Write (4100)

In another preferred embodiment switching GND high can write a low ("0") into the memory cell as generally illustrated in FIG. 41 (4100). This would be the desirable approach if the interface circuitry has more difficulty writing a low. As an example, a P-channel Pass Gate would have difficulty pulling low, but can pull high with much more drive.

#### Exemplary 5T Memory Cell Detail With VSS Write (4200)

A preferred exemplary embodiment of the previously described VSS write memory cell is generally illustrated in FIG. 42 (4200). As seen from this and previous embodiments, the MULTI-WRITE embodiments are not limited to switching either the GND or VDD of the second (feedback) inverter. It can also be used instead on the first (feedthru) inverter based on the requirements and limitations to the interface circuitry that connects the true (T) and complement (C) nodes of the latch. Choosing to switch the power supply on the second (feedback) inverter or the first (feedthru) inverter will depend on what type of interface circuitry

that is used and how it best interfaces with the internal nodes of the latch.

## 5T Memory Cell Summary (4300)

The present invention discloses an embodiment referred to herein as MULTI-WRITE that makes writing the memory very easy, and in fact can be done with a single sided write where only one pass gate is required, thus reducing the number of transistors within the memory cell from 6 to 5. This also allows the memory cell to be adjusted more to prevent READ DISTURB without trading off write-ability by removing the conflicts between READ DISTURB and write. This 5T memory cell is illustrated in FIG. 43 (4300).

Some of the other preferred embodiments taught by the present invention include but are not limited to the following:

- Easy One-Sided Write

- TWO-STEP-WRITE;

10

15

- Flexibility to use different Bit Line voltage levels and conditions during write and read;

- Ability to write a high in the memory cell even if the Word Line is low thus keeping the Pass Gate off;

- Array Implementation with Global Word Lines;

- Array Implementation with Group Word Lines;

- Array dynamic and leakage power reduction which includes the flexibility to reduce the voltage swing on the Bit Lines.

- Embodiments listed above may be implemented in memory arrays utilizing a Global Word Line as well as

modified into memory arrays utilizing a Group Word Line.

These preferred embodiments will be discussed below, but are by no means limitive of the scope of the present invention.

5

10

15

20

25

30

### **One-Sided Write (MULTI-WRITE)**

A major first step is to make the writing of the memory cell very easy without adding transistors that would make it bigger, and in fact can make the memory cell smaller by eliminating one of the transistors. Having the ability to write the memory cell without needing to consider READ DISTURB and its sizing issues of the Pull Down vs. the Pass Gate removes the tradeoff required between the conflicts of READ DISTURB vs. write. The one-sided write can be used in many different types of memory cells that include a latch to hold data such as Register Files, Single Port, Dual Port, Multiports, CAMs, and the like.

As mentioned in the Background Section, a single-sided write can't be done to the traditional 6T memory cell shown in FIG. 11 (1100), because there must be access to both the true and complement sides of the latch, and the only way a cell can be written in the traditional 6T SRAM memory cell is to pull the high side low when writing opposite data. This limitation is not present in the disclosed 5T SRAM memory cell, which has the ability of a single-sided write, 2<sup>nd</sup> pass gate. thus eliminating the Therefore, embodiment that uses a new method of writing a high into a memory cell that had a low previously stored is disclosed This embodiment overcomes the limited pull-up ability of the N-channel pass gate since, by pulling its source high, it begins to turn itself off and therefore loses its drive strength. Also, it is limited by how high

it can eventually pull which is the supply voltage (VDD) minus a N-channel threshold voltage (VTN) or (VDD - VTN) (VDD - VTN). The 5T memory cell with a virtual VDD switch on the inverter (Inverter 2) that is not connected to the Pass Gate for the write is illustrated in FIG. 26 (2600).

5

10

15

20

25

Storing a high in the memory cell can be achieved simply by taking the virtual VDD (WVDDS) on inverter 2 low which in turn caused node t to go high if it is low or to remain high if a high was previously stored. This may not even require turning on the pass gate and accessing the state on the Bit Line, thereby creating alternatives for writing a high by using a method that drives the virtual VDD of inverter 2 low and/or using the state on the Bit Line to influence node C. Once this step is complete then the virtual source signal on inverter 2 can now be re-applied, thus holding the stored state high.

The opposite can be achieved by driving the ground of Inverter 2 high thus writing a low on node t. The point is that by just switching and driving the source of P2 low or the source of N2 high a low or a high can be written into the memory cell creating great flexibility as to how the memory cell can be written and making the write very easy.

Power gating the inverter that is not used to drive the Bit Line is desirable to switching a virtual ground of Inverter 1, because the path to pulling the Bit Line low during a read would have to go through 2 N-channel transistors thus requiring a much larger transistor switch to pull to ground on the shared virtual ground to prevent READ DISTURB.

30 The ability to write a high into the memory cell without having to have a full voltage swing on the Bit Line or even requiring that the Word Line be high to turn on the

Pass Gate are additional embodiments. Writing the traditional memory cell required that there be a full voltage swing where both the bit true and bit complement Bit Lines are first pre-charged high to VDD then one side must be pulled all the way to ground to pull the high side low enough to flip the cell. Limiting the high voltage level required in this embodiment provides 2 very important benefits:

It reduces the array power that is burned during a 10 write, because the delta voltage is much smaller thus reducing dv/dt.

15

20

25

30

Reduces the READ DISTURB that can occur on the rest of the memory cells along the row.

This creates great flexibility in lowering the high voltage on the Bit Line and/or reducing the drive strength of the Pass Gate. In fact, the design could be adjusted to substantially reduce the high voltage on the Bit Line especially if the Pass Gate remains off during the portion of the write when VDD is switched low for the initial step of writing a high. Keeping the Pass Gate off will prevent the lower high on the Bit Line from actually impeding the transition to a high on internal node of the latch (t in this case). Reducing the high voltage on the Bit Line can allow for the possibility to greatly reduce the power due to the voltage swing on the Bit Lines.

Writing a low through the Pass Gate is easy, because pulling the Bit Line to ground will pull the source of the Pass Gate to ground, and since it is an N-channel transistor, it will be able to pull node t to ground with good drive to overcome the P-channel of the inverter which can be sized to have reduced drive if necessary.

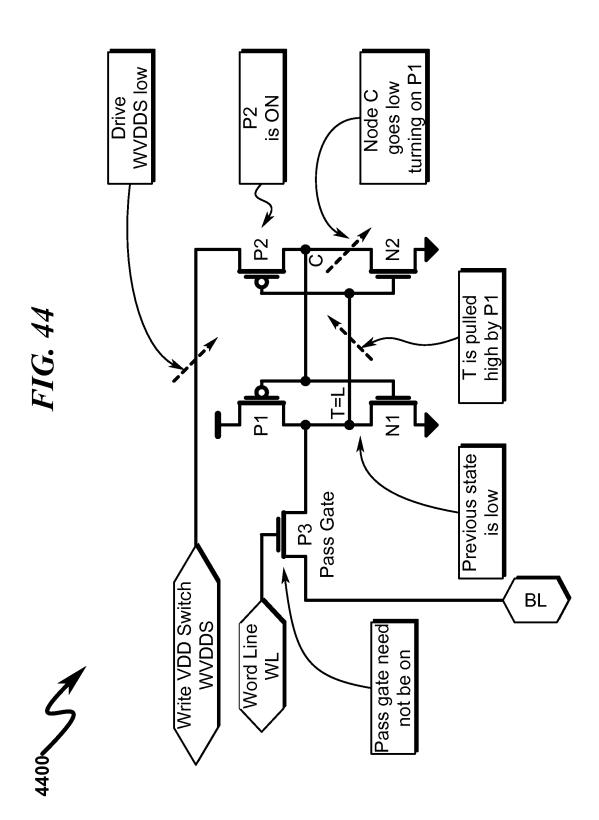

#### Exemplary Memory Cell Writing High When Low Previously Stored (4400)

An example of writing a high when a low was previously stored is generally illustrated in FIG. 44 (4400).

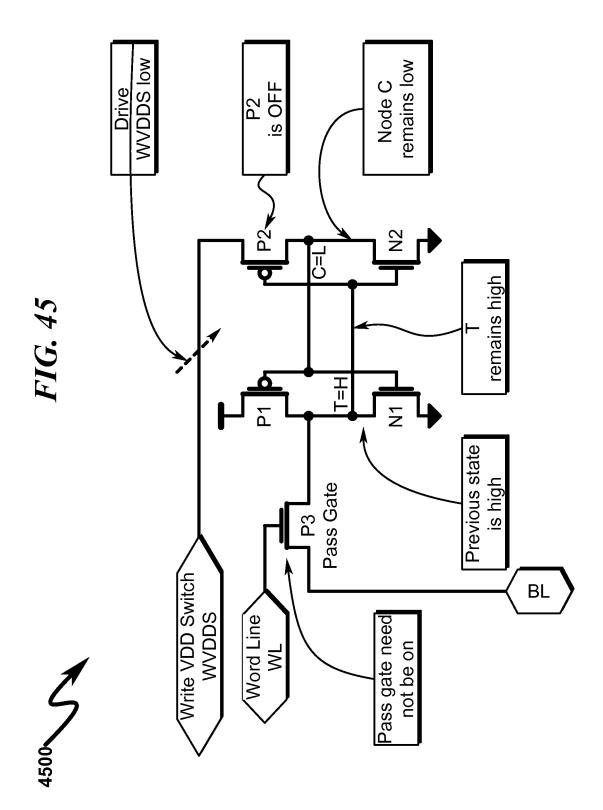

#### Exemplary Memory Cell Writing High When High Previously Stored (4500)

An example of writing a high when a high was previously stored is generally illustrated in FIG. 45 (4500).

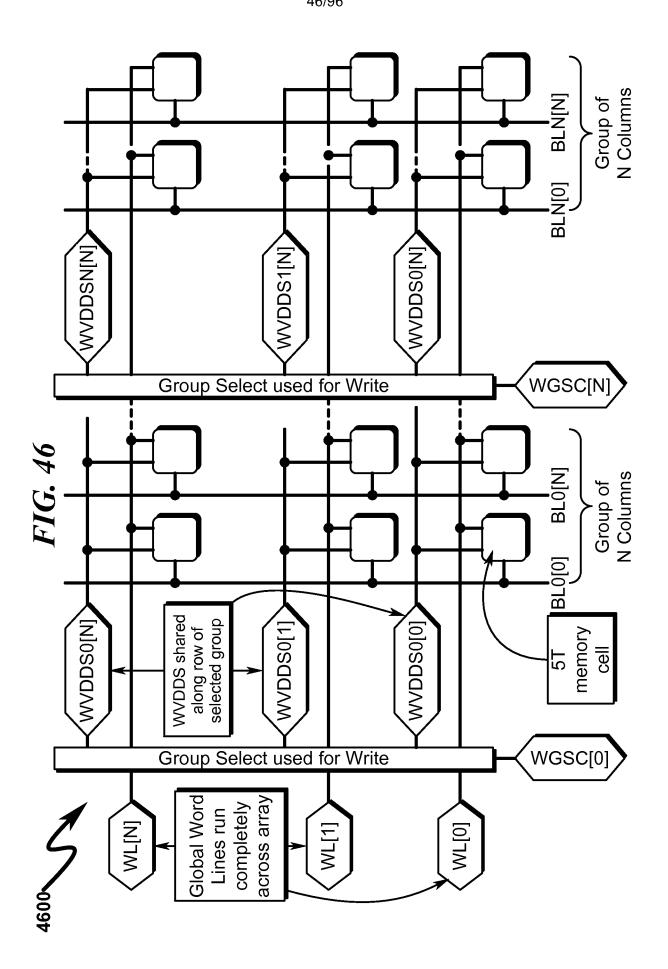

#### Memory Array Cells and Control Structure (4600)

5

10

15

20

25

30

The circuits utilized to create the array of memory cells and its control by the Group Select circuitry are shown in FIG. 46 (4600) and following. Most of the initial drawings (FIG. 46 (4600)) and following) and the discussions below are based on the Global Word Line approach, but the approaches and designs can apply to the Group Word Line approach as well. An important point is that the MULTI-WRITE embodiment and its structure within the array opens up many avenues to adjust the design based on the process that it will be built in and the goal for that particular memory product.

The general array structure consist of stepping Groups in rows and columns where each group is made up of a group of memory cells controlled and selected by a Group Select that is based on the logical combination of the selected Word Line and a group decode. The number of memory cells along the row within the group can vary depending on the design goal for the architecture. If the number of memory cells within a group are equal to the Bits Per Word (BPW) then a read-modify-write is not required, because every memory cell that is exposed to VDD being driven low are going to be written with the state dictated by the Data In pins. If the number of bits to be written are greater than the BPW then a read-modify-write or other methods can be

used to rewrite the previously stored data back into the memory cells that were not intended to be written. This approach allows for more memory cells to be within a group than there are Bits Per Word which can reduce the number of group select circuits that are required and thus reduce the physical size of the array.

A top level view of the array is generally illustrated in FIG. 46 (4600).

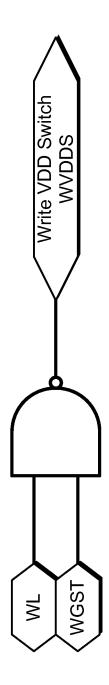

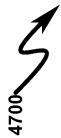

#### **Group Select Decoder (4700)**

The Group Select Decoder that creates a write VDD switch is generally illustrated in FIG. 47 (4700). The Group Select circuitry for a write is the logical combination of the active Word Line (WL) and the particular group of columns to be accessed when a write occurs.

Although, the schematic shown in FIG. 47 (4700) is a simple NAND gate, other arrangement of transistors could be used to achieve the same logical results.

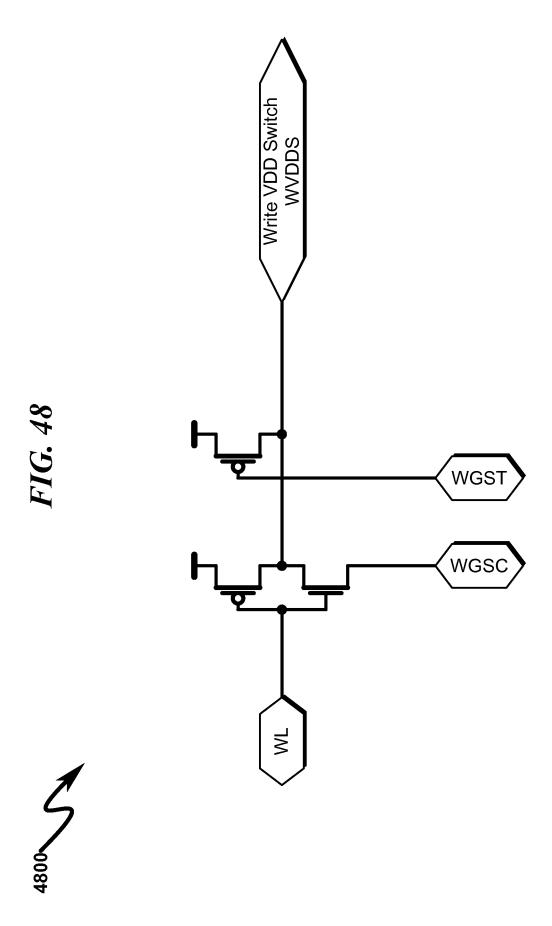

#### Group Select Decoder Detail (4800)

20

25

30

An exemplary 3-transistor Group Select Decoder detailed circuit implementation that creates a write VDD switch (WVDDS) is generally illustrated in FIG. 48 (4800).

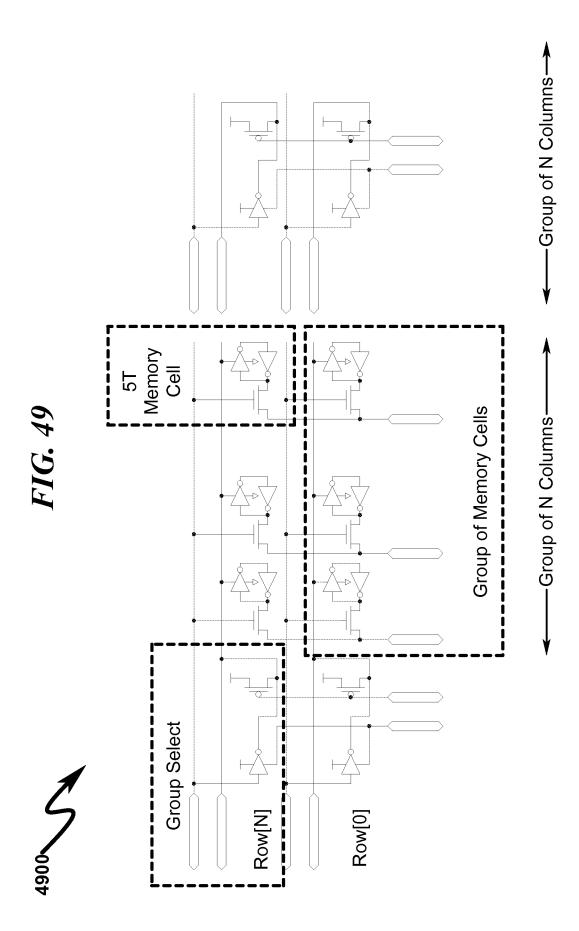

#### Exemplary Memory Array Detail (4900)

An exemplary memory array implementing these VDD switching techniques is generally illustrated in FIG. 49 (4900) and illustrates the internal transistors for the icons in FIG. 29 (2900).

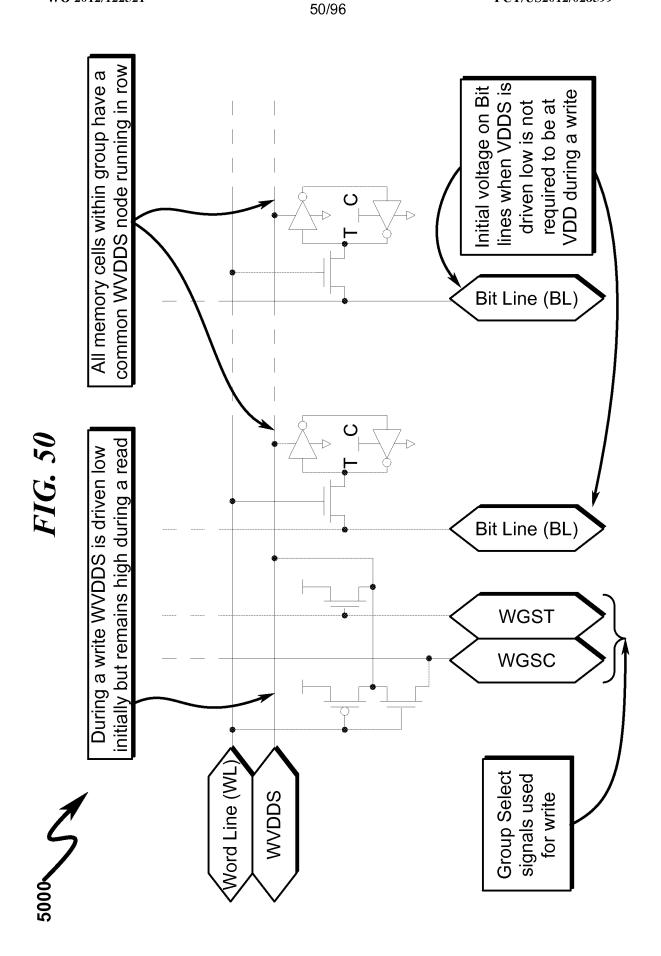

#### Memory Cell Access (5000)

An important element of many preferred embodiments is the method used to access the memory cell within the array. The connections and functions that are formed between the

Group Select circuitry and the row of a group of memory cells are shown in FIG. 50 (5000). In this context, all virtual VDD nodes (WVDDS) within the selected group are shared and driven low when a write occurs, because every cell within the group will be written (A Read-Modify-Write technique or other techniques can be used for cases where it is desired to have a group that has more columns than the number of bits to be written). The WGS true (T) / complement (C) signals if decoded to be asserted are used during a write to drive WVDDS low during a write and to hold it high during a read.

#### Bit Line Current Path During WVDDS Low (5100)

10

15

20

25

30

Pulling the Bit Line low at the same time that WVDDS is being driven low may briefly create unacceptable levels of power consumption. An example of this is illustrated in FIG.  $51 \ (5100)$ .

There are alternatives to the timing of the Bit Line vs. when WVDDS goes low at the start of a write. The Bit Line can be forced to its high or low state at the start when WVDDS is going low so that it will be ready to write as soon as possible. The brief current path illustrated in FIG. 51 (5100) may be an acceptable tradeoff if the highest priority is to have the write be as fast as possible.

#### TWO-STEP Write Waveforms (5200) (5300) (5400)

This current path can be eliminated by either having a separate Word Line driving the Pass Gate that is low during the first portion of write when WVDDS is low or not pulling the Bit Line low until the first stage of the write is complete and WVDDS goes back high. The waveforms illustrated in FIG. 52 (5200), FIG. 53 (5300), and FIG. 54 (5400) show the latter which is another embodiment called a TWO-STEP-WRITE.

#### TWO-STEP Write Schematic (5500)

5

10

15

20

25

30

As can be seen in the timing waveforms referenced in the previous section and schematic shown in FIG. 55 (5500), the only goal of step 1 of the TWO-STEP-WRITE is to write a high in every memory cell that shares WVDDS within the selected group by taking WVDDS low which doesn't necessarily require that the Bit Line be pulled all the way to VDD. In this example the Bit Lines float at the pre-charged value that is use for a read during step 1, but other values for the high voltage on the Bit Lines can be chosen based on the process and design goals.

#### Exemplary TWO-STEP Write Logic (5600)

An example of a circuit that only pulls the Bit Line Low when Data In (DI) is low is generally illustrated in FIG. 56 (5600).

#### Alternative TWO-STEP Write Methodology (5700)

Another embodiment would be to drive and hold the Bit Lines high during step 1 to give maximum effect and speed of writing a high which may be necessary in some designs based on the worst case processes and conditions. Once a high is written, step 2 begins by pulling WVDDS back high and pulling the selected Bit Lines low that have a low required from the appropriate Data In. An example of forcing the Bit Line high to VDD during Step 1 is illustrated in FIG. 57 (5700).

#### Alternative TWO-STEP Write Methodology Waveforms (5800) (5900) (6000)

Waveforms associated with the alternative TWO-STEP write methodology discussed in the previous section are generally illustrated in FIG. 58 (5800), FIG. 59 (5900), and FIG. 60 (6000).

Holding the Bit Lines at VDD, or some other high voltage, during Step 1 of the write may be required to maximize the ability to write a high in the memory cell to overcome process variation and speed up the write time under worst case conditions. This embodiment variation is illustrated in the drawings associated with this and the previous section.

#### Bit Line Voltage Levels (6100)

30

There are several choices as to what the voltage levels

10 can be on the Bit Lines when WVDDS goes low (L) during a

write. A few are listed below:

- Drive Bit Lines High, but not necessarily to VDD, for those associated with Data In being high. This has the possibility of the fastest write time to a "1".

- Pull selected Bit Lines Low for those requiring a Low to be written into the memory cell based on Data In being Low at the start of the write cycle when WVDDS first goes low. This has the possibility of being the fastest write.

- Pull selected Bit Lines Low for those requiring a Low to be written into the memory cell based on Data In being Low after WVDDS goes back high utilizing a TWO-STEP-WRITE.

- Leave Bit Line pre-charged to desired level used for reading such as VDD, VDD/2 or lower, whereby the influence by the Bit Line is determined by the Pass Gate which could be off or have reduced drive strength.