(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7021726号**

**(P7021726)**

(45)発行日 令和4年2月17日(2022.2.17)

(24)登録日 令和4年2月8日(2022.2.8)

(51)国際特許分類

H 03 K 17/16 (2006.01)

F I

H 03 K 17/16

H

請求項の数 20 (全23頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2018-568867(P2018-568867) |

| (86)(22)出願日       | 平成29年6月30日(2017.6.30)       |

| (65)公表番号          | 特表2019-520760(P2019-520760) |

| A)                |                             |

| (43)公表日           | 令和1年7月18日(2019.7.18)        |

| (86)国際出願番号        | PCT/IB2017/001097           |

| (87)国際公開番号        | WO2018/002729               |

| (87)国際公開日         | 平成30年1月4日(2018.1.4)         |

| 審査請求日             | 令和2年6月21日(2020.6.21)        |

| (31)優先権主張番号       | 15/196,323                  |

| (32)優先日           | 平成28年6月29日(2016.6.29)       |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |

|          |                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>- 5474 ダラス メイル ステイション<br>3999 ピーオーボックス 655474 |

| (74)代理人  | 100098497<br>弁理士 片寄 恒三                                                                                            |

| (72)発明者  | カイル シュルマイヤー<br>アメリカ合衆国 75025 テキサス州<br>, ブレイノ, チューリヒ ドライブ 7<br>809                                                 |

| (72)発明者  | スアルプ アラス<br>アメリカ合衆国 75206 テキサス州<br>ダラス, エイビーティー 19307,<br>最終頁に続く                                                  |

(54)【発明の名称】 高誘導負荷システムにおけるFETに対する継続的電流制限の方法及び装置

**(57)【特許請求の範囲】****【請求項1】**

装置であつて、

ドレイン端子とソース端子とゲート端子とを有するFETと、

前記FETの前記ソース端子と前記ドレイン端子との間の電流導通経路に電流を供給するために結合される第1の供給電圧と、

前記FETの電流導通経路を介して流れる電流を受け取るために結合される出力端子と、

前記FETのゲート端子に結合されるバイアス電流供給と、

前記FETのゲート端子に結合される第2の供給電圧と、

前記FETを介して流れる電流に比例する感知電流を出力するために結合される電流感知回路と、

前記感知電流に結合され、前記感知電流を所定の制限電流と比較する電流制限コンパレータと、

前記電流制限コンパレータに結合され、前記FETのゲート端子から電流を除去するために結合されるプルダウン電流回路と、

前記感知電流に結合され、感知レート電流を出力する電流時間導関数回路と、

感知レート電流を受け取るために結合され、前記バイアス電流供給に結合される回路と、

を含む、装置。**【請求項2】**

請求項1に記載の装置であつて、

前記電流制限コンパレータから前記プルダウン電流回路に結合されるイネーブル出力を更に含む、装置。

**【請求項 3】**

請求項 1 に記載の装置であって、

前記感知レート電流に応答して前記 F E T のゲート端子への前記バイアス電流を低減するための回路要素を更に含む、装置。

**【請求項 4】**

請求項 1 に記載の装置であって、

前記所定の制限電流がプログラム可能である、装置。

**【請求項 5】**

請求項 4 に記載の装置であって、

前記所定の制限電流が書き込み可能記憶回路に記憶される、装置。

10

**【請求項 6】**

請求項 1 に記載の装置であって、

前記電流時間導関数回路が、前記感知電流の増加のレートが所定の閾値を超えるときに前記感知レート電流を出力する電流レート検出回路を含む、装置。

**【請求項 7】**

請求項 1 に記載の装置であって、

前記感知レート電流と前記バイアス電流供給との間に結合されるイネーブル回路と、

前記感知電流と基準電流とに結合され、前記イネーブル回路にイネーブル信号を出力する電流レートイネーブルコンパレータ回路と、

を更に含む、装置。

20

**【請求項 8】**

請求項 7 に記載の装置であって、

前記電流レートイネーブルコンパレータ回路がスケーリングファクタを含み、前記電流レートイネーブルコンパレータ回路が、前記感知電流と、前記スケーリングファクタと前記所定の制限電流との乗算した積との間の差を、前記基準電流と比較する、装置。

**【請求項 9】**

請求項 8 に記載の装置であって、

前記スケーリングファクタがプログラム可能である、装置。

30

**【請求項 10】**

請求項 9 に記載の装置であって、

前記スケーリングファクタを記憶するプログラム可能記憶回路を更に含む、装置。

**【請求項 11】**

請求項 10 に記載の装置であって、

前記プログラム可能記憶回路に対処するために結合される外部バスインターフェースを更に含む、装置。

**【請求項 12】**

方法であって、

イネーブル信号を受信することと、

供給電圧端子と電流を供給するための出力端子との間で F E T の電流導通経路を結合することと、

電圧とプルアップバイアス電流とを前記 F E T のゲート端子に結合することと、

前記 F E T を介して流れる電流を感知することと、

前記 F E T を介して流れる電流を所定の電流制限と比較することと、

前記 F E T を介して流れる電流を所定の電流制限と比較することに応答して、前記 F E T のゲート端子における電流を低減することと、

前記 F E T を介して流れる電流の増加のレートをレート增加閾値と比較することと、

前記 F E T を介して流れる電流の増加のレートを比較することに応答して、前記 F E T のゲート端子への前記プルアップバイアス電流を低減することと、

40

50

を含む、方法。

**【請求項 13】**

請求項 12 に記載の方法であって、

前記 FET を流れる電流の増加のレートを比較することが、

前記 FET を介して流れる電流を前記所定の電流制限の所定のパーセンテージである閾値と比較することを含む、方法。

**【請求項 14】**

請求項 12 に記載の方法であって、

前記 FET のゲート端子における電流を低減した後に、前記出力端子における電流を前記所定の電流制限で供給するように前記 FET を動作させることを更に含む、方法。

10

**【請求項 15】**

請求項 12 に記載の方法であって、

前記供給電圧端子と電流を供給するための出力端子との間で FET の電流導通経路を結合することが、前記 FET のドレイン端子を供給電圧に結合することと、前記 FET のソース端子を前記出力端子に結合することとを含む、方法。

**【請求項 16】**

請求項 12 に記載の方法であって、

前記供給電圧端子と電流を供給するための出力端子との間で FET の電流導通経路を結合することが、電流を供給するための端子に前記 FET のドレイン端子を結合することと、接地電位を受け取るための端子に前記 FET のソース端子を結合することとを含む、方法。

20

**【請求項 17】**

請求項 12 に記載の方法であって、

前記電圧とプルアップ電流とを前記 FET のゲート端子に結合することが、供給電圧より大きい増大されたゲート電圧を供給することを含む、方法。

**【請求項 18】**

請求項 12 に記載の方法であって、

前記 FET を介して流れる電流を所定の電流制限と比較することが、前記 FET を介して流れる電流を書き込み可能記憶回路に記憶された調節可能電流制限と比較することを含む、方法。

30

**【請求項 19】**

集積回路であって、

電圧供給と負荷との間に結合される電流導通経路を有するパワー FET のゲートを駆動するための端子と、

供給電圧を前記集積回路に結合するための電圧入力端子と、

前記パワー FET のゲート端子を駆動するための前記端子と増大された電力供給を結合するための電圧入力端子とに結合されるプルアップバイアス回路と、

前記パワー FET に流れる電流に比例する電圧を受け取るために前記電圧入力端子に結合され、感知された電流出力を有する電流感知回路と、

前記感知された電流を電流制限と比較する電流制限コンパレータと、

前記電流制限コンパレータと前記パワー FET のゲートを駆動するための前記端子とに結合されるプルダウン電流回路と、

40

前記感知された電流に結合される電流時間導関数回路と、

前記電流時間導関数回路と前記プルアップバイアス回路とに結合されるプルアップ電流低減回路と、

を含む、集積回路。

**【請求項 20】**

請求項 19 に記載の集積回路であって、

前記電流制限を設定するための調節可能トリム電流供給を更に含む、集積回路。

**【発明の詳細な説明】**

**【技術分野】**

50

**【0001】**

本願は、概してパワートランジスタに関し、より具体的には、高誘導負荷を駆動するためのパワー電界効果トランジスタ(FET)デバイスに関する。

**【背景技術】****【0002】**

高誘導負荷を駆動するために、パワー電界効果トランジスタ(FET)が用いられることが多い。例示的な応用例において、パワーFETが自動車又は他の車両におけるヘッドライト又はヘッドライトを駆動する。パワーFETは、電源と高電流電球との間でケーブルを用いて結合されて、パワーFET回路からヘッドライトに電流を結合する。ケーブル及び電球は、 $5 \mu H$ を超える高誘導負荷を示す可能性がある。オートモーティブの例示の応用例において、誘導負荷は $5 \sim 20 \mu H$ の範囲内であり得る。いくつかの従来のヘッドライトの電球は、ターンオン時に非常に高い電流を必要とする。例えば、ヘッドライトのための「突入」電流(初期ターンオン時に引き込まれる電流)は、 $90 \sim 100$ アンペアの範囲であり得る。

10

**【0003】**

パワーFETは、デバイスへの損傷なしに維持され得る電流及び電圧の安全動作領域(SOA)を有する。SOAは、FETの製造業者によって決定される。SOAは、FETへの損傷なしに信頼できる動作を保証するため、及び、FETが製品の予想寿命を満たすことを保証するために、維持される必要のある電流及び電圧の条件を示す。パワーFETを保護するため、及び、デバイスの動作を推奨されるSOA内に保つために、電流制限が用いられる。しかしながら、電流制限回路に、FETデバイスに流れる電流をシャットダウン又は制限させるかなり高い電流がFETを介して生じる場合、誘導負荷にストアされたエネルギーを放電させなければならない。FETはオフであるか又はオフにされ得るが、FETは依然として誘導負荷と電源との間の回路内にあり、ストアされたエネルギーはFETを介して放電される。FETを介したインダクタエネルギーの放電は、望ましくないデバイス応力を生じさせる恐れがあり、又は、SOA境界条件に違反し得るためにFETを破壊する可能性さえもある。パワーFET回路の従来の電流制限又はシャットダウンの特定の特徴は、電流オーバーシュートがターンオフ時に生じる可能性があること、又は、FETの電流制限がFETのSOAの境界を超える可能性があることである。

20

**【発明の概要】**

30

**【0004】**

説明する例において、装置が、ドレイン端子、ソース端子、及びゲート端子を有するFETデバイスと、FETのドレイン端子に結合される第1の供給電圧と、FETのソース端子に結合される出力端子と、FETのゲート端子に結合されるバイアス電流供給と、FETのゲート端子に結合される第2の供給電圧と、FETを介して流れる電流に比例する感知電流を出力するために結合される電流感知回路とを含む。感知電流に結合される電流制限コンパレータが、感知電流を所定の制限電流と比較し、ブルダウン電流回路が、FETのゲート端子から電流を除去するために結合され、電流時間導関数回路が感知電流に結合され、感知レート電流を出力し、或る回路が、感知レート電流を受け取るために結合され、バイアス電流供給に結合される。

40

**【図面の簡単な説明】****【0005】**

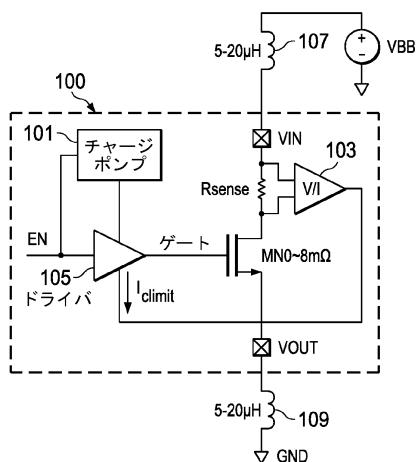

【図1】誘導負荷に結合される、従来のハイサイドパワーFET回路及びドライバデバイスの回路図である。

**【0006】**

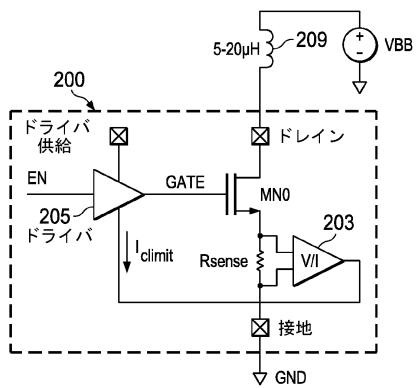

【図2】誘導負荷に結合される、従来のローサイドパワーFET回路及びドライバデバイスの別の回路図である。

**【0007】**

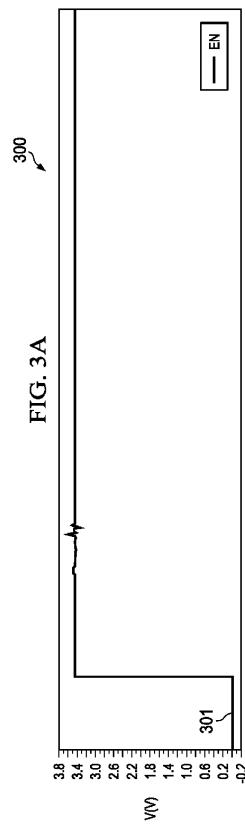

【図3A】従来のパワーFET回路についての電圧のグラフである。

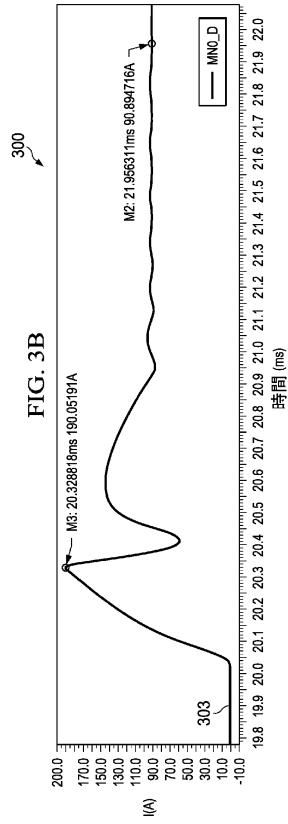

【図3B】従来のパワーFET回路についての電流のグラフである。

50

【0008】

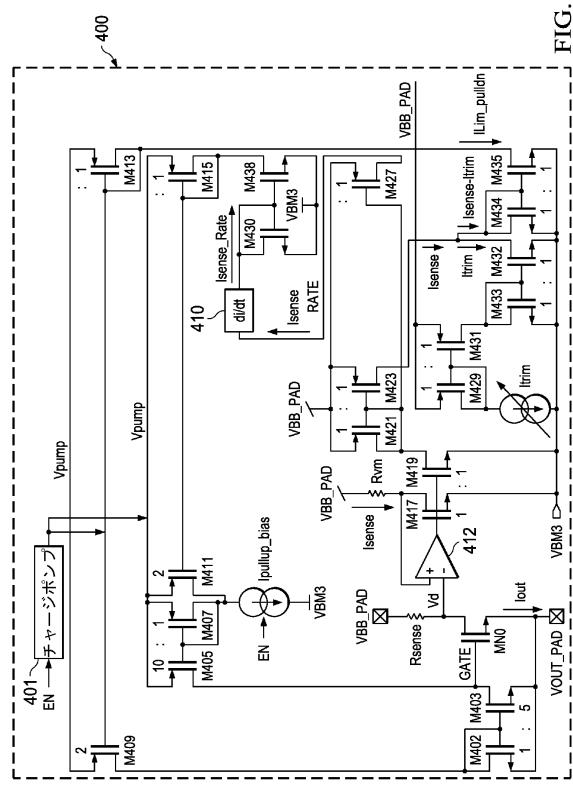

【図4】ハイサイドドライバ構成のパワーFET実施形態の回路図である。

【0009】

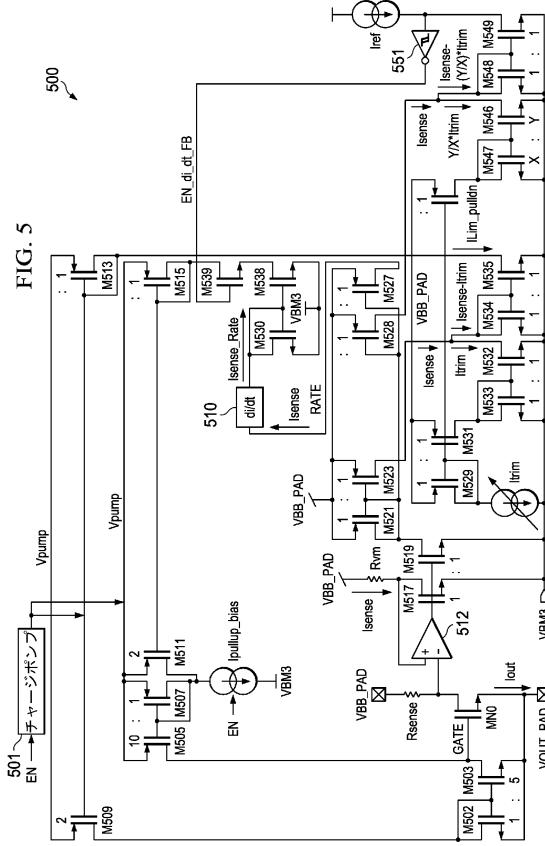

【図5】付加的なパワーFET実施形態の別の回路図である。

【0010】

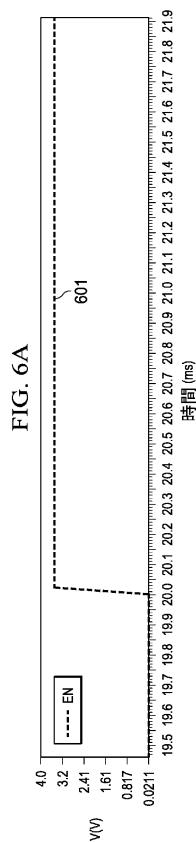

【図6A】例示的なパワーFET回路についての入力電圧のグラフである。

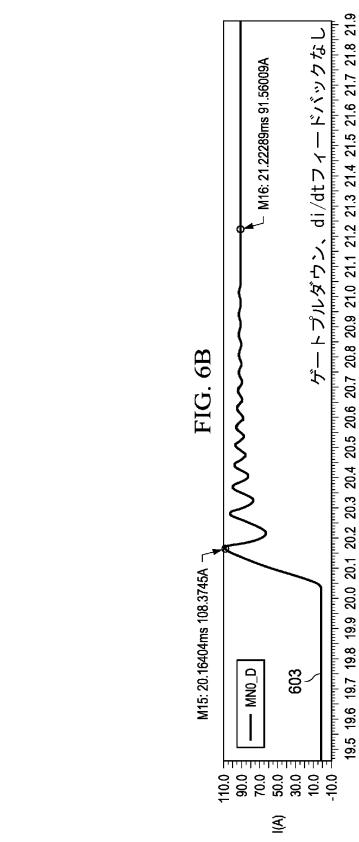

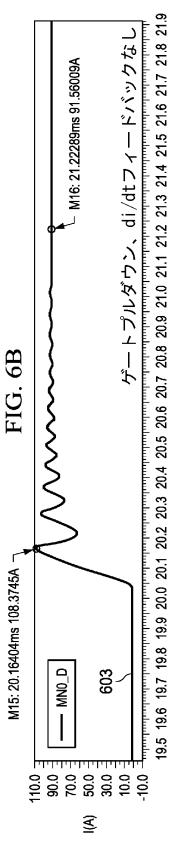

【図6B】例示的なパワーFET回路についての出力電流のグラフである。

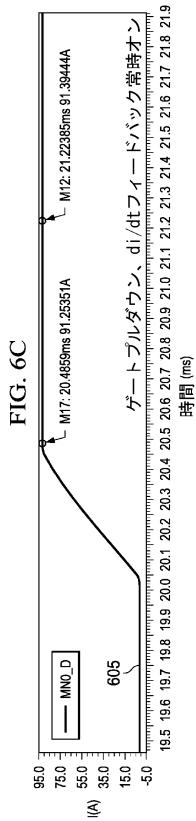

【図6C】例示的なパワーFET回路についての出力電流のグラフである。

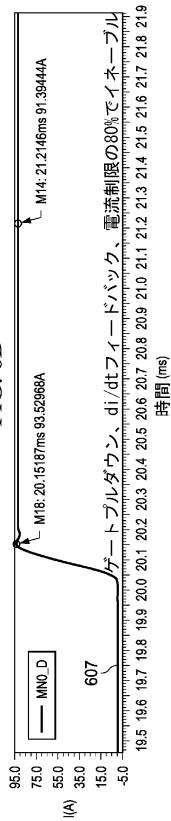

【図6D】例示的なパワーFET回路についての出力電流のグラフである。

【0011】

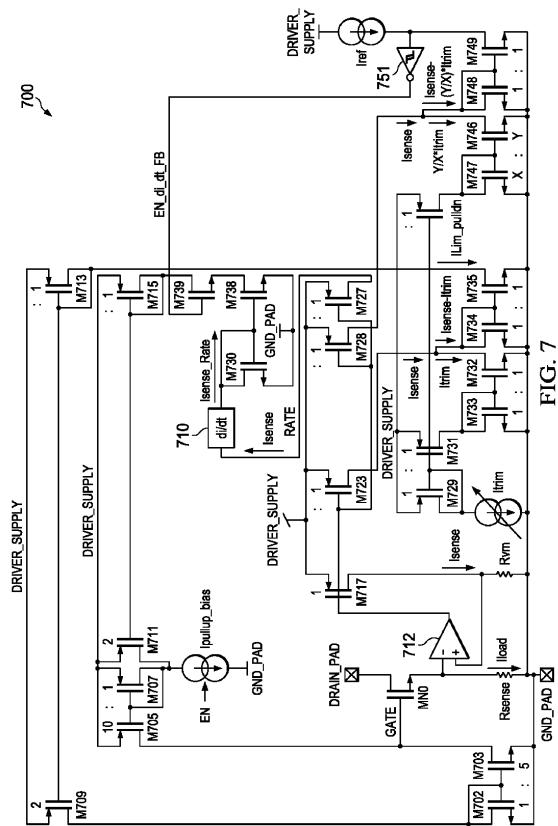

【図7】ローサイドドライバ構成のパワーFET実施形態の回路図である。

【0012】

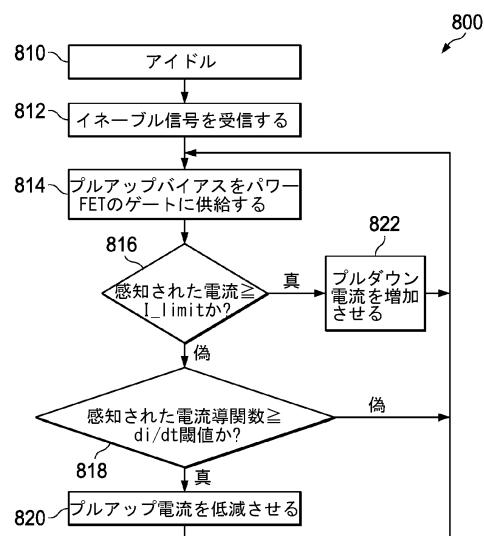

【図8】例示の方法のフローチャートである。

【0013】

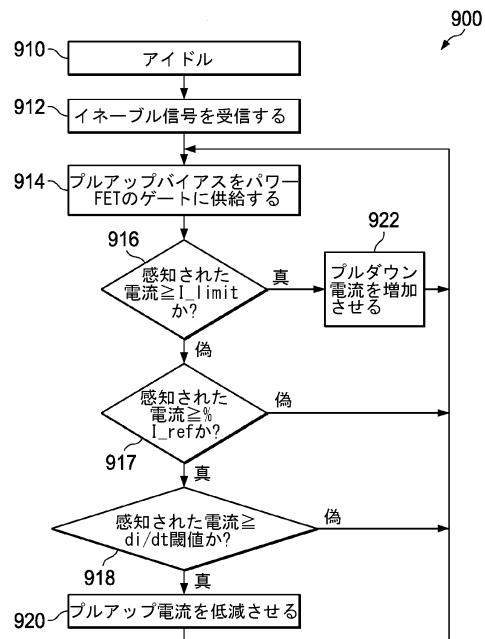

【図9】代替の方法の別のフローチャートである。

【発明を実施するための形態】

【0014】

図面において、対応する数字及び記号は、特に指示されない限り、概して対応する部分を指す。図面は必ずしも一定の縮尺で描かれていない。

【0015】

「結合される」という用語は、介在要素を用いてなされる接続を含み、「結合」される任意の要素の間は付加要素及び様々な接続が存在し得る。

【0016】

図1は、電流を誘導負荷に供給するためにパワーFETを用いる従来の回路の回路図である。図1において、パワーFET MN0が、パワーFETがドレイン端子において電源に結合され、ソース端子から負荷に電流を供給するという点において、「ハイサイド」ドライバとして配置される。図1において、FET MN0はN型FETとして示される。代替の配置において、FET MN0は、ドレイン及びソース端子が逆にされたP型FETとしても配置されてもよい。様々なFETデバイスがパワー応用例に利用可能であり、これらは本実施形態に適用可能である。

【0017】

FETデバイスのゲート導体及びゲート絶縁体は、半導体基板とキャパシタを形成する。パワーFETの場合、ゲートキャパシタンスは非常に大きくなり得る。パワーFETを初期のオフ状態からオン状態に切り替えるためには、ゲートキャパシタを充電させなければならない。その後、FETをオン状態からオフ状態に切り替えるためには、ゲートキャパシタを放電させなければならない。FETのスイッチング速度は回路の適切な動作にとって重要であるため、パワーFETをオン及びオフにするために、しばしばゲートドライバデバイスがFETのゲート端子に結合される。ゲートキャパシタを充電及び放電させるため、並びに、必要に応じて、FETをオン又はオフにするために、スイッチング動作の間、かなりの電流が、パワーFETのゲート端子に供給され得るか又はゲート端子から取り出され得る。

【0018】

図1において、ハイサイドドライバとして負荷を駆動させるための従来のパワーFET回路100が図示されている。パワーFET MN0は、GATEと示されるゲート端子における電圧及び電流に応答して、端子VOUTにおいて電圧及び電流を供給する。FETのドレイン・ソース間電流導通経路に、及びその後、端子VOUTにおける負荷に電流を供給するために、供給電圧VBBが入力端子VINに結合される。ドライバ回路105が付加的なFETデバイスも含み得、ドライバ105は、ENと示される入力イネーブル信号に応答して、FET端子GATEにおいてFETゲート信号を供給する。この例示的配置において、ドライバ回路105はチャージポンプ101から供給される電力を有する。

10

20

30

40

50

チャージポンプ 101 は、 GATE 信号を駆動するために電圧 V<sub>IN</sub> よりも大きな電圧を提供する。端子 V<sub>OUT</sub> における出力電圧は、入力 V<sub>IN</sub> に近い高電圧レベルを取り得る。この出力電圧 V<sub>OUT</sub> は、 FET MN0 のソース端子におけるものである。トランジスタ MN0 をオンにするために、端子 GATE における電圧を、ソース電圧よりトランジスタ閾値電圧 V<sub>t</sub> だけ上に上昇させなければならない。供給電圧を供給電圧 V<sub>IN</sub> より実質的に上の FET GATE 入力まで上昇させることによって、 FET MN0 はドライバ 105 によって常にオンにされ得る。一例において、チャージポンプが、 V<sub>IN</sub> より 13 ボルト上にブーストされたポンプ電圧をゲートドライバ 105 に出力する。

#### 【 0019 】

負荷に電流を供給するとき、 FET MN0 は通常、線形モードで動作される。このモードでのパワー FET の動作において、 V<sub>OUT</sub> は V<sub>IN</sub> とほぼ等しくし得る。

10

#### 【 0020 】

図 1 において、パワー FET MN0 を保護するために電流制限が適用される。例示的なオートモーティブ応用例において、 FET MN0 のソースにおいて出力 V<sub>OUT</sub> に結合されるケーブルが、ヘッドライトなどの負荷 109 に結合され得る。車両事故などに起因して、ヘッドライト又はケーブルが損傷した場合、接地への短絡が生じ得る。これが、図 1 に図示されたケースである。短絡の場合において、出力 V<sub>OUT</sub> において引き込まれた電流は、パワー FET MN0 が安全に導通し得る電流を急速に超える可能性がある。図 1 において、負荷は電球を備えるものとは図示されておらず、接地に短絡するように表されたケーブル 109 を備えるものと図示されている。パワー FET を保護するためにパワー FET MN0 を介して流れる電流を検出及び制限するために、電流感知回路が用いられる。いくつかの応用例において、電流限界に達したとき、パワー FET はディセーブルにされ得る。他の応用例において、電流限界に達したとき、パワー FET は、最大安全電流を導通しながら負荷への電力供給を続行するように動作される。

20

#### 【 0021 】

図 1 において、入力電圧 V<sub>IN</sub> と FET MN0 のドレイン端子との間に感知抵抗器 R<sub>sense</sub> が結合される。抵抗器 R<sub>sense</sub> を介して流れる電流は、出力電流（これは、 FET MN0 を介して流れるドレイン・ソース間電流又は I<sub>ds</sub> 電流でもある）と同じである。したがって、オームの法則により、感知抵抗器 R<sub>sense</sub> で生じる電圧が、 FET 電流に比例する。抵抗器 R<sub>sense</sub> の電圧は、電圧電流 (V/I) 変換器 103 によって電流に変換される。感知された電流が増加するにつれて、図 1 において I<sub>climit</sub> と示される電流は、ドライバ 105 から出力されるゲート電流を変調し、したがって、 GATE 端子への電流を低減する。利用可能な電流を制限することによって、パワー FET MN0 を介して流れるドレイン・ソース間電流を最大レベルに制限し得る。ヘッドライトドライバ応用例などの重要な応用例では、システムは、 FET が最大安全電流で負荷に電流を供給し続けることを必要とし得る。例えば、この条件は、ヘッドライトの初期ターンオンの間、高い突入電流が維持されなければならない始動時にも生じ得る。

30

#### 【 0022 】

図 1 の従来のパワー FET 回路に伴う問題は、立ち下がり信号 EN に応答する際など、 FET MN0 がオフにされたとき、負荷 109 が（特に、誘導負荷を駆動させるとき）放電させる必要があるエネルギーを内部にストアし得ることである。FET のゲートキャパシタンスを放電するための経路がないと、FET がオフになる前に不必要に長い時間が経過し得る。この時間の間、FET は、放電インダクタ（負荷）を備える直列回路内にあり、FET に流れ込む大量の電流に起因して、FET についての SOA 条件を超える I<sub>ds</sub> 電流が生じ得る。

40

#### 【 0023 】

回路 100 は、通常はヘッドライトに結合されるが接地に短絡するように示されたケーブルを表すなど、誘導負荷 109 に結合されるように示されている。オートモーティブ応用例において、負荷は約 5 ~ 20 μH の範囲とし得る。他の負荷が FET MN0 によって駆動され得る。

50

### 【0024】

図2は、ローサイドドライバ応用例についての、従来のパワーFET回路200の回路図である。図2の回路200は、上述した図1の回路100と同様であり、回路100のように動作する、いくつかの構成要素を含む。図2において、ドライバ205、感知抵抗器R sense、電圧電流V/I回路203、及びパワーFET MN0は、いずれも図1の同様の要素に対応し、参照符号は、便宜上、図1における「1XX」から図2における「2XX」に変更されている。図2において、回路200は「ドライバ供給」と示された端子における電圧によって供給される一方で、パワーFET MN0は負荷209に結合されるドレイン端子「ドレイン」を有する。この例示的配置において、負荷は、供給電圧VBBとパワーFETのドレインとの間に直列に結合される。いくつかの例において、この電圧VBBは、鉛酸バッテリから供給される12~13ボルトであり得る。他の例において、24ボルト、48ボルト、6ボルト、或いはより高いか又は低い電圧など、他の電圧が用いられ得る。ヘッドライトスイッチの例において、負荷209は、ヘッドライトと、ヘッドライトにバッテリを接続するケーブルとを含む。負荷209はインダクタとして図示される。例示的なオートモーティブ応用例において、インダクタ209は、5~20μHの範囲にあり得る。回路200は他の負荷も駆動し得る。

10

### 【0025】

それぞれ、図1及び図2のハイサイド配置とローサイド配置との間の違いの1つは、図2におけるFETゲート端子GATEは、図1のようにブーストされた電圧に結合される必要がない点である。図2のローサイドドライバ構成におけるFET MN0のソース端子は、感知抵抗器R senseを介して接地に結合される。FET MN0をオンにするために必要とされるゲート・ソース間電圧は、単に閾値電圧Vtに、接地より上の、感知抵抗器R senseの電圧を加えたものであり、したがってこの例において、ゲート電圧を供給するためにチャージポンプは不要である。

20

### 【0026】

図2の回路の動作において、FET MN0は、ドライバ回路205がイネーブル信号ENを受信したとき少なくともFETについての閾値電圧より上の電圧まで上昇する、ゲート端子GATEにおける電圧に応答して、電流が負荷209を介して流れるようにする。負荷209を介して流れれる電流は、FETによって導通されるドレイン・ソース間電流と同じであり、この同じ電流が、感知抵抗器R senseを介して接地に流れれる。抵抗器R senseの電圧は、オームの法則の作用に起因して、FET MN0を介して流れれる電流に比例する。電圧は、V/I又は電圧電流変換器203によって電流に変換される。FET電流は、制限電流Iclimitを用いてドライバ205から電流を除去することによって制限される。Iclimitは、感知された電流が閾値電流レベルを超える場合、図1におけるハイサイドドライバ回路についての電流制限動作と同様に、ゲート端子GATEにおいてパワーFET MN0に入る電流を減少させる。

30

### 【0027】

図3A及び図3Bは、ターンオン動作における、回路100などのFET回路の電圧入力及び対応する電流の、電圧グラフ及び電流グラフである。図3A及び図3Bの水平軸は、ミリ秒単位の時間を示す。図3Aの垂直軸は、入力端子EN上の立ち上がり電圧をデータライン301で示す。時間20.0において、イネーブル端子は3.4ボルトの立ち上がり電圧を受け取る。データライン303は、FET MN0を介して流れれる電流を図3Bの垂直軸上に示す。この例において、電流限界は90アンペアとなるように構成される。図3Bのデータライン303において、電流は、時間M3:20.3において、特定された電流限界をオーバーシュートし、90アンペアの望ましい電流限界よりも100アンペア高いレベルである、190アンペアを超える最大電流まで立ち上がる。時間M2:21.95において、電流は、ほぼ90アンペアの限界である、90.89アンペアで整定する。電流オーバーシュートが生じるのは、限界（ここでは90アンペア）に達したとき電流制限回路要素がゲート信号を減少させるにもかかわらず、ゲートキャパシタンスを放電させるため及びFET内の電流フローを減少させるために要する時間が、低減された電流

40

50

でパワーFET MN0が動作し得るようになるまで、電流オーバーシュートを発生させ得るためである。

#### 【0028】

図4は、例示の実施形態のパワーFET回路400の回路図である。図4において、ハイサイドドライバ配置が示されている。パワーFET MN0は、出力端子VOUT\_PADにおいて電流及び電圧を負荷に供給するように結合される。高電圧及び高電流処理能力を備え、非常に低いオン抵抗( $R_{DSon}$ )を有するパワーFETは、テキサス・インスツルメンツ・インコーポレーテッドから現在入手可能なNexFET(商標)MOSFETデバイスを含む。NexFET(商標)デバイスは、半導体基板の底部表面にドレインコンタクトを有し、基板の上側表面上にソースコンタクトを有する垂直FETの一種であり、基板内に形成される一つ又は複数のパラレルMOSFETデバイスを含む多くのチャネル領域によって共有され得る共有ドレイン領域を特徴とする。しかしながら、本実施形態は、いずれか1つのパワートランジスタタイプ又はいずれの半導体技術タイプにも限定されず、様々な実施形態が任意のパワーFETデバイスに適用可能である。

10

#### 【0029】

図4において、回路は出力電流 $I_{out}$ を出力する。バッテリ電圧などの供給電圧が、入力端子VBB\_PADに結合され得る。チャージポンプ回路401からの電圧 $V_{pump}$ は、様々な構成要素に結合される。この供給電圧 $V_{pump}$ は、入力端子VBB\_PADにおける電圧を上回って上昇する。図4において、すべての構成要素は、境界400において破線によって示されるように、単一の集積回路上に実装され得る。しかしながら、代替の配置において、構成要素のうちのいくつかが離散構成要素として実装され得、他の構成要素が一つ又は複数の集積回路上に配置される。一例において、パワーFET MN0及び感知抵抗器RsenseがパワーFET集積回路上に製造され、残りの構成要素が別個のドライバ集積回路上に製造された。これらの別個の集積回路は、個々にパッケージングされ得、回路ボード又はモジュール上に搭載され得る。代替の配置において、たとえ構成要素が別個の集積回路上又は別個の集積回路ダイ上に実装されるときでも、マルチチップモジュール(MCM)又はスタッカーダイパッケージなどの先進パッケージング技法を用いて、システム400のための単一のパッケージを形成し得る。本実施形態と共に用いるためのパワーFETは、NexFET(商標)デバイス、パワー応用例に適した垂直FETデバイス、DMOSパワーFET、及びLDMOSパワーFETを含む。本実施形態は、任意のFETデバイスに適用可能である。

20

#### 【0030】

図4において、パワーFET MN0のゲート端子GATEは、これに結合される幾つかの回路を有する。これらの回路は、パワーFETゲート電流及び電圧を供給及び変調する。これらの回路は、ゲートドライバ回路要素を構成する。端子GATEはトランジスタM405からプルアップバイアス電流を受け取り、トランジスタM405はトランジスタM407と共に形成される電流ミラーの一部であるPFETトランジスタであり、電流源「 $I_{pullup_bias}$ 」によってバイアスされている。

30

#### 【0031】

電流源 $I_{pullup_bias}$ は、イネーブル信号ENに応答して、ゲート端子GATEを電圧供給 $V_{pump}$ までプルアップするために用いられる電流を提供する。イネーブル端子EN上で信号が受信されるとき、チャージポンプ401及びプルアップバイアス電流源 $I_{pullup_bias}$ はアクティブになる。トランジスタM405及びM407も、チャージポンプ電圧 $V_{pump}$ からFET MN0のGATE端子に供給される電流を、電流 $I_{pullup_bias}$ の10倍に増加させるために、ここでは10:1として示される電流スケーリングを提供する。電流ミラーにおいて異なるサイズのトランジスタを用いることによって、様々なトランジスタが電流スケーリングを提供し得る。スケーリングフィーチャは、より小さなバイアス及び基準電流源が用いられ得るようにする。附加的な実施形態を形成するために、他のスケーリングファクタが用いられ得る。図4におけるスケーリングファクタは、コロンによって区切られる2つの整数によって、1:1、

40

50

2 : 1、1 : 5、10 : 1などのように示される。

#### 【0032】

また、パワーFET MN0のゲート端子GATEは、電流ミラーを形成するトランジスタM403及びトランジスタM402によって結合され、トランジスタM409によって電圧Vpumpに結合される。トランジスタM413は、M409と共に電流ミラーを形成し、「Llim\_pulldn」と示されるプルダウン電流をゲート端子GATEへとミラーする。

#### 【0033】

電流感知回路が図4に含まれる。バッテリ供給電圧を結合するためのパッドVBB\_PA

Dと、パワーFET MN0のドレイン端子との間に、感知抵抗器Rsenseが結合される。

FETドレン電圧Vdは、電圧電流変換器における演算増幅器412に結合される。演算増幅器及びトランジスタM417は、抵抗器Rvmと共に、電圧電流変換器回路を形成する。演算増幅器412は、負の入力と正の入力との間に仮想接地を備えるフィードバック構成で配置されるため、回路は、正の入力と負の入力との差を最小にするために出力電圧を変調し、トランジスタM417のゲート端子における電圧は、電圧Vdと共に増大又は低減され得る。抵抗器Rvmを介して流れる電流Isenseは、出力電流Ioutに比例し、電流感知機能を提供する。

10

#### 【0034】

感知された電流Isenseは、Isenseをいくつかの他の基準電流レベルと比較することによって、パワーFETの動作を制御するために用いられる。トランジスタM419は、Isenseを、トランジスタM421及びM423によって形成される電流ミラーに、及びその後、トランジスタM432、M433、及びM434を用いて形成されるコンパレータに結合する。「Ltrim」と示される電流源が、トランジスタM429及びM431で形成される電流ミラーによってコンパレータに供給される。トリム電流Ittrimは固定され得、又は調節可能であり得る。例えば、Ittrimは、デジタルアナログ変換器(DAC)によって、Ittrimのための電流を設定するためにデジタル制御ワードが提供され得る。付加的な配置が、電流Ittrimを提供するためのトリム可能電流源又は固定電流源を含む。パラレル電流源をM429に選択的に結合するために書き込み可能レジスタを用いるプログラム可能電流源が、トリム可能電流源Ittrimのために用いられ得る。別の実施形態において、電流源Ittrimは、I2Cバスなどのデジタルバスインターフェース、及び設定可能レジスタ値を用いることによって設定され得る。レジスタに値を書き込むことによって、システムコントローラ又はCPUが電流Ittrimの値を変更し得る。他の実施形態において、値はトリム抵抗器を用いて製造時に設定され得る。更なる実施形態において、電流源Ittrimについての値は固定され得る。トランジスタM433、M432によって形成されるコンパレータは、トランジスタM434及びM435で形成される電流ミラーに結合される。

20

#### 【0035】

動作において、電流Isenseがトリム電流Ittrimより大きいとき、コンパレータはプルダウン電流Llim\_pulldnを出力する。このプルダウン電流は、P型FETデバイスM413、M409によってFETトランジスタMN0のゲートにミラーされ、またトランジスタM402、M403によって形成されるミラーと共に、パワーFET MN0のゲート端子GATEに流れ込む電流を減少させるために用いられ、それによって出力電流Ioutを制御する。Ittrimのための値によって設定される電流限界に達したとき、プルダウン電流を用いて、出力電流Ioutを所望の電流限界に維持し得る。例示的な実施形態400において、様々なトランジスタ及び電流ミラーデバイスが、電流を増加させるためのデバイススケーリングを有する。例えば、M402、M403で形成される電流ミラーは5:1のサイズ比を有し、このサイズ比が、FET MN0のゲートにおけるプルダウン電流を増加させる。同様に、トランジスタM413、M409によって形成される電流ミラーは2:1の比を有する。これらのスケーリングファクタは、特定の応用例の必要に応じて、代替の実施形態を形成するために改変され得る。トランジスタス

30

40

50

ケーリングを用いることによって、感知電流  $I_{sense}$  を出力電流  $I_{out}$  より低くし、ドライバ制御回路要素における電力を節約することが可能である。

#### 【0036】

回路 400 をオンにしようとするとき、イネーブル信号  $E_N$  が、受信され、チャージポンプ 401 をオンにして、電力供給電圧  $V_{pump}$  を出力する。プルアップ電流  $I_{pull\_up\_bias}$  は、トランジスタ M407、M405 によって形成される電流ミラーを介して FET MN0 のゲートに供給される。この例示的な実施形態において、トランジスタ M405、M407 は、FET MN0 のゲート端子 GATE においてプルアップ電流を増加させるために、10:1 のスケーリングを提供する。FET が初期にオフにされるとき、ゲートとソース端子  $Cgs$ との間のゲートキャパシタは完全に放電される。電圧  $V_{pump}$  及びバイアス電流源  $I_{pull\_up\_bias}$  からのプルアップ電流が FET のゲートに供給される際、FET MN0 のソースは、パワー FET MN0 のゲートキャパシタンス  $Cgs$  が充電され、ゲート端子 GATE がパワー FET MN0 の閾値電圧を超える。FET MN0 がオンになるまで、ソースフォロワ構成におけるゲートにおける増大する電圧に従う。FET MN0 のゲート端子 GATE の立ち上がり時間は、バイアス電流  $I_{pull\_up\_bias}$  によって設定される。このプルアップバイアス電流は、製造前、製造後に固定され得、また調節可能又はトリム可能とし得る。10

#### 【0037】

FET MN0 がオンになった後、ゲート電流及び電圧を用いて電流  $I_{out}$  を制御し得る。FET MN0 は、ほとんどの状況について線形モードで動作される。FET がオフする状況においてゲート端子 GATE をプルダウンするための付加的な回路要素が、ゲートを  $V_{OUT\_PAD}$  に結合するための付加的な制御回路要素と共に、トランジスタ M402、M403 を用いてゲートを迅速に放電するために用いられ得る。20

#### 【0038】

端子  $V_{OUT\_PAD}$  において負荷に電流を供給する動作において、抵抗器  $R_{sense}$  及び  $R_{vm}$  は、式(1)及び(2)に従い、出力電流  $I_{out}$  より小さいがこれに比例する電流  $I_{sense}$  を形成するための比で動作する。

$$R_{sense} \times I_{out} = I_{sense} \times R_{vm} \quad (1)$$

$$I_{sense} = I_{out} \times (R_{sense} / R_{vm}) \quad (2)$$

#### 【0039】

感知された電流  $I_{sense}$  が、調節可能電流  $I_{trim}$  より大きいか又は  $I_{trim}$  に等しいとき、トランジスタ M432、M433、M434、M435 で形成される電流コンパレータが、プルダウン電流  $I_{lim\_pull\_ldn}$  を出力し始める。コンパレータ回路は図 4 に図示されるような差 ( $I_{sense} - I_{trim}$ ) を形成し、この差は、 $I_{lim\_pull\_ldn}$  となるようにミラーされる。電流限界に達するときの出力電流  $I_{out}$  対トリム及びプルダウン電流の関係は、式(3)によって与えられる。30

$$I_{out(limit)} = (R_{vm}/R_{sense}) \times (I_{trim} + I_{lim\_pulldn}) \quad (3)$$

#### 【0040】

トリム電流  $I_{trim}$  の値をアレンジすることによって、出力電流  $I_{out}$  の電流制限を制御及び設定し得る。回路要素におけるトランジスタのサイズは、回路における様々な電流を比率で示すように改変され得る。例えば、トランジスタ M413 及び M409 は 2 対 1 の比を有し、トランジスタ M403 及び M402 は 5 対 1 の比を有するため、出力電流  $I_{out}$  は回路における他の電流よりもかなり大きくなれる。40

#### 【0041】

電流制限回路要素に加えて、図 4 における実施形態は、電流時間導関数制御回路 410 も特徴とする。実施形態において、パワー FET MN0 は、電流制限動作の間に減少されるか又はなくされる電流オーバーシュートを有し得る。従来の電流制限回路要素において観察される出力電流オーバーシュートは、実施形態を用いることによってなくされるか又は大幅に減少される。これは、まず、パワー FET を流れる電流が電流制限に達する前に、感知された電流における急速なレート増加を検出することによって、また、出力電流増50

加のレートを減少させることによって達成される。出力電流  $I_{out}$  が電流制限に達すると、出力電流における増加のレートが減少される。電流制限に近付いた場合、電流レート増加を減少させることにより、出力電流を電流制限で整定させることが可能であるが、オーバーシュートはないか又はオーバーシュートはほとんどない。したがって、出力電流における増加のレートを感知することによって、及び、電流制限に近付いた場合であってもパワー FET を介する電流増加のレートを変調させることによって、出力電流は電流制限に安全に到達し得、従来の電流制限回路要素の大幅な電流オーバーシュートなしに電流制限で整定し得る。このように、FET は、損傷又は寿命の短縮から FET を保護する SOA 条件内で動作され得る。

#### 【 0 0 4 2 】

図 4において、電流時間導関数又は「 $d_i / dt$ 」関数 410 は、トランジスタ M421 及びトランジスタ M427 を含む電流ミラーから感知電流  $I_{sense}$  を受け取る。電流時間導関数 410 は、感知電流  $I_{sense}$  の増加のレートを決定し、増加のレートは出力電流  $I_{out}$  の増加のレートに比例する。トランジスタ M430、M438 で形成される電流ミラーが、トランジスタ M415、M411 を用いて、出力電流  $I_{sense\_Rate}$  をブルアップバイアス電流回路要素に結合する。電流  $I_{sense\_Rate}$  は M438 を介して接地へ流れ、パワー FET MN0 の GATE 端子に流れ込むブルアップ電流  $I_{pullupbias}$  を減少させる。

#### 【 0 0 4 3 】

動作において、感知された電流  $I_{sense}$  の増加のレートが閾値を超えるとき、電流時間導関数回路 410 は、電流  $I_{sense\_Rate}$  を出力し得、FET MN0 のゲートに供給されるブルアップ電流を減少させ得る。FET MN0 のゲートに供給される電力を減少させると、FET ゲート端子 GATE のスルーレートが減少し、出力電流  $I_{out}$  の増加のレートが遅くなる。電流制限に達した後、出力電流の変化のレートは再び下がり得（電流  $I_{out}$  は電流制限において固定され、もはや増加しないため）、電流時間導関数回路 410 はもはや  $I_{sense\_rate}$  を出力しなくなり、もはや出力電流に影響を与えない。出力電流  $I_{out}$  が制限電流において固定されるか又はほぼ固定された後、電流時間導関数回路 410 は、感知された電流レートにおけるいかなる増加も検出しなくなる。

#### 【 0 0 4 4 】

電流時間導関数回路 410 は、電流時間又は  $d_i / dt$  感知に有用な様々な回路を用いて実装され得る。 $I_{sense}$  の電流電圧変換、並びに、その後周期的にサンプリングされるキャパシタを用いる抵抗容量性感知が用いられ得る。ホール効果センサ、コイル、電流ループ、及びその他のフィールド感知手法が用いられ得る。電流レート閾値は、固定され得、プログラム可能であり得、又は、製造が完了した後の較正動作の間にプログラムされるワンタイムプログラム可能値であり得る。電流レート閾値を設定するためにトリム可能抵抗器が用いられ得る。I2C インターフェースバスなどのバスを介してコントローラ又はプロセッサによってアクセス可能なレジスタが、電流増加レート閾値についてのプログラム可能値を提供し得る。

#### 【 0 0 4 5 】

図 4 に示される実施形態において、電流時間導関数回路 410 は常にアクティブである。この配置は出力電流  $I_{out}$  における望ましい低減されたオーバーシュートを提供し、一方で、電流時間導関数回路 410 は、立ち上がり時間を通して FET MN0 のスルーレートも低減し得、そのため、FET のターンオン時間は増大されることになる。いくつかの応用例において、この影響は、初期パワーアップ動作において負荷への突入電流を制限し得るか、又はシステムの始動を遅くし得るため、望ましくない可能性がある。

#### 【 0 0 4 6 】

図 5 は、代替実施形態 500 の回路図である。図 5において、構成要素の多くは、図 4 の実施形態と同様であり、図 4 の実施形態と同じように機能する。これらの構成要素に対して、参照符号は図 4 に図示されたものと同様であるが、便宜上、先頭の数字が「4」から

10

20

30

40

50

「5」に変更されている。

#### 【0047】

図5において、パワーFET MN0が、パワーパッドVBB\_PADにおける供給電圧と出力端子VOUT\_PADとの間に結合される。パワーFET MN0は、図4に関して上記で説明したものと同じように、パワーFET MN0のターンオン及びターンオフを制御するためのゲート電流を提供するために、ゲート端子GATEへの供給及びバイアス回路要素結合を有する。チャージポンプ501は、イネーブル信号ENを受信するとき供給電圧Vpumpを出力する。プルアップバイアス電流供給Ipullup\_biasは、信号ENによってもイネーブルされる。

#### 【0048】

図4に関して上記で説明したように配され、動作する演算増幅器512を含む電流感知回路に加えて、図5において、時間導関数回路510は、イネーブルスイッチ、トランジスタM539によって、プルアップバイアス回路要素及びプルアップ電流源Ipullup\_biasに結合される。付加的なイネーブル回路が、制御信号EN\_didt\_FBを出力する。この制御信号は、電流Isense(及び、それに対応してIout)が電流制限に近付いている間に、電流制限の選択されたパーセンテージまで増加したときのみ、スイッチM539に、didt感知回路である電流時間導関数回路510のIsense\_Rate出力を、トランジスタM505、M507のプルアップバイアス供給回路に結合させるために用いられる。

#### 【0049】

図5において、基準電流Iref、トランジスタM546、M547、M548、M549、制限電流Ittrim、及び感知された電流Isenseによって、コンパレータ回路が形成される。トランジスタM528は、感知された電流Isenseを、トランジスタM547、M546によって形成される電流ミラーを含むコンパレータにミラーする。トリム電流Ittrimは、図5に図示されるスケーリングファクタ「X」及び「Y」によって示されるような、トランジスタM547及びM546のそれぞれのサイズによってミラー及びスケーリングされる。このスケーリングされたトリム電流は、感知された電流Isenseから減じられる。この差分電流は、その後、トランジスタM548及びM549によって、シュミットトリガデバイス551の入力端子にミラーされ、ここで基準電流Irefと比較される。Isenseと(Y/X)×Ittrimのスケーリングされた積との間の差分電流がIrefより大きいとき、シュミットトリガ551はインバータであるため、シュミットトリガ551への入力は少なくなり、出力EN\_didt\_FBは高に向かう。シュミットトリガデバイス551は、感知電流Isenseとスケーリングされたトリム電流(Y/X)×Ittrimとの間の差がIrefより大きいか又は等しいときにのみ、パルスを出力する。

#### 【0050】

イネーブル信号EN\_didt\_FBは、式(4)の不等式が満たされるとき高に向かう。

$$Isense - (Y/X) \times Ittrim > Iref \quad (4)$$

#### 【0051】

シュミットトリガ551から出力されるイネーブル信号EN\_didt\_FBは、トランジスタM539に結合される。トランジスタM539は、電流時間導関数回路510の出力、電流Isense\_rateを、プルアップバイアス回路要素に選択的に結合するように動作する。このようにして、電流時間導関数回路510の出力は、感知された電流Isenseとスケーリングされたトリム電流(Y/X)×Ittrimとの間の差が、基準電流Irefに合致するか又は基準電流Irefを超えるとき、FET MN0ゲート端子GATEの立ち上がり時間のその部分に対してのみ用いられる。感知された電流がこの閾値まで立ち上がらない動作の場合、時間導関数回路510はパワーFET MN0の電流に影響を与えない。出力電流が立ち上がり、感知された電流Isenseとスケーリングされたトリム電流(Y/X)×Ittrimとの間の差が基準電流Irefに等しいか

10

20

30

40

50

又は基準電流  $I_{ref}$  を超える場合、時間導関数回路 510 はプルアップバイアス回路要素に結合される。次いで、電流  $I_{sense\_rate}$  は、電流が電流制限に向かって立ち上がる際に、電流  $I_{out}$  における増加レートを減少させる。

#### 【0052】

イネーブル信号  $EN\_di\_dt\_FB$  は、電流制限の所定のパーセンテージにおいてアクティブになるように調節され得る。上記で説明したように、電流制限は電流源  $Ir_{trim}$  を調節することによって設定され、電流時間導関数回路をイネーブルするための電流制限のパーセンテージは、トランジスタ M546、M547 の相対的サイズを選択することによってトランジスタスケーリング比  $Y : X$  を用いて設定され得る。また、代替の配置において、スケーリングは、DAC 回路に結合されるアドレス指定可能レジスタなどの書き込み可能記憶回路を提供することによって達成され得る。I<sub>2</sub>C シリアルインターフェースなどの外部プロセッサへのインターフェースが、スケーリングファクタが記憶され得るように構成され得る。イネーブル信号の異なる動作は、電流源  $Ir_f$  及び  $Ir_{trim}$  を調節することによって調節され得る。

10

#### 【0053】

図 6A～図 6D は、図 4 及び図 5 に図示されるような、例示の実施形態動作の 4 つのグラフである。図 6A～図 6D のすべてにおいて、水平軸は時間をミリ秒単位でプロットする。図 6A において、イネーブル信号電圧  $EN$  は垂直軸上にプロットされる。データライン 601 は、イネーブル端子における電圧をプロットする。時間 20.0 ミリ秒において、イネーブル信号  $EN$  は、図 4 及び図 5 の回路実施形態において、ほぼゼロ電圧から、プルアップバイアス回路及びチャージポンプにパワー FET をオンにさせるのに十分な電圧まで立ち上がる。

20

#### 【0054】

図 6B～図 6D において、パワー FET を介する電流は、垂直軸上にアンペア (A) 単位でプロットされる。図 6B におけるデータライン 603 は、図 4 及び図 5 に図示されるようなプルダウン制限電流回路を備えるパワー FET の FET ドレイン電流応答を示すが、電流時間導関数回路要素はイネーブルされていない。図 6B において、時間 M15:20.16404 で、電流が 108 アンペアを超えるまで立ち上がるデータライン 603 に応答して、オーバーシュートが発生する。時間 21.0 で発振が収まるまで、数サイクルの間、発振は約 90 アンペアの望ましい電流制限をオーバーシュートし続け、電流  $I_{out}$  は、時間 M16:21.22289 において、90 アンペアの望ましい電流制限に近い約 91 アンペアで最終的に整定する。

30

#### 【0055】

図 6B において、出力電流  $I_{out}$  は、電流時間導関数回路 410 が常に動作している図 4 の実施形態について示されている。データライン 605 は、パワー FET のドレイン電流を表す。時間 20.05 において、出力電流はイネーブル信号に応答して立ち上がりを開始するが、増加レート（傾斜）は電流時間導関数回路によって制限され、そのため、ほぼ時間 M17:20.485 で、91.39 アンペアは約 90 アンペアの制限をわずかに上回る 91.39 アンペアの制限において最終電流に達する。図 6A のデータライン 603 とは対照的に、図 6B における電流出力データライン 605 は、目に見えるオーバーシュートを有さない。電流時間導関数又は  $di/dt$  回路は電流のオーバーシュートをなくしているが、パワー FET を介する出力電流の立ち上がり時間も実質的に増加されている。

40

#### 【0056】

図 6D において、データライン 607 は図 5 の実施形態のためのドレイン電流を示し、電流時間導関数回路は、感知された電流が電流制限値のパーセンテージ閾値に達した後にのみイネーブルされる。閾値は、80% など、最大電流又は制限電流のパーセンテージであり得る。代替例において、他のパーセンテージ閾値も用いられ得る。図 6D において、電流は時間 20.05 で急速に開始し、時間 20.5 までに約 90 アンペアの最大電流制限に達した。データライン 605 において、時間 M18:20.15187 で、約 93 アンペアへのわずかなオーバーシュートが発生するが、このオーバーシュートは 90 アンペア

50

の望ましい制限近くへと即時に整定し、図 6 C にプロットされた図 4 の実施形態に関するものと同じ整定電流である、91.39 アンペアで整定する。パワー F E T についてのタンオン時間は、図 6 D のプロットでは大幅に短い。特定の応用例の要件に応じて、図 4 及び図 5 の適切な実施形態が用いられ得る。電流制限、パーセンテージ閾値、及び電流レート増加閾値は、いずれも、特定の設計要件に適切なように付加的な実施形態を形成するために改変され得る。

#### 【 0 0 5 7 】

図 7 は、ローサイドドライバ応用例についての実施形態の別の回路図である。図 7 において、図 4 及び図 5 における同様の要素に対応する要素には、図 7 では参照番号の最初の数字が「7」であることを除き、同様の参照番号が与えられる。回路 700 は、回路ボード又はモジュール上で、離散構成要素を用いて、マルチチップモジュールを用いて、又は、高度に集積されたデバイスを形成するために単一パッケージにおいて複数のダイを用いて、单一の集積回路として実装され得る。一配置において、パワー F E T M N 0 及び感知抵抗器 R s e n s e が単一の集積回路に形成され得、残りのデバイスが、F E T のためにドライバ I C を提供するために第 2 の別個の集積回路に形成される。単一又は複数の集積回路におけるデバイスの他の組み合わせも可能である。

10

#### 【 0 0 5 8 】

図 7において、パワー F E T M N 0 は、「D R A I N \_ P A D」と示される入力パッドに結合されるドレン端子を有する。一応用例において、この端子は負荷の一方の端部に結合され得る。パワー F E T M N 0 は、パッド「G N D \_ P A D」において負荷と接地電位との間に結合される、ドレンからソースへの電流導通経路を有し、そのため、図 7 はローサイドドライバ配置を図示する。パワー F E T M N 0 のゲートへの様々な電圧及び電流供給のための供給電圧は、「D R I V E R \_ S U P P L Y」と示される。図 2 に関連して上記で説明したように、ローサイドドライバ構成の場合、F E T M N 0 のゲートは、F E T をオンにするためのブースト電圧を必要としない。電源と入力 D R A I N \_ P A D における F E T M N 0 のドレンとの間に、負荷（図 7 には図示せず）が結合され得る。F E T M N 0 は、イネーブル信号 E N に応答して、負荷を介して接地へ電流を流すことができる。

20

#### 【 0 0 5 9 】

図 7 における電流制限回路要素は、ハイサイドドライバ配置について図 5 に示されたものと同様であり、同じ方式で動作する。図 7 において、イネーブル信号 E N は、バイアス電流源 I p u l l u p \_ b i a s をオンにする。トランジスタ M 707 及び M 705 で形成される電流ミラーは、このバイアス電流をパワー F E T M N 0 のゲートに提供することになる。トランジスタ M 705、M 707 は、バイアス電流を 10 : 1 でスケーリングするように配され、そのため、トランジスタゲート端子 G A T E における電流は、電流源 I p u l l u p \_ b i a s より大きくなる。端子 D R I V E R \_ S U P P L Y における電圧も、G A T E と示されるゲート端子に結合される。

30

#### 【 0 0 6 0 】

ドレン・ソース間電流がパワー F E T M N 0 内を流れているとき、感知抵抗器 R s e n s e に F E T 電流に比例する電圧が現れる。演算増幅器、トランジスタ M 717、及び抵抗器 R v m は、負荷電流 I l o a d に比例する感知電流を出力するように配される。電流感知回路の抵抗器比及び動作は、図 4 に関して上記で説明したものと同じである。感知電流 I s e n s e は、トランジスタ M 729、M 731、M 733、M 732、M 734、及び M 735 によって形成されるコンパレータによって、トリム可能電流源 I t r i m と比較され、次いで、出力される差分電流 I L i m \_ p u l l d n を用いて、電流制限に達した後ゲート端子 G A T E に流れ込む電流を制御する。電流 I L i m \_ p u l l d n は、電流 I s e n s e とトリム可能電流源 I t r i m との間の差であり、トリム可能電流源 I t r i m の値を変更することによって設定され得る。トランジスタ M 713、M 709 及び M 702、M 703 は、制限電流を G A T E 端子からのプルダウンに結合する 2 つの電流ミラーを形成する。トランジスタのスケーリングは、トランジスタ M 703 からのトランジ

40

50

ンジスタM N 0のゲートにおける電流が電流I L i m \_ p u l l d nより大きくなるように用いられる。トランジスタスケーリングを用いることによって、電力及び面積を節約するため、I t r i mなどのより小さな電流源を用いられ得る。

#### 【0061】

図7の実施形態は、図5に関して上記で説明したように、パワーF E Tを介する電流が電流制限に向かって立ち上がる際にこの電流における増加のレートを低減するため、及び、オーバーシュート電流を防ぐための、電流時間導関数回路要素も含む。トランジスタM 7 4 7、M 7 4 6、M 7 4 8、M 7 4 9によって形成されるコンパレータ回路要素、及び基準電流I r e fは、感知された電流からトリム電流I t r i mを引いてトランジスタスケーリング比Y / Xを掛けたものが、基準電流I r e fより大きい場合、シミュットトリガ7 5 1に、イネーブルスイッチM 7 3 9に対してイネーブル信号E N \_ d i \_ d t \_ F Bを出力させる。基準電流I r e f及びスケーリングファクタY / Xを設定することによって、80%など、制限電流のパーセンテージが閾値として設定され得る。感知された電流I s e n s eがこの閾値に達した後にのみ、パワーF E T M N 0のゲートへの電流を低減するために電流時間導関数回路7 1 0が結合される。

10

#### 【0062】

電流時間導関数回路7 1 0は、ゲート端子G A T Eに入力されるp u l l \_ u pバイアス電流を低減するために結合される電流I s e n s e \_ R a t eを出力する。感知された電流I s e n s eにおける、閾値より大きい立ち上がりをd i / d t回路7 1 0が検出したとき、I s e n s e \_ r a t eが出力される。このようにして、F E T M N 0を介する電流の増加のレートは、電流制限に達するまで制御されて、オーバーシュートが防止される。電流源I r e f、I t r i m、I p u l l u p \_ b i a s、並びにスケーリングファクタX及びYは、固定され得、又は調節可能であり得る。D A C回路及び書き込み可能レジスタを用いて形成されるプログラム可能電流源が用いられ得る。不揮発性記憶レジスタは、製造時又は使用中にプログラム可能である。プログラム可能レジスタに書き込むために、I 2 Cインターフェースなどのインターフェースバスが用いられ得る。トリム可能抵抗器又はヒューズも用いられ得る。

20

#### 【0063】

図8は、例示の方法のフローチャートである。図8の方法において、時間導関数回路又はd i / d tが常時アクティブである。図8において、この方法はステップ8 1 0のアイドルで開始する。ステップ8 1 2において、イネーブル信号が受信される。次いでこの方法は、ステップ8 1 4に移行し、電圧及びバイアス電流がパワーF E Tのゲート端子に結合される。パワーF E Tは、バイアス電流に応答してターンオンを開始する。ゲートキャパシタンスを充電するために十分な電流がゲート端子に入力された後、パワーF E Tは線形モード動作に入る。

30

#### 【0064】

ステップ8 1 6において、パワーF E Tを介して流れる電流が感知される。感知された電流は電流制限と比較される。ステップ8 1 6における比較が真である場合、この方法はステップ8 2 2に移行する。ステップ8 1 6における比較が偽である場合、この方法はステップ8 1 8に移行する。

40

#### 【0065】

ステップ8 1 8において、感知された電流又はd i / d tの時間導関数が閾値と比較される。感知された電流の増加のレートが閾値より大きい場合、この方法はステップ8 2 0に移行する。この比較が偽である場合、この方法はステップ8 1 4に戻り、続行される。

#### 【0066】

ステップ8 2 0において、ステップ8 1 8における比較が真であったため、パワーF E Tを介して流れる電流における増加のレートは低減される。これは、上記で説明したように、プルアップバイアス電流を低減することによってなされ得る。次いで、この方法はステップ8 1 4に戻り、続行される。

#### 【0067】

50

ステップ 816 における比較が真である場合、すなわち電流制限に達している場合、ステップ 822 に入る。ステップ 822 において、パワー FET を介して流れる電流は、ゲート端子から  $V_{out}$  端子へと電流をプルダウンすることによって制限される。ゲートキャパシタンスを放電させることによって、パワー FET は、低減されたゲート電圧と、パワー FET を介して流れる低減された電流とを有することになる。この方法は、最大制限まで制限された電流を用いて動作を続行する。

#### 【0068】

感知された電流が最大制限に達した後、電流  $d_i/dt$  における増加のレートはゼロになり、そのため、電流がプルダウン電流によって制限されるとき、ステップ 818 における比較は常に偽となる。

10

#### 【0069】

図 8 の方法ステップは、ステップの 1 つのあり得る順序を示しているが、ステップの順序は代替の実施形態を形成するために改変され得る。例えば、ステップ 816、818 における比較は、異なる順序で実施され得るか、又は図 8 に示された順序の代わりに同時に実施され得る。

#### 【0070】

図 9 は、代替方法の別のフロー チャートである。図 9 において、方法 900 は、電流時間導関数を選択的にイネーブルにすることを含む。ステップ 910 において、この方法はアイドルステップにおいて開始する。ステップ 912 において、イネーブル信号が受信される。ステップ 914 において、電力がパワー FET に供給され、電圧及びバイアス電流がパワー FET のゲート端子に印加されて、ゲート端子をプルアップし、パワー FET をオンにする。

20

#### 【0071】

ステップ 916 において、電流センサが、パワー FET を介して流れる電流を感知する。感知された電流が電流制限を超える場合、この方法はステップ 922 に移行する。比較が偽である場合、この方法はステップ 917 へと続行される。

#### 【0072】

ステップ 917 において、感知された電流が基準電流と比較される。基準電流は、調節され得るか、又は電流制限の或るパーセンテージである電流に設定され得る。例えば、一つの試みにおいて、基準電流は電流制限の約 80% に設定された。

30

#### 【0073】

比較がステップ 917 の通りである場合、この方法はステップ 918 に移行する。ステップ 918 において、感知された電流における増加のレートが、電流時間導関数演算における閾値と比較される。感知された電流における変化のレートが閾値を超えて増大している場合、この方法はステップ 920 に移行する。ステップ 920 において、プルアップ電流が低減され、パワー FET に流れる電流における増加のレートが低減される。次いで、この方法はステップ 914 へと続き、続行される。

#### 【0074】

ステップ 918 における比較が偽である場合、この方法はステップ 914 に移行し、続行される。ステップ 916 における比較が真である場合、電流制限に達しており、この方法はステップ 922 に移行する。ステップ 922 において、プルダウン電流が増加され、パワー FET を介して流れる電流は、出力端子における出力電流を最大電流まで制限されたまま維持するために低減される。

40

#### 【0075】

図 9 の方法ステップは、ステップの 1 つのあり得る順序を図示しているが、ステップの順序は代替の実施形態を形成するために改変され得る。例えば、ステップ 916 及び 917 における比較は、異なる順序で、又は図 9 に示された順序の代わりに同時になされ得る。

#### 【0076】

例示の実施形態及び配置は、電流が継続的に制限されるパワー FET 回路を形成する。説明する例において、FET デバイスに結合される電流感知回路要素が、FET を介して流

50

れる電流に対応する感知電流を供給する。感知電流はコンパレータに結合される。所定の制限電流が感知電流と比較される。所定の制限電流に達していることをコンパレータが示すとき、FETを介して流れる電流を制限するためにプルダウン電流が印加される。感知電流は電流時間導関数回路にも供給される。感知電流における増加のレートは、閾値レートと比較される。感知電流における増加のレートが閾値レートを超えるとき、出力電流における増加のレートを低減させるために、FETへのバイアス電流が低減される。

#### 【0077】

更なる例において、電流時間導関数回路とバイアス電流供給との間にイネーブル回路が結合され、電流レートコンパレータ回路が、感知電流及び基準電流に結合され、イネーブル信号をイネーブル回路に出力する。

10

#### 【0078】

付加的な例において、プルダウン電流回路をイネーブルにするために、電力制限コンパレータから出力が結合される。

#### 【0079】

少なくとも1つの代替例において、装置は、感知レート電流に応答してFETのゲート端子へのバイアス電流を低減させるための回路要素をさらに含む。

#### 【0080】

別の例において、装置は、プログラム可能な所定の制限電流を含む。更なる例において、所定の制限電流は書き込み可能記憶回路に記憶される。更なる例において、電流時間導関数回路は、感知された電流の増加レートが所定のしきい値を超えるとき感知レート電流を出力するためのレート検出回路を含む。

20

#### 【0081】

更なる例において、装置は、感知レート電流とバイアス電流供給との間に結合されるイネーブル回路と、感知電流及び基準電流に結合され、イネーブル回路にイネーブル信号を出力する電流レートコンパレータ回路とをさらに含む。別の例において、電流レートコンパレータ回路はスケーリングファクタを含み、電流レートコンパレータ回路は、感知電流と、スケーリングファクタ及び所定の制限電流の乗算との間の差を、基準電流と比較する。

#### 【0082】

別の例において、スケーリングファクタはプログラム可能である。別の付加的な例において、プログラム可能記憶回路はスケーリングファクタを記憶する。さらに別の例において、プログラム可能記憶回路に対処するために、外部バスインターフェースが結合される。

30

#### 【0083】

例示の方法は、イネーブル信号を受信すること、供給電圧端子と電流を供給するための出力端子との間でFETの電流導通経路を結合すること、電圧及びプルアップバイアス電流をFETのゲート端子に結合すること、FETを介して流れる電流を感知すること、FETを介して流れる感知された電流を電流制限と比較すること、FETを介して流れる電流を比較することに応答して、FETのゲート端子における電流を低減することを含む。この方法は、FETを介して流れる電流の増加レートをレート増加閾値と比較すること、及び、FETを介して流れる電流の増加レートを比較することに応答してFETのゲート端子へのプルアップ電流を低減することをさらに含む。

40

#### 【0084】

少なくとも1つの例において、この方法はさらに、FETを介して流れる電流を電流制限の所定のパーセンテージである閾値と比較すること、及び、比較することに応答してFETのゲート端子へのプルアップ電流の低減をイネーブルにすることを含む。別の例において、この方法はさらに、FETのゲート端子における電流を低減した後、出力端子における電流を電流制限で供給するようにFETを動作させることを含む。

#### 【0085】

別の例において、この方法はさらに、FETのゲート端子における電流を低減した後、出力端子における電流を所定の電流制限で供給するようにFETを動作させることを含む。

#### 【0086】

50

別の例において、供給電圧端子と電流を供給するための出力端子との間で F E T の電流導通経路を結合する方法はさらに、F E T のドレイン端子を電圧供給に結合すること、及び、F E T のソース端子を出力端子に結合することを含む。

【 0 0 8 7 】

さらに別の例において、供給電圧端子と電流を供給するための出力端子との間で F E T の電流導通経路を結合する方法はさらに、電流を供給するための端子にドレイン端子を結合すること、及び、接地電位を受け取るための端子にソース端子を結合することを含む。

【 0 0 8 8 】

さらなる例において、この方法は、供給電圧より大きい増加された電圧を供給することをさらに含む。別の例において、F E T を介して流れる感知された電流を、所定の電流制限と比較する方法は、感知された電流を、書き込み可能記憶回路に記憶された調節可能電流制限と比較することを含む。

10

【 0 0 8 9 】

さらに別の例において、集積回路が、電圧供給と負荷との間に結合される電流導通経路を有するパワー F E T のゲートを駆動するための端子と、供給電圧を集積回路に結合するための電圧入力端子と、パワー F E T のゲート端子を駆動するための端子に、及び増大された電力供給を結合するための入力端子に結合されるプルアップバイアス回路と、パワー F E T に流れる電流に比例する電圧を受け取るために端子に結合され、感知された電流出力を有する電流感知回路と、感知された電流を制限電流と比較する電流制限コンパレータと、電流制限コンパレータに、及びパワー F E T のゲートを駆動するための端子に結合されるプルダウン電流回路と、感知された電流に結合される電流時間導関数回路と、電流時間導関数回路に、及びプルアップバイアス回路に結合されるプルアップ電流低減回路とを含む。

20

【 0 0 9 0 】

別の例において、集積回路は、調節可能トリム電流供給によって設定される制限電流をさらに含む。

【 0 0 9 1 】

特許請求の範囲内で、説明された実施形態における改変が可能であり、他の実施形態が可能である。

30

40

50

【図面】

【図 1】

【図 2】

FIG. 2

【図 3 A】

【図 3 B】

【図4】

【図5】

【図6A】

【図6B】

【図 6 C】

【図 6 D】

【 四 7 】

【 义 8 】

FIG. 8

【図 9】

FIG. 9

10

20

30

40

50

---

フロントページの続き

サウスウェスタン ブールバード 8749

(72)発明者 アビドゥル ラーマン

アメリカ合衆国 75081 テキサス州 リチャードソン, カスケーダ ドライブ 445

審査官 橋本 和志

(56)参考文献 米国特許出願公開第2016/0028307(US, A1)

特開2015-050925(JP, A)

(58)調査した分野 (Int.Cl., DB名)

H03K 17/16