(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-524858

(P2006-524858A)

(43) 公表日 平成18年11月2日(2006.11.2)

(51) Int.C1.

GO6F 12/04

(2006.01)

F 1

GO6F 12/04

530

テーマコード(参考)

5B06O

審査請求 未請求 予備審査請求 未請求 (全 19 頁)

(21) 出願番号 特願2006-506835 (P2006-506835)

(86) (22) 出願日 平成16年4月13日 (2004.4.13)

(85) 翻訳文提出日 平成17年10月17日 (2005.10.17)

(86) 國際出願番号 PCT/IB2004/050426

(87) 國際公開番号 WO2004/092960

(87) 國際公開日 平成16年10月28日 (2004.10.28)

(31) 優先権主張番号 03101037.4

(32) 優先日 平成15年4月16日 (2003.4.16)

(33) 優先権主張国 歐州特許庁 (EP)

(71) 出願人 590000248

コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ

Koninklijke Philips Electronics N. V.

オランダ国 5621 ベーー アインドーフェン フルーネヴァウツウェッハ

1

Groenewoudseweg 1, 5

621 BA Eindhoven, The Netherlands

(74) 代理人 100075812

弁理士 吉武 賢次

(74) 代理人 100088889

弁理士 橋谷 英俊

最終頁に続く

(54) 【発明の名称】メモリに記憶されたデータに圧縮を使用するデータ処理装置

## (57) 【要約】

画像のようなデータは、それぞれのデータアドレスに個々に関連付けられたデータアイテム(画素)で構成される。データを表現する圧縮ブロックはメモリシステムに記憶される。圧縮データアイテムを表現する各ブロックは、それぞれのデータのアドレスのサブレンジ内のデータアドレスに関連付けられる。各ブロックは、マルチアドレス転送のための優先開始アドレスから始まる。各ブロックのアドレスのサブレンジは、優先開始アドレス間のアドレス間隔に対応する長さを有し、圧縮のためにブロックの間に特定のブロックによって占有されていないメモリアドレスをそのまま残す。伸長器はプロセシングエレメントとメモリシステムとの間に結合される。伸長器は、プロセシングエレメントがブロックへのアクセスを必要とするときに動的にメモリシステムから必要な1個のブロックのマルチアドレスメモリ転送を開始し、次の1個のブロックのための優先開始アドレスまでブロックの直ぐ後に続くメモリアドレスを転送中に転送されないままに残す。転送されたデータは伸長され、プロセッサへ渡される。

A

B

**【特許請求の範囲】****【請求項 1】**

データアドレスのレンジ内のそれぞれのデータアドレスに個々に関連付けられたデータアイテムを処理する装置にして、

前記データアイテムを表現する圧縮ブロックがメモリシステムに記憶され、

メモリアドレスが前記メモリシステムのマルチアドレス転送のためのそれぞれの優先開始アドレスから開始する各ブロックによって占有され、

各ブロックが前記レンジのそれぞれのサブレンジ内のデータアドレスに関連付けられた圧縮データアイテムを表現し、

前記サブレンジが連続的に隣接し、

特定のサブレンジのそれそれが、前記特定のサブレンジ内で前記データアイテムを表現する特定のブロックのアドレスが開始する優先開始アドレスと、次の連続的なサブレンジのための次の1個のブロックのアドレスが開始する優先開始アドレスとの間のアドレス間隔に対応する長さを有し、

プロックとプロックの間に前記特定のプロックによって占有されないメモリアドレスを残す、装置であって、

前記優先開始アドレスだけから開始し、または、前記優先開始アドレス以外のアドレスから開始するよりもオーバーヘッドが小さい、選択可能な長さのマルチアドレスメモリ転送を実行する能力を備えた前記メモリシステムと、

前記データアイテムを処理するプロセシングエレメントと、

前記プロセシングエレメントと前記メモリシステムとの間に結合された伸長器と、を具備し、

前記伸長器が、前記プロセシングエレメントが前記プロックへのアクセスを必要とするときに動的に前記メモリシステムから必要な1個のプロックのマルチアドレスメモリ転送を開始し、次の1個のプロックのための優先開始アドレスまで前記プロックの直ぐ後に続くメモリアドレスを転送中に転送されない状態で残し、前記データアイテムを前記プロセシングエレメントへ渡す前に、前記必要な1個のプロックからの前記データアイテムを伸長するように構成される、装置。

**【請求項 2】**

前記プロセシングエレメントが、転送されるべき前記必要な1個のプロックの前記優先開始アドレスから開始する連続的により小さいアドレスを必要とする一連の種々の伸長オプションから選択された伸長オプションを、前記伸長器へ指示するように構成され、

前記伸長器が指示された伸長オプションに応じて前記メモリ転送の前記長さを設定する、

請求項1に記載の装置。

**【請求項 3】**

前記伸長器が、前記必要な1個のプロックの長さに応じて選択されたワード数が転送完了したときに前記必要な1個のプロックの前記マルチアドレスメモリ転送を終了するため、前記メモリシステムへ信号を送信するように構成される、請求項1に記載の装置。

**【請求項 4】**

前記伸長器が前記マルチアドレスメモリ転送から前記必要な1個のプロックの前記長さを表現する情報を取り出すように構成され、

前記伸長器が前記情報に応じて前記信号を発生する、

請求項3に記載の装置。

**【請求項 5】**

前記伸長器が、

前記必要な1個のプロックよりも先に取り出されたプロックのマルチアドレスメモリ転送から前記必要な1個のプロックの前記長さを表現する情報を取り出し、

前記必要な1個のプロックのための前記マルチアドレスメモリ転送の開始時に前記情報から得られた転送長さ選択信号を前記メモリシステムへ送信するように構成される、

10

20

30

40

50

請求項 1 に記載の装置。

【請求項 6】

前記サブレンジの前記長さが連続的な優先開始アドレスの間の間隔以上であり、

前記伸長器が前記ブロックの前記長さに条件付きで応じて前記必要な 1 個のブロックのための後のマルチアドレスメモリ転送を開始するように構成される、

請求項 1 に記載の装置。

【請求項 7】

各ブロックが互いに独立して伸長可能である複数のサブブロックを含み、

各サブブロックが前記ブロックの前記サブレンジのそれぞれの等しいサイズの部分に対応し、

前記伸長器が前記マルチアドレスメモリ転送中に読み出された圧縮データの前記サブブロックをバッファリングするバッファメモリ領域と前記サブブロックから連続的に伸長されたデータを格納する中間メモリ領域とを具備し、

前記伸長器が前記メモリ転送中に読み出されたそれぞれのサブブロックからの前記伸長データを前記中間メモリ内で連続して相互に交換する、

請求項 6 に記載の装置。

【請求項 8】

前記伸長器が非可逆ブロック圧縮に対応する伸長を適用するように構成される、請求項 1 に記載の装置。

【請求項 9】

前記伸長器が可変長ブロック圧縮に対応する伸長を適用するように構成される、請求項 1 に記載の装置。

【請求項 10】

前記サブレンジが相互に等しい長さを有する、請求項 1 に記載の装置。

【請求項 11】

優先開始アドレスのペアの間の間隔に等しい長さを有する前記サブレンジのそれぞれに関連付けられた前記データアイテムを圧縮する圧縮器を具備し、

前記圧縮器が前記サブレンジの 1 個ずつに関連付けられた前記データアイテムを、前記ブロックの対応する 1 個に圧縮し、

前記圧縮器が前記ブロックの 1 個ずつのための対応するマルチアドレスメモリ転送を使用して前記圧縮ブロックを前記メモリシステムに格納するように構成され、

各転送が前記優先開始アドレスの対応する 1 個から始まり、

前記伸長器が各ブロックの格納の終了時に、前記ブロックが要求されないときに次の優先開始アドレスまで書き込むことなく、前記マルチアドレスメモリ転送を終了する、

請求項 1 に記載の装置。

【請求項 12】

前記プロセシングエレメントが圧縮のための前記データアイテムを計算し、

前記圧縮器が前記プロセシングエレメントから圧縮のための前記データアイテムを受信するように構成される、

請求項 1 に記載の装置。

【請求項 13】

前記圧縮器が前記メモリシステムへアクセスするため利用可能な帯域幅の動的に測定されたレベルに応じて前記データの圧縮のための圧縮率を適応させるように構成される、請求項 1 に記載の装置。

【請求項 14】

各データアイテムがデータアドレスのレンジ内のそれぞれのデータアドレスに関連付けられたデータアイテムの組を処理する方法であって、

マルチアドレスメモリ転送が独占的に開始される、または、前記開始アドレス以外のアドレスからよりもオーバーヘッドが小さい、等間隔の優先開始アドレスの部分集合を含むメモリアドレスを有するメモリシステムを準備し、

10

20

30

40

50

圧縮ブロックを前記メモリシステムに格納し、前記ブロックの1個ずつのため使用されるアドレスが前記優先開始アドレスの対応する1個から開始し、各ブロックが前記レンジのそれぞれのサブレンジ内のデータアドレスに関連付けられた圧縮データアイテムを表現し、前記サブレンジが連續的に隣接し、特定のサブレンジのそれぞれが、前記特定のサブレンジ内で前記データアイテムを表現する特定のブロックが開始する優先開始アドレスと、次の連續的なサブレンジのための次の1個のブロックが開始する優先開始アドレスとの間のアドレス間隔に対応する長さを有し、ブロックとブロックの間に前記特定のブロックによって占有されないメモリアドレスを残す、方法。

【請求項 15】

前記ブロックから得られた圧縮データアイテムを処理し、

10

必要な1個のブロックが格納され始める前記優先開始アドレスから開始するマルチアドレスメモリ転送を使用して、前記処理のため前記メモリシステムから前記必要な1個のブロックを取り出し、

前記必要な1個のブロックの長さに応じて前記必要な1個のブロックのための前記マルチアドレスメモリ転送を終了し、前記必要な1個のブロックのため使用されたアドレスの直ぐ後に続くメモリアドレスの内容を転送されないまま残す、

請求項14に記載の方法。

【請求項 16】

前記マルチアドレスメモリ転送における転送のため前記必要な1個のブロックの長さを表現する情報を前記必要な1個のブロックと共に前記メモリシステムに格納する、請求項14に記載の方法。

20

【請求項 17】

論理的に先行する1個のブロックのためのマルチアドレスメモリ転送における転送のため、前記マルチアドレスメモリ転送における転送のため前記必要な1個のブロックの長さを表現する情報を、前記必要な1個のブロックから先行するデータアイテムの前記処理の間にデータアイテムの通常処理が始まる前記論理的に先行する1個のブロックと共に格納する、請求項14に記載の方法。

【請求項 18】

前記論理的に先行する1個のブロックから前記情報を読み出し、

前記必要な1個のブロックのための前記マルチアドレスメモリ転送の開始時に前記情報に応じて選択された転送長さ選択信号を前記メモリシステムへ送信する、

30

請求項17に記載の方法。

【請求項 19】

非圧縮データの非可逆ブロック圧縮が前記ブロックを生成するため使用される、請求項14に記載の方法。

【請求項 20】

非圧縮データの可変長ブロック圧縮が前記ブロックを生成するため使用される、請求項14に記載の方法。

【請求項 21】

前記可変長ブロック圧縮の圧縮率が前記メモリシステムにアクセスするための動的に利用可能な帯域幅に応じて動的に調節される、請求項20に記載の方法。

40

【請求項 22】

請求項14から21のいずれか一項に記載のメモリ転送および伸長を制御する機械命令を含む、コンピュータプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はメモリに記憶されたデータに圧縮を使用するデータ処理装置に関する。

【背景技術】

【0002】

50

米国特許第6,173,381号から、バスを介して接続されたプロセッサおよびシステムメモリを備えたデータ処理システムは知られている。画像データのようなデータは、圧縮または非圧縮形式でシステムメモリに記憶される。プロセッサは、システムメモリとの間でデータを書き込み、読み出すときに、データを圧縮し、圧縮データを伸長する集積メモリコントローラを介してシステムメモリに接続される。米国特許第6,173,381号は、圧縮形式でのデータの記憶が非圧縮形式の同じデータのために必要なメモリロケーションよりも少ないメモリロケーションを占有するので、メモリ占有およびバス帯域幅を削減するために圧縮が使用される方法を教示する。

#### 【0003】

圧縮形式でのデータ記憶は、処理がデータの範囲内の様々なロケーションのアドレスを必要とするときに、データの処理を妨げる可能性がある。圧縮、特に、可変長圧縮のために、非圧縮データの様々な要素間のアドレス間隔は圧縮データにおいて保存されない。米国特許第6,173,381号は、プロセッサと集積メモリコントローラとの間でキャッシュメモリを使用し、伸長データをキャッシュに記憶することによりこの問題を解決する。かくして、伸長データは、伸長データの仮想アドレスを使用してキャッシュメモリ内でプロセッサによってアドレス指定可能である。集積メモリコントローラは、圧縮データがキャッシュフェッチまたはライトバックの間に適切なシステムメモリアドレスで読み出しと書き込みが行われることを保証する。米国特許第6,173,381号は、どのようにして圧縮データが適切にアドレス指定されるかについては開示していないが、おそらく、プロセッサによって出された伸長データの仮想アドレスが圧縮形式のデータの物理アドレスに変換され、データがこれらの物理アドレスへ書き込まれ、物理アドレスから読み出されるのであろう。仮想アドレスの物理アドレスへの変換は処理の速度を落とす。

#### 【0004】

多数の最新データ処理システムにおいて、データは、たとえば、64～128バイトまでの多数のアドレス可能なワードを含むブロックが單一アドレスごとに応じてメモリとプロセッサとの間で転送されるバス転送中に取り出される。このような転送は、典型的に互いに等間隔である特定の開始アドレス（以下では、優先開始アドレスと呼ぶ）、たとえば、128バイトのブロック境界のアドレス（多数の下位ビットが0であるアドレス）から開始する必要があり、転送が優先開始アドレスではないアドレスから始まらなければならないならば、少なくとも余分なオーバーヘッドが必要になる。転送の長さは選択可能である。これはメモリ帯域幅を増加させる。従来のプロセッサでは、このワード数は圧縮パラメータと無関係である。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

特に、本発明の目的は、データをアクセスするため必要なバス帯域幅が、データの様々なアドレス指定可能な部分へのアクセスを複雑化することなく、圧縮によって削減されたデータ処理装置および方法を提供することである。

#### 【0006】

特に、本発明の目的は、画像および／または音声データにアクセスするため必要なバス帯域幅が、データの様々なアドレス指定可能な部分へのアクセスを複雑化することなく、圧縮によって削減されたデータ処理装置および方法を提供することである。

#### 【0007】

特に、本発明の目的は、伸長データを使用するプロセスのため使用されるバス帯域幅が動的に適応させられるデータ処理装置および方法を提供することである。

#### 【課題を解決するための手段】

#### 【0008】

本発明によるデータ処理装置は請求項1に記載されている。この装置は、x、yアドレスに関連付けられた画像の画素、または、サンプリング時点 $t_n$ に関連付けられた時間的データのような、データアドレスのレンジ内のそれぞれのデータアドレスに個々に関連付

10

20

30

40

50

けられたデータアイテムを処理する。データアドレスのレンジのそれぞれのサブレンジからのデータアイテムを個々に表現する圧縮ブロックが使用される。サブレンジの長さは、マルチアドレスメモリ転送のための優先開始メモリアドレスのペアの間の間隔に対応するように選択される。好ましくは、各サブレンジは同じ長さを有する。圧縮ブロックはメモリシステムに記憶され、それぞれが優先開始メモリアドレスから始まるので、次のブロックの開始メモリアドレスまでのアドレス間隔は、ブロック内のデータアイテムに関連付けられたデータアドレスのサブレンジの長さに対応する。

#### 【0009】

かくして、ブロックが転送完了したときに終了するマルチアドレスメモリ転送を使用することにより、ブロックを格納し取り出すためのメモリアクセス帯域幅を削減することが可能になる。ブロックの開始アドレスの間の間隔は非圧縮データの場合と同じであるので、転送の開始アドレスは、たとえば、データアドレスの上位部を利用することにより、必要な非圧縮データアイテムのデータアドレスから直接的に決定される。その結果として、圧縮ブロックが記憶されるメモリアドレスのレンジは、非圧縮データアイテムの場合に必要とされるレンジと実質的に同じである。したがって、占有されたメモリのアドレスレンジの削減は実現されないが、帯域幅使用量だけが削減される。

#### 【0010】

プロセシングエレメントは、フィルタリングのような処理演算をこれらのデータアイテムに適用する。典型的に、プロセシングエレメントは、(たぶん、あるオフセットで修正された)データアドレスを用いてデータアイテムをアドレス指定するが、プロセッサは、たとえば、次のデータアイテムが必要であることを単に示すだけで隣接したデータアドレスを有するデータアイテムを呼び出すことにより、そのデータアドレスを非明示的にのみ使用することが可能である。好ましくは、伸長ブロック内のすべてのデータアドレスに対する伸長データは、このような取り出しのためバッファに記憶されるが、或いは、ブロック内のアドレス指定されたデータだけをその都度伸長することが可能である。メモリシステムは、たとえば、メモリバスが付属する单一の半導体メモリであるか、または、アドレスに応答してデータを供給するため協働するメモリの組み合わせである。

#### 【0011】

圧縮データのブロックが伸長のため取り出されるとき、マルチアドレスメモリ転送の長さは実際のブロックサイズに応じて選択される。メモリ転送中に、転送は、次のブロックの開始までのデータが転送完了する前に、圧縮データのブロックからのデータが転送完了したときに終了する。かくして、圧縮データのブロックは最小バス帯域幅で取り出され、他の圧縮データのブロックのサイズの知識を必要とすることなくアドレス指定される。

#### 【0012】

データがまとめて圧縮ブロックに圧縮されたアドレスのサブレンジの長さは、好ましくは、連続した優先開始メモリアドレスのペアの間の間隔と同じである。これは、メモリバス利用の効率を高め、メモリアクセスレイテンシーを削減する可能性がある。しかし、本発明を逸脱することなく、サブレンジは、連続した優先開始メモリアドレスの間の複数の間隔に拡張される。これにより、圧縮率が高くなるので、メモリ帯域幅が減少する。この場合、複数のマルチアドレスメモリ転送が1個のブロックを転送するため使用される。

#### 【0013】

圧縮データのブロックの長さに関する情報は、好ましくは、ブロックと共に記憶される。したがって、これらの長さは、ブロックが転送されたときに、さらなるメモリアドレッシングを必要とすることなく、自動的に利用可能になる。一実施形態では、圧縮データのブロックの長さ情報はブロック自体と共に記憶される。かくして、信号がブロック自体にある情報に基づいて転送を終了させるため発生される。別の実施形態では、論理的に次の圧縮データのブロックの長さ情報は圧縮データのブロックと共に記憶される。(論理的に次のブロックは、そのプロセシングエレメントによって次にアクセスされるブロックを意味し、たとえば、ブロックは、隣接した画像領域の画像データを符号化するとき、論理的に互いに隣り合う)。したがって、長さ情報は、ブロックがアドレス指定される前に、ブ

10

20

30

40

50

ロックのための転送長さを設定するため利用できるようになる。これは、転送長さが各転送の開始時に設定されるべきときに役立つ。

【0014】

好ましくは、伸長の品質が長さの長いブロックと短いブロックを使用することにより適応されるスケーラブル伸長技術が使用される。かくして、帯域幅使用量は、ブロックからのデータの転送の長さを適応させることにより、伸長品質を犠牲にして動的に適応される。

【0015】

好ましくは、特に、データが人間の知覚の表現（たとえば、画像データまたは音声データ）を対象とするとき、非可逆圧縮が使用される。非可逆圧縮後、データは一般に伸長によって正確に再現できないが、それは、圧縮率に応じて、かなりの程度またはそれほどでなくとも同じ知覚内容を伝える。一実施形態では、圧縮率は、動的に利用可能なメモリ帯域幅に応じて、動的に適応される。

【0016】

別の実施形態では、異なる伸長オプションが利用可能であり、使用するデータを様々に徐々に減少させると、再現されるデータの精度が徐々に低下するので、メモリ転送をより早く終了することにより、精度は低下するが、使用される帯域幅が少なくなる。

【発明を実施するための最良の形態】

【0017】

本発明の上記ならびにその他の目的と有利な態様は添付図面を使用して説明される。

20

【0018】

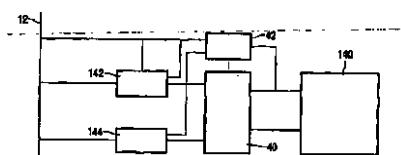

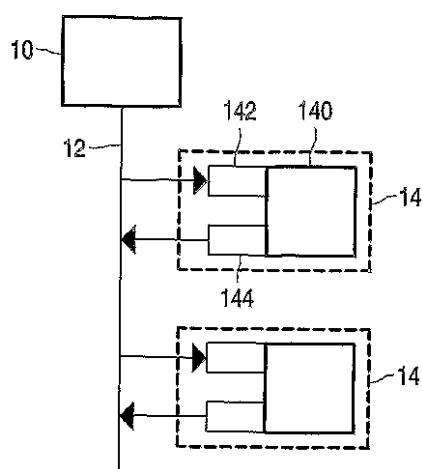

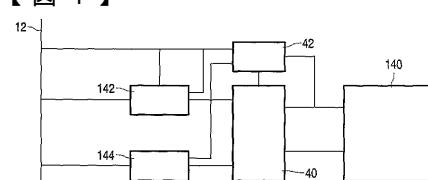

図1は、バス12によって相互接続されたメモリ10と多数台のプロセシングエレメント14（一実施例として2台だけが表されている）とを備えたデータ処理装置を表す。プロセシングエレメント14は、プロセッサ140、伸長器142および圧縮器144を含む。プロセッサ140は、伸長器142および圧縮器144を介してバス12に結合される。本願のコンテキストでは、メモリ10およびバス12は、メモリ10内のデータにアクセスするメモリシステムの一部であるといわれる。

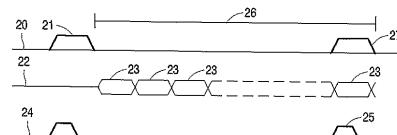

【0019】

図2は、図1の装置の動作中に、バス12を介してメモリ10によって生じるメモリ転送を説明する。一実施例として、図2は、別個のアドレス信号20、データ信号22およびエンド信号24を例示する。メモリ10からのデータの読み出しありは書き込みを行うため、プロセシングエレメント14は、最初に、アドレス信号20にブロックアドレス21を出力する。次に、多数のデータワード23がそのブロックアドレス21に対して転送される。読み出し動作の場合、データワード23は、ブロックアドレス21から始まるアドレスをもつ連続的なメモリロケーションからのデータワードである。書き込み動作の場合、データワード23は、ブロックアドレス21から始まるアドレスをもつ連続的なメモリロケーションに書き込まれるべきプロセシングエレメント14からのデータワードである。

30

【0020】

多数のデータワード23の転送後、プロセシングエレメント14は、ブロックアドレス21に対するメモリ転送の終了と、次のブロックアドレス27での次のメモリ転送のためのバス12の可用性を示すエンド信号25を発生する。かくして、データワード23はタイムスロット26の間に送信され、その長さはプロセシングエレメント14によって制御される。（実際的な実施では、アドレス信号20、データ信号22、および／または、エンド信号24とは異なるタイプの信号が使用されるが、同じ情報を表現する。たとえば、エンド信号は転送の開始時に送信される長さコードによって表現される）。

40

【0021】

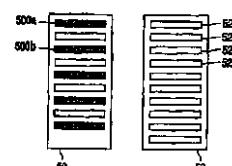

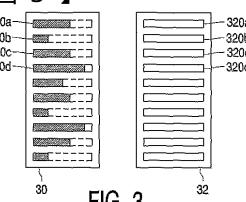

図3は、メモリ10における実際のメモリ占有30と、プロセッサ140から見えるような仮想メモリ占有32とを表す。ブロック300a-dに編成されたメモリ10が表され、ブロック300a-dは上下に表されている。ブロックの長さは、様々なブロックア

50

ドレス 21 によってアドレス指定される連續的なロケーションの間のワード数に対応する。典型的に、長さは 2 のべき乗であり、たとえば、1 ブロック当たり 64 ワードまたは 128 ワードである。

#### 【 0022 】

一実施形態では、マルチアドレスメモリ転送がブロック境界アドレスだから、たとえば、アドレスの下位 7 または 8 ビットがゼロである 128 バイトまたは 256 バイト離れたアドレスから開始するように構成されたメモリ 10 ( 本質的に知られている ) が使用される。マルチアドレスメモリ転送の要求に応答して、メモリは、最初に、メモリ内で連續的にアドレス指定するロケーションと同等の効果をもたらす信号を発生し、それらのロケーションのアドレスはアドレスの下位ビットに異なる値をもつ。このようなメモリシステムのアーキテクチャは、ラインの開始からのこのタイプのアクセスに対して ( バス利用率およびレイテンシーの観点で ) 最適な性能を出すように設計される。これは、読み出しと書き込みの両方に当てはまる。本実施形態における開始アドレスは用語「優先開始アドレス」と呼ばれるが、実際には、それらは事実上マルチアドレスメモリ転送の場合に限り可能な開始アドレスである。

#### 【 0023 】

別の実施形態では、マルチアドレスメモリ転送の開始アドレスの最下位部がオプションとして、少なくとも余分なメモリクロックサイクルを犠牲にして、マルチアドレスメモリ転送の開始アドレスを選択するため使用されるメモリ ( 本質的に知られている ) が使用される。この場合、信号は、この余分なクロックサイクルを使用するためではなく、適応された開始アドレスのため 1 個以上の余分なクロックサイクルを使用することなく、最小オーバーヘッドで標準的な開始アドレスから直ぐにマルチアドレスメモリ転送を開始するため、メモリ 10 へ送信される。用語「優先開始アドレス」は本実施形態ではこれらの標準的なアドレスを表すために使用される。当然ながら、両方の実施形態は、最大転送長さが連續的な優先開始アドレスの間の間隔によって定められるので、転送されるべきブロックが 2 個以上の開始アドレスに広がるならば、新しいマルチアドレス転送が優先開始アドレスごとに開始されなければならないさらなる実施形態があるが、本発明はこのようなさらなる実施形態に限定されない。

#### 【 0024 】

好ましくは、圧縮ブロックサイズは、非圧縮データの連續的なブロックの間の間隔がマルチアドレスメモリ転送の開始アドレスのペアの間の間隔に等しくなるように選択される。多数の圧縮アルゴリズムでは、ブロックサイズは調節可能であり、または、圧縮ブロックはより大きなブロックに結合されるので、メモリアーキテクチャによって規定されるような所要ブロックサイズが実現される。以下で説明するように、圧縮ブロックサイズは、このメモリシステムのブロックサイズの整数倍に設定してもよい。ブロックからの圧縮データが伸長されるとき、伸長データの各ブロックは、メモリ 10 内の優先開始アドレスのペアの間の間隔に対応する長さを有する。好ましくは、伸長データの全ブロックは同じ長さを有する。

#### 【 0025 】

圧縮データによって占有された実際のメモリ占有 30 におけるこれらのメモリロケーションは斜線領域で示されている。実際のメモリ占有 30 に表されているように、可変長圧縮が使用されるとき、メモリ転送ユニット 300 a - d の様々な部分が圧縮データによって占有されずに残される。

#### 【 0026 】

プロセシングエレメント 14 は伸長器 142 および圧縮器 144 を含む。伸長器 142 は、圧縮データのブロックのブロックアドレス 21 を供給し、アドレス指定されたブロックからのすべての圧縮データの転送が終わり、すべての物理的なメモリ転送ユニットの内容の転送が終わる前にメモリ転送を終了するためエンド信号 25 を発生することにより、バス 12 を介してメモリ 10 から圧縮データを取り出す。伸長器 142 はアドレス指定されたブロックから取り出されたデータを伸長し、伸長データをプロセッサ 140 へ供給す

る。

#### 【0027】

同様に、圧縮器144はプロセッサ140によって生成されたデータを圧縮し、バス12を介して圧縮データをメモリ10へ書き込む。この場合に、圧縮器144は、圧縮データのブロックの单一ブロックアドレス21を供給し、圧縮ブロックからの圧縮データワードを送信し、圧縮データを表現するワード数が転送完了し、物理的なメモリ転送ユニット内の全ワードが上書き完了する前に、ブロックアドレス21の転送を終了するため信号を送信する。

#### 【0028】

プロセッサ140は伸長データのアドレスを用いてブロック内のデータをアドレス指定する。すなわち、データアドレスは一般に伸長ブロックのブロックアドレスと伸長ブロック内のワードアドレスとにより構成される。ワードアドレスは所定の伸長ブロックサイズまでの任意の値をとる。したがって、プロセッサ140から、アドレス空間は仮想メモリ占有32に表されるように見え、各ブロック320a-dは同じ所定数のロケーションを占有する。プロセッサ140が読み出し要求を出すとき、それはデータアドレスを伸長器142へ供給する。アドレス指定されたデータがキャッシュされるまで、伸長器142はバス12を介してメモリ10をアドレス指定するためデータアドレスのブロックアドレス部を使用する。続いて、伸長器142はアドレス指定されたブロックから、圧縮ブロックを表現するために必要な実際のワード数を取り出し、メモリ転送はこの実際の数が転送完了したときに、しかし、一般には所定のブロックの長さの全体が転送完了する前に終了される。伸長器142は取り出されたデータを伸長し、プロセッサ140からのデータアドレスによってアドレス指定されたデータを選択し、選択されたデータをプロセッサ140へ返す。

#### 【0029】

好みしくは、伸長器142は、伸長ブロックの全データアドレスのデータを記憶するバッファメモリ（別個に表されていない）を含む。ブロックが伸長されたとき、伸長データはこれらの全ロケーションに書き込まれ、プロセッサ140によってアドレス指定されたデータはこれらのロケーションからプロセッサ140へ供給される。或いは、その都度にデータからのアドレス指定されたワードだけが、または、アドレス指定されたワードを含むワードの部分集合が伸長される。一般に、1ワードだけでなく、ブロックの全ワードを伸長するために追加的な努力は殆ど不要であり、全ワードをバッファリングすることにより、アクセスレイテンシーは平均的に減少する。しかし、一実施形態では、圧縮ブロックは、互いに独立して伸長可能であるサブブロックにより構成されることが理解されるであろう。この場合に、1個のサブブロックからのデータが必要であるとき、メモリシステム10からの新しいブロックをフェッチすることなく、1個のサブブロックの伸長データは、バッファメモリ内の同じブロックからの別のサブブロックのデータを上書きする。

#### 【0030】

プロセッサ140がデータを書き込むとき、プロセッサ140は、書き込みデータのため圧縮器144によって使用されるデータアドレスを供給する。典型的に、圧縮器144は、完全な非圧縮ブロックからのデータを格納し、データアドレスによってアドレス指定されたアドレスでこの非圧縮データを置き換えるため書き込みデータを使用し、その後で、データを圧縮し、プロセッサ140によって使用されるデータアドレスからのブロックアドレスを使用して圧縮データをメモリ10に書き込む。圧縮器144は、ブロックアドレスの圧縮データが転送完了し、一般に、連続的なブロックアドレスの間の間隔に対応する所定数のワードがメモリ10へ転送完了する前に、転送を終了する。

#### 【0031】

その結果として、プロセッサ140が実質的にすべての伸長データをアドレス指定するとき、プロセシングエレメント14とメモリ10との間でバス12を介して転送されるべきワード数は圧縮データの総ワード数よりも少なく、他の転送のためより多くのバスとメモリの帯域幅が残される。圧縮データによって占有されるメモリ空間は、一般に圧縮データ

10

20

30

40

50

タを使用しても削減されないが、その理由は、非占有空間は、伸長ブロックの使用されたブロックアドレスが圧縮ブロックを取り出すためのブロックアドレスとして使用することを可能にするため、メモリ10内の各圧縮ブロックの背後に残されるからである。

#### 【0032】

一実施形態では、圧縮ビデオ画像はメモリ内の複数の連続した圧縮ブロックに分散して記憶される。伸長後、プロセッサ140は、この画像の画素を個別にアドレス指定する。この場合、圧縮画像によって占有されたメモリロケーションの最小アドレスと最大アドレスとの間の間隔は、非圧縮画像を記憶するために必要とされる間隔と実質的に同じであり、この場合もその理由は、使用されていないメモリロケーションが各圧縮ブロック300a-dの最後にそのまま残されるからである。この場合、テレビジョンモニタのようなビデオ表示装置は、伸長器およびバス12を介してメモリ10に結合され、或いは、カメラまたはケーブル入力のようなビデオソースが圧縮器およびバス12を介してメモリ10に結合される。

#### 【0033】

圧縮器144および伸長器142は、好ましくは、各圧縮ブロック内の圧縮データの長さをブロック内の特定の非圧縮データに適応させる可変長圧縮を使用する。これは、メモリおよびバス帯域幅使用量を最小化することが可能である。

#### 【0034】

画像データ、または、音声データのようなその他の知覚データの場合に、ある種の情報の損失を犠牲にしてデータを圧縮する非可逆圧縮が使用される。これは、同様にメモリおよびバス帯域幅使用量を最小化することが可能である。一実施形態では、圧縮率（したがって、損失の量）は動的に利用可能なバス帯域幅に動的に適応される。本実施形態では、バスモニタ装置（図示せず）が帯域幅使用量を決定するためバス12に結合される。これは、たとえば、プロセシングエレメント14が要求された帯域幅使用量を示すためバスモニタへ信号を送信するように設計されているとき、または、バスモニタが単位時間当たりに使用されていないバスサイクル数をカウントするときに実現できる。バスモニタは、動的に、または、圧縮データの書き込みを開始するためプロセシングエレメント14からの要求に応答して、圧縮器144の圧縮率を設定するため圧縮器144に結合される。

#### 【0035】

好ましくは、圧縮器144は、圧縮データのブロック内のワード数を示すため、圧縮データの各ブロックに長さコードを組み込む。長さコードは、たとえば、圧縮データよりも前にある圧縮ブロックの第1ワードに組み込まれる。かくして、ブロックのフォーマットは、

（ブロックの長さコード、圧縮データ）

である。伸長器142が圧縮ブロックを取り出すためにブロックアドレスを使用するとき、伸長器142は圧縮ブロックから長さコードを読み出し、ブロックアドレスのためのメモリ転送が何ワード後に終了されたかをメモリ10へ知らせるためこの長さコードを使用する。

#### 【0036】

代案として、圧縮器144は、メモリ10内の特定の圧縮ブロックに隣接する先行および/または後続の圧縮ブロック内の特定の圧縮ブロックごとに長さコードを記憶するよう構成される。

#### 【0037】

（先行および/または後続ブロックの長さコード、圧縮データ）

この場合、伸長器142は、メモリ転送に含まれるべきワード数を決定するため、最初に先行または後続のブロックを読み出す必要がある。ブロックは、メモリに格納された順序で大半が転送されるので、伸長器142は、一般に、次にフェッチされる圧縮ブロックのためのメモリ転送の長さを制御するために圧縮ブロックからの長さコードを保持することにより、長さコードを取り出すための付加的なメモリ転送を回避する。これは、メモリ転送の開始時に長さコードを供給できるようにする。一般に、データは一方向のアドレス

10

20

30

40

50

方向だけでアクセスされる。この場合、この一方向の隣接ブロックのための長さコードを特定の圧縮ブロックのそれぞれに格納すれば十分である。別の実施形態では、いずれかの方向に読み出すときに長さコードの別個の読み出しを回避するため、両方向の隣接ブロックの長さコードが収容される。この連続的な転送のプロセスが開始されるとき、第1のブロックの長さは未知である。このような場合、非圧縮長さの全体が転送され、1回目の転送に限り僅かな不利益が生じる。

#### 【0038】

さらに別の実施形態では、長さコードが特定の圧縮ブロックと共にメモリ10に収容された特定の圧縮ブロックは、連続的にブロックをアドレス指定する期待される方法に適応され、たとえば、一つおきの伸長ブロックを飛び越すことが期待されるならば、二つ先の圧縮ブロックの長さコードが各ブロックと共に収容される。さらなる実施形態では、長さコードが収容されている論理的に後に続くブロックを示すため、次のブロックコードがブロックと共に収容される。この場合、ブロックフォーマットは、たとえば、

(論理的に後に続くブロックを識別するコード、論理的に次に続くブロックの長さコード、現在ブロックの圧縮データ)

10

である。

#### 【0039】

たとえば、圧縮画像データが記憶される一実施形態では、インターレース画像がアクセスされるとき、1本おきの画像ラインを飛び越すことが望ましい。それに応じて、各画像ラインの最後の長さコードは、1本おきの画像ラインの開始のための圧縮ワードの個数を記述するように構成される。

20

#### 【0040】

図4は、キャッシュメモリ40およびキャッシュ管理ユニット42を備えたプロセシングエレメントの一実施形態を表す。キャッシュメモリ40は、一方側のプロセッサ140と、反対側の圧縮器144および伸長器142との間に結合される。動作中に、キャッシュメモリ40は、伸長データの1個以上のブロックと、それに加えてキャッシュされたブロックのアドレスに関する情報を記憶する。プロセッサ140がキャッシュされたブロックからのデータをアドレス指定するとき、バス12へのアクセスは必要ない。プロセッサ140がキャッシュメモリ40にないデータをアドレス指定するとき、キャッシュ管理ユニット42は、伸長後にアドレス指定されたデータを取り出すことができる圧縮ブロックを取り出すように伸長器142をトリガーする。伸長器142は取り出されたブロックを伸長し、伸長ブロックをキャッシュメモリに書き込むので、その後にアドレス指定される。

30

#### 【0041】

必要に応じて、キャッシュ管理ユニット42は、前の非圧縮データのブロックのため使用されたキャッシュメモリ空間を再利用することにより、キャッシュメモリ40に余裕を作る。プロセッサ140がこのブロック内のデータを更新したとき、キャッシュ管理ユニット42は、最初に、非圧縮ブロックを圧縮し、圧縮ブロックをメモリ10(図示せず)に書き込むように圧縮器144へ信号を送る。ライトスルー(プロセッサ140がキャッシュメモリ40内のデータワードを更新するときに圧縮および書き込みを行う)、または、ライトバック(新しい非圧縮ブロックのためのキャッシュ空間が必要なときに限る)のような種々の従来型のキャッシュライトバック戦略が使用される。

40

#### 【0042】

圧縮データのブロックをメモリ10へ書き込むとき、圧縮器144は、一般に、プロセッサ140によって1ワードしか更新されなかったとしても、非圧縮データの全ブロックを必要とすることに注意すべきである。したがって、データワードを書き込むため、メモリ10から圧縮データのブロックを取り出し、圧縮データのブロックを伸長し(好ましくは、伸長器142を使用して)、非圧縮データのブロック内の関連した1ワード以上のデータワードを更新し、更新されたブロックを圧縮し、圧縮ブロックをライトバックしなければならない。しかし、一般には、非圧縮ブロックの多数の様々なデータワードは連続的

50

に更新される。好ましくは、ライトバックは、非圧縮ブロックの処理が完了したときに限り行われる。その上、多くの場合に、伸長ブロック内の全データは更新されるので、旧いブロックの伸長は必要ない。

#### 【0043】

一実施形態では、圧縮および伸長は任意的である。本実施形態では、圧縮ブロックと伸長ブロックの両方がメモリ10に記憶される。圧縮するかしないかの選択は、たとえば、圧縮制御レジスタ(図示せず)を設定することにより、または、データアドレスが所定のアドレスレンジの範囲内にあるとき圧縮を選択し、所定のアドレスレンジの範囲外にあるとき圧縮なしを選択することにより、プロセッサ140によって実行される。非圧縮データの場合、圧縮器144および142は、たとえば、一つ以上の特定のアドレスレンジの範囲外にあるデータアドレスに対して効果的に迂回される。データアドレスからのビットは、たとえば、圧縮データまたは非圧縮データがアドレス指定されたレンジ内のアドレスか、または、レンジ外のアドレスかを示すために使用される。10

#### 【0044】

別の実施形態では、伸長器142は、同じ圧縮データから、しかし、伸長データの徐々に小さくなる部分集合を使用して、それぞれに伸長情報を取得することができる一連の様々な圧縮オプションのうちの一つを使用するように構成される。メモリ内で、圧縮データのブロックごとに、最小の部分集合からのデータは最初に入れられ、その後には常に、次の大きさの部分集合を完成するために必要なさらなるデータが続く。たとえば、ブロックが一連の数字を用いて符号化されるとき、そのブロックの数字のより上位ビットを収容するワードは、最初にメモリに入れられ、次に、下位ビットを収容するワードが続けられ、該当するならば、さらに下位ビットを含むワードが続けられ、以下同様である、しかし、ブロックのサブサンプリングされた部分集合を表現する数字を入れるなどのような他の可能性も存在することが認められる。様々な圧縮オプションは、圧縮データの徐々に大きくなる部分集合を読み出し、それを用いて、伸長器は徐々に高品質の伸長データを再現することが可能である。ある特定の伸長オプションが使用されるとき、伸長器は、データの関連した部分集合が転送完了したときにメモリ転送を終了する。必要な転送の長さは使用されるオプションから計算され、妥当であれば、ブロックの長さコードから計算される(たとえば、より上位のビットが使用されるとき、転送されるべきビット数は、長さ(ブロック内の数字の個数)に使用されたより上位のビットの割合を掛けたものから得られる)。これにより、バス12上の帯域幅使用量は最小化される。2030

#### 【0045】

したがって、より少ないバス12の帯域幅使用量は、徐々に品質が低下する伸長を使用することによって達成される。プロセッサ14によって実行されるアルゴリズムの要求に応じて、プロセッサ14は、伸長アルゴリズムの一つを選択し、伸長器142に対し選択された伸長アルゴリズムの使用を命令する。かくして、帯域幅使用量はプロセッサ14の要求に適合される。同様に、バスマネージャ(図示せず)は、バス12のバス帯域幅使用量を決定し(従来の帯域幅使用量を決定する方法が利用される)、バス12上で利用可能な帯域幅に応じて伸長アルゴリズムを選択するように信号を送信するため設けられる。40

#### 【0046】

データキャッシュ40の他に、プロセシングエレメントは、プロセッサ140のための命令キャッシュ(図示せず)を具備する。好ましくは、命令キャッシュはバス12への別個のインターフェースを有する。命令は、好ましくは、伸長なしに読み出され、レイテンシーを最小化し、伸長データとは別個にキャッシュ管理される。

#### 【0047】

ここまで、連続的な圧縮ブロックが圧縮ブロックに対応する伸長ブロックの開始データアドレスの間の間隔に対応するアドレス間隔で記憶される方法を説明した。好ましくは、間隔は、単一のブロックアドレスに応答してバス12を介してマルチアドレスメモリ転送を開始するメモリシステムアーキテクチャによって規定されるような連続的な優先開始アドレスのペアの間の間隔に対応する。しかし、さらなる一実施形態では、間隔は、この間50

隔の整数倍に対応し、すなわち、他の優先開始アドレスによって分離された優先開始アドレスのペアの間の間隔に対応する。最大マルチアドレス転送長さが連続的な優先開始アドレスの間の間隔によって制限されるならば、この場合に圧縮ブロックのため利用可能なメモリ空間全体は単一のブロックアドレス 21 によってアドレス指定できない。これは、原理的に、複数のブロックアドレス 21 が圧縮ブロックにアクセスするために供給されるべきであることを意味する。圧縮ブロックが転送されるか、および / または、供給されたブロックアドレスでアクセスできる最終的なデータワード数を転送する必要がないとき、圧縮率に応じて 1 個以上のこれらのブロックアドレスが省略される。

#### 【 0 0 4 8 】

本コンテキストで理解されるべき点は、用語「圧縮データのブロック」は他のブロックを参照することなく伸長されるデータの集まりを表すが、圧縮ブロックからの全データがブロック内のいずれかのワードを伸長するために必要であるということを意味しないということである。たとえば、圧縮データのブロックは、独立に伸長され得る圧縮データにより構成された多数のサブブロックを含む。同様に、ハフマン符号化のような可変長符号化が使用されるならば、非圧縮データの特定のアドレスに対するワードの開始点を決定するためだけに、他のワードのデータを参考にする必要がある。

#### 【 0 0 4 9 】

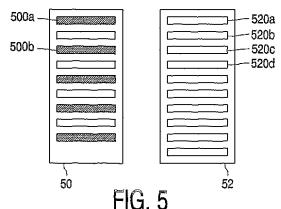

図 5 は、ブロックの開始アドレスの間の非常に大きい間隔を利用する物理的なメモリ占有 50 の一実施例を表す。本実施例では、圧縮率は 2 である。その結果として、転送のための 2 個のブロックアドレスを要求する伸長データ 520a、b は、1 個のブロックアドレスごとに転送できるサイズのメモリ空間 500a、b（斜線領域で表される）に圧縮データとして格納される。このサイズの一つおきのメモリ空間（斜線なしの領域として表される）は圧縮データによって占有されず、その内容を転送する必要はない。かくして、メモリ 10 へ供給されるべきブロックアドレスの個数は半分になる。他の圧縮率の場合、他の個数のメモリ空間が開放されることが分かるであろう。

#### 【 0 0 5 0 】

原理的に、伸長ブロック内のアドレスを用いて容易にアドレス指定するため開放されたメモリ内の中間の空間は該当するデータがない。しかし、本発明から逸脱することなく、他のデータが他のプロセスによって使用するためこれらの中間の空間に格納される。さらに、他のブロックからの圧縮データのコピーがこれらの中間の空間に格納される。この場合、ルックアヘッドは、好ましいアドレスの間の全空間からデータを取り込むことにより、一部の演算において実現される。しかし、当然ながら、中間の空間のこのデータは、次の圧縮データのブロックが開始する次の優先開始アドレスを通り過ぎない。

#### 【 0 0 5 1 】

さらに、伸長データの一部は圧縮データに依存しないダミーデータであることが分かるであろう。その結果として、2 個のブロックアドレスの間に格納された圧縮データから伸長を使用して実際に取得されるデータワード数は、実際には、これらの 2 個のブロックアドレスの間のデータワード数よりも少ない。その上、圧縮データのブロック（オプションとして長さ情報を含む）は、好ましくは、優先開始アドレスから直ちに開始するが、本発明から逸脱することなく、オフセットが使用されることが分かるであろう。この場合、優先開始は、依然としてマルチアドレスメモリ転送の開始アドレスであるが、転送の開始からの一部の転送データは伸長のため使用されない状態で残される。同様に、マルチアドレス転送の終了アドレスを、圧縮ブロックの最終アドレスの少し向こうへオフセットさせることができある。帯域福利得は、次の優先開始アドレスまでの一部のデータを転送されないまま残して転送を終了する限り、依然として実現される。

#### 【 0 0 5 2 】

本発明は、非圧縮データのアドレスを明示的に供給するプロセシングエレメントと、メモリ内の圧縮ブロックをアドレス指定するためプロセシングエレメントによって供給されたアドレスを使用する圧縮器および伸長器との観点で説明されているが、プロセシングエレメントは、たとえば、アドレスの隣接アドレス（たとえば、右側の画素、または、時間

10

20

30

40

50

的な信号の後のサンプル)への変更を示すために圧縮器または伸長器に「次」を信号で送ることにより、データを非明示的にアドレス指定してもよいことが分かるであろう。本発明が有利であるのは、非圧縮データのアドレスが圧縮データのブロックのメモリアドレスへ直接的に変換されるためだけでなく、ランダムアクセスの場合に廃棄されることになる不要なブロックのためのデータをフェッチしなくてもよいからである。様々なブロックの開始点に関して管理を続ける必要がない。

## 【0053】

本発明は、好ましくは、非圧縮データのアドレスの同じサイズのサブレンジ内のデータをそれぞれに表現する圧縮ブロックに適用されるが、本発明から逸脱することなく、種々のサイズのサブレンジが様々なブロックのため使用されることが分かるであろう。

10

## 【図面の簡単な説明】

## 【0054】

【図1】データ処理装置を表す図である。

【図2】メモリアクセスを示す図である。

【図3】メモリ占有を表す図である。

【図4】プロセシングエレメントを表す図である。

【図5】メモリ占有を表す図である。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【国際調査報告】

60500810482

## INTERNATIONAL SEARCH REPORT

Inten - National Application No

PCT/TB2004/050426A. CLASSIFICATION OF SUBJECT MATTER

G06F12/02 H03M7/30 G06F12/08

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G06F

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                 | Relevant to claim No. |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | US 6 175 896 B1 (BUI TUAN H)<br>16 January 2001 (2001-01-16)<br>abstract<br>figures 2,3<br>column 1, line 27 - column 2, line 41<br>column 3, line 45 - column 4, line 44<br>column 5, line 25 - column 6, line 40 | 1-22                  |

| A        | US 6 263 413 B1 (MOTOMURA MASATO ET AL)<br>17 July 2001 (2001-07-17)<br>figure 2<br>column 4, line 6 - line 43                                                                                                     | 1-22                  |

| A        | US 5 392 417 A (IYENGAR ET AL)<br>21 February 1995 (1995-02-21)<br>column 3, line 45 - column 4, line 13                                                                                                           | 5,6,15                |

|          |                                                                                                                                                                                                                    | -/-                   |

Further documents are listed in the continuation of box C. Patent family members are listed in annex.

## \* Special categories of cited documents:

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the International filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the International search

22 November 2005

Date of mailing of the International search report

29/11/2005

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Jardon, S

29. 6. 2006

2

| INTERNATIONAL SEARCH REPORT                          |                                                                                                                                                                                                                                                        | Int'l. Application No<br>PCT/IB2004/050426 |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                        |                                            |

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                     | Relevant to claim No.                      |

| A                                                    | US 5 864 859 A (FRANASZEK ET AL)<br>26 January 1999 (1999-01-26)<br>figure 2<br>column 1, line 61 - column 2, line 14<br>-----                                                                                                                         | 1                                          |

| A                                                    | WELCH T A: "A TECHNIQUE FOR<br>HIGH-PERFORMANCE DATA COMPRESSION"<br>COMPUTER, IEEE SERVICE CENTER, LOS<br>ALAMITOS, CA, US,<br>vol. 17, no. 6, 1 June 1984 (1984-06-01),<br>pages 8-19, XP000673349<br>ISSN: 0018-9162<br>the whole document<br>----- | 8,9,13,<br>19-21                           |

| 1                                                    |                                                                                                                                                                                                                                                        |                                            |

3**INTERNATIONAL SEARCH REPORT**

Information on patent family membersInternational Application No

PCT/IB2004/050426

| Patent document cited in search report | Publication date | Patent family member(s) |                                       | Publication date                       |

|----------------------------------------|------------------|-------------------------|---------------------------------------|----------------------------------------|

| US 6175896                             | B1 16-01-2001    | NONE                    |                                       |                                        |

| US 6263413                             | B1 17-07-2001    | CN<br>JP<br>JP          | 1201238 A<br>3127853 B2<br>10301841 A | 09-12-1998<br>29-01-2001<br>13-11-1998 |

| US 5392417                             | A 21-02-1995     | NONE                    |                                       |                                        |

| US 5864859                             | A 26-01-1999     | US                      | 6240419 B1                            | 29-05-2001                             |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,M,D,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100082991

弁理士 佐藤 泰和

(74)代理人 100096921

弁理士 吉元 弘

(74)代理人 100103263

弁理士 川崎 康

(74)代理人 100118876

弁理士 岡澤 順生

(72)発明者 アブラハム、カー・リーメンス

オランダ国 5 6 5 6、アーアー、アインドーフェン、ケアオブ、プロフ・ホルストラーン、6

(72)発明者 レナトゥス、イエー・ファン、デル、フレウテン

オランダ国 5 6 5 6、アーアー、アインドーフェン、ケアオブ、プロフ・ホルストラーン、6

(72)発明者 ピーター、ファン、デル、ボルフ

オランダ国 5 6 5 6、アーアー、アインドーフェン、ケアオブ、プロフ・ホルストラーン、6

F ターム(参考) 5B060 GA18